Page 1

TP400 PC/104-PLUS

PC COMPATIBLE COMPUTER

TECHNICAL REFERENCE MANUAL

Revision B00 19 February 2001

TRM-TP400 158004.B00 CGP

Page 2

(This page is intentionally left blank)

Page 3

All information in this manual is believed to be accurate and reliable. However, no

responsibility is assumed by DSP Design Limited for its use. Since conditions of

product use are outside our control, we make no warranties express or implied in

relation thereto. W e therefore cannot accept any liability in connection with any use

of this information. Nothing herein is to be taken as a license to operate under or a

recommendation to infringe any patents.

Whilst every ef fort has been made to ensure that this document is correct , er rors can

occur. If you find any errors or omissions please let us know, so that we can put this

right.

All information contained in this manual is proprietary to DSP Design Limited and

cannot be reproduced without the consent of DSP Design Limit ed. The circuit design

and printed circuit board design is copyright of DSP Design Limited 2000.

DSP Design Limited

Tapton Park Innovation Centre

Brimington Road

Chesterfield S41 0TZ

United Kingdom

Tel +44 (0) 1246 545 910

Fax +44 (0) 1246 545 911

Email sales@dspdesign.com

Web: www.dspdesign.com

Page 4

(This page is intentionally left blank).

Page 5

158004.B00 i

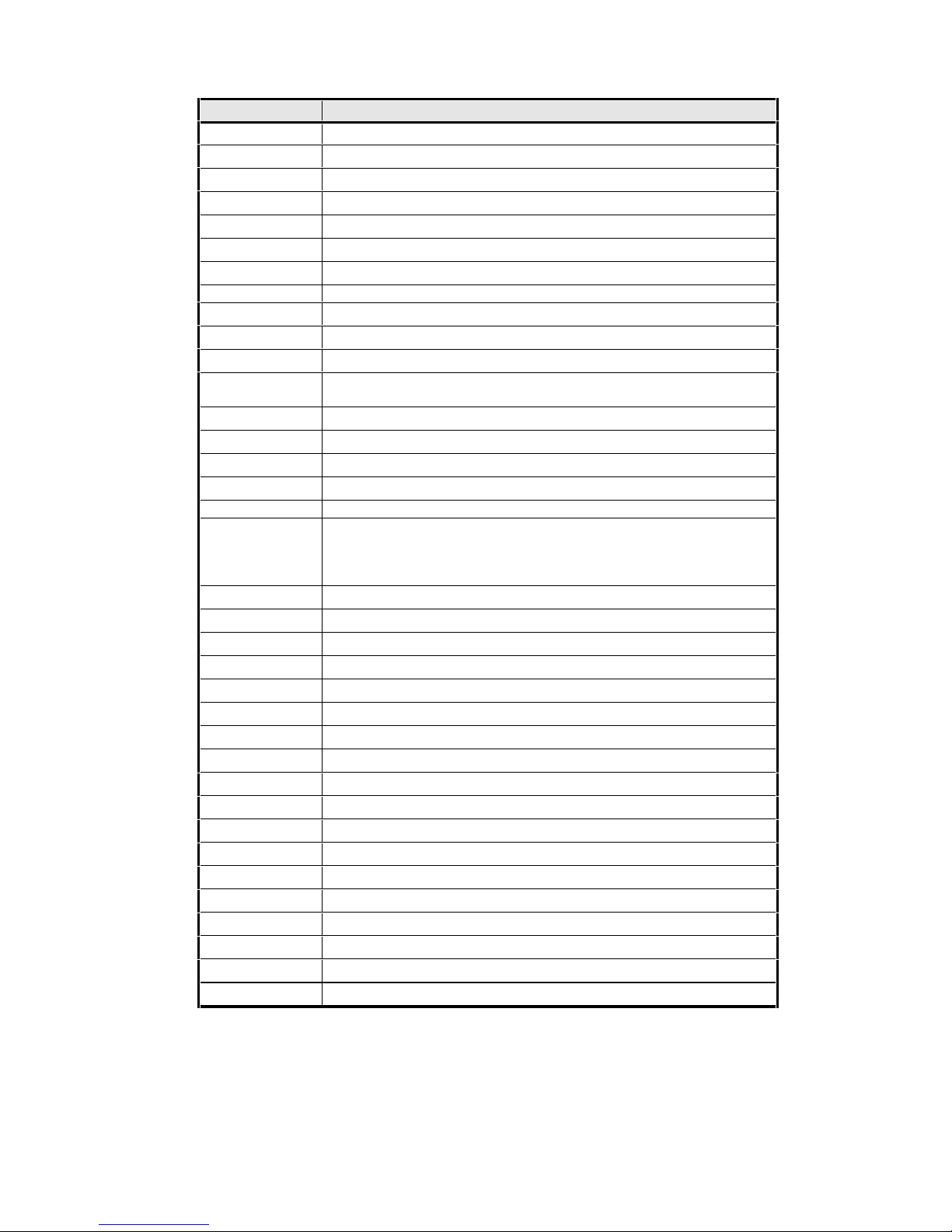

CONTENTS

1 INTRODUCTION ..................................................................................................1

1.1 OVERVIEW .......................................................................................................................................1

1.2 TP400 FEATURES............................................................................................................................2

1.3 PC/AT COMPATIBILITY....................................................................................................................3

1.4 PC/104-PLUS AS A PC EXPANSION BUS......................................................................................4

1.5 THE TP400 ARCHITECTURE..........................................................................................................4

1.6 GETTING STARTED QUICKLY .......................................................................................................7

1.6.1 TCDEVPLUS and TCDEV Development Systems ..................................................................7

1.6.2 Using the TCDEVPLUS Development System ........................................................................8

1.6.3 Using the Rev D TCDEV Development System.......................................................................9

1.6.4 TCONN Connector Breakout Board .......................................................................................11

1.7 AVOIDING COMMON PROBLEMS................................................................................................12

2 PROCESSOR AND MEMORY...........................................................................13

2.1 PROCESSOR..................................................................................................................................13

2.2 CLOCK.............................................................................................................................................15

2.3 SDRAM............................................................................................................................................16

2.4 FLASH MEMORY............................................................................................................................17

2.5 MEMORY ADDRESS MAP.............................................................................................................18

3 PERIPHERALS...................................................................................................19

3.1 I/O ADDRESS MAP.........................................................................................................................19

3.2 SUPER I/O CHIP.............................................................................................................................21

3.3 EXTRA UART..................................................................................................................................21

3.4 SERIAL PORTS...............................................................................................................................21

3.4.1 Signals, Addressing and Interrupts.........................................................................................21

3.4.2 RS-485 Operation....................................................................................................................22

3.4.3 Disabling Serial Ports ..............................................................................................................23

3.4.4 Extended Modes......................................................................................................................23

3.4.5 Infra-Red Operation Modes.....................................................................................................23

3.5 PRINTER PORT..............................................................................................................................24

3.6 REAL TIME CLOCK........................................................................................................................25

3.7 KEYBOARD AND MOUSE..............................................................................................................26

3.8 FLOPPY DISK DRIVE.....................................................................................................................27

3.9 IDE DISK DRIVE..............................................................................................................................27

3.10 DISPLAY CONTROLLER................................................................................................................29

3.10.1 Overview..................................................................................................................................29

3.10.2 Using CRTs and TFT LCDs....................................................................................................30

3.10.3 External Graphics Cards, and No Graphics ...........................................................................31

3.10.4 Native Display Drivers.............................................................................................................32

3.10.5 The System Management Interrupt Issue ..............................................................................32

3.10.6 PanelLink.................................................................................................................................33

3.10.7 TV Clock..................................................................................................................................33

3.11 VIDEO PLAYBACK..........................................................................................................................34

3.12 AUDIO RECORDING AND PLAYBACK.........................................................................................34

3.13 SPEAKER........................................................................................................................................34

3.14 USB PORTS....................................................................................................................................35

3.15 ETHERNET .....................................................................................................................................35

3.16 ANALOG TO DIGITAL CONVERTER............................................................................................36

3.17 SERIAL EEPROM ...........................................................................................................................38

3.18 UTILITY REGISTER........................................................................................................................38

Page 6

ii 158004.B00

4 STAND-ALONE OPERATION AND EXPANSION BUSES...............................40

4.1 STAND-ALONE OPERATION........................................................................................................ 40

4.2 PC/104 BUS.................................................................................................................................... 40

4.3 PC/104-PLUS BUS........................................................................................................................... 41

4.4 PC/104 AND PC/104-PLUS CLOCK AND RESET SIGNALS.........................................................43

4.4.1 PC/104 Clock and Reset Signals............................................................................................ 43

4.4.2 PC/104-Plus Clock and Reset Signals ...................................................................................43

4.5 INTERRUPTS .................................................................................................................................44

4.5.1 On-Board and PC/104 Bus Interrupts..................................................................................... 44

4.5.2 PC/104-Plus Bus Interrupts ....................................................................................................45

4.5.3 Plug and Play Control of Interrupts......................................................................................... 46

4.6 DMA.................................................................................................................................................47

5 HARDWARE RESET OPTIONS ........................................................................48

5.1 POWER SUPPLY MONITOR......................................................................................................... 48

5.2 ONBOARD WATCHDOG TIMER...................................................................................................48

5.3 RESET SWITCH.............................................................................................................................49

5.4 RESETTING THE PC/104 AND PC/104-PLUS BUSES .................................................................49

6 SOFTWARE...........................................................................................................50

6.1 SYSTEM BIOS................................................................................................................................50

6.2 BIOS SETUP PROGRAM...............................................................................................................50

6.2.1 Operation of the Setup Program............................................................................................. 51

6.2.2 Reducing Boot Time ...............................................................................................................52

6.3 VGA BIOS AND OTHER BIOS EXTENSIONS.............................................................................. 52

6.3.1 Principles of Operation............................................................................................................ 52

6.3.2 The VGA BIOS Extension.......................................................................................................52

6.3.3 The Flash File System BIOS Extension .................................................................................53

6.4 MS-DOS AND OTHER OPERATING SYSTEMS..........................................................................53

6.5 FLASH MEMORY PROGRAMMING............................................................................................. 54

6.5.1 Programming the 2M byte 29F016 Flash Chips.....................................................................54

6.5.2 Programming the 4M byte 29F032 Flash Chips.....................................................................56

6.5.3 Steps to Perform after Programming BIOS............................................................................ 57

6.6 FLASH FILE SYSTEM.................................................................................................................... 57

6.6.1 Overview..................................................................................................................................58

6.6.2 Operation of the Flash File System ........................................................................................59

6.6.3 Write Operations and Garbage Collection.............................................................................. 60

6.6.4 Flash File System Statistics....................................................................................................61

6.7 SAVING CMOS RAM DATA IN THE SERIAL EEPROM............................................................... 62

6.8 SERIAL EEPROM PROGRAMMING.............................................................................................63

6.9 WATCHDOG TIMER PROGRAMMING ........................................................................................64

7 POWER MANAGEMENT ...................................................................................65

Page 7

158004.B00 iii

APPENDIX A: SPECIFICATION...............................................................................A1

APPENDIX B: TP400 SET-UP PROCEDURE.........................................................B1

B.1 PROCESSOR COOLING................................................................................................................B1

B.2 SDRAM CONFIGURATION............................................................................................................B1

B.3 SOLDER LINK AREAS....................................................................................................................B2

LK1 - LK4 Not Present .....................................................................................................................B2

LK5 PME# Connection........................................................................................................................B2

LK6 VREF or Microphone..................................................................................................................B2

LK7 ADC0 or LINE_IN_R....................................................................................................................B2

LK8 ADC1 or LINE_IN_L....................................................................................................................B3

LK9 ADC2 or LINE_OUT_R ...............................................................................................................B3

LK10 ADC3 or LINE_OUT_L............................................................................................................B3

LK11 A/D Converter Reference........................................................................................................B3

LK12 Clock Shutdown.......................................................................................................................B3

LK13 Super I/O Configuration...........................................................................................................B3

LK14 VREF or Microphone..............................................................................................................B4

LK15 COM2 RS-232/RS-485 Selection ...........................................................................................B4

LK16 Remote Bootstrap ...................................................................................................................B4

LK17 Not Present..............................................................................................................................B4

LK18 PC/104-Plus VI/O Selection....................................................................................................B4

LK19 PanelLink Disable....................................................................................................................B4

LK20 PanelLink Power......................................................................................................................B5

LK100 - LK102 Processor Clock Speed ..............................................................................................B5

LK103 A/D Converter Input ADC3......................................................................................................B5

LK104 - LK107 Vcore Voltage Selection. ................................................................................................B6

LK108 Power Supply Clock ................................................................................................................B6

LK109 Ethernet Serial EEPROM........................................................................................................B6

LK110 Ethernet TxD Circuit................................................................................................................B6

LK111 Ethernet PCI Slot Selection.....................................................................................................B6

LK112 Ethernet PCI Interrupt Selection..............................................................................................B6

LK113 SDRAM Clock Feedback ........................................................................................................B7

LK114 IDE /PDIAG Pin .......................................................................................................................B7

APPENDIX C: MECHANICAL DRA WINGS AND SCHEMATICS........................... C1

APPENDIX D: OPTIONS AND ORDERING INFORMATION..................................D1

D.1 PROCESSOR BOARDS................................................................................................................D1

D.2 SDRAM MEMORY MODULES...................................................................................................... D1

D.3 TP400 PROCESSOR STARTER PACK........................................................................................ D2

D.4 PC/104 I/O BOARDS...................................................................................................................... D3

D.5 ACCESSORIES.............................................................................................................................. D4

APPENDIX E: CONNECTOR PIN ASSIGNMENTS ................................................ E1

E.1 SUMMARY OF CONNECTORS.....................................................................................................E1

E.2 EXPANSION BUS CONNECTORS................................................................................................E2

E.3 TP400 PERIPHERAL CONNECTOR.............................................................................................E5

E.4 COM3, COM4 SERIAL PORT CONNECTOR................................................................................E7

E.5 AUDIO, A/D CONVERTOR AND CRT CONNECTOR ..................................................................E7

E.6 PANELLINK CONNECTOR ...............................................................................................................E8

E.7 FLAT PANEL CONNECTOR ..........................................................................................................E9

E.8 USB CONNECTOR...................................................................................................................... E10

E.9 IDE CONNECTOR ....................................................................................................................... E11

E.10 FLOPPY CONNECTOR............................................................................................................... E12

E.11 POWER SUPPLY AND FAN CONNECTORS............................................................................ E13

E.12 ETHERNET CONNECTOR ......................................................................................................... E13

E.13 INTER-BOARD CONNECTORS.................................................................................................. E14

Page 8

iv 158004.B00

APPENDIX F: TFTIF FLA T PANEL INTERFACE BOARDS...................................... F1

F.1 INTRODUCTION.............................................................................................................................F1

F.2 INSTALLATION...............................................................................................................................F2

F.3 CABLE LENGTHS...........................................................................................................................F2

F.4 TFTIF CONNECTOR AND SOLDER LINKS.................................................................................F3

F.5 TFTIF41 CONNECTOR AND SOLDER LINKS.............................................................................F4

F.6 TFTIF31 CONNECTOR AND SOLDER LINKS.............................................................................F5

F.7 TFTIFS15 CONNECTOR AND SOLDER LINKS...........................................................................F7

APPENDIX G: CF100 COMPACT FLASH IDE DRIVE...............................................G1

G.1 INTRODUCTION............................................................................................................................ G1

G.2 INSTALLING THE CF100 ONTO THE TP400.............................................................................. G1

G.2.1 Direct Connection................................................................................................................... G1

G.2.2 Cable Connection................................................................................................................... G2

G.3 INSTALLING THE COMPACT FLASH CARD INTO THE CF100................................................ G2

G.4 CONFIGURING THE TP400 FOR THE CF100 AND CARD........................................................ G2

G.5 USING COMPACT FLASH CARDS.............................................................................................. G3

G.5.1 Hot Plugging........................................................................................................................... G3

G.5.2 Formatting and Making the Card Bootable............................................................................ G3

G.5.3 Configuring the CF100 as a slave drive................................................................................. G3

G.6 ACCESSORIES.............................................................................................................................. G4

G.7 DIMENSIONS................................................................................................................................. G4

APPENDIX H: RELIABILITY.......................................................................................H1

H.1 ASSUMPTIONS AND METHODOLOGY.......................................................................................H1

H.1.1 Reliability Standard..................................................................................................................H1

H.1.2 Methodology............................................................................................................................H1

H.1.3 Failure Effect Assumptions.....................................................................................................H2

H.2 RELIABILITY DATA USEAGE........................................................................................................H2

H.2.1 Operating Temperature...........................................................................................................H2

H.2.2 Flash Memory Usage..............................................................................................................H2

H.2.3 Usage Environment.................................................................................................................H2

H.2.4 Sensitivity Analysis..................................................................................................................H3

H.3 RELIABILITY DATA ............................................................................................................... .........H3

APPENDIX J: TP400ET ETHERNET ADAPTER BOARD..........................................J1

APPENDIX K: TP400 USB ADAPTER BOARD.........................................................K1

APPENDIX L: FAULT REPORTING ...........................................................................L1

Page 9

158004.B00 v

TABLES

TABLE 1 - TP400 PERFORMANCE RATINGS.........................................................................................14

TABLE 2 - TP400 ADDRESS MAP - FIRST 1M BYTE.............................................................................18

TABLE 3 - ON-BOARD I/O DEVICES.......................................................................................................20

TABLE 4 - SDRAM ALLOCATED TO DISPLAY CONTROLLER ............................................................29

TABLE 5 - TFT PANEL DISPLAY RESOLUTIONS..................................................................................30

TABLE 6 - CRT DISPLAY RESOLUTIONS ..............................................................................................31

TABLE 7 - UTILITY REGISTER BIT ALLOCATIONS...............................................................................39

TABLE 8 - PCI BUS RESOURCE ALLOCATIONS ..................................................................................42

TABLE 9 - INTERRUPT ALLOCATION....................................................................................................45

TABLE B1 - SODIMM MODULES..............................................................................................................B1

TABLE B2 - PROCESSOR CLOCK SPEED.............................................................................................B5

TABLE B3 - VCORE VOLTAGE SELECTION..........................................................................................B6

TABLE D1 - PROCESSOR BOARDS...................................................................................................... D1

TABLE D2 - SDRAM MEMORY MODULES............................................................................................ D1

TABLE D3 - CONTENTS OF THE TP400PAK........................................................................................ D2

TABLE D4 - PC/104 I/O BOARDS............................................................................................................ D3

TABLE D5 - TP400 ACCESSORIES........................................................................................................ D4

TABLE D6 - COMPACT FLASH ACCESSORIES ................................................................................... D5

TABLE E1 - CONNECTORS USED ON TP400 MAIN BOARD...............................................................E1

TABLE E2 - CONNECTORS USED ON TP400 DAUGHTER BOARD ...................................................E1

TABLE E3 - PC/104 J2 PIN ASSIGNMENTS ...........................................................................................E2

TABLE E4 - PC/104 J1 PIN ASSIGNMENTS ...........................................................................................E3

TABLE E5 - PC/104-PLUS J3 PIN ASSIGNMENTS ................................................................................E4

TABLE E6 - RS485 FUNCTION OF COM2 SERIAL PORT.....................................................................E5

TABLE E7 - J4 I/O CONNECTOR PIN ASSIGNMENTS..........................................................................E6

TABLE E8 - J5 COM3, COM4 CONNECTOR PIN ASSIGNMENTS.......................................................E7

TABLE E9 - J6 VGA AND A/D CONNECTOR PIN ASSIGNMENTS.......................................................E8

TABLE E10 - J7 PANEL LINK CONNECTOR PIN ASSIGNMENTS.......................................................E8

TABLE E11 - J8 FLAT PANEL CONNECTOR PIN ASSIGNMENTS ......................................................E9

TABLE E12 - FUNCTION OF FLAT PANEL SIGNALS......................................................................... E10

TABLE E13 - J9 USB CONNECTOR PIN ASSIGNMENTS.................................................................. E10

TABLE E14 - J101 IDE CONNECTOR PIN ASSIGNMENTS............................................................... E11

TABLE E15 - J103 FLOPPY CONNECTOR PIN ASSIGNMENTS....................................................... E12

TABLE E16 - J101 POWER SUPPLY CONNECTOR PIN ASSIGNMENTS........................................ E13

TABLE E17 - J102 POWER SUPPLY CONNECTOR PIN ASSIGNMENTS........................................ E13

TABLE F1 - TFTIF BOARDS AND THEIR DISPLAYS.............................................................................F1

TABLE F2 - TFTIF DISPLAY PIN ASSIGNMENTS..................................................................................F3

TABLE F3 - TFTIF41 DISPLAY PIN ASSIGNMENTS..............................................................................F4

TABLE F4 - TFTIF41 SOLDER LINK CONNECTIONS............................................................................F5

TABLE F5 - TFTIF31 DISPLAY PIN ASSIGNMENTS..............................................................................F5

TABLE F6 - TFTIF31 SOLDER LINK CONNECTIONS............................................................................F6

TABLE F7 - TFTIF31 AND TFTIF41 J3 PIN ASSIGNMENTS .................................................................F6

TABLE F8 - TFTIFS15 J4 PIN ASSIGNMENTS.......................................................................................F7

TABLE F9 - TFTIFS15 PIN ASSIGNMENTS............................................................................................F8

TABLE H1 - TP400 RELIABILITY DATA.................................................................................................. H5

Page 10

vi 158004.B00

FIGURES

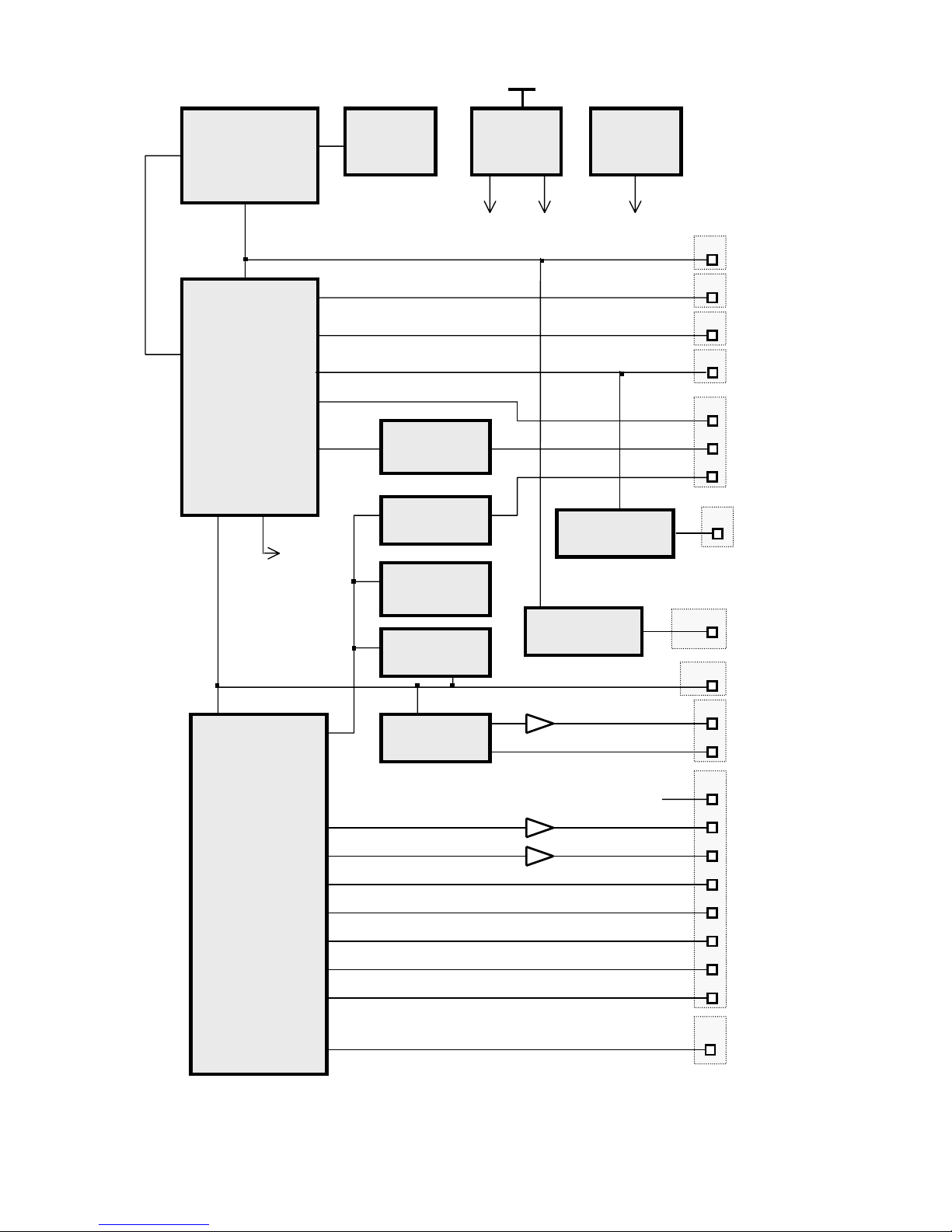

FIGURE 1

- TP400 BLOCK DIAGRAM....................................................................................................... 6

FIGURE 2 - RECOMMENDED BATTERY BACK-UP CIRCUIT ..............................................................26

FIGURE C1 - MAIN BOARD TOP COMPONENT PLACEMENT ............................................................C2

FIGURE C2 - MAIN BOARD BOTTOM COMPONENT PLACEMENT....................................................C3

FIGURE C3 - DAUGHTER BOARD TOP COMPONENT PLACEMENT.................................................C4

FIGURE C4 - DAUGHTER BOARD BOTTOM COMPONENT PLACEMENT ........................................C5

FIGURE C5 - MAIN BOARD MECHANICAL DIMENSIONS....................................................................C6

FIGURE C6 - DAUGHTER BOARD MECHANICAL DIMENSIONS.........................................................C7

FIGURE H1 - TP400 MEAN TIME TO FAILURE......................................................................................H4

FIGURE H2 - TP400 UNIT FAILURE RATE.............................................................................................H4

FIGURE J1 - TP400ET MECHANICAL DRAWINGS ...............................................................................J2

FIGURE J2 - TP400ET CIRCUIT DIAGRAM............................................................................................ J2

FIGURE K1 - TP300USB MECHANICAL DRAWINGS............................................................................K2

FIGURE K2 - TP300USB CIRCUIT DIAGRAM.........................................................................................K2

REVISION HISTORY

B00 First release of this manual.

Page 11

158004.B00 1

1 INTRODUCTION

1.1 OVERVIEW

To maintain our lead in advanced and highly integrated PC compatible computers,

DSP Design have released a very highly integrated, high performance processor

board compliant with the PC/104-Plus V1.1 specification. The board has been

specially designed to allow low power operation.

This processor card is fitted with the National Semiconductor Geode GX1 high

integration processor chip set, which operates at up to 300MHz. The Geode GX1 is a

Pentium-class processor, with MMX instruction set capability. The Geode GX1

incorporates a high-perf ormance graphics controller and audio processor. The chip

set integrates many of the functions commonly found in core logic chips on PC

motherboards and provides a num ber of power saving features. Both ISA bus and

PCI bus interfaces are provided.

The consequence of using the Geode GX1 chip set is that an extremely high

performance PC compatible computer can be implemented in a very small form

factor.

The TP400 is the first processor board from DSP Design that complies with the

PC/104-Plus standard. The PC/104-Plus standard adds a PCI bus interface to the

PC/104 standard, thus allowing the use of high- performance PCI expansion boards

while retaining the small size and rugged construction of t he PC/104 bus boards. The

PCI bus connector is a 120-pin connector on the edge of the PCB opposite the

PC/104 connectors.

The board supports up to 256M bytes of high-speed SDRAM. It also features the

standard PC compatible floppy and IDE disk interfaces, serial ports, parallel port,

keyboard interface, PS/2 mouse port and the standard PC speaker. The powerful

graphics controller in the Geode GX 1 can dr ive both CRT and flat panel displays, and

a SoundBlaster-compatible sound system is also implemented in the Geode GX1.

Two USB ports, a 10/100Base-T Ethernet interface and an A/D converter are also

provided.

The TP400 is a single board PC/104-Plus compatible comput er t hat can operate as a

stand-alone module or can be used in a system consisting of a number of other

PC/104 or PC/104-Plus modules.

The standard TP400 boards are provided with Flash File System software, which

converts the on-board 2M byte flash chip into a solid-state read/write disk drive. Up t o

8M bytes of Flash memory can be fitted, subject to a minimum order quantity.

A range of other PC/104 boards is available from DSP Design. Various designs

include the TP300, An earlier version of the T P400 with 10base-T Ethernet, and the

TB486, a highly integrated low-power single board computer. A wide range of I/O

boards is available. Contact DSP Desig n f or up- to-dat e inf orm ation on ot her product s

in our range.

The TP400 provides connectors with the same pin assignments as other DSP Design

processor boards, for easy upgrading.

Page 12

2 158004.B00

1.2 TP400 FEATURES

• High integration processor: a Geode GX1 processor is fitted, running at up to

300MHz.

• PC/104 V2.3 16-bit bus interface for wide compatibility.

• PC/104-Plus connector is fitted to allow PCI expansion cards to be used.

• Floppy and IDE disk controllers.

• Four serial ports - three are RS-232 compatible and one provides TTL level

signals only. COM2 is user-configurable as RS-485.

• The CO M2 serial port can be optionally config ured for IrDA-compatible infrared

serial communications.

• Bi-directional Centronics parallel port. EPP and ECP compatible.

• Up to 256M bytes of SDRAM. SDRAM is implemented with a user-installable 144-

pin SODIMM module (dual in line memory module). 32M, 64M, 128M and 256M

byte modules are available.

• 2M-byte flash memory for BIOS and solid-state disk is fitted as standard.

Alternatively 4M or 8M bytes may be fitted by special order. A Flash File System

is provided with every TP400, to provide a read-write logical disk drive.

• Keyboard, PS/2 mouse and speaker ports.

• Two high-speed USB ports. Filter components and a dual USB socket are

provided on a small PCB (the T P300USB) which connects via twisted pair cable

to the TP400

• The Geode GX1 integrates graphics circuitry, providing VGA graphics on CRT

monitors at resolutions of up to 1280 x 1024 and TFT displays at resolutions of up

to 1024 x 768. The graphics accelerator uses part of the system memory for high

performance and low system cost. MMX instruction set and MPEG hardware

acceleration enhance video performance.

• High-speed serial PanelLink interface to drive displays over twisted pair cable at a

distance of up to 10m.

• The Geode GX1 integrates a SoundBlaster compatible sound system. The

TP400 can record and play back high-quality audio.

• 10/100Base-T Ethernet chip. The Ethernet magnetics and RJ45 socket are

provided on a small PCB (the TP400ET, an optional extra) that connects via

twisted pair cable to the TP400.

Page 13

158004.B00 3

• Powered by a single 5V supply. A switched mode power supply is provided to

efficiently produce 2.2V and 3.3V for the processor and memory that require

these voltages.

• Millennium compliant AT compatible calendar/clock chip uses external battery.

• A 512-byte size serial EEPROM is provided to retain set-up parameters in the

absence of an external battery. Space is also available for user data.

• Reset, power supply monitor and watchdog timer circuitry.

• Expansion is by way of a full-function PC/104 bus that complies with the V2.3

version of the PC/104 bus specification. High performance expansion is by way of

the PCI-compatible PC/104-Plus connector.

• The TCDEVPLUS Development System provides all the facilities to get your

TP400 running quickly, and is recommended for fast product development.

• Largely pin compatible with the TC386, TC486, TX486, TC586, TB486 and

TP300 processors.

1.3 PC/AT COMPATIBILITY

The TP400 offers an extremely high degree of compatibility with desktop PC

computers. This compatibility extends from the operating system level, through

BIOS-level compatibility to register-level compatibility.

The Geode GX1 chip set used on the TP400 board includes on-chip peripherals timers, interrupt controller, DMA controller etc. These are software compatible with

equivalent Intel peripheral chips used on the original IBM PC and PC/AT.

Around the Geode GX1 chip DSP Design has integrated floppy and IDE disk

controllers, a keyboard and mouse controller, four serial ports and a Centronics

parallel port. These peripherals are software and hardware compatible with the

standard PC.

The Geode GX1’s in-built graphics circuitry provides for VGA, SVGA and XGA

graphics. Windows drivers provide access to the high performance 2D graphics

accelerator engine. Audio logic within the Geode GX1 chip set is also software

compatible with SoundBlaster industry-standard sound chips. Note that some aspects

of the VGA and SoundBlaster circuitry are em ulated in software, which can lead to

some incompatibilities.

Page 14

4 158004.B00

1.4 PC/104-PLUS AS A PC EXPANSION BUS

Users can operate the TP400 as a single board computer . If expansion is required

I/O boards can be accessed via the PC/104 and PC/104-Plus interfaces provided on

the TP400.

The PC/104 bus is a compact version of the IEEE P996 (PC and PC/AT) bus,

optimized for embedded systems applications. DSP Design and other PC/104

manufacturers offer a wide range of I/O boards that will work with the TP400, in the

same manner that a conventional PC can be enhanced by the addition of expansion

boards.

The PC/104 I/O card range includes analog and digital I/O cards, serial comms, local

area network boards and other specialist functions. DSP Design manufactures a

number of PC/104 modules and is committed t o expanding this range. It is the policy

of DSP Design to introduce, where appropriate, new PC/104 I/O cards that are

software compatible with similar cards for the PC. This has the tremendous

advantage of allowing users to make use of the software that has already been

written for desktop PC cards.

The PC/104-Plus specificat ion enhances the PC/104 specification by adding a new

120-pin connector. This connector consists of four rows of thirty pins each arr anged

in a 2mm-pitch grid. It is positioned on the board edge opposite the PC/104 bus

connectors. This new connector carries the PCI bus signals, allowing the TP400 to

access high-performance PCI chips on expansion boards.

PC/104 and PC/104-Plus boards stack one on top of another, providing a compact,

rugged computer system. For details of the PC/104 bus specification and the

PC/104-Plus specification, see DSP Design’s web site.

Because the Geode GX1 may require a heat sink or fan, the T P400 must be the top

board in a stack of PC/104 boards.

1.5 THE TP400 ARCHITECTURE

The block diagram in Figure 1 shows the archit ecture of the TP400. The Geode GX1

processor is directly connected to the SDRAM through a 64-bit wide high-speed

memory bus. It also performs t he “north bridg e” functions, accessing most of the rest

of the circuitry through the PCI bus.

The CS5530A companion chip provides the south bridge funct ions, and implements

an ISA bus interface to the PC/104 bus and slower peripherals. The CS5530A

includes a high-speed Ultra-ATA disk interface, USB ports and motherboard

functions (timers, interrupt and DMA controllers etc).

A high-speed connection between the Geode GX1 and the CS5530A transfers

graphics and video data from the Geode GX1 to the CS5530A, which drives both

analog CRT monitor s and TFT LCD displays. A PanelLink interf ace chip is attached

to the TFT LCD interface.

The Geode GX1 and CS5530A are also linked by the PCI bus, which goes to the

Ethernet chip and to the PC/104-Plus connector.

Page 15

158004.B00 5

The audio processor logic in the CS5530A chip connects to an AC97 compatible

audio codec chip, which provides audio A/D and D/A conversions.

The CS5530A also provides a slower PC/104 bus (ISA bus), on which the Flash

memory and Super I/O chips are located. The Super I/O chip includes the floppy and

IDE disk controllers, serial and parallel I/O functions as well as the keyboard and

mouse controller. A second dual UART chip implements COM3 and COM4.

A 16-bit PC/104 interface allows the TP400 to perform memory and I/O accesses to

the PC/104 bus, and a PC104/Plus interface allows PCI bus transfers.

Page 16

6 158004.B00

FIGURE 1 - TP400 BLOCK DIAGRAM

+5V

PC/104-PLUS

Geode GX1

SDRAM

5530A

SUPER I/O

AC97

CODEC

A/D

E2PROM +

RESET

FLASH

UARTS

ETHERNET

SPKR

SPKR

CRT

Utility Register

POWER

SUPPLY

2.0V

3.3V

CLOCK

GEN.

J3

J10

IDE

J9

J8

USB

TFT

J6

CRT

AUDIO

A/D

ETHERNET

J106

J1/J2

PC/104

J5

COM3

COM4

SPEAKER

COM1

COM2

PRN

KBD

MOUSE

IRDA

BATT

FLOPPY

Video + Graphics

PCI Bus

RS232

RS232

RS232 / RS485

J4

J10

PANELLINK

PANELLINK

J7

Page 17

158004.B00 7

1.6 GETTING STARTED QUICKLY

This manual gives all of the inform ation that most users will need in order to operate

the TP400. This section g ives a quick introduction to g etting started. More details on

configuring the board are given in Appendix B: TP400 Setup Procedure. Those

people who have special requirements m ay require further information. If this is the

case our support engineer s will be pleased to help you, but please read the manual

first.

As well as reading this section, please read section 1.7 which identifies common

problems.

1.6.1 TCDEVPLUS and TCDEV Development Systems

DSP Design strongly recommend developing with the TCDEVPLUS Development

System, as in our experience this significantly reduces development tim e and users’

technical problems.

The TCDEVPLUS is a PC/104 based development platform. It supercedes the

TCDEV development system that many DSP Design’s customers may already have.

The TCDEVPLUS adds new features to those of the TCDEV, and customers who

already have a TCDEV can continue to use it, although they will not benefit f rom the

new features added to the TCDEVPLUS. Throughout this manual the term

“TCDEVPLUS” can be read as “TCDEV or TCDEVPLUS”, except where explicitly

noted. In particular, jumper areas E2 – E7 have the same functions on both boards.

The features of the TCDEVPLUS include an on-board VGA g raphics controller with

15 pin VGA connector, a floppy and hard disk controller , a floppy drive plus cable,

PC/AT and PCI slots f or interfacing standard PC and PCI bus cards to the PC/104

bus and a battery for CMOS RAM backup. The TCDEVPLUS has all the st andard PC

connectors for interf acing to the outside world. These include serial port 9-way D-type

connectors, a parallel port 25-way D-type connector, a VGA connector and PS/2 style

keyboard and mouse connectors. Connectors for the TP400’s Ethernet and USB

ports are also provided on the TCDEVPLUS (but not on the TCDEV).

The TCDEVPLUS (but not the TCDEV) provides convenient options for connecting t o

2.5” and 3.5” IDE drives, CD-ROM drives and Compact Flash cards. It allows power

consumption to be monitored and provides diagnostic LEDs with programmable

address decoding. It also supports DSP Design’s GCAT486 range of embedded PC

computers.

DSP Design also supply the TPPSU, which is a compact 45W power supply with

cabling to make it easy to use with the TCDEVPLUS. The 25W TCPSU power supply

that we have supplied with the TCDEV in the past may not have enough capacity to

drive the TP400 and TCDEVPLUS, particularly if disk drives and other peripherals are

used. Users with a TCPSU should ensure they obtain the TPPSU supply.

Most users will find getting started with the TP400 and TCDEVPLUS simplicity itself.

The TP400 plugs directly onto the TCDEVPLUS. A 50-way ribbon cable connects the

TP400 J4 I/O connector to the TCDEVPLUS. This links the COM1 and COM2 serial

ports, parallel port, and keyboard and m ouse onto the TCDEVPLUS, and in turn to

the PC compatible connectors mounted on t he edge of the T CDEVPLUS board. The

Page 18

8 158004.B00

TCDEVPLUS (but not the TCDEV) also includes 14-way ribbon cable connects to the

TP400 J5 connector, making connections for COM3 and COM4.

The TP400 includes its own VGA, floppy and IDE disk controller s, and VGA, floppy

and IDE disk controllers are also present on the TCDEVPLUS. It is possible to use

either the VGA and disk controllers on the TP400 or the controllers on the

TCDEVPLUS (though not a mixture of both). These instructions assume that the

VGA controller and floppy disk controller on the TCDEVPLUS are used initially, as

this will be more convenient during early stages of development. Users can move to

the TP400’s on-board disk and graphics controllers as the development process

progresses.

The next two sections describe using the TCDEVPLUS and the TCDEV with the

TP400. Note that the old REV B TCDEV cannot be used with the TP400. The old

REV B TCDEV boards can be identified by having only one site for PC/104 boards,

and only one power LED.

1.6.2 Using the TCDEVPLUS Development System

To use the system, first inst all an SDRAM SODIMM module into the TP400 SDRAM

socket, observing its polarity, and observing proper anti-static precautions. The

SODIMM socket has a lug that engages with a cutout on the module, which prevents

incorrect installation.

A fan or heatsink should be added to t he TP400, as it may ge t too hot without one. A

heatsink is supplied as part of the TP400PAK starter pack (see Appendix D for

details).

Enable the floppy disk controller and VGA graphics on the TCDEVPLUS. This is done

by setting the jumpers at jumper areas E3 and E5 to the "EN" position. Disable the

IDE disk controller on the TCDEVPLUS by setting jumper E4 to the “DIS” position.

The TCDEVPLUS COM4 UART should be disabled at E8. The battery back-up

jumper should be set in the BATT position at E2. The status LED jumpers at E7

should both be set in the 1 - 2 position. At jumper area E6 set t he C000 jumper to the

"EN" position and the other seven jumpers to t he "DIS" position. T he speaker should

be enabled by fitting a jumper at E1. T he GCAT486 pr inter should be disabled at E9.

Jumpers should be removed from E10 and E11.

Plug the TP400 onto the TCDEVPLUS and connect the 50-way and 14-way ribbon

cables from J4 and J5 of the TP400 to the corresponding connectors on the

TCDEVPLUS. Ensure that pin 1 of the TP400 connectors go to pin 1 of the

TCDEVPLUS connectors. Failure to connect the 50-way cable correctly may

damage the equipment.

Connect but do not switch on the TPPSU. (Note that t he TPPSU power connector is

polarized. Ensure that the locking tab on the power supply cable mates with the

locking tab on the TCDEVPLUS connector). Failure to connect t he power supply

cable assembly correctly may damage the equipment.

Connect the keyboard and VGA monitor to the appropriate connectors.

Insert a bootable f loppy disk into the TCDEVPLUS floppy disk drive and switch the

power supply on. The computer should begin booting. You may press the F2 key

Page 19

158004.B00 9

before or during the memor y test to enter t he Setup prog ram, where you can change

the time and date and make ot her changes. The "EXIT" menu option allows you to

save the settings in CMOS RAM and exit.

While using the TCDEVPLUS’s floppy disk controller the BIOS will print a warning

message to the effect that it is disabling the floppy disk controller on board the

TP400.

You should now boot DOS from the floppy disk drive on the TCDEVPLUS.

An alternative to using floppy disks is to mak e use of the hard disk present on the

TP400 or the TCDEVPLUS. You m ay connect an IDE drive, or Compact Flash card

installed in the CF100 adapter , t o the 44-way IDE connector J100 on the T P400. T he

BIOS will automatically detect the drive’s parameters.

Alternatively, you may use the IDE controller on the TCDEVPLUS. T his allows you to

connect to both 2.5” and 3.5” IDE drives, and to make use of the Compact Flash

socket on the TCDEVPLUS. To use the TCDEVPLUS IDE controller you must enable

it at jumper E4, and use t he BIOS Setup program to disable the TP400’s on-board

IDE controller.

(The IDE disk controller on the TCDEVPLUS is slower than the controller on the

TP400, but it offers the convenience of the wider range of connectors. I n principle it is

possible to use a 44-way cable to connect the TP400’s IDE controller to the

TCDEVPLUS PCB, to take advantage of the wider range of connectors on the

TCDEVPLUS PCB, while using the faster TP400’s IDE controller. Unfortunately, if

you want to do this with the REV B TCDEVPLUS you must cut pin 32 of the ribbon

cables. The REV C TCDEVPLUS provides links to do this.)

Section 3.9 has more details on the IDE interface. A Flash File system is also

provided with the TP400. Section 6.6 has details of the Flash File System.

When you want to use the TP400's on-boar d floppy and graphics controllers then you

may make the appropriate connections to the TP400's connectors and disable the

corresponding TP400 device at the TCDEVPLUS jumper areas E3 and E5. To

disable the TCDEVPLUS's VGA chip you must also set the E6 jumpers all to the

"DIS" position.

When development is complete the TP400 is removed from the TCDEVPLUS

Development System. It can then operate stand-alone, or be used with other PC/104

modules.

Refer to the TCDEVPLUS Technical Reference Manual for full details of the

TCDEVPLUS.

1.6.3 Using the Rev D TCDEV Development System

To use the system, first inst all an SDRAM SODIMM module into the TP400 SDRAM

socket, observing its polarity, and observing proper anti-static precautions. The

SODIMM socket has a lug that engages with a cutout on the module, which prevents

incorrect installation.

Page 20

10 158004.B00

A fan or heatsink should be added to t he TP400, as it may ge t too hot without one. A

heatsink is supplied as part of the TP400PAK starter pack (see Appendix D for

details).

Enable the floppy disk controller and VGA graphics on the TCDEV. This is done by

setting the jumpers at jumper areas E3 and E5 to the " EN" position. Disable the IDE

disk controller on the TCDEVPLUS by setting jumper E4 to the “DIS” position.

Ensure there are jumpers between positions 1 and 12, and between 4 and 9 at

jumper area E1. T he battery back-up jumper should be set in the BATT position at

E2. The status LED jumpers at E7 should both be set in the 1 - 2 position. At jumper

area E6 set the C000 jumper to the "EN" position and the other seven jumpers to the

"DIS" position.

Plug the TP400 onto the T CDEV and connect t he 50-way ribbon cable from J4 of the

TP400 to the corresponding connect or on the TCDEV (J3 on the TCDEV). Ensure

that pin 1 of the TP400 50-way connector J4 goes to pin 1 of the TCDEV J3

connector. Failure to connect the 50-way cable correctly may damage the

equipment.

Connect but do not switch on the TPPSU. (Note that t he TPPSU power connector is

polarized. Ensure that the locking tab on the power supply cable mates with the

locking tab on the TCDEV connector) . Failure to connect the pow er supply cable

assembly correctly may damage the equipment.

Note that on the TPPSU the mains earth is connect ed to 0V. This is done in the 6way connector, with the braid (earth) connecting to one of the 0V wires. Users who

are using the earlier TCPSU power supply must explicitly connect the mains earth to

their TCDEV, by plug ging the green and yellow earth lead onto the spade terminal

soldered to the printer connector, though note the earlier warning that the 25W

TCPSU will probably not have enough capacity for TP400 development.

Connect the keyboard and VGA monitor to the appropriate connectors.

Insert a bootable f loppy disk into the TCDEV floppy disk drive and switch the power

supply on. The computer should begin booting. You m ay press the F2 key before or

during the memory test to enter t he Setup program, where you can change the time

and date and make other changes. T he "EXIT" menu option allows you to save the

settings in CMOS RAM and exit.

While using t he TCDEV's floppy disk controller the BIOS will print a warning message

to the effect that it is disabling the floppy disk controller on board the TP400.

You should now boot DOS from the floppy disk drive on the TCDEV.

An alternative to using floppy disks is to mak e use of the hard disk present on the

TP400 or the TCDEV. You may connect an IDE drive, or Compact Flash card

installed in the CF100 adapter , t o the 44-way IDE connector J100 on the T P400. T he

BIOS will automatically detect the drive's parameters.

Alternatively, you may use the IDE controller on the TCDEV. This allows you to

connect to 2.5” IDE drives (and to 3.5” IDE drives with an appropriate cable). To use

the TCDEV IDE controller you must enable it at j umper E4, and use the BIOS Setup

program to disable the TP400’s on-board IDE controller.

Page 21

158004.B00 11

Section 3.9 has more details on the IDE interface. A Flash File system is also

provided with the TP400. Section 6.6 has details of the Flash File System.

When you want to use the TP400’s on-board floppy and graphics controllers then you

may make the appropriate connections to the TP400’s connectors and disable the

corresponding TP400 device at t he TCDEV jumper areas E3 and E5. To disable the

TCDEV’s VGA chip you must also set the E6 jumpers all to the "DIS" position.

When development is complete the TP400 is removed from the TCDEV

Development System. It can then operate stand-alone, or be used with other PC/104

modules.

Refer to the TCDEV Technical Reference Manual for full details of the TCDEV.

1.6.4 TCONN Connector Breakout Board

After developing your product with the TCDEVPLUS you may be interested in using

our TCONN board for production.

The TCONN is a breakout board that provides an easy way of connecting to DSP

Design’s PC/104 processor boards. It mates with the I/O connectors of the PC/104

board, and provides standard PC compatible connectors for most of the peripherals.

All connectors are filtered, which gr eatly simplifies compliance with EMC standards.

Features include:

• PC/104 board plugs directly into the TCONN.

• All connectors filtered for good EMC performance.

• Two 6-pin mini-DIN connectors for keyboard and mouse.

• Keyboard and mouse power rails have thermal fuse protection.

• Three 9-way D-type connectors for serial ports.

• 25-way D-type connector for printer.

• 15-way high density D-type connector for VGA.

• Circular power inlet connector.

• Pin header carrying miscellaneous signals.

• Lithium battery for CMOS SRAM and RTC.

• Small speaker.

• Reset switch.

• Power LED.

See Appendix D for ordering information.

Page 22

12 158004.B00

1.7 AVOIDING COMMON PROBLEMS

This section draws your attention to a number of issues that can cause problems, but

that can be avoided if you are aware of them.

The battery pin must not be connected to +5V and must not be left floating. See

section 3.6 for further details.

Some old disk drives and some Compact Flash cards do not report t heir parameters

and so the parameters will need to be set manually for these devices. See section 3.9

for further details.

Some form of cooling may be needed for the Geode GX1 processor. This is

discussed in section 2.1.

The VGA display controller and SoundBlaster-compatible audio circuitry is not fully

implemented within the Geode chip. Missing registers are emulated in software, using

SMIs (System Management Interrupts). This can cause problems in certain cases,

although there is usually a work-around. W hen t he VGA emulation is in operation, in

some display modes, a regular SMI occurs every 1ms. During this time the Geode will

not respond to interrupts, and if interrupts are arriving at high speed (due to highspeed serial comms f or example) then inter rupts can be lost. There are solut ions for

Windows, Linux and some other operating systems, and work-arounds to some

extent for DOS. The problem and its resolution are discussed in section 3.10.5.

If you find that a USB peripheral does not operate correctly when directly plugged into

the TP400, then you should consider using a powered hub. This is discussed in

section 3.14.

Page 23

158004.B00 13

2 PROCESSOR AND MEMORY

The TP400 single board computer is based around the National Semiconductor

Geode GX1 chip set. There is one SODI MM SDRAM socket. The standard TP400 is

supplied without memory, allowing you to choose memory to suit your application.

SDRAM options are detailed in Appendix D, Options and Ordering Information.

2.1 PROCESSOR

The TP400 is based on the National Semiconductor Geode GX 1 chip set. This is a

highly integrated chip set that includes a Pentium-class MMX-Enhanced x86

compatible processor and many integrated peripherals. It includes all of the

motherboard support circuits used in PCs as well as graphics and audio circuitry.

The Geode GX1 is a 320-pin pin-grid ar ray (PGA) chip that is visible on the top side

of the TP400. The processor is sock eted, allowing different speed-grade processors

to be fitted. The Geode GX 1 is available at a variety of speed grades, up to 300MHz.

A 300MHz processor is fitted as standard, although it may be run at slower clock

speeds to reduce power consumption. A heatsink or fan can be fitted to the

processor, and a connector close to the processor provides power to the fan.

Although the Geode GX1 runs much cooler than equivalent Pentium processors,

some heatsink or fan is likely to be required in most applications.

DSP Design can supply a passive heatsink, and a heatsink/fan combination. See

Appendix D for ordering information.

The Geode GX1 also integrates a high- performance graphics engine. This provides

VGA-compatible graphics as well as adding high-performance 2D graphics

accelerator logic that is driven by operating system-specific drivers. To provide a high

level of system integration, improve performance and reduce system costs, the

graphics engine uses a portion of the system SDRAM memory as graphics memory.

This is referred to as u n i fie d me mo ry architecture (UMA).

So as to stop the graphics sub-system from using too much of the memory

bandwidth, the Geode GX1 implement s graphics compression and caching circuitry.

Under this scheme, graphics data is read f rom the graphics memory, compressed,

and written back to a separate graphics cache memor y. From then on, and until that

line of the display is changed, it is the compressed data t hat is read from the cache

and displayed, rather than the full uncompressed graphics data.

The graphics compression and caching scheme, together with the fact that the

processor, graphics engine and SDRAM interface are closely coupled, results in a

very high level of graphics performance.

As a compromise, not all of the legacy VGA register s are implemented in hardware.

Some registers are emulated by an SMI interrupt. National Semiconductor refers to

this as VSA - Virt ual System Architecture. T he VSA code is also responsible for the

SoundBlaster-compatible audio and some power management features. This

software emulation of hardware can give rise to some problem s, which are described

in section 3.10.

The companion chip to the Geode GX1 processor is t he CS5530A. This is the BGA

Page 24

14 158004.B00

(ball grid array) device on the main printed circuit board. The CS5530A contains

graphics processing logic, the IDE and USB ports, clock generators, ISA bus

interface and the peripheral devices traditionally implemented in a motherboard chip

set. (Earlier versions of the TP400 used the CX5530A, which has the same

functionality).

These peripherals include two 8237 compatible DMA control units (7 channels), one

8254 compatible timer control unit (3 channels) and two 8259 compatible interrupt

control units (15 int errupts). The majorit y of the peripheral f unctions are the same on

all PC compatible computers. This includes the tim ers, interrupt controllers and DMA

controllers as well as registers such as the NMI and speaker inhibit registers, fast

reset and A20 gate registers. Software that accesses desktop PC peripherals will

have the same effect when running on the TP400, giving rise to a high degree of

PC-compatibility.

The other housekeeping functions provided by the CS5530A are:

• PCI to ISA bus bridge.

• ISA bus memory and I/O address decoding logic.

• Power management.

• Game port (unused on the TP400).

• MPEG playback hardware assist circuitry

The Geode GX1 and CS5530A chips also include a number of internal conf iguration

registers. These r egisters ar e unique to the G eode GX1 chip set. They control timing

on the expansion bus, shadow RAM, SDRAM configuration, memory mapping and so

forth. They ar e initialized by the BIOS and will not normally need to be accessed by

the user.

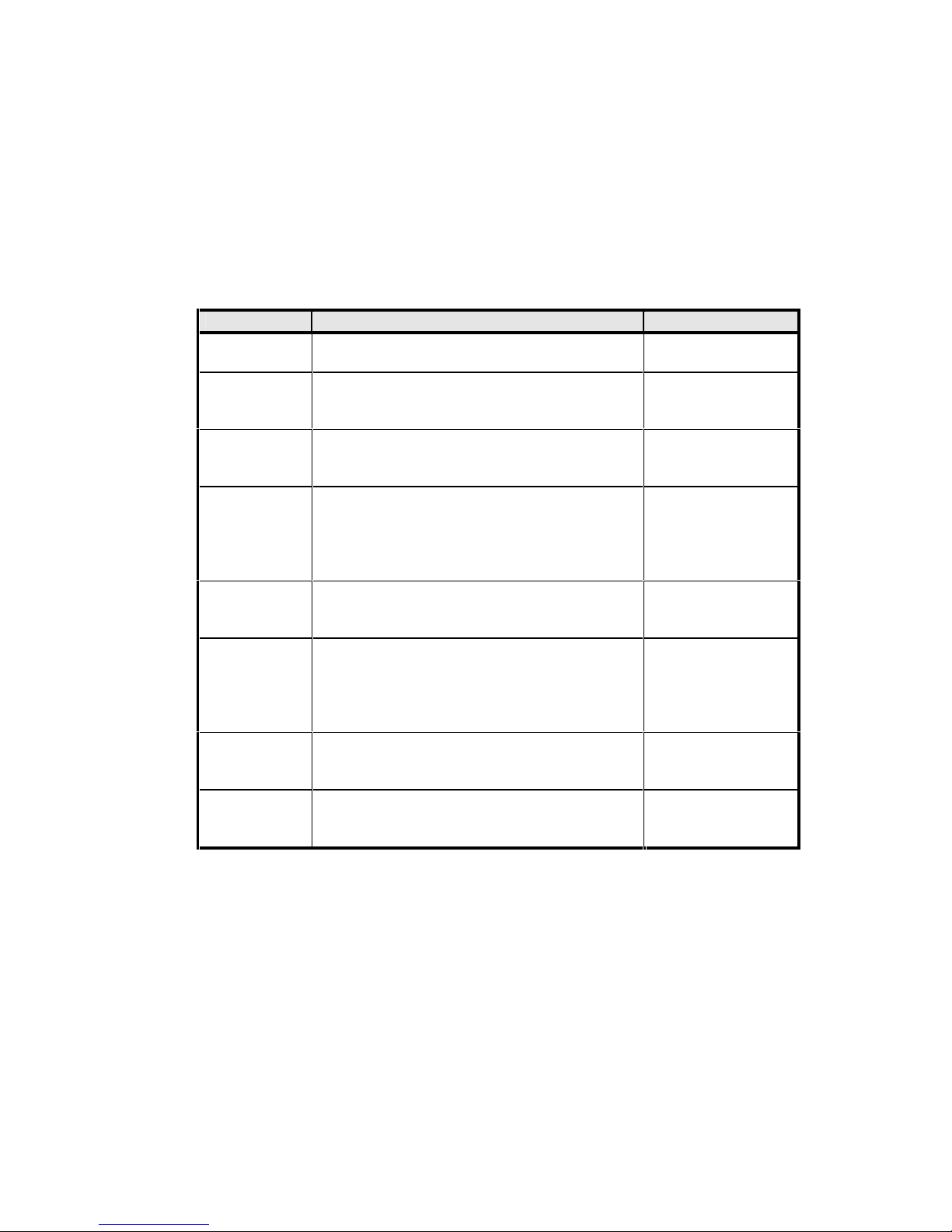

The performance of t he TP400 may be gauged by the processor performance ratings

produced by the Norton SI program as shown in Table 1. T his table also g ives typical

power consumption figures for the TP400. At the tim e of writing the BIOS does not

support operation at 133MHz. The board will run at 333MHz, but the processor is not

rated to operate at this speed, so the 333MHz entry is for reference only.

The TP400 off ers very low power consumption for a board of its perform ance. One

power measurement has been made with the graphics disabled – as can be seen

power consumption is significantly reduced with the graphics disabled. There is a

small increase of power as the graphics resolution increases, and a further small

increase when the PanelLink interface is used.

CPU

FREQUENCY

NORTON

RATING

TYPICAL

POWER

CONSUMPTION

POWER WITH

GRAPHICS OFF

133MHz N/A N/A 166MHz 317 670mA 200MHz 387 700mA 233MHz 456 820mA 266MHz 526 870mA 300MHz 595 1.03A 810mA

333MHz 663 1.09A -

TABLE 1 - TP400 PERFORM ANCE RATINGS

Page 25

158004.B00 15

The above measurements were made with a 4-chip 32M-byte SODIMM module

installed. The power consumption figures were tak en after DOS had booted and the

processor was sitting idle at the DOS prompt. Power management was disabled.

Users should make their own decision concerning cooling of the processor. The

TP400 draws very little power, considering its level of perfor mance, but is still lik ely to

need cooling. The TP400 dissipates up to 5W , depending on the clock speed (see

Table 1 for overall power consumption) Most of this cur rent goes to the processor,

which may get quite hot. We recommend a heat sink and/or a fan to keep the

temperature of the processor down. The cooler a chip is t he more reliable it will be. A

fan or fan and heatsink combinat ion can be fitted to the processor, or a fan could be

provided in the enclosure along with the PC/104 boards. Connector J102 is provided

to power a +5V fan. DSP Design can provide both a passive heatsink and a

fan/heatsink combination.

As an alternative the enclosur e could be desig ned so that part of the enclosur e acted

as the heat sink. Thermal materials are available to provide a good thermal bond

between the CPU and the case.

2.2 CLOCK

A number of clock frequencies are used on the TP400. Most of these are derived

from a 14.318MHz crystal and a synthesiser chip that generates other required

frequencies.

Several 33MHz clocks are generated. These are fed to the PCI bus and to the Geode

GX1 and CS5530A chip.

The Geode GX1 incorporates its own clock multiplier that generates the processor

clock. A number of processor clock frequencies can be selected by solder links on

the board, which are set as described in Appendix B. The TP400 is fitted with a

Geode GX1 processor with a clock frequency 300MHz.

The clock synthesiser logic also generates the following clock frequencies:

• 14.318MHz for the PC/104 OSC signal.

• 8MHz for the PC/104 BUSCLOCK signal.

• 24MHz for the Super I/O chip (where it is used for serial ports, keyboard controller

and floppy disk controller).

• 48MHz for the USB ports.

• 24.5MHz for the AC97 audio codec.

• 1.8MHz for the COM3 and COM4 UARTs.

The Geode GX1 and CS5530A generate clocks for the SDRAM (synchronous

SDRAM) and graphics sub-systems.

The real-time clock, or calendar/clock, in the Super I/O chip uses a separate

32.768kHz crystal to maintain the time and date. The Ethernet chip has its own

25MHz crystal.

Page 26

16 158004.B00

2.3 SDRAM

The main memory of the TP400 consist s of Synchronous Dynamic RAM (SDRAM)

chips. The chips are mounted on a small 144-pin printed circuit board called a

SODIMM module (small outline dual-in-line memory module). T he memory is 64-bits

wide. Four options are available:

• 32M bytes

• 64M bytes

• 128M bytes

• 256M bytes

The standard configuration of the TP400 is to have no SDRAM fitted. SODIMM

modules must be ordered separately and fitted into the SODIMM socket on the

TP400. Thus users can select the correct memor y capacity for their application. See

Appendix D: TP400 Options and Ordering Information.

The use of SODIMM modules for SDRAM memory means that the SDRAM

configuration can be alter ed at a later stag e. DSP Desig n car ry stock of the SO DIMM

modules described above, or customers may provide their own. PC100 SODIMM

modules should be used.

Care must be tak en when handling the TP400 and associated components. Ensure

that all anti-static handling precautions are taken. See Appendix B: TP400 Setup

Procedure for instructions on installing SODIMM modules.

The BIOS automatically deter mines the amount of SDRAM present and configures

the internal Geode GX1 registers accor dingly. Registers within the Geode GX1 chip

allow SDRAM timing to be optimised according to CPU speed and SDRAM access

time. At reset the SDRAM timing defaults to the slowest case and the BIOS then

optimizes timing for the best performance.

Some of the SDRAM is taken from the processor and allocated to the graphics

controller, using a technique ref err ed to as UMA (unified mem ory architectur e). Up to

4.5M bytes may be allocated to graphics; the BIOS configures the correct amount

depending on the graphics mode selected in the BIOS Setup menu.

Note that only the f irst 640k bytes of SDRAM are usually directly accessible by DOS.

Some of the remaining SDRAM is used to shadow the BIOS (see section 6.1) and

the remainder is re-mapped above the 1M byte boundary, where it can be used by

DOS extenders and by Windows and other operating systems.

Memory between C0000H and FFFFFH (the top of the 1M-byte block) can be used to

shadow BIOS code. This allows the BIOSes to run at t he fast SDRAM speed rather

than the slow EPROM speed. Typically the system BIOS (from E8000H - FFFFFH),

the VGA BIOS (from C0000H - C7FFFH) and the Flash File System (from CC000H CFFFFH) driver are shadowed. Memory beyond the 1M byte limit is available for

Windows and other protected mode operating systems.

Page 27

158004.B00 17

2.4 FLASH MEMORY

By default the TP400 is fitted with one 2M-byte AMD or Fujitsu 29F016 Flash memory

chip. However, the TP400 has sites for two flash chips, and the 4M byte 29F032 can

be fitted as an alternat ive to the 29F016. Thus there are options f or 4M or 8M bytes

of Flash memory as well as the standard 2M-byte complement. The 4M and 8M byte

options are available by special order and are subject to a minimum order quantity.

Flash memory is non-volatile memory that can be program med while it is soldered to

the TP400. Data written to the Flash memory is retained after power is removed.

The Flash memory serves two purposes. Firstly, it contains the BIOS:

machine-dependent software that is required to run an operating system.

The second function of the Flash memory is to provide a Flash File System f or users

who want a solid state disk.

The top 256k bytes of the Flash chip ar e used for the system BIOS and any BIOS

extensions, such as the VGA BIOS extension and the Flash File System BIOS

extension. The TP400 comes pre-programmed with a system BIOS, a VGA BIOS

extension for on-chip graphics controller and a Flash File System BIOS extension.

See section 2.5 for mor e informat ion on memory mapping of the TP400, and section

6.3 for more information on BIOS extensions.

Utility programs are provided on the TP400 Ut ility Disks that allow the Flash chip to

be programmed by the user. This allows the user to program various alternative BIOS

image files into the Flash memory. These utility programs are described in section

6.5.

A Flash File System is provided with every TP400. This converts the remaining 1744k

bytes of the 2M byte Flash chip into a non-volatile read-write logical disk dr ive. This

Flash disk can contain the MS-DOS operating system as well as your application

program. The Flash File System is described in section 6.6.

Optionally, 4M byte and 8M byte Flash disks are available.

The TP400 allows the Flash File System to access the large Flash chips through a

window in the 1M byte address space. Memory management logic in the Geode GX1

and hardware in the Super I/O chip allows the high order address lines of the Flash

chip to be changed by software. The Flash File System driver software controls the

memory management logic and bank switch hardware transparently to the user’s

software.

The Flash File System is intended for ROM-DOS and MS-DOS. In principle Flash file

systems could be created for other operating systems, such as Linux, QNX, OS/9

and VxWorks, but at the tim e of writing this work has not been done and DSP Design

cannot provide FFS drivers for these operating systems. This situation may change in

the future, so contact us if you have an interest in these operating systems.

The Flash chip resides on the eight-bit PC/104 data bus.

The BIOS makes use of "shadow RAM" in place of t he Flash chip for gr eater speed.

In this scheme the BIOS contained within the Flash chip is copied by the BIOS to

SDRAM at the same addresses. The Flash chip is then disabled and the BIOS is

Page 28

18 158004.B00

executed from the 32-bit wide SDRAM, much faster than it would be from the Flash

chip. Section 6.3 contains further information on BIOS extensions.

2.5 MEMORY ADDRESS MAP

Table 2 shows the memory map as configured by the standard BIO S of the TP400.

This table shows the bottom 1M byte address space. Extra SDRAM is located

immediately above the 1M byte boundary. Memory accesses beyond the top of the

SDRAM are performed on the PCI bus.

ADDRESS MEMORY DEVICE DECODED MEMORY SIZE

FFFFF

E8000

BIOS in Flash Chip - copied to shadow

SDRAM memory during the boot sequence. 96K

E7FFF

E0000

This space is reserved for the Flash memory

programming program and the Flash File

System.

32K

DFFFF

D0000

Available for PC/104 memory mapped

boards. BIOS Extension code can be located

here and optionally shadowed in SDRAM.

64K

CFFFF

CC000

The Flash File System BIOS extension is

initially located here, before it copies itself to

low memory. Available for PC/104 bus

memory mapped boards if the FFS is not

used.

16K

CBFFF

C8000

Available for PC/104 memory mapped

boards. BIOS Extension code can be located

here and optionally shadowed in SDRAM.

16K

C7FFF

C0000

Usually VGA BIOS, which is copied from

Flash chip to shadow SDRAM at this

address. Alternatively used by VGA BIOS on

PC/104 or PC/104-Plus bus that can also be

shadowed.

32K

BFFFF

A0000

Usually allocated to VGA memory.

128K

9FFFF

00000

SDRAM

640K

TABLE 2 - TP400 A DDRESS MAP - FIRST 1M BYTE

Page 29

158004.B00 19

3 PERIPHERALS

This section describes the I/O address map and the on-board peripherals.

3.1 I/O ADDRESS MAP

The TP400 features a number of on-board I/O mapped resources, and supports

access to the PC/104 bus I/O space as well.

All I/O mapped functions that are present on deskt op PCs are present at the same

I/O addresses on the TP400. The TP400 is therefore compatible at the machine code

or register level with desktop PCs.

On-board I/O devices include registers within the Geode GX1 chip set, the Super I/O

chip, Ethernet chip and the extra UART chip. The Super I/O chip contains the floppy

disk controller, Utility Register, keyboard controller, calendar/clock module and the

serial and parallel I/O ports. The on-board I/O addresses are listed in Table 3.

I/O accesses are routed as follows. I/O accesses within the Geode GX1 processor

remain internal to this chip. I/O addresses that are within PCI bus devices (which

includes the registers internal to the CS5530A chip) are performed on t he PCI bus.