Page 1

EK-SA001-0P-002

PDP-Sf

A OPERATOR'S

HANDBOOK

digital

equipment

corporation • maynard. massachusetts

Page 2

PDP;;;8/ A

OPERATOR'S

HANDBOOK

digital

equipment

corporation

• maynard. massachusetts

Page 3

18t

Edition, September 1975

2nd Printing (Rev),

September 1976

Copyright

© 1975, 1976

by

Digital Equipment Corporation

The material in this manual

is

for informational

purposes and

is

subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this

manual.

Printed in U.S.A.

This document

was

set

on

DIGITAL's DECset-8000

computerized typesetting system.

The following are trademarks

of

Digital Equipment

Corporation, Maynard, Massachusetts:

DEC

FLIP CIllP

DIGITAL

UNIBUS

DEC

US

PDP

FOCAL

COMPUTER LAB

MASSBUS

Page 4

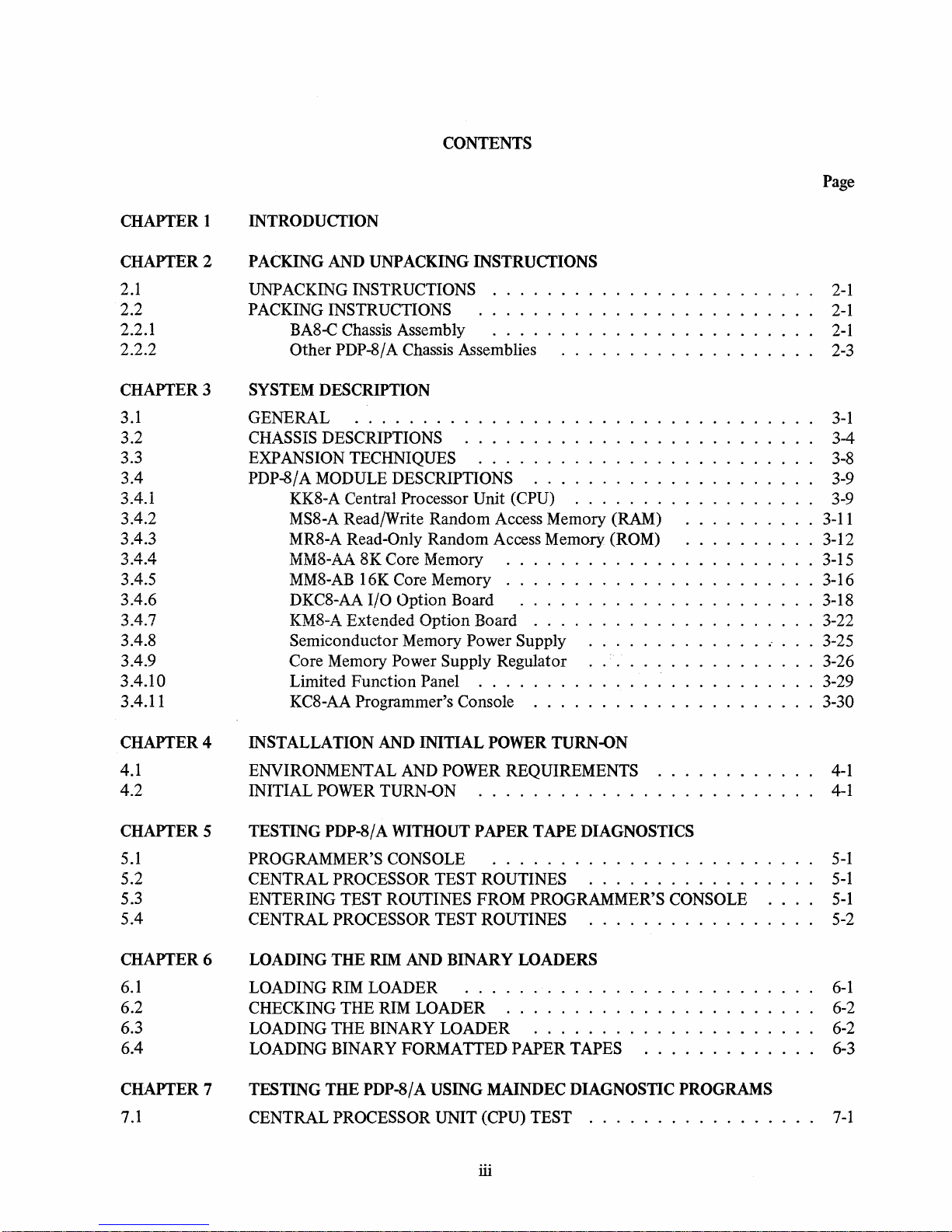

CONTENTS

Page

CHAPTER 1

CHAPTER

2.1

2.2

2.2.1

2.2.2

CHAPTER 3

3.1

3.2

2

3.3

3.4

3.4.1

3.4.2

3.4.3

3.4.5

3.4.6

3.4.7

3.4.8

3.4.9

3.4.10

3.4.11

INTRODUCfION

PACKING AND UNPACKING INSTRUCTIONS

UNPACKING INSTRUCTIONS

PACKING INSTRUCTIONS

BA8-C Chassis Assembly

Other

PDP-8/A Chassis Assemblies

SYSTEM DESCRIPTION

GENERAL

CHASSIS DESCRIPTIONS . . . . . . . . . . . . . . . . . . . .

EXPANSION TECHNIQUES . . . . . . . . . . . . . . . . . . . .

PDP-8/ A MODULE DESCRIPTIONS

KK8-A Central

MS8-A Read/Write Random Access Memory

MR8-A

NHvI8-AA

MM8-AB 16K Core Memory . . . . . . . .

DKC8-AA

K~M8=A

Semiconductor Memory

Core Memory

Limited Function

KC8-AA

.......

Processor Unit (CPU)

Read-Only Random Access Memory (ROM)

8K Core Memory . . . . . . . . . . . . . . 3-15

I/O Option Board

Extended Option Board

Power Supply Regulator

Panel

Programmer's Console

.....

. . . . . . . . . . . . . . . . . . . .

.....................

..................

(RAM)

.......

....

Power Supply . . . . . . . . . . 3-25

...................

........

...

..........

..........

......

.

....

. . . . .

...........

. . . . . . . . . . . 3-30

....

.

....

..

..

..

2-1

2-1

2-1

2-3

3-1

3-4

3-8

3-9

3-9

3-11

3-12

3-16

3-18

3-22

3-26

3-29

CHAPTER

4.1

4.2

CHAPTERS

5.1

5.2

4

5.3

5.4

CHAPTER

6.1

6.2

6

6.3

6.4

CHAPTER

7.1

7

INSTALLATION AND INITIAL POWER TURN-ON

ENVIRONMENTAL AND

INITIAL POWER TURN-ON

TESTING PDP-8/A WITHOUT PAPER TAPE DIAGNOSTICS

PROGRAMMER'S CONSOLE

CENTRAL PROCESSOR TEST ROUTINES

ENTERING TEST ROUTINES FROM PROGRAMMER'S CONSOLE

CENTRAL PROCESSOR TEST ROUTINES . . . . . . . . . . . .

LOADING THE RIM AND BINARY

LOADING

CHECKING THE RIM

LOADING THE BINARY LOADER

LOADING BINARY

TESTING THE PDP-8/A USING MAINDEC DIAGNOSTIC PROGRAMS

CENTRAL PROCESSOR UNIT (CPU) TEST

RIM LOADER

POWER REQUIREMENTS

............

........................

LOADERS

..........

LOADER

FORMATIEDPAPER

.......

.....

iii

.................

.

.

.

TAPES

.

....

. . . . . .

..

..

..

4-1

4-1

5-1

5-1

5-1

5-2

6-1

6-2

6-2

6-3

7-1

Page 5

CHAPTER 8

S.l

S.2

S.3

S.4

CONTENTS (Cont)

ADDITIONAL DIAGNOSTIC TESTS

MEMORY TEST

.........

.

DKCS-AA TEST . . . . . . . . . . .

KMS-A

EXTENDED OPTION BOARD TEST

TESTING

EXTENDED MEMORIES

CHAPTER 9 BASIC PDP-8/A MAINTENANCE

APPENDIX A INSTRUCTION SUMMARY

APPENDIX

B DOCUMENTATION

APPENDIX

C WARRANTY AND MAINTENANCE SERVICES

APPENDIX

D

OMNmus

LOADING

APPENDIX

E POWER CONNECTION

Figure No.

2-1

2-2

2-3

3-1

3-2

3-3

3-4

3-5

3-6

3-7

3-S

3-9

3-10

3-11

3-12

3-13

3-14

3-15

3-16

3-17

3-1S

ILLUSTRATIONS

Title

SA420, SA620, SAS20 Packaging .

PDP-S/A Computer Packaging (Inner)

PDP-S/A Computer Packaging (Outer)

PDP-8/A

Computer

........

.

Part

of

MS320 Module Showing R55, Which is Removed for SA Operation

PDP-8/A Semiconductor

Chassis

..........

.

PDP-8/A Semiconductor Computer Chassis Dimensions

SA Chassis - H9300 (Transformer Cover Removed)

SA620 Chassis . . . . . . . . . . . . . .

SA420/SA620/SAS20 Chassis Dimensions

SA600/SA620 Expansion

.......

.

KKS-A (MS315) CPU Module

.....

.

MSS-A (MS311) Read/Write Random Access Memory

MRS-A (MS312) Read Only Memory (ROM)

MMS-AA SK

Core Memory

.....

MMS-AB

16K Core Memory . . . .

'.

. . . .

DKC8-AA

(MS316) I/O Option Board

D

Etch

Revision

of

DKCS-AA

(MS3l6)

I/O Option Board

KMS-A (MS317) Extended Option Board

.....

Semiconductor Memory Regulator Board (GS016)

SA Master/Slave Switch

.............

.

iv

Page

S-l

S-2

S-6

S-9

Page

2-2

2-4

2-5

3-1

3-3

3-4

3-5

3-6

3-7

3-S

3-9

· 3-10

·

3-11

· 3-13

· 3-15

3-17

·

3-18

· 3-19

..

3-20

3-25

· 3-27

Page 6

Figure No.

3-19

3-20

3-21

6-1

6-2

E-l

Table No.

3-1

3-2

3-3

3-4

3-5

3-6

3-7

3-8

3-9

3-10

3-11

3-12

3-13

3-14

8-1

8-2

9-1

ILLUSTRA

nONS

(Cont)

Title

Core Memory Regulator Board

(G8018)

Limited Function Panel

.....

KC8-AA Programmer's Console

Paper Tape Leader

.......

.

LT33 Teletype Controls

.....

.

PDP-8/ A Electrical Connection

TABLES

Title

PDP-8/ A Computer Assemblies . . . . . . . . . .

PDP-8/ A Computers, Dedicated

Omnibus Slots

....

KK8-A (M8315) Central Processor Unit Switch Settings

MS8-A Read/Write Memory Switch Settings

MR8-A Read

Only Memory Switch

SettLl1gs

. . .

MM8-AA 8K Core Memory Jumper Installation

..

. . . . .

MM8-AB

16K Core Memory Jumper Installation

DKC8-AA

I/O

Option Board Switch Settings, C-Etch Module

DKC8-AA

Option Board Switch Settings, D-Etch Module . .

Auto-Restart Select Switch Settings

..

. . . . . . . . . . .

Bootstrap Select Switch Settings for ROMs Labeled 87 A2 and 88A2

Page

· 3-28

· 3-29

· 3-30

6-2

6-3

E-l

Page

3-2

3-3

· 3-10

..

3-12

·

..

3-14

.....

3-16

·

..

3-16

· 3-20

.....

3-21

..

3-23

· 3-23

· 3-23

·

..

3-24

Bootstrap Select Switch Settings for ROMs Labeled 158A2 and 159 A2

Bootstrap Select Switch Settings for ROMs Labeled 156A2 and 157 A2

Bootstrap/Auto-Restart Switch Settings . . . . . . . . . . . .

.....

Bootstrap Switch Settings for ROMs Labeled

87

A2 and 88A2 (E82 and E87)

Bootstrap Switch Settings for ROMs (E82 and E87) Labeled 158A2 and 159A2

3-24

8-8

8-8

9-1

Basic PDP-8/ A Troubleshooting

.......................

.

v

Page 7

Page 8

CHAPTER 1

INTRODUCTION

There are two basic types

of

computers in the PDP-8/ A family. The first type

is

the

PDP-8/

A, which uses

semiconductor memories (MS8 and MR8). The second type

is

represented by a series

of

computers, each

of

which uses 8K or

16K

core memory (MM8); this series consists

of

the 8A400, 8A420, 8A600, 8A620, 8A800, and

8A820 computers. When a reference applies to both types

of

computers, the designation

"PDP-8/

A"

is

used.

"PDP-8/A

semiconductor" refers to the semiconductor memory computer, while "8A400," for example, refers

to a specific core memory machine and

"8A"

refers to the core memory machines in general.

The

PDP-8fA

Operator's Handbook includes instructions for packing, unpacking, and installing a PDP-8/A

miniprocessor. All computers and modules are tested thoroughly at DIGITAL's manufacturing facilities before

they are shipped. However, many switches and jumper wires can be arranged

by

the customer for specific pur-

poses; furthermore, there

is

a need both to verify system interconnections and site preparations, and to detect

possible hidden damage incurred during shipping. Consequently, a number

of

initial operating tests are also

included in this handbook.

A

PD

P-8

/ A basic system can comprise a variety

of

components. The following three basic systems are the most

common:

1.

A basic PDP-8/ A, * a memory, and a Limited Function Panel. (This computer does not include a KM8

Extended Memory

Option module and, hence, must be a PDP-8/ A semiconductor.)

2.

A basic PDP-8/ A, a memory, a Limited Function Panel, a KM8 Extended Memory Option module,

a DKC8-AA

I/O

Option module, and a Programmer's Console. (Chapter 5 describes operating tests

for this arrangement.)

3.

A basic system as described in

2,

but accompanied by a teletypewriter and diagnostic** programs.

(Chapter 7 describes operating tests for this arrangement.)

*A

basic PDP-8fA

is

defmed as a Central Processor Unit (CPU) and a chassis assembly (chassis, Omnibus, and power supply).

**Diagnostics are test programs written

to

fmd faults

in

the logic. The PDP-8fA programs are supplied

on

paper tape. Diagnostic pro-

grams are optional and may be ordered from

the

Software Distnoution Center, 146 Main St., Maynard,

MA,

01754.

1-1

Page 9

Page 10

2.1

UNPACKING

INSTRUCfIONS

CHAPTER 2

PACKING AND UNPACKING

INSTRUCTIONS

All PDP-8

fA

computers are packaged in two containers; the inner container holds the computer and some kind

of

protective material.

The

steps

in

this section

are

sufficiently general

to

apply to any PDP-8f A.

To

unpack the PDP-8f A computer, proceed as follows.

i.

Open the outer carton and remove the inner carton.

2.

Open the inner carton.

3.

Carefully remove the cardboard from the top and sides

of

the computer.

4.

Carefully remove the computer from the box.

5.

Inspect the computer for damage.

If

the computer

is

damaged, notify the carrier immediately.

6.

Unpack any other boxes included in the shipment.

7.

Check that all equipment, software, manuals, etc., are present as specified on the shipping list inside

the carton.

8.

Save the cartons

and

packing material

to

use if the PDP-8f A is later repacked.

9.

Refer

to

Chapter 4 for PDP-8f A installation procedures.

2.2 PACKING INSTRUCTIONS

Two types

of

packages are used for the PDP-8f A computers. The type used and the applicable packing instruc-

tions depend on the type

of

PDP-8f A chassis assembly.

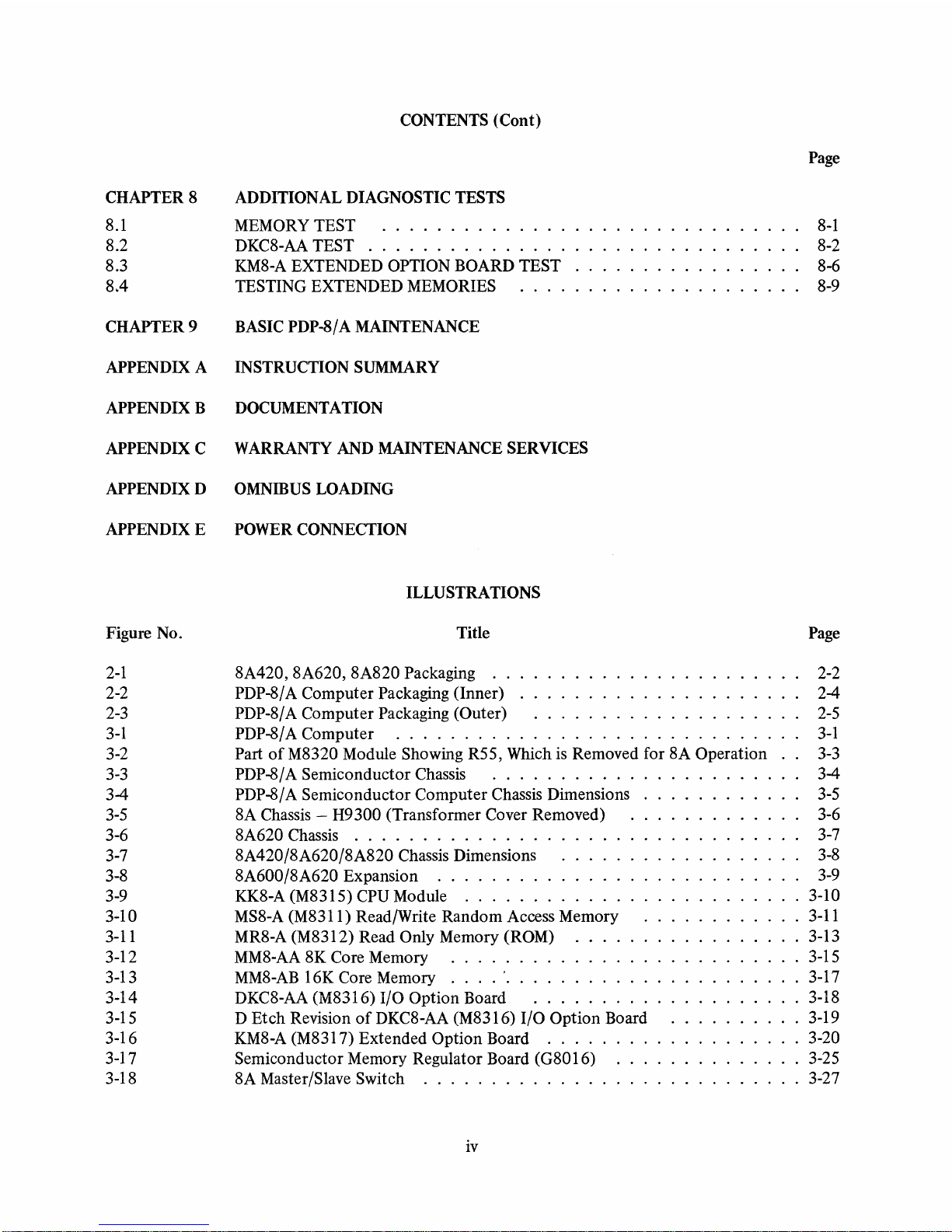

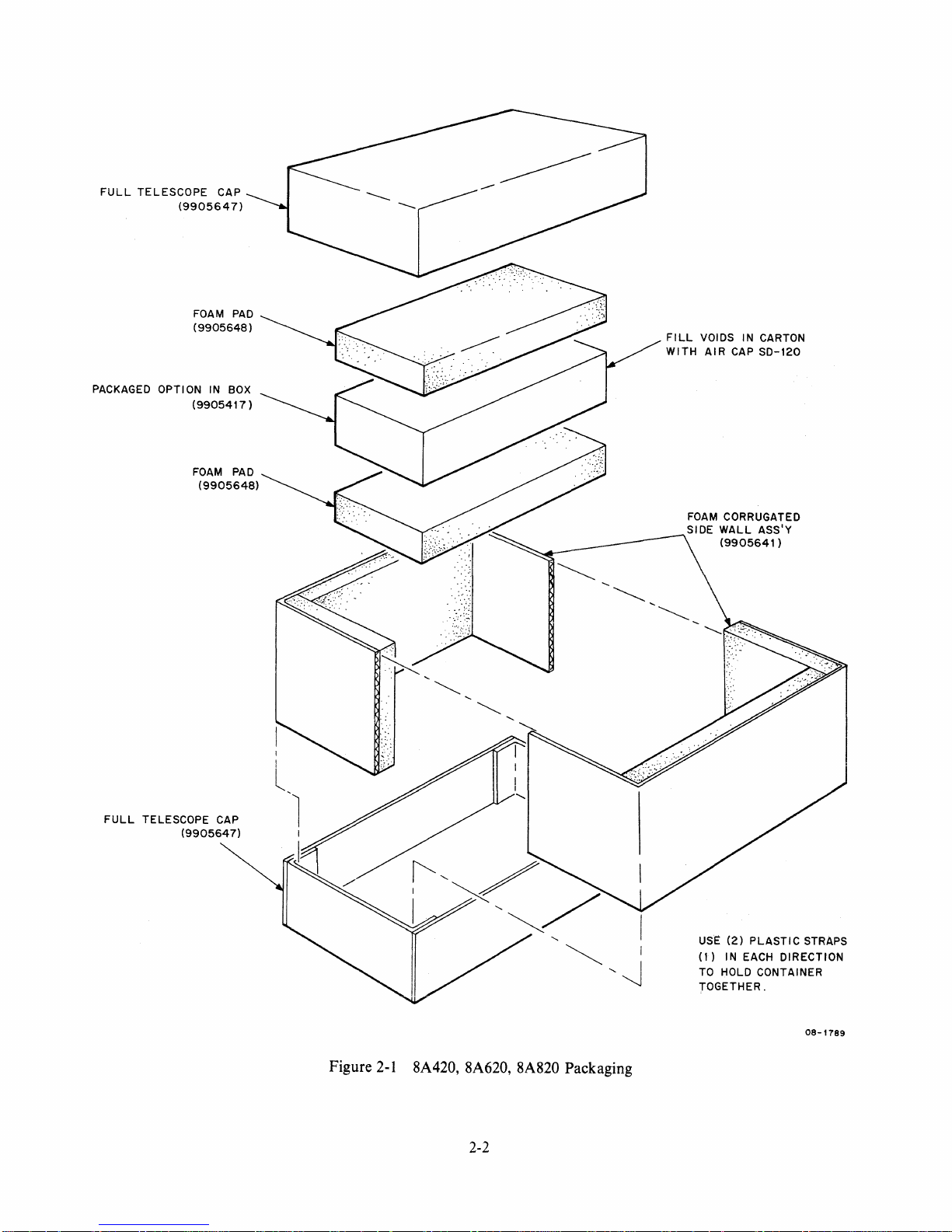

2.2.1 BA8-C Chassis Assembly

The 8A420, 8A620, and 8A820 computers use a BA8-C chassis assembly (20-slot Omnibus). Figure

2-1

illustrates

the packing procedure. The computer

is

first placed in the inner container (9905417), the empty space

is

filled

with plastic protective material

(AIR

CAP, SD-120), and the container

is

sealed.

The

sealed inner container

is

surrounded with protective foam material which

is

then enclosed by the two telescope caps. Finally, the package

is

secured by two plastic straps.

2-1

Page 11

FULL

TELESCOPE

CAP

(9905647)

FOAM

PAD

(9905648)

PACKAGED

OPTION

IN BOX

(9905417)

FULL

TELESCOPE CAP

(9905647)

Figure

2-1

8A420, 8A620, 8A820 Packaging

2-2

FILL

VOIDS I N CARTON

WITH

AIR

CAP

SD-120

FOAM CORRUGATED

SIDE

WALL

ASS'Y

(9905641

)

ust:

(2)

PLASTIC

STRAPS

(1)

IN

EACH

DIRECTION

TO HOLD CONTAINER

TOGETHER.

08-1789

Page 12

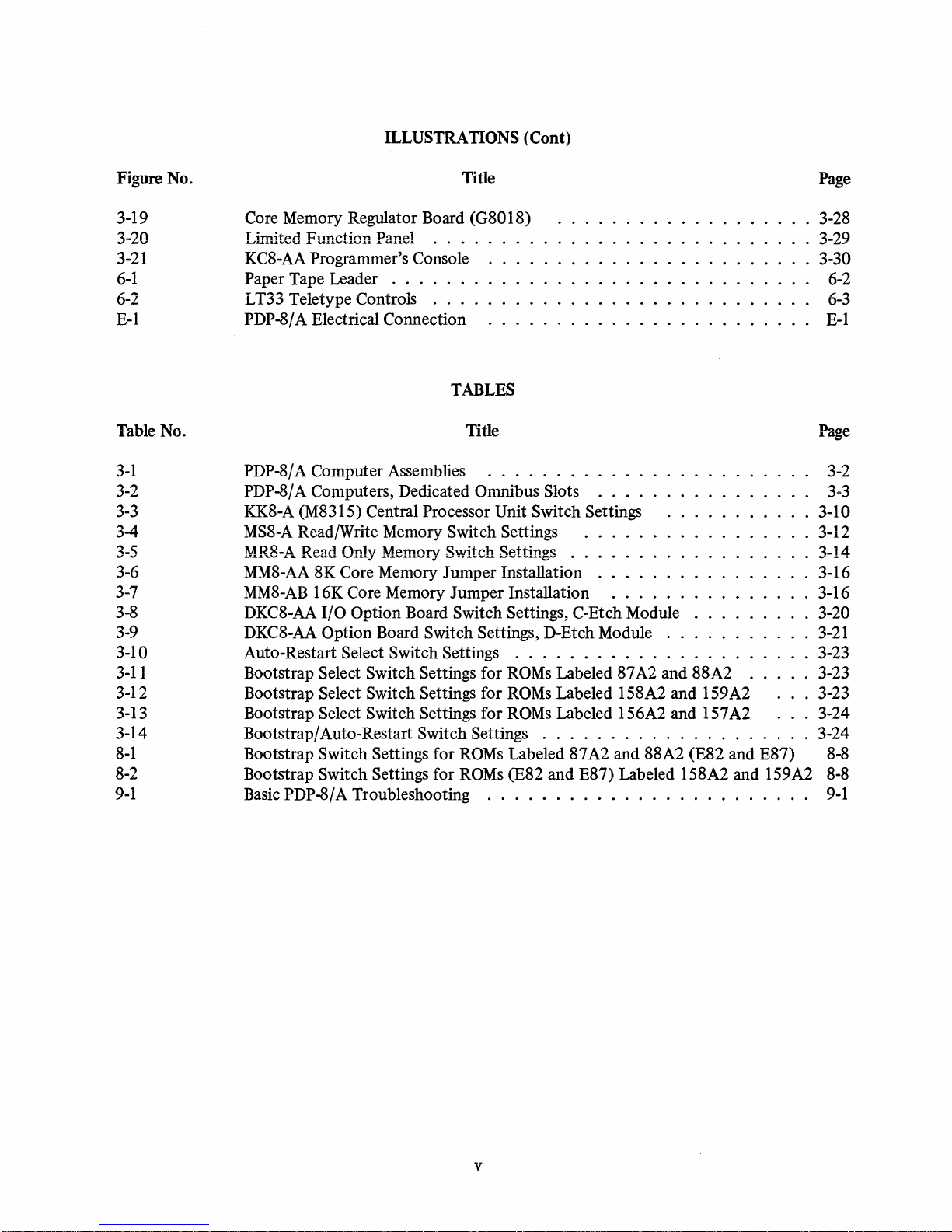

2.2.2 Other

PDP-8/

A Chassis Assemblies

CAUTION

The G8016 Regulator Board assembly used on

PDP-8/A

semiconductor computers contains a battery. This battery,

while not

of

sufficient t'oltage to cause electrical shock,

represents a possible hazard

if

shorted.

If

repacking this

type computer, ensure that there is

no

loose metal, such as

solder, wire, or sheet metal parts, inside the cabinet.

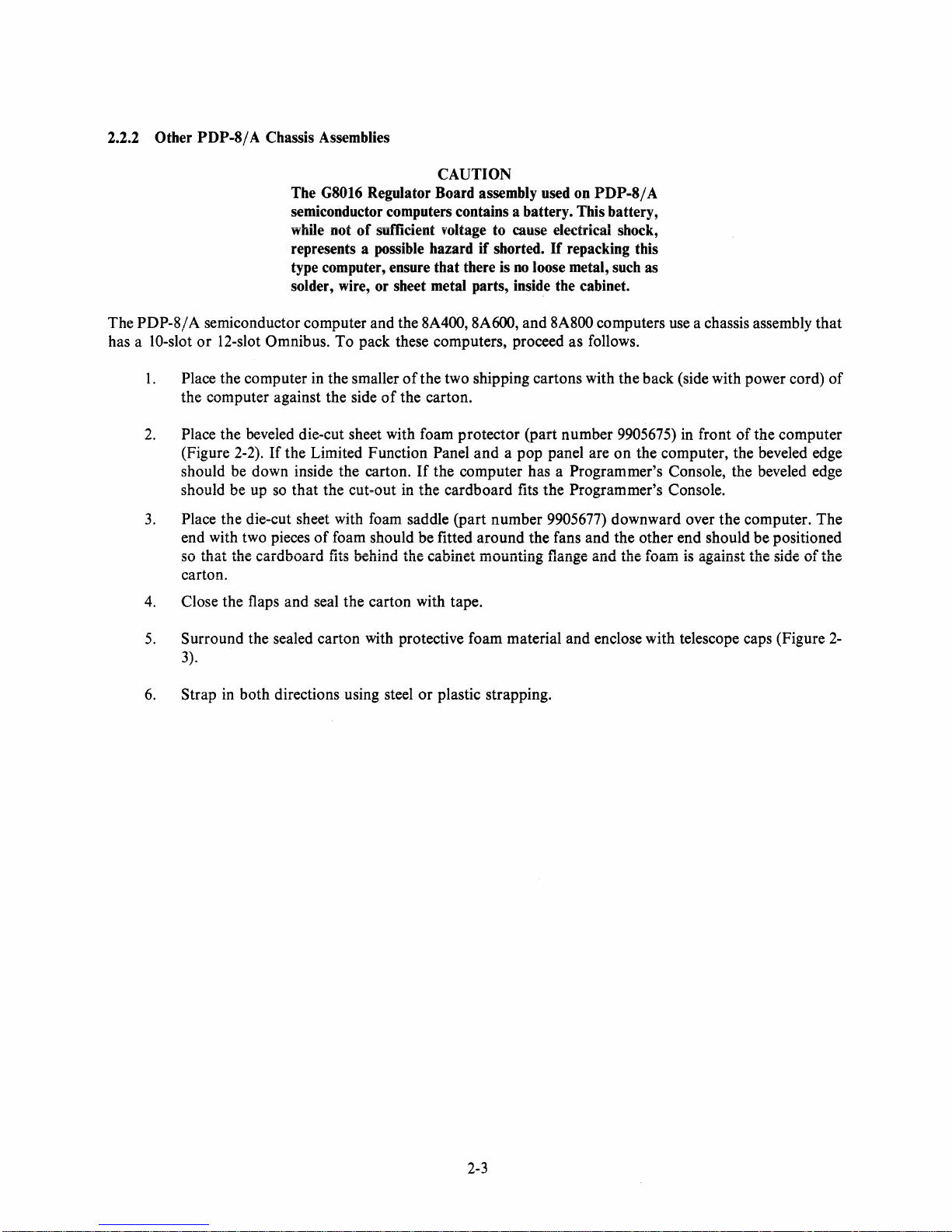

The PDP-8f A semiconductor computer and the 8A400, 8A600,

and

8A800 computers use a chassis assembly

that

has a

lO-s10t

or

12-s10t

Omnibus.

To

pack these computers, proceed as follows.

1.

Place the computer in the smaller

of

the two shipping cartons with the back (side with power cord)

of

the computer against the side

of

the carton.

2.

Place the beveled die-cut sheet with foam protector (part number

9905675)

in front

of

the computer

(Figure 2-2).

If

the Limited Function Panel

and

a pop panel are

on

the computer, the beveled edge

should be down inside the carton.

If

the computer has a Programmer's Console, the beveled edge

should be up

so

that

the cut-out in the cardboard fits the Programmer's Console.

3.

Place the die-cut sheet with foam saddle (part number

9905677)

downward over

the

computer.

The

end with two pieces

of

foam should be fitted around the fans and the other end should be positioned

so that the cardboard fits behind the cabinet mounting flange and the foam

is

against the side

of

the

carton.

4.

Close the flaps and seal the carton with tape.

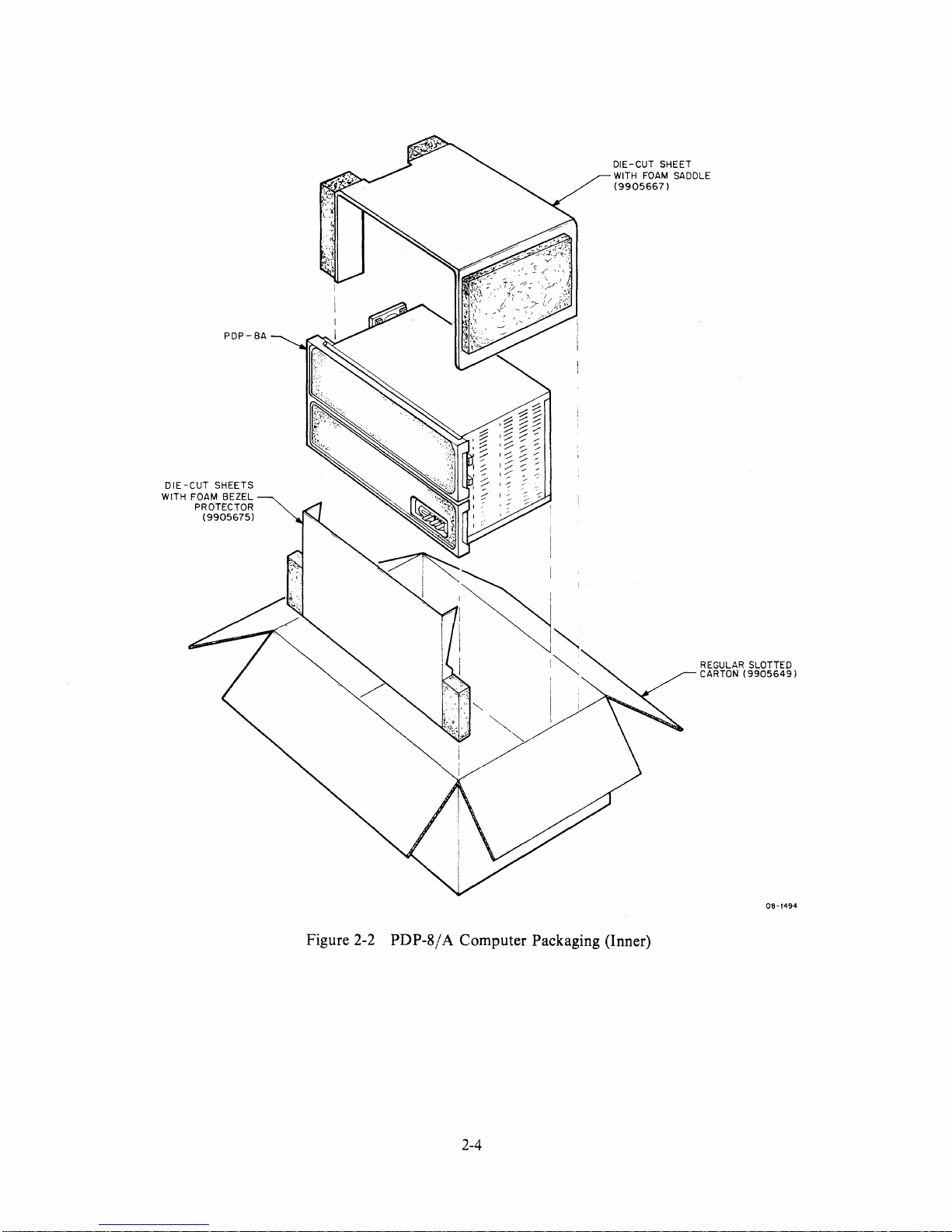

5.

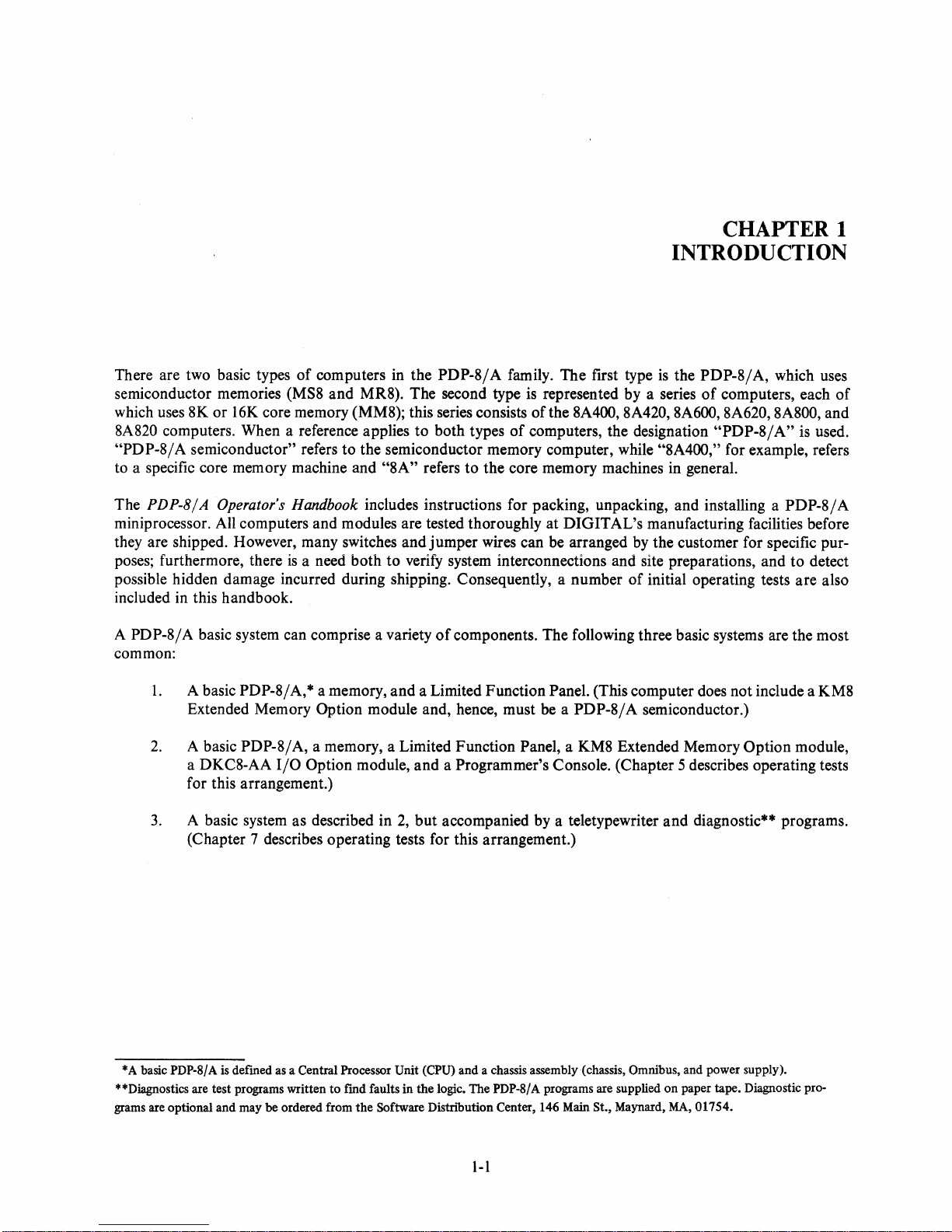

Surround the sealed carton with protective foam material and enclose with telescope caps (Figure

2-

3).

6.

Strap in both directions using steel

or

plastic strapping.

2-3

Page 13

DIE

-CUT

WITH FOAM BEZEL

SHEETS

PROTECTOR

(9905675J

DIE-CUT SHEET

WITH

FOAM

(9905667]

SADDLE

Figure 2-2 PDP-8f A Computer Packaging (Inner)

REGULAR SLOTTED

CARTON

(9905649)

08-1494

2-4

Page 14

FULL

TELESCOPE

CAP

(9905662)

FOAM

PAD

(9905663)

PACKAGED

OPTION

IN BOX

(9905649)

FOAM

PAD

(9905663)

FOAM CORRUGATED

SIDE

WALL

ASS'Y

~

(9905661)

~

Figure

2-3

PDP-8f A Computer Packaging (Outer)

,

2-5

08-1790

Page 15

Page 16

CHAPTER 3

SYSTEM DESCRIPTION

3.1

GENERAL

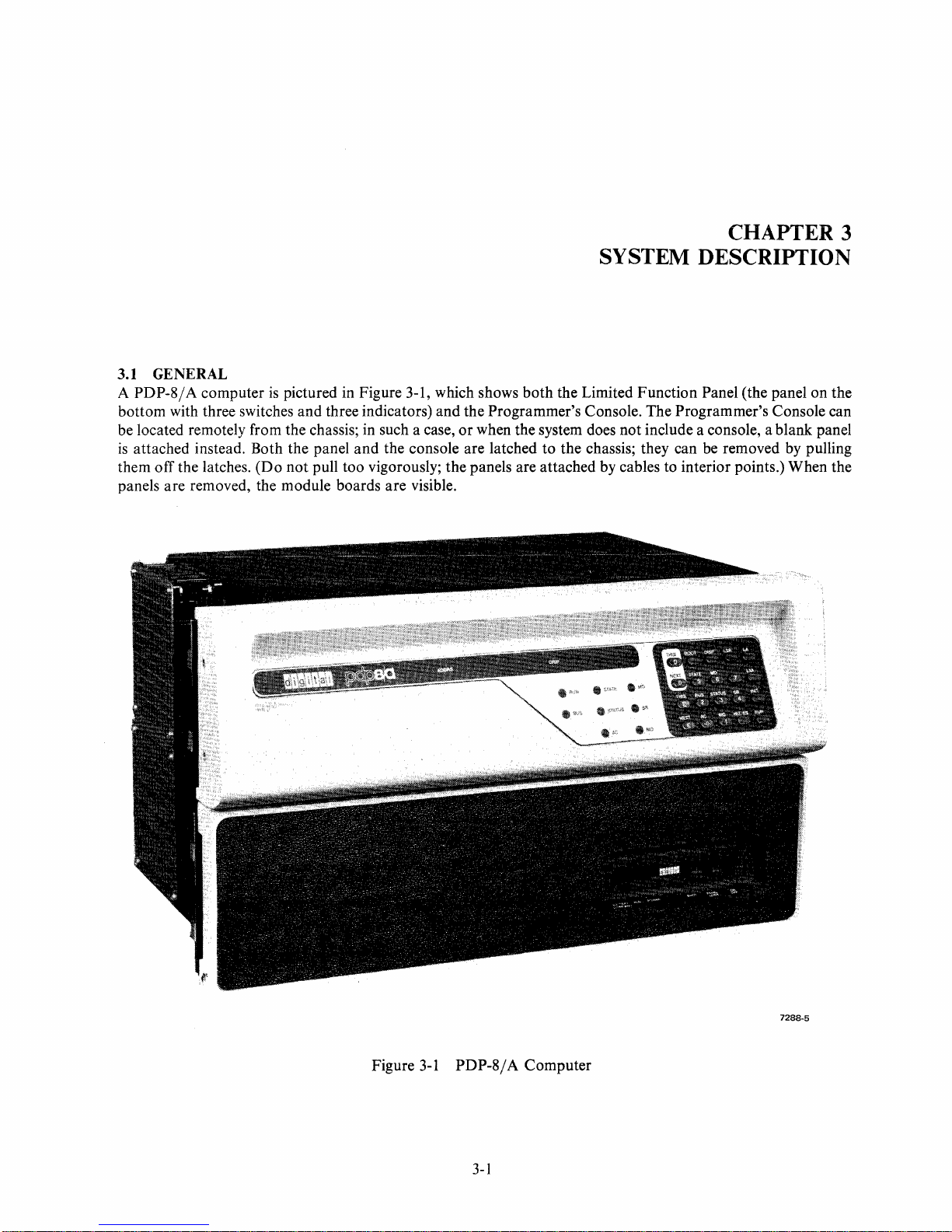

A

PDP-8/

bottom with three switches and three indicators) and the Programmer's Console. The Programmer's Console can

be located remotely from the chassis; in such a case,

is

attached instead. Both the panel

them

panels

A computer

off

the latches.

are

removed, the module boards

is

pictured in Figure 3-1, which shows

(Do

not

both

the Limited Function Panel (the panel on the

or

when the system does not include a console, a blank panel

and

the console are latched to the chassis; they can be removed by pulling

pull too vigorously; the panels are attached by cables to interior points.) When the

are

visible.

Figure

3-1

PDP-8/A

3-1

7288-5

Computer

Page 17

The

PDP-SI

A computers have three different mechanical assemblies

that

can be characterized by

the

number

of

available Omnibus slots;

that

is, the

PDP-SI

A semiconductor

computer

assembly

has

a IO-slot Omnibus, while

the

SA

computer assemblies have either a 12-slot

or

a 20-slot Omnibus. Table

3-1

relates the various PDP-S I A

computers

to

some

of

the basic system components.

Note

that

the

SA400 can be considered to be the basic SA

computer,

having a core memory,

an

SA

CPU,

and

a 12-slot Omnibus. Thus,

the

SA420 differs only in

that

it has

a

20-slot Omnibus; the SA600 differs in

that

it has a

PDP-S/E

CPU;

the

SA620 differs in

that

it has a

PDP-S/E

CPU

and

a 20-s10t Omnibus; the

SASOO

differs

in

that

it

has

an

FPP-SA

(not

indicated in Table 3-1);

and,

the

SAS20 differs in

that

it has an FPP-SA

and

a 20-s10t Omnibus. Also, note

that

only the

SA

computers

that

use a

PDP-S/E

CPU

can be expanded.

Table

3-1

PDP-8fA Computer Assemblies

Computer

CPU

Memory *

Basic Power Assembly

Omnibus

Expandable ?

PDP-8fA

KK8-A

Semiconductor

H763 H9192

(1

O-sIot)

No

8A400

KK8-A

Core

H9300

H9194 (12-s10t)

No

8A420

KK8-A

Core

BA8-C

H9195 (20-slot)

No

8A600

KK8-E

Core

H9300 H9194 (12-slot)

Yes -as

many

as

20

slots can

be

added

8A620

KK8-E

Core

BA8-C

H9195 (20-slot)

Yes -as

many

as

20

slots can

be

added

8A800

KK8-A

Core

H9300

H9194 (12-slot)

No

8A820

KK8-A

Core

BA8-C

H9195 (20-slot)

No

* A

KMS-A

(or

KMS-E)

Extended Memory Option module must

be

included

in

all the

SA

computers, since their basic memory capacity

is

SK

or 16K; the

KMS

is

optional with the PDP-Sf A semiconductor computer, since the basic memory capacity can be less than,

greater than, or equal to 4K.

In addition to the

CPU,

most

DIGITAL

PDP-S/E

options

will

operate

with the

PDP-S/A

computers. The

following will not:

1.

KPS-E Power

Faill

Auto-Restart

option

2.

DKS-EA Line Frequence Real-Time Clock

option

3.

MMS-E

4K

Core

Memory

4. MMS-EJ SK

Core

Memory

The

KES-E

option

(Extended Arithmetic Element)

and

the

TDS-E

DECtape

Control

will

operate

only with the

SA600 and SA620 computers.

Moduies

can

be inserted in almost any

PDP-SI

A Omnibus slot. There are, however, some restrictions

and

these

are summarized in Table 3-2.

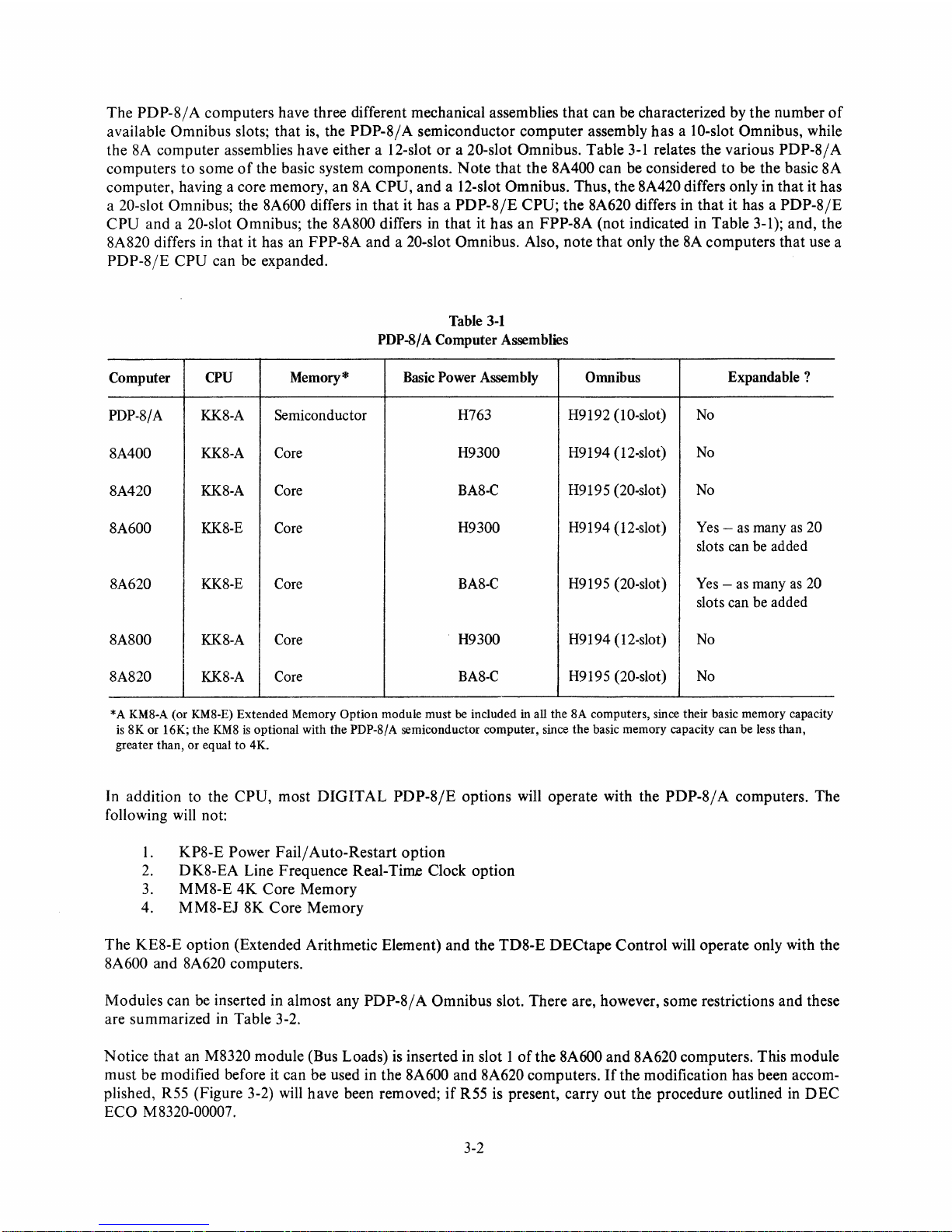

Notice

that

an MS320 module (Bus Loads)

is

inserted in slot 1

of

the

SA600

and

SA620 computers. This module

must be modified before it can be used in the

SA600 and SA620 computers.

If

the modification has been accom-

plished, R55 (Figure 3-2) will have been removed;

if

R55 is present, carry

out

the procedure outlined in

DEC

ECO

MS320-00007.

3-2

Page 18

Table 3-2

PDP-Sf A Computers, Dedicated Omnibus Slots

PDP-8/ A Semiconductor,

Omnibus Slot SA600 SA600 + KES-E SA620

SA620

+ KES-E

SA400, SA420,

SASOO,

SAS20

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

IS

19

20

NOTES:

I

M8320

M8316

M8317

I

I

I

M8300

I

M8310

M8330

M8320

I

M8316

M8317

I

M8300

M8310

M8341

M8340

I

M8330

I

M8320

M8316

M8317

MS300

MS310

MS330

M8320

M8316

M8317

MS300

MS310

MS341

MS340

MS330

I

I

I

I

1. MS316 and MS317 are interchangeable in slots 2 and 3.

2. Module numbers are related

to

options as follows:

MS315

MS316

MS317

MS320

MS300 }

MS310

MS330

CPU

(KKS-A)

I/O Option Board (DKCS-AA)

Extended Option Board (KMS-A)

Bus Loads

I

CPU

KKS-E

Timing Generator

KKS-E

08

-1785

Figure

3-2

Part

of

M8320 Module Showing R55,

Which

is

Removed for 8A Operation

3-3

M8315

M8316

M8317

Page 19

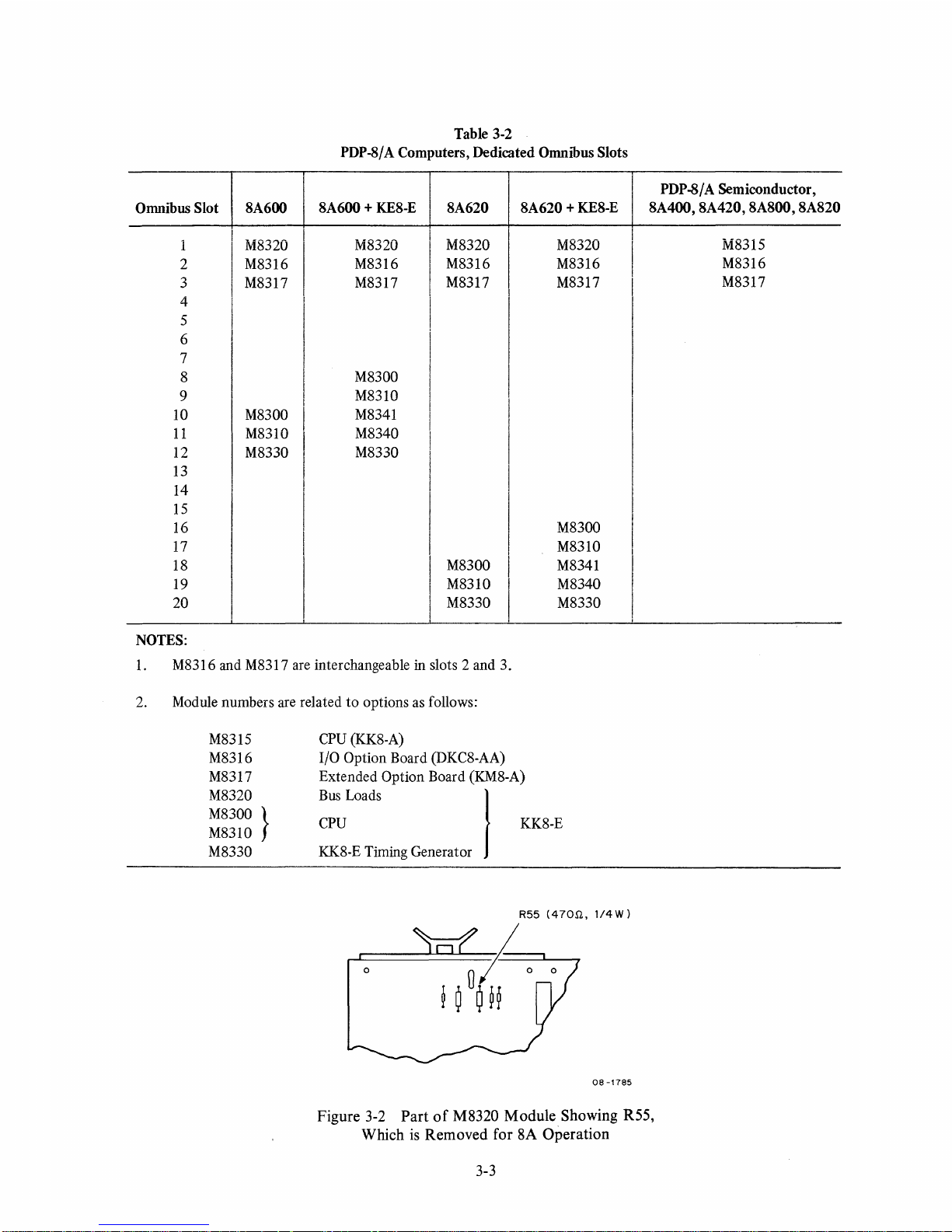

3.2 CHASSIS DESCRIPTIONS

Three chassis types are available. The

PDP-8/

A semiconductor computer chassis

is

illustrated in Figure 3-3. (The

front panels have been removed.) Modules are inserted in the Omnibus from the front

of

the unit. Both quad-and

hex-size modules can be inserted;

the

fingers

on

connectors E

and F of

the hex size modules do

not

carry

Omnibus signals. (Some hex modules

do

not

have connectors E

and

F.) Figure 3-4 illustrates the dimensions

of

the same computer, as well as indicating the ac line

and

fuse locations.

G8016

REGULATOR

ASSEMBLY

POWER

CONTROL

FUSE

MASTER-SLAVE

SWITCH

Figure 3-3 PDP-8 / A Semiconductor Chassis

3-4

LIMITED

FUNCTION

PANEL

7.2884

Page 20

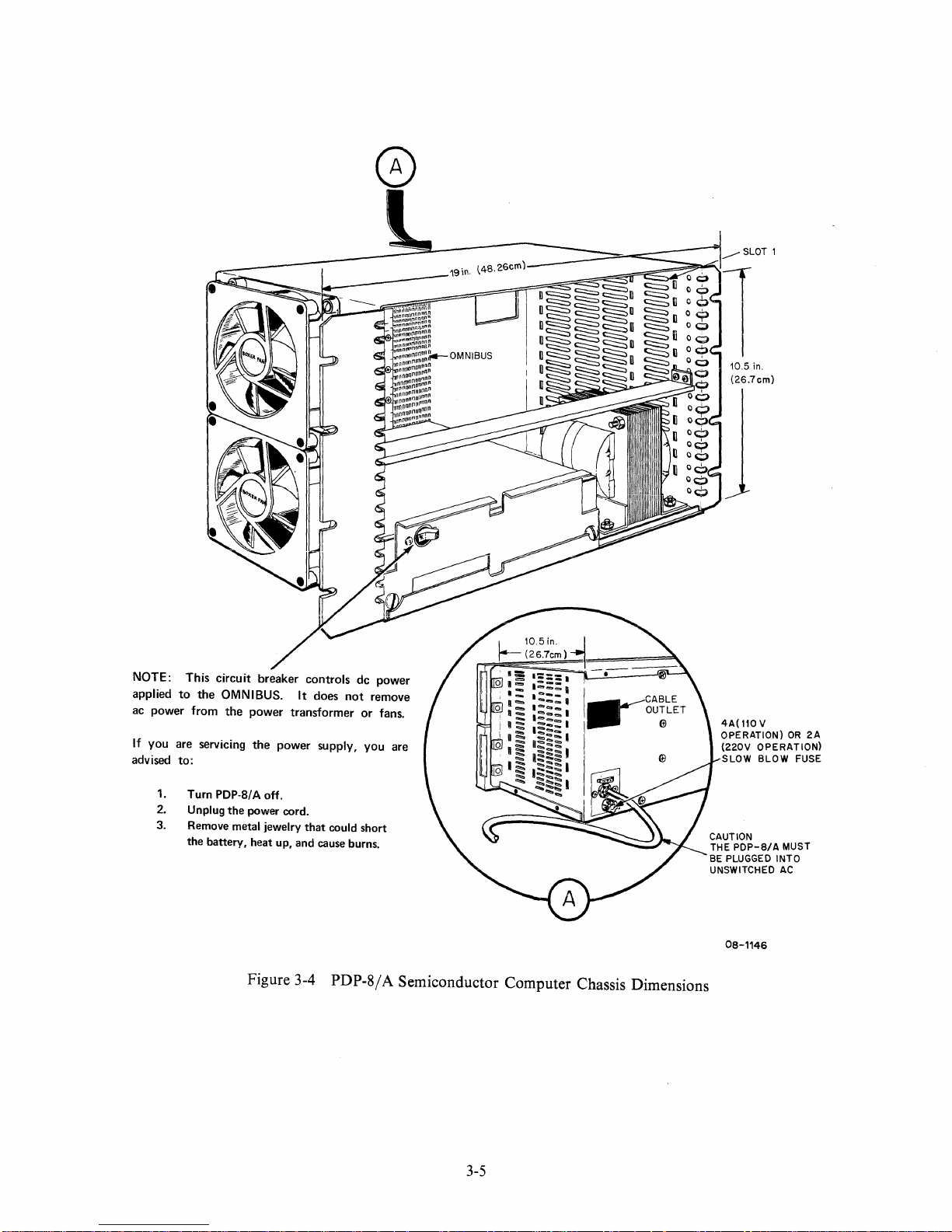

'\9

in.

l48.

26cm)

NOTE:

applied

ac

power

If

you

advised

1.

2.

3.

This

circuit

to

the

OMNIBUS.

from

the

are servicing

breaker

power

the

controls

It

does

transformer

power

supply,

not

to:

Turn PDP-8/A

off.

Unplug the power cord.

Remove metal jewelry that could short

the battery, heat up, and

cause

burns.

Figure 3-4 PDP-8f A Semiconductor Computer Chassis Dimensions

dc power

remove

or

fans.

you

are

4A(110V

OPERATION)

(220V

OPERATION)

SLOW

BLOW

08-1146

OR

FUSE

2A

3-5

Page 21

Figure 3-5 shows the chassis

that

is

used with

the

8A400, 8A600, and 8A800 computers. The dimensions are the

same as the

PDP-8/

A semiconductor chassis; interior components

are

different.

The

08018

Regulator Board

assembly has been removed to show the connector in which

the

assembly is inserted. The Omnibus connector

blocks in the connector

HE" position are needed

to

accommodate the E connector

of

the core memory modules.

REGULATOR

BOARD

SLOT

POWER

CONTROL

FUSE

CORE

MEMORY

SLOTS

CABLE

TO CONNECT

LIMITED

FUNCTION

PANEl

Figure 3-5 8A Chassis - H9300 (Transformer Cover Removed)

3-6

7367-3

Page 22

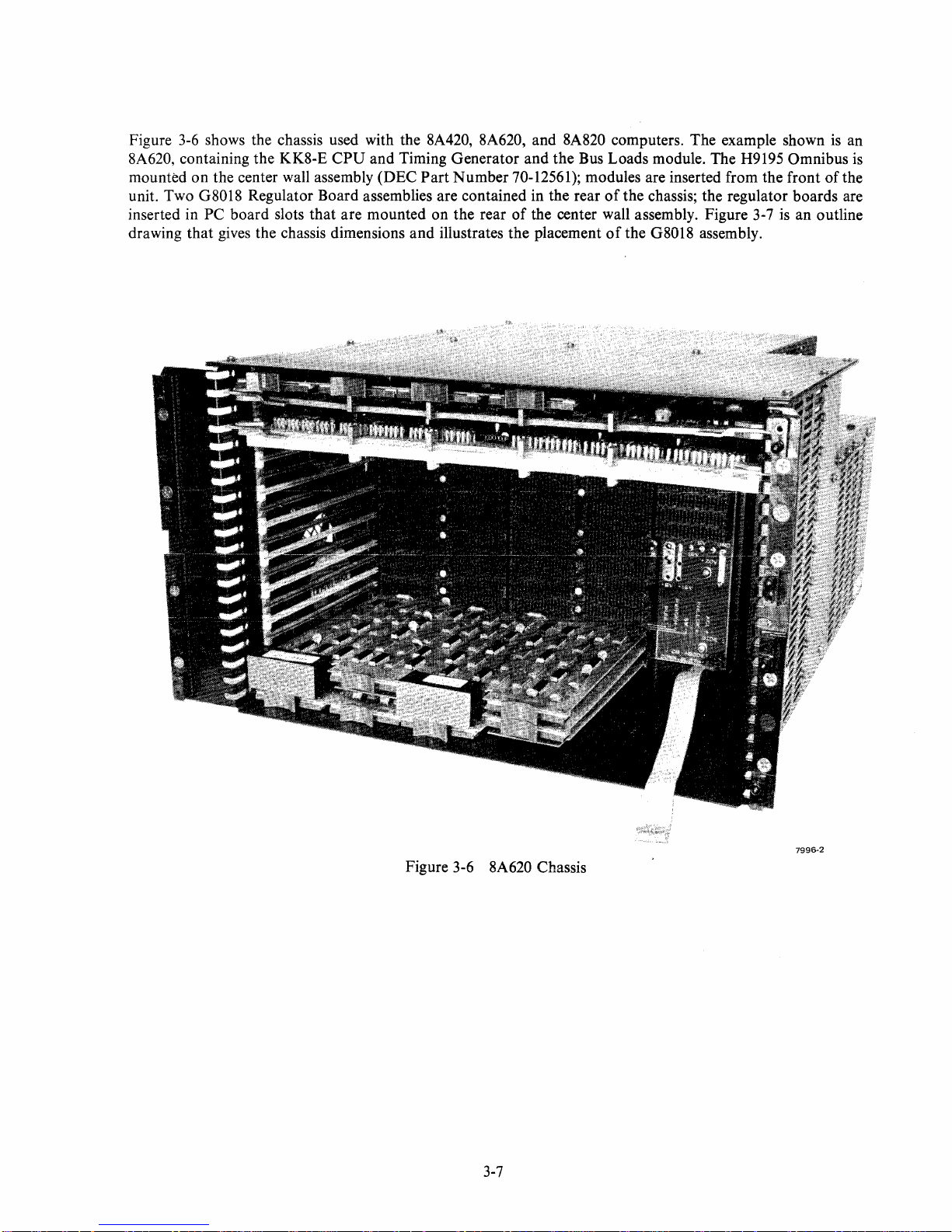

Figure

3-6

shows the chassis used with the 8A420, 8A620, and 8A820 computers. The example shown

is

an

8A620, containing the KK8-E

CPU

and Timing Generator

and

the Bus Loads module. The H9195 Omnibus

is

mounted on the center wall assembly (DEC

Part

Number

70-12561); modules are inserted from the front

of

the

unit. Two G8018 Regulator Board assemblies are contained in the rear

of

the chassis; the regulator boards are

inserted in

PC board slots

that

are mounted on the rear

of

the center wall assembly. Figure 3-7

is

an outline

drawing that gives the chassis dimensions

and

illustrates the placement

of

the G8018 assembly.

7996-2

Figure 3-6 8A620 Chassis

3-7

Page 23

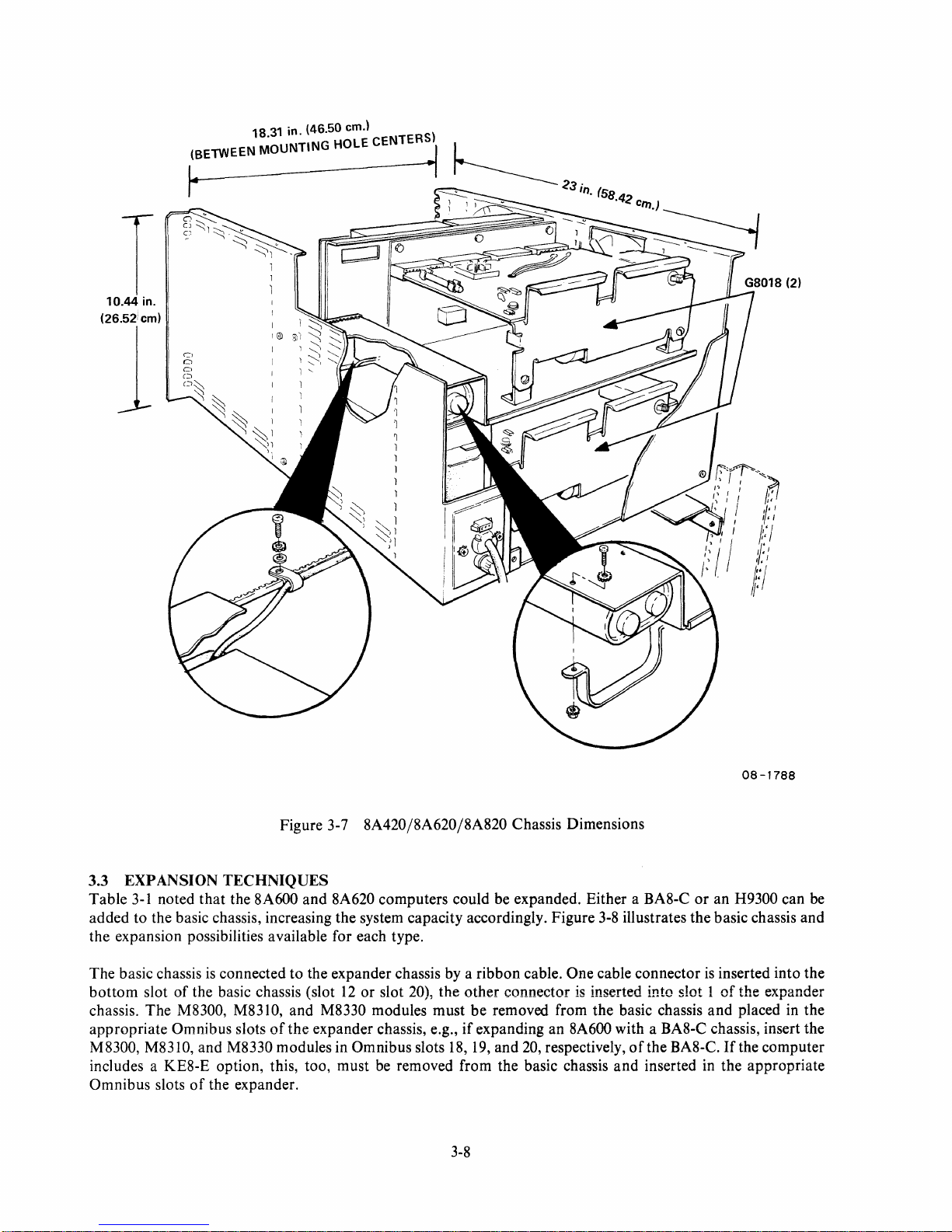

(BElWEEN

1831

in.

(46.50 em.)

~OUNTING

HOLE

CENTER~

~

T

10.44

in.

(26.52: em)

1

~

~~~

8.42

e,".)

~

Figure 3-7 SA420 /SA620 /SAS20 Chassis Dimensions

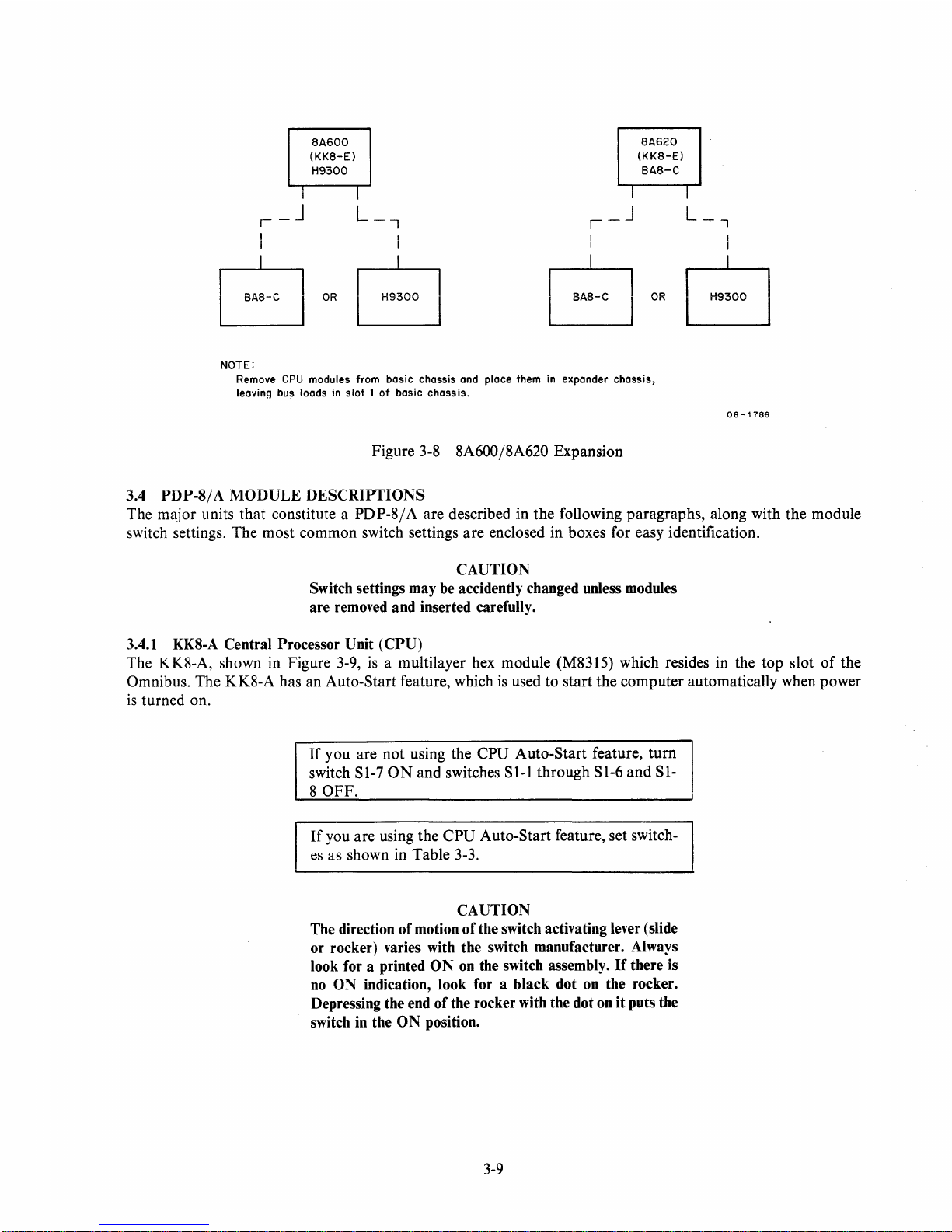

3.3 EXPANSION TECHNIQUES

Table

3-1

noted

that

the SA600

added to the basic chassis, increasing the system capacity accordingly. Figure

the expansion possibilities available for each type.

The basic chassis

bottom

chassis. The

appropriate

MS300, MS310, and MS330 modules in Omnibus slots IS,

includes a

Omnibus slots

slot

is

connected to the expander chassis by a ribbon cable.

of

the basic chassis (slot

MS300, MS310, and MS330 modules must

Omnibus slots

KES-E option, this, too, must be removed from the basic chassis

of

the expander.

and

of

the

expander chassis, e.g.,

SA620 computers could be expanded. Either a BAS-C

3-S

illustrates the basic chassis and

One

cable connector

12

or

slot 20), the

other

connector

be

removed from the basic chassis

if

expanding an SA600 with a BAS-C chassis, insert the

19,

and 20, respectively,

3-S

is

inserted into slot 1

of

the BAS-C.

and

inserted in the appropriate

08

-1788

or

an H9300 can be

is

inserted into the

of

the expander

and

placed in the

If

the computer

Page 24

SA600

(KKS-E)

H9300

I

L_-,

I

BORB

NOTE:

SA620

(KKS-E)

BAS-C

Remove

CPU

modules from basic chassis and place them in expander chassis,

leaving bus loads in

slot 1 of

basic chassis.

Figure 3-8 8A600 /8A620 Expansion

3.4

PDP-8f

A

MODULE

DESCRIPTIONS

08

-1786

The major units

that

constitute a

PDP-8/

A are described in

the

following paragraphs, along with

the

module

switch settings. The most common switch settings

are

enclosed in boxes for easy identification.

CAUTION

Switch settings may be accidently changed unless modules

are removed and inserted carefully.

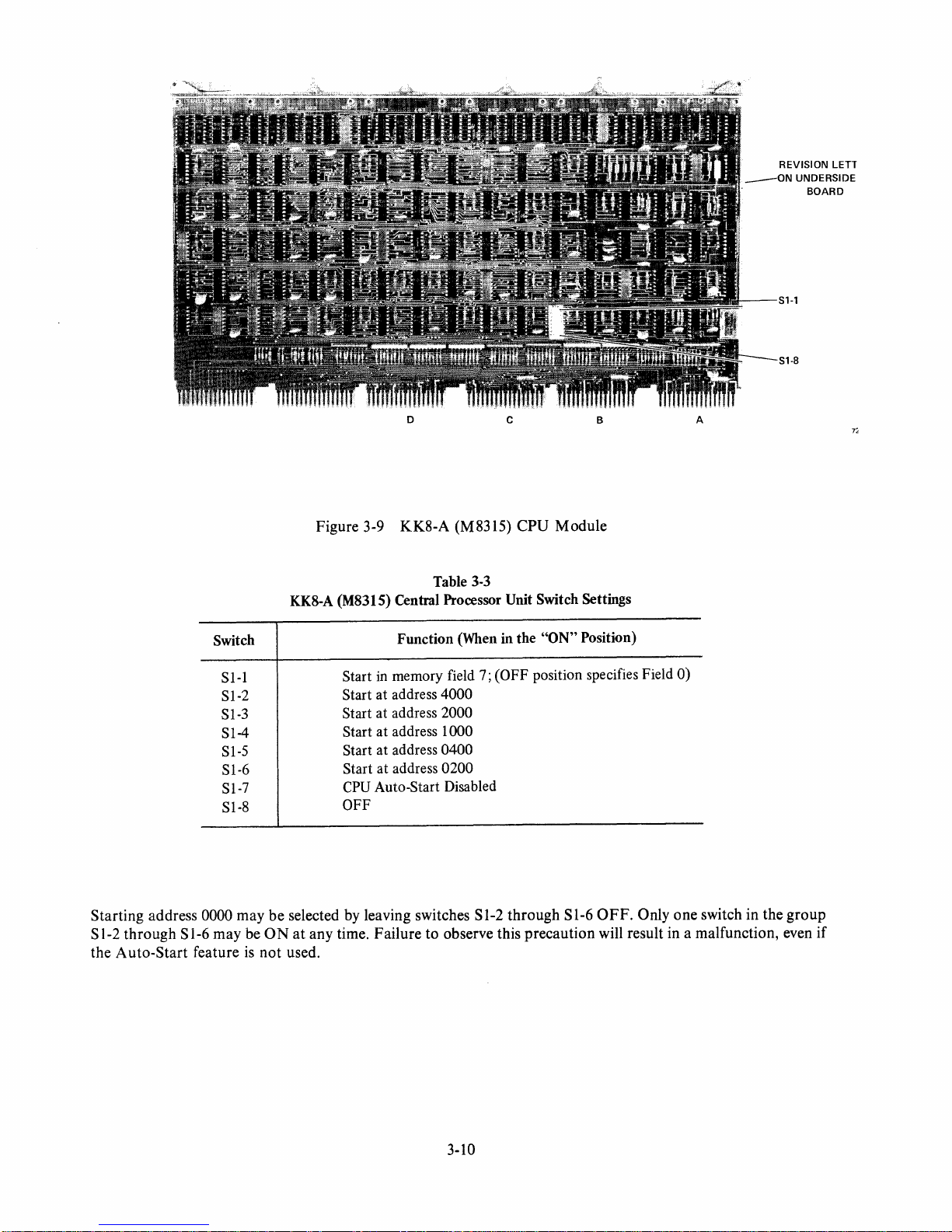

3.4.1

KKS-A Central Processor Unit

(CPU)

The KK8-A, shown in Figure 3-9,

is

a multilayer hex module (M8315) which resides in the

top

slot

of

the

Omnibus. The KK8-A has an Auto-Start feature, which

is

used to start

the

computer automatically when power

is

turned on.

If

you

are

not

using the

CPU

Auto-Start feature,

turn

switch SI-7

ON

and

switches SI-1

through

S1-6

and

SI-

8

OFF.

If

you are using

the

CPU

Auto-Start feature, set switch-

es

as shown in Table 3-3.

CAUTION

The direction

of

motion

of

the switch activating lever (slide

or rocker) varies with the switch manufacturer. Always

look for a printed

ON

on

the switch assembly.

If

there is

no

ON indication, look for a black dot on the rocker.

Depressing the end

of

the rocker with the dot on it puts the

switch in the

0 N position.

3-9

Page 25

__

ON

REVISION LETT

UNDERSIDE

BOARD

S1-1

S1-8

Switch

Sl-l

SI-2

SI-3

Sl4

Sl-S

SI-6

Sl-7

SI-8

D

Figure

KK8-A (M8315) Central Processor Unit Switch Settings

Start

3-9

KK8-A

Function

in

memory field 7; (OFF position specifies Field 0)

(M8315)

Table 3-3

(When in

c

CPU

the

Module

"ON"

B

Position)

Start at address 4000

Start at address 2000

Start at address looO

Start at address 0400

Start at address 0200

CPU

Auto-Start Disabled

OFF

A

Starting

SI-2

the

address 0000

through

Auto-Start

Sl-6

feature

may

may

be

is

be

selected by leaving switches

ON

at

any

not

used.

time.

Failure

Sl-2

to

observe this

3-10

through

precaution

Sl-6

OFF.

Only

one

switch

will result in a malfunction, even

in

the

group

if

Page 26

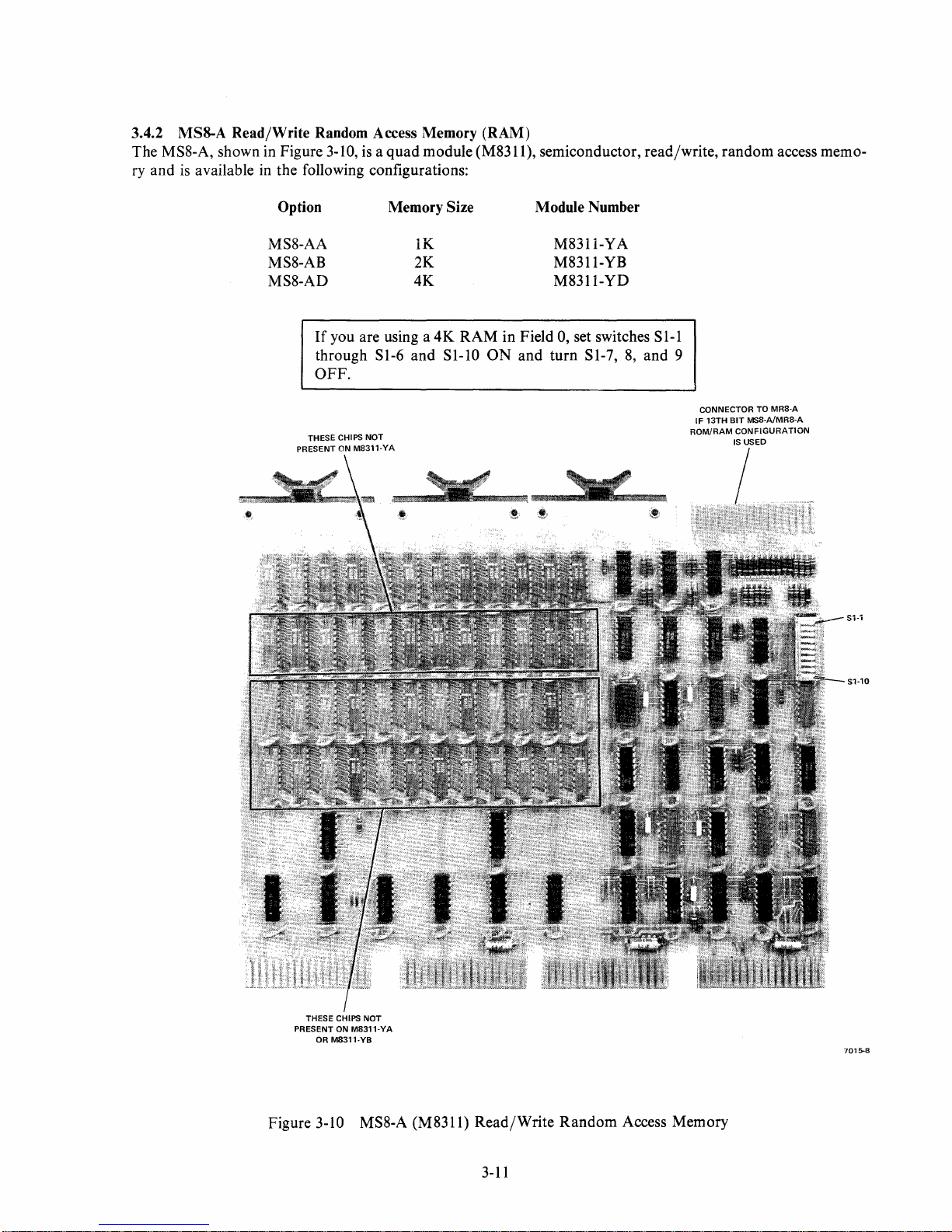

3.4.2 MS8-A

MS8-A, shown in Figure 3-10,

The

ry and

is

Read/Write

available in the following configurations:

Random Access Memory (RAM)

is a quad

module (M8311), semiconductor, read/write,

random

access memo-

Option

MS8-AA

MS8-AB

MS8-AD

If

through SI-6

OFF.

Memory Size

lK

2K

4K

you are using a

and

4K

SI-10

Module Number

M8311-YA

M8311-YB

M8311-YD

RAM

in Field 0, set switches SI-1

ON

and

turn

SI-7,

8,

and 9

CONNECTOR TO MRS-A

IF

13TH

BIT

ROM/RAM

MSS-A/MRS-A

CONFIGURATION

S1-1

THESE CHIPS

PRESENT ON

OR

MS311-YA

M8311-YB

NOT

Figure 3-10 MS8-A (M8311)

Read/Write

Random

S1-10

7015-8

Access Memory

3-11

Page 27

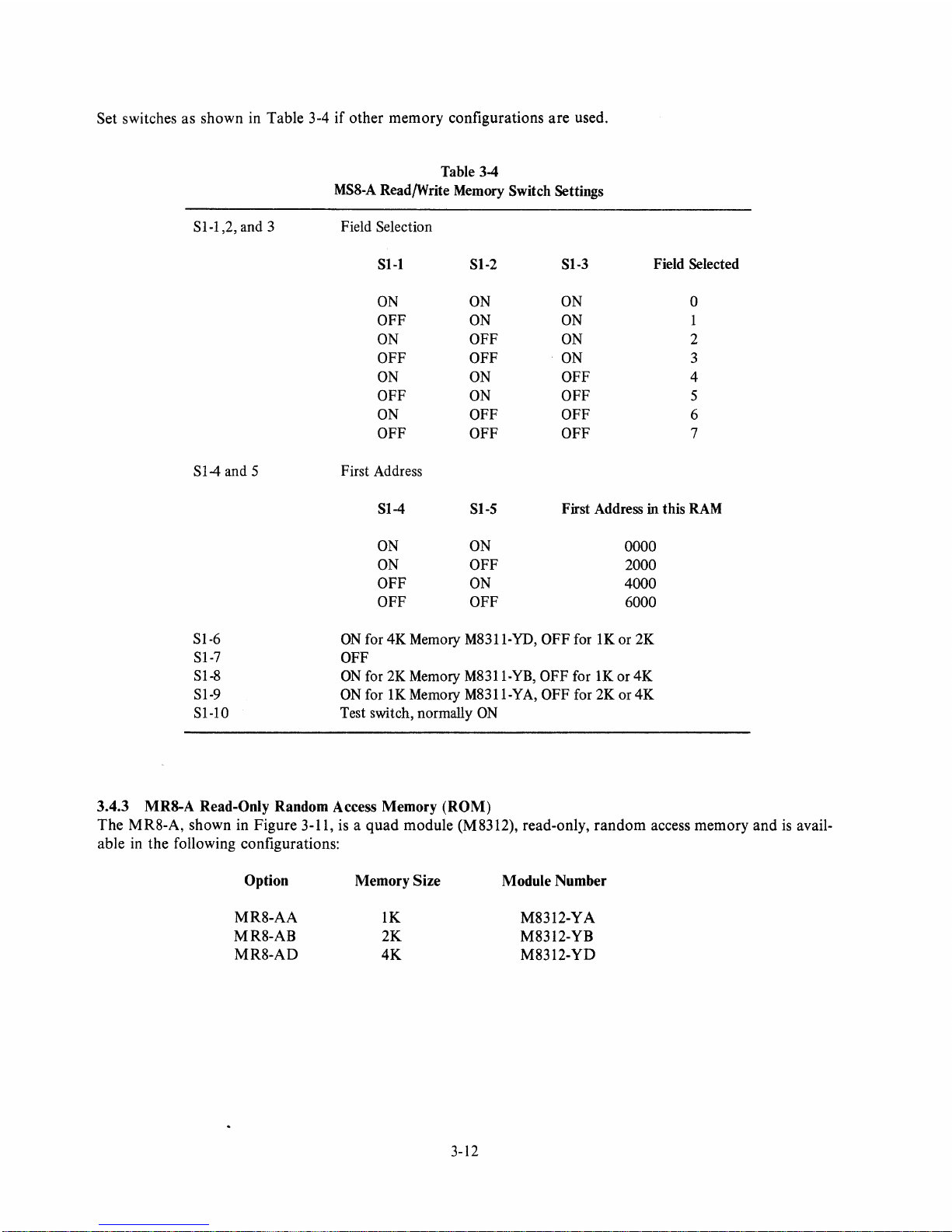

Set switches

as

shown

in

Table

3-4

if

other

memory

configurations

are

used.

Table

34

MS8-A

Read/Write Memory Switch Settings

SI-1 ,2, and 3 Field Selection

SI-1 SI-2

81-3

Field Selected

ON

ON ON

0

OFF ON

ON

1

ON

OFF

ON

2

OFF OFF

ON

3

ON ON

OFF 4

OFF

ON

OFF

5

ON

OFF

OFF

6

OFF

OFF

OFF

7

Sl-4and5

First Address

SI-4 81-5 First Address

in

this

RAM

ON ON

0000

ON OFF

2000

OFF

ON

4000

OFF OFF

6000

SI-6

ON

for

4K

Memory M8311-YD, OFF for 1K or 2K

SI-7

OFF

SI-8

ON

for 2K Memory M8311-YB, OFF for

lK

or

4K

SI-9

ON

for

lK

Memory M8311-YA, OFF for 2K or

4K

Sl-10

Test switch, normally

ON

3.4.3 MRS-A Read-Only Random Access Memory

(ROM)

The

MRS-A,

shown in

Figure

3-11, is a

quad

module

(MS312), read-only,

random

access

memory

and

is avail-

able in

the

following configurations:

Option

MRS-AA

MRS-AB

MRS-AD

Memory Size

lK

2K

4K

3-12

Module Number

MS312-YA

MS312-YB

MS312-YD

Page 28

S9-1

S9-8

THESE

THREE

CONNECTORS

ARE

REMOVED

TO

PROGRAM

THE

ROM,

BUT

THEY

MUST

BE

IN

PLACE

FOR

NORMAL

OPERATION

CONNECTOR

TO

MS8-A

IF

13TH

BIT

MS8-A/MR8-A

ROM/RAM

CONFIGURATION

IS

USED

Figure 3-11

MR8-A

(M8312)

Read

Only

Memory

(ROM)

The

first address

is

always location 0000

of

the

selected memory field.

I f you

are

using a 4K

ROM

in Field 0 with no connections

to

RAM,

set the following switches

ON:

SI-1 through SI-8;

S3-1

through S3-8;

S5-1

through S5-8;

S7-1

through S7-8;

S8-1

through S8-8;

S9-1

through S9-8; S4-1, 2,

3,4,

6, 7;

and

S6-3

through S6-8. Set the following switches OFF:

S2-1

through S2-8; S4-5, 8; S6-1, 2.

If a RAM

is

used with

top connectors, change

S4-7

to

OFF and

S4-8

to

ON.

3-13

S3

S1-1

Sl·8

54

S2

7230-1

Page 29

Set switches

as

shown

in Table 3-5

All switches must be

grammed (i.e., while

if

MRS-

other

configurations

are

used.

CAUTION

OFF

when the M8312 is being pro-

data

is being loaded into

Table 3-5

A Read Only Memory Switch Settings

ROM).

Switch

SI-1 to SI-8

S2-1

,8, and 5

82-2 and 4

82-3,6 and 7

Function/Position

ON

Size 8elect 8witch 8ettings

S2

..

S2-1

ON

ON

OFF

OFF

Field 8elect 8witch 8ettings

Field

0

1

2

3

4

5 ON

6 OFF

7

S

ON

ON

OFF

S2·6

OFF

ON

OFF

ON

OFF

ON

S2-5

OFF

OFF

OFF

S2-3

OFF

OFF

ON

ON

OFF

OFF

ON

ON

Memory Size

lK

2K

4K

S2-7

OFF

OFF

OFF

OFF

ON

ON

ON

ON

S3-1

to

S3-8

84-1,2,3,4, and 6

84-5

84-7

84-8

85-1

to

S5-8

86-1

and 86-2

86-3,4,5,6,7, and 8

87-1

to

87-8

88-1

to

88-8

89-1

to

89-8

ON

ON

OFF

OFF

for ROM/RAM Combination; otherwise

ON

for ROM/RAM Combination; otherwise OFF

ON

OFF

ON

ON

ON

ON

3-14

ON

Page 30

3.4.4 MM8-AA

The

MM8-AA,

of

core memory.

8K

Core Memory

shown in Figure 3-12,

If

you

are using core memory

Wl-3

and

is

a hex module (G649) with

in

Wl-2

and remove W2-4

an

Fields 0

and

W3-4.

H219-A Stack Assembly

and

1,

install

that

contains

8K

Figure 3-12 MMS-AA SK

3-15

Core

7388-2

Memory

Page 31

Install

or

remove

jumpers

as

shown

MM8-AA

in

Table

8K

3-6

if

other

Table

3-6

Core Memory

memory

Jumper

fields

are

Installation

in

use.

3.4.5

The

of

core

I nstall

Fields Used

o and 1

2 and 3 Removed

4 and 5 In Removed

6 and 7 Removed Removed

MMS-AB

MMS-AB,

memory.

or

remove

16K

shown

jumpers

Core

in

Figure

as

WI-3

In

Memory

3-13, is a

If

the

MMS-AB

ers

WI-3

W3-4

should

shown

MM8-AB

and

in

hex

Wl-2

be

Table

16K

module

is

removed.

WI-2 W2-4 W3-4

In

In

(0650)

installed

3-7

Core Memory

should

if

other

Table 3-7

in

be

Removed

In

Removed

In

with

an

H219-B

Fields 0 through

installed

memory

Jumper

and

fields

Installation

Stack

3,

jump-

W2-4

are

used.

Assembly

and

Removed

Removed

In

In

that

contains

16K

Fields Used

o to 3

4

to

7

WI-3 WI-2 W2-4

In

Out

In

In

Out

In

3-16

W3-4

Out

Out

Page 32

7388-1

Figure

3-13

MMS-AB

3-17

16K

Core Memory

Page 33

3.4.6 DKC8-AA

There

14).

the

(side 1

are two

OK

other

as etch revision D (shown in

is

the

component

viewing side 2).

I/O

Option Board

C8-AA

hex

modules

(M 8316) in existence;

side). Lettering

Figure

similar

3-15).

to

the

one

The

etch

following

is defined as

etch

revision C (shown in

revision is identified

appears

near

the

on

side 2

of

lower right

Figure

the

PC

corner

3board

(when

Option

Board

1

Side 2

M8316

50109000

The

letter

0 indicates

the 0 etch

revision level; differences

S1-1

that

exist

revision.

are

indicated in

The

information

the

description.

in

this section is

J1

PROGRAMMERS

CONSOLE

not

totally applicable

J2 PROGRAMMERS

CONSOLE (CONNECTS

TO BOTTOM CONNEC-

TOR OF PROGRAMMERS

CONSOLE)

to

each

J5

PARALLEL

If 0

TRANSMIT

J4

PARALLEL

If 0 RECEIVE

J3

SERIAL

LINE

UNIT

-

{

{ "

------"'!'

..

,',

Figure

3-14

OKC8-AA

(M8316)

I/O

Option

7015-6

Board

3-18

Page 34

REVISION LETTER

ON

UNDERSIDE

OF

BOARD (SIDE 2)

J3

SERIAL

LINE

UNIT

J5

PARALLEL

I/O

TRANSMIT

J4

S1-1

S1-10

PARALLEL

I/O

RECEIVE

SIDE

1

J2

PROGRAMMER'S

CONSOLE (CONNECTS)

TO BOTTOM

CONNECTOR

OF

PROGRAMMER'S CONSOLE

J1

PROGRAMMERS

CONSOLE

Figure 3-15 0 Etch Revision

of

OKC8-AA

(M8316)

I/O

Option

Board

The 0 KC8-AA combines four options:

8071-1

L Serial Line

Unit

(SLU),

110

to

9600 (50

to

9600 for revision

D)

baud

rate interface for Teletype,@

VT50,

or

other

compatible serial line unit

2_

Real-Time Clock - Crystal controlled

at

100

Hz

3_

General-Purpose Parallel

I/O

- 12-bit

I/O

for

user's device

or

another

POP-8/

A

NOTE

The General-Purpose Parallel

I/O

on

the D etch revision

of

the M8316 module can

be

used

as

an interface for the

LA180.

Data

to

the LA180 must be supplied in com-

plemented form. The

lOTs

are

different from the LA8

interface designed for the LAl80. A BC80-A cable, available from DIGITAL, must be used to connect the GeneralPurpose Parallel

I/O

to the LA180.

®Teletype

is

a registered trademark

of

Teletype Corporation.

3-19

Page 35

4.

Console Logic - Logic

to

connect the

KC8-AA

Programmer's

Console

to

the

Omnibus

Revision C:

For

Teletype (ASR33)

operation

without

real-time clock software, set switches S 1-4, 6,

and 8 to

the

ON

position; set switches SI-1, 2,

3,

5,

and 7 to

the

OFF

position.

Revision D:

For

Teletype (ASR33) operation

without

real-time clock software, set switches

SI-I,

3,4,6,8,

and

9

to

the

ON

position; set switches

Sl-2,

5,

and 7 to

the

OFF

position.

(Sl-10

is

a spare.)

For

other

operation, set switches as shown in Tables 3-8 and 3-9.

Table 3-8

DKC8-AA

I/O Option Board Switch Settings, C-Etch Module

Switch

Function

Sl-1,2and3

Baud Rate

as

shown in Table below:

SI-1

SI-2

SI-3 Baud Rate

OFF

OFF

OFF

110

OFF

OFF

ON

150

OFF

ON

OFF

300

OFF

ON ON

600

ON

OFF OFF

1200

ON

OFF

ON

2400

ON

ON

OFF

4800

ON ON

ON

9600

S14

Clear Data Available at Time State 1 (normally

ON)

Sl-5

ON

enables Real Time Clock

Sl-6

Test (normally

ON,

OFF

for special testing)

Sl-7

ON

for 1 stop bit,

OFF

for two stop bits

Sl-8

ON

enables TTY filter

in

20

rnA

CKT

(used only for 100 baud)

3-20

Page 36

Table 3-9

DKC8-AA Option Board Switch Settings, D-Etch Module

Switch

Sl-1, 2, 3, and 4

Sl-5

Function

as

Baud rate

*OFF

ON

= Real Time Clock enabled

OFF = Read Time Clock disabled

shown in table below:

SI-4 SI-3

ON

ON

ON ON

ON

ON

ON

ON

ON

OFF

OFF

OFF ON

OFF

OFF

OFF

OFF

ON

ON

ON

OFF

OFF

OFF OFF

OFF

ON

ON

ON

OFF

OFF

OFF

OFF

SI-2

ON

ON

OFF

OFF

ON

ON

OFF

ON

ON

OFF

OFF OFF 3600

ON

ON

OFF

OFF

SI-1 Baud Rate

ON

OFF

ON

OFF

ON 150

OFF 300

ON 600

OFF 1200

ON

OFF 2000

ON

ON

OFF 7200

ON

OFF 19.2K

50

75

110

134.5

1800

2400

4800

9600

Sl-6

Sl-7

Sl-8

Sl-9

*Serial Line will

ON

= Test Switch (always ON)

ON

= 1 Stop Bit in SLU character

OFF = 2 Stop Bits in SLU character

ON;:: ASR/KSR 33 DR35 fIlter in (across SLU 20 rnA REC'V Leads.

ON

if

Baud Rate

OFF -filter out

ON = TS1

OFF

not

run at this baud rate. This setting

clears DATA AVAIL flip-flop in Parallel I/O Section

= DATA AVAIL

is

110

or

not

is

below.)

cleared by TSI

not

to be used.

3-21

Page 37

3.4.7 KMS-A Extended Option Board

The KMS-A, shown in Figure 3-16,

is

Power-Fail/ Auto-Restart

Bootstrap Loaders - Provide commonly used

and

Memory Extension

Timeshare Control

If

you are using paper tape under control

strap switches, no Auto-Restart, and timeshare enabled,

set the following switches

S2-1, S2-5 through S2-7; set the following switches

Sl-5 through Sl-7, S2-2 through S2-4,

a hex module (MS317)

I/O

loaders

ON:

SI-1 through SI-4, SI-S,

that

combines the following options:

of

the boot-

OFF:

and

S2-S.

Figure 3-16 KMS-A (MS317) Extended

3-22

Option

7299-1

Board

Page 38

Other

switch settings for

the

KM8-A

are listed in Tables 3-10

through

3-14.

Program

S2-5

Hi-Lo

RIM*

ON

RK8-E*

ON

TC08*

ON

RF08/DF32D*

OFF

TA8-E*

OFF

NOTE

There

are

three types

of

bootstrap

ROMs

used on the

KM8-A. E82 and E87 have different labels for the different bootstrap

ROMs.

Switches on modules

that

have E82

and E87 (Figure 3-16) labeled 87A2 and 88A2 should be

set according to Table 3-11.

If

E82 and E87 are labeled

158A2 and 159A2, use Table 3-12 for switch settings.

For

CL8

systems using the RX8-E, E82 and E87 are labeled

156A2 and 157A2; use Table 3-13.

(If

Table 3-13 is used,

Auto-Restart address

0 must be selected, i.e., S2-2 is

OFF,

S2-3 is

OFF,

and S2-4 is

OFF.)

Restart

Address

0

200

2000

4200

S2-6

ON

OFF

OFF

ON

ON

Table 3-10

Auto-Restart Select Switch Settings

S2-2

S2-3

OFF OFF

OFF

ON

ON

OFF

ON ON

Table

3-11

Bootstrap Select Switch Settings

for

ROMs

Labeled 87 A2 and 88A2

S2-7

S2-8

SI-1

ON

OFF

ON

ON

OFF

ON

OFF

ON

OFF

ON

ON

ON

ON

OFF

ON

S2-4

OFF

OFF

OFF

OFF

SI-2

ON

OFF

ON

OFF

OFF

*May

only be used with 4K

of

Read/Write Memory in Field

O.

Program

S2-5

Hi-La

RIM

ON

RK8-E

ON

RX8-E

ON

RF08jDF32D

OFF

TA8-E

OFF

Table 3-12

Bootstrap Select

Switch Settings for

ROMs

Labeled 158A2 and 159A2

S2-6

S2-7

S2-8 SI-1

ON

ON

OFF

ON

OFF

ON

OFF

ON

OFF

OFF

ON

OFF

ON

OFF

I

ON

OFF

ON

OFF

OFF OFF

3-23

SI-2

ON

OFF

ON

ON

ON

Memory

SI-3

Address

ON

7737

ON

0024

ON

7613

OFF 7750

OFF

4000

Memory

SI-3

Address

ON

7737

ON

0024

ON

0033

OFF

7750

OFF

4000

Page 39

Program

S2-5 S2-6

RX8E TEST

ON

ON

Feature

Bootstrap Enabled And Auto Restart

Disabled

Bootstrap Enabled And Auto Restart

Enabled

Bootstrap Disabled And Auto Restart

Enabled

Bootstrap Enabled And Auto Restart

Disabled

Bootstrap Enabled And Auto Restart

Disabled

Bootstrap And Auto Restart Disabled

Time

Share Enabled

Time

Share Disabled

Table 3-13

Bootstrap Select Switch Settings

for

ROMs Labeled 156A2 and 157 A2

S2-7 S2-8

SI-1

SI-2 SI-3

ON

ON ON

OFF

ON

Table 3-14

Bootstrap/Auto-Restart

Switch Settings

Start Switch

or

Activating

Signal

BOOT

Key

BOOT Key or

AC

OK*

ACOK*

I

ACOK*

AC

OK* or BOOT Key

I

Bootstrap Activated In Run Or Stopped State

Bootstrap Activated In Stopped State Only

Not Used

*Starts if power voltage becomes adequate.

3-24

First

First

ROM

Memory

Address

Address

004

0000

Switches

SI-6

SI-7 SI-8

OFF

OFF

ON

ON

ON

ON

ON

ON OFF

ON

OFF

OFF

ON

OFF

ON

OFF

OFF OFF

S2-1

OFF

ON

SI-4

OFF

ON

SI-5

Page 40

3.4.8 Semiconductor Memory Power Supply

The H763 Semiconductor Memory Power Supply can supply

20 A

at

5.0

V.

It

will

support

only semiconductor

memory

(RAM

and ROM).

The

regulator (08016, shown in Figure 3-17) plugs into a dedicated backplane slot

near the

bottom

of

the chassis. The power supply has battery

backup

for power failures.

The

machine will be

totally supported for approximately

30-40 seconds after

an

ac line failure.

~

nun

n

+5 v ADJUST

CAUTION

This area

of

the

G8016

is

normally covered

with

an

insulating shield. Removal

of

the

shield exposes

the

battery

terminals.

Should

you

accidentally

short

these terminals

with

a ring

or

watchband,

you

W2 could receive a

burn.

POWER

FAILUl)

POWER

FAIL

DOWN

7015-11

Figure 3-17 Semiconductor Memory Regulator Board

(08016)

3-25

Page 41

To

enable control

the

ON-OFF

to the

identified in Figure 3-3.)

All PDP-8f A dc power supply outputs are provided to

drive logic inside the chassis. DIGITAL is not responsible

for the performance

used outside of the chassis.

Refer to Appendix D (Omnibus Loading Chart) to ensure

current rating is not exceeded.

MASTER

of

the

PDP-8/

switch, set

(to the right) position. (The switch

the

NOTE

of

the

CAUTION

A system power from

MASTER/SLAVE

PDP-8f

A

if

any dc power is

switch

is

I n the 8A computers, the

ON

/OFF,

Panel; remove the panel

it

is

3.4.9 Core Memory Power

The core memory power supply supplies the following voltages

The G

board

PANEL

shown in the

+5 V at

-5

+

-15 V at

+20 V at

8018

slot

25

V at 2 A

15 V at

2 A

2 A

4 A

regulator (Figure 3-19) plugs into a dedicated backplane slot near the

is

pictured in Figure 3-5.)

MASTER

A

MASTER/SLAVE

LOCK,

and

to

gain access

position (to the right when viewing the front

Supply Regulator

switch is mounted

BOOT switches. This

to

the

MASTER/SLAVE

board

on

the printed circuit

is attached to the rear

switch. The switch

of

at

the currents specified:

the

is

switch).

bottom

board

that includes the

of

the Limited Function

illustrated in Figure 3-18;

of

the chassis. (The

3-26

Page 42

I

MASTER/SLAVE

SWITCH

Figure3-18 8A

Master jSlave S .

wItch

3-27

08-1787

Page 43

+5V

CIRCUIT

BREAKER

ADJUSTMENT

TOOL MUST

ENTER HERE

FOR

+5V

ADJUSTMENT

POWER

OK

LIGHT

(LIT

WHEN

ALL

DC

VOLTAGES ARE

PRESENT)

ADJUSTMENT

TOOL MUST

ENTER HERE

FOR

+20

VOLT

ADJUSTMENT

+5

V ADJUSTMENT

-5 V FUSE

POWER

POWER

+20 V

FUSE

FAIL

(4A)

(2.5 A)

FAIL

UP

DOWN

Figure 3-19 Core Memory Regulator Board (GSOlS)

3-28

+15 V

FUSE

-15 V FUSE

(2.5 A) (2.5 A)

7404-1

Page 44

3.4.10 Limited Function Panel (Figure 3-20)

The Limited Function Panel has three external switches and three indicator lights as defined below. (The MAS-

TER/SLA

VE switch

is

mounted in the rear

of

the panel for 8A computers.)

7288-3

Figure 3-20 Limited Function Panel

3-29

Page 45

Lights

The

POWER

light, which indicates

that

the

PDP-8/

A is operating

on

ac power.

The

RUN

light, which indicates

that

the

PDP-8/A

RUN

flip-flop is set.

The

BATTERY

CHARGING

light indicates either

that

the power supply

battery

is

being charged

(PDP-

8/

A semiconductor computer)

or

that

both

G8018 regulators

are

operating

properly (8A420, 8A620,

and

8A820 computers). The light

is

present

on

the

8A400, 8A600,

and

8A800 computers

but

is

not

used.

Switches

The

ON-OFF

switch, which

turns

ac power

on

when in the up position. (This switch will

not

turn

battery

power on unless ac

is

present.)

Turn

power

off

before removing

the

power

cord

from the wall receptacle;

otherwise, the

PDP-8/

A will run

on

battery

power

for

as

long as the battery lasts.

On

those systems having a Programmer's Console, the

PANEL

LOCK

switch disables the following

switches:

HLT

ISS, E

NEXT,

E THIS, D

THIS, D NEXT,

LA, LXA,

INIT,

BOOT,

and

RUN.

The down

position activates the

Programmer's Console; the up position panel-locks the console.

The

BOOT switch initiates the

bootstrap

function (if it

is

enabled) on the

KM8-A

Extended

Option

Board

(M 8317).

It

is

normally left

in

the

down

position.

The

BOOT

switch

is

not

affected by

PANEL

LOCK.

3.4.11 KC8-AA Programmer's Console (Figure 3-21)

The

Programmer's

Console

has

7-segment

LED

displays

of

the Extended

Memory

Address (EMA), Memory

Address (MA),

and

the Status Register.

The

console can be located up

to

15

ft

from the

PDP-8f

A. Two BC08R

cables connect the console

to

the M8316 module (JI and 12).

;

~sooo6

N£XT

STATE

MD

LXA

0CDCDCDO

ORUN

OSTATE

OMD

THIS

BUS

STATUS

SR

INIT

CDCDCDCDOI

NEXT

AC

MQ

HLT/SS

RUN

I

00000

)

_....:::

--==--:.~..:::;::._~..;::.l

Oaus

o

STATUS

OSR

08-1121

Figure 3-21 KC8-AA

Programmer's

Console

3-30

Page 46

CHAPTER 4

INSTALLATION AND INITIAL

POWER

TURN-ON

4.1

ENVIRONMENTAL

AND

POWER

REQUIREMENTS

Recommended

operating

conditions for the

PDP-Sf

A are an

ambient

temperature

of

5°

to

50° C

(41

° - 122°

F)

and

a noncondensing relative humidity

of

10-95 percent. Voltage requirements

are

90-132 Vac single

phase

(using approximately 3.2 A),

or

lSO-264 Vac single phase (using

approximately

1.6

A). Line frequency

may

be

49-51 Hz

or

59-61 Hz, depending

on

the

power

transformer

used in

the

power

supply. Check

the

label

at

the

rear

of

the

computer

to

determine the correct voltage

and

frequency.

WARNING

Ensure

that

the ac outlet provides a non-current-carrying

ground.

4.2

INITIAL

POWER

TURN-ON

After unpacking the computer, allow

at

least 30 minutes for

the

machine

to

stabilize

to

ambient

temperature

before applying power. This time should be increased

to 1 hour

or longer when the difference between storage

or

shipping

temperature

and

the

operating

ambient

temperature

exceeds 30° F (17° C).

Install

the

equipment, using the following procedure:

1.

Check switch settings

on

all modules. (See instructions in

Chapter

3.)

2. Ensure

that

the regulator circuit

breaker

is

ON.

(The

breaker

is pictured in Figure 3-4.)

3.

Turn

OFF

the

ON/OFF

switch

on

the

Limited

Function

Panel (Figure 3-20).

4. Ensure

that

all ac power is received from

the

same

branch

circuit

if

the

system

has

more

than

one

power cord.

5.

Plug in the power cord.

If

a power

control

is used, plug

the

power

cord

into the receptacle

marked

UNSWITCHED

AC.

WARNING

Do not touch the computer after plugging

it

in

until

grounding has been checked.

6.

Before touching

the

computer,

check

the

frame

to

ground

voltage

to

ensure

that

less

than

10 Vac

is

present.

7.

Without

touching any metal

part

of

the

PDP-S/A,

turn

ON

the

power

ON/OFF

switch.

4-1

Page 47

8.

Repeat step

6.

In case of difficulty, have an electrician check the socket into which the computer has

been connected. (Refer to Appendix E for power connection information.) If no difficulty

is

encoun-

tered, the computer frame

is

properly grounded, and there

is

no danger in touching it.

9.

Power

is

now applied

to

the PDP-8/A. The fans should be running, and the BATTERY

CHARG-

ING

light should light momentarily

or

stay on. (The light

is

not

used in the H9300 chassis assembly.)

If

none

of

the above occur, check the

MASTER/SLAVE

switch (refer to Paragraph 3.4.8). Turn the

power

OFF

before checking the

MASTER/SLAVE

switch. This switch should be in the MASTER

(to the right) position. Then turn the power ON. If the condition still exists, refer to the basic mainte-

nance section

in

Chapter

9.

10.

Turn the

PDP-8/

A power

switc.h

OFF

and the Teletype

LINE/OFF/LOCAL

switch to the

OFF

position.

11.

Connect the Teletype signal cable to the short cable

(DEC

Part

Number

BCOSM-IF, plugged into J3

of

the M8316) in the PDP-8/A.

The

cable connectors are keyed for proper mating.

12.

Plug the Teletype into the same ac outlet as the

PDP-8/

A.

13.

Turn the power

ON/OFF

switch on the

PDP-8/

A to

ON.

14.

Turn the Teletype

LINE/OFF/LOCAL

switch to LINE. Only the hum

of

the Teletype's running

motor and the

PDP-8/

A fans should be heard.

4-2

Page 48

CHAPTER 5

TESTING

PDP-8/A

WITHOUT PAPER TAPE DIAGNOSTICS

The procedures in this chapter are used to test

the

PDP-8f A computer from the Programmer's Console.

No

paper tape diagnostic programs are required for these tests.

5.1

PROGRAMMER'S

CONSOLE

The

Programmer's Console

is

shown in Figure

3-21

and

is

fully described in the

PDP-8/A

Miniprocessor

Handbook

and the

PDP-8/

A User's Manual. Its use in testing the

PDP-8f A is

described in detail as needed

in

the paragraphs below.

5.2

CENTRAL

PROCESSOR

TEST

ROUTINES

When no

MAINDEC

diagnostics are available, small routines may be keyed into memory and run to check

PDP-8f

A operation. These tests will not completely check

out a PDP-8f A but

will locate the most common

failures. All routines start at address

0200.

If

any failures occur, carefully examine each instruction

of

the rou-

tine.

If

the instructions are correct, switch power

OFF

and check all

of

the module switch settings. (All mem-

ory contents are lost when power

is

switched

OFF

and

the routines must be reloaded.)

If

the routine

is

not

entered properly, reenter the routine and try

to

run it again.

These routines are also useful when

MAINDEC

programs

cannot

be loaded because

of

a hardware problem.

5.3 ENTERING

TEST

ROUTINES

FROM

PROGRAMMER'S

CONSOLE

The following procedure should be used

to

run Routine

1,

the first

PDP-8f

A test.

l.

Press

MD,

then DISP. This wi11let you see what you deposit.

2.

Press,

in

order, 0 0 0 0 LXA. Select memory field

O.

3.

Press,

in

order, a 2 0 0 LA. Start loading instructions

at

address 200.

4. Press,

in

order,

700

1 D

NEXT.

Deposit an instruction.

5.

Press, in order, 2 3

00 D NEXT.

Deposit an instruction.

6.

Press,

in

order, 5 2

OlD

NEXT.

Deposit an instructi9n.

7.

Press, in order, 5 2

00 D NEXT.

Deposit an instruction.

8.

Press, in order, 0 2

00

LA.

Now

get ready to start

at

location 200.

9.

To

see the accumulator (AC), press AC, then DISP.

10.

Press

INIT,

and

RUN.

Start

the program.

5-1

Page 49

All

other

routines should be entered into

memory

using this procedure.

NOTE

If

you make a mistake while you are entering a number,

and you have not pressed D

NEXT,

LA etc., you can

correct the entry by reentering the entire number.

The

number appearing in the

DISP

indicator is the entry

that

the

PDP-8/

A will use.

5.4

CENTRAL

PROCESSOR

TEST

ROUTINES

The

following routines

should

be

used

to

check

the

CPU:

Routine 1 - This

program

will increment

the

AC

slowly so

that

the

user

can

see

that

it

is

working.

The

inter-

nal

numbering

system

of

the

PDP-8/

A does

not

use 8

and

9.

0200

0201

0202

0203

7001

2300

5201

5200

/Increment

the

AC

by I;

start

here.

/Increment

a location

and

skip

if

it is zero.

/Jump

back

l.

/Start

program

over again.

Routine 2 - This routine

should

print a pattern

of

all

printable

characters.

Omit

this routine

if

your

POP-

8/ A is

not equipped with a Teletype

or

similar terminal.

NOTE

Ensure

that

the Teletype is set to

LINE

for routines 2

and 3.

The

following line will

print

out

while this routine is running.

Characters

mayor

may

not

be

printed

after

the

letter Z, depending

on

the column width

of

the terminal. These extra

characters

should

be

disregarded.

Disregard the first line printed.

!"#%$,O* +

,-.j0123456789:;~

=

=?@ABCDEFGHIJKLMNOPQRSTUVWYZ

(Random

Characters)

0200

0201

0202

0203

0204

7001

6046

6041

5202

5200

II

ncrement the A C by I;

start

here.

ITransmit.

/

Am I done

transitting?

IN

0 I am

not

done

transmitting.

IYes I am done.

Jump

back

and

start

over.

Routine 3 - This

routine

will

print

what

is

typed

on

the

terminal

(echo characters).

Type

several sentences, en-

suring

that

the terminal prints

out

what

you type.

Omit

this step

if

your

PDP-81 A

is

not

equipped

with a

terminal.

0200

0201

0202

0203

0204

0205

0206

6031

5200

6036

6046

6041

5204

5200

IHas

a key been pressed?

IN

0,

go

back

and

wait.

I A key was hit.

Read

it.

ITransmit

the

character

to

the

printer.

I

Am I done

printing?

IN

o.

Go

back

one.

IYes I am done.

Let's

go

back

to wait for

another

key.

5-2

Page 50

Routine 4 -

The

following

program

checks

some

of

the

Operate

instructions.

The

program

should

halt

at

loca-

tion

00216

(ADDRS

should read

00217)

with the

AC

cleared

(AC

=

0000)

0200

7240

0201

7001

0202

7640

0203

7402

0204

7120

0205

7010

0206

75iO

0207

7410

0210

7402

0211

7001

0212

7002

0213

1202

0214

7420

0215

7402

0216

7402

IClear

the

AC,

then complement the

AC.

IIncrement

the

AC

by

1.

ISkip

if

AC

= 0, then clear the AC.

IError halt.

Computer

should

not

halt

here.

ISet

the

link to

1.

IRotate

the

AC

right

1.

The

AC

should then equal

4000.

ISkip

if

AC

bit 0 =

o.

ISkip

unconditionally.

IHalt.

Computer

should

not

halt

here.

IIncrement

the

AC

by

1.

IByte swap.

AC

should

equal

0140.

I

Add

7640

to

0140.

ISkip

if

link equals

1.

IHalt on error.

IGood.

Halt

if

AC

= 0000.

Routine 5 -

The

following routine tests the ISZ instruction.

The

program

should

halt

at

location

00207

(ADDRS

should read

00210)

with the

AC

cleared (AC =

0000).

To

read

the AC, depress

AC

and

then

DISP.

0200

0201

0202

0203

0204

0205

0206

0207

7300

3300

7001

2300

5202

7440

7402

7402

IClear

the

AC

and

link.

IStore 0 in location

300.

IIndex

the AC.

jlndex

location

300.

I

Jump

back

and

do

again.

IDone. Check

if

AC

=

0000.

IError

(AC

and

location

300

should

be zero).

IGood. Halt.

Routine 6 - This routine tests the

JMS

instructions.

It

should

halt with

ADDRS

00215,

with the

AC

cleared

(AC

=

0000).

To

read the AC, press

AC,

then

DISP.

0200

0201

0202

0203

0204

0205

0206

0207

0210

0211

0212

0213

0214

0215

7300

3300

3204

4204

0000

1204

7041

1215

7440

7402

2300

5202

7402

0204

IClear

the

AC

and

link.

IZero pass counter.

IZero entry.

IJMS

to

subroutine.

IReturn address written here.

IGet

return

address.

IComplement

and

index the AC.

I

Add

to

known

good

return address.

ISkip

on 0 AC.

IError halt.

IIncrement

pass counter.

IDo

again.

IGood. Halt.

IConstant.

5-3

Page 51

Routine 7 - This routine tests the

Jump

instructions.

The

program

should halt

at

location 00214.

(ADDRS

should read 00215.) Run this test twice.

0200

0201

0202

0203

0204

0205

0206

0207

0210

0211

0212

0213

0214

5210

7402

5206

7402

5212

7402

5204

7402

5202

7402

2300

5200

7402

/Jump

210.

/Error

halt.

/Jump

206.

/Error

halt.

/Jump

212.

/Error

halt.

/Jump

204.

/Error

halt.

/Jump

202.

/Error

halt.

/Loop

to do this program 4096 times.

/Start

program

over again.

/Good.

Halt

after 4096 passes.

5-4

Page 52

CHAPTER 6

LOADING THE

RIM

AND

BINARY LOADERS

Programs

in binary

format

may

be

used in machines with

4K

or

more

of

read/write

memory.

The

RIM

loader

must

be

used to

load

the

binary

loader.

The

binary

loader

is

then

used

to

load a program

in

binary

format.

The

RIM

and

binary

loaders reside in

the

highest 1 K

of a 4K

memory.

Machines

with less

than

4K

of

mem-

ory require

the

RIM

loader

to

be

loaded

at

addresses in

the

lowest 1 K

of

memory. Use

of

the

binary

loader

on

machines with less

than

4K

of

read/write

memory

is

not

recommended

because

of

the

length

of

the

binary

loader

routine.

Each

test

procedure

will tell you where

to

load

the

RIM

loader.

6.1

LOADING

RIM

LOADER

The

RIM

loader

is

a 17-instruction

program

needed

to

load

the

binary

loader

and

other

RIM

formatted

tapes.

There

are

two

methods

of

loading

the

RIM

loader.

The

first

method

consists

of

manually

loading each instruc-

tion

through

the

Programmer's

Console

keys as described in

the

next few

paragraphs.

The

second

method

consists

of

using the

bootstrap

option,

if

there

is

4K

or

more

of

read/write

memory

and

the

KMS-A

Extended

Option

Board

(MS317)

is

in

the

computer.

If

using

the

second

method,

go

directly

to

Paragraph

6.3.

Enter

the

RIM

loader

through

the

Programmer's

Console

keys as follows.

Press keys, in

order,

from left

to

right as they

appear

in

the

following steps.

1.

MD

2.

0000

3.

XXXX

4. 6032

5.

6031

6. 5357

7.

6036

S.

7106

9.

7006

10.

7510

11.

5357

12.

7006

13.

6031

14. 5367

15.

6034

16.

7420

17. 3776

18. 3376

19.

5356

DISP

LXA

LA

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

DNEXT

/Enables

memory

data

to

the

readout

dislay.

/Sets

instruction

and

data

field

to

O.

/