Page 1

Page 2

.

~nmnomn

0

000

processor

handbook

digtal equipment corporation

Page 3

Copyright©

The

material

purposes and is

Digital

sponsibility

this

handbook.

Digital

Equipment

1975

in

this

Equipment

for

any

The

following

Corporation,

by Digital

manual

subject

to

Corporation

errors

are

Equipment

is

for

change

assumes

which

trademarks

Maynard, Massachusetts:

Corporation

informational

without

no re-

may

appear

of

notice.

in

DEC

FLIP CHIP

DIGITAL

LSl-11

PDP

FOCAL

DEC

US

ii

Page 4

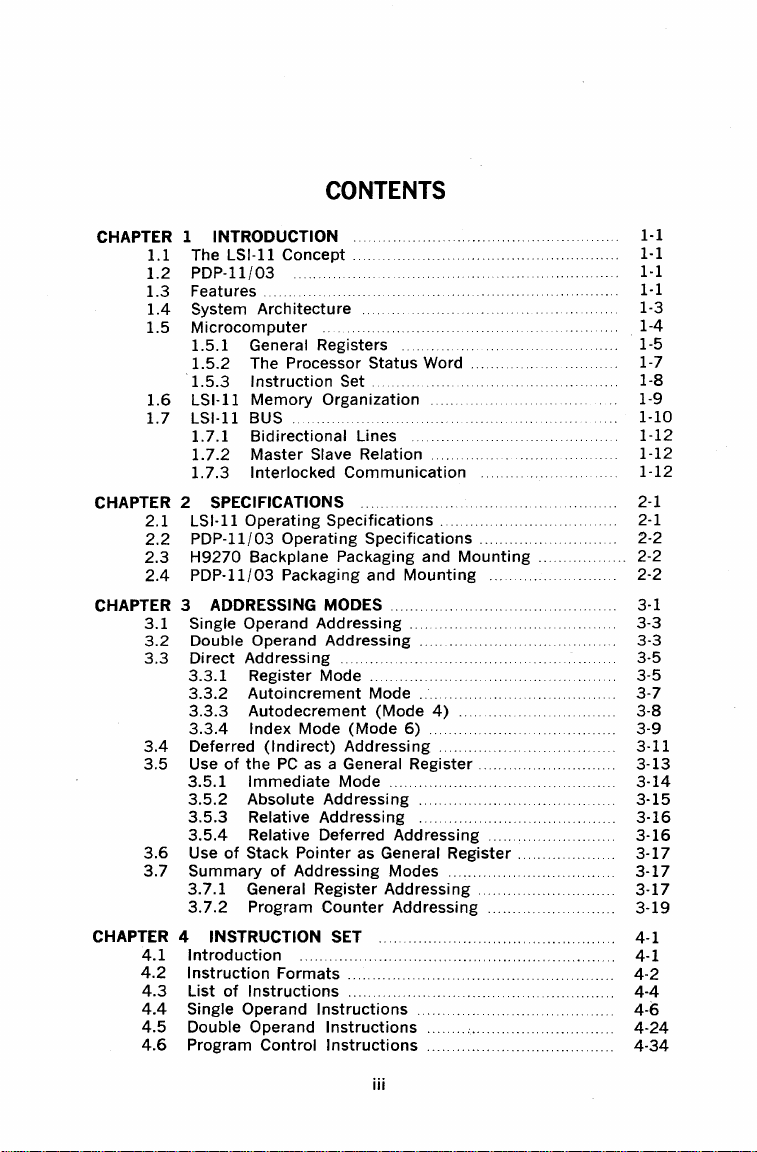

CONTENTS

CHAPTER

CHAPTER 2 SPECIFICATIONS

CHAPTER 3 ADDRESSING MODES ....

CHAPTER 4

1 INTRODUCTION

The LSl-11 Concept .

1.1

1.2

PDP-11/03

Features .

1.3

System

1.4

Microcomputer

1.5

1.5.1 General Registers

1.5.2

i.5.3

·

LSl-11

1.6

LSl-11 BUS

1.7

1.7.1

1. 7

1.7.3

LSl-11

2.1

2.2

PDP-11/03

2.3

H9270

2.4

PDP-11/03

Single Operand Addressing ....

3.1

Double Operand

3.2

Direct

3.3

3.3.1

3.3.2

3.3.3

3.3.4

Deferred

3.4

3.5

Use

3.5.1

3.5.2

3.5.3

3.5.4

3.6

Use

3.7

Summary

3.7.1

3.7.2

4.1

Introduction

4.2

Instruction

4.3

List

4.4

Single Operand

4.5

Double Operand

4.6

Program

Architecture

The Processor

Instruction

Memory

Bidirectional

.2

Master

Interlocked

Operating

Backplane Packaging and

Addressing

Register Mode ....

Autoincrement

Autodecrement

Index Mode

of

the

Immediate

Absolute

Relative Addressing .

Relative Deferred Addressing

of

Stack

General Register

Program

INSTRUCTION SET

of

Instructions

Slave Relation

Operating

Packaging and

(Indirect)

PC

as a General Register .

Pointer

of

Addressing Modes

Formats

Instructions

Control

Status

Set .

Organization

Lines

Communication

Specifications

Addressing

Addressing ..... .

Counter

Instructions

Instructions

..........

Specifications ... .

Mode .

(Mode

(Mode

Addressing

Mode .....

as General Register .

Addressing

........ .

..

.

Word .....

.

.................

Mounting

Mounting

.

4)

6)

.

...............

Addressing

............

.

..

.....

.

................. .

.

1-1

1-1

1-1

1-1

1-3

1-4

1-5

1-7

1-8

1-9

1-10

1-12

1-12

1-12

2-1

2-1

2-2

2-2

2-2

3-1

3-3

3-3

3-5

3-5

3-7

3-8

3-9

3-11

3-13

3-14

3-15

3-16

3-16

3-17

3-17

3-17

3-19

4-1

4-1

4-2

4-4

4-6

4-24

4-34

iii

Page 5

CHAPTER 5 PROGRAMMING TECHNIQUES

5.1 The Stack ·

5.2 Subroutine Linkage ....

5.2.1 Subroutine

5.2.2

Argument

5.2.3

Subroutine

LSl-11 Set Subroutine Calls

5.2.4

5.3

Interrupts

5.3.1· General Principles .

5.3.2

5.4

5.5 Device Registers

CHAPTER 6 EXTENDED ARITHMETIC OPTION

6.1 General ......... .

6.2

6.3

CHAPTER 7

7-1 General

7.2

7.3 CDT/Console Microcode

APPENDIX A

APPENDIX B

APPENDIX C

APPENDIX D

APPENDIX E

Nesting

Programming

Fixed Point

Floating Point

CONSOLE OPERATION

Interfacing

Memory

Instruction

LSl·ll

Instruction

Summary

Calls

Transmission

Return ...................... .

. . . . .

..

. . . .

..

. . . . .............. .

Peripherals

Arithmetic

Arithmetic

Map

PDP-11

of

............

....

Timing

Family

Index

LSl-11

(EIS)

.................

(FIS) .

.

of

Instructions

Computers

..

5·1

5-1

5.5

5.5

5-6

5.9

5.9

5·10

5-10

5-11

5·13

5-14

..

.

6·1

6·1

6-1

6-6

7·1

7-1

7-1

7-2

A·l

B·l

....... .

.....

C·l

D·l

E·l

iv

Page 6

The LSl-11

of

computer

microcomputer

fore,

small

sion

systems

(PDPll/03)

This

floating

Since

to

optimize

hardware

process. The

tensively

The

effort

sive

design

nel MOS

requires

have

mils x 200

carried

DECsystem-10.

system

levels

logic

Transfer

1/0

equipment).

All

the

lieve,

quality

them.

(PDPll/03)

the

us,er can

for

computer

of

the

LSl-11,

tool

includes

instruction

the

main

total

have been

simulated

of

engineering

semiconductor

many

approximately

mils

out

for

for

computer-aided-design,

of

simulation

(Gate Level), and

Level). Finally,

preparation

is

necessary

computers

systems.

package

truly

application.

the

at

lower

maintains

programs

set

design

system

initial

and

bringing

circuits.

50,000

(0.16

the

basic

The

in

to

at

is

the

It

offers

that

crosses

add

computer

PDPll/03,

cost

without

traditional

up

to

(FIS)

and

objective

performance,

carefully

PDP-11 was

benchmarked.

the

LSl-11

ranging

densities

In

fact,

active

square

circuits

basic

logic

were

carried

the

behavior

complete

the

design

support

the

our

lowest

smallest

the

Yet

64K

extended

of

considered

specified

to

over

the

inches).

that

masks

main

cost

member

user

minicomputer

traditional

power

for

our

offers a completely

are

elements

out

and

traditional

sacrificing

PDP-11

bytes

and

instruction

the

PDP-11

the

interaction

at

in

the

marketplace

many

disciplines.

state-of-the-art,

4-chips

systems

Extensive

comprise

were

which

on a

of

the

production

goal:

by

which

that

in an area

is

DECsystem-10

of

the

PDP-11

performance

industry

in

systems

performance.

architectural

the

family

every

the

comprise

those

laid

based on a PDP-11.

microprograms

were

providing

you,

barriers.

previously

user,

the

integrated

use

ISP

circuit

out

simulated

of

compatibility.

of

the

set

(EIS).

has

always

of

software

step

in

language

has

required

The basic N-chan-

since

the

the

of

about

simulation

elements-using

using

an

to

computers,

high

our

performance

users, can

boxed ver-

The

(optional)

the

processor

check

(Register-

(including

family

in a

There-

too

smaller

LSl-11

been

and

design

and

ex-

exten-

PDP-11

4 x

200

was

Applicon

Two

the

we

be-

apply

a

fL~

C.

Gordon

Vice President,

Digital

v

Bell

Equipment

Engineering

Corporation

Page 7

vi

Page 8

CHAPTER

1

INTRODUCTION

1.1 THE

DIGITAL

ily

of

a

family

vices. Today,

computer

the

The LSl-11 is a

of a minicomputer.

almost

1.2

The

is designed as an

LSl-11

mounting

description

LSl·ll

introduced

PDP-11

LSl-11.

Computer

of

processors,

the

products

16-bit

any

instrumentation,

PDP-11/03

PDP-11/03, a 3lh

microcomputer, a modular

box is designed

of

PDP-11/03

1.3 FEATURES

The LSl-11 has

400

Plus

•

• Extensive

than

More

set.

This

user

to

ture

from

tions,

velopment

linkers, editors,

higher

The processor

oxide

elements

The

latter

struction

(ODT),

processor

bus, a

clock

other

plus all

10-inch

the

Instruction

400

instruction

take advantage

the

used

to

programs

level languages.

Compute

semiconductor

as well as

are

programmed

set,

along

operator

also

4096-word

input,

priority

features

to

of

the

above-mentioned features, are

printed

CONCEPT

the

first

PDP-11 Processor in 1970. Since

products

but a family

PDP-11

on

the

microcomputer

Due

to

"H x 19"W x 13%

off-the-shelf

following

Set

instructions

set

standard

explicitly

as in

loaders,

Power and Small Processor Size

module

contains a 16-bit

circuit

is

(MOS) chips,

two

with

interfacing,

MOS random-access

interrupt

provide

board.

has been

family

market,

its

size and

data processing,

to

mount

specifications,

features:

make

(also used by

of

standard

software

access

utility

built

microcoded

to

routines

stand-alone

of

is

the

with

with

microcomputer

power supply, and a

in a

up

PDP-11 software. The

is

the

processor

the

PDP-11

packages,

around a set

emulate

for

and

boot-strap

buffered

control

peripherals, software, and serbroadest

one

unique

"D

refer

the

the

the

which

read-only

the

on-line

logic, power-fail/

operation.

constantly

of

the

or

boxed version

standard

LSl-11

PDP-11/

addition

family

include

powerful

parallel

memory

evolving-not

family

the

latest

additions

speed and

capabilities,

controller

system.

to

operating

of

contained

It

mounting

19"

Chapter

's

extensive

35,40)

of

two

status

word (PSW),

include

four

N-channel

control

memories

PDP-11/35,40

debugging

loader capability. The

input/

(RAM), a real-time

auto

The

entire

then, a fam·

of

instruction

it

configuration.

of

consists

cabinet. For a

just

compatible

being

can

the

set

fit

into

LSl-11,

of

an

box. The

2.

instruction

permits

only

new

assemblers,

systems, and

(microms).

techniques

output

restart, and

on one 8.5-by-

the

depar-

instruc-

De-

metal

and

data

in-

(I/

0)

processor,

1-1

Page 9

•

Modularity

The processor, memory, device interfaces, backplane, and interconnecting

the

tailoring

• Serial and Parallel

Serial and

cessor bus

to

prototype

interfaces.

• Choice

Memory

than

the

ory, a 1024-word

automatically

memory

512-word

•

16-Bit

Direct

• Word

Very

swap,

• Asynchronous Operation

System

with

software changes.

• Stack Processing

Hardware

structured

•

Direct

Inherent

vices.

• 8 General-Purpose Registers

For

• Priority-Structured

Daisy-chained

• Vectored

Fast

• Single

Powerful and convenient

• Power-Fail/ Auto Restart

Whenever

power loss, a microcoded power-fail sequence is

is restored,

Four

hardware are all

type

and size

to

meet

specific

of

memory,

modular

application

in design. Module selection, such as

and device interfaces, enable

requirements.

custom

1/0 Modules

parallel

peripherals when and

processor board. Included are a non-volatile 4096-word core mem-

accumulators

with

systems

of

Memory

modules are offered

is available

(PROM/ ROM)

increments

Word (Two

addressing

or

Byte Processing

efficient

or

mask.

components

faster

devices means

sequential

data, subroutines, and

Memory

in

Interrupts

interrupt

and Double Operand

DC

options

1/0

modules

external devices. These modules

without

with

the

static

refreshed by central processor microcode, and read·only

handling

Access (OMA)

the

grant

response

power sequencing signals

the

are available

RAM, a

with

(2048

8-Bit

Bytes)

of

32K

16-bit

of

run

at

memory

architecture

or

address generation.

I/

0 System

signals provide a

without

set

processor can

are available

if

required, and also

penalizing

4096-word

capacity

words in 256-word

8-bit

their

faster

is

Instructions

of

for

power up sequencing.

later

for

applications

MOS random-access

4096-word

to a maximum

words.

characters

highest

operation

manipulation

interrupts.

direct

memory

priority-structured

device polling.

programming

automatically

possible speed;

for

interfacing

simplify

facilitate

development

requinng

dynamic

without

without

indicate

RAM

of

increments).

the

other

makes

it

access

instructions.

an

initiated.

return

to

the

connection

assembly

of

customized

more

storage

memory

which can be

4096

words in

need

to

replacement

hardware

easy

to

for

multiple

1/0 system.

impending

When power

the

run state.

pro-

of

on

rotate,

or

handle

de-

AC

J-2

Page 10

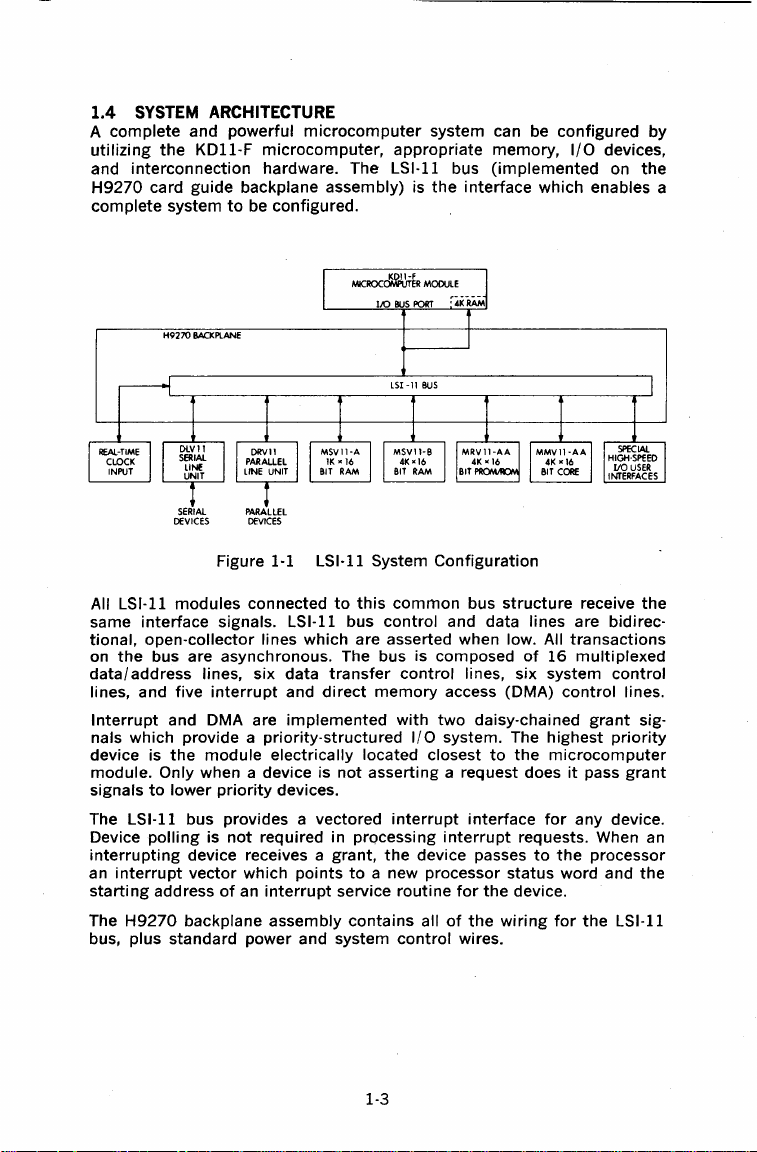

1.4

SYSTEM

A

complete

utilizing

interconnection

and

H9270

card

complete

ARCHITECTURE

and

the

KDll-F

guide

system

H9270

BACKPLANE

powerful

microcomputer,

hardware.

backplane

to

be configured.

microcomputer

appropriate

The

LSl-11 bus

assembly)

LSI

·11

system can be

memory,

(implemented

is

the

interface

BUS

configured

1/0 devices,

which

enables a

on

by

the

SERIAL PARALLEL

DEVICES

All LSl-11

same

tional,

on

data/

modules

interface

open-collector

the

bus are asynchronous. The bus is composed

address lines,

lines, and five

Interrupt

nals

device is

module.

signals

The

Device

interrupting

an

starting

The

bus, plus

and

provide a priority-structured

which

the

Only when a device is

to

lower

LSl-11

bus

polling

device receives a

interrupt

vector

address

H9270

backplane

standard

DEVICES

MSVll·A

11( • 16

SIT RAM

MSV11·8

BIT

Figure 1-1 LSl-11 System

connected

signals. LSl-11 bus

lines

six

interrupt

DMA

are

module

electrically

priority

provides a vectored

is

not

required in processing

which

of

an

interrupt

assembly

power

to

which

are asserted when low. All

data

transfer

and

direct

implemented

not

devices.

grant,

points

to

service

contains

and system

this

common

control

memory

located closest

asserting

interrupt

the

a new processor

41(•16

RAM

MMVll·AA

41(

BIT

Configuration

bus

structure

and data lines are bidirec·

of

control

with

1/0

lines, six system

access

two

daisy-chained

system. The

(DMA)

to

16

highest

the

microcomputer

a request does

interface

interrupt

device passes

for

requests. When an

to

status

routine

for

the

device.

all

of

the

control

wiring

wires.

SPECIAL

HIGH·SPfEO

•16

UO

CORE

INTERFACES

receive

transactions

multiplexed

control

control

grant

priority

it

pass

any

device.

the

processor

word

and

for

the

LSl-11

USER

the

lines.

sig-

grant

the

1-3

Page 11

1.5 MICROCOMPUTER

The

microcomputer

of

location

logic

speed, general-purpose registers which can be used as

address pointers,

processor does both single and

both

directly

cessor

The

The

(microcode

the

operations

16-bit

word and

between

registers.

microcomputer

four

chips

read-only

connected

LSl-11

and

index

1/0

processor is

are

the

memory)

bus

instruction

8-bit

devices and

to

for

peripherals

registers, and

double

byte data. The bus

implemented

control

chip,

chips.

the

LSl-11 bus

decoding.

other

operand

memory

the

and

performs

It

contains

specialized

addressing

without

with

data

chip, and

controls

permits

disturbing

four

Control Chip

This

chip

and

•

• Location

• Return Register

• Data

•

provides

control

Programmable

anism

for

tions.

accesses

Transfer

data/

address port.

Interrupt

cessor

and

the

for

generating

Counter

are

Logic-Provides

four

microinstruction

the

data access port.

Translation

(LC)-Stores

being made.

(RR)-Used

Control

external flags

It

Array

microinstruction

Logic-Provides

control

(PTA)-Provides a decoding

the

address in

to

hold a microsubroutine

over

for

the

address sequence,

contains

addresses

control

three

system.

the

the

microm

and

internal

following

from

timing

flags

Data Chip

The data

microinstructions.

• Register

quired

Arithmetic

•

operations

•

Condition

section.

•

Data/

chip

File-Provides

data.

and Logic

necessary

Flags

Address

incorporates

It

offers

Unit

for

Logic-Monitors

Port-Provides

the

paths, registers, and logic

the

following

multiple

(ALU)-Performs

instruction

registers

the

access

features:

for

execution.

status

to

the

storage

the

of

the

data

arithmetic

result

address lines.

Microm Chips

The

microm

basic

nique)

An

optional

cessor, via a

instruction

chips provide storage

PDP-11/35,40

firmware,

fifth

socket

set

resident

chip

to

include

of

instruction

ASCII/ console routine, and

(third

available on

microm)

fixed

the

set,

resident

the

microcomputer

and

floating

microcode

ODT

(octal

can be added

point

module,

arithmetic

for

bootstrap.

to

the

time

arithmetic

multiple

accumulators,

functions.

and

handles

data

transfers

the

LSI

40-pin

two

microm

for

the

microm

features:

macroinstruc-

from

return

address.

signals

for

the

to

execute

of

frequently

and logic

from

the

emulation

debugging

the

LSl-11 pro-

to

extend

instructions.

al-

and

high-

The

pro-

chips.

mech-

which

for

pro-

re-

ALU

of

the

tech-

the

1-4

Page 12

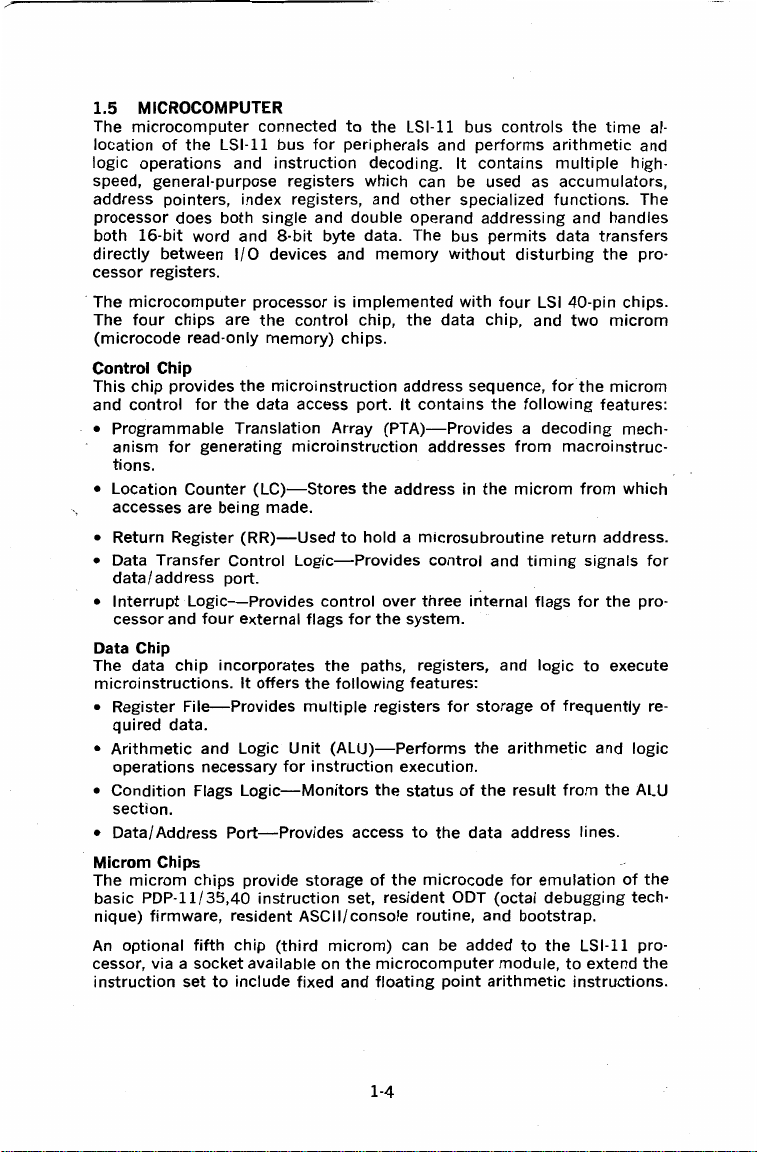

1.5.1 General Registers

LSl-11 central processor

The

pose registers

can serve as

decrement

Arithmetic

one

memory

locations

tration

identifies

that

can

accumulators, index registers,

registers,

or

operations can be

location

or

a device register and a general register. The

the

or

eight

module

contains

perform a variety

as

stack

pointers

from

one general register

device register

16-bit

general registers

eight

of

functions.

autoincrement

for

temporary

to

another,

16-bit

These registers

registers, auto-

storage

to

or

between

following

RO

through

general-pur-

of

another,

memory

R7.

data.

from

illus-

GENERAL

REGISTERS

STACK

PROGAAM

Figure 1-2 General Register

Registers R6 and

as

the

Stack Pointer (SP) and

entry

in

the

Counter (PC) and contains

It

cuted.

is

accumulator.

not

require bus cycles (except

peripheral device data

tion

time.

faster

Thus, general registers used

execution times. The bus cycles required

R7

in

stack. Register

normally

Register

used

operations

transfers

the

LSl-11 are dedicated. R6

contains

R7

the

address

for

addressing purposes

for

do

references are described below.

Bus Cycles

The bus cycles

DATI Data word

DATIO

DATIOB

DATO

DATOB

(with

respect

transfer

Data word

transfer

lowed by word

Data word

transfer

lowed by byte

Data word

Data byte

transfer

transfer

to

the

transfer

transfer

RO

Rl

R2

RJ

R•

RS

R6

POINTER

R7

COUNTER

It

SP)

ltPC)

Identification

the

serves as

are internal

location (address)

of

the

instruction

the

processor's Program

next

instruction

to

the

fetch);

require bus cycles and

for

processor operations result in

for

processor) are:

in

Equivalent

ti

on

in, fol- Equivalent

out

Write

in, fol- Equivalent

out

Write

out

out

Equivalent

ti

on

Equivalent

ti

on

normally

of

to

only

and

not

processor and

all

memory

longer

memory

and device

to

Read opera-

Read/

to

Read/

to

Write opera-

to

Write

to

serves

the

last

be exe-

as an

and

execu-

Modify

Modify

opera-

do

1-5

Page 13

Every processor

instruction

requires one

or

operation required is a DATI, which fetches an

tion

addressed by

referenced in

required

for

however, one

Note

the

which

processor

distinction

may

instructions;

cycles since

the

memory

instruction

or

more

change

these

operations

Program Counter (R7).

or

in an

1/0

execution.

additional

between

the

state

DMA

operations

device, no

If

memory

bus cycles are required.

interrupts

of

the

processor, can

do

not

change

and DMA operations:

can

occur

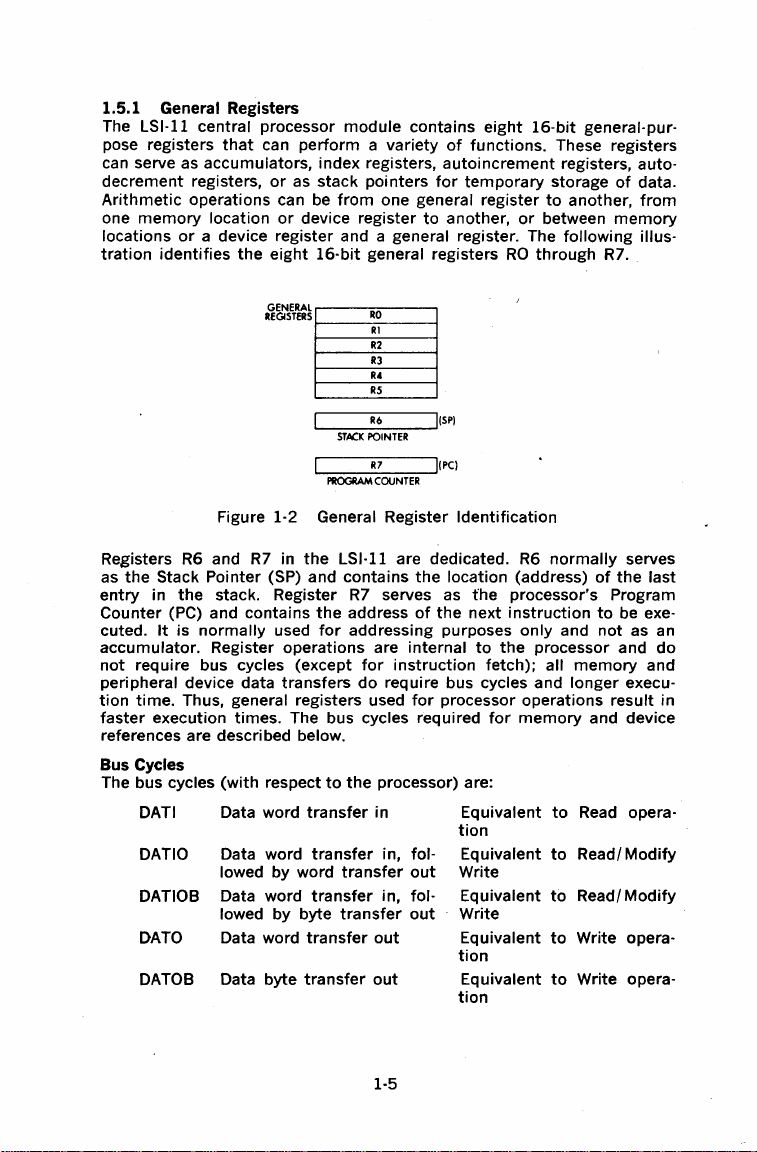

Addressing Memory and Peripherals

The

maximum

memory.

addressed in

(28K-32K)

dressing. However,

space

to

An

LSl-ll

direct

LSl-ll's

precisely

are

usually

1/0; he can

word is

address space

memory

locations

the

same manner. The

reserved by convention

the

user does

implement

divided

only

into

a high byte and a low byte as shown

of

the

LSl-11 is

and peripheral device registers are

not

need

what

he needs.

below.

more

bus cycles. The

instruction

If

no

additional

or

a device is referenced,

further

bus cycles are

from

operands are

Interrupts,

occur

32K

only

individual

of

the

16-bit

4096

the

processor.

addresses

between

the

state

upper

for

peripheral device ad-

to

dedicate

the

loca-

between

words

entire

first

bus

of

4K

15

: HIGH:

BYTE

Figure 1-3 High and Low Byte

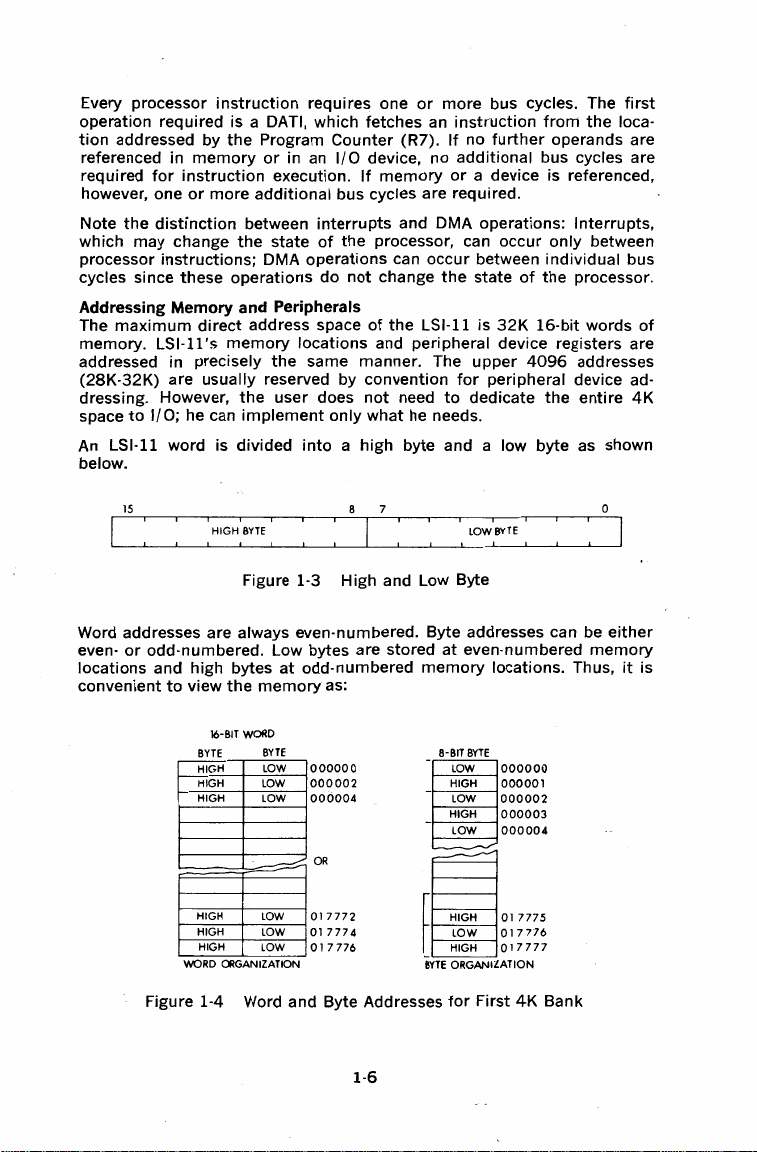

Word addresses are

even-

or

odd-numbered. Low bytes are stored

always even-numbered. Byte addresses can be

locations and high bytes

convenient

to

view

the

16-BIT

WORD

BYTE

HIGH LOW

HIGH LOW

HIGH LOW

HIGH

HIGH

HIGH

WORD ORGANIZATION

memory

Figure 1-4 Word and Byte Addresses

:

at

odd-numbered

BYTE

000000

000002

000004

___.-"'.'.

OR

01

LOW

LOW

01

017776

LOW

as:

7772

7774

1-6

7

1

LOW0PifTE:

I I

at

even-numbered

memory

8-BIT

BYTE

LOW

HIGH

LOW

HIGH

LOW

HIGH

LOW

HIGH

t

BYTE

ORGANIZATION

for

First

0

memory

locations. Thus,

000000

000001

000002

000003

000004

01

7775

017776

017777

4K

Bank

either

it

is

Page 14

Certain

and

trap

3768 are

Several

itiated)

1.5.2

memory

of

traps.

The Processor

handling

usually

these

locations

and peripheral device registers. Addresses

reserved

are reserved in

have been reserved by

for

trap

and device

particular

Status

Word (PSW)

convention

interrupt

for

system

for

vector

(processor

interrupt

from O to

locations.

in·

lS

[~=~=~~~~---~~=~=-~---~~~Rl-ORTY~:

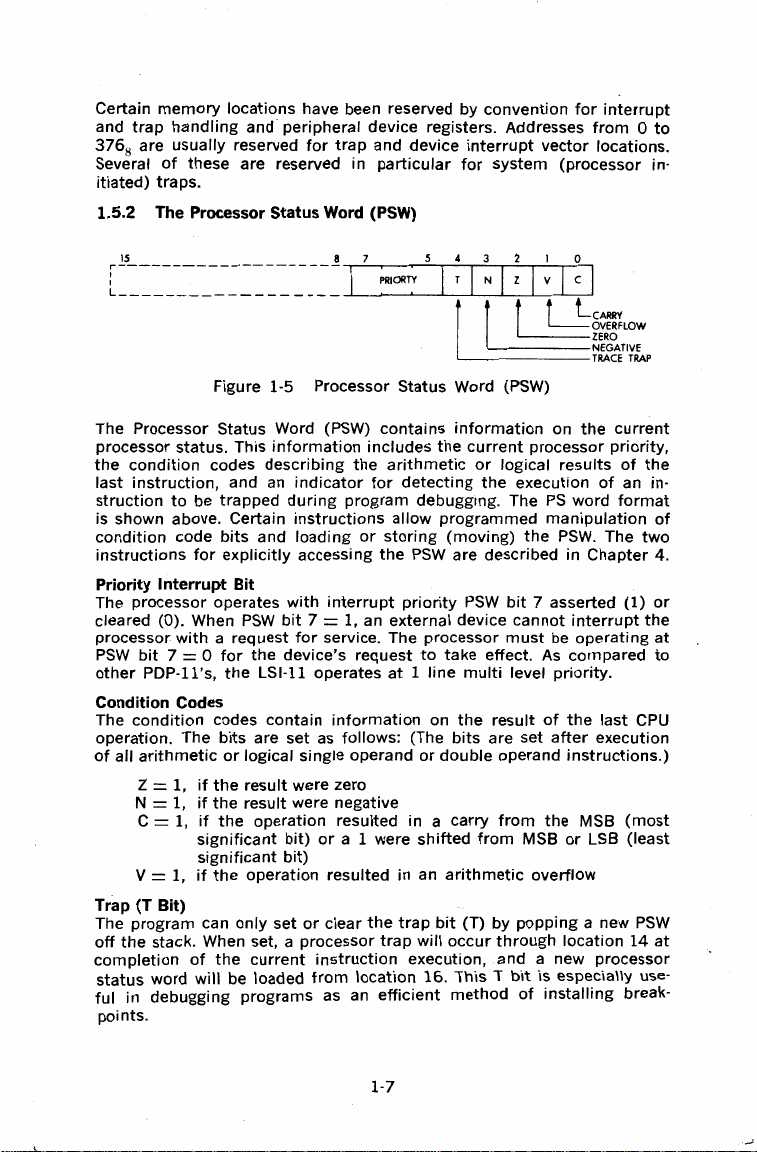

Figure 1-5 Processor Status Word (PSW)

The Processor Status Word (PSW)

processor status. This

the

condition

last

instruction,

struction

is shown above. Certain

condition

instructions

Priority

The processor operates

cleared

processor

PSW

bit

other

PDP-ll's,

Condition

condition

The

operation. The

of

all

arithmetic

Z = 1,

N

C

V = 1,

Trap

(T

The

program

off

the

completion

status

ful

in

debugging

points.

codes

to

be

code

for

Interrupt

(0).

When

with

7 = 0

Codes

if

= 1,

if

=

l,

if

significant

significant

if

Bit)

can

stack. When set, a processor

of

word

will

information

describing

and an

trapped

bits

explicitly

a request

for

the

codes

bits

or

the

the

the

the

the

be loaded

indicator

during

program

instructions

and

loading

accessing

Bit

with

PSW

the

LSl-11

contain

are set as follows: (The

logical single operand

result

result

operation

operation

only

current

programs

interrupt

bit

7 = 1, an external device

for

service. The processor

device's

operates

information

were zero

were negative

resulted in a

bit)

or

a 1 were

bit)

resulted

set

or

clear

instruction

from

as an

the

or

request

location

~r~l_N_l_z~l

)

1

~-

-----NEGATIVE

'---------TRACE

contains

includes

arithmetic

for

allow

storing

the

at 1 line

the

trap

efficient

information

the

current

detecting

PSW

priority

in

trap

execution,

or

debugging. The

to

or

shifted

an

will

the

programmed

(moving)

are described in

PSW

take

effect.

multi

on

the

bits

double

carry

from

arithmetic

bit

(T)

occur

16.

This

method

logical

bit

cannot

must

level

result

are set

operand

from

by

through

and

T

b"1t

0

_v

~I

~c

I

UJ:~'°"

TRAP

on

the

processor

execution

PS

manipulation

the

7 asserted

be

As

priority.

of

after

the

MSB

overflow

popping

a new processor

is

of

installing

current

priority,

results

PSW.

especia\ly use-

of

the

of

an in·

word

format

The

two

Chapter

(1)

interrupt

operating

compared

the

instructions.)

MSB

or

a new

location

last

CPU

execution

(most

LSB

(least

PSW

14

break-

the

of

4.

or

at

to

at

1-7

Page 15

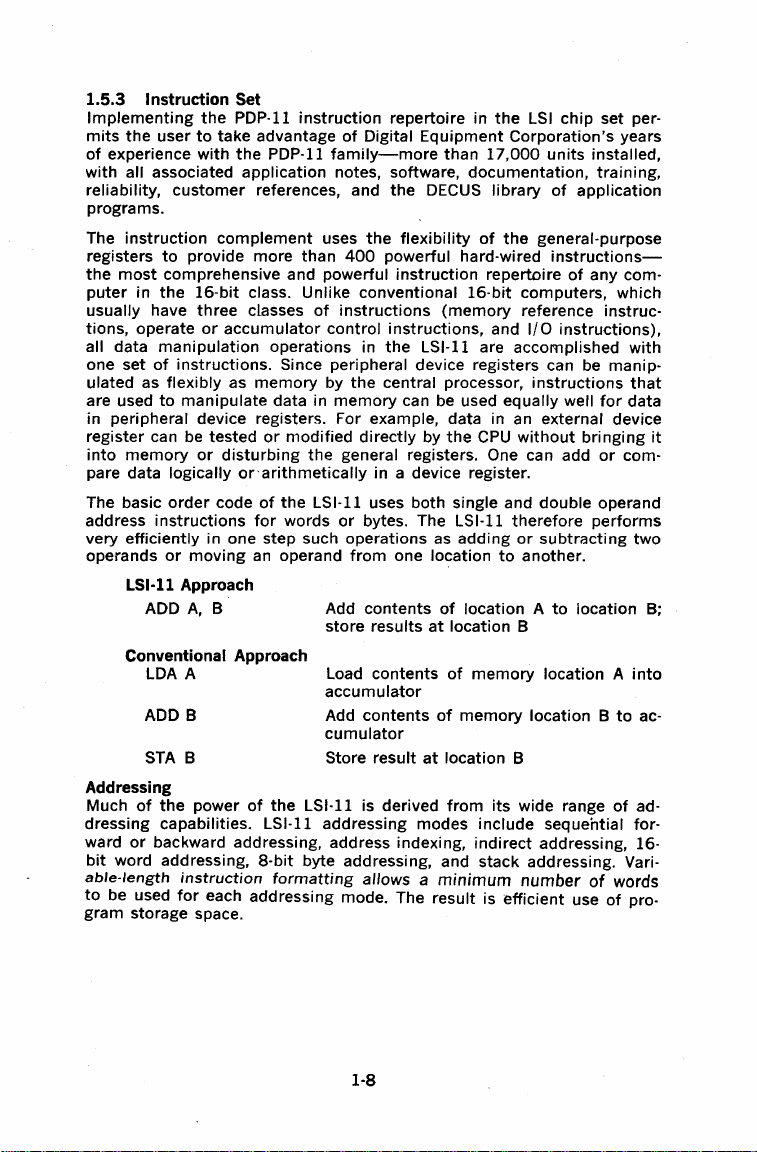

1.5.3

Instruction

Implementing

mits

the

of

with all associated application notes, software,

reliability,

programs.

The

registers

the

puter

usually have

tions, operate

all data

one

ulated

are used

in

register can be tested

into

pare data logically

The basic

address

very efficiently in one step such operations as

operands

user

experience

customer

instruction

to

most

comprehensive and powerful

in

the

manipulation

set

of

as

flexibly

to

peripheral device registers. For example, data in an external device

memory

order

instructions

or

LSl-11 Approach

ADD

Conventional Approach

LOA

ADD B

STA B

Addressing

Much

of

dressing capabilities. LSl-11 addressing modes

ward

bit

able-length

to

gram

the

or

backward addressing, address indexing,

word addressing,

be used

storage space.

Set

the

PDP-11

to

take

with

the

complement

provide

16-bit

three

or

accumulator

instructions.

as

manipulate

or

disturbing

or·arithmetically

code

moving

A,

B

A

power

instruction

for

each addressing mode. The

instruction

advantage

PDP-11

references, and

more

class. Unlike conventional

classes

operations in

memory

data in

or

of

for

an

operand

of

the

8-bit

formatting

of

family-more

uses

than

400

of

instructions

control

Since peripheral device registers can be manip-

by

the

memory

modified

the

general registers. One can add

the

LSl-11 uses both single and

words

or

from

Add

store results

Load

accumulator

Add

cumulator

Store result

LSl-11 is derived

byte addressing, and stack addressing. Vari-

repertoire in

Digital

Equipment

than

17,000

the

the

flexibility

powerful hard-wired

instruction

instructions,

the

central processor,

can be used equally well

directly

in a device register.

bytes. The LSl-11

one location

contents

contents

contents

allows a

documentation,

DECUS

LSl-11 are accomplished

by

at

at

library

of

repertoire

16-bit

(memory

and 1/0

the

CPU

adding

of

location A

location B

of

memory

of

memory

location B

from

its

include

indirect

minimum

result

is efficient use

the

LSI

chip

Corporation's

units

installed,

training,

of

application

the

general-purpose

instructions-

of

computers, which

reference instruc-

without

therefore

or

to

another.

wide range

number

any com-

instructions),

instructions

bringing

or

double

operand

performs

subtracting

to

location

location A

location B

sequential for-

addressing, 16-

of

set per-

years

with

that

for

data

com-

two

into

to

ac-

of

ad-

words

of

pro-

it

B;

1-8

Page 16

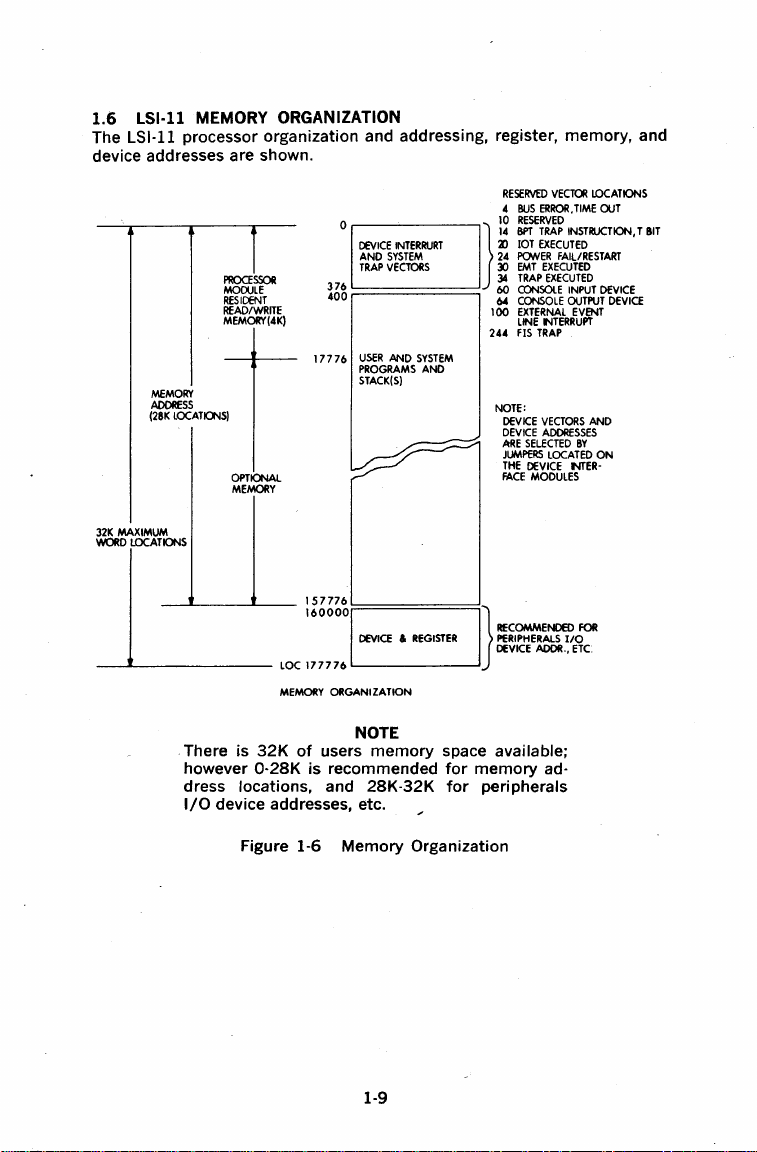

1.6

LSl·ll

MEMORY

ORGANIZATION

The LSl-11 processor organization and addressing, register, memory, and

device addresses are shown.

RESERVED

VECTOR

ERROR,

TIME

TRAP

INSTRUCTION, T BIT

EXECUTED

FAIL/RESTART

EXECUTED

EXECUTED

~~~D~

EVENT

NTERRUPT

TRAP

VECTORS

AND

ADDRESSES

BY

LOCATED

NTER-

ADDR.,

ETC:

LOCATIONS

OUT

1

~1~

ON

32K

MAXIMUM

WORD

LOCATIONS

----''---------

PROCESSOR

MODULE

RESICfNT

READ/WRITE

MEMORY(4K)

~MORY

ADORE

SS

(28K

LOCATIOllS)

OPTIONAL

MEMORY

_......_

___

4

O

~--------.

DEVICE

INTERRURT

AND

SYSTEM

TRAP

VECTORS

!6~

~============:

1 7 7 7 6

USER

AND

SYSTEM

PROGRAMS

STACK(S)

.....__

__

:~~~~~::=========:}

DEVICE & REGISTER

LOC

177776

....__

MEMORY

ORGANIZATION

AND

_____

BUS

10

RESERVED

14

BPT

~

!OT

24

PONER

30

EMT

}

34

TRAP

~

~~

100

EXTERNAL

LINE

244

FIS

NOTE:

DEVICE

DEVICE

ARE

SELECTED

JUMPERS

THE

DEVICE

l'ACE

MODULES

=~=~OFOR

DEVICE

__,

There is

however

32K

of

0-28K

is recommended

users

memory

dress locations, and 28K-32K

NOTE

1/0

device addresses, etc.

Figure 1-6 Memory Organization

1-9

space available;

for

memory

for

peripherals

ad-

Page 17

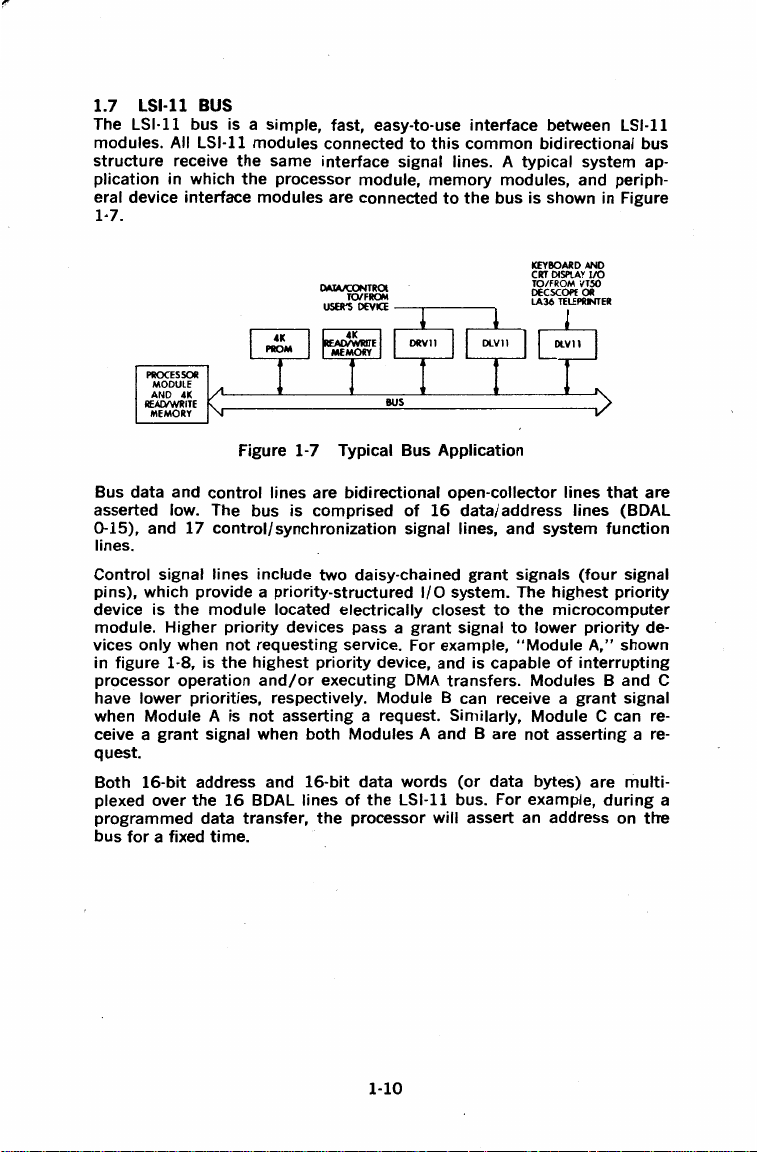

1.7

LSl·ll

The

LSl·ll

modules. All LSl-11

structure

plication

eral device

BUS

bus

receive

in

which

interface

is a

modules

the

the

modules

1·7.

PROCESSOR

MODULE

AND

41(

~ITE

MEMORY

Figure

Bus

data

and

control

asserted low. The bus

0-15),

and

17

control/synchronization

lines.

Control

pins),

device

module.

vices

in

processor

have

when

ceive a

which

only

figure

lower

Module

signal

lines

include

provide a priority-structured

is

the

module

Higher

priority

when

not

the

highest

requesting

and/or

1·8, is

operation

priorities,

A is

signal

not

when

grant

quest.

Both

16-bit

over

a fixed

address

the

16

data

time.

BOAL

transfer,

plexed

programmed

bus

for

simple,

fast, easy-to-use

connected

same

interface

processor

are

OoUAJCONTROI.

TO/FROM

USER'S

4K

PROM

1·7

Typical

lines

are

bidirectional

is

comprised

two

located

electrically

devices pass a

service. For example,

priority

executing

respectively.

asserting

both

Modules A and

and

16·bit

lines

of

the

to

this

signal lines. A

module,

memory

connected

DEVICE

-~--~

Bus

Application

of

16

signal lines,

daisy-chained

1/0

closest

grant

device,

and

OMA

Module

a request.

data

words

the

LSl·ll

processor

will

interface

common

between LSl-11

bidirectional

typical

modules,

to

the

bus

is

shown

KEYBOARD

CRT

DtSPl.AY

TO/FROM VT50

DECSCOPE

LA36

TELEPRNTER

open-collector

data/address

and

system

grant

signal

to

to

signals

The

the

lower

highest

microcomputer

system.

"Module

is

capable

transfers.

of

Modules B and

B can receive a

Similarly,

(or

B are

data

Module

not

asserting

bytes)

bus. For example,

assert

an address

system

and

periph·

in

Figure

ANO

l/O

OR

lines

that

lines

(BOAL

function

(four

signal

priority

priority

A,"

shown

interrupting

grant

signal

C can re·

are

during

on

bus

ap-

are

de·

C

a re·

multi·

a

ttre

1·10

Page 18

HIGHEST

PRIORTY

DEVICE

DECREASING

FRIORITY

-

~-----.

KDIH

MICRO·

COMPUTER

MODULE

(CO'HAINS4K

READIWRITE

RAM)

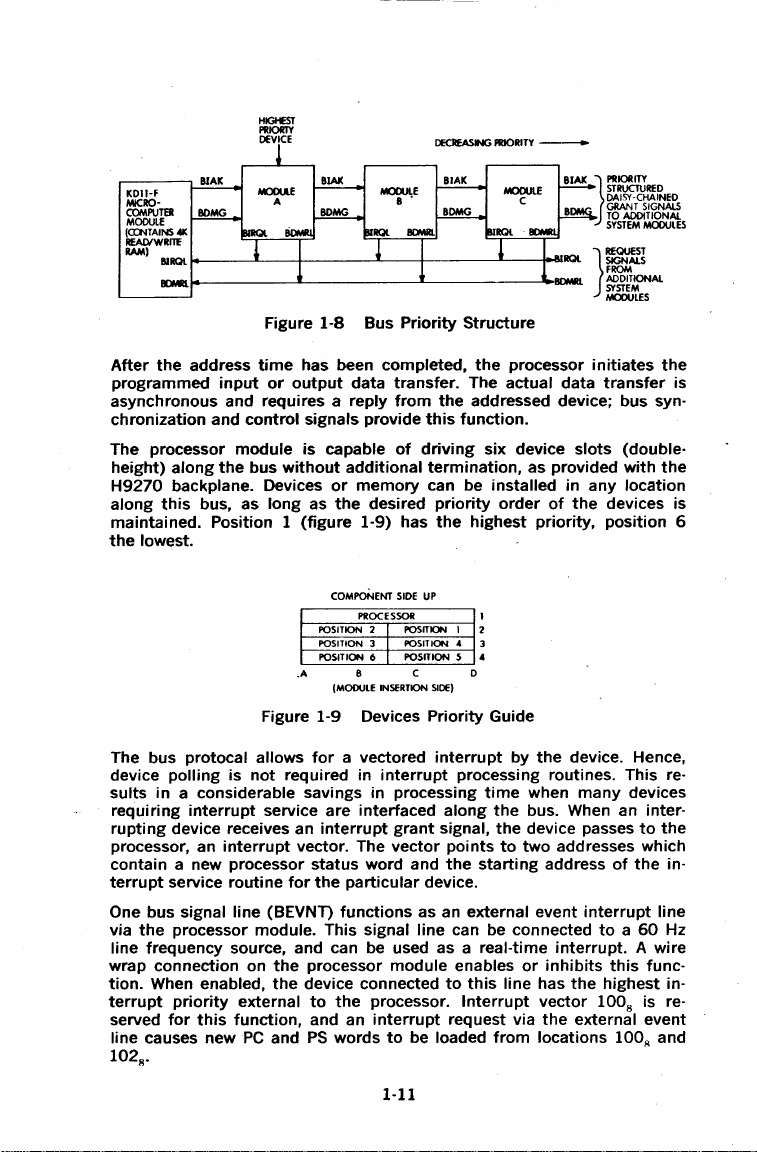

After

programmed

asynchronous and requires a

chronization

The

height)

H9270

along

maintained.

the

BIAK

the

address

input

and

control

processor

along

module

the

backplane. Devices

this

bus,

as

Position 1

lowest.

~E

A

Figure 1-8

time

has been completed,

or

output

data

reply

signals

is capable

bus

without

additional

or

long

as

the

(figure

COMPONENT

POSITION 2 POSITION 1

POSITION 3 POSITION 4

POSITION 6

_A

(MODULE

MOOULE

8 .

Bus

Priority

transfer.

from

provide

of

memory

desired

1-9) has

SIDE

PROCESSOI!

POSITION S 4

8

INSERTION

Figure 1-9 Devices

for

The bus protocal

device

polling

sults

in

requiring

rupting

processor, an

contain

terrupt

One bus signal

via

the

is

a considerable savings in processing

interrupt

device receives an

interrupt

a new processor

service

routine

line

processor module. This signal line can be connected

allows

not

service

(BEVNT)

a vectored

required in

are

interfaced

interrupt

vector. The

status

for

the

particular

functions

interrupt

grant

vector

word

and

line frequency source, and can be used

wrap

connection

tion.

When enabled,

terrupt

served

priority

for

line causes new

this

on

the

the

external

function,

PC

and

processor

module

device connected

to

the

words

processor.

interrupt

to

be loaded

and an

PS

1028.

BIAIC

MOOUlE

c

e

Structure

the

processor

The

actual

the

addressed device; bus syn-

this

function.

driving

six device

termination,

can be

UP

C D

Priority

priority

the

highest

SIDE)

installed

order

Guide

interrupt

data

slots

as provided

in

of

the

priority,

by

the

device. Hence,

processing routines. This re-

time

when

along

signal,

points

the

the

the

to

starting

many

bus. When an interdevice passes

two

addresses which

address

device.

as an external event

as

a real-time

enables

to

this

Interrupt

request via

from

or

inhibits

line has

vector

the

locations

interrupt.

the

external event

J

PRIORITY

STRUCTURED

DAISY-CHAINED

WAtiJij8"~

SYSTEM

MODULES

REQUEST

SIGNALS

FROM

ADDITIONAL

}

SYSTEM

MOOULES

initiates

transfer

the

is

(double-

with

any

the

location

devices is

position

6

devices

to

the

of

the

in·

interrupt

to a 60

line

Hz

A wire

this

func-

highest

in·

1008 is re-

1008 and

1-11

Page 19

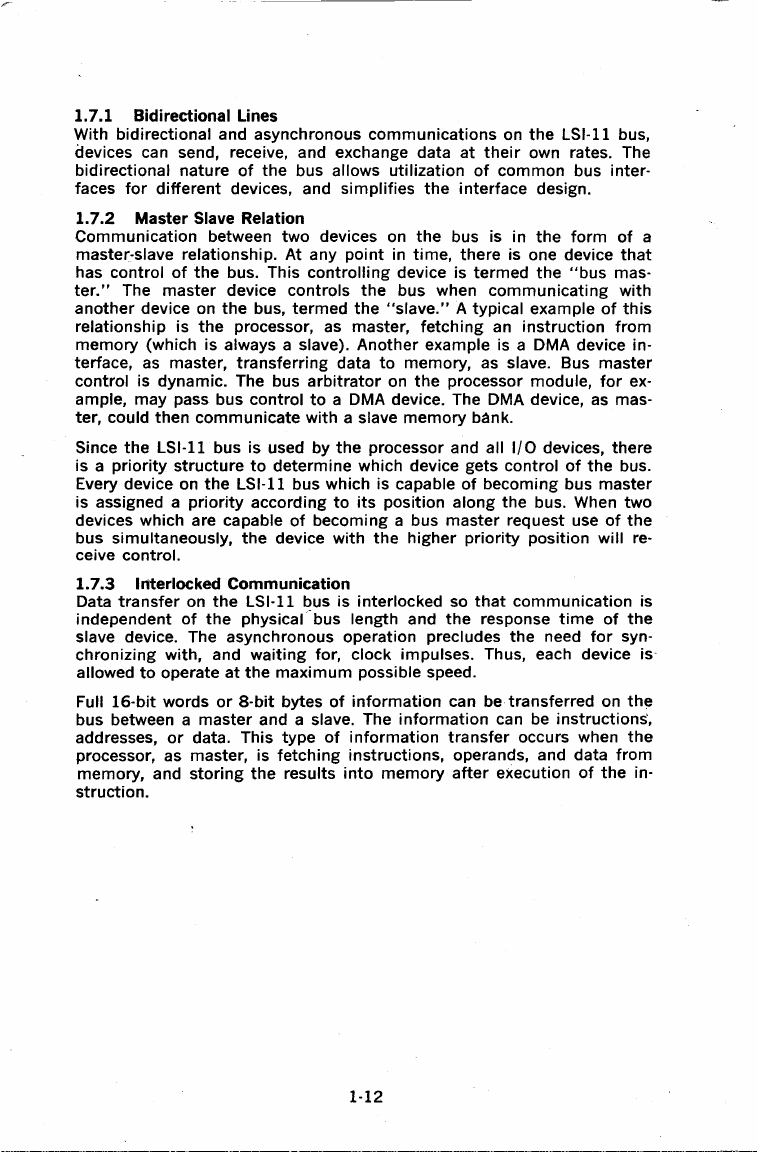

1.7.1 Bidirectional Lines

With bidirectional and asynchronous

devices can send, receive, and exchange data

bidirectional nature

faces

for

different

1. 7

.2

Communication

has control

ter."

another

relationship is

memory

terface, as master,

control is dynamic. The bus

ample, may pass bus control

ter, could

is a priority

is assigned a

devices which are capable

bus simultaneously,

ceive control.

chronizing

addresses,

processor, as master, is

Master

master-slave relationship. At any

Since

Every device on

1.7.3

Data

independent

slave device. The asynchronous operation precludes

allowed

Full

bus between a

memory, and

struction.

of

The

master

device on

(which is always a slave).

then

the

LSl-11 bus

structure

lnlerlocked

transfer

with, and

to

operate

16-bit

words

or

of

the

devices, and simplifies

Slave Relation

between

the

bus. This

device controls

the

the

processor, as master,

transferring

communicate

the

LSl-11 bus which is capable

priority

Communication

on

the

of

the

at

or

master

data. This

storing

bus allows utilization

two

controlling

bus,

termed

arbitrator

with

is

used by

to

determine

according

of

the

device

LSl-11 bus is interlocked so

physica(bus

waiting

the

maximum

8-bit

bytes

and a slave. The

type

fetching

the

results

communications

devices on

point

in

device is

the

bus when

the

"slave."

Another

data

to

to

becoming a bus

for, clock impulses. Thus, each device is-

of

on

a DMA device. The DMA device,

a slave

the

processor and all

which device

to

its

position

with

the

length and

possible speed.

of

information

information

information

instructions, operands, and data

into

memory

at

their

of

the

interface design.

the

bus is in

time,

there

termed

A typical example

fetching

example is a DMA device in-

memory, as slave. Bus

the

processor module,

memory

higher

bank.

gets

of

becoming bus

along

master

priority

that

the

response

can be transferred on

transfer

after

on

the

LSl-11 bus,

own rates. The

common

is one device

communicating

an

1/0

control

the

request use

communication

the

can be instructions',

execution

bus inter-

the

form

the

"bus

as

devices,

of

the

time

need

for

of

of

master

for

master

of

of

the

instruction

bus. When

position will

occurs when

of

that

mas-

with

this

from

mas-

there

bus.

two

the

the

syn-

the

the

from

a

ex-

re-

is

in-

1-12

Page 20

CHAPTER

2

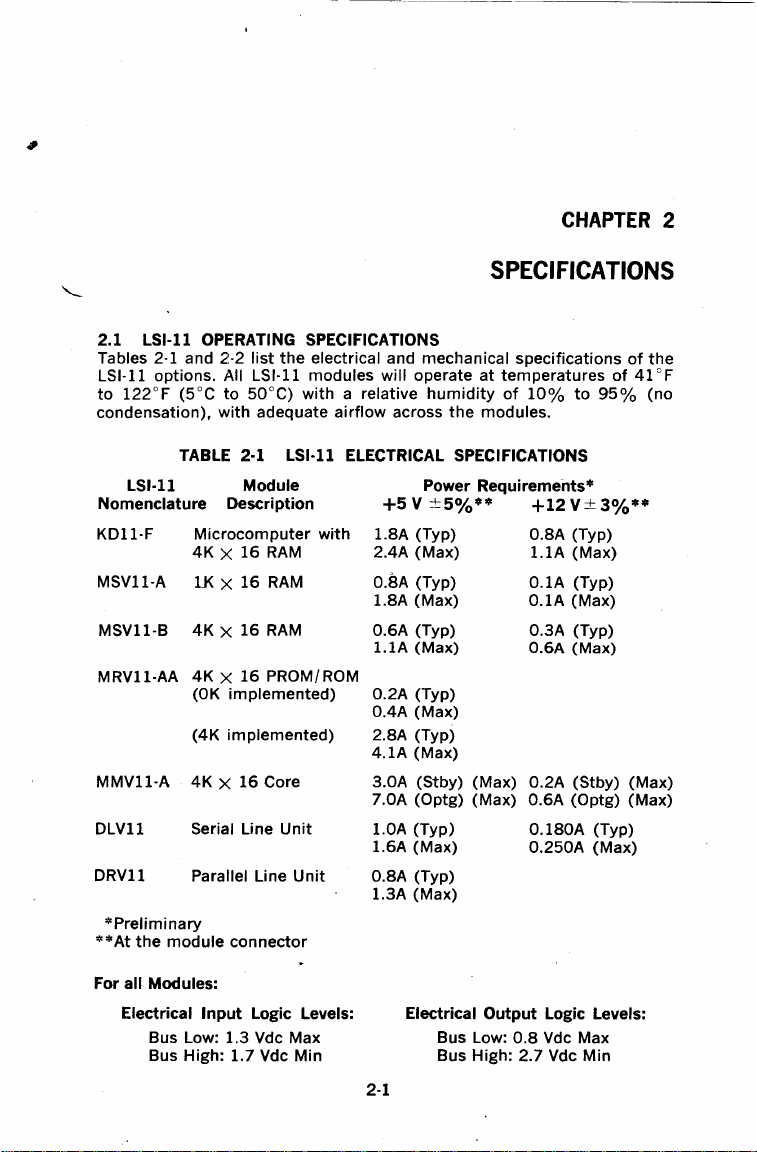

2.1 LSl-11 OPERATING SPECIFICATIONS

Tables 2-1 and 2-2

LSl-11 options. All LSl-11 modules will operate

to

122°F

condensation), with adequate airflow across

Nomenclature

KDII-F

MSVII-A

MSVll-B

MRVll-AA

MMVll·A

DLVll

DRVII

*Preliminary

**At

(5°C

TABLE 2-1 LSl-11 ELECTRICAL SPECIFICATIONS

LSl-11 Module

4K X 16

4K X 16

4K X 16

(OK

(4K

4K x 16

Serial Line

Parallel Line

the

module

list

the

to

50°C)

Description

Microcomputer

lK X 16

RAM

RAM

RAM

PROM/

implemented)

implemented)

Core

Unit

Unit

connector

electrical and mechanical specifications

with a relative

with

ROM

humidity

the

Power

+5 v ±5%**

I.SA

(Typ)

2.4A (Max)

O.SA

(Typ)

I.SA

(Max)

0.6A (Typ) 0.3A (Typ)

l.lA

(Max)

0.2A (Typ)

0.4A (Max)

2.SA (Typ)

4.IA

(Max)

3.0A (Stby) (Max)

7.0A (Optg) (Max) 0.6A (Optg) (Max)

1.0A (Typ)

I.GA (Max)

O.SA

(Typ)

1.3A (Max)

SPECI

at

modules.

Requirements*

FICA

temperatures

of

10%

to

+12V±3%**

O.SA

(Typ)

I.IA

(Max)

0.IA

(Typ)

O.IA

(Max)

0.6A

(Max)

0.2A (Stby) (Max)

0.ISOA (Typ)

0.250A

TIO

of

95%

(Max)

NS

of

41 ° F

the

(no

For all Modules:

Electrical

Input

Bus Low: 1.3 Vdc Max

Bus High: 1.7 Vdc Min

Logic Levels:

2-1

Electrical

Output

Bus Low:

Bus High: 2.7 Vdc Min

O.S

Logic Levels:

Vdc Max

Page 21

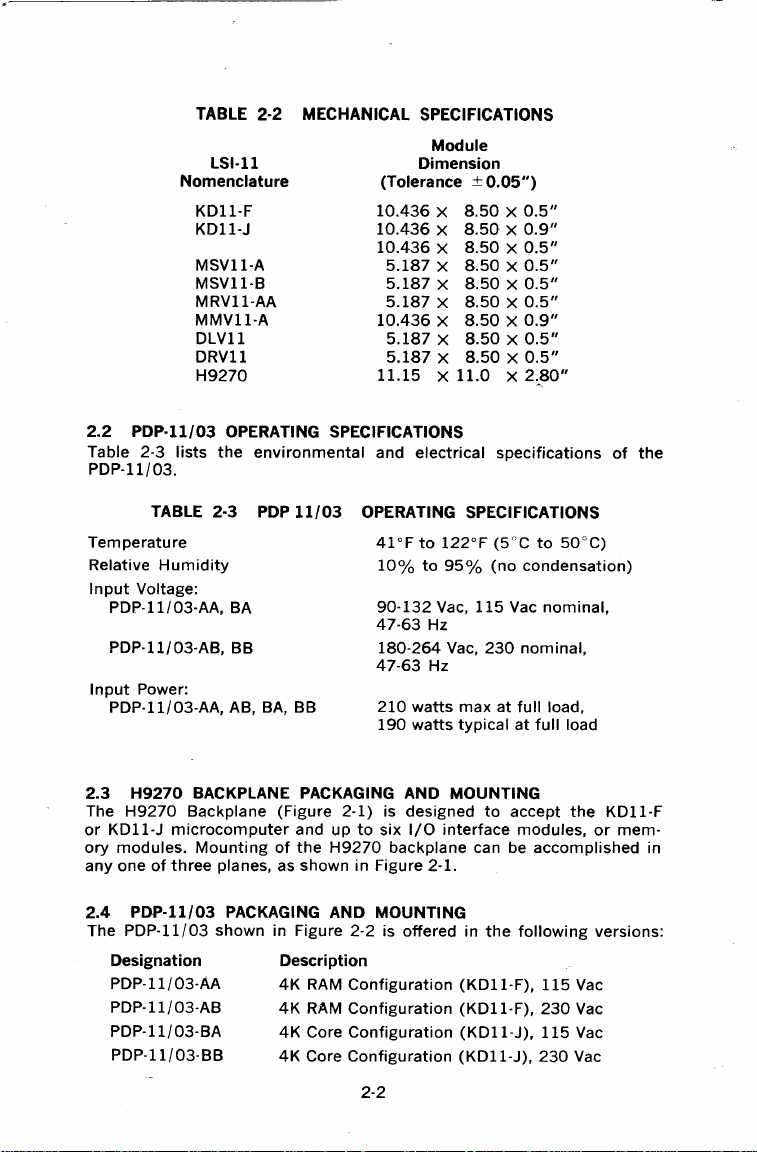

2.2

PDP·ll/03

Table

2·3

PDP·ll/03.

TABLE

2·2

MECHANICAL SPECIFICATIONS

LSl·ll

Nomenclature

KDll·F

KDll·J

MSVll·A

MSVll·B

MRVll·AA

MMVll·A

DLVll

DRVll

H9270

OPERATING SPECIFICATIONS

lists

the

environmental

Module

Dimension

(Tolerance ±

10.436 x 8.50 x 0.5"

10.436 x 8.50 x 0.9"

10.436 x 8.50 x 0.5"

5.187 x 8.50 x 0.5"

5.187 x 8.50 x 0.5"

5.187 x 8.50 x 0.5"

10.436 x 8.50 x 0.9"

5.187 x 8.50 x 0.5"

5.187 x 8.50 x 0.5"

11.15 x 11.0

and

electrical

0.05")

x 2._80"

specifications

of

the

TABLE

Temperature

Relative

Input

Input

2.3

The

or

ory

any

2.4

The

Humidity

Voltage:

PDP-11/03-AA, BA

PDP·ll/03·AB,

Power:

PDP-11/03-AA,

H9270

H9270

KDll-J

modules.

one

Backplane (Figure 2-1) is designed

microcomputer

of

three

PDP·ll/03

PDP-11/03

Designation

PDP-11/03-AA

PDP-11/03-AB

PDP-11/03-BA

PDP-11/03-BB

2·3

PDP

11/03

BB

AB, BA, BB

OPERATING SPECIFICATIONS

41°F

to

122°F

(5°C

10%

to

95%

(no

condensation)

90-132

47-63

180-264

47-63

210

190

Vac,

Hz

Hz

watts

watts

115

Vac,

max

typical

230

at

Vac

nominal,

full

at

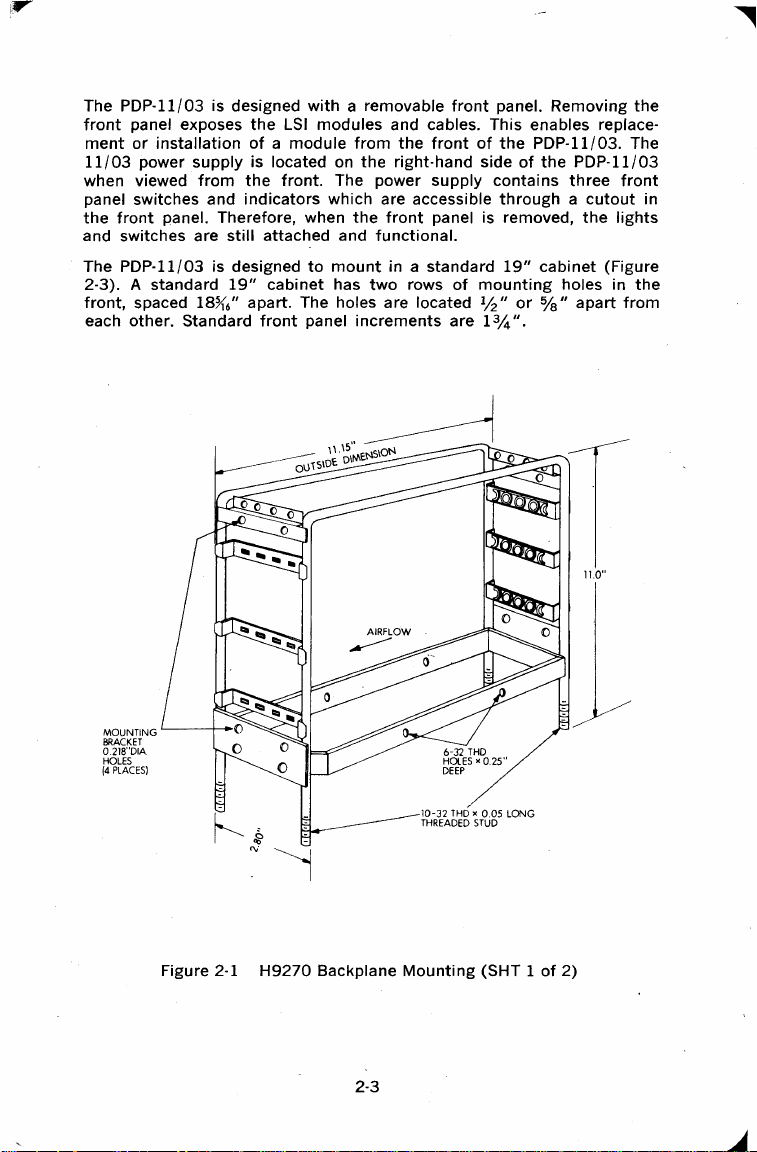

BACKPLANE PACKAGING AND MOUNTING

to

and

up

to

Mounting

of

planes, as shown in Figure 2-1.

the

six

H9270

backplane can be

1/0

interface

accept

modules,

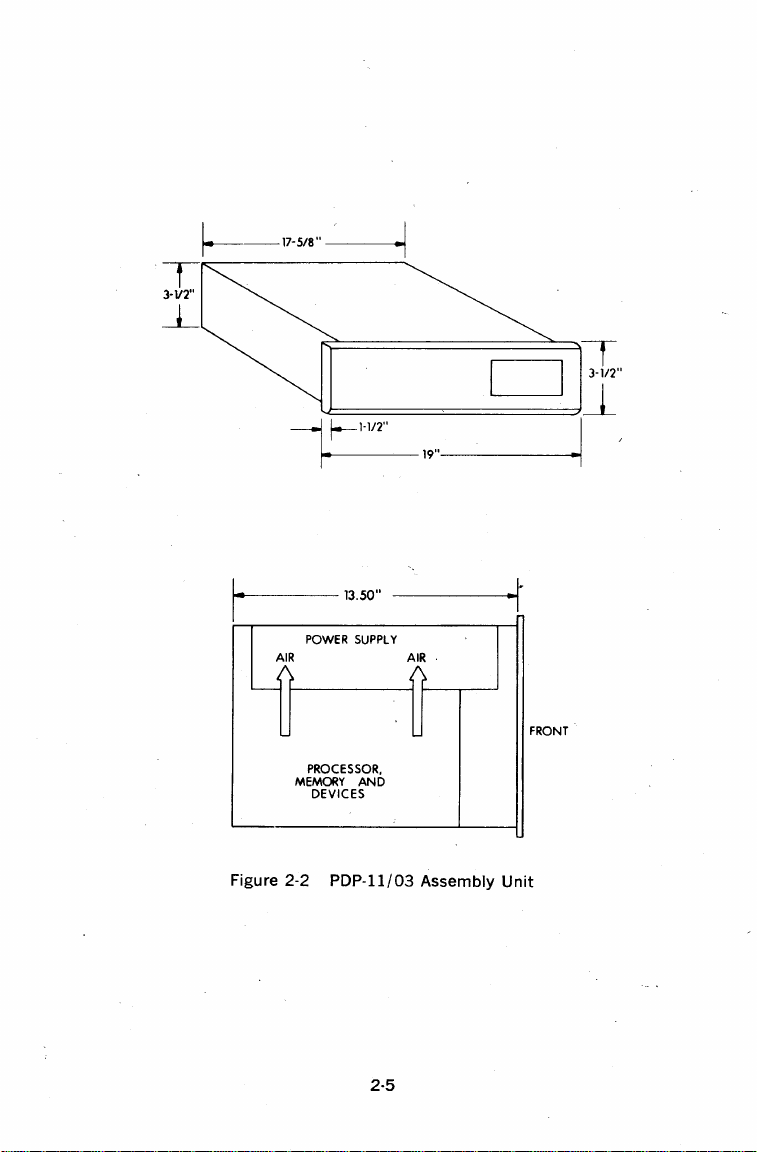

PACKAGING AND MOUNTING

shown in Figure 2-2 is offered in

the

following

Description

4K

RAM

4K

4K

4K

Configuration

RAM

Configuration

Core

Configuration

Core

Configuration

(KDl

(KDl

(KDl

(KDl

1-F),

1-F),

1-J),

1-J),

2-2

to

50°C)

nominal,

load,

full

load

the

KDll-F

or

accomplished

115

230

115

230

mem-

versions:

Vac

Vac

Vac

Vac

in

Page 22

1r

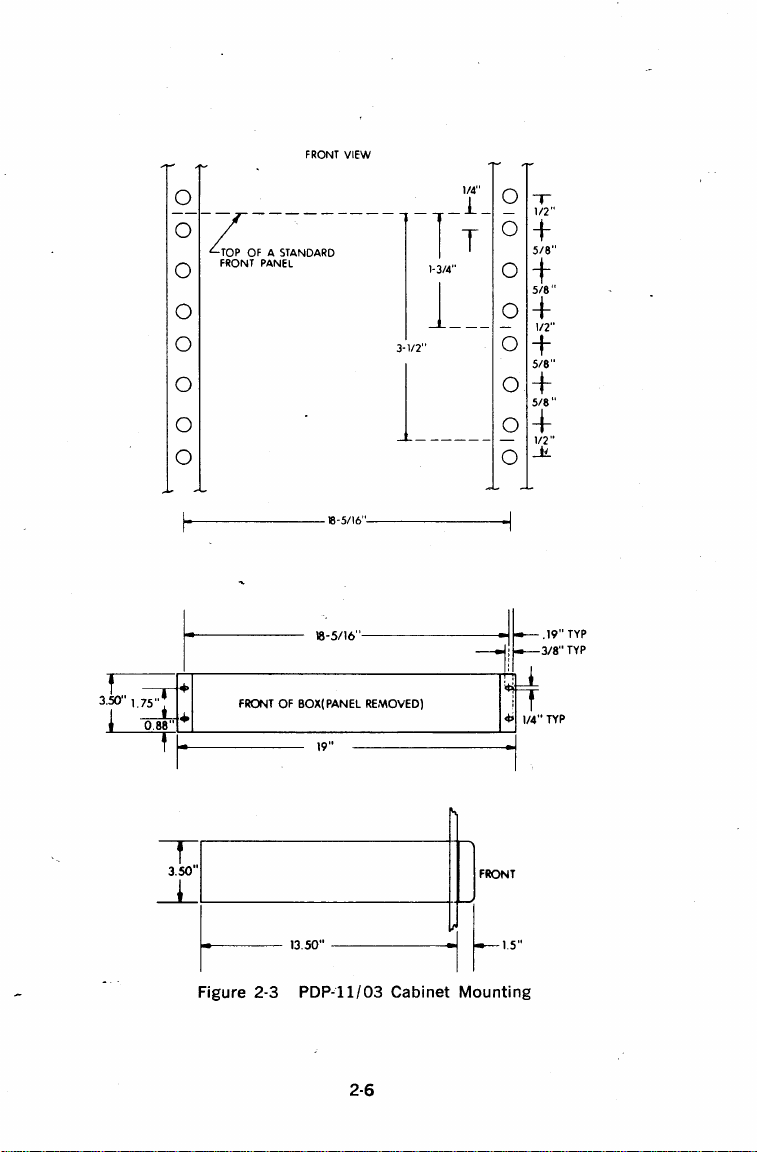

The PDP-11/03 is designed

front

panel exposes

ment

or

11/03

installation

power

when viewed

panel switches and

the

front

panel. Therefore, when

and switches are

supply

from

still

the

LSI modules and cables. This enables replaceof a module

is located on

the

front.

indicators

attached and

The PDP-11/03 is designed

2-3).

A standard

front,

spaced 18Yi

each other. Standard

19"

cabinet

apart. The holes are located If2"

"

6

front

with

a removable

from

the

the

The power

front

right-hand side

supply

which are accessible

the

front

functional.

to

mount

in a standard

has

two

rows

panel

increments

front

panel. Removing

of

the

PDP-11/03. The

of

the

contains

through a cutout

panel is removed,

19"

of

are

cabinet

mounting

or

1 % ".

holes in

% "

the

PDP-11/03

three

front

the

lights

(Figure

the

apart

from

in

MOUNTING

BRACKET

0.218"DIA

HOLES

(4

PLACES)

Figure 2-1

H9270

Backplane

2-3

Mounting

(SHT 1

of

2)

Page 23

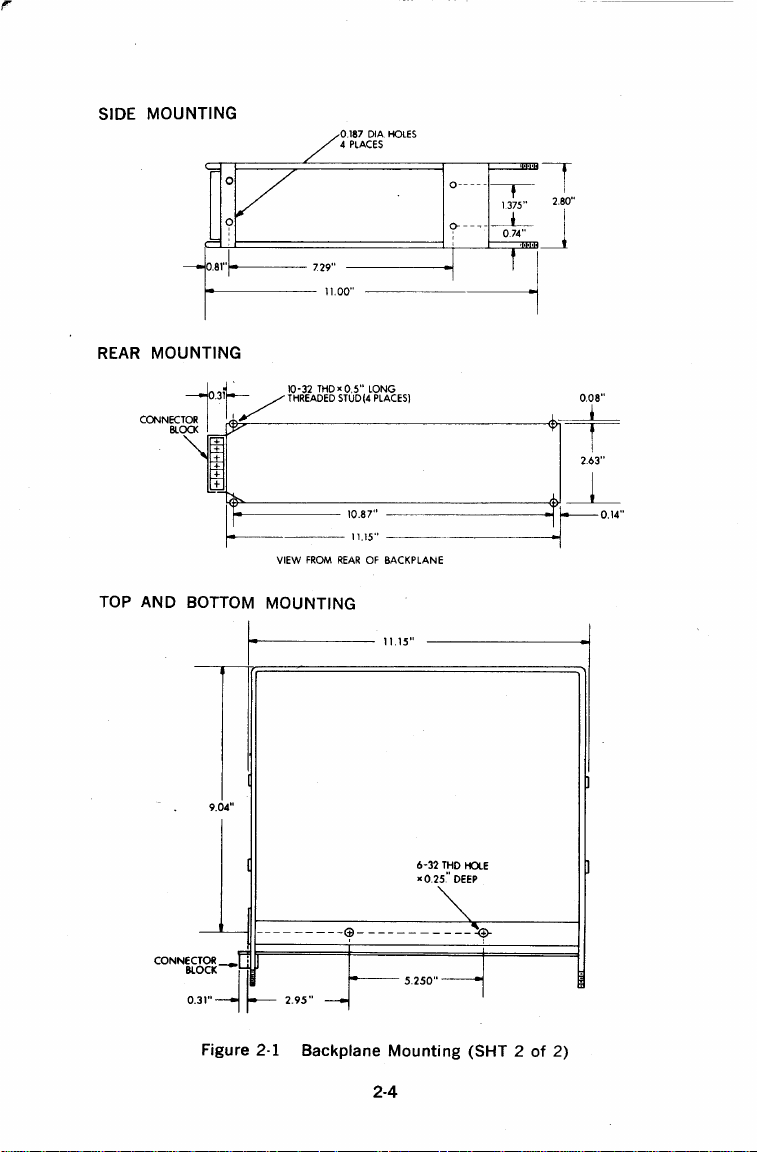

SIDE MOUNTING

REAR

MOUNTING

OCNNECT

0.31

~

BLOCK

...

I . -

0.187

DIA

HOLES

4

PLACES

10-32 THDx0.5"

' -

/T"'EADEDSTUO{HCACESJ

t

/ I

LONG

~

i

'~-1~;~1:"··

VIEW

FROM

REAR

TOP AND BOTTOM MOUNTING

I·

9.04"

----

-----9-

Figure 2-1 Backplane Mounting (SHT 2

-==--0"

OF

BACKPLANE

11.15"

THD

HOLE

6-32

xo.25"

DEEP

----

- - - -

5.250"

--:@-

of

2)

' !

2-4

Page 24

.j

l....t:::========:lj

f--1·1/2"

-

i

13.50"

19"------~

r

POWER

PROCESSOR,

MEMORY

DEVICES

SUPPLY

AND

AIR

/I

-

·

~

AIR

/\

.....__

-

Figure 2-2 PDP-11/03 Assembly

C=:J

.

FRONT

Unit

IT

3-112"

_l

2-5

Page 25

FRONT

VIEW

0

o--z---------

TOP

Q

0

0

0

0

0

-------18-5/16"-------

OF A STANDARD

FRONT

PANEL

3-112" 0 +

l

114"

Q T

_1_1_

a

~r

T 518"

1-3/4" 0 +

---

l

------

518"

0 t

518"

0 +

5/8"

9

*·

0

_k

..

l---

~,--~.-.-r-----------------,.-.:

3.50" 1.75"

~

~

1

~._•.....__

T

3.50'

_l__.____

FRONT

_____________

____

18-5/16''-------L.19"

OF

BOX(

PANEL

19"

REMOVED)

~13~"

Figure 2-3 PDP-11/03 Cabinet

2-6

114"

TYP

TYP

TYP

-u--~3/8"

__..___.ci:I

FRONT

t-_

~

~.,..

Mounting

Page 26

CHAPTER

3

Data stored in

dling

is specified by an

usually indicates:

function

• The

• A general-purpose register is

and

and/or

destination operand.

•

An

addressing mode

be used).

A large portion

(in character strings, arrays, lists, etc.).

vide

for

efficient and flexible

The general registers

following ways:

•

As

accumulators. The data

ister.

• As pointers. The contents

rather

As

pointers which

•

matically

autoincrement

as autodecrement addressing. These modes are

processing

•

As

index registers. In

the

word

-

-Of

the

An

important

with

the

• Six general-purpose registers (RO -

• A hardware Stack Pointer (SP), register (R6)

• A Program Counter (PC}, register (R7)

Registers

use is determined by

• They can be used

registers can be added and stored in

• They can contain

the

address

• They can be used

• They can be used as index registers

access.

memory

(operation code).

a general-purpose register

of

than

the

stepping

tabular

following

operand. This allows easy access

LSl-11 feature, which should be considered in

addressing modes, is

RO

through

o!

an operand.

must

LSl·ll

(to

specify how

the

data handled by a

handling

may

be used

operand itself.

automatically

addressing;

the

for

of

forward

or

the

the

for

automatically

array data.

this

instruction

RS

are

not

instruction

operand storage. For example,

address

the

autoincrement

be accessed and manipulated. Data han·

instruction

to

be used when

the

LSl-ll's

of

structured

with

to

be manipulated resides

the

register is

step

through

instance,

the

through

consecutive locations is known as

the

are

summed

register arrangement:

RS)

dedicated

that

is decoded:

another

of

an operand

for

3·1

ADDRESSING

(MOV, ADD, etc.), which

locating

to

be

used when

selected register(s)

computer

an

stepping

contents

to

to

or

convenient data and program

is usually

addressing modes pro-

data.

instruction

the

address

memory

backwards is known

particularly

of

to

produce

variable entries in a list.

any specific

register.

or

serve as pointers

autodecrement

MODES

the

source aper·

locating

is/are

structured

in any

within

of

lo~ations.

the

function;

contents

of

the

reg-

the

operand,

Auto·

useful

register and

the

address

conjunction

their

of

two

features.

the

to

the

for

to

Page 27

The LSl-11 also has

itate

temporary

handling

stack

tion

pointer"

with

R6 as a

ferred

• The

• The

• The hardware

Register

recommended

Whenever an

is

word.

The

• Single Operand

• Double Operand

•

• Deferred

• Use

• Use

•

of

data

manipulation.

is

known as

under

subroutine

"hardware

to

as

the

stack

stack

moves

up

of

the

stack.

information

R7

automatically

next

section is

register;

registers;

operands.

Direct

ister.

is

general-purpose registers in one

processor retrieves an

by 2. By

of

-immediate,

operations.

Summary

the

Addressing-The

(Indirect)

the

address

of

the

combining

the

basic

of

Stack

of

Instruction

bols are

programs. The

cerned

is

program.

instruction

data

storage

which

The

the

stack

program

linkage and

stack

"SP":

pointer

as

is used by

(SP) keeps

pointer

the

moves down as

items

stack

allowing

that

R7

instruction

incremented

divided

Addressing-One

second

Addressing-part

remaining

of

the

PC

as a General

addressing

absolute, relative, and relative deferred.

Pointer

Addressing

sufficient

about

accomplished

structures.

must

register

pointer.

control;

interrupt

pointer."

are removed. Therefore,

is used

the

processor

the

processor as

not

be used as a

is fetched

into

part

provides

parts

operand is

Addressing-The

operand.

instruction,

this

automatic

modes, we

as

General

Modes

mnemonics

programmer

conversion

automatically

addressing

be

frequently

used

to

Any

however,

service

For

track

of

items

during

trap

to

from

by

two

to

seven

major

part

information

of

provide

the

Register-The

important

it

advancement

produce

Register-Can

NOTE

and address

for

writing

to

mode

This can be used

register

this

the

return

of

the

contents

combinations

accessed. This is known as

keep

track

can be used as a

certain

its

automatically

assembly

instructions

automatically

reason, R6 is

latest

are added

it

always

or

interrupt

to

the

program

stack

pointer

memory,

point

to

categories:

the

instruction

for

instruction

information

contents

of

PC

respect. Whenever

the

four

mode

need

not

binary

digits;

by

the

for

of

stack

use Register

frequently

entry

on

to

the

points

handling

main

counter

or

the

the

locating

the

is

language

assembler

accumulator.

program

next

word specifies a

word specifies

for

of

the

selected reg-

selected register

unique

advances

of

the

special

be used

sym-

be con-

this

the

program.

the

locating

PC

that

facil-

convenient

manipula-

"stack

associated

re-

stack.

stack

and

to

the

top

to

store

(PC).

It

counter

instruction

operand.

the

two

from

other

the

the

PC

with

four

PC

modes

for

stack

is

3-2

Page 28

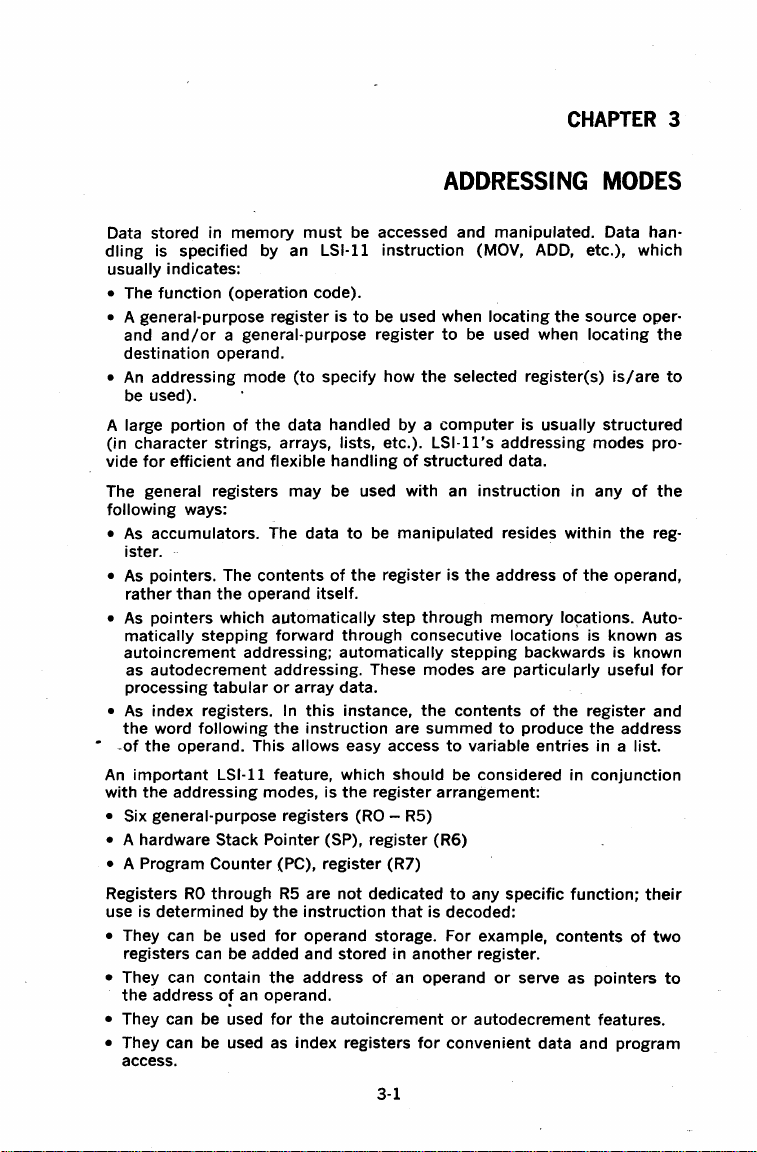

3.1 SINGLE OPERAND ADDRESSING

The

instruction

increment,

test)

format

is:

for

all single operand

instructions

(such as clear,

15

OP

CODE---~

DESTINATION

Bits

15

struction

through

to

Bits 5 through 0 form

This consists

a)

Bits O through

is

to

be referenced by

b) Bits 3

through

dress mode).

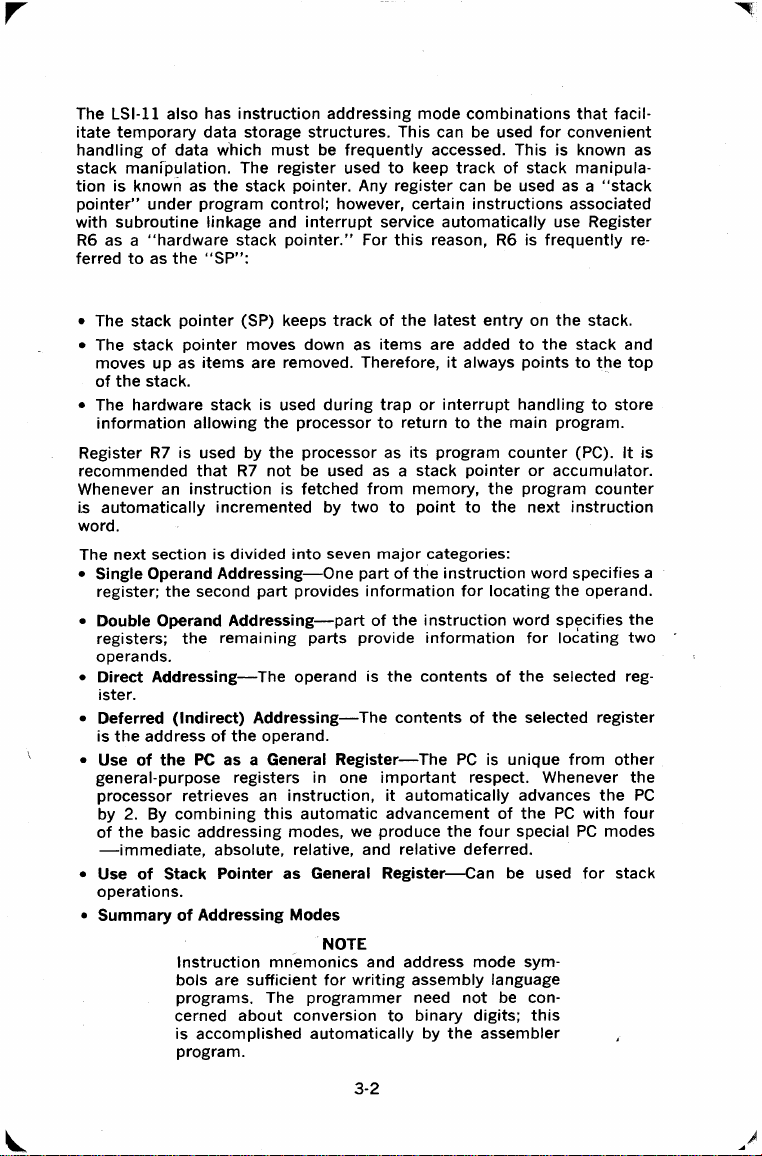

3.2

DOUBLE OPERAND ADDRESSING

Operations which

compare) are handled by

first

operand is called

operand.

may

format

Bit

specify

for

the

15

SOURCE

DESTINATION

ADDRESS----------~

6 specify

be executed.

a six-bit field called

of

two

subfields:

2 specify which

5 specify how

Bit 3 is·

imply

two

the

assignments in

different

modes and

double operand

OP

CODE

11

12

ADDRESS~--~

ADDRESS-------------'

the

this

set

instructions

source operand,

MODE

10

6 5 4 3 2

operation code

of

the

instruction

to

indicate deferred

eight

word.

the

selected register will be used (ad·

MODE

that

the

destination address field.

general purpose registers

Rn

defines

(indirect)

0

the

type

addressing.

of

in·

operands (such as add, subtract, move and

that

specify

the

source and destination address ffelds

different

instruction

9 8 6 5 4

is:

Rn

two

the

second

registers. The

MOOE

addresses. The

the

destination

Instruction

Rn

0

The source address field is used

to

select

the

source operand,

operand. The destination is used similarly, and locates

erand and

contents (source operand)

operand)

addition and

the

result. For example,

of

location

the

B.

contents

the

of

location A

After

execution B will contain

of

A will

instruction

be

unchanged. ·

to

ADD

the

contents (destination

3-3

the

A,

the

the

second op-

B adds

result

of

first

the

the

Page 29

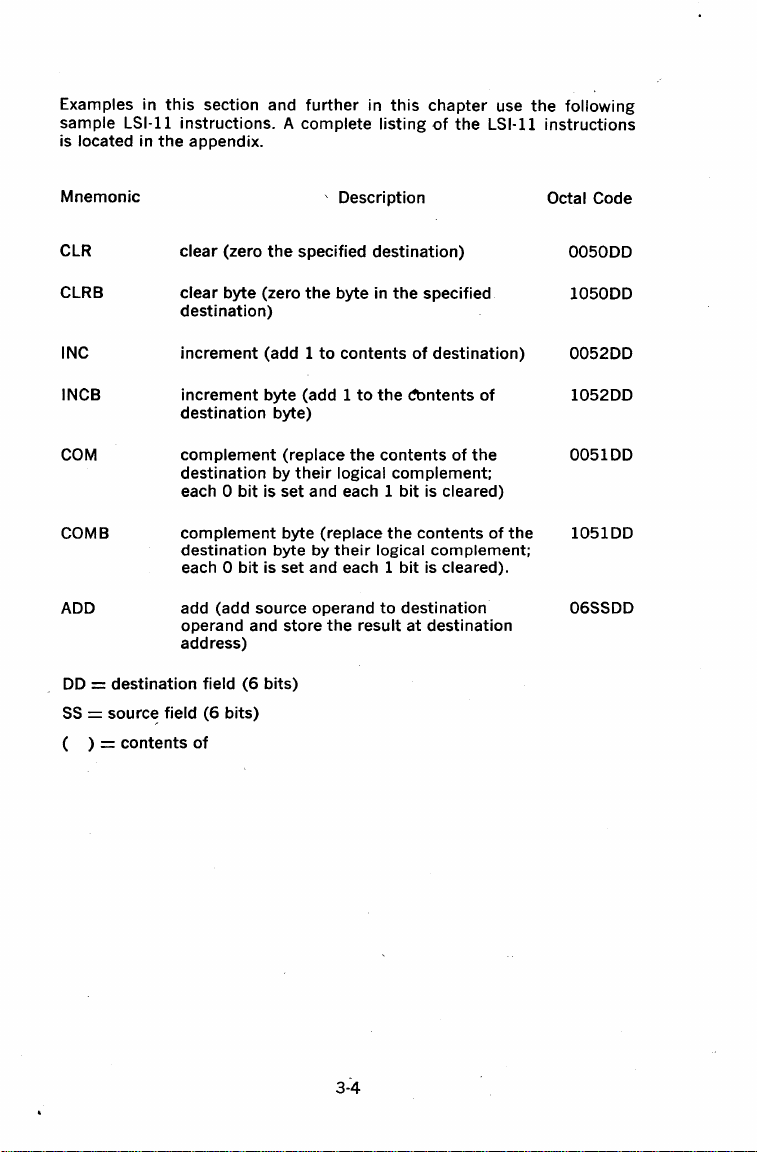

Examples in

this

section and

further

sample LSl-11 instructions. A complete

is located in

the

appendix.

in

this

listing

chapter

-0f

the

use

LSl-11

the

following

instructions

Mnemonic

CLR

CLRB

INC

INCB

COM

COMB

ADD

DD

= destination field

SS

=

sourc~

)

=contents

, Description Octal Code

clear (zero

clear byte (zero

the

specified

the

destination)

increment

increment

(add 1

to

byte (add 1

destination byte)

complement

destination by

each 0

complement

destination

each 0

(replace

their

bit

is set and each 1

byte (replace

byte by

bit

is set and each 1

add (add source operand

operand and store

the

address)

(6

bits)

field

(6

bits)

of

destination)

byte in

the

specified 1050DD

contents

the

to

the

contents

of

destination)

~ntents

of

the

logical complement;

bit

is cleared)

the

their

contents

logical complement;

bit

is cleared).

to

destination 06SSDD

result at destination

of

of

the

0050DD

0052DD

1052DD

0051

DD

1051DD

3-4

Page 30

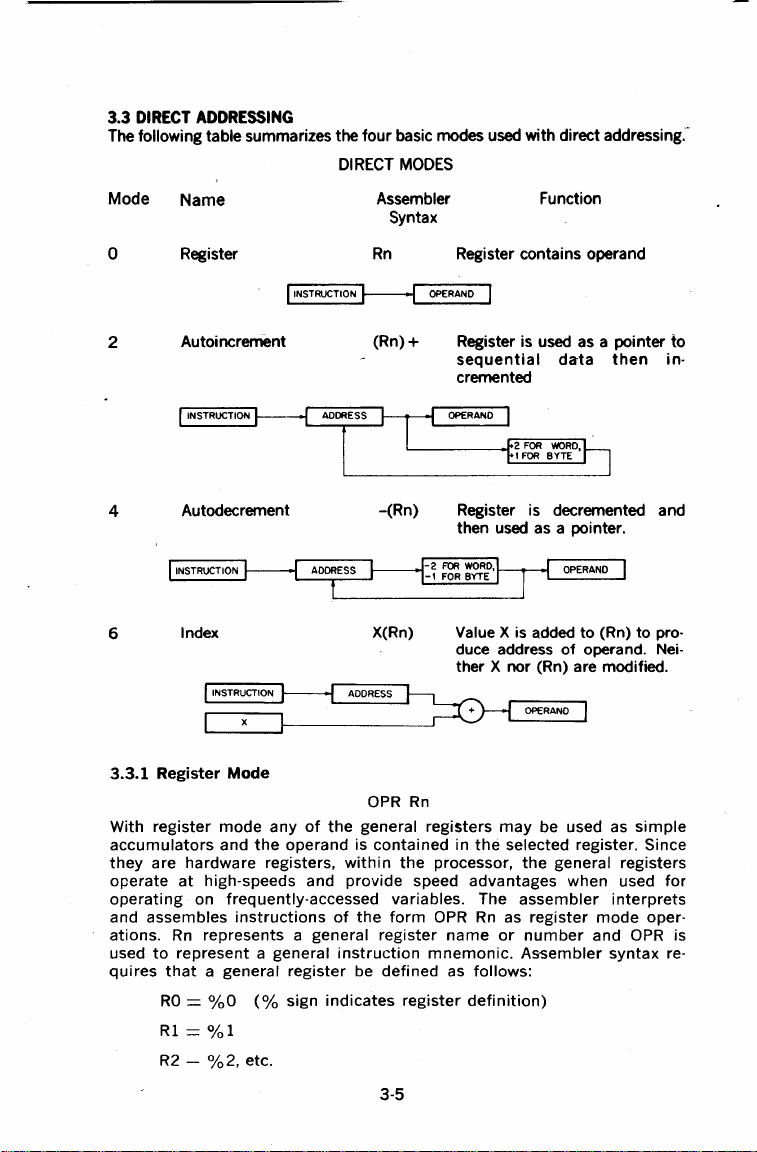

3.3

DIRECT

ADDRESSING

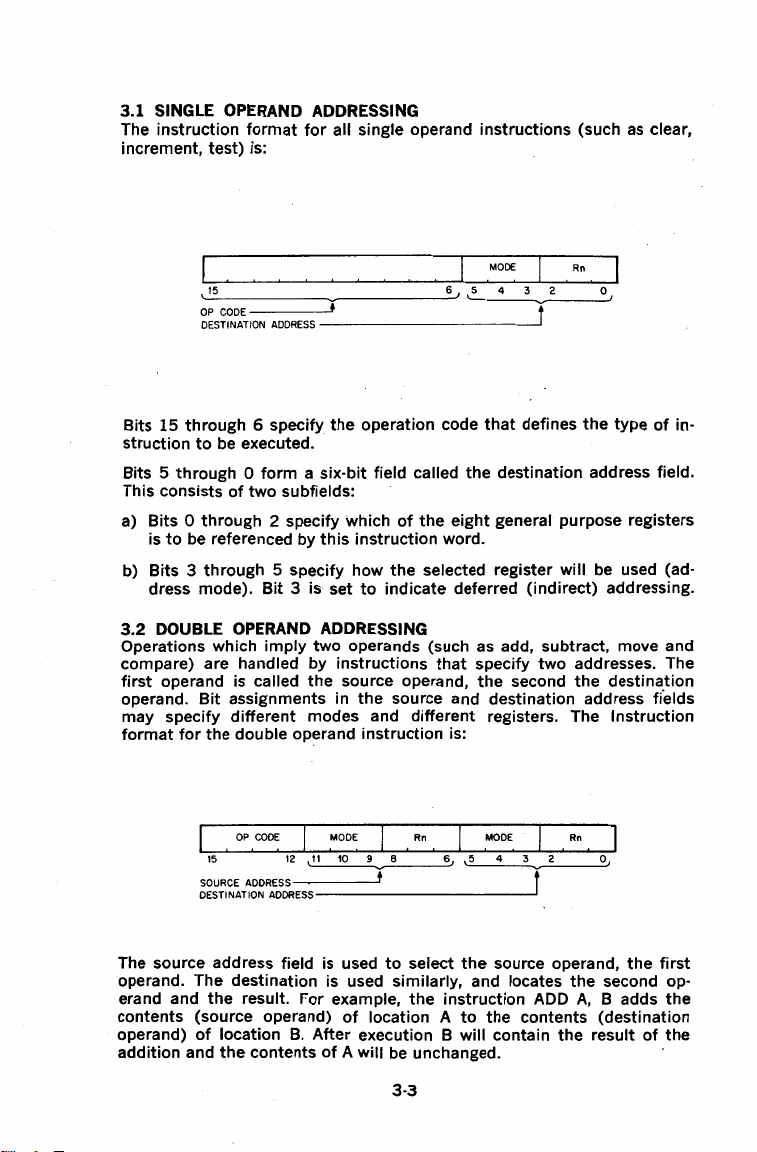

The following table summarizes the four basic modes used with direct addressing.-

Dl

RECT

MODES

Mode

0

2

4

6

3.3.1

Name

Register

Autoincrement

INSTRUCTION ADDRESS

Autodecrement

INSTRUCTION

Index

:

'"'7"0N

Register

With register

accumulators

they

are

operate

operating

hardware registers,

at

high-speeds and provide speed advantages when used

on frequently-accessed variables. The

and assembles

Rn

ations.

used

quires

represents a general register

to

represent

that

a general register be

RO=

%0

Rl = %1

R2 -%2,

Mode

mode

any

and

the

instructions

a general

(%

etc.

Assembler Function

Syntax

I

1NSTRUCTION

Rn

~

(Rn)+

Register contains operand

OPERAND I

Register is used

sequential

as

data

a pointer

then

to

in-

cremented

-(Rn)

ADDRESS

X(Rn)

Register is decremented and

as

then used

-2

FOR

WORD,

-1

FOR

BYTE

Value X is added

duce address

a pointer.

OPERAND

to

(Rn)

of

operand. Nei-

to

pro-

ther X nor (Rn) are modified.

~r-----A-00-R-ES-S-~~

OPR

of

the

operand is

general registers

contained

within

the

Rn

processor,

+

_OPE_R_AN_O__.

may

in

the

be used as

selected register. Since

the

general registers

simple

for

sign

of

the

instruction

defined

indicates

form

register

OPR

Rn

name

or

mnemonic.

as follows:

definition)

assembler

as

register

number

Assembler

interprets

mode

and

OPR

syntax

oper-

is

re-

3-5

Page 31

Registers are typically referred

R6

and R7. However

R6

and

respectively.

Register Mode Examples

(all numbers in octal)

to

by name as

R7

are also referred

RO,

Rl,

R2, R3,

to

as

SP

R4,

and

R5,

PC,

Symbolic

INC

1.

R3

Operation:

._l_o_._o_.._o_.__o_.__.._o_.___.._o_.._,__o~j_o_.._o_._)_o~l~o-·....__._~1

~·---~~-----6-

OP

CODE

(INC(0052))_J

DESTINATION

2.

Operation: Add the contents of

FIELD-----------~

ADDR2,R4

R4

BEFORE

R2

._I

__

...

I

__._o_ooo_04

Octal Code

005203

Add one

to

'-5

060204

00000

__

2~

__

Instruction

Increment

the

contents

4 3 2 0

Add

R2

to the contents of

AFTER

R2

._I

__

0_0_000_2__,,

R4

._I

__

o_oo_o_o_s__,,

Name

of

general register 3

R0

RI

R2

..

l~~~~R

R3

R4

~·

R5

R6(SP)

R7 (PC)

R4.

3. COMBR4

Operation:

BEFORE

R4

I 02<!222

105104

One's complement bits 0-7 (byte) in

Complement Byte

R4.

(When

general registers are used, byte instructions only

operate on bits 0-7; i.e. byte 0 of the register)

AFTER

R4 I

022155

3-6

Page 32

3.3.2 Autoincrement Mode

OPR

This mode provides

tial

elements

selected general register

registers are stepped

two

for

R6 and R7)

of

for

a table

(by

to

automatic

of

operands.

to

be

the

one

for

address

the

increment mode is especially useful

cessing.

address

handling,

of

It

the

this

purposes.

will access an element

next operand in

of a table

the