Page 1

PDF

-10

System

Reference

Manual

7

J

5

gpgMHittKMtfttlitfg

'

ORDER NO.

DEC-10-HGAA-D

FROM

PROGRAM

LIBRARY,

MAYNARD,

MASSACHUSETTS

PRICE

$5.00

DIRECT COMMENTS

CONCERNING

THIS MANUAL

TO SOFTWARE

QUALITY

CONTROL,

MAYNARD,

MASSACHUSETTS

DIGITAL

EQUIPMENT

CORPORATION

MAYNARD,

MASSACHUSETTS

Page 2

April

1968

Second

printing,

June

1968

Changes

are

indicated

by

a

triangle

(A)

in the

outside

margin.

Copyright

1968

by

Digital

Equipment

Corporation

Instruction

times,

operating speeds

and the like are

included here for reference

only; they

are not to be

taken as

specifications.

Written and

designed

for

Digital Equipment Corporation

by

William

English,

Wayland,

Massachusetts

Manufactured in the United States

of America

Page 3

Contents

1 INTRODUCTION

1-1

1.1

Number

System

1-4

Floating point

arithmetic 1-5

1.2

Instruction

Format

1-6

Effective address

calculation

1-7

1.3

Memory

1-8

Memory

allocation 1-9

1.4

Programming

Conventions

1-10

2

CENTRAL PROCESSOR

2-1

2.

1 Half Word Data

Transmission

2-2

2.2

Full Word

Data

Transmission

2-9

Move

instructions 2-10

Pushdown list

2-12

2.3

Byte

Manipulation

2-15

2.4

Logic

2-17

Shift and

rotate 2-24

2.5

Fixed Point

Arithmetic

2-26

Arithmetic

shifting

2-3 1

2.6

Floating

Point

Arithmetic

2-32

Scaling

2-33

Operations

with

rounding

2-34

Operations

without

rounding

2-37

2.7

Arithmetic

Testing

2-41

2.8

Logical

Testing

and

Modification

2-47

2.9

Program

Control

2-54

2.10

Unimplemented Operations

2-64

2. 1 1

Programming

Examples

2-65

Double

precision floating

point

2-67

2.12

Input-Output

2-68

Readin mode 2-72

Console data

transfers

2-73

Page 4

VI

2.13

Priority Interrupt

2-73

2.14

Processor

Conditions 2-78

3

BASIC

IN-OUT

EQUIPMENT

3-1

3.1

Paper Tape

Reader

3-1

Readin

mode 3-4

3.2

Paper

Tape

Punch

3-5

3.3

Teletype

3-7

APPENDICES

A

Instruction

and Device Mnemonics

A

1

Numeric

listing

A3

Alphabetic

listing

A6

Device

mnemonics A10

B

In-out

Codes

Bl

Teletype

code B2

Card codes

B6

C

Miscellany

Cl

Page 5

Introduction

The

PDF- 10 is a

general purpose,

stored

program computer

that includes a

central

processor,

a

memory,

and

a

variety

of

peripheral equipment

such as

paper

tape

reader and

punch, teletype,

card

reader,

line

printer, DECtape,

magnetic tape,

disk

file and

display.

The central

processor

is the control

unit

for

the entire

system:

it

governs

all

peripheral

in-out

equipment,

sequences

the

program,

and

performs

all

arithmetic,

logical

and data

handling opera-

tions.

The

processor

is

connected

to

one

or

more

memory

units

by

a mem-

ory

bus and to the

peripheral

equipment

by

an in-out bus. The fastest

devices,

such as the disc

file,

although

controlled

by

the

processor

over the

in-out

bus,

have direct access to

memory

over a

second

memory

bus.

The

processor

handles words of

thirty-six

bits,

which are stored in a mem-

ory

with a maximum

capacity

of

262,144

words.

Storage

in

memory

is

usually

in the form of

37-bit

words,

the extra bit

producingoddparit^

for

the word.

The bits of a

word

are

numbered

0-35,

left to

right,

as are the

bits in the

registers

that

handle the words. The

processor

can also handle

half

words,

wherein the left half

comprises

bits

0-17,

the

right

half,

bits

18-35.

Optional

hardware is available for

byte

manipulation

a

byte

is

any

contiguous

set of

bits

within a word.

Registers

that hold addresses

have

eighteen

bits,

numbered 18-35

according

to

the

position

of the address

in

a

word. Words are used either as

computer

instructions in the

program,

as

addresses,

or as

operands

(data

for the

program).

Of the internal

registers

shown in

the illustration on the next

page, only

PC,

the

18 bit

program

counter,

is

directly

relevant to

the

programmer.

The

processor performs

a

program by executing

instructions retrieved from the

locations

addressed

by

PC.

At the

beginning

of

each instruction PC is incre-

mented

by

one so that it

normally

contains an address one

greater

than the

location

of the

current instruction.

Sequential

program

flow

is

altered

by

changing

the contents of

PC,

either

by incrementing

it an extra time in a

skip

instruction or

by replacing

its

contents with the value

specified

by

a

jump

instruction. Also of

importance

to the

programmer

is

the 36-bit data

switch

register

DS on the

processor

console:

through

this

register

the

pro-

gram

can read data

supplied by

the

operator.

The

processor

also contains

flags

that

detect various

types

of

errors,

including

several

types

of overflow

in arithmetic

and

pushdown operations,

and

provide

other information

of

interest

to the

programmer.

The

processor

has other

registers

but the

programmer

is not

usually

con-

cerned with them

except

when

manually stepping

through

a

program

to

debug

it.

By

means of

the address switch

register

AS,

the

operator

can

1-1

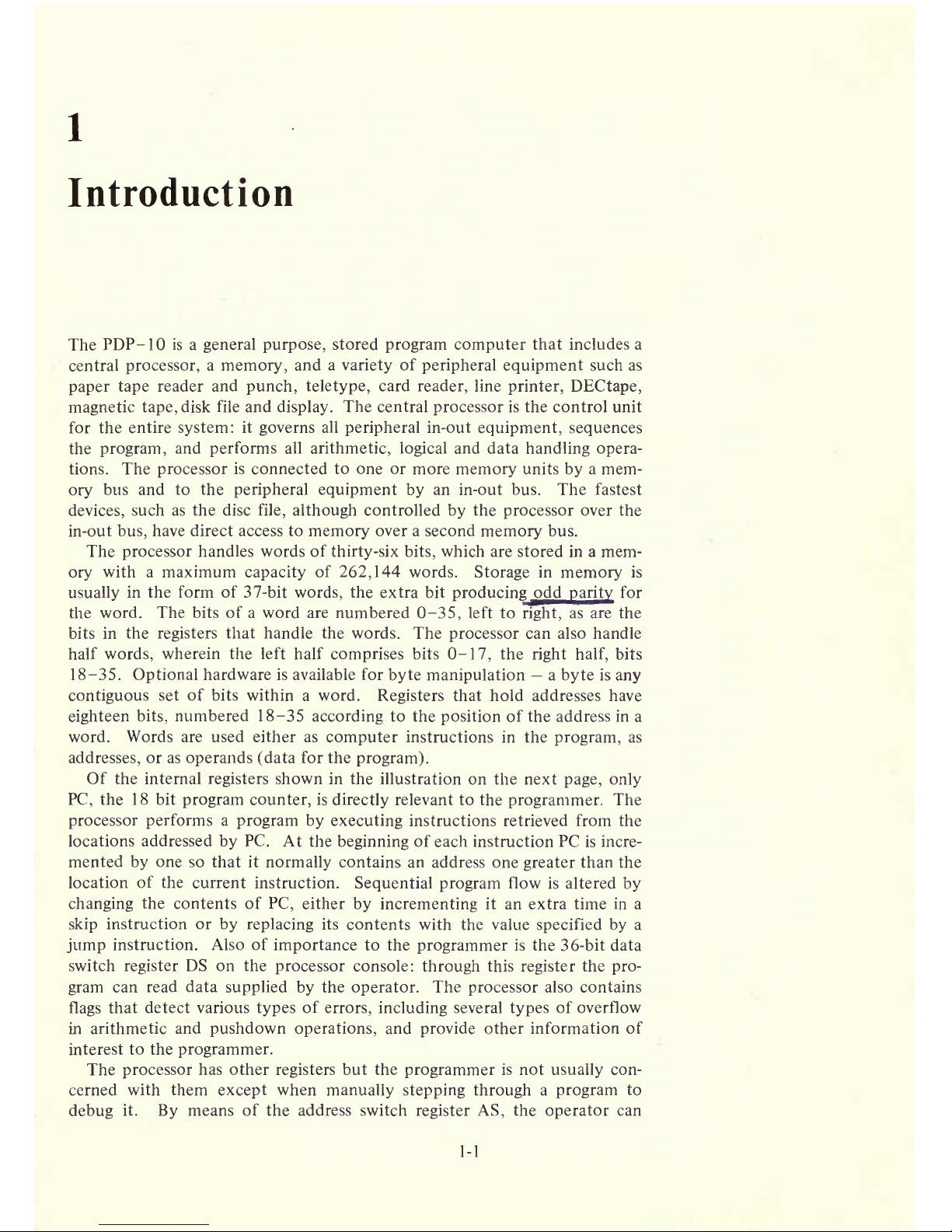

Page 6

1-2

INTRODUCTION

CORE

MEMORY

8192

OR 16384

37-BIT

WORDS

CORE MEMORY CORE

MEMORY

MEMORY BUS

FAST

MEMORY

16 X36

MA

18

AS

18

PC

18

ARITHMETIC

LOGIC

(AR, BR,

MQ)

IN-OUT BUS

CENTRAL

PROCESSOR

18

Ml

36

DS

36

PRIORITY

INTERRUPT

PAPER TAPE

READER

PAPER TAPE

PUNCH

TELETYPE

PDP-10

SIMPLIFIED

examine the contents

of,

or

deposit

information

into,

any

memory

location;

stop

or

interrupt

the

program

whenever a

particular

location

is

referenced;

and

through

AS

the

operator

can

supply

a

starting

address

for the

program.

Through

the

memory

indicators

MI the

program

can

display

data for the

operator.

The instruction

register

IR contains

the left half

of the current

instruction

word,

ie

all

but the address

part.

The

memory

address

register

MA

supplies

the

address

for

every memory

access.

The

heart of the

proc-

essor

is the

arithmetic

logic,

principally

the 36-bit

arithmetic

register

AR.

Page 7

1-3

This

register

takes

part

in all

arithmetic,

logical

and data

handling

operations;

all

data transfers

to and from

memory, peripheral equipment

and console are

made

via

AR. Associated

with AR are an

extremely

fast full

adder,

a buffer

register

BR

that holds a second

operand

in

many

arithmetic and

logical

instructions,

a

multiplier-quotient

register MQ

that serves

primarily

as an

extension

of AR

for

handling

double

length operands,

and smaller

registers

that

handle

floating point exponents

and control shift

operations

and

byte

manipulation.

From the

point

of view of the

programmer

however the arithmetic

logic

can

be

regarded

as a black box.

It

performs

almost all of

the

operations

necessary

for the execution

of

a

program,

but it never retains

any

informa-

tion from

one instruction to the next.

Computations performed

in

the

black

box

either affect

control

elements

such as PC

and

the

flags,

or

produce

results

that are

always

sent to

memory

and must be retrieved

by

the

proc-

essor

if

they

are

to be

used

as

operands

in other

instructions.

An instruction

word

has

only

one 18-bit address field for

addressing any

location

throughout

all of

memory.

But most

instructions

have two 4-bit

fields

for

addressing

the first sixteen

memory

locations.

Any

instruction

that

requires

a second

operand

has an accumulator address

field,

which can

address one of these

sixteen locations as an

accumulator;

in other

words

as

though

it were a result held over

in

the

processor

from some

previous

instruction

(the

programmer usually

has a choice of

whether the result

of

the

instruction

will

go

to the location addressed as an accumulator or to that

addressed

by

the 18-bit

address

field,

or to

both).

Every

instruction has a

4-bit

index

register

address

field,

which can address

fifteen

of these locations

for use

as index

registers

in

modifying

the 18-bit

memory

address

(a

zero

index

register

address

specifies

no

indexing). Although

all

computations

on

both

operands

and addresses are

performed

in

the

single

arithmetic

register

AR,

the

computer actually

has sixteen

accumulators,

fifteen of which can

double

as index

registers.

The factor that

determines whether one

of

the

first sixteen

locations

in

memory

is an

accumulator or an index

register

is

not the information

it

contains

nor

how its contents

are

used,

but rather

how the

location is addressed. There

need be no difference

physically

be-

tween these

locations and

other

memory

locations,

but an

optional,

fast

flip-

flop

memory

contained

in

the

processor

can be

substituted

for the bottom

sixteen

locations in core. This allows much

quicker

access to these locations

whether

they

are addressed as

accumulators,

index

registers

or

ordinary

memory

locations.

They

can even be

addressed from the

program

counter,

gaining

faster execution

for

a short but

oft-repeated

subroutine.

Besides

the

registers

that enter into the

regular

execution of the

program

and its

instructions,

the

processor

has a

priority

interrupt system

and can

contain

optional

equipment

to facilitate time

sharing.

The

interrupt system

facilitates

processor

control of the

peripheral

equipment by

means of a num-

ber of

priority-ordered

channels over which external

signals may interrupt

the normal

program

flow. The

processor acknowledges

an

interrupt

request

by

executing

the instruction contained in a

particular

location

assigned

to

the channel.

Assignment

of channels to

devices is

entirely

under

program

control. One

of the

devices to which the

program

can

assign

a channel is the

processor

itself,

allowing

internal

conditions such

as

overflow

or a

parity

Page 8

1-4

INTRODUCTION

1.1

error to

signal

the

program.

The time share hardware

provides

memory protection

and

relocation.

Without time

sharing,

all

instructions

and all

memory

are

available to

the

program.

Otherwise

a

number of

programs

share

processor time,

with

each

program

relocated and

restricted to a

specific

area

in

core,

and

certain in-

structions are

usually illegal.

An

attempt by

any

user

to

execute an

illegal

instruction

or address a

memory

location

outside of his

area

results in a

transfer

of control

back to the

time-sharing

monitor.

1.1 NUMBER

SYSTEM

The

program

can

interpret

a

data word as

a

36-digit, unsigned

binary

num-

ber,

or the left and

right

halves

of

a word can

be taken

as

separate

1

8-bit

numbers.

The PDF- 1

repertoire

includes

instructions that

effectively

add

or subtract

one from both

halves of a

word,

so the

right

half

can be

used for

address

modification

when the

word

is

addressed as

an index

register,

while

the left half is used to

keep

a

control

count.

The standard arithmetic

instructions in

the PDF- 10 use

twos

comple-

ment,

fixed

point

conventions

to do

binary

arithmetic. In a

word used

as

a

number,

bit

(the

leftmost

bit)

represents

the

sign,

for

positive,

1 for

negative.

In a

positive

number the

remaining

35

bits are the

magnitude

in

ordinary binary

notation.

The

negative

of a

number is

obtained

by taking

its

twos

complement.

If

x

is

an

-digit binary number,

its twos

complement

is

2"-x,

and its ones

complement is(2"-l)-jc,

or

equivalently

(2"-x)

-

1.

Subtracting

a number from 2"- 1

(ie,

from all

Is)

is

equivalent

to

perform-

ing

the

logical

complement,

ie

changing

all Os

to Is and all Is to Os.

There-

fore,

to form the twos

complement

one takes

the

logical

complement

(usually

referred to

merely

as

the

complement)

of

the entire word

including

the

sign,

and

adds 1 to

the

result.

In a

negative

number the

sign

bit is

1,

and

the

remaining

bits are the twos

complement

of the

magnitude.

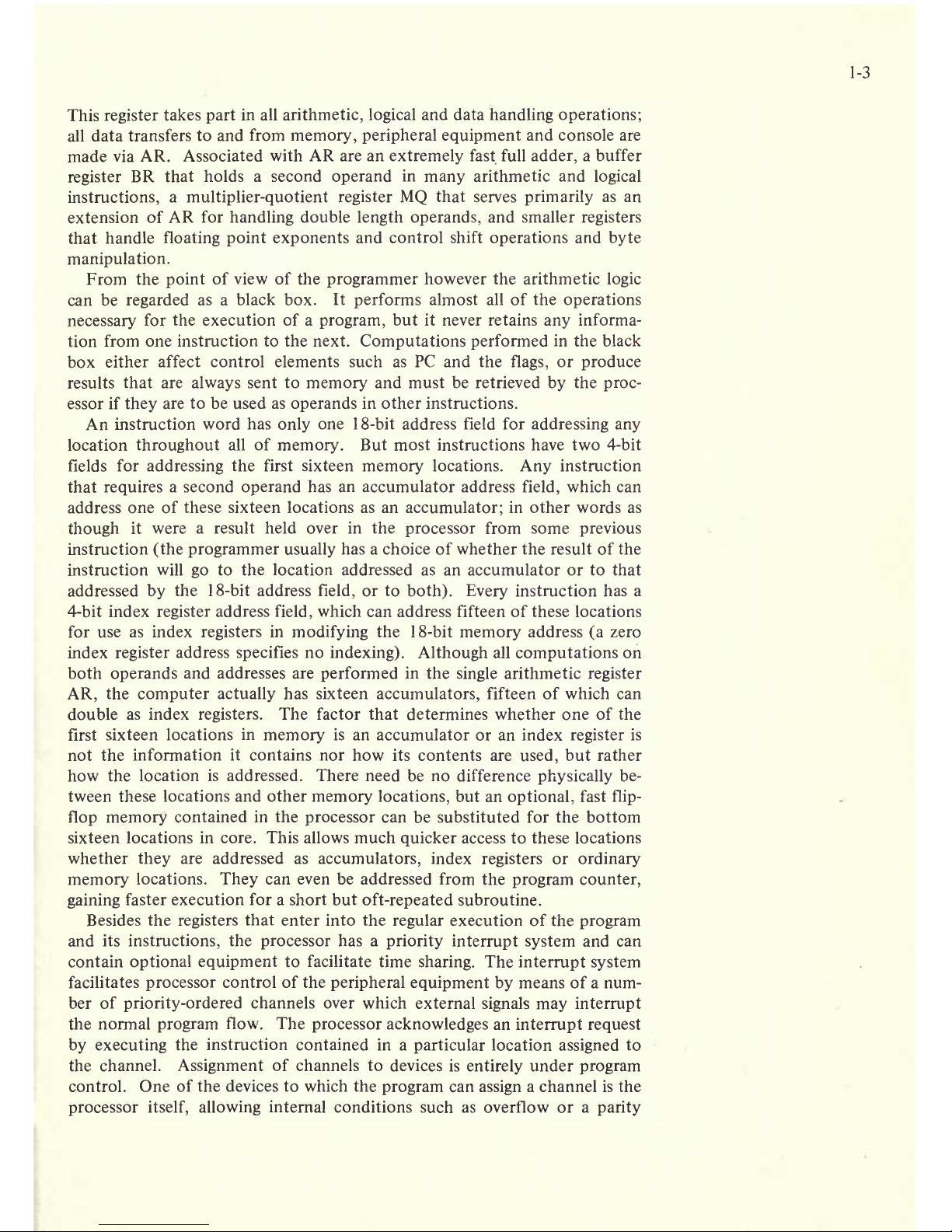

+

153,

-

+231

8

-000000000000000000000000000010011001

35

-153,0

=

-231

8

=1111

111 111 111 111

111 111 111 111 101 100111

35

Zero is

represented

by

a word

containing

all Os.

Complementing

this num-

ber

produces

all

Is,

and

adding

1 to that

produces

all Os

again.

Hence there

is

only

one

zero

representation

and

its

sign

is

positive.

Since the numbers

are

symmetrical

in

magnitude

about

a

single

zero

representation,

all even num-

bers both

positive

and

negative

end

in

0,

all odd numbers in 1

(a

number all

Is

represents

-

1).

But

since there are the

same number of

positive

and

nega-

tive numbers

and

zero

is

positive,

there is

one more

negative

number than

there are nonzero

positive

numbers. This is the

most

negative

number

and

it

cannot be

produced by negating any

positive

number

(its

octal

representa-

Page 9

1.1

NUMBER SYSTEM

1-5

tion

is

400000

000000

8

and

its

magnitude

is one

greater

than the

largest

positive

number).

If ones

complements

were used

for

negatives

one could read a

negative

number

by

attaching

significance

to the Os instead of

the

Is. In twos com-

plement

notation

each

negative

number is one

greater

than the

complement

of the

positive

number

of the same

magnitude,

so one can read a

negative

number

by

attaching significance

to the

rightmost

1

and

attaching signifi-

cance

to

the Os at the left of

it

(the

negative

number of

largest magnitude

has

a

1 in

only

the

sign

position).

In a

negative

integer,

Is

may

be discarded at

the

left,

just

as

leading

Os

may

be

dropped

in a

positive

integer.

In a

negative

fraction,

Os

may

be discarded at

the

right.

So

long

as

only

Os are

discarded,

the

number remains in

twos

complement

form because it still

has a 1 that

possesses

significance;

but if a

portion

including

the

rightmost

1 is

discarded,

the

remaining part

of the fraction is now

a

ones

complement.

The

computer

does not

keep

track of a

binary point

the

programmer

must

adopt

a

point

convention and

shift the

magnitude

of the result

to

con-

form

to the convention used.

Two common conventions are to

regard

a

number

as

an

integer

(binary point

at the

right)

or as a

proper

fraction

(binary point

at the

left);

in these two cases the

range

of numbers

repre-

sented

by

a

single

word is 2

35

to 2

35

-

1 or-1 to 1 2~

35

. Since

multiplica-

tion

and division make use of double

length

numbers,

there are

special

instructions

for

performing

these

operations

with

integral operands.

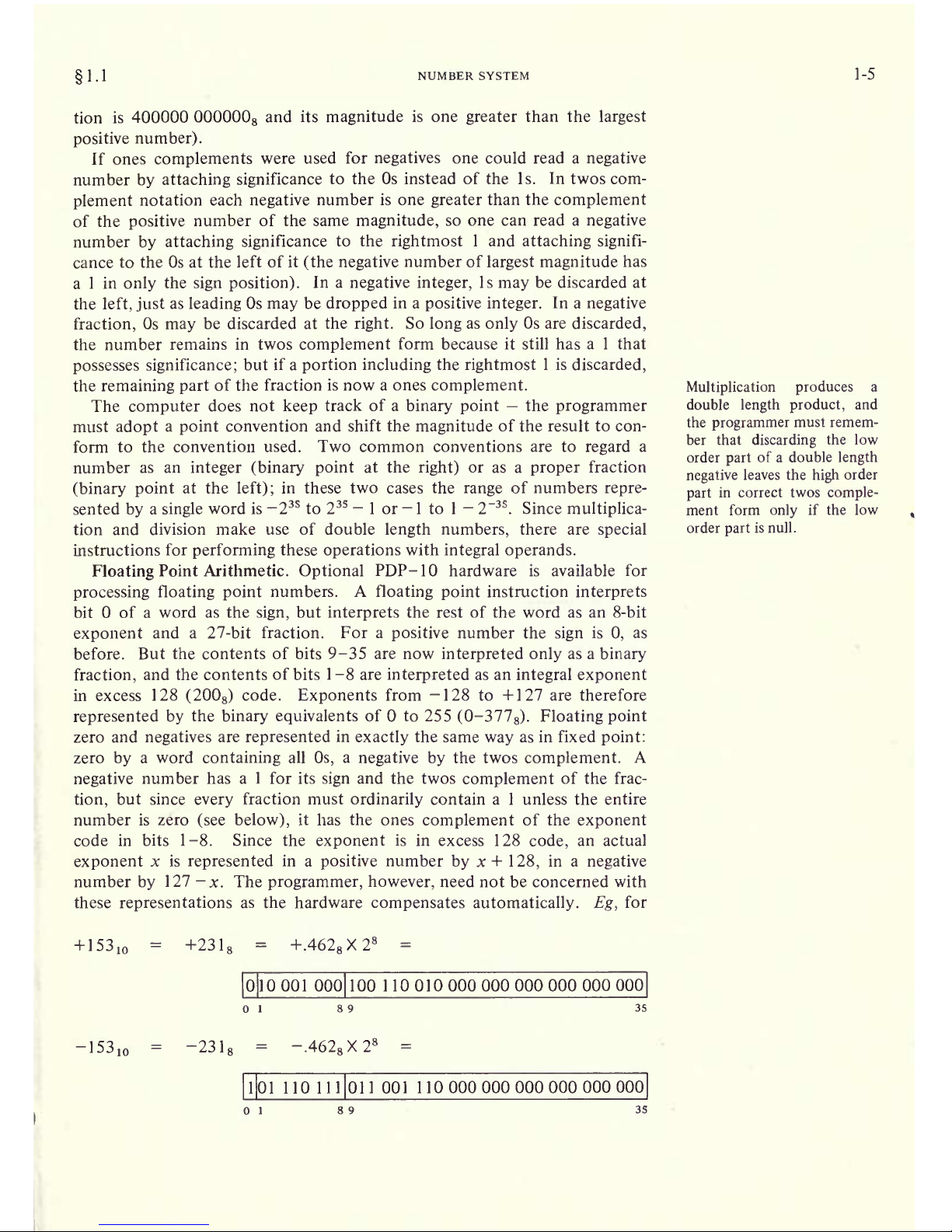

Floating

Point

Arithmetic.

Optional

PDF- 1 hardware is available for

processing

floating

point

numbers.

A

floating point

instruction

interprets

bit of a word

as the

sign,

but

interprets

the

rest

of the word as an 8-bit

exponent

and a 27-bit fraction.

For a

positive

number the

sign

is

0,

as

before.

But the contents

of

bits 9-35

are now

interpreted only

as a

binary

fraction,

and the contents

of

bits 1-8 are

interpreted

as an

integral exponent

in excess

128

(200

8

)

code.

Exponents

from -128 to +127

are

therefore

represented by

the

binary equivalents

of to 255

(0-377

8

).

Floatingpoint

zero and

negatives

are

represented

in

exactly

the same

way

as

in

fixed

point:

zero

by

a word

containing

all

Os,

a

negative by

the twos

complement.

A

negative

number

has a 1 for its

sign

and the twos

complement

of

the frac-

tion,

but since

every

fraction

must

ordinarily

contain a

1

unless the entire

number

is zero

(see below),

it has the ones

complement

of the

exponent

code

in bits 1-8. Since the

exponent

is in excess 128

code,

an

actual

exponent

x is

represented

in a

positive

number

by

x

+

128,

in a

negative

number

by

127

-x.

The

programmer,

however,

need not

be

concerned with

these

representations

as the hardware

compensates automatically. Eg,

for

+

153

10

=

+231

8

=

+.462

8

X2

8

-

Page 10

1-6

INTRODUCTION

1.2

the instruction

that

scales the

exponent,

the

hardware

interprets

the

integral

scale

factor in standard twos

complement

form

but

produces

the

correct

ones

complement

result for

the

exponent.

Except

in

special

cases

the

floating

point

instructions

assume that all

non-

zero

operands

are

normalized,

and

they

normalize a

nonzero

result. A

floating

point

number

is

considered

normalized if

the

magnitude

of

the frac-

tion

is

greater

than or

equal

to

l

/2 and less than 1

.

These numbers

thus

have a

fractional

range

in

magnitude

of

1

A.

to 1

-2"

27

and

an

exponent

range

of

-

1 28 to +127. The hardware

may

not

give

the

correct result if

the

program

supplies

an

operand

that is not

normalized or

that has a

zero fraction

with a

nonzero

exponent.

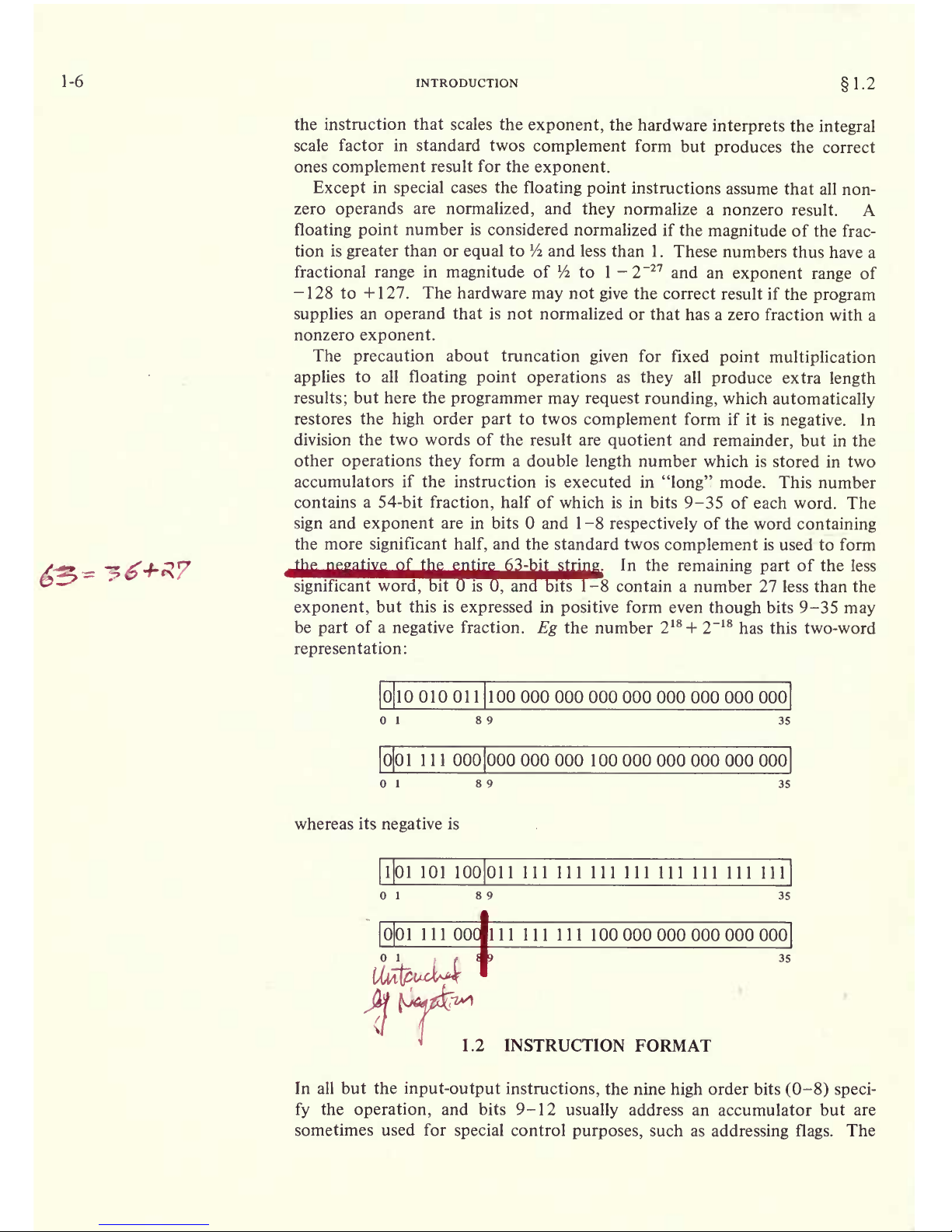

The

precaution

about truncation

given

for fixed

point

multiplication

applies

to all

floating point

operations

as

they

all

produce

extra

length

results;

but here

the

programmer

may request rounding,

which

automatically

restores the

high

order

part

to twos

complement

form if it

is

negative.

In

division the

two

words of

the result are

quotient

and

remainder,

but in the

other

operations they

form

a double

length

number which is

stored in two

accumulators

if the instruction is

executed in

"long"

mode.

This number

contains

a 54-bit

fraction,

half of which is in bits

9-35 of

each word. The

sign

and

exponent

are in bits and 1 -8

respectively

of

the word

containing

the more

significant

half,

and the standard twos

complement

is

used

to

form

In

the

remaining

part

of the

less

8 contain

a number 27

less

than

the

exponent,

but this is

expressed

in

positive

form

even

though

bits

9-35

may

be

part

of a

negative

fraction.

Eg

the

number

2

18

+

2~

18

has this

two-word

representation:

010

Page 11

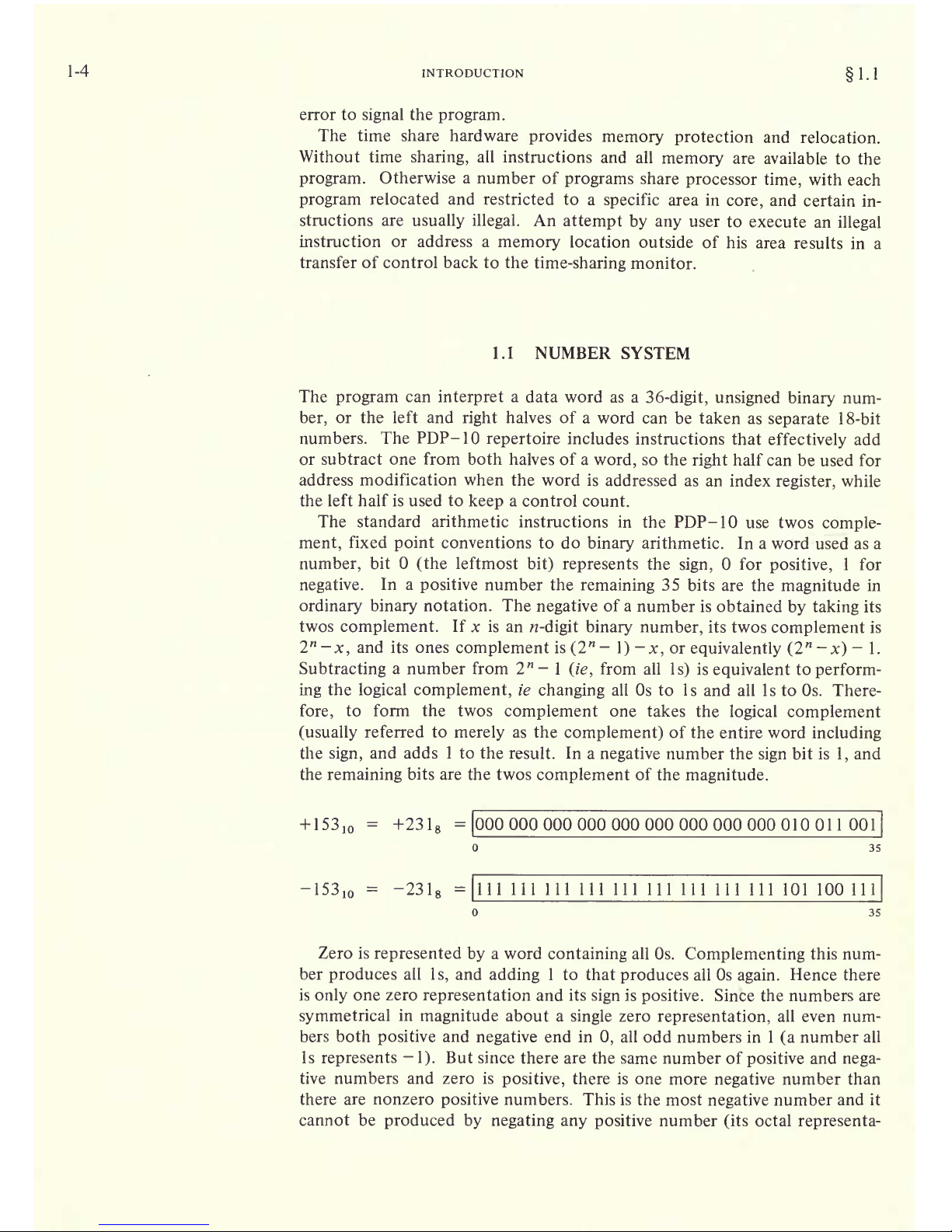

1.2

INSTRUCTION FORMAT

1-7

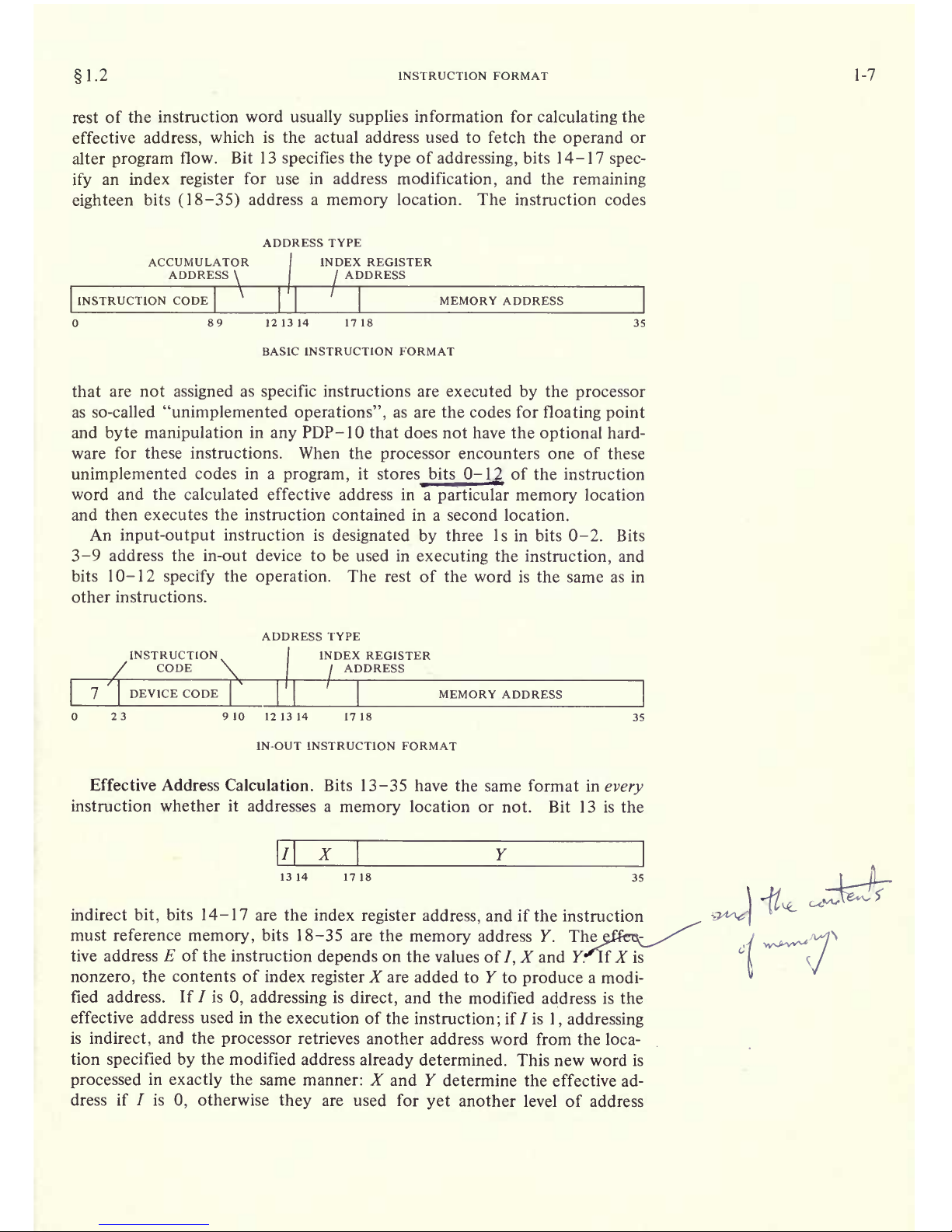

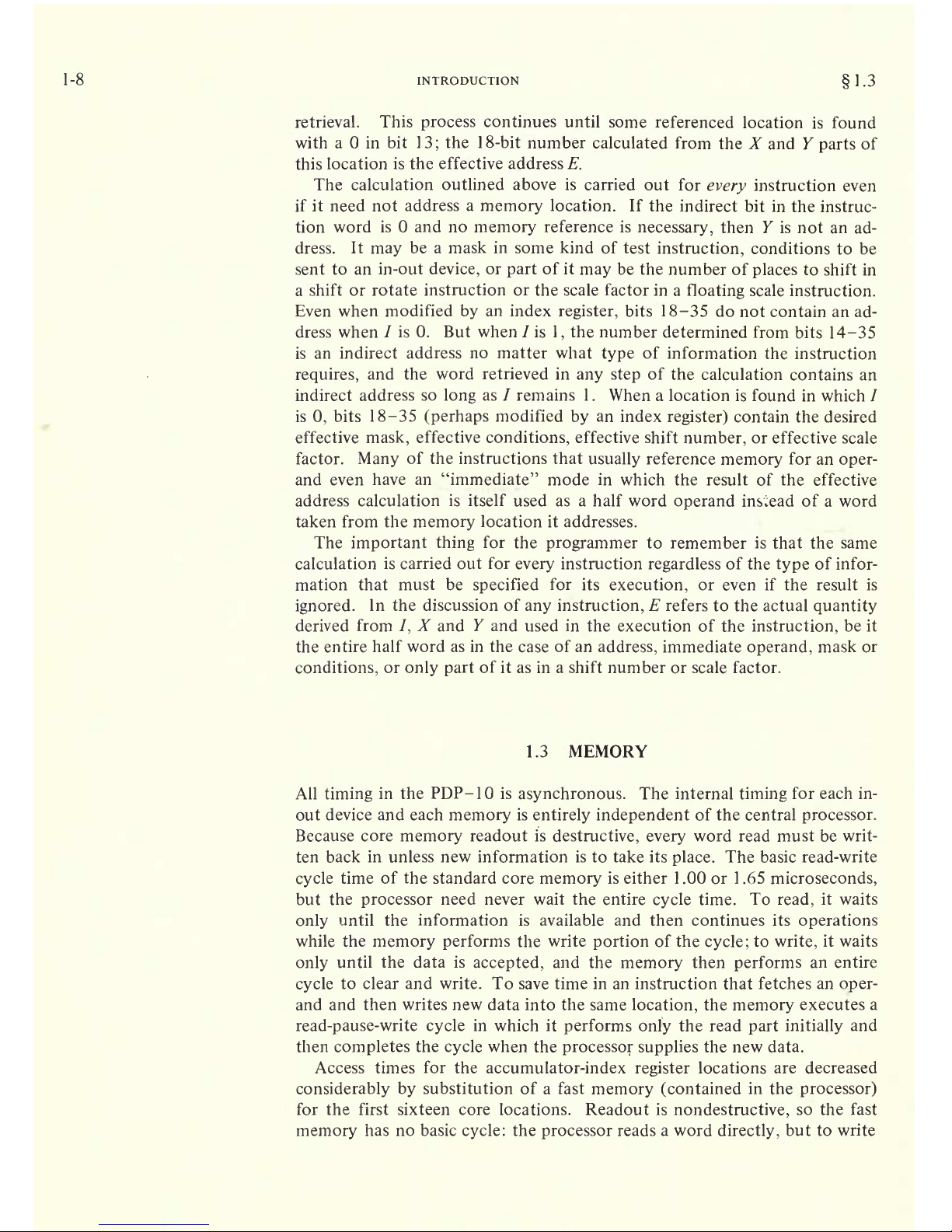

rest of

the instruction

word

usually supplies

information for

calculating

the

effective

address,

which is the actual address used to fetch

the

operand

or

alter

program

flow.

Bit 13

specifies

the

type

of

addressing,

bits 14-17

spec-

ify

an index

register

for use in address

modification,

and the

remaining

eighteen

bits

(18-35)

address

a

memory

location.

The instruction codes

ADDRESS TYPE

ACCUMULATOR

ADDRESS

\

INDEX REGISTER

ADDRESS

INSTRUCTION CODE

Page 12

1-8

INTRODUCTION

1.3

retrieval.

This

process

continues until

some

referenced

location is found

with a in bit

13;

the 18-bit

number

calculated

from the X and Y

parts

of

this

location

is

the

effective

address E.

The calculation

outlined above is

carried

out for

every

instruction

even

if

it

need

not address

a

memory

location. If

the

indirect bit in the

instruc-

tion word

is and no

memory

reference is

necessary,

then

Y

is not

an ad-

dress.

It

may

be a mask

in

some kind

of test

instruction,

conditions to be

sent

to an in-out

device,

or

part

of it

may

be the

number of

places

to shift in

a

shift or rotate instruction or the scale factor in

a

floating

scale instruction.

Even when modified

by

an index

register,

bits

18-35 do not contain an

ad-

dress

when

/ is 0.

But

when /

is

1,

the number

determined from

bits 14-35

is an

indirect address

no

matter what

type

of

information the

instruction

requires,

and

the word retrieved in

any

step

of the calculation

contains an

indirect address

so

long

as /

remains

1 .

When a

location is found in which

/

is

0,

bits 18-35

(perhaps

modified

by

an index

register)

contain the

desired

effective

mask,

effective

conditions,

effective shift

number,

or

effective scale

factor.

Many

of the

instructions

that

usually

reference

memory

for an

oper-

and even have

an

"immediate" mode in which

the result of the effective

address

calculation

is

itself used as a half word

operand

instead of a word

taken from the

memory

location it addresses.

The

important

thing

for

the

programmer

to remember

is

that the same

calculation

is carried out for

every

instruction

regardless

of the

type

of infor-

mation

that must be

specified

for its

execution,

or

even

if the

result

is

ignored.

In the discussion of

any

instruction,

E refers to the actual

quantity

derived

from

/,

X and

Y

and used in the execution of

the

instruction,

be

it

the entire

half word as in the

case

of an

address,

immediate

operand,

mask or

conditions,

or

only part

of it as in a shift

number

or

scale factor.

1.3

MEMORY

All

timing

in the PDF- 10 is

asynchronous.

The internal

timing

for each in-

out

device and each

memory

is

entirely independent

of the

central

processor.

Because core

memory

readout

is

destructive,

every

word read must be

writ-

ten back

in

unless new information

is

to take

its

place.

The basic read-write

cycle

time of the standard

core

memory

is either 1

.00

or 1

.65

microseconds,

but the

processor

need never

wait

the entire

cycle

time. To

read,

it waits

only

until the information is available and then continues its

operations

while

the

memory performs

the write

portion

of the

cycle;

to

write,

it waits

only

until

the data is

accepted,

and the

memory

then

performs

an entire

cycle

to clear and write. To

save time

in an

instruction that fetches

an

oper-

and and

then

writes new data into the same

location,

the

memory

executes

a

read-pause-write

cycle

in

which it

performs

only

the read

part

initially

and

then

completes

the

cycle

when the

processor

supplies

the new data.

Access times for the

accumulator-index

register

locations are decreased

considerably by

substitution of a fast

memory

(contained

in

the

processor)

for

the first sixteen core

locations. Readout is

nondestructive,

so the fast

memory

has no basic

cycle:

the

processor

reads

a

word

directly,

but to write

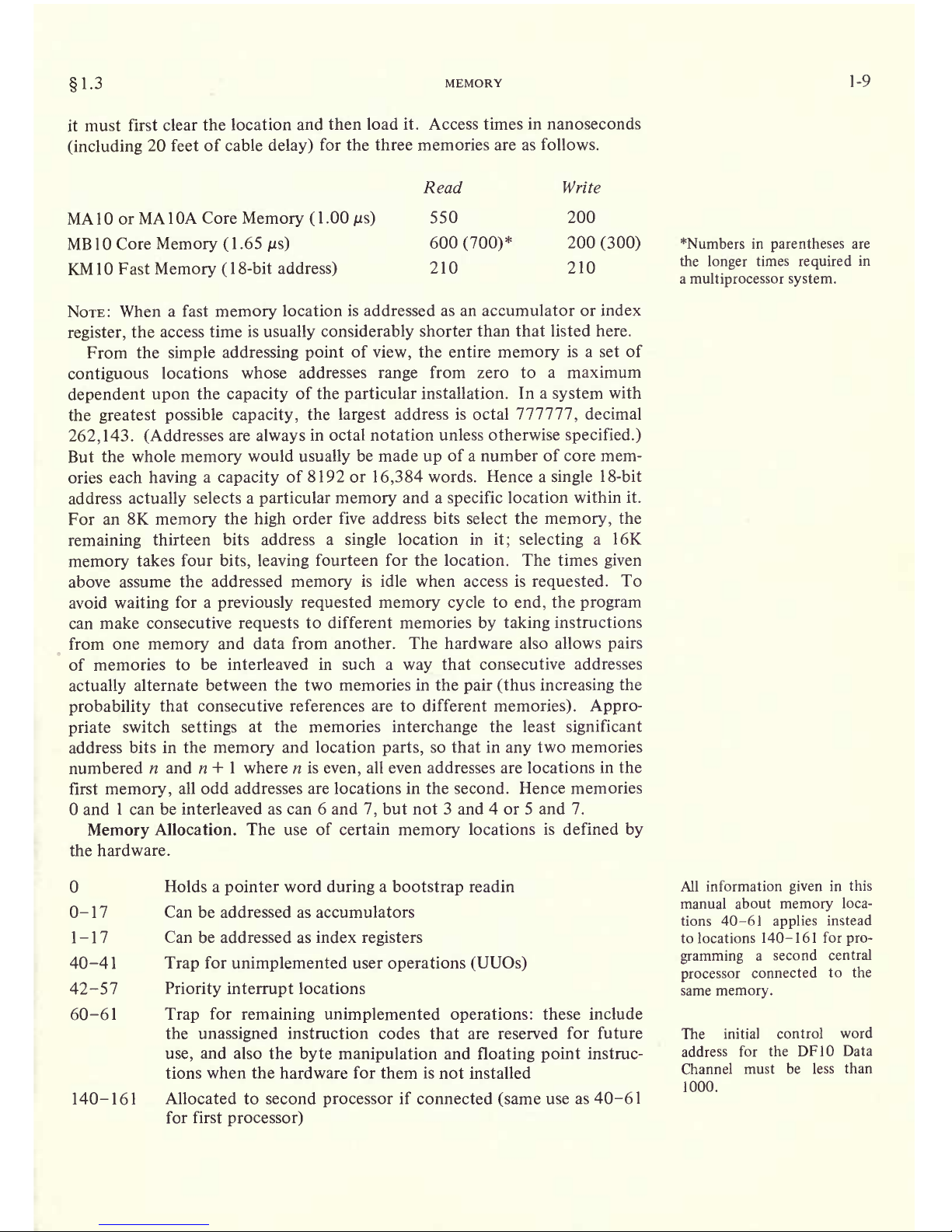

Page 13

1-3

MEMORY

1-9

it

must

first clear

the

location and

then load it. Access times

in

nanoseconds

(including

20 feet

of cable

delay)

for the

three

memories

are as follows.

MA 1 or

MA

1 OA Core

Memory

(

1 .00

jus)

MB

1

Core

Memory

(

1 .65

jus)

KM

10 Fast

Memory

(

1

8-bit

address)

Read

550

600

(700)*

210

Write

200

200

(300)

210

NOTE:

When

a fast

memory

location

is

addressed

as an

accumulator

or index

register,

the access

time

is

usually

considerably

shorter

than that listed here.

From

the

simple

addressing

point

of

view,

the entire

memory

is a set of

contiguous

locations

whose addresses

range

from zero to a maximum

dependent

upon

the

capacity

of the

particular

installation.

In a

system

with

the

greatest possible

capacity,

the

largest

address

is octal 777777

',

decimal

262,143.

(Addresses

are

always

in octal notation unless otherwise

specified.)

But

the

whole

memory

would

usually

be made

up

of a

number

of core mem-

ories each

having

a

capacity

of

8192 or

16,384

words.

Hence a

single

18-bit

address

actually

selects a

particular memory

and a

specific

location

within it.

For an

8K

memory

the

high

order five address bits select the

memory,

the

remaining

thirteen

bits address a

single

location in

it;

selecting

a 16K

memory

takes

four

bits,

leaving

fourteen

for the

location.

The times

given

above

assume

the addressed

memory

is idle when

access

is

requested.

To

avoid

waiting

for a

previously

requested memory cycle

to

end,

the

program

can

make consecutive

requests

to different memories

by taking

instructions

from one

memory

and

data from another. The hardware also allows

pairs

of memories

to

be interleaved in such a

way

that consecutive

addresses

actually

alternate between the two memories

in the

pair

(thus

increasing

the

probability

that consecutive

references are to different

memories).

Appro-

priate

switch

settings

at the memories

interchange

the least

significant

address

bits in the

memory

and

location

parts,

so that in

any

two memories

numbered

n and n

+

1

where n

is

even,

all even addresses are locations

in the

first

memory,

all odd addresses

are locations in the second. Hence memories

and

1 can be

interleaved as can 6 and

7,

but not 3 and

4

or 5 and

7.

Memory

Allocation.

The use of certain

memory

locations

is

defined

by

the

hardware.

Holds a

pointer

word

during

a

bootstrap

readin

0-17

Can be addressed as accumulators

1-17 Can

be

addressed as index

registers

40-41

Trap

for

unimplemented

user

operations

(UUOs)

42-57

Priority interrupt

locations

60-61

Trap

for

remaining

unimplemented operations:

these include

the

unassigned

instruction codes that are reserved

for future

use,

and also the

byte manipulation

and

floating

point

instruc-

tions when the hardware

for

them is not installed

140-161

Allocated

to second

processor

if

connected

(same

use as 40-61

for first

processor)

*Numbers in

parentheses

are

the

longer

times

required

in

a

multiprocessor

system.

All information

given

in

this

manual

about

memory

loca-

tions

40-61

applies

instead

to

locations

140-161 for

pro-

gramming

a

second central

processor

connected

to the

same

memory.

The

initial control

word

address

for

the DF10

Data

Channel

must be less

than

1000.

Page 14

1-10

INTRODUCTION

1.4

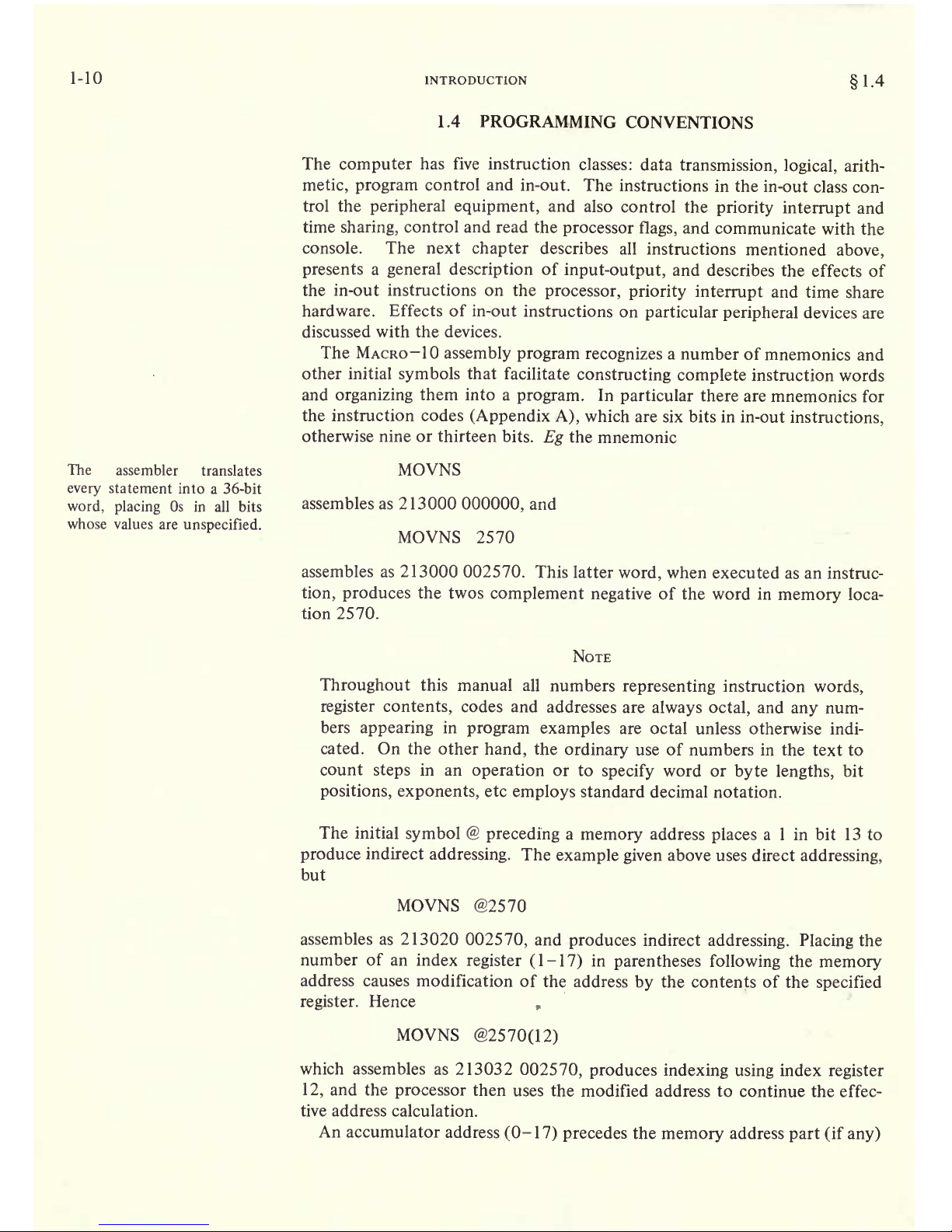

The

assembler

translates

every

statement into

a 36-bit

word,

placing

Os in all bits

whose values

are

unspecified.

1.4

PROGRAMMING

CONVENTIONS

The

computer

has five

instruction

classes:

data

transmission,

logical,

arith-

metic,

program

control and in-out.

The

instructions

in the

in-out

class con-

trol the

peripheral equipment,

and also

control

the

priority

interrupt

and

time

sharing,

control and read

the

processor

flags,

and

communicate with

the

console. The next

chapter

describes all

instructions

mentioned

above,

presents

a

general description

of

input-output,

and

describes

the

effects of

the in-out instructions on the

processor,

priority

interrupt

and

time share

hardware. Effects of in-out

instructions

on

particular

peripheral

devices are

discussed

with

the devices.

The MACRO-IO

assembly program

recognizes

a

number of

mnemonics and

other

initial

symbols

that

facilitate

constructing

complete

instruction

words

and

organizing

them into a

program.

In

particular

there are

mnemonics for

the

instruction

codes

(Appendix A),

which

are six bits in

in-out

instructions,

otherwise nine or thirteen bits.

Eg

the

mnemonic

MOVNS

assembles as 213000

000000,

and

MOVNS 2570

assembles as 213000 002570.

This

latter

word,

when executed as an

instruc-

tion,

produces

the twos

complement negative

of the

word in

memory

loca-

tion 2570.

NOTE

Throughout

this manual all

numbers

representing

instruction

words,

register contents,

codes and

addresses

are

always

octal,

and

any

num-

bers

appearing

in

program

examples

are octal

unless

otherwise indi-

cated. On

the other

hand,

the

ordinary

use of

numbers in the text to

count

steps

in an

operation

or

to

specify

word or

byte

lengths,

bit

positions, exponents,

etc

employs

standard

decimal notation.

The

initial

symbol

@

preceding

a

memory

address

places

a

1

in bit 13 to

produce

indirect

addressing.

The

example

given

above uses direct

addressing,

but

MOVNS

@2570

assembles as 213020

002570,

and

produces

indirect

addressing. Placing

the

number of an

index

register (1-17)

in

parentheses following

the

memory

address

causes

modification of

the address

by

the contents of the

specified

register.

Hence

,

MOVNS

@2570(12)

which

assembles

as

213032

002570,

produces indexing using

index

register

12,

and the

processor

then

uses

the modified

address to

continue

the

effec-

tive address

calculation.

An

accumulator

address

(0-

1

7)

precedes

the

memory

address

part

(if

any)

Page 15

1

.4

PROGRAMMING

CONVENTIONS

1-11

and

is terminated

by

a comma. Thus

MOVNS

4,@2570(12)

assembles

as 213232

002570,

which

negates

the

word in location E and

stores

the result

in both

E and in accumulator

4. The same

procedure

may

be

used

to

place

Is in bits

9-12

when

these are used for

something

other

than

addressing

an

accumulator,

but mnemonics are available

for this

pur-

pose.

The device

code in an in-out

instruction is

given

in the same

manner as an

accumulator

address

(terminated

by

a comma

and

preceding

the address

part),

but

the

number

given

must

correspond

to the octal

digits

in the word

(000-774).

Mnemonics are however

available for all standard device

codes.

To

control the

priority interrupt system

whose code

is

004,

one

may

give

CONO

4,1302

which assembles

as

700600

0001302,

or

equivalently

CONO

PI,

1302

The

programming

examples

in this manual use the

following addressing

conventions:

*

A colon

following

a

symbol

indicates that it

is a

symbolic

location name.

A:

ADD

6,5704

indicates that

the location that contains ADD

6,5704

may

be addressed

sym-

bolically

as

A.

*

The

period represents

the current

address,

eg

ADD

5,

.+2

is

equivalent

to

A:

ADD

5,A+2

4

Square

brackets

specify

the contents of a

location,

leaving

the address

of

the location

implicit

but

unspecified.

Eg

ADD

12,[7256004]

and

ADD

12,

A

A:

7256004

are

equivalent.

Anything

written at the

right

of

a semicolon is

commentary

that

explains

the

program

but

is not

part

of it.

Page 16

Page 17

Central

Processor

This

chapter

describes

all PDF- 10 instructions but does

not

discuss

the

effects

of

those in-out instructions

that address

specific peripheral

devices.

In the

description

of each

instruction,

the

mnemonic

and name

are

at the

top,

the format is in a box below

them. The mnemonic

assembles

to the

word

in the

box,

where

bits in those

parts

of the

word

represented by

letters

assemble

as Os. The letters

indicate

portions

that must

be added

to the mne-

monic

to

produce

a

complete

instruction

word.

For

many

of the non-IO

instructions,

a

description applies

not

to

a

unique

instruction

with a

single

code in bits

0-8,

but rather to an instruction set

defined

as a basic instruction

that can

be executed

in a

number of modes.

These

modes define

properties subsidiary

to the basic

operation; eg

in data

transmission the mode

specifies

which of the

locations addressed

by

the

in-

struction

is the source and which the destination of the

data,

in test instruc-

tions it

specifies

the

condition

that must be

satisfied for

a

jump

or

skip

to

take

place.

The mnemonic

given

at the

top

is for the basic

mode;

mnemonics

for

the other forms of the instruction are

produced by appending

letters

directly

to the basic

mnemonic.

Following

the

description

is a table

giving

the mnemonics

and

octal codes

(bits 0-8)

for the various modes.

The

processor

execution time for each

instruction

is

also

given

at the

top

unless

the time differs from one mode to another. The time

listed

is that

required

for direct

addressing

without

indexing

(ie

with

no effective address

calculation),

assuming

the instruction and location E

are

both in the same

1.00 microsecond core

memory,

and that an

accumulator is addressed

only

if

necessary

and is in fast

memory.

The

time that can be saved

(if

any)

by

interleaving

or

keeping

instructions

and

operands

in different memories is

indicated

either with the

description

or with

the

discussion

of the modes

preceding

a

group

of instructions. To

determine the exact time

required

for

an

instruction

under

any

circumstances,

refer to the

timing

chart

in

Appendix

C.

In a

description

E

refers to the effective

address,

half word

operand,

mask,

conditions,

shift

number or

scale factor calculated from the

/,

X

and

Y

parts

of the instruction word. In an

instruction that

ordinarily

references mem-

ory,

a reference to E as the

source

of

information means that the instruction

retrieves

the word

contained in location

E;

as a

destination it means the in-

struction stores a word in location E. In

the immediate mode of these

instructions,

the effective half

word

operand

is

usually

treated as a full word

that contains

E in

one half and zero in the

other,

and is

represented

either as

0,E

or

,0

depending

upon

whether E is in the

right

or left half.

2-1

Letters

representing

modes

are

suffixes,

which

produce

new

mnemonics that are rec-

ognized

as distinct

symbols

by

the assembler.

Page 18

2-2

CENTRAL PROCESSOR

2.1

Most of the

non-IO

instructions

can

address an

accumulator,

and in the

box

showing

the format

this

address

is

represented by

A

;

in

the

description,

"AC" refers

to the accumulator addressed

by

A . "AC

left" and "AC

right"

refer to the

two halves of AC.

If an

instruction uses two

accumulators,

these

have addresses

A and

,4

+

1,

where

the

second address is if A is

17. In some

cases

an instruction uses

an

accumulator

only

if A is

nonzero:

a

zero address

in bits

9-12

specifies

no accumulator.

It is assumed

throughout

that time

sharing

is not

in

effect,

and

the

pro-

gram

is unrestricted.

For

completeness,

however,

the

effects of restrictions

on

particular

instructions are

noted;

and execution times are

given

both for

unrestricted

operation

and

t

including relocation

in

a

user

program (the

latter

jtime

is

given

in

parentheses).

2.15 lists all restrictions on

user

programs

and

explains

the

special

effects

produced

by

certain instructions when exe-

cuted

under control

of the monitor while

the

processor

is in

user mode.

Some

simple

examples

are included

with

the instruction

descriptions,

but

more

complex

examples

using

a

variety

of instructions are

given

in 2. 1 1.

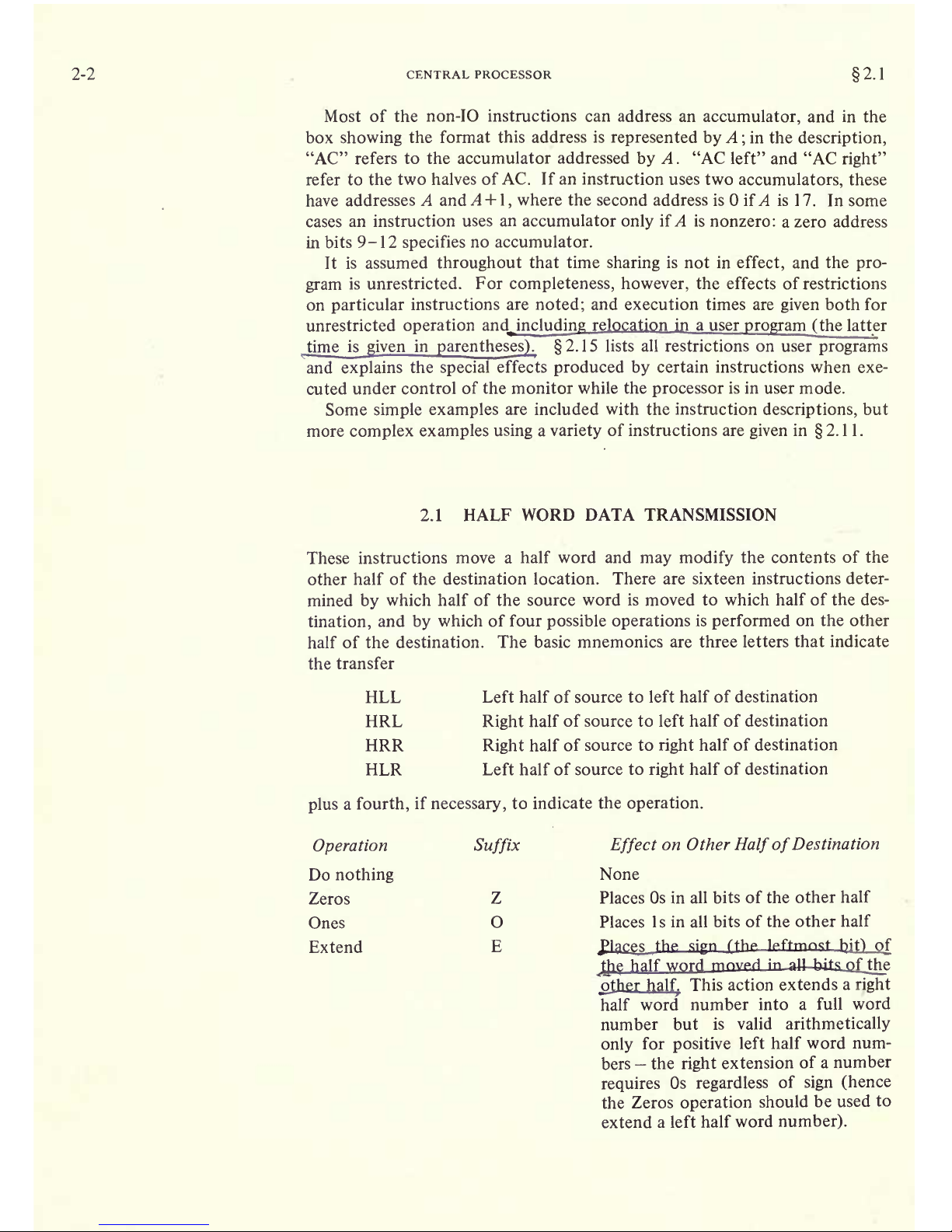

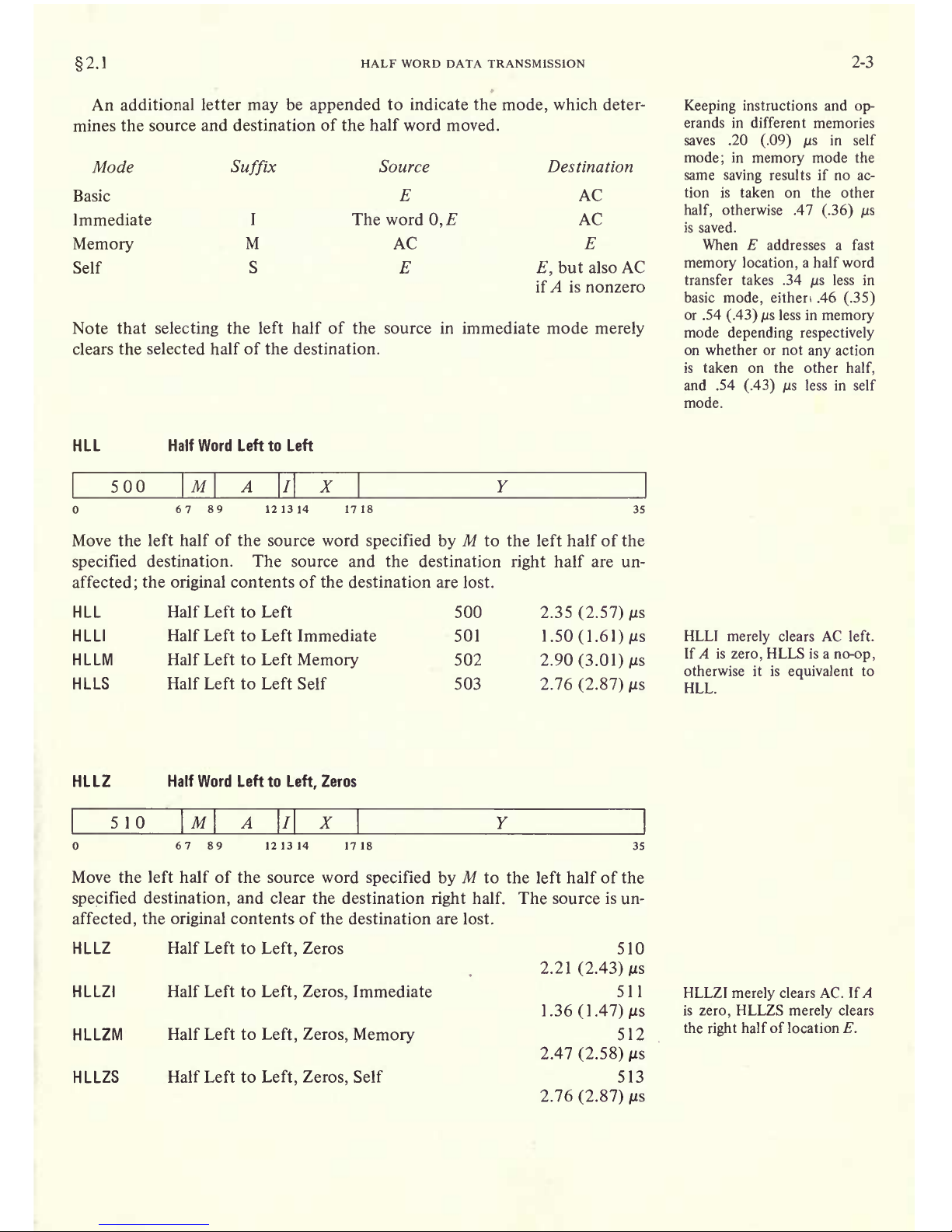

2.1

HALF WORD

DATA TRANSMISSION

These instructions

move a

half word and

may modify

the contents

of the

other

half of the destination location.

There are sixteen instructions

deter-

mined

by

which

half of the source word

is

moved

to which half of the des-

tination,

and

by

which of four

possible

operations

is

performed

on the other

half of

the destination.

The basic mnemonics

are three letters

that indicate

the

transfer

HLL Left

half

of source

to left half of destination

HRL

Right

half

of source to left half of destination

HRR

Right

half of

source to

right

half of destination

HLR

Left half of source

to

right

half of destination

plus

a

fourth,

if

necessary,

to

indicate the

operation.

Operation

Suffix

Effect

on Other

Half

of

Destination

Do

nothing

None

Zeros

Z

Places

Os in all bits of

the other

half

Ones

O

Places Is

in

all

bits of the

other half

Extend

E

Jlgces_Jh

dgn

rthp leftmost

b,jt)

nf

Qie

half

word

mnvpfl

in all

bits

pf

tjv'

other half. This action extends

a

right

half

word number

into a full

word

number but

is valid

arithmetically

only

for

positive

left

half word

num-

bers

the

right

extension

of a

number

requires

Os

regardless

of

sign

(hence

the Zeros

operation

should

be used

to

extend

a left

half word

number).

Page 19

2.1

HALF

WORD DATA TRANSMISSION

2-3

An additional

letter

may

be

appended

to

indicate the

mode,

which deter-

mines

the source

and destination of the half word moved.

Mode

Page 20

2-4

HLLOI sets AC to

all Os in

the left

half,

all

Is

in the

right.

HLLO

CENTRAL

PROCESSOR

Half Word Left to

Left,

Ones

2.1

520

Page 21

2.1

HALF

WORD

DATA

TRANSMISSION

2-5

H R

LM

Half

Right

to Left

Memory

H R LS

Half

Right

to Left

Self

506

2.90

(3.01)

MS

507

2.76

(2.87)

jus

HRLZ

Half Word

Right

to

Left,

Zeros

5

14

Page 22

2-6

CENTRAL PROCESSOR

2.:

specified

destination,

and make all

bits in

the

destination

right

half

equal

to

bit

18 of the source. The

source

is

unaffected,

the

original

contents

of the

destination

are lost.

H R

L E Half

Right

to

Left

,

Extend

HRLEI

Half

Right

to

Left, Extend,

Immediate

H R LEM Half

Right

to

Left, Extend,

Memory

HRLES Half

Right

to

Left, Extend,

Self

534

2.21

(2.43)

jus

535

1.36

(1.47)

MS

536

2.47

(2.58)

MS

537

2.76

(2.87) MS

If

A is

zero,

HRRS is

a

no-op;

otherwise

it

is

equivalent

to

HRR.

HRR

Half Word

RighttoRight

540

Page 23

2.1 HALF WORD

DATA TRANSMISSION

2-7

HRRO

Half Word

Right

to

Right,

Ones

560

Page 24

2-8

CENTRAL PROCESSOR

HLRM Half Left

to

Right

Memory

HLRS Half

Left to

Right

Self

2.1

546

547

2.90

(3.01)

2.76

(2.87)

HLRZI

merely

clears AC

and

is thus

equivalent

to HLLZI.

HLRZ

Half Word Left to

Right,

Zeros

554

Page 25

2.2

FULL

WORD DATA

TRANSMISSION

2-9

bit of

the source. The

source

is

unaffected,

the

original

contents of

the

destination

are lost.

HIRE Half Left to

Right,

Extend

HLREI Half Left to

Right,

Extend,

Immediate

HLREM Half Left

to

Right, Extend,

Memory

HIRES Half Left to

Right, Extend,

Self

574

2.21

(2.43) MS

575

1.36

(1.47)

/is

576

2.47

(2.58) jus

577

2.76

(2.87)

MS

HLREI is

equivalent

to

HLRZI

(it

merely

clears

AC).

EXAMPLES.

The

half

word transmission

instructions

are

very

useful for

handling

addresses,

and

they provide

a

convenient means of

setting

up

an

accumulator whose

right

half is to be

used for

indexing

while a control

count

is

kept

in the left half.

Eg

this

pair

of

instructions loads

the 18-bit numbers

M and N into the

left and

right

halves

respectively

of an

accumulator that is

addressed

symbolically

as XR.

HRLZI

HRRI

XR,M

XR,N

Of

course the source

program

must

somewhere define

the value of

the

symbol

XR as an octal

number

between

1

and 17.

Suppose

that at some

point

we wish to

use the two

halves of XR

inde-

pendently

as

operands

(taken

as

18-bit

positive

numbers)

for

computations.

We can

begin

by moving

XR

left

to the

right

half

of

another

accumulator

AC and

leaving

the

contents of XR

right

alone

in

XR.

HLRZM

HLLI

XR,AC

XR,

;Clear

XR left

It

is not

necessary

to clear the

other half of

XR

when load-

ing

the first half word. But

any

instruction that

modifies

the other half is faster than

the

corresponding

instruction

that does

not,

as the latter

must fetch the destination

word in

order

to

save half

of

it.

(The

difference does not

apply

to self

mode,

for here

the source and destination are

the

same.)

2.2

FULL

WORD DATA

TRANSMISSION

These

are

the

instructions

whose basic

purpose

is to

move one or

more full

words of data from

one

place

to

another,

usually

from an

accumulator to a

memory

location or

vice versa. In a

few cases

instructions

may perform

minor

arithmetic

operations,

such as

forming

the

negative

or the

magnitude

of the word

being processed.

EXCH

Exchange

2.90

(3.01)

MS

250

Page 26

2-10

CENTRAL PROCESSOR

2.2

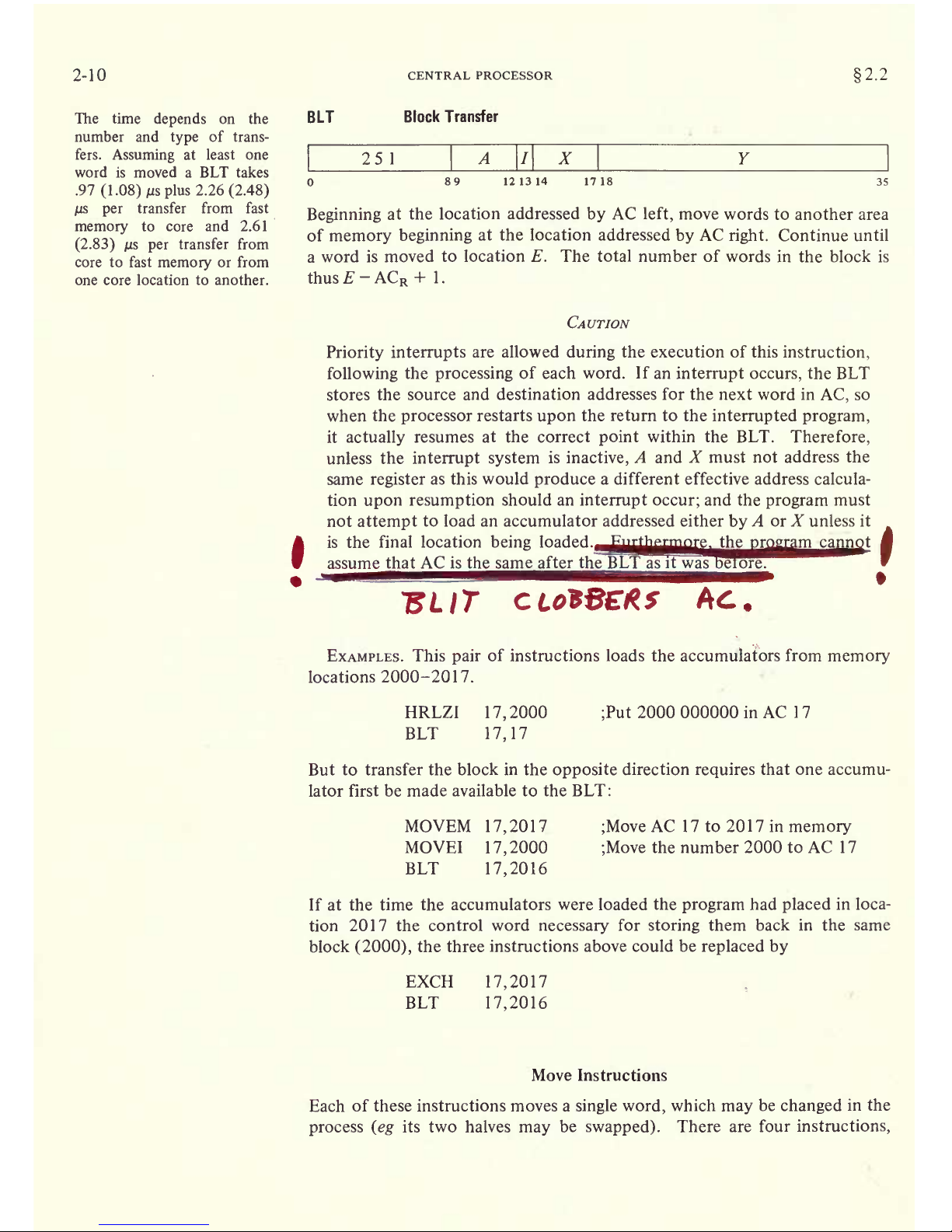

The

time

depends

on the

number and

type

of trans-

fers.

Assuming

at least one

word is moved a BLT takes

.97

(1.08)

MS

plus

2.26

(2.48)

jus

per

transfer from fast

memory

to core

and

2.61

(2.83)

us

per

transfer from

core to fast

memory

or from

one core location to another.

BLT

Block Transfer

25

1

Page 27

2.2

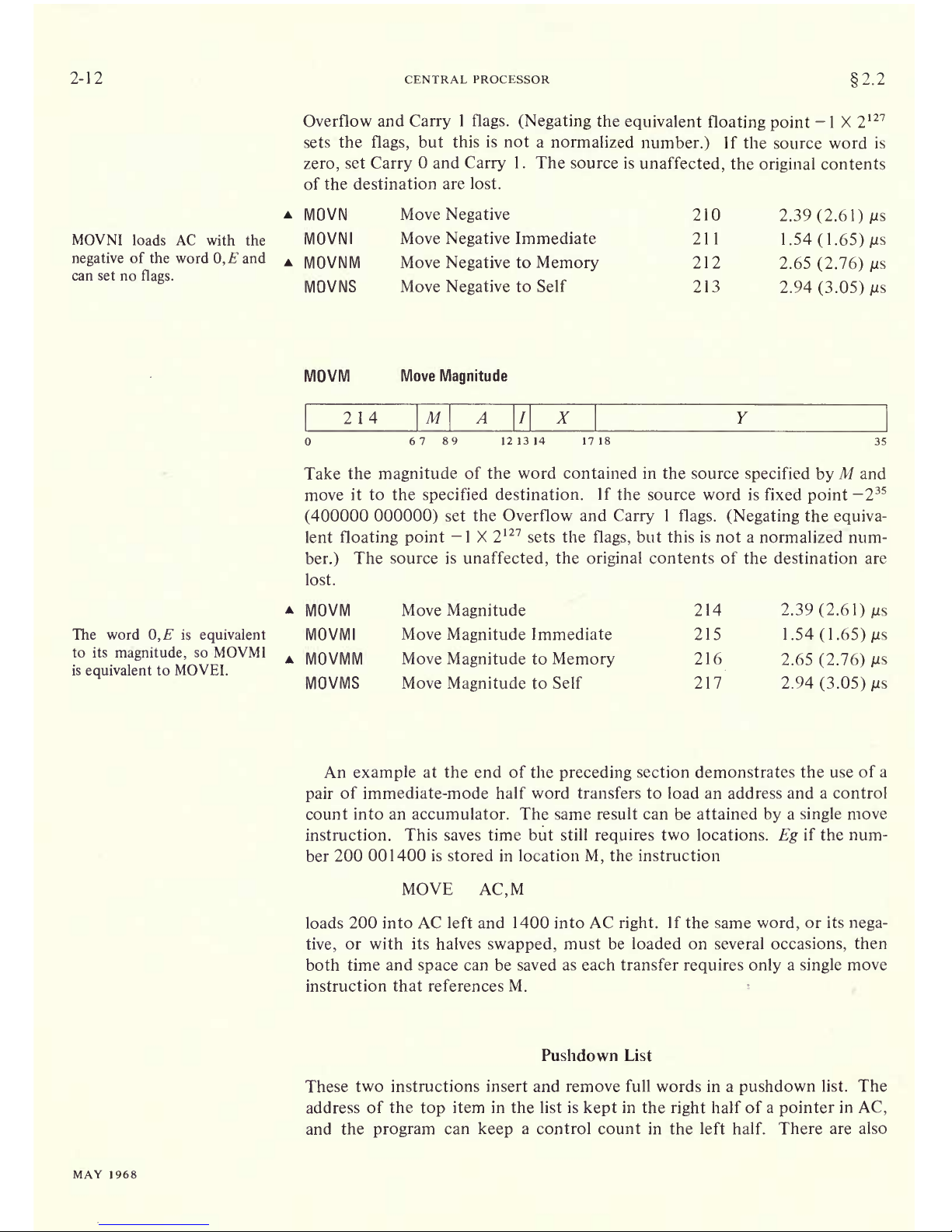

FULL WORD DATA TRANSMISSION

2-11

each

with

four

modes

that

determine

the source and destination of the word

moved.

Mode

Basic

Immediate

Memory

Self

Suffix

I

M

S

Source

E

The word

0,

AC

E

Destination

AC

AC

E

E,

but also AC

if A is nonzero

Keeping

instructions and

op-

erands

in different

memories

saves .47

(.36)

/is

in

memory

mode,

.20

(.09)

MS

in self

mode.

When

E

addresses a fast

memory

location,

a move in-

struction takes .34

MS

less in

basic

mode,

.46

(.35)

MS

less

in

memory

mode,

.54

(.43)

MS

less in self mode.

MOVE

Move

200

Page 28

2-12

CENTRAL PROCESSOR

2.:

MOVNI

loads

AC

with the

negative

of the

word

0,E

and

can set no

flags.

Overflow

and

Carry

1

flags.

(Negating

the

equivalent

floating point

-1

X

2

127

sets the

flags,

but

this is not

a

normalized

number.)

If

the source word

is

zero,

set

Carry

and

Carry

1.

The source is

unaffected,

the

original

contents

of

the destination

are lost.

MOVN

Move

Negative

MOVNI

Move

Negative

Immediate

MOVNM

Move

Negative

to

Memory

MOVNS

Move

Negative

to Self

210

2.39

(2.61)

MS

211

1.54(1.65)MS

212

2.65

(2.76) MS

213

2.94

(3.05) MS

The word

0,"

is

equivalent

to its

magnitude,

so MOVMI

is

equivalent

to MOVEI.

MOVM

Move

Magnitude

2 14

Page 29

2.2

FULL WORD

DATA TRANSMISSION

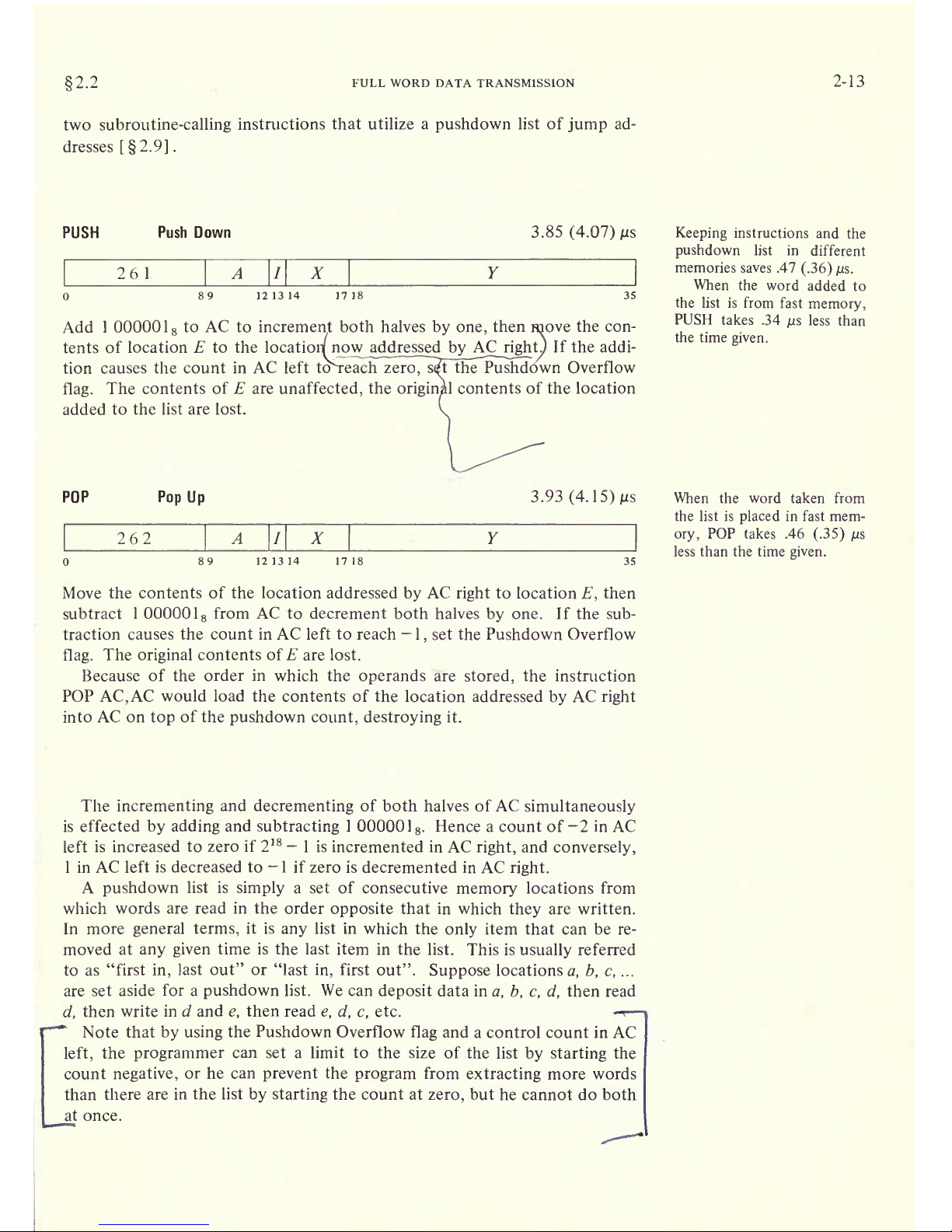

2-13

two

subroutine-calling

instructions that utilize

a

pushdown

list of

jump

ad-

dresses

[

2.9]

.

PUSH Push

Down 3.85

(4.07)

261

Page 30

2-14

CENTRAL

PROCESSOR

2.2

Pushdown

storage

is

very

convenient

for a

program

that can

use data

stored in this manner

as

the

pointer

is

initialized

only

once

and

only

one

accumulator

is

required

for the most

complex pushdown

operations.

To

ini-

tialize a

pointer

P

for a

list

to be

kept

in a

block of

memory beginning

at

BLIST and to contain

at most N

items,

the

following

suffices.

MOVSI

P,-/V

HRRI

P,BLIST-1

Of

course the

programmer

must define BLIST

elsewhere and set

aside loca-

tions

BLIST to BLIST

+

N

-

\.

Using

MACRO to full

advantage

one could

instead

give

MOVE

P,[IOWD

7V,BLIST]

where the

pseudoinstruction

IOWD

J,K

is

replaced

by

a word

containing

-J in

the left half

and K

-

1 in

the

right.

Elsewhere

there would

appear

BLIST:

BLOCK TV

which defines BLIST as the current contents of

the location counter and

sets

aside

the TV locations

beginning

at

that

point.

In the POP- 10 the

pushdown

list is

kept

in

a random access

core mem-

ory,

so the restrictions on order of

entry

and removal of items

actually apply

only

to the standard

addressing

by

the

pointer

in

pushdown

instructions

-

other

addressing

methods can

reference

any

item at

any

time. The

most

convenient

way

to do this is to use the

right

half of

the

pointer

as an index

register.

To move the last

entry

to

accumulator

AC

we need

simply

give

MOVE

AC,(P)

Of course this does not shorten the list

the word moved remains

the last

item

in it.

One

usually

regards

an

index

register

as

supplying

an additive factor for

a

basic address contained in an instruction

word,

but the

index

register

can

supply

the basic address and the instruction the additive factor. Thus we can

retrieve

the next to last

item

by

giving

MOVE

AC,-1(P)

and so

forth.

Similarly

PUSH

P,-3(P)

adds the third to last item to

the

end of the

list;

POP

P,-2(P)

removes

the last

item and inserts

it in

place

of the next to last item

in the

shortened

list.

Page 31

2.3

BYTE MANIPULATION

2-15

2.3

BYTE

MANIPULATION

This set

of five instructions allows the

programmer

to

pack

or

unpack

bytes

of

any length anywhere

within a word. Movement of a

byte

is

always

between AC and a

memory

location:

a

deposit

instruction takes

a

byte

from

the

right

end of AC and inserts

it

at

any

desired

position

in the

memory

location;

a load instruction

takes

a

byte

from

any position

in

the

memory

location

and

places

it

right-justified

in

AC.

The

byte manipulation

instructions

have the standard

memory

reference

format,

but the effective address E

is

used to retrieve

a

pointer,

which

is

used

in turn

to

locate

the

byte

or

the

place

that will

receive

it. The

pointer

has

the

format

p

Page 32

2-16

CENTRAL

PROCESSOR

2.3

Keeping

the

pointer

in fast

memory

saves .34

jus.

Taking

bytes

from a

fast

memory

location

saves

another .34

/us.

LDB

Load

Byte

4.02(4.35)

+

A5(P

+

S) [+.26]

/us

135

Page 33

2.4 LOGIC

2-17

the

right

S bits of AC

into the location and

position specified

by

the

newly

incremented

pointer.

The

original

contents of

the bits that receive the

byte

are

lost,

AC and

the

remaining

bits of

the

deposit

location are

unaffected.

Note that

in

the

pair

of

instructions that both

increment the

pointer

and

process

a

byte,

it is

the

modified

pointer

that determines

the

byte

location

and

position.

Hence to

unpack bytes

from a block of

memory,

the

program

should set

up

the

pointer

to

point

to a

byte

just

before

the

first

desired,

and

then load them with

a

loop containing

an

ILDB.

If

the

first

byte

is at

the

left end of a

word,

this is most

easily

done

by initializing

the

pointer

with a

P of 36

(44

8

).

Incrementing

then

replaces

the 36 with

36 S to

point

to the

first

byte.

At

any

time that

the

program

might

inspect

the

pointer during

execution

of

a series of

ILDBs or

IDPBs,

it

points

to the last

byte processed

(this

may

not

be true when

the

pointer

is

tested from an

interrupt

routine

[2.13]).

Special

Considerations.

If

S is

greater

than P

and also

greater

than

36,

incrementing

produces

a

new

P

equal

to

lOO-S

rather than

36-5. For

S>

36

the

byte

is at most

the entire

word;

for />

36 no

byte

is

processed

(loading

merely

clears

AC).

If both P

and

S

are

less than 36

but P

+

S >

36,

a

byte

of size 36

-

P is

loaded from

position

P. or

the'right

36

-

P

bits of the

byte

are

deposited

in

position

P.

2.4 LOGIC

For

logical

operations

the PDF-

10 has

instructions for

shifting

and

rotating

as well as for

performing

the

complete

set of

sixteen Boolean

functions

of

two variables

(including

those

in

which the

result

depends

on

only

one or

neither

variable).

The

Boolean functions

operate

bitwise on

full

words,

so

each instruction

actually performs

thirty-six logical

operations

simultane-

ously.

Thus in the

AND function of two

words,

each bit of

the

result

is

the

AND of the

corresponding

bits of

the

operands.

The

table on

page

2-23 lists

the

bit

configurations

that

result from the

various

operand

configurations

for

all instructions.

Each Boolean instruction

has four modes

that

determine

the

source of the

non-AC

operand,

if

any,

and

the destination

of the

result.

Mode

Basic

Immediate

Memory

Both

Suffix

I

M

B

Source

of

non-

AC

operand

The

word

0,

E

E

Destination

of

result

AC

AC

E

AC and E

Keeping

instructions and

op-

erands in different

memories

saves .47

(.36)

p.s

in

memory

and both

modes in the first

four of these

instructions

(those

that have no

operand

or

only

an

AC

operand),

.20

(.09)

/us

in

memory

and both

modes in the

remaining

twelve

(those

that have a

memory

or

immediate

op-

erand).

Page 34

2-18 CENTRAL PROCESSOR

2.4

A Boolean

instruction in

which E

addresses a fast

memory

location

takes .46

(.35)

M

S less in

memory

or

both mode if it

has no

oper-

and or

only

an AC

operand.

If it has

a

memory

operand,

it

takes .34

/us

less in basic

mode,

.54

(.43)

MS

less in

memory

or both

mode.

SETZ

and SETZI

are

equiva-

lent

(both

merely

clear

AC).

MACRO also

recognizes

CLEAR,

CLEARI,

CLEARM

and CLEARS

as

equivalent

to

the

set-to-zeros

mnemonics.

For an instruction without an

operand

(one

that

merely

clears a

location

or

sets it to all

Is)

the modes

differ

only

in

the

destination of

the

result,

so

basic and immediate modes

are

equivalent.

The

same

is

true

also of an

instruction

that uses

only

an AC

operand.

When

specified by

the

mode,

the

result

goes

to the accumulator

addressed

by

A,

even when

there is no AC

operand.

SETZ

Set

to Zeros

400

Page 35

2.4

SETCA

LOGIC

Set

to

Complement

of AC

450

Page 36

2-20

CENTRAL PROCESSOR

2.4

AND

And with AC

404

Page 37

2.4

ANDCB

LOGIC

And

Complements

of Both

440

Page 38

2-22

CENTRAL PROCESSOR

2.4

ORCM

Inclusive Or

Complement

of

Memory

with

AC

464

Page 39

2.4 LOGIC

2-23

EQV

Equivalence

with

AC

444

M

X

67 89

121314 1718

35

Change

the contents of the

destination

specified by

M to the

complement

of

the exclusive OR function of

the

specified

operand

and AC

(the

result has Is

wherever the

corresponding

bits of the

operands

are the

same).

EQV

Equivalence

444

2.35

(2.57)

jus

EQVI

Equivalence

Immediate

445

1.50

(1.61) jus

EQVM

Equivalence

to

Memory

446 2.90

(3.01) /us

EQVB

Equivalence

to Both

447

2.90

(3.01) jus

The

original