Digital Equipment DMO9AL, PDP-9 Instruction Manual

INSTRUCTION

DMOSA

MANUAL

ADAPTER/MUL

TIPLEXER

DIGITAL

EQUIPMENT

CORPORATION.

MAYNARD,

MASSACHUSETTS

DMDSA

DEC-09-19AA-D

ADAPTER/MUL

INSTRUCTION

TIPLEXER

MANUAL

DIGITAL

EQUIPMENT

CORPORATION.

MAYNARD.

MASSACHUSETTS

October 1968

Copyright © 1968 by Digital Equipment Corporation

The following are registered trademarks of Digital

Equipment Corporation, Maynard, Massachusetts:

DEC

FLIP

CHIP

DIGITAL

ii

PDP

FOCAL

COMPUTER

LAB

CONTENTS

Page

1 •

1 . 1

1

.2

2.

2.1

2.2

Introducti

Specifications

on

Related

Engineering Drawing References

Environmental

Power Requirements 2

Documentation

2.3 Physical

2.4

Controls

and

2.5 Performance

3.

4.

4.1

4.2

4.2.1

4.2.2

4.2.3

Installation

Principles

Basic

Detailed

Power

Internal

Single-Fast-Input

of

Operation

Indi

cators

Turn-On

Control Pulse Train 4

Cycle

1

1

2

2

2

2

2

2

3

3

3

4

4

5

4.2.4

4.2.5

5.

6.

6.1

6.2

6.3

7.

1-1

3-1

4-1

4-2

Single-Slow-Output

Double (Back

Acceptance

Maintenance

General

Delay

Module

Engineering Drawings

Basic DM09A System Block Diagram

Installation

Control Pulse Train

Control Pulse Train Time Relationship

Test

Adjustments

Complement

Diagram

to

Procedure

Circuitry

Cycle

Back) -

ILLUSTRATIONS

Fast-Output

Cycles

6

7

11

11

11

11

11

12

3

5

5

iii

CONTENTS

TABLES

(Cant)

1-1

4-1

4-2

4-3

6-1

7-1

Reference

Single-Fast-Input

Single-Slow-Output

Double

Module

Engineering

Documents

{Back

to

Back)-Fast-Output

Complement

Drawings

Cycle

Cycle

Signal Flow

Signal

Flow

Cycles

Signal Flow

1

8

9

10

12

12

iv

1 • INTRODUCTION

The DM09A

Corporation

(DEC), provides

PDP-9 memory

This document

installation,

is

fami

liar

with

via

the

operation

the

basic

Adapter/Multiplexer

an

interface

DMA

channel. A basic

an

option

to

through which

system

block

the

PDP-9 manufactured by Digital Equipment

three

I/O

diagram

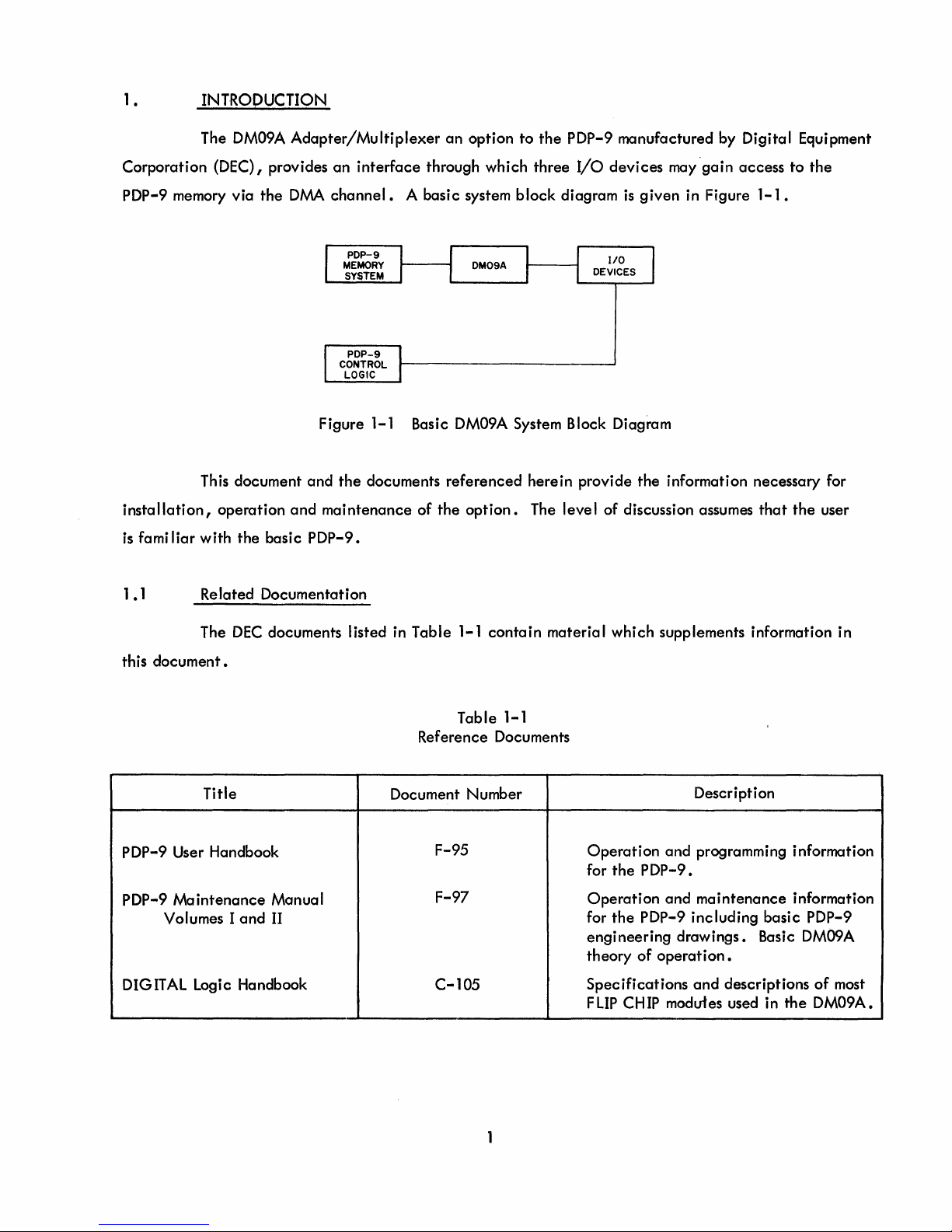

Figure 1-1 Basic DM09A System Block Diagram

and

the

and

maintenance

documents

referenced

of

the

option.

herein

provide

The level

PDP-9.

devices

of

may'gain

is

given

in Figure

the

information necessary for

discussion assumes

access

1-1.

that

to

the

the

user

1 • 1 Related Documentation

DEC

documents listed in

this

document.

The

Title

P DP-9 User Handbook

PDP-9

Maintenance

Volumes I

and

Manual

II

DIGITAL Logic Handbook

Table

1-1

contain

Table 1-1

Reference Documents

Document Number

F-95

F-97

C-105

material

Operation

for

Operation

for

engineering

theory

Specifications

FLIP

which

supplements information in

Description

and

programming information

the

PDP-9.

and

maintenance

the

PDP-9

including

drawings.

of

operation.

and

descriptions

CHIP moduies used in

information

basic

PDP-9

Basic DM09A

of

most

the

DM09A.

1

.2

Engineering Drawing References

II

be

Engineering drawings wi

referenced

using

an

abbreviated

code.

As

an

example,

drawing

D-BS-DM09-A-2,

[DM-2(2)] •

2.

2.1

Therefore,

2.2

No

additional

2.3

DMA

Adapter

Multiplexer

SPECIFICATIONS

Environmental

DM09A consists

The

entire

Iy

of

modu les

PDP-9 environmenta I spec ifications

Power Requirements

The option obtains a

power

supplies,

II

necessary

operating

power control

Physica I

The DM09A consists

entirely

of

modules which

Control,

of

the

apply

to

power from

or

fan assemblies

sheet 1 of

type used in

the

DM09A.

the

are

are

housed by two

2,

wi

II

be

referenced

the

PDP-9

centra

I processor.

PDP-9 power supply system.

necessary.

DEC

standard 1943 mount-

as

panels,

ing

tion

3,

2.4

control

2.5

thus requiring

INSTALLATION.

Controls

No

of

the

and

controls

PDP-9

or

and

PeITormance

The multiplexer

high

speed

and

thus

achieve

low speed of 3 iJS/transfer

the

speed range

applies

1 iJS/transfer.

10-1/2

Indicators

indicators

the

I/O

operates

a 1 iJS/transfer

to

permit

only

to

the

in.

of

mounting

are

associated

space.

with

devices.

at

two

speeds.

rate;

I/O

sufficient

data-line

DM09A. The PDP-9

the

I/O

devices

devices

settling

Placement of these panels

DM09A. The option

with 10

mHz

logic may request

is

is

entirely

with low speed logic should request

DMA

time.

channel

It should

and

the

be

remembered

memory require

given

in

Sec-

under

the

that

only

the

the

2

3.

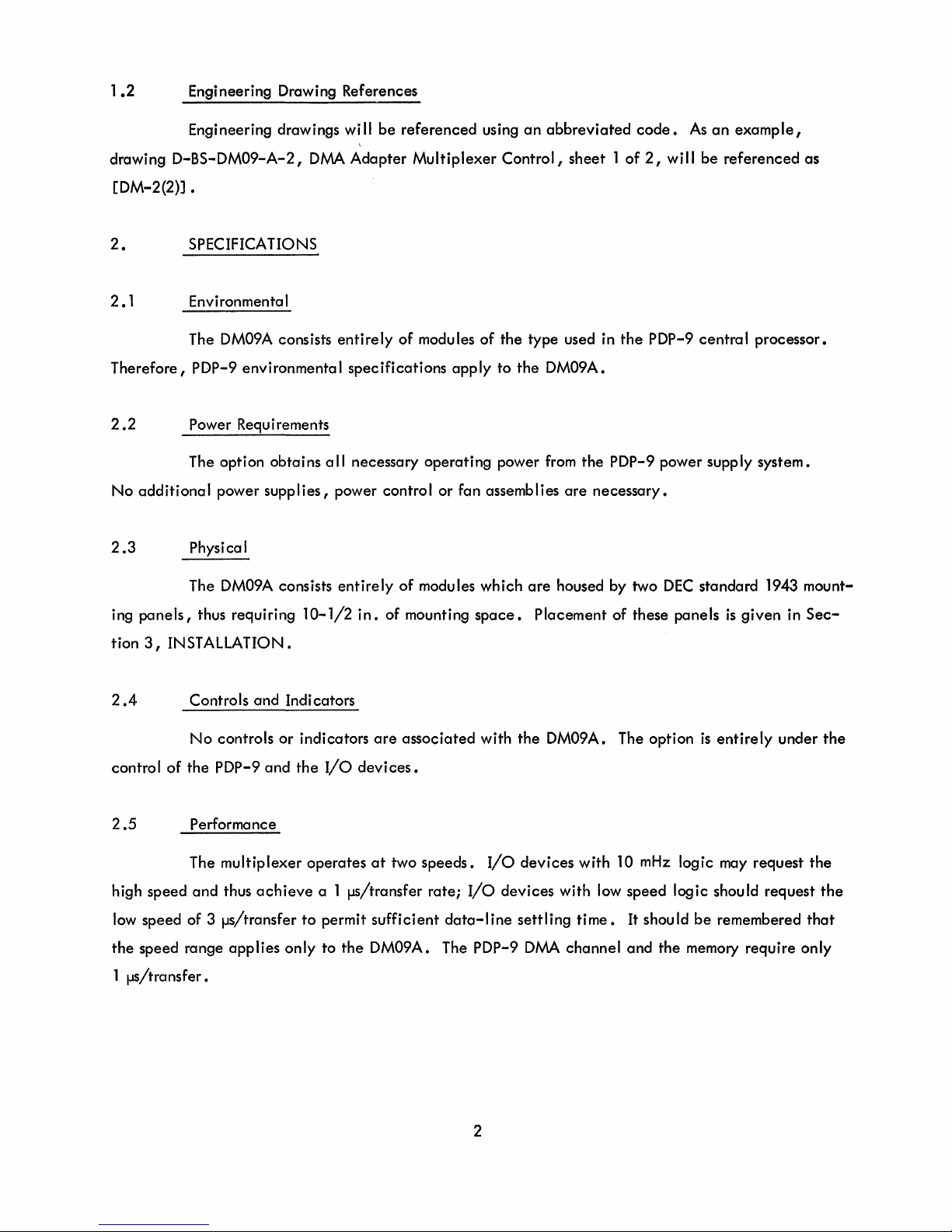

INSTALLATION

prewired

Figure

3-1

Implementation

locations in

the

•

of

the

option

basic PDP-9

Figure

involves insta

cabinet.

3-1

The

PAPER

READER AND

OPERATOR'S CONSOLE

TABLE

Insta

II

location

RESERVED

FOR

DM09A

RESERVED

FOR

ME09B

TAPE

PUNCH

Ilation

ing

the

option

in

which

Diagram

modules

the

option

into

their

preassigned,

mounts is shown in

The following

Drawing

Number

D-CD-DM09-A-9

CD-D-DM09-A-10

CD-D-DM09-A-11

4.

4.

1 Basic

Channel

is

also

PRINCIPLES

A

basic

Transfers, of

contain

in

engineering

(Rev. A)

OF

description

the

PDP-9

that

section.

drawings

Title

Memory

Interface

DM09 Memory

Cabling

Inter-Memory

OPERATION

of

DM09A logic

Maintenance

provide

Interface

Cabling

DMA

Manual,

all

Interface

PDP-9 memory.

Interface

extension

bank.

Interface

and

operation

Volume

necessary

between

between

control

between

MM09A,

can

be

1. A detailed

interface

information.

Description

the

DM09A

the

DM09A, ME09A memory

and

MM09A

the

MC70B

Band C extended

obtained

from

and

extended

basic

memory

Section

DM09A

the

basic

memory

PDP-9 memory

banks.

3.8.3,

block

DMA

diagram

This

document

describes in

detail

the

operation

3

of

the

DM09A

DMA

Adapter/Multiplexer.

4.2

Detai led

A

variety

of

transfer

type

combinations

are

possible with

the

DM09A.

To

avoid

excessive

repetition,

cyc

Ie

and

only

Doub

three

Ie

Certain

initialization

via

descriptions assume

Simi lar

operations

All transfer types

cing

with

a PDP-9

made

With

ready,

multiple

in which a

transfers,

When reading

referenced

DM-8(2) should

4.2.1

on

the

Power

When

be

Turn-On

the

types will

(Back

to

Back)-Fast-Output

DM09A

power

I/O

wi

ClK

operations

turn-on

device 0 is

II

result

pulse.

device

synchronization

the

signal flow

referenced

system

be

described

are

executed

and

when

can

be thought

interna

being

any

I DM09A control pulse

acted

other

of

Single transfers consist

is

synchronized

is

established

logic

descriptions,

tables.

for

is

first turned

In

specific

addition,

timing

on,

herein;

cyc

Single-Fast-Input

les.

regardless

upon.

device

is

acted

as consisting

to

the

PDP-9,

during

the

user should

DM09A timing

information.

PK

ClR

(power

All

of

time

of

transfer

train

reference

upon.

of

a number

states

or in which a

the

previous

refer

diagrams,

and

key

cycle,

type;

generation.

wi

II

be

of

"time

in

which

data

to

the

clear)

Single-Slow-Output

namely,

control

Transfer

made

to

I/O

device

either

data

states"

transfer

an

each

I/O

takes

transfer.

engineering

drawings

drawings DM-8(1)

pulses

arrive

at

circuitry

type

O.

commen-

device

place.

and

the

DM09A

is

control

The

operations

4.2.2

generate

system

logic

and

produce

performed

Clear

SYNC

Clear

SET

Clear

SET

Clear

DEV 0 CaNT

Clear

SLOW CYCLE A

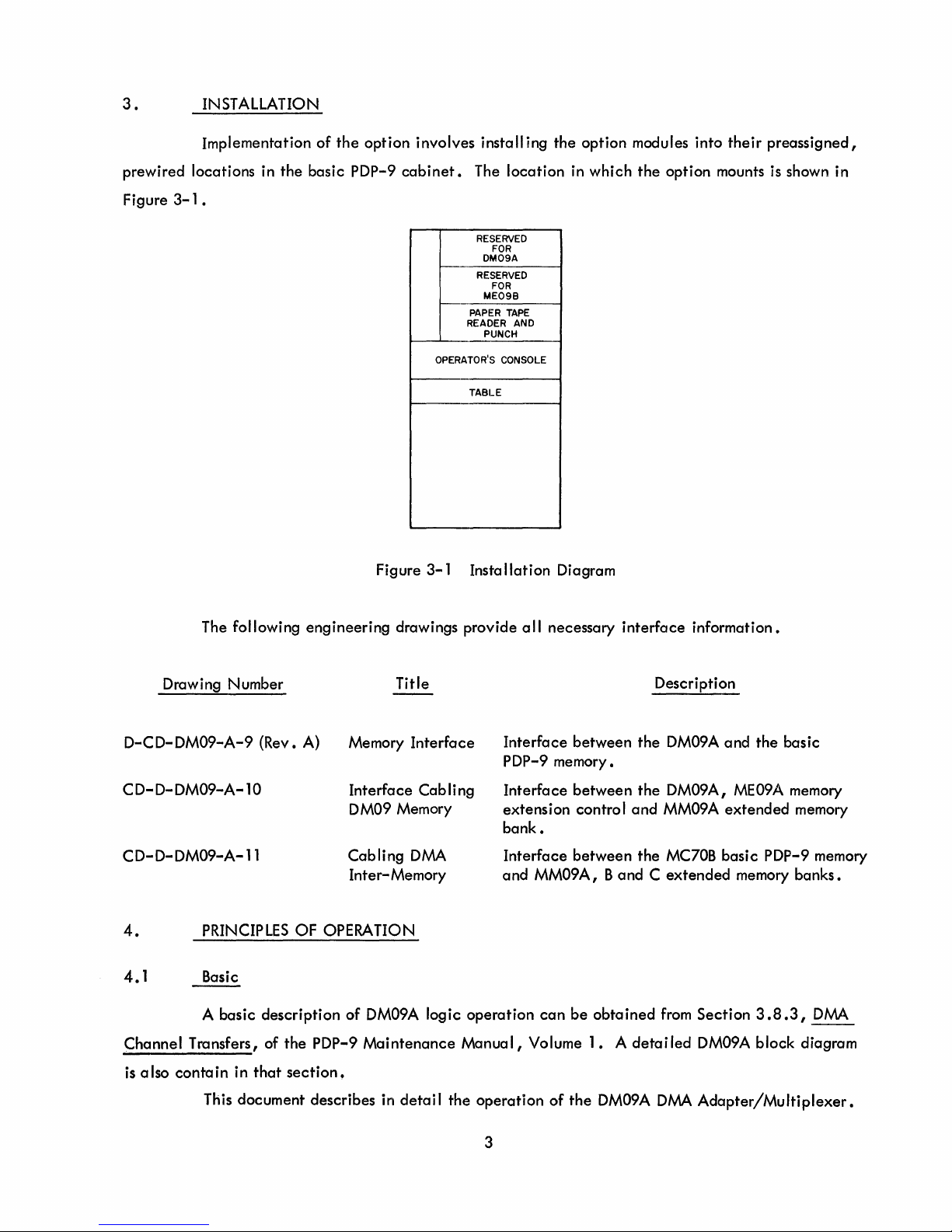

Interna I Contro I

Following

an

internal

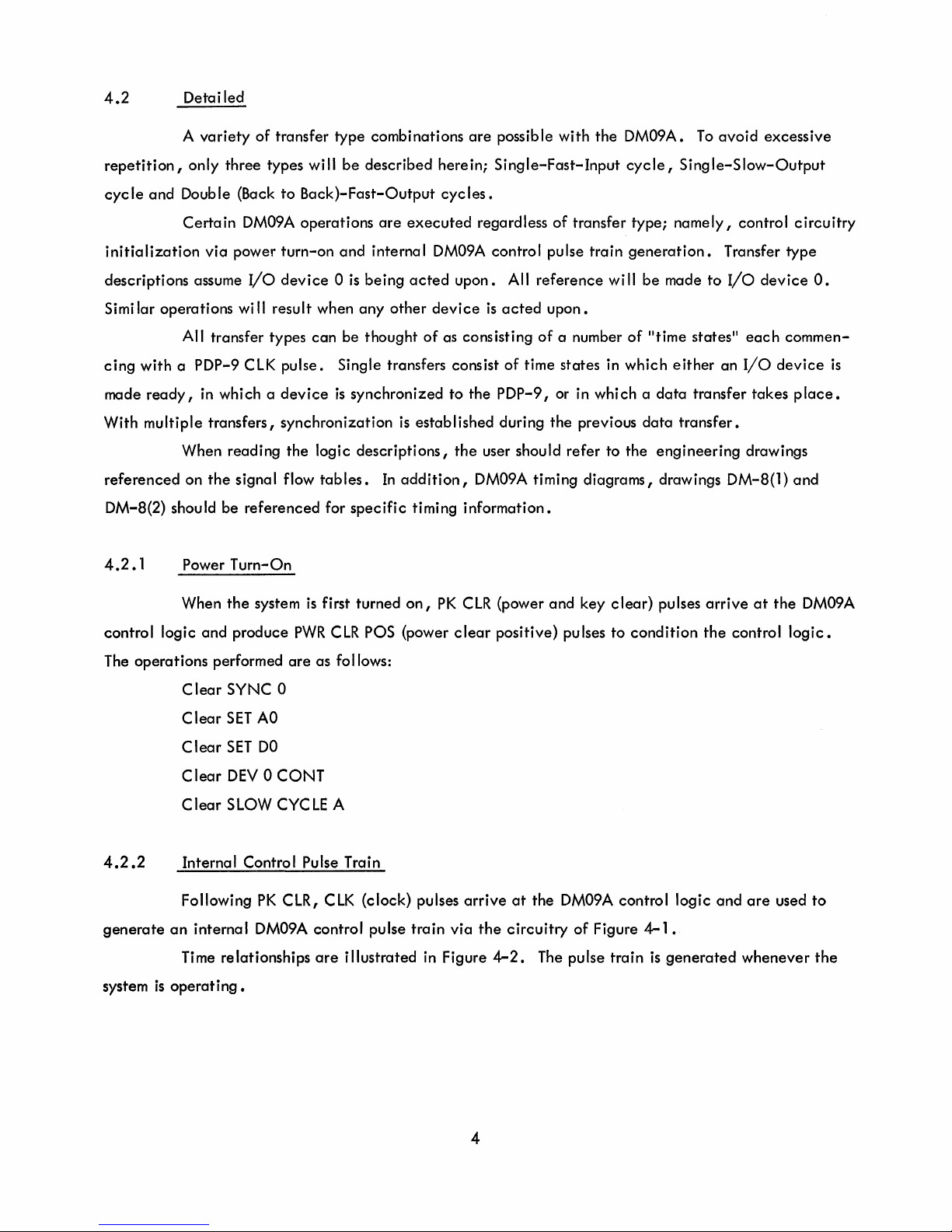

Ti

me

re lationships

is

operat i ng

AO

DO

PK

DM09A

•

PWR

are

0

Pu

ClR,

ClR

POS (power

as follows:

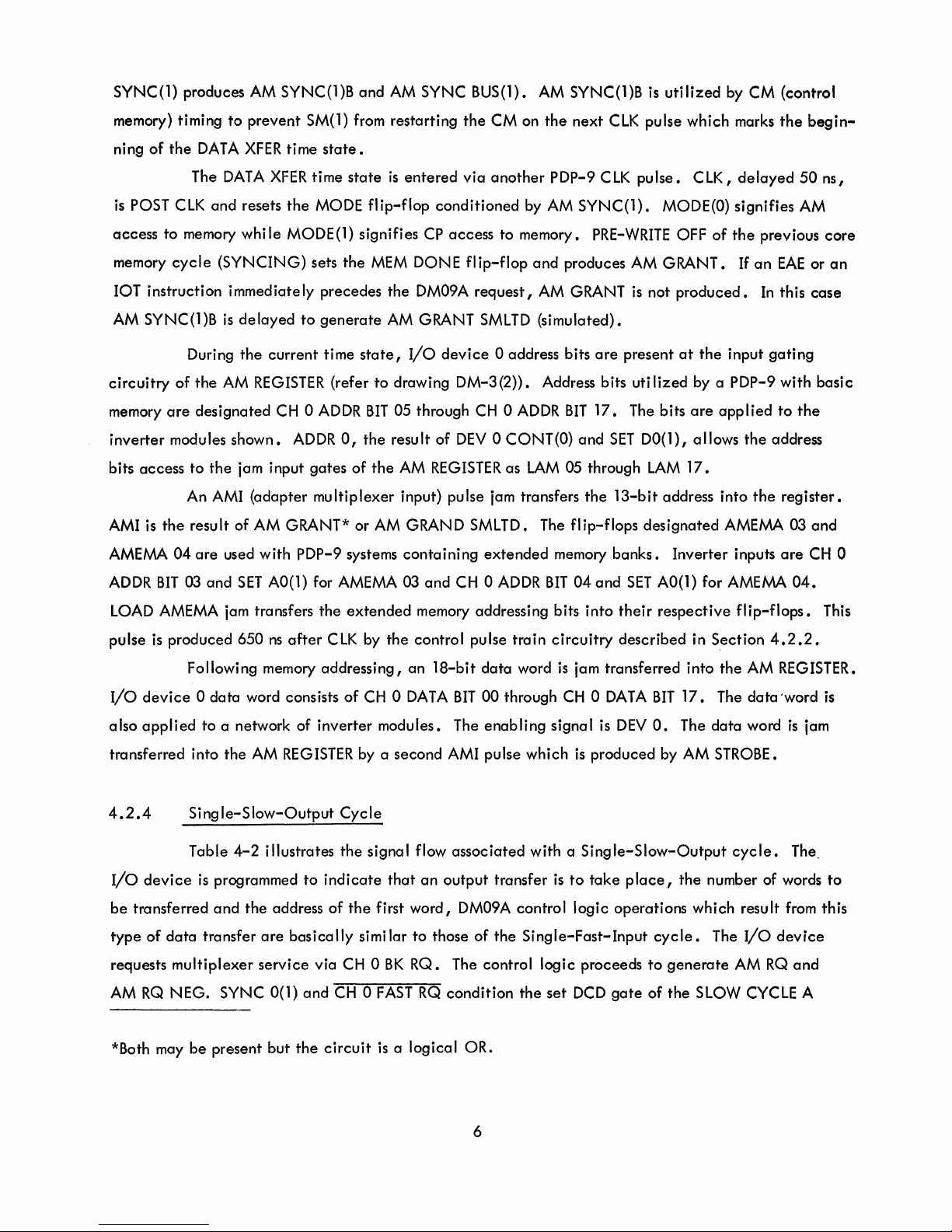

Ise T ra i n

ClK

(clock) pulses

control

are

pulse

illustrated

train

via

in Figure

clear

arrive

the

positive)

at

circuitry

4-2.

pulses

to

the DM09A control logic

of

Figure

The pulse

train

condition

4-1.

is

generated

the

and

control

are

used

whenever

logic.

to

the

4

ClK

---+---JII

150fl

WI)05

A23

W005

W005

A23

A23

u

A D

PHASE PHASE

W005

A23

D

H

o

'VA

RIll

A21

F

U

4.2.3

ClK

A PHASE

lOAD

AMEMA

D PHASE

Sing

le-Fast-Input

Figure

-----.U

I

~oons-n~------'n'---------

I

----:-1-----------'

__

!-14-------650ns----n

--'-

________

..

~----7oons----n

I

I

I

I

Figure

4-2

Cycle

4-1

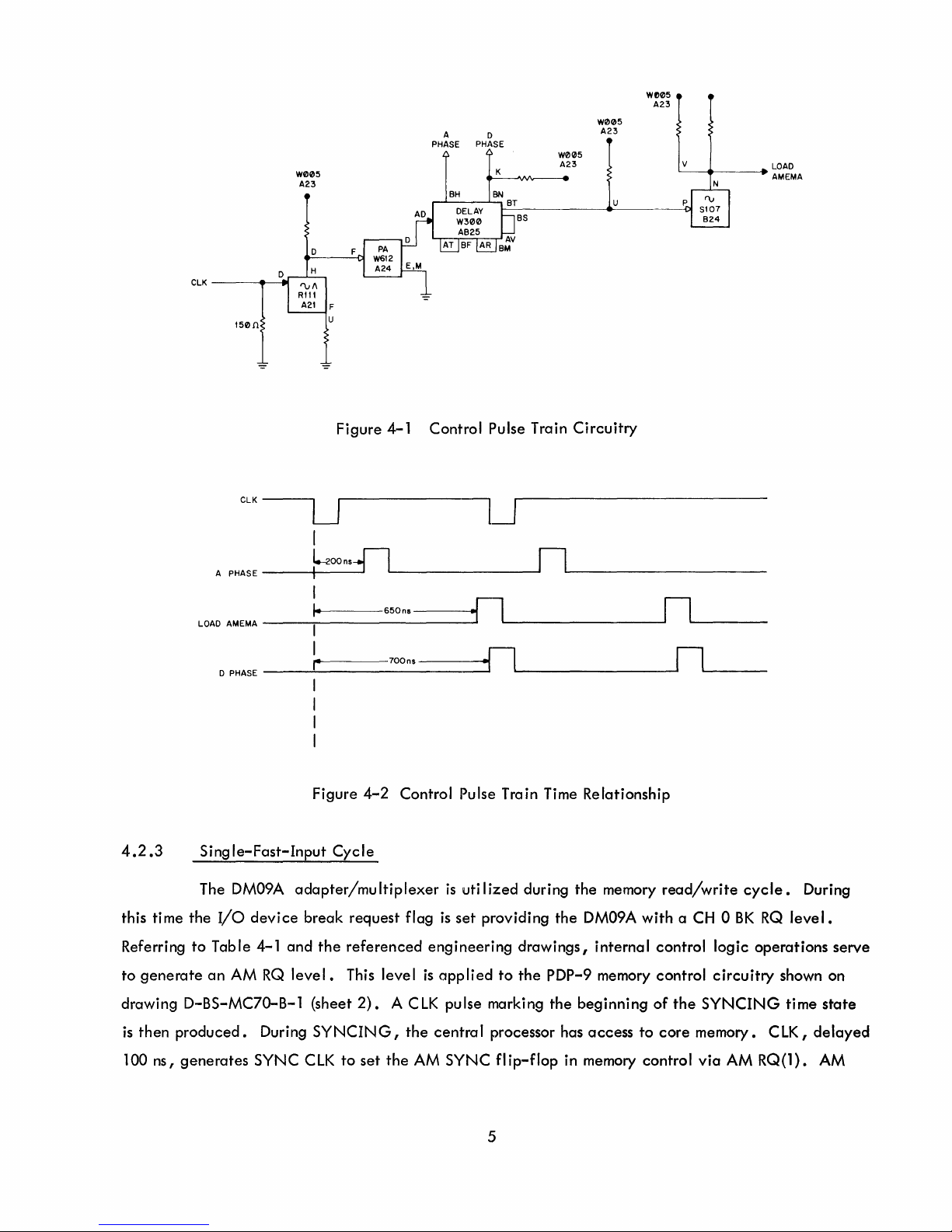

Control Pulse Train

Circuitry

U

.....

----------'

----=.J

Control Pulse Train Time Relationship

L..

________

n

--I

n

~---

L..

__

_

this time

Referring

to

generate

The DM09A

the

I/O

to

Table 4-1

an

AM

adapter/multiplexer

device

RQ

break

and

level.

the

drawing D-BS-MC70-B-1 (sheet

is

then

produced.

100

ns,

generates

During

SYNC

SYNCIN

ClK

request

referenced

This level

2). A ClK

G,

to

set

the

is

flag

is

set

engineering

is

applied

pulse marking

the

centra

AM

SYNC

uti

lized

during

providing

drawings,

to

the

I processor has

flip-flop

5

the

memory

the

DM09A

internal

PDP-9 memory

the

beginning

access

to

in memory

read/write

with

a CH 0

control

control

of

the

core

control

cycle.

BK

RQ

level.

logic

operations

circuitry

SYNCING

shown on

time

memory. C LK,

via

AM

RQ{l).

During

serve

state

delayed

AM

SYNC(l)

produces AM

SYNC(l)B

and

AM

SYNC

BUS(l).

AM

SYNC(l)B

is

utilized

by

CM

(control

memory) timing

ning

of

the

DATA

The

is

POST

ClK

access

memory

lOT

AM

to

memory whi Ie MODE (1) signifi es CP

cycle

instruction

SYNC(l)B

During

circuitry

memory

inverter

bits

are

modules

access

of

the

designated

to

An AMI

AMI is

AMEMA

the

04

result

are

to

prevent

XFER

DATA

XFER

and

resets

(SYNCING)

immediately

is

delayed

the

current

AM

REGISTER

CH 0

shown.

the

jam input

(adapter

of

AM GRANT*

used

with

SM(l)

from

time

state.

time

state

the

MODE

sets

the

precedes

to

generate

time

state,

(refer

ADDR

ADDR

gates

0,

the

of

multiplexer

or

PDP-9 systems

restarting

is

entered

flip-flop

MEM

DONE

the

DM09A

the

CM

via

another

conditioned

access

to memory.

flip-flop

request,

AM GRANT SMlTD

I/O

to

drawing

BIT

05 through

result

the

AM

device

of

REGISTER

0 address bits

DM-3(2».

CH 0 ADDR

DEY

0 CONT(O)

input) pulse jam transfers

AM GRAND

containing

SMlTD.

extended

on

the

PDP-9

by AM

and

produces AM

AM GRANT

(simulated).

Address bits uti

BIT

as

lAM

05 through

The

memory

next

ClK

ClK

SYNC(l).

PRE-WRITE

are

present

17.

and

SET

the

13-bit

flip-flops

banks.

pulse

pulse.

MODE(O)

OFF

GRANT.

is

not

produced.

at

lized

The bits

DO(1),

lAM

address

designated

Inverter

which

ClK,

of

the

by a

are

applied

allows

17.

marks

the

delayed

signifies

the

previous

If

an

EAE

In

this

input

gating

PDP-9

with

to

the

address

into

the

register.

AMEMA 03

inputs

are

begin-

50

AM

or

case

basic

the

and

CH 0

ns,

core

an

ADDR

pulse

also

BIT

lOAD

AMEMA jam transfers

is

I/O

device 0 data

applied

produced

transferred

4.2.4

I/O

device

be

transferred

type

of

data

requests

AM

multiplexer

RQ

NEG.

03

and

SET

AO(l) for AMEMA 03

650

ns

after

Following memory

word consists

to

a network

into

the

AM

of

REGISTER

Single-Slow-Output

Table

4-2

illustrates

is

programmed

and

the

transfer

address

are

basically

to

service

SYNC

0(1)

and

the

extended

ClK

by

addressing,

of

CH 0

inverter

modules.

by a

Cycle

the

signal

indicate

of

the

first

simi lar

via

CH 0

CH 0

FAST

and

CH 0

ADDR

memory addressing bits

the

control

an

DATA

second

flow

that

word,

to

BK

RQ.

an

RQ

pulse

18-bit

BIT

data

00

The

AMI pulse

associated

output

DM09A

those

of

The control

condition

through

enabling

transfer

the

BIT

04

and

SET

AO(l) for AMEMA

into

their

respective

train

word

which

circuitry

is

CH 0 DATA

signal

described

jam transferred

BIT

is

DEY

O.

is

produced

by AM STROBE.

with a Single-Slow-Output

is

to

take

place,

control

Single-Fast-Input

the

logic

set

logic

operations

proceeds

DCD

gate

cycle.

to

generate

of

the

flip-flops.

in S.ection

into

the

17.

The

The

data

4.2.2.

AM REGISTER.

data

word

cycle.

the

number of words

which

result from this

The

I/O

AM

RQ

SLOW CYCLE A

04.

'word

is

jam

The

device

and

This

is

to

be

*Both may

present

but

the

circuit

is a logical

OR.

6

flip-flop

the

this

which

multiplexer

pulse jam transfers

is

and

set

in

by

the

the

the

positive

PDP-9,

device

going

transition

an

AM GRANT pulse

supplied

address

of

into

AM RQ

is

issued

the

AM

NEG.

to

produce

register.

Following

AMI.

This

is

logic

With

not

operations

input

necessary

in

transfers,

with

the

current

cycle,

to

produce

access

transfer

to

4.2.5

DM09A

DM09A

condition

time

state

DCD

gate

sired;

the

type

of

transfer.

Following

PDP-9

AM

SAl (sense

the

jam

these

bits

Doub Ie (Back

Signal

control

that

service

the

set

sets

SYNC 0 to

to

produce

computer

The A

STROBE

input

into

flow for

logic

is

DCD

responds

PHASE

further

amplifier

are

AM

DM09A

arrives

gates

of

the

AM

register.

to

Back)-Fast-Output

the

current

CH 0

requested.

gate

of

the

establish

RQ

and

with

pulse

of

control

at

the

DM09A. This

input) thus

the

AM

BK

RQ,

This

SYNC 0 flip-flop.

device

AM

AM

SYNCING

allowing

register. A second

transfer

CH 0

signal

priority.

RQ

NEG.

SYNC(l)

logic

Cyc

type

FAST

and

B.

1 sets

operations,

pulse

PDP-9

les

is

given

RQ

and

internal

The D

This

conditions

AM RQ

SET

signals

AO

similar

is

sense

AMI pulse

in

Table

CH 0

SLOW CYCLE

PHASE

and

generates

to

gated

with

amplifier

4-3.

RQ

IN.

pulse

the

the

PDP-9

those

CH 0

bits

is

produced

Initial

CH 0

A(O)

preceding

CH 0

that

CLR

of

Single-Fast-Input

RQ

IN

and

SA

00

through

at

this

time

signals

BK

produce

FAST

a DMA

SYNC.

sent

RQsignals

SYNC

the

SYNCING

CLR

and

cycle

This

SET

SA

to

to

the

0 EN

sets

is

clears

DO(l)

17

jam

the

to

1

the

de-

SYNC

SET

EN

set

another

CLK,

XFER 1 and

the

operations,

amplifier

AM reg ister •

place

O.

SET

AO(l)

DO

fl

ip-flop.

The following D

which

again

AM REGISTER. During

with

A PHASE,

because

AM RQ

the

to

jam

signa

flip-flop

The

PDP-9

SYNCING 2 time

and

syncing

AM

STROBE

bits,

SA

DATA

transfer

XFER

and

AM

SYNC(l)B

PHASE

maintains

SLOW CYCLE

I.

Because

remains

00

set.

produced

these

operations

arrives

through SA '17,

2 is

entered.

the

data

bits

generate

pulse sets

SLOW CYCLE A(O), a

A(O)

and

this

signal

AM GRANT

states

are

time

for

from

the

access

SET

of

the

CH 0

entered.

states

the

next

PDP-9

AO

second

SET

is

arrives

the

through

is

SET

DO.

BK

RQ

applied

at

The pulse

data

data

and

generates

cleared

word

DO

EN

SET

AO(l)

are

to

the

the

multiplexer

transfer

transfer

the

AM

and

into

the

which

characteristic

sti

PDP-9

jam-transfers

take

SAl

register

operations

conditions

and

SET

II

present.

AM

control

associated

pla.ce.

and

AMI,

gating

AM

register.

the

DO(l)

of

fast

Setting

SYNC

circuitry

address

with

the

thus a Ilowi ng

circuitry

simi lar to

The D

set

DCD

gate

produce

transfers.

fl

ip-flop

DATA

CLR

SLW

SYNC 0 is

SYNC 0 generates

prior

as

the

information

preceding

and

PHASE

syncing

the

sense

into

XFER 1 take

pulse

of

CYC

to

SYNC

DATA

into

the

at

the

the

end

of

the

current

ti me

state

c I

ears

SET

DO.

7

Time

Control

State

Pulse

D

PHASE

SYNCING A

PHASE

D

PHASE

DATA

XFER

A

PHASE

D

PHASE

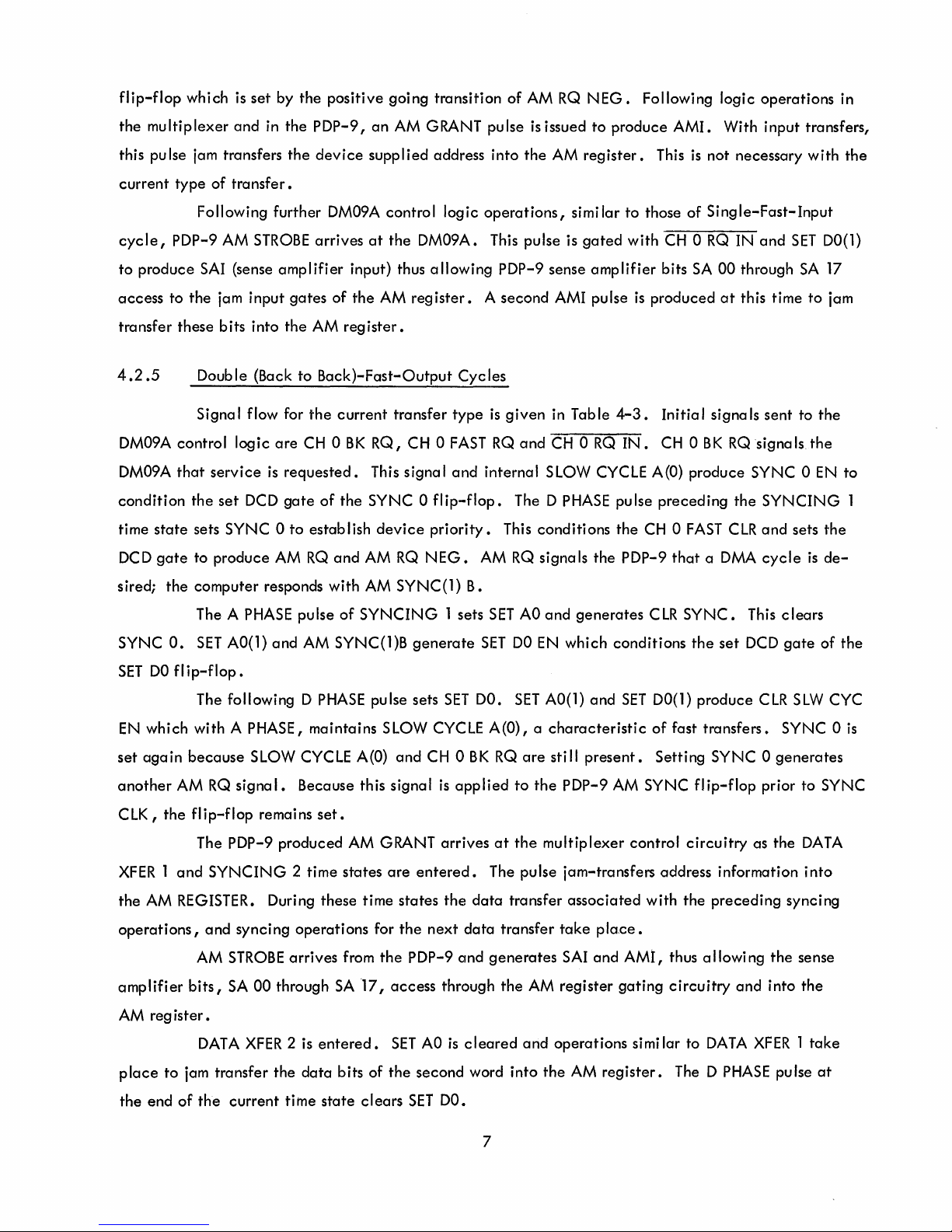

Table 4-1

Single-Fast-Input Cycle Signal

Flow

Signal Conditions

SYNC 0

EN

CH 0 BK

RQ * SLOW

CYCLE

A(O)

SYNC 0(1)

D

PHASE

* SYNC 0

EN

AM

RQ

SYNC 0(1)

AM

SYNC(l)B

From

PDP-9

SET

AO(l)

A

PHASE

* SYNC 0(1)

CLR

SYNC A

PHASE * AM

SYNC(l

)B(B)

SET

DO

EN

AM

SYNC(l)B *

SET

AO

(1)

CH 0 FAST

CLR

CLR

SYNC * SYNC 0

(1)

SYNC 0(0)

SYNC

0(1) *

CLR

SYNC

SET

DO(l)

D

PHASE * SET

DO

EN

CLR

SLW

CYC

EN

SET

AO(O) * SET

DO(l)

AM

GRANT

From

PDP-9

CH 0 ADDR

ACC

A

PHASE * SET

AO(l) *

SET

DO(l)

IN

DEV

0 CONT(l)

CH 0 ADDR

ACC

IN * SET

DO(l)

DEVICE

0

DEV

0 CONT(l) *

SET

DO(l) * CH 0 RQ

IN

SET

AO

(0)

A

PHASE

* SYNC 0(0) *

SET

DO(l)

CH 0 ADDR

ACC

CH 0 AD

DR

ACC

IN

SLOW

CYCLE

A(O)

A

PHASE * CLR

SLW

CYC

EN

AM

STROBE

From

PDP-9

CH 0 DATA

RDY

D

PHASE * SET

DO(l) * SLOW

CYCLE

D(O)

IN

INH 0

DAP(O)

CH 0 DATA

RDY

IN

CH 0 DATA

RDY

CH 0 DATA

RDY

IN

CH 0 DATA

ACC

DPHASE

*CH

ORQIN * INHODAP(O)*SETDO(l)

SET

DO(O)

D

PHASE * SET

AO(O) * SLOW

CYCLE

D(O)

Drawing

Number

DM-2(2)

DM-2(1)

DM-2(2)

MC-1

(2)

DM-2(1)

DM-2(2)

DM-2(2)

DM-2(1)

DM-2(1)

DM-2(1)

DM-2(1)

MC-1

(2)

DM-2(1)

DM-2(1)

DM-2(2)

DM-2(1)

DM-2(1)

DM-2(1)

MC-2

DM-2(2)

DM-2(2)

DM-2(2)

DM-2(l)

DM-2(1)

Loading...

Loading...