Page 1

Xilinx University Program

Virtex-II Pro Development

System

Hardware Reference Manual

UG069 (v1.0) March 8, 2005

R

Page 2

R

"Xilinx" and the Xilinx logo shown above are registered trademarks of Xilinx, Inc. Any rights not expressly granted herein are reserved.

CoolRunner, RocketChips, Rocket IP, Spartan, StateBENCH, StateCAD, Virtex, XACT, XC2064, XC3090, XC4005, and XC5210 are

registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

ACE Controller, ACE Flash, A.K.A. Speed, Alliance Series, AllianceCORE, Bencher, ChipScope, Configurable Logic Cell, CORE Generator,

CoreLINX, Dual Block, EZTag, Fast CLK, Fast CONNECT, Fast FLASH, FastMap, Fast Zero Power, Foundation, Gigabit Speeds...and

Beyond!, HardWire, HDL Bencher, IRL, J Drive, JBits, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroBlaze, MicroVia,

MultiLINX, NanoBlaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, Real-PCI, RocketIO, SelectIO, SelectRAM, SelectRAM+,

Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, SMARTswitch, System ACE, Testbench In A Minute, TrueMap, UIM, VectorMaze,

VersaBlock, VersaRing, Virtex-II Pro, Virtex-II EasyPath, Wave Table, WebFITTER, WebPACK, WebPOWERED, XABEL, XACTFloorplanner, XACT-Performance, XACTstep Advanced, XACTstep Foundry, XAM, XAPP, X-BLOX +, XC designated products, XChecker,

XDM, XEPLD, Xilinx Foundation Series, Xilinx XDTV, Xinfo, XSI, XtremeDSP and ZERO+ are trademarks of Xilinx, Inc.

The Programmable Logic Company is a service mark of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey

any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any

time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for

the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx provides any design, code, or

information shown or described herein “as is.” By providing the design, code, or information as one possible implementation of a feature,

application, or standard, Xilinx makes no representation that such implementation is free from any claims of infringement. You are

responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with

respect to the adequacy of any such implementation, including but not limited to any warranties or representations that the implementation

is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose. Xilinx, Inc. devices

and products are protected under U.S. Patents. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown

or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to

correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability

for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without

the written consent of the appropriate Xilinx officer is prohibited.

The contents of this manual are owned and copyrighted by Xilinx. Copyright 1994-2005 Xilinx, Inc. All Rights Reserved. Except as stated

herein, none of the material may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form

or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent

of Xilinx. Any unauthorized use of any material contained in this manual may violate copyright laws, trademark laws, the laws of privacy and

publicity, and communications regulations and statutes.

XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

The following table shows the revision history for this document.

Version Revision

03/08/05 1.0 Initial Xilinx release. (DRAFT)

XUP Virtex-II Pro Development System www.xilinx.com UG069 (v1.0) March 8, 2005

Page 3

Contents

Chapter 1: XUP Virtex-II Pro Development System

Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

General Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Board Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Virtex-II Pro FPGA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Power Supplies and FPGA Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Multi-Gigabit Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

System RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

System ACE Compact Flash Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Fast Ethernet Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

User LEDs, Switches, and Push Buttons. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Expansion Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

XSGA Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

AC97 Audio CODEC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

CPU Trace and Debug Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

USB 2 Programming Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Chapter 2: Using the System

Configuring the Power Supplies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Configuring the FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Clock Generation and Distribution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Using the DIMM Module DDR SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Using the XSGA Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Using the AC97 Audio CODEC and Power Amp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Using the LEDs and Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Using the Expansion Headers and Digilent Expansion Connectors . . . . . . . . . . . 44

Using the CPU Debug Port and CPU Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Using the Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Using the Fast Ethernet Network Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Using System ACE Controllers for Non-Volatile Storage. . . . . . . . . . . . . . . . . . . . . 65

Using the Multi-Gigabit Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

UG069 (v1.0) March 8, 2005 www.xilinx.com XUP Virtex-II Pro Development System

Page 4

Appendix A: Configuring the FPGA from the Embedded USB

Configuration Port

Appendix B: Programming the Platform FLASH PROM User Area

Appendix C: Restoring the Golden FPGA Configuration

Appendix D: Using the Golden FPGA Configuration for System Self-

Test

Hardware-Based Tests. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Power Supply and RESET Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Additional Hardware Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Clock, Push Button, DIP Switch, LED, and Audio Amp Test . . . . . . . . . . . . . . . . . . . . 99

Additional Hardware Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

SVGA Gray Scale Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Additional Hardware Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

SVGA Color Output Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Additional Hardware Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Silicon Serial Number and PS/2 Serial Port Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Additional Hardware Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Processor-Based Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Additional Hardware Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

MGT Serial ATA Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Additional Hardware Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

EMAC Web Server Test. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Additional Hardware Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

EMAC Web Server Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

AC97 Audio Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Additional Hardware Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Digital Passthrough Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

FIFO Loopback Test Procedure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Game Sounds Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

System ACE Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

System ACE Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

DDR SDRAM Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Additional Hardware Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Expansion Port Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Additional Hardware Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

XUP Virtex-II Pro Development System www.xilinx.com UG069 (v1.0) March 8, 2005

Page 5

Appendix E: User Constraint Files (UCF)

Appendix F: Links to the Component Data Sheets

FPGA Related Documentation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Configuration Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

DDR SDRAM Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Audio Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

XSGA Video Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Ethernet Networking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Power Supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

UG069 (v1.0) March 8, 2005 www.xilinx.com XUP Virtex-II Pro Development System

Page 6

XUP Virtex-II Pro Development System www.xilinx.com UG069 (v1.0) March 8, 2005

Page 7

Figures

Chapter 1: XUP Virtex-II Pro Development System

Figure 1-1: XUP Virtex-II Pro Development System Block Diagram . . . . . . . . . . . . . . . . . 14

Figure 1-2: XUP Virtex-II Pro Development System Board Photo. . . . . . . . . . . . . . . . . . . . 15

Figure 1-3: I/O Bank Connections to Peripheral Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Chapter 2: Using the System

Figure 2-1: Typical Switching Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 2-2: MGT Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 2-3: Configuration Data Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 2-4: External Differential Clock Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 2-5: Alternate Clock Input Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 2-6: Definition of Start and Stop Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 2-7: Acknowledge Response from Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 2-8: EEPROM Sequential Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 2-9: EEPROM Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 2-10: Clock Generation for the DDR SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 2-11: XSGA Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 2-12: AC97 Audio CODEC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 2-13: Audio Power Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

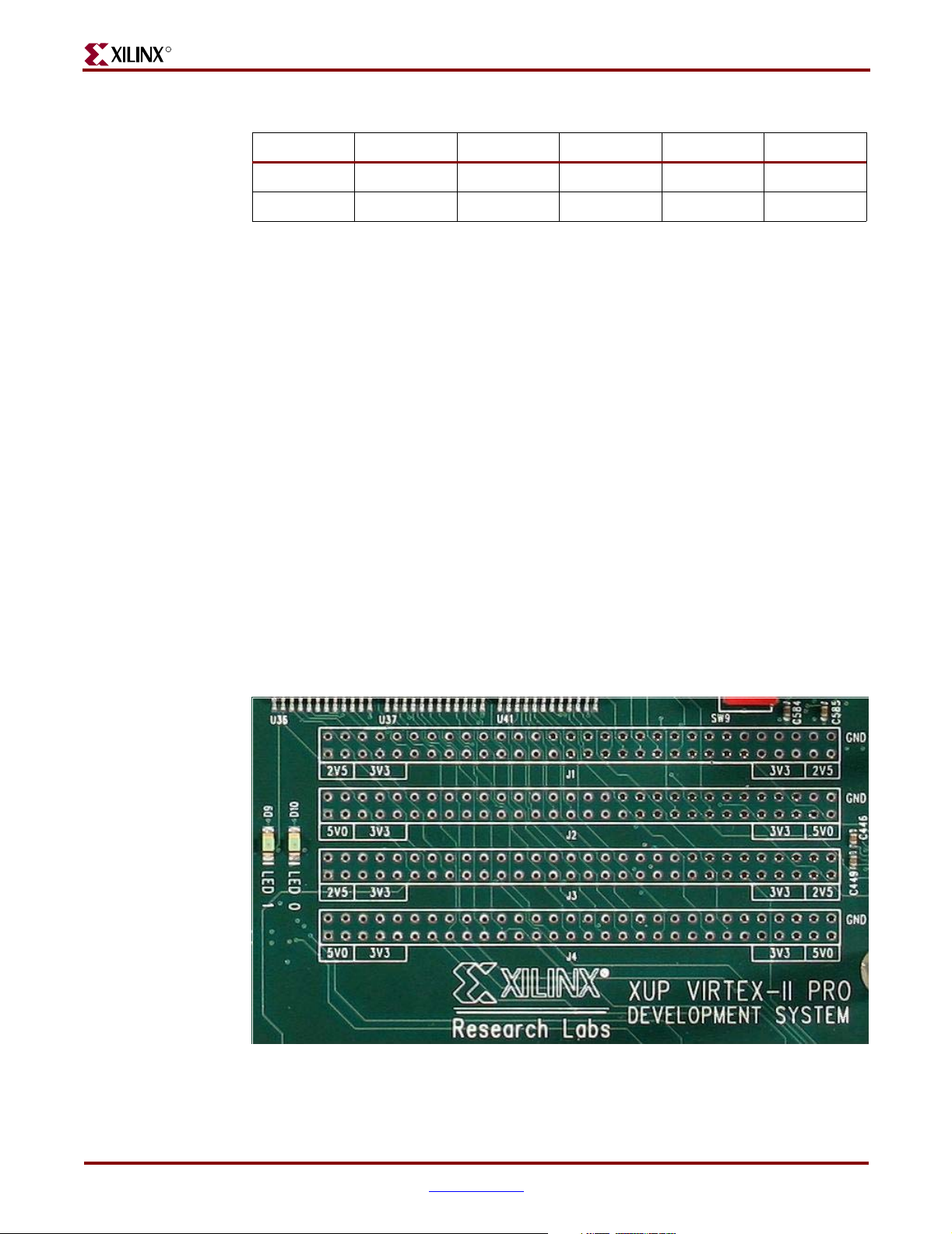

Figure 2-14: Expansion Headers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 2-15: CPU Debug Connector Pinouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 2-16: RELOAD and CPU RESET Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Figure 2-17: RS-232 Serial Port Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 2-18: PS/2 Serial Port Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 2-19: 10/100 Ethernet Interface Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 2-20: SMA-based MGT Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

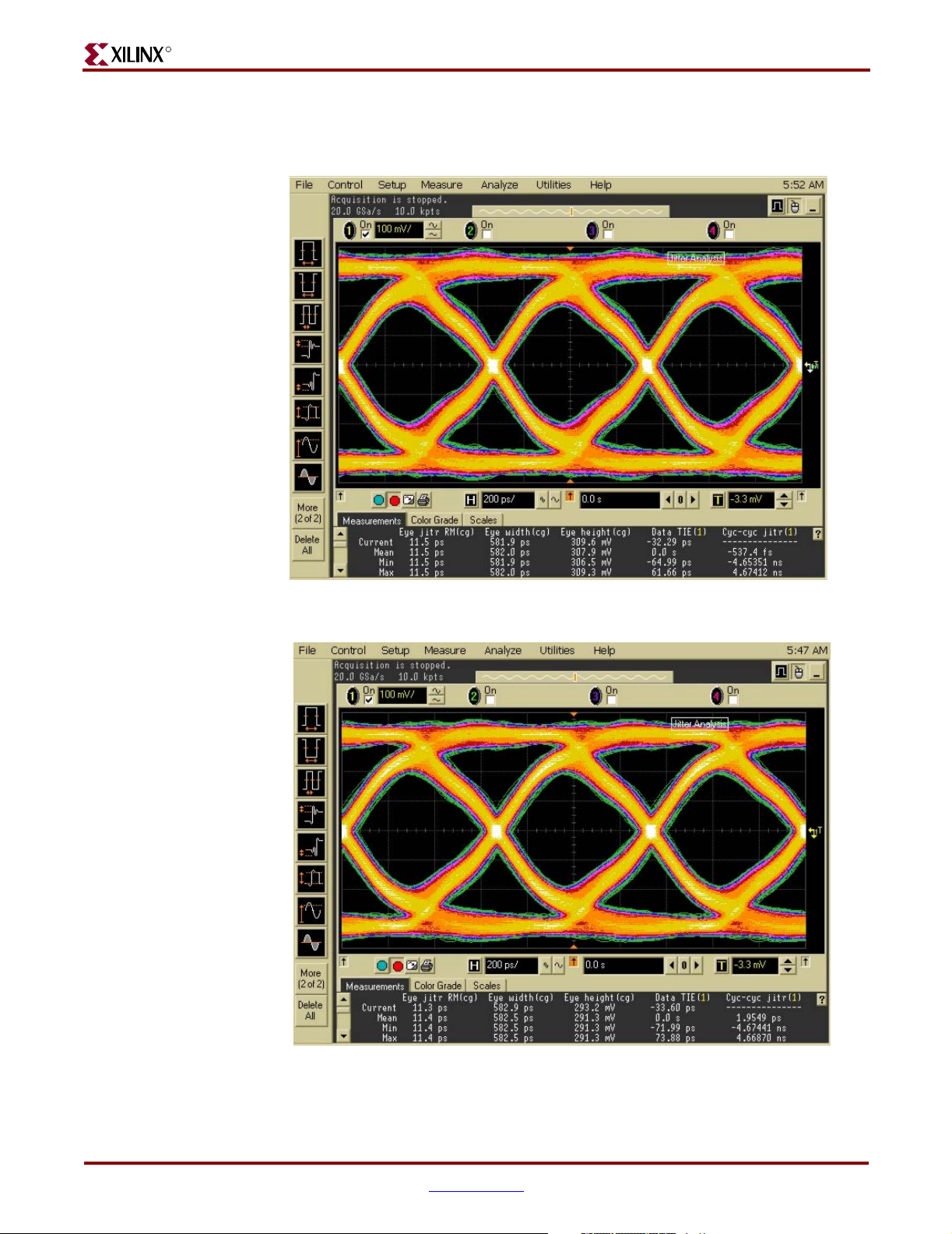

Figure 2-21: 1.5 Gb/s Serial Data Transmission over 0.5 meter of SATA Cable . . . . . . . . 70

Figure 2-22: 1.5 Gb/s Serial Data Transmission over 1.0 meter of SATA Cable . . . . . . . . 70

Appendix A: Configuring the FPGA from the Embedded USB

Configuration Port

Figure A-1: Device Manager Cable Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure A-2: iMPACT Cable Selection Drop-Down Menu . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure A-3: iMPACT Cable Communication Setup Dialog . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure A-4: Initializing the JTAG Chain. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure A-5: Properly Identified JTAG Configuration Chain . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure A-6: Assigning Configuration Files to Devices in the JTAG Chain . . . . . . . . . . . . 75

Figure A-7: Assigning a Configuration File to the FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

UG069 (v1.0) March 8, 2005 www.xilinx.com XUP Virtex-II Pro Development System

Page 8

Figure A-8: Programming the FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Appendix B: Programming the Platform FLASH PROM User Area

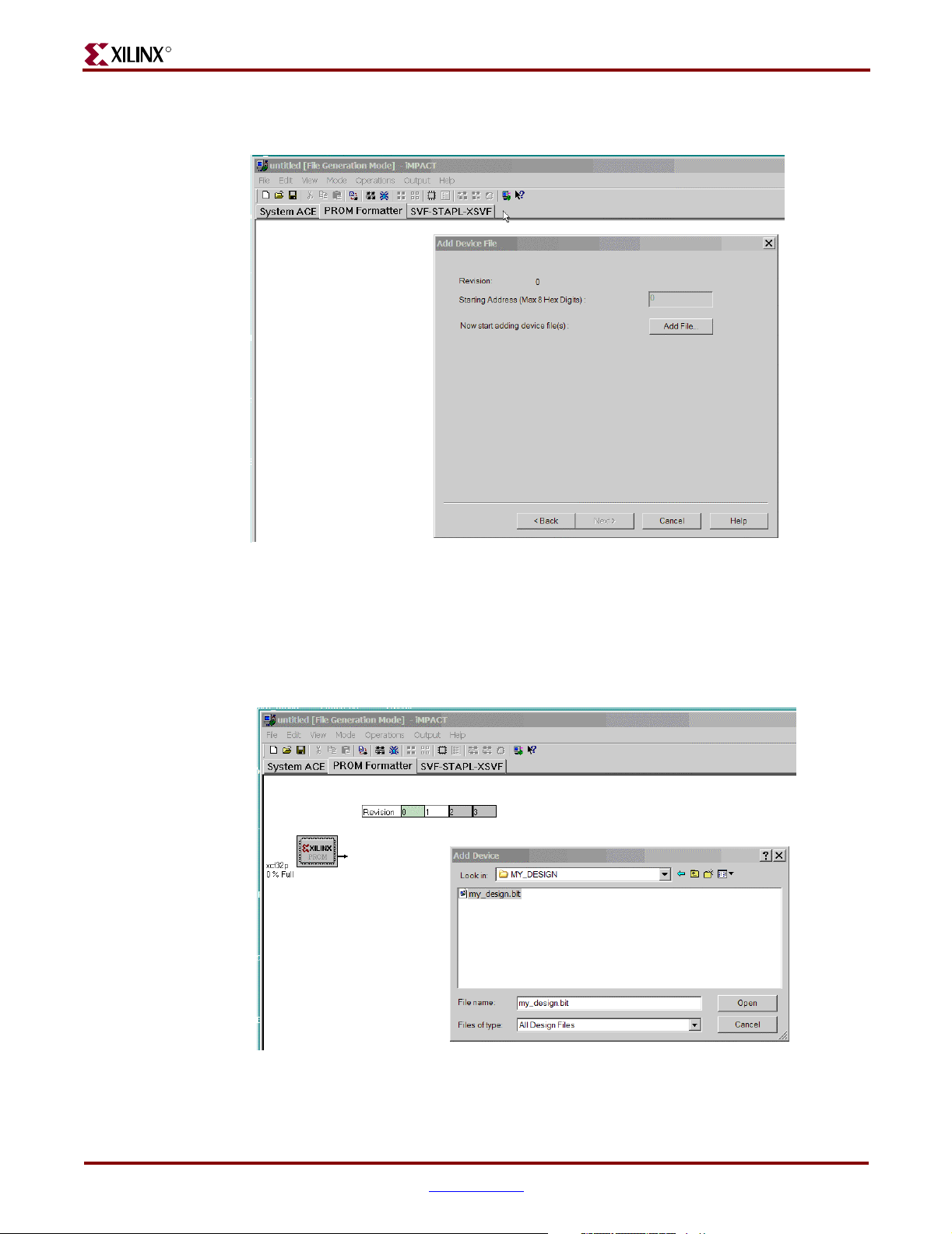

Figure B-1: Operation Mode Selection: Prepare Configuration Files . . . . . . . . . . . . . . . . . 77

Figure B-2: Selecting PROM File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure B-3: Selecting a PROM with Design Revisioning Enabled . . . . . . . . . . . . . . . . . . . 79

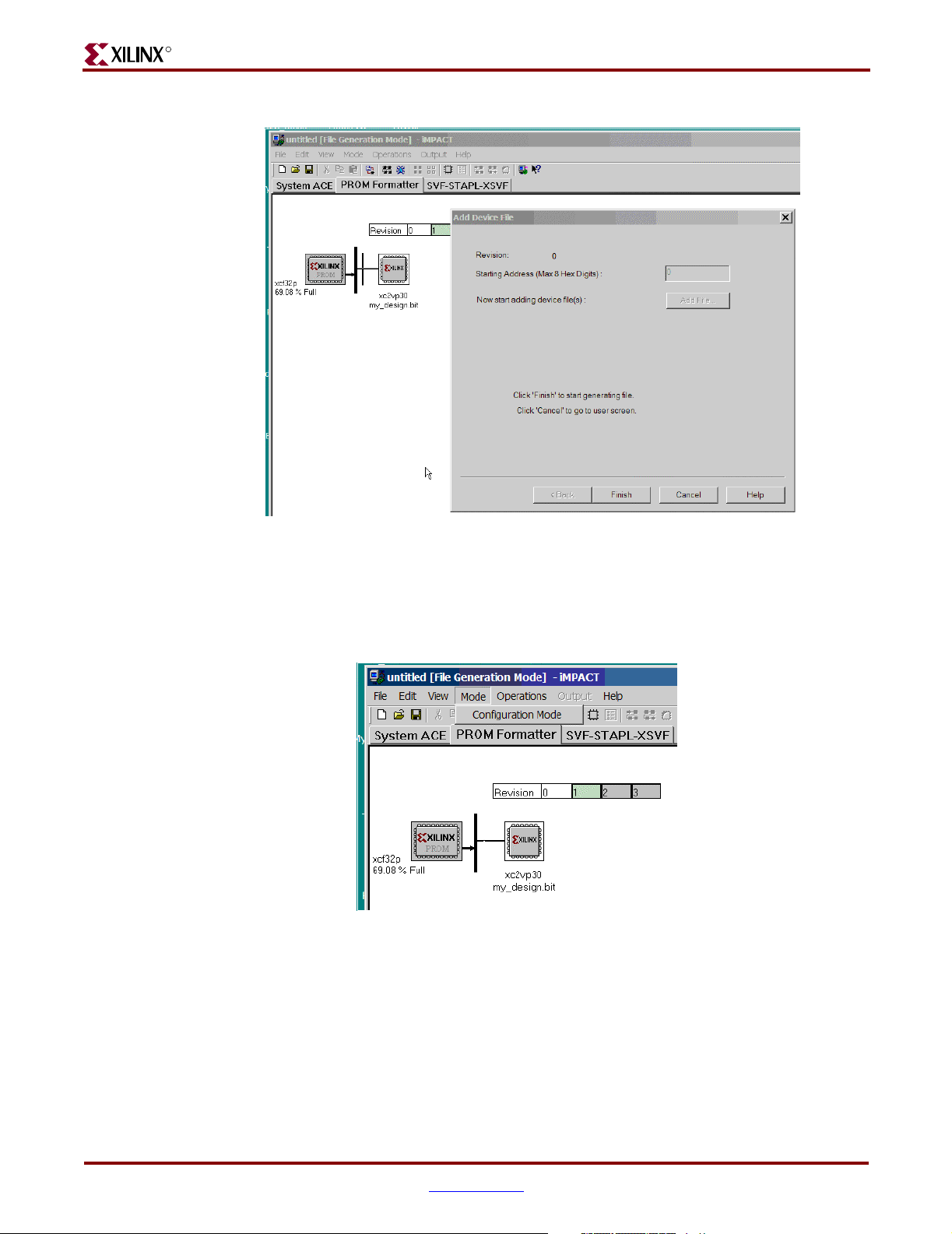

Figure B-4: Selecting an XCF32P PROM with Two Revisions . . . . . . . . . . . . . . . . . . . . . . . 79

Figure B-5: Adding a Device File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure B-6: Adding the Design File to Revision 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

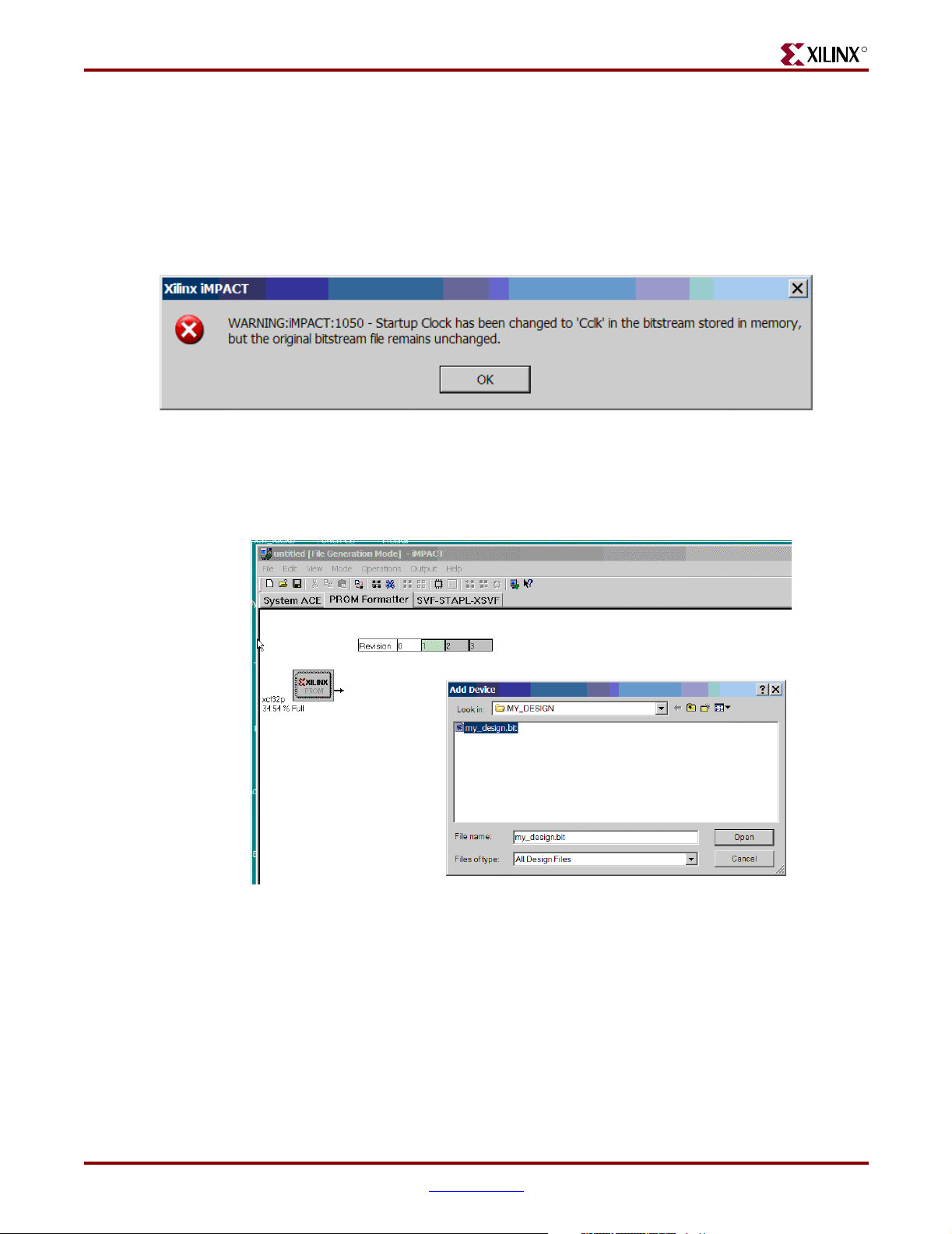

Figure B-7: iMPACT Startup Clock Warning. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure B-8: Adding the Design File to Revision 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure B-9: Generating the MCS File. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Figure B-10: Switching to Configuration Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Figure B-11: Initializing the JTAG Chain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Figure B-12: Assigning the MCS File to the PROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

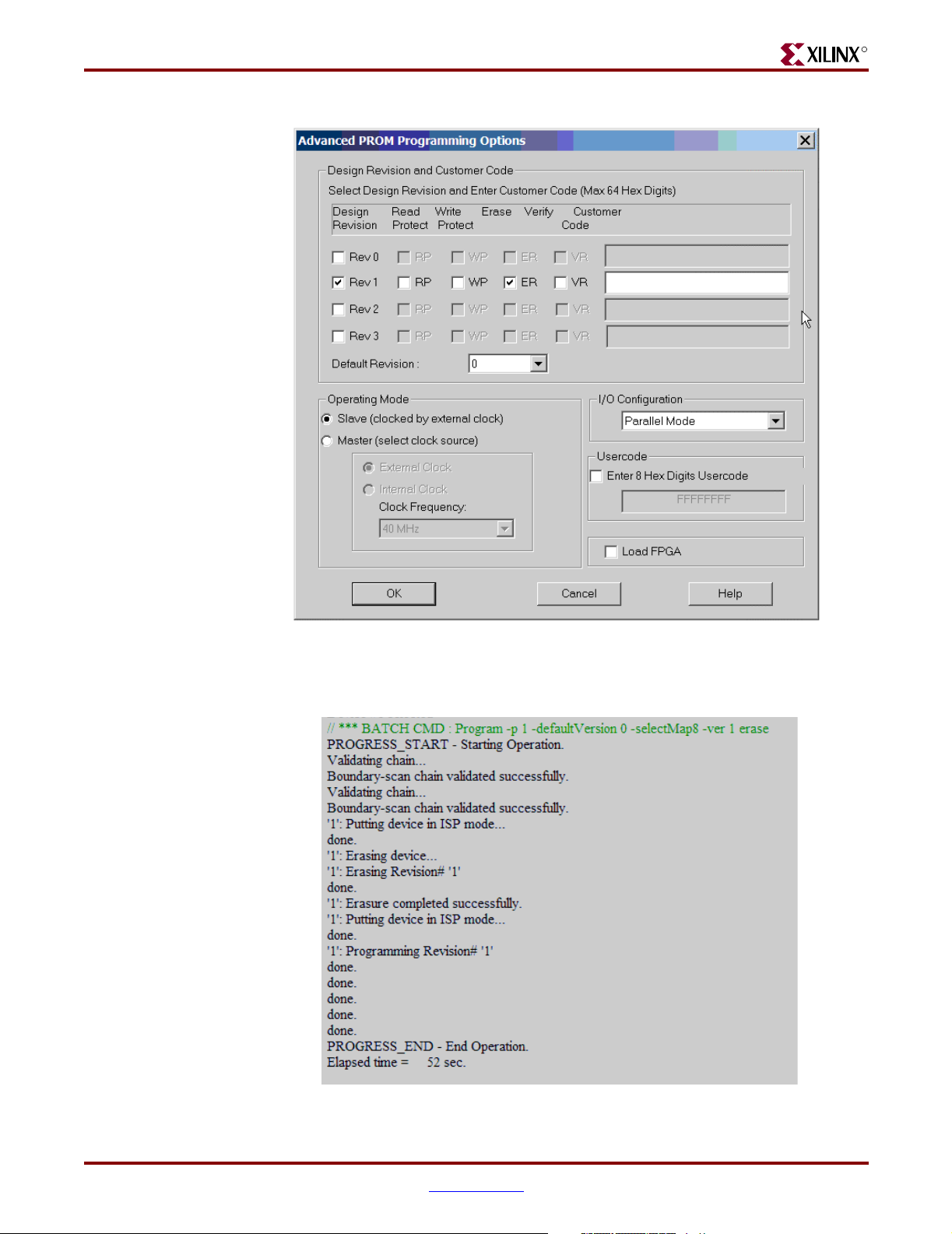

Figure B-13: Programming the PROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure B-14: PROM Programming Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure B-15: iMPACT PROM Programming Transcript Window . . . . . . . . . . . . . . . . . . . . 85

Appendix C: Restoring the Golden FPGA Configuration

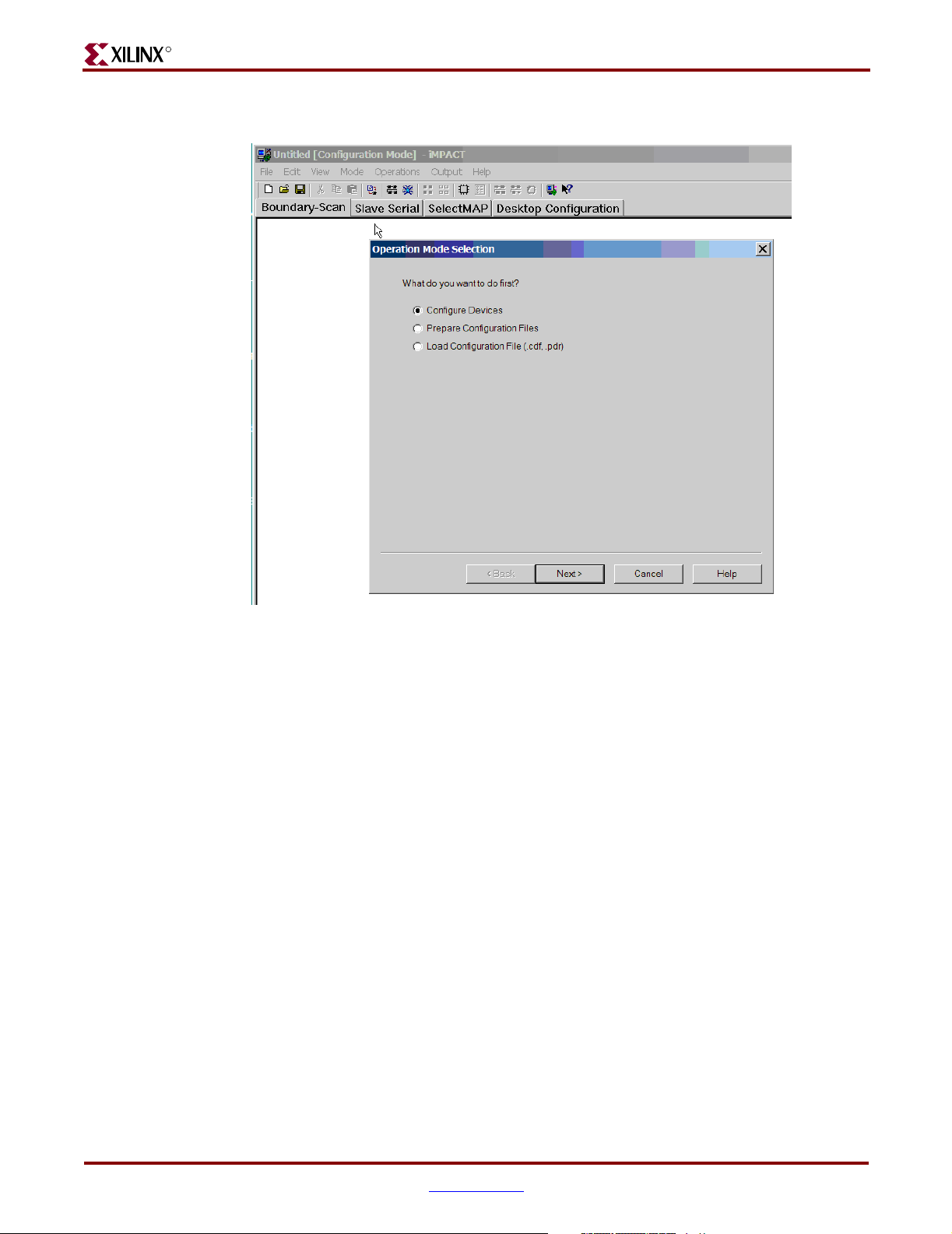

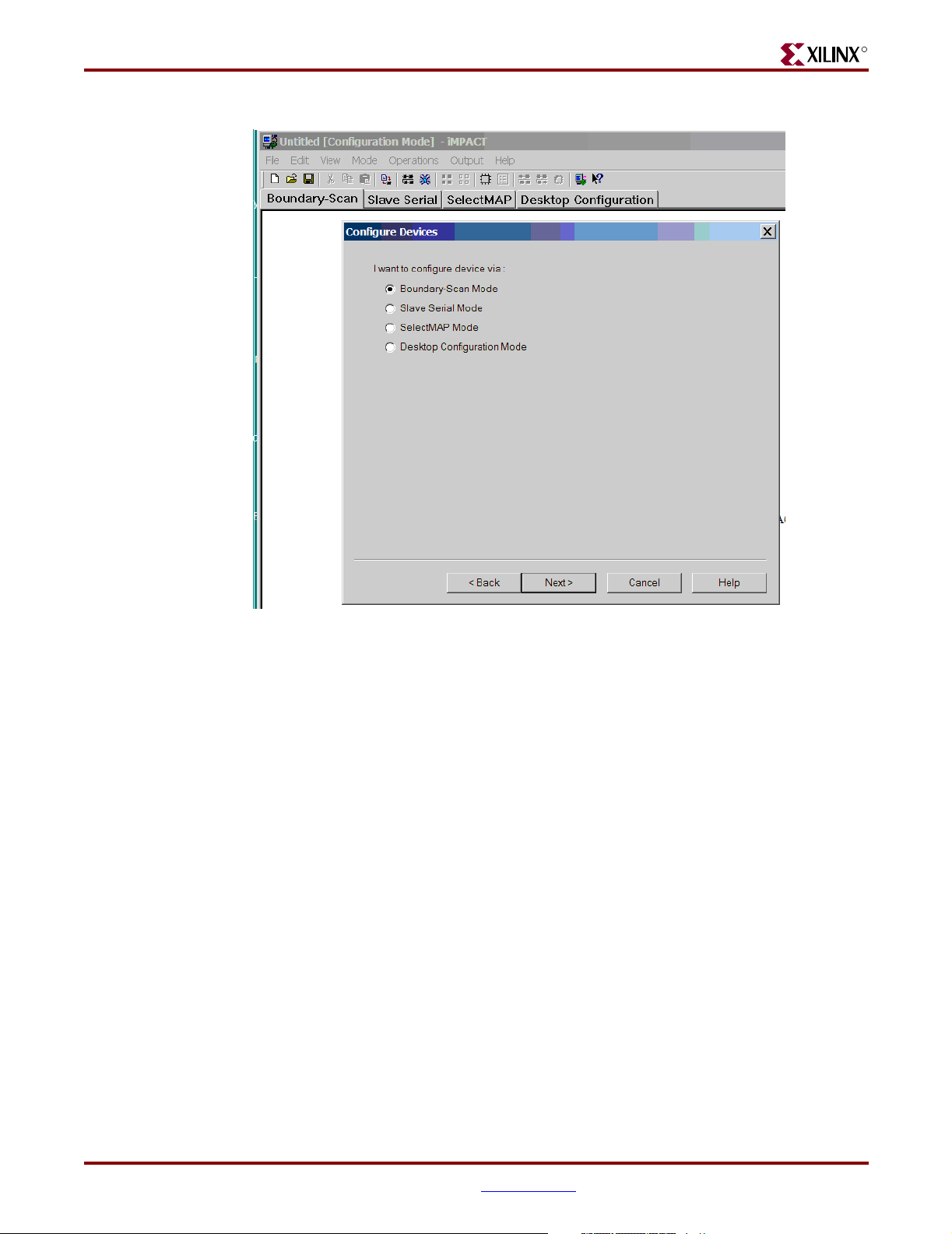

Figure C-1: Operation Mode Selection: Configure Devices . . . . . . . . . . . . . . . . . . . . . . . . . 88

Figure C-2: Selecting Boundary Scan Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Figure C-3: Boundary Scan Mode Selection: Automatically Connect to the Cable

and Identify the JTAG Chain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

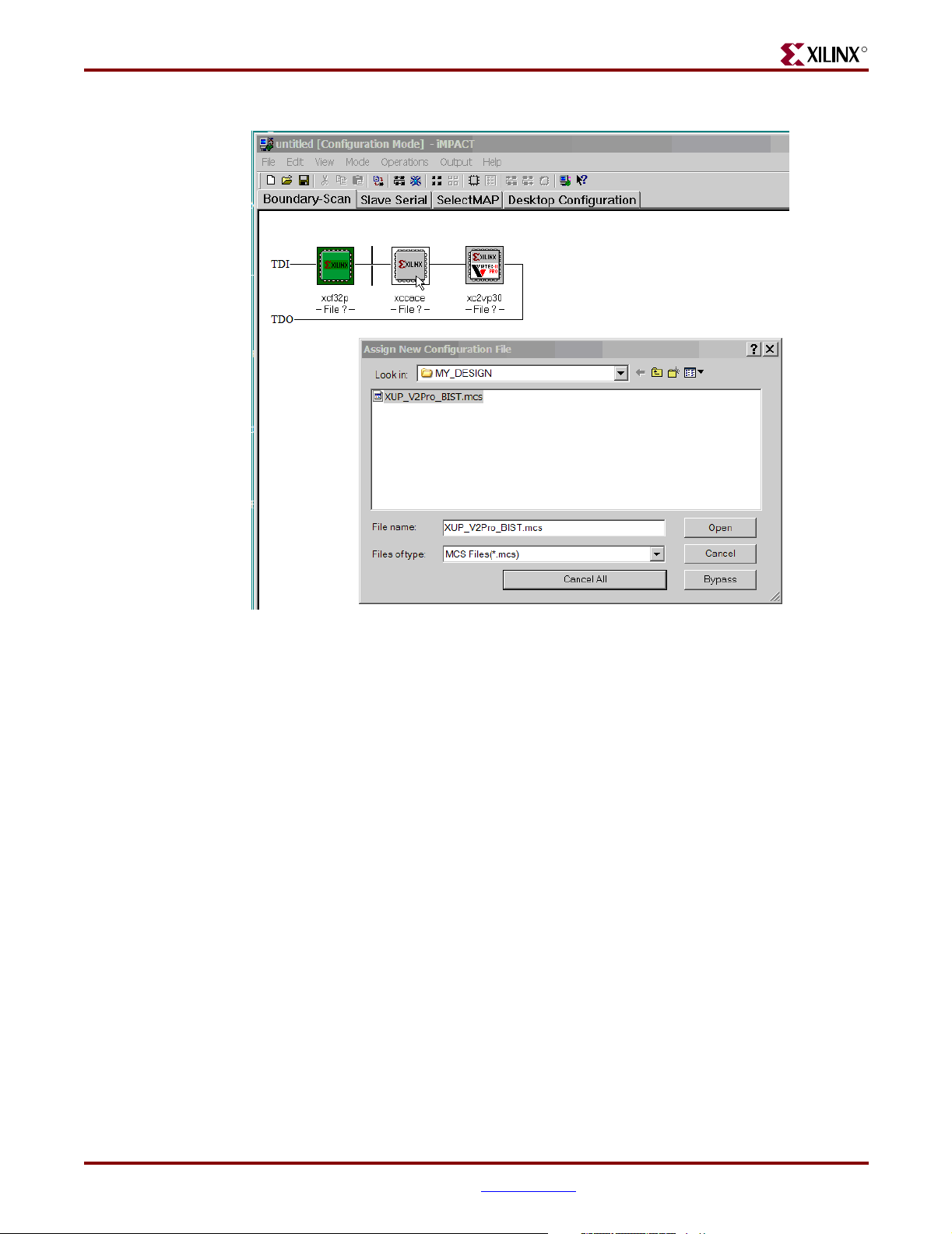

Figure C-4: Assigning New PROM Configuration File. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Figure C-5: Erasing the Existing PROM Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure C-6: Transcript Window for the Erase Command . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure C-7: Selecting the Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Figure C-8: PROM Programming Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure C-9: iMPACT PROM Programming Transcript Window. . . . . . . . . . . . . . . . . . . . . 95

Appendix D: Using the Golden FPGA Configuration for System Self-

Test

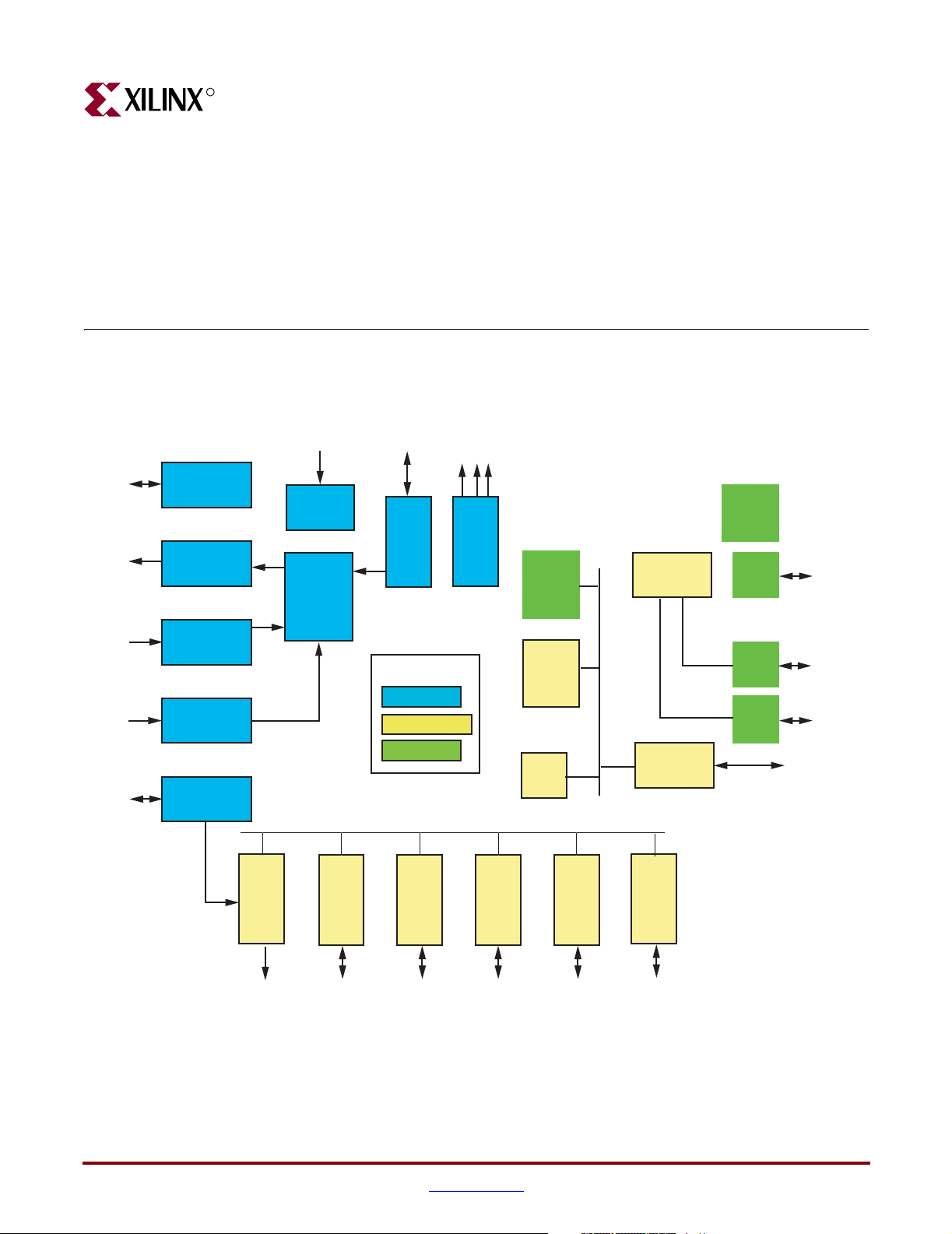

Figure D-1: XUP Virtex-II Pro Development System BIST Block Diagram . . . . . . . . . . . 97

Figure D-2: Built-In Self-Test Main Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Figure D-3: Testing the SATA 0 HOST to SATA 1 TARGET Connection. . . . . . . . . . . . 103

Figure D-4: Testing the SATA 2 HOST to SATA 1 TARGET Connection. . . . . . . . . . . . 103

Figure D-5: Selecting the SATA Port Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure D-6: Selecting the Specific SATA Port to Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure D-7: Resetting the MGTs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure D-8: No Link Established Error Message. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Figure D-9: SATA Test Running . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Figure D-10: SATA Loopback Test PASSED . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

XUP Virtex-II Pro Development System www.xilinx.com UG069 (v1.0) March 8, 2005

Page 9

Figure D-11: Specifying IP Address for XUP Virtex-II Pro Development System. . . . . 107

Figure D-12: Web Server Running . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Figure D-13: Web Server Display. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Figure D-14: Web Server Stopped . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Figure D-15: Selecting the Specific AC97 Audio Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Figure D-16: Digital Passthrough Test Completion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Figure D-17: FIFO Loopback Test Completion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Figure D-18: Game Sounds Test Completion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Figure D-19: System ACE Test Completion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Figure D-20: DDR SDRAM Test Completion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Figure D-21: Confirming Start of the Expansion Port Walking Ones Test . . . . . . . . . . . 114

Appendix E: User Constraint Files (UCF)

Appendix F: Links to the Component Data Sheets

UG069 (v1.0) March 8, 2005 www.xilinx.com XUP Virtex-II Pro Development System

Page 10

XUP Virtex-II Pro Development System www.xilinx.com UG069 (v1.0) March 8, 2005

Page 11

Tables

Chapter 1: XUP Virtex-II Pro Development System

Chapter 2: Using the System

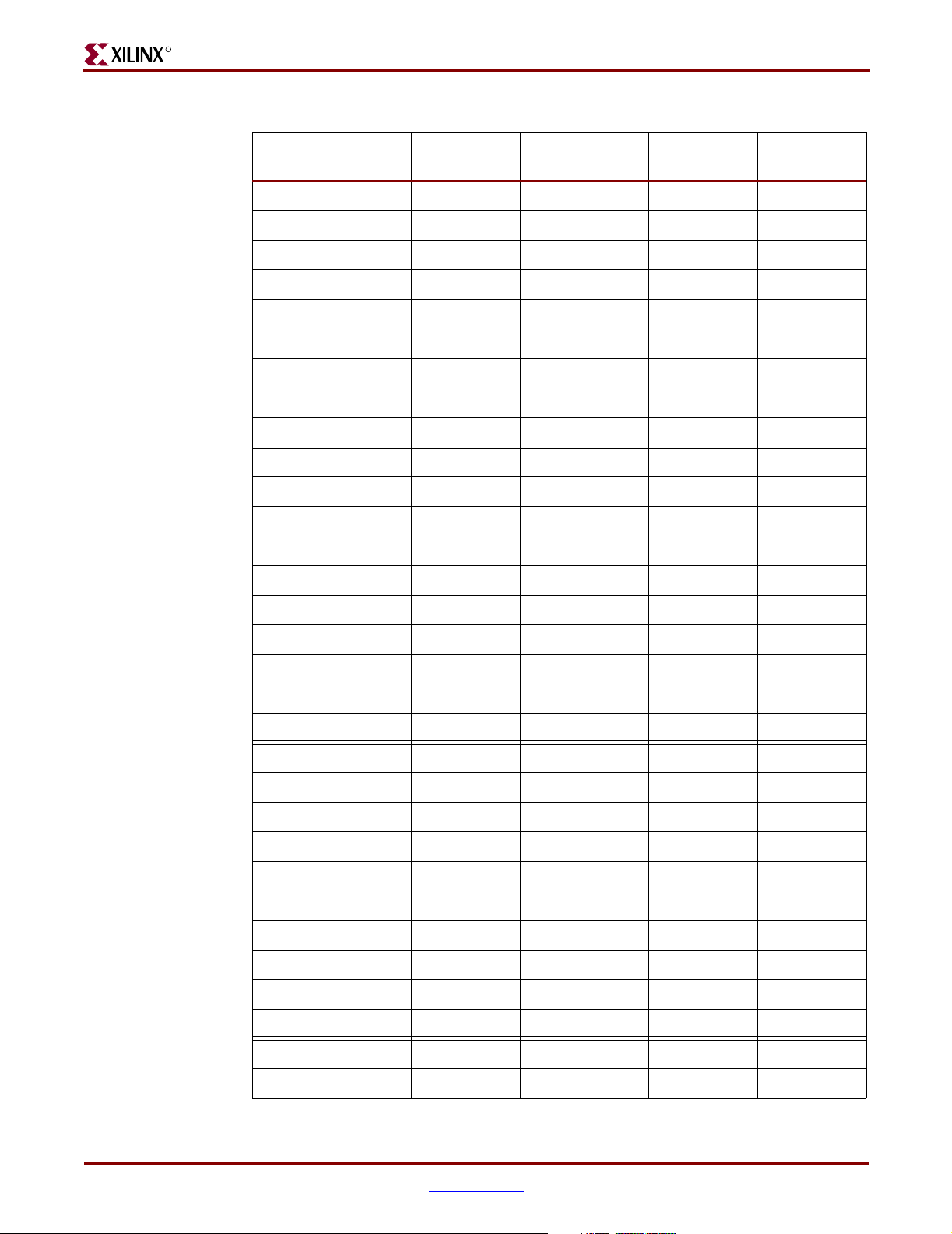

Table 1-1: XC2VP20 and XC2VP30 Device Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 2-1: System Configuration Status LEDs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 2-2: Clock Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 2-3: SPD EEPROM Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 2-4: Qualified SDRAM Memory Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

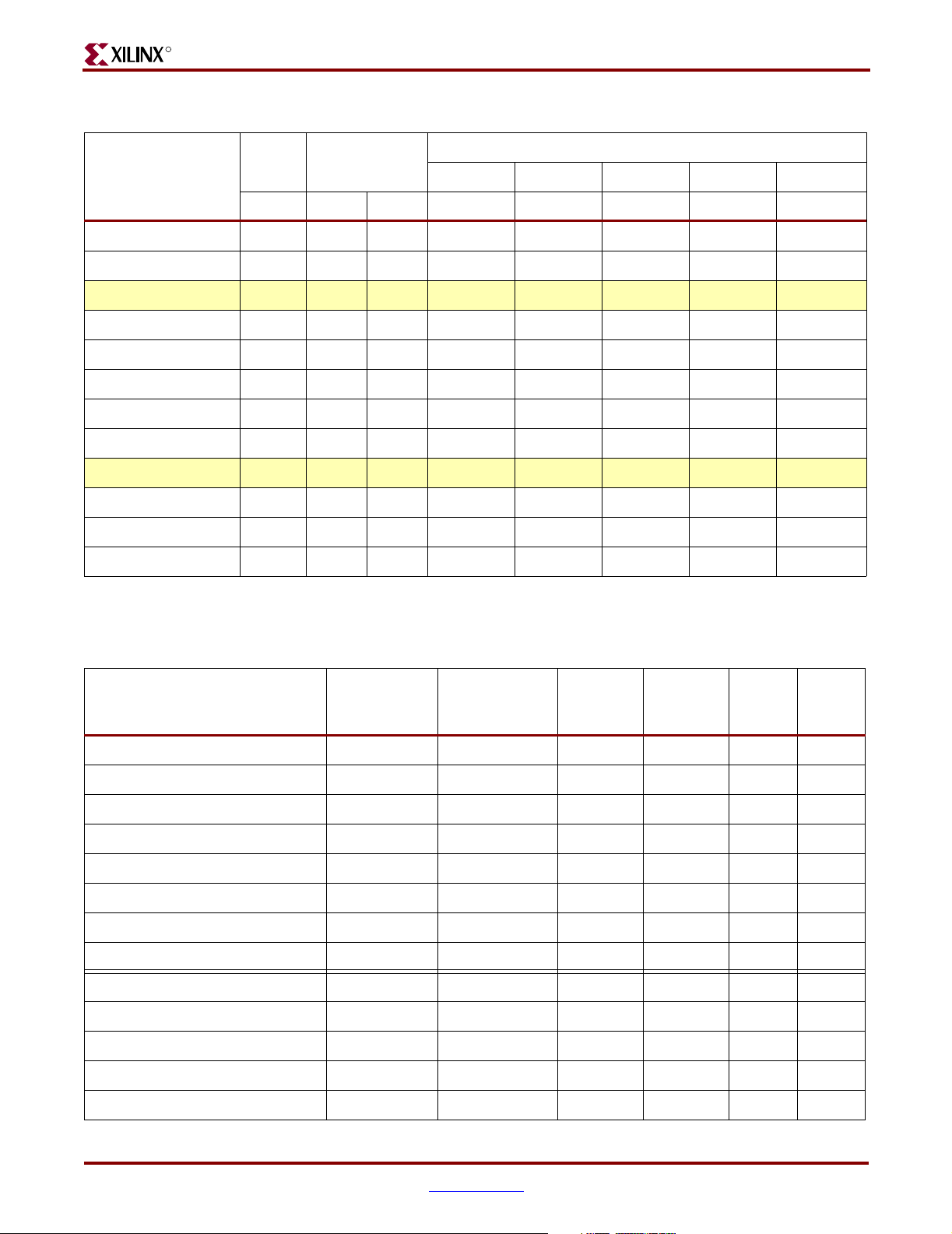

Table 2-5: DDR SDRAM Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

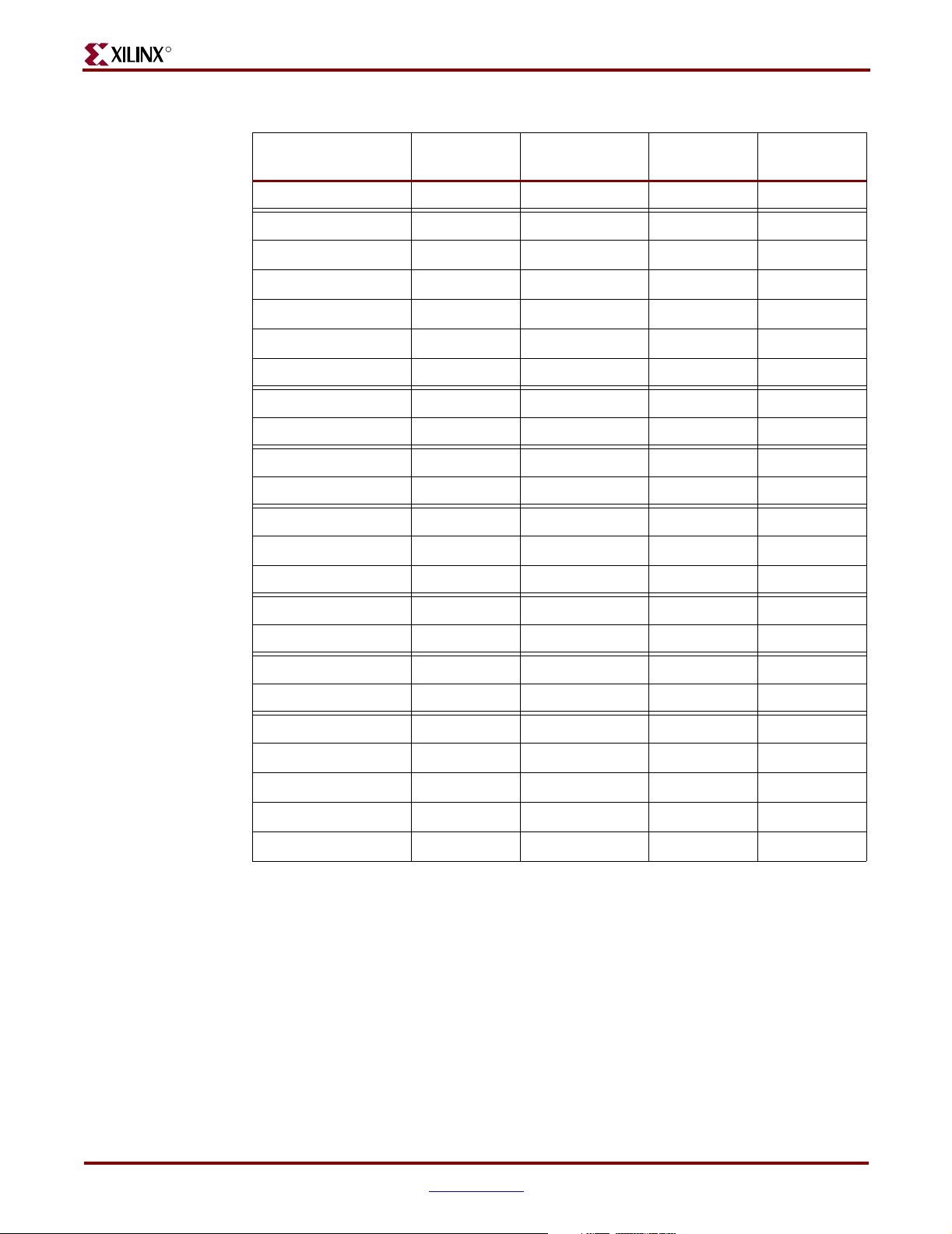

Table 2-6: DCM and XSGA Controller Settings for Various XSGA Formats . . . . . . . . . . 37

Table 2-7: XSGA Output Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 2-8: AC97 Audio CODEC Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 2-9: User LED and Switch Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 2-10: Top Expansion Header Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 2-11: Upper Middle Expansion Header Pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 2-12: Lower Middle Expansion Header Pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 2-13: Bottom Expansion Header Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 2-14: Left Digilent Expansion Connector Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 2-15: Right Digilent Expansion Connector Pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 2-16: High-Speed Digilent Expansion Connector Pinout. . . . . . . . . . . . . . . . . . . . . . 56

Table 2-17: CPU Debug Port Connections and CPU Reset . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 2-18: Keyboard, Mouse, and RS-232 Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 2-19: 10/100 ETHERNET Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 2-20: System ACE Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 2-21: SATA and MGT Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

UG069 (v1.0) March 8, 2005 www.xilinx.com XUP Virtex-II Pro Development System

Page 12

Appendix A: Configuring the FPGA from the Embedded USB

Configuration Port

Appendix B: Programming the Platform FLASH PROM User Area

Appendix C: Restoring the Golden FPGA Configuration

Appendix D: Using the Golden FPGA Configuration for System Self-

Test

Appendix E: User Constraint Files (UCF)

Appendix F: Links to the Component Data Sheets

XUP Virtex-II Pro Development System www.xilinx.com UG069 (v1.0) March 8, 2005

Page 13

R

Chapter 1

XUP Virtex-II Pro Development System

Features

• Virtex™-II Pro FPGA with PowerPC™ 405 cores

• Up to 2 GB of Double Data Rate (DDR) SDRAM

• System ACE™ controller and Type II CompactFlash™ connector for FPGA

configuration and data storage

• Embedded Platform Cable USB configuration port

• High-speed SelectMAP FPGA configuration from Platform Flash In-System

Programmable Configuration PROM

• Support for “Golden” and “User” FPGA configuration bitstreams

• On-board 10/100 Ethernet PHY device

• Silicon Serial Number for unique board identification

• RS-232 DB9 serial port

• Two PS-2 serial ports

• Four LEDs connected to Virtex-II Pro I/O pins

• Four switches connected to Virtex-II Pro I/O pins

• Five push buttons connected to Virtex-II Pro I/O pins

• Six expansion connectors joined to 80 Virtex-II Pro I/O pins with over-voltage

protection

• High-speed expansion connector joined to 40 Virtex-II Pro I/O pins that can be used

differentially or single ended

• AC-97 audio CODEC with audio amplifier and speaker/headphone output and line

level output

• Microphone and line level audio input

• On-board XSGA output, up to 1200 x 1600 at 70 Hz refresh

• Three Serial ATA ports, two Host ports and one Target port

• Off-board expansion MGT link, with user-supplied clock

• 100 MHz system clock, 75 MHz SATA clock

• Provision for user-supplied clock

• On-board power supplies

• Power-on reset circuitry

• PowerPC 405 reset circuitry

XUP Virtex-II Pro Development System www.xilinx.com 13

UG069 (v1.0) March 8, 2005

Page 14

R

General Description

The XUP Virtex-II Pro Development System provides an advanced hardware platform that

consists of a high performance Virtex-II Pro Platform FPGA surrounded by a

comprehensive collection of peripheral components that can be used to create a complex

system and to demonstrate the capability of the Virtex-II Pro Platform FPGA.

Block Diagram

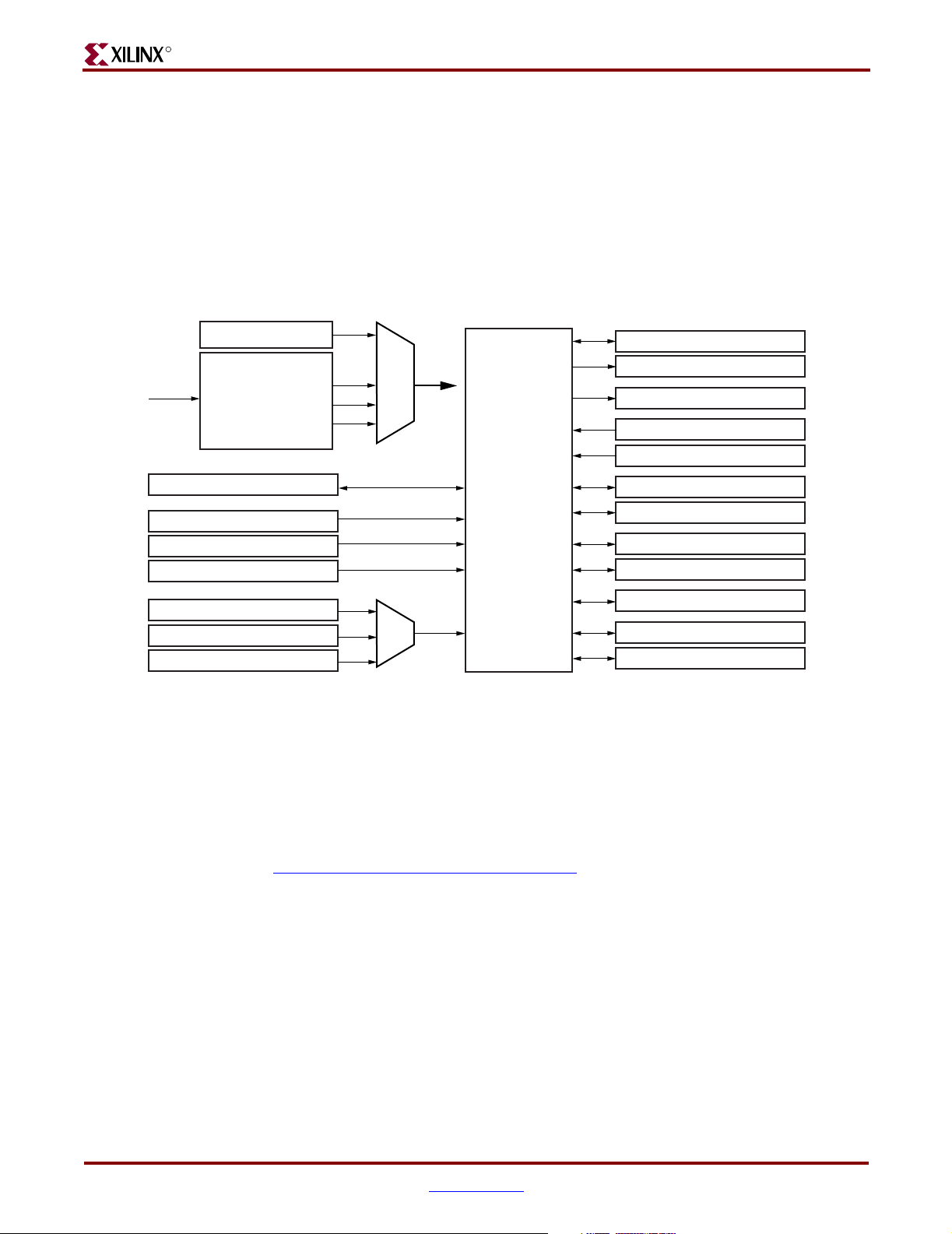

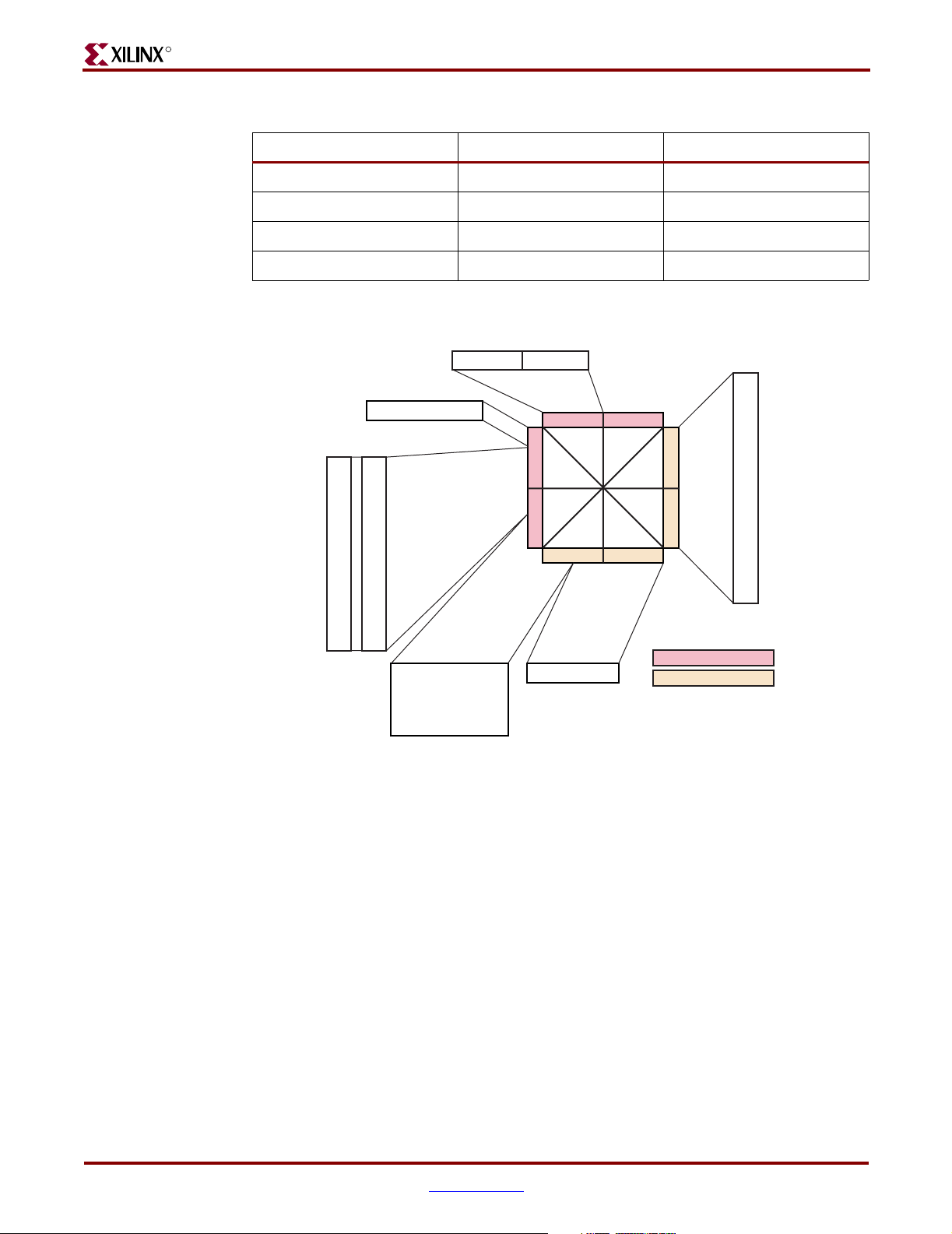

Figure 1-1 shows a block diagram of the XUP Virtex-II Pro Development System.

Chapter 1: XUP Virtex-II Pro Development System

External Power

Internal Power Supplies

4.5-5.5V

CPU Debug Port

100 MHz System Clock

75 MHz SATA Clock

User Clocks (2)

Platform Flash Configurations (2)

Compact Flash Configurations (8)

USB2 High Speed Configuration

3.3V

2.5V

1.5V

Figure 1-1: XUP Virtex-II Pro Development System Block Diagram

Board Components

Virtex-II Pro

FPGA

AC97 Audio CODEC & Stereo Amp

XSGA Video Output

User LEDs (4)

User Switches (4)

User Push-button Switches (5)

10/100 Ethernet PHY

RS-232 & PS/2 Ports (2)

Serial ATA Por ts (3)

Multi-Gigabit Transceiver Port

2 GB DDR SDRAM DIMM Module

5V Tolerant Expansion Headers

High Speed Expansion Port

UG069_01_012105

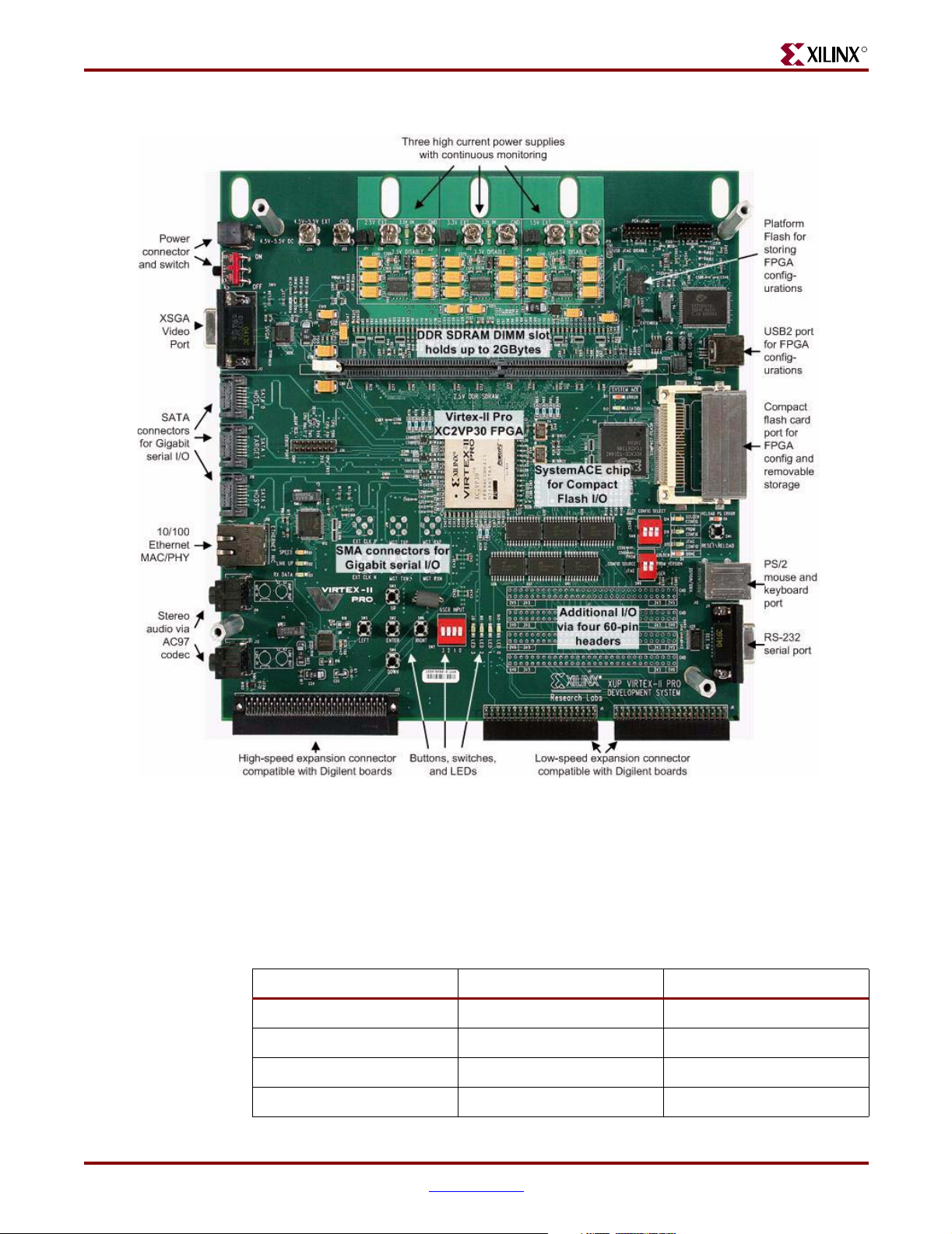

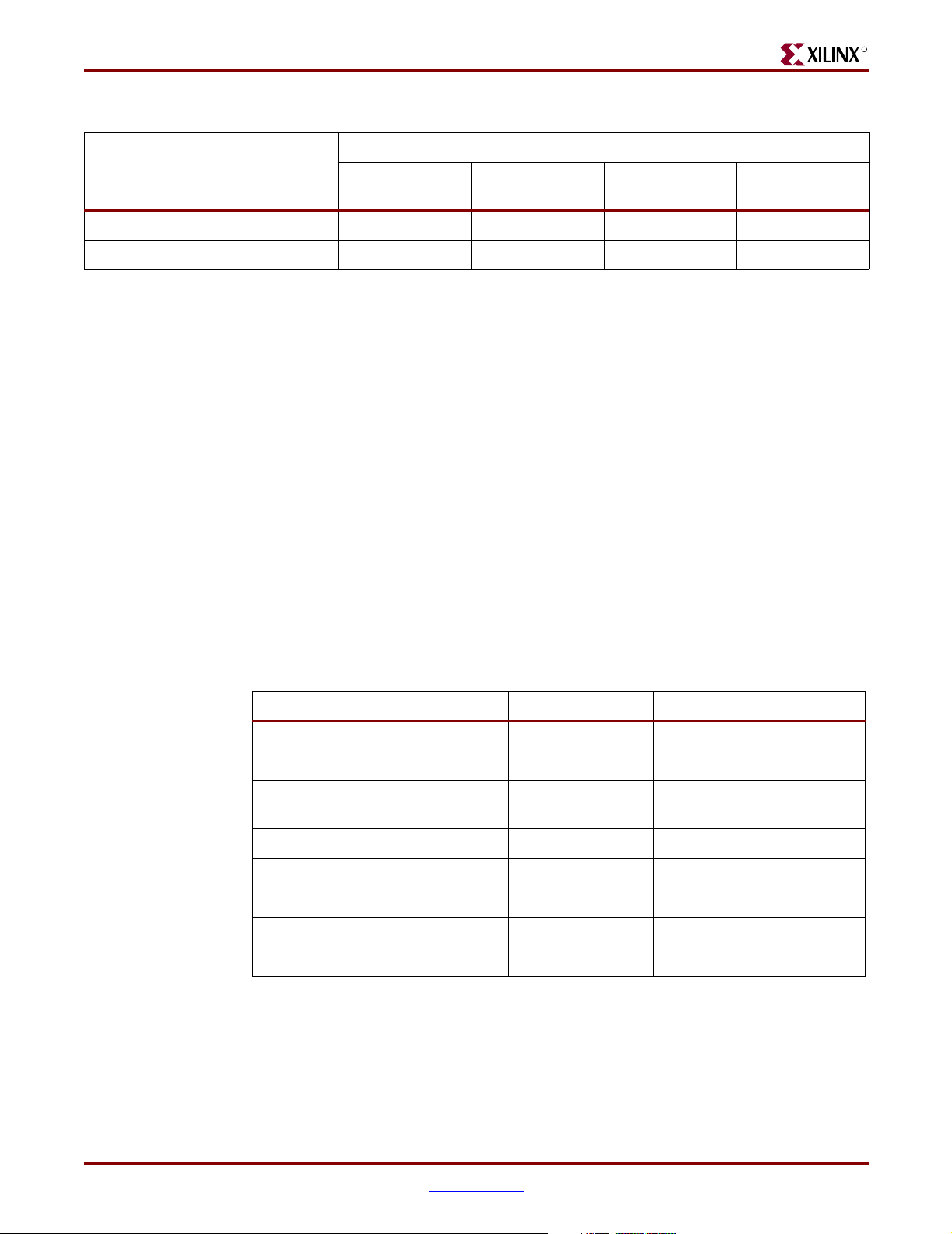

This section contains a concise overview of several important components on the XUP

Virtex-II Pro Development System (see Figure 1-2). The most recent documentation for the

system can be obtained from the XUP Virtex-II Pro Development System support website

at: http://www.xilinx.com/univ/xup2vp.html

14 www.xilinx.com XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Page 15

General Description

R

Figure 1-2: XUP Virtex-II Pro Development System Board Photo

Virtex-II Pro FPGA

U1 is a Virtex-II Pro FPGA device packaged in a flip-chip-fine-pitch FF896 BGA package.

Two different capacity FPGAs can be used on the XUP Virtex-II Pro Development System

with no change in functionality. Ta bl e 1-1 lists the Virtex-II Pro device features.

Table 1-1: XC2VP20 and XC2VP30 Device Features

Features XC2VP20 XC2VP30

Slices 9280 13969

Array Size 56 x 46 80 x 46

Distributed RAM 290 Kb 428 Kb

Multiplier Blocks 88 136

XUP Virtex-II Pro Development System www.xilinx.com 15

UG069 (v1.0) March 8, 2005

Page 16

R

Chapter 1: XUP Virtex-II Pro Development System

Table 1-1: XC2VP20 and XC2VP30 Device Features (Continued)

Features XC2VP20 XC2VP30

Block RAMs 1584 Kb 2448 Kb

DCMs 8 8

PowerPC RISC Cores 2 2

Multi-Gigabit Transceivers 8 8

Figure 1-3 identifies the I/O banks that are used to connect the various peripheral devices

to the FPGA.

AC97 Audio SXGA port

10/100 Ethernet

1

0

2

7

OVER VOLTAGE CLAMPS

EXPANSION CONNECTORS

LEDs & SWITCHES

PS/2 KBD & MOUSE

PUSH BUTTONS

RS-232

System ACE port

Figure 1-3: I/O Bank Connections to Peripheral Devices

Power Supplies and FPGA Configuration

The XUP Virtex-II Pro Development System is powered from a 5V regulated power supply.

On-board switching power supplies generate 3.3V, 2.5V, and 1.5V for the FPGA, and

peripheral components and linear regulators power the MGTs.

The board has provisioning for current measurement for all of the FPGA digital power

supplies, as well as application of external power if the capacity of the on-board switching

power supplies is exceeded.

3

6

45

256M x 64/72 DDR SDRAM DIMM MODULE

3.3V IO

2.5V IO

UG069_03_012105

The XUP Virtex-II Pro Development System provides several methods for the

configuration of the Virtex-II Pro FPGA. The configuration data can originate from the

internal Platform Flash PROM (two potential configurations), the internal CompactFlash

storage media (eight potential configurations), and external configurations delivered from

the embedded Platform Cable USB or parallel port interface.

16 www.xilinx.com XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Page 17

General Description

Multi-Gigabit Transceivers

System RAM

R

Four of the eight Multi-Gigabit Transceivers (MGTs) that are present in the Virtex-II Pro

FPGA are brought out to connectors and can be utilized by the user. Three of the

bidirectional MGT channels are terminated at Serial Advanced Technology Attachment

(SATA) connectors and the fourth channel terminates at user-supplied Sub-Miniature A

(SMA) connectors. The MGT transceivers are equipped with a 75 MHz clock source that is

independent for the system clock to support standard SATA communication. An

additional MGT clock source is available through a differential user-supplied (SMA)

connector pair. Two of the ports with SATA connectors are configured as Host ports and

the third SATA port is configured as a Target port to allow for simple board-to-board

networking.

The XUP Virtex-II Pro Development System has provision for the installation of usersupplied JEDEC-standard 184-pin dual in-line Double Data Rate Synchronous Dynamic

RAM memory module. The board supports buffered and unbuffered memory modules

with a capacity of 2 GB or less in either 64-bit or 72-bit organizations. The 72-bit

organization should be used if ECC error detection and correction is required.

System ACE Compact Flash Controller

The System Advanced Configuration Environment (System ACE™) Controller manages

FPGA configuration data. The controller provides an intelligent interface between an

FPGA target chain and various supported configuration sources. The controller has several

ports: the Compact Flash port, the Configuration JTAG port, the Microprocessor (MPU)

port and the Test JTAG port. The XUP Virtex-II Pro Development System supports a single

System ACE Controller. The Configuration JTAG ports connect to the FPGA and front

expansion connectors. The Test JTAG port connects to the JTAG port header and USB2

interface CPLD, and the MPU ports connect directly to the FPGA.

Fast Ethernet Interface

The XUP Virtex-II Pro Development System provides an IEEE-compliant Fast Ethernet

transceiver that supports both 100BASE-TX and 10BASE-T applications. It supports full

duplex operation at 10 Mb/s and 100 Mb/s, with auto-negotiation and parallel detection.

The PHY provides a Media Independent Interface (MII) for attachment to the 10/100

Media Access Controller (MAC) implemented in the FPGA. Each board is equipped with a

Silicon Serial Number that uniquely identifies each board with a 48-bit serial number. This

serial number is retrieved using “1-Wire” protocol. This serial number can be used as the

system MAC address.

Serial Ports

The XUP Virtex-II Pro Development System provides three serial ports: a single RS-232

port and two PS/2 ports. The RS-232 port is configured as a DCE with hardware

handshake using a standard DB-9 serial connector. This connector is typically used for

communications with a host computer using a standard 9-pin serial cable connected to a

COM port. The two PS/2 ports could be used to attach a keyboard and mouse to the XUP

Virtex-II Pro Development System. All of the serial ports are equipped with level-shifting

circuits, because the Virtex-II Pro FPGAs cannot interface directly to the voltage levels

required by RS-232 or PS/2.

XUP Virtex-II Pro Development System www.xilinx.com 17

UG069 (v1.0) March 8, 2005

Page 18

R

Chapter 1: XUP Virtex-II Pro Development System

User LEDs, Switches, and Push Buttons

A total of four LEDs are provided for user-defined purposes. When the FPGA drives a

logic 0, the corresponding LED turns on. A single four-position DIP switch and five push

buttons are provided for user input. If the DIP switch is up, closed, or on, or the push button

is pressed, a logic 0 is seen by the FPGA, otherwise a logic 1 is indicated.

Expansion Connectors

A total of 80 Virtex-II Pro I/O pins are brought out to four user-supplied 60-pin headers

and two 40-pin right angle connectors for user-defined use. The 60-pin headers are

designed to accept ribbon-cable connectors, with every second signal a ground for signal

integrity. Some of these signals are shared with the front-mounted right-angle connectors.

The front-mounted connectors support Digilent expansion modules. In addition, a highspeed connector is provided to support Digilent high-speed expansion modules. This

connector provides 40 single-ended or differential I/O signals in addition to three clocks.

Consult the Digilent website at www.diglentinc.com

compatible with the XUP Virtex-II Pro Development System.

XSGA Output

The XUP Virtex-II Pro Development System includes a video DAC and 15-pin highdensity D-sub connector to support XSGA output. The video DAC can operate with a pixel

clock of up to 180 MHz. This allows for a VESA-compatible output of 1280 x 1024 at 75 Hz

refresh and a maximum resolution of 1600 x 1200 at 70 Hz refresh.

for a list of expansion boards that are

AC97 Audio CODEC

An audio CODEC and stereo power amplifier are included on the XUP Virtex-II Pro

Development System to provide a high-quality audio path and provide all of the analog

functionality in a PC audio system. It features a full-duplex stereo ADC and DAC, with an

analog mixer, combining the line-level inputs, microphone input, and PCM data.

CPU Trace and Debug Port

The FPGA is equipped with a CPU debugging interface and a 16-pin header. This

connector can be used in conjunction with third party tools, the Xilinx Parallel Cable IV, or

the Xilinx Platform Cable USB to debug software as it runs on either PowerPC 405

processor core.

ChipScope Pro™ can also be used to perform real-time debug and verification of the FPGA

design. ChipScope Pro inserts logic analyzer, bus analyzer, and Virtual I/O low-profile

software cores into the FPGA design. These cores allow the designer to view all the internal

signals and nodes within the FPGA including the Processor Local Bus (PLB) or On-Chip

Peripheral Bus (OPB) supporting the PowerPC 405 cores. Signals are captured and brought

out through the embedded Platform Cable USB programming interface for analysis using

the ChipScope Pro Logic Analyzer tool.

USB 2 Programming Interface

The XUP Virtex-II Pro Development System includes an embedded USB 2.0

microcontroller capable of communications with either high-speed (480 Mb/s) or fullspeed (12 Mb/s) USB hosts. This interface is used for programming or configuring the

Virtex-II Pro FPGA in Boundary-Scan (IEEE 1149.1/IEEE 1532) mode. Target clock speeds

are selectable from 750 kHz to 24 MHz. The USB 2.0 microcontroller attaches to a desktop

or laptop PC with an off-the-shelf high-speed A-B USB cable.

18 www.xilinx.com XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Page 19

R

Using the System

Configuring the Power Supplies

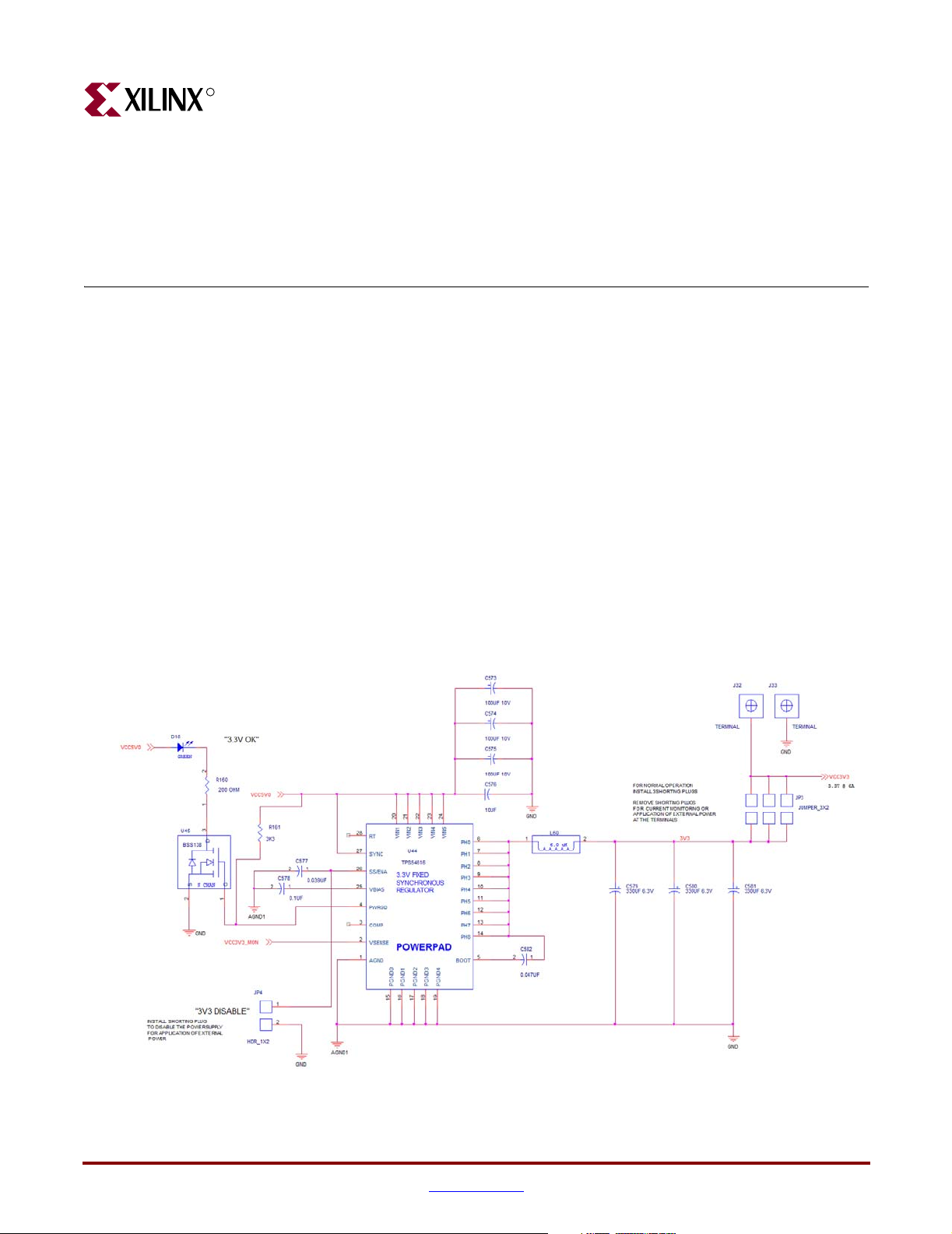

The XUP Virtex-II Pro Development System supports the independent creation of the

power supplies for the core voltage of 1.5V (FPGA_VINT), 2.5V general-purpose power,

I/O and/or VCCAUX supplies (VCC2V5), and 3.3V I/O and general-purpose power

(VCC3V3). These voltages are created by synchronous buck-switching regulators derived

from the 4.5V-5.5V power input provided at the center-positive barrel-jack power input

(J26) or the terminal block pair (J34-J35). Each of these supplies can be disabled through the

insertion of jumpers (JP2, JP4, and JP6), and the external application of power from the

terminal blocks (J28-J33). If external power is supplied, the associated internal power

supply must be disabled (through the insertion of JP6, JP2, or JP4) and the associated onboard power delivery jumpers (JP5, JP1, or JP3) must be removed. The power consumption

from each of the on-board power supplies can be monitored through the removal of JP5,

JP1, or JP3 and the insertion of a current monitor. If any of the power supplies are outside

the recommended tolerance, internally or externally provided, the system enters a RESET

state indicated by the illumination of the RESET_PS_ERROR LED (D6) and the assertion of

the RESET_Z signal. A typical switching power supply is shown in Figure 2-1.

Chapter 2

ug069_04_021505

Figure 2-1: Typical Switching Power Supply

XUP Virtex-II Pro Development System www.xilinx.com 19

UG069 (v1.0) March 8, 2005

Page 20

VCC3V3

R

Chapter 2: Using the System

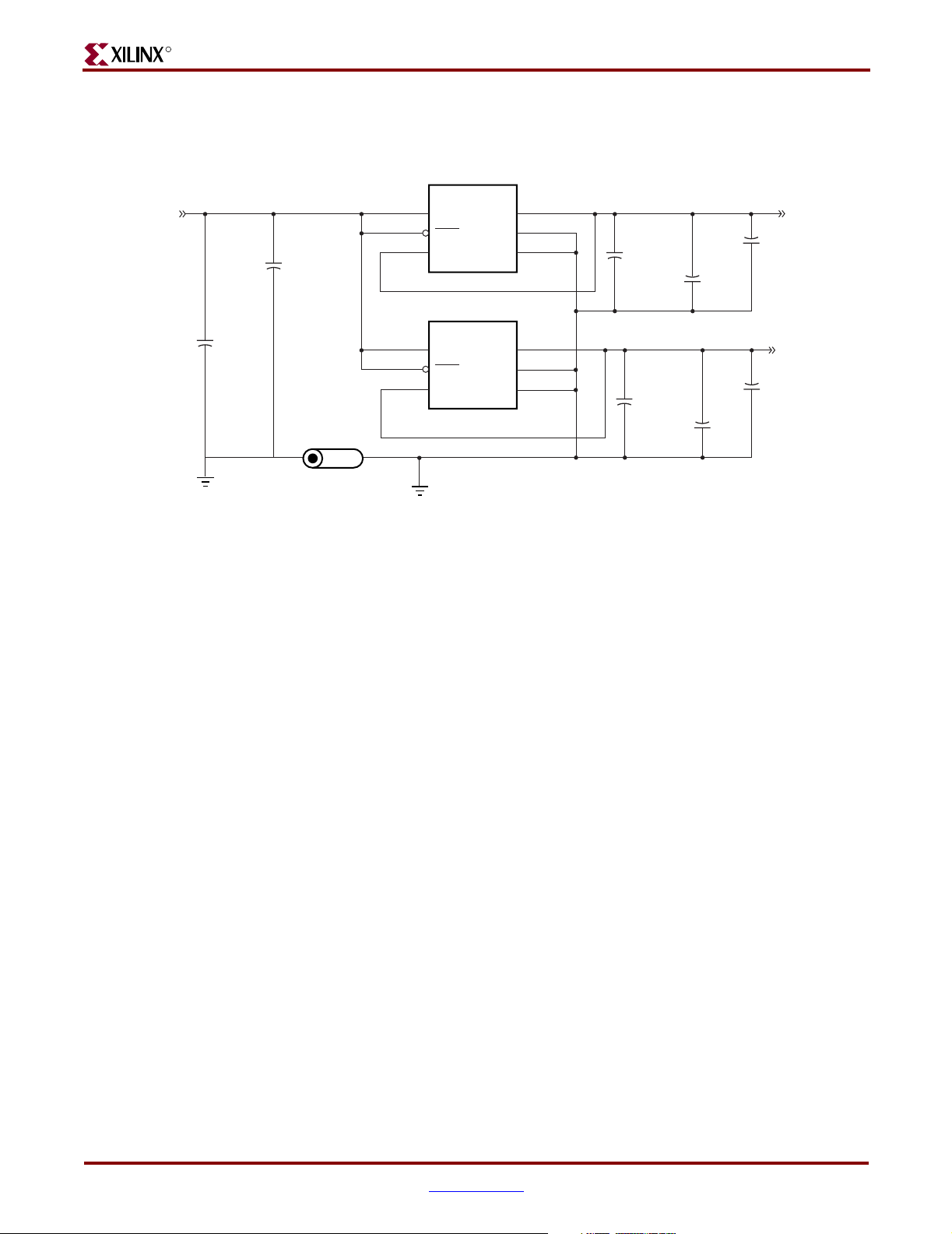

Because of the analog nature of the MGTs, the power for those elements are created by low

noise, low dropout linear regulators. Figure 2-2 shows the power supply for the MGTs.

U20

FIXED 2.5V LDO

TA B

TA B

4

3

+

6

4

3

6

C428

330UF 6.3V

C433

+

330UF 6.3V

C430

0.1UF

C434

0.1UF

VCC_MGT

C427

1000PF

VTT_MGT

C432

1000PF

UG069_05_010605

C431

+

33OUF 6.3V

C429

+

33OUF 6.3V

FERRITE BEAD

2961666671

L32

2

IN OUT

1

SHDN GND

5

SENSE

LT1963AEQ-25

U21

FIXED 2.5V LDO

2

IN OUT

1

SHDN GND

5

SENSE

LT1963AEQ-25

GND_MGT

Configuring the FPGA

At power up, or when the RESET_RELOAD push button (SW1) is pressed for longer than

2 seconds, the FPGA begins to configure. The two configuration methods supported, JTAG

and master SelectMAP, are determined by the CONFIG SOURCE switch, the most

significant switch (left side) of SW9.

If the CONFIG SOURCE switch is closed, on, or up, a high-speed SelectMap byte-wide

configuration from the on-board Platform Flash configuration PROM (U3) is selected as

the configuration source. This is identified to the user through the illumination of the

PROM CONFIG LED (D19).

The Platform Flash configuration PROM supports two different FPGA configurations

(versions) selected by the position of the PROM VERSION switch, the least significant

switch (right side) of SW9.

If the PROM VERSION switch is closed, on, or up, the GOLDEN configuration from the onboard Platform Flash configuration PROM is selected as the configuration data. This is

identified to the user through the illumination of the GOLDEN CONFIG LED (D14). This

configuration can be a board test utility provided by Xilinx, or another safe default

configuration. It is important to note that the PROM VERSION switch is only sampled on

board powerup and after a complete system reset. This means that if this switch is changed

after board powerup, the RESET_RELOAD pushbutton (SW1) must be pressed for more

than 2 seconds for the new state of the switch to be recognized.

Figure 2-2: MGT Power

If the PROM VERSION switch is open, off, or down, a User configuration from the on-board

Platform Flash configuration PROM is selected as the configuration data. This

configuration must be programmed into the Platform Flash PROM from the JTAG

Platform Cable USB interface or the USB interface following the instructions in Appendix

B, “Programming the Platform FLASH PROM User Area.”

20 www.xilinx.com XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Page 21

Configuring the FPGA

The Platform Flash is normally disabled after the FPGA is finished configuring and has

asserted the DONE signal. If additional data is made available to the FPGA after the

completion of configuration, jumper JP9 must be moved from the NORMAL to the

EXTENDED position to permanently enable the PROM and allow the FPGA to clock out

the additional data using the FPGA_PROM_CLOCK signal. The process of loading

additional non-configuration data into the FPGA is outlined in application note:

XAPP694:

Reading User Data from Configuration PROMs.

If the CONFIG SOURCE switch is open, off, or down, a lower speed JTAG-based

configuration from Compact Flash or external JTAG source is selected as the configuration

source. This is identified to the user through the illumination of the JTAG CONFIG LED

(D20).

The JTAG-based configuration can originate from several sources: the Compact Flash card,

a PC4 cable connection through J27, and a USB to PC connection through J8 the embedded

Platform Cable USB interface.

If a JTAG-based configuration is selected, the default source is from the Compact Flash

port (J7). The System ACE controller checks the associated Compact Flash socket and

storage device for the existence of configuration data. If configuration data exists on the

storage device, the storage device becomes the source for the configuration data. The file

structure on the Compact Flash storage device supports up to eight different configuration

data files, selected by the triple CF CONFIG SELECT DIP switch (SW8). During JTAG

configuration, the SYSTEMACE STATUS LED (D12) flashes until the configuration process

is completed, and the FPGA asserts the FPGA_DONE signal and illuminates the DONE

LED (D4). At any time, the RESET_RELOAD pushbutton (SW1) can be used to load any of

the eight different configuration data files by pressing the switch for more than 2 seconds.

R

If a JTAG-based configuration is selected and a valid configuration file is not found on the

Compact Flash card by the System ACE controller (U2), the SYSTEMACE ERROR LED

(D11) flashes, and the System ACE controller connects to an external JTAG port for FPGA

configuration.

The default external source for FPGA configuration is the high-speed embedded Platform

Cable USB configuration port (J8) and is enabled when the System ACE controller does not

find configuration data on the storage device. Detailed instructions on using the highspeed Platform Cable USB interface can be found in Appendix A, “Configuring the FPGA

from the Embedded USB Configuration Port.”

If a USB-equipped host PC is not available as a configuration source, then a Parallel Cable

4 (PC4) interface can be used instead by connecting a PC4 cable to J27.

It should be noted that if SelectMap byte-wide configuration from the on-board Platform

Flash configuration PROM is enabled, the FPGA Start-Up Clock should be set to CCLK in

the Startup Options section of the Process Options for the generation of the programming

file, otherwise JTAG Clock should be selected.

XUP Virtex-II Pro Development System www.xilinx.com 21

UG069 (v1.0) March 8, 2005

Page 22

R

Chapter 2: Using the System

Figure 2-3 illustrates the configuration data path.

USB2

Microcontroller

& CPLD

GOLDEN

VERSION SELECT

USER

JTAG Port

JTAG Port

PLATFORM

FLASH

SMAP Port

Test JTAG Port Config JTAG Port

SystemACE

Controller

PROM

CONFIG SOURCE

JTAG

CF Card/

MicroDrive

SMAP Port

Micro Port

CF CONFIG SELECT

FPGA

Micro PortJTAG Port

UG069_06_122704

Figure 2-3: Configuration Data Path

Four status LEDs show the configuration state of the XUP Virtex-II Pro Development

System at all times. The user can see the configuration source, configuration version, and

tell when the configuration has completed from the status LEDs shown in Tab le 2- 1.

Table 2-1: System Configuration Status LEDs

LED Status

System Status

D19 (Green)

PROM Config

D20 (Green)

CF Config

D14 (Amber)

GOLDEN Config

D4 (Red)

Done

SelectMAP USER LOADING ON OFF OFF OFF

SelectMAP USER COMPLETED ON OFF OFF ON

SelectMAP GOLDEN LOADING ON OFF ON OFF

SelectMAP GOLDEN

ON OFF ON ON

COMPLETED

JTAG COMPACT FLASH

OFF ON OFF OFF

LOADING

JTAG COMPACT FLASH

OFF ON OFF ON

COMPLETED

22 www.xilinx.com XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Page 23

Clock Generation and Distribution

Table 2-1: System Configuration Status LEDs (Continued)

LED Status

System Status

D19 (Green)

PROM Config

D20 (Green)

CF Config

D14 (Amber)

GOLDEN Config

D4 (Red)

Done

JTAG USB or PC4 LOADING OFF ON OFF OFF

JTAG USB or PC4 COMPLETED OFF ON OFF ON

Clock Generation and Distribution

The XUP Virtex-II Pro Development System supports six clock sources:

• A 100 MHz system clock (Y2),

• A 75 MHz clock (U10) for the MGTs operating the Serial Advanced Technology

Attachment (SATA) ports,

• A dual footprint through-hole user-supplied alternate clock (Y3),

• An external clock for the MGTs (J23-J24),

• A 32 MHz clock (Y4) for the System ACE interfaces, and

• A clock from the Digilent high-speed expansion module.

R

The 75 MHz SATA clock is obtained from a high stability (20 ppm) 3.3V LVDSL differential

output oscillator, and the external MGT clock is obtained from two user-supplied SMA

connectors. The remaining three oscillators are all 3.3V single-ended LVTTL sources. Each

of the oscillators is equipped with a power supply filter to reduce the noise on the clock

outputs.

Tab le 2 -2 identifies the various clock connections for the FPGA.

Table 2-2: Clock Connections

Signal FPGA Pin I/O Type

SYSTEM_CLOCK AJ15 LVCMOS25

ALTERNATE_CLOCK AH16 LVCMOS25

HS_CLKIN (from high speed

B16 LVCMOS25

expansion port)

MGT_CLK_P F16 LVDS_25

MGT_CLK_N G16 LVDS_25

EXTERNAL_CLOCK_P G15 LVDS_25

EXTERNAL_CLOCK_N F15 LVDS_25

FPGA_SYSTEMACE_CLOCK AH15 LVCMOS25

For the user to take advantage of the external differential clock inputs, two SMA

connectors must be installed at J23 and J24. These SMA connectors can be purchased from

Digi-Key® under the part number A24691-ND. Figure 2-4 identifies the location of the

external differential clock inputs.

XUP Virtex-II Pro Development System www.xilinx.com 23

UG069 (v1.0) March 8, 2005

Page 24

R

Chapter 2: Using the System

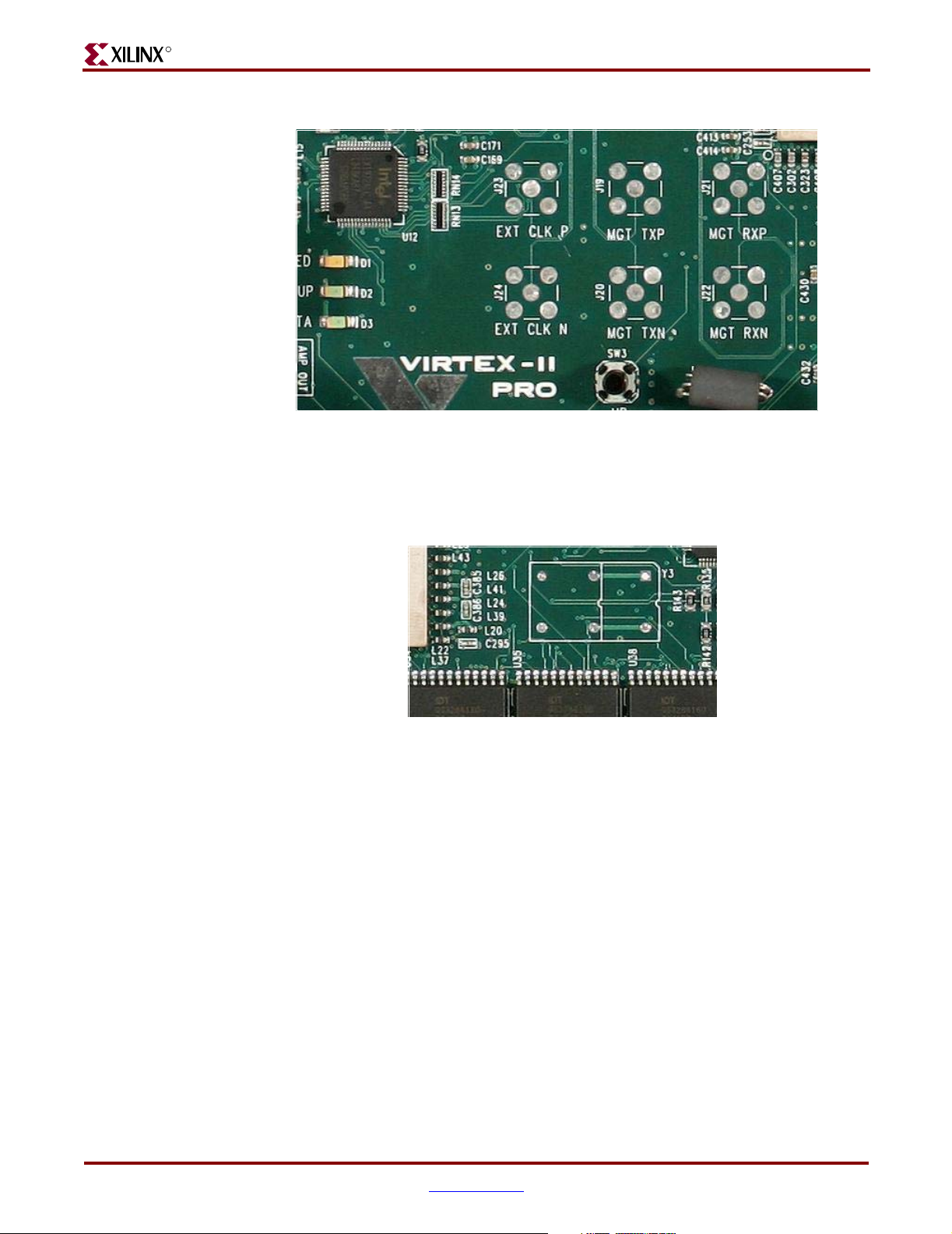

Figure 2-4: External Differential Clock Inputs

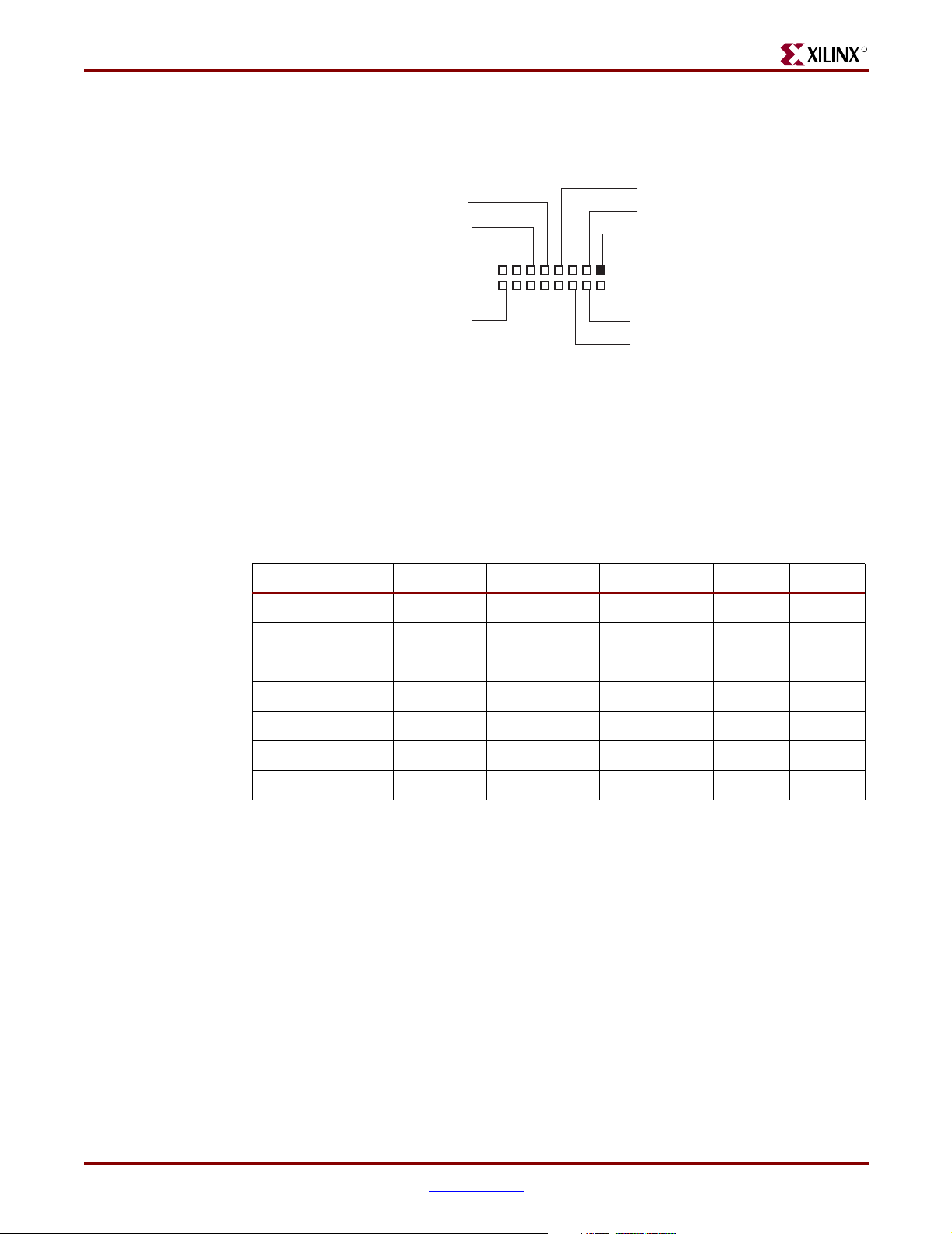

The alternate clock input is obtained from a user-supplied 3.3V oscillator. The footprint on

the printed circuit board supports either a full size (21mm x 13mm) or half size (13mm x

13mm) through-hole oscillator. Figure 2-5 identifies the location of the alternate clock

input oscillator.

Figure 2-5: Alternate Clock Input Oscillator

Using the DIMM Module DDR SDRAM

The XUP Virtex-II Pro Development System is equipped with a 184-pin Dual In-line

Memory Module (DIMM) socket that provides access up to 2 GB of Double Data Rate

SDRAM. The DDR SDRAM is an enhancement to the traditional Synchronous DRAM. It

supports data transfer on both edges of each clock cycle, effectively doubling the data

throughput of the memory device.

The DDR SDRAM operates with a differential clock: CLK and CLK_Z (the transition of

CLK going high and CLK_Z going low is considered the positive edge of the CLK)

commands (address and control signals) are registered at every positive edge of the CLK.

Input data is registered on both edges of the data strobe (DQS), and output data is

referenced to both edges of DQS, as well as both edges of CLK.

A bidirectional data strobe is transmitted by the DDR SDRAM during Reads and by the

FPGA DDR SDRAM memory controller during Writes. DQS is edge-aligned with the data

for Reads and center-aligned with the data for Writes.

24 www.xilinx.com XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Page 25

Using the DIMM Module DDR SDRAM

Read and Write accesses to the DDR SDRAM are burst oriented: accesses start at a selected

location and continue for a programmed number of locations in a programmed sequence.

Accesses begin with the registration of an Active command, which is followed by a Read or

Write command. The address bits registered coincident with the Read or Write command

are used to select the bank and starting column location for the burst address.

DDR SDRAM provides for 2, 4, 8, or full-page programmable Read or Write burst lengths.

The allowable burst lengths depend on the specific DDR SDRAM used on the DIMM

module. This information can be obtained from the serial presence detect (SPD) EEPROM.

An auto-precharge function can be enabled to provide a self-timed precharge that is

initiated at the end of the burst sequence. As with standard SDRAMs, the pipelined

multibank architecture of DDR SDRAMs allows for concurrent operation, thereby,

providing high effective bandwidth by hiding row precharge and activation time.

The modules incorporate a serial presence detect (SPD) function implemented using a

2048-bit EEPROM. The first 128 bytes of the EEPROM are programmed by the module

manufacturer to identify the module type and various SDRAM timing parameters. The

remaining 128 bytes of EEPROM are available for use as non-volatile memory. The

EEPROM is accessed using a standard I

clock) and SDRAM_SDA (serial data) signals.

Data on the SDRAM_SDA signal can change only when the clock signal SDRAM_SCL is

low. Changes in the SDRAM_SDA data signal when SDRAM_SCL is high; this indicates a

start or stop bit condition as shown in Figure 2-6. A high-to-low transition of

SDRAM_SDA when SDRAM_SCL is high indicates a start bit condition, the start of all

commands. A low-to-high transition of SDRAM_SDA when SDRAM_ SCL is high

indicates a stop bit condition, terminating the command placing the SPD device into a low

power mode.

2

C bus protocol using the SDRAM_SCL (serial

R

SDRAM_SCL

SDRAM_SDA

START BIT STOP BIT

UG069_07_082604

Figure 2-6: Definition of Start and Stop Conditions

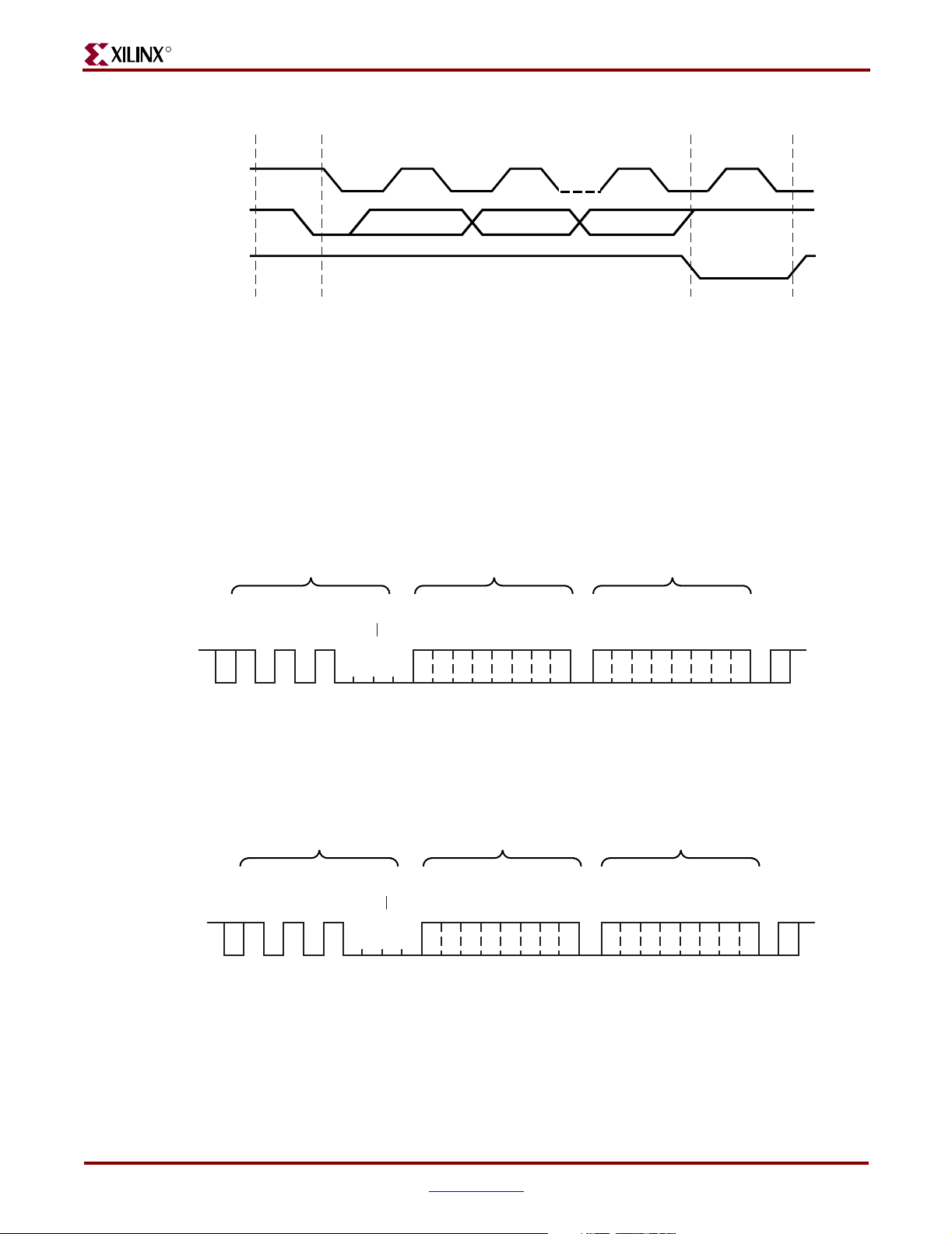

All commands commence with a start bit, followed by eight data bits. The transmitting

device, either the bus master or slave, releases the bus after transmitting eight bits. During

the ninth clock cycle, the receiver pulses the SDA data signal low to acknowledge that it

received the eight bits of data as shown in Figure 2-7.

XUP Virtex-II Pro Development System www.xilinx.com 25

UG069 (v1.0) March 8, 2005

Page 26

R

SCL FROM

MASTER

SDA OUTPUT FROM

TRANSMITTER

SDA OUTPUT FROM

RECEIVER

Chapter 2: Using the System

1289

START BIT ACKNOWLEDGE

UG069_08_021405

Figure 2-7: Acknowledge Response from Receiver

The SPD device always responds with an acknowledge after recognition of a start

condition and its slave address (100). If a read command was issued, the SPD device

transmits eight bits of data, releases the SDRAM_SDA data line, and monitors the

SDRAM_SDA data line for an acknowledge. If an acknowledge is detected and no stop bit is

generated by the master, the SPD device continues to transmit data. If no acknowledge is

detected, the SPD device terminates further data transmission and waits for the stop bit

condition to return to low power mode.

MASTER

(FPGA)

SDRAM_SDA

SLAVE

(SPD EEPROM)

MASTER

(FPGA)

SDRAM_SDA

SPD device read and write operations are shown in Figure 2-8 and Figure 2-9.

SLAVE ADDRESS

READ DATA n DATA n+1

START

0011 00011

A2A1A0

R/W

ACK

ACK

Figure 2-8: EEPROM Sequential Read

SLAVE ADDRESS

WRITE WORD ADDRESS DATA

START

0011 00011

A2

A1A0R/W

ACK

STOP

UG069_09_021405

STOP

SLAVE

(SPD EEPROM)

ACK

ACK

ACK

UG069_10_021405

Figure 2-9: EEPROM Write

26 www.xilinx.com XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Page 27

Using the DIMM Module DDR SDRAM

The ability to read the SPD EEPROM is important because the module specific timing

parameters are included in the EEPROM data and are required by the DDR SDRAM

controller to provide the highest memory throughput. The definitions of the SPD data

bytes are outlined in Tab le 2 -3.

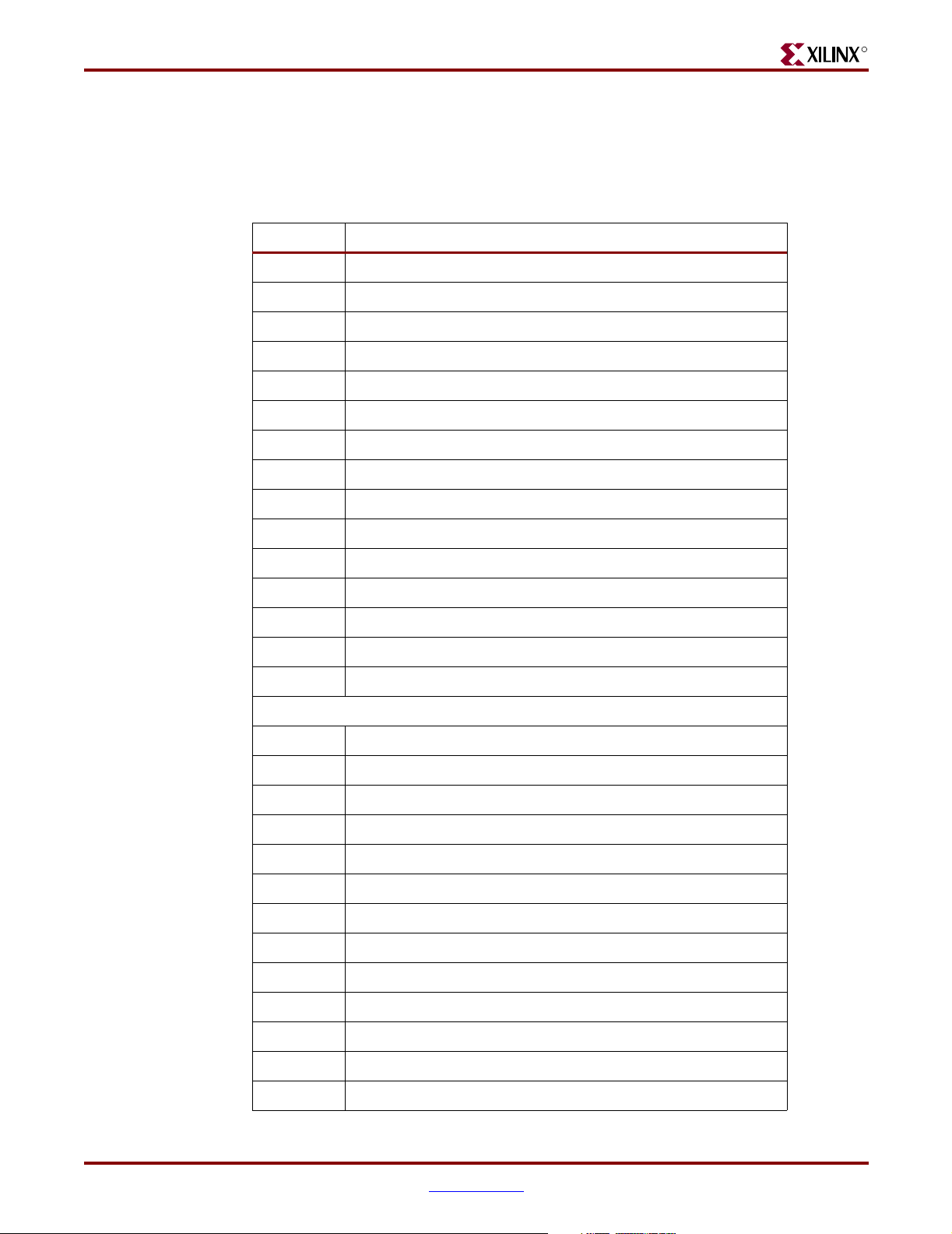

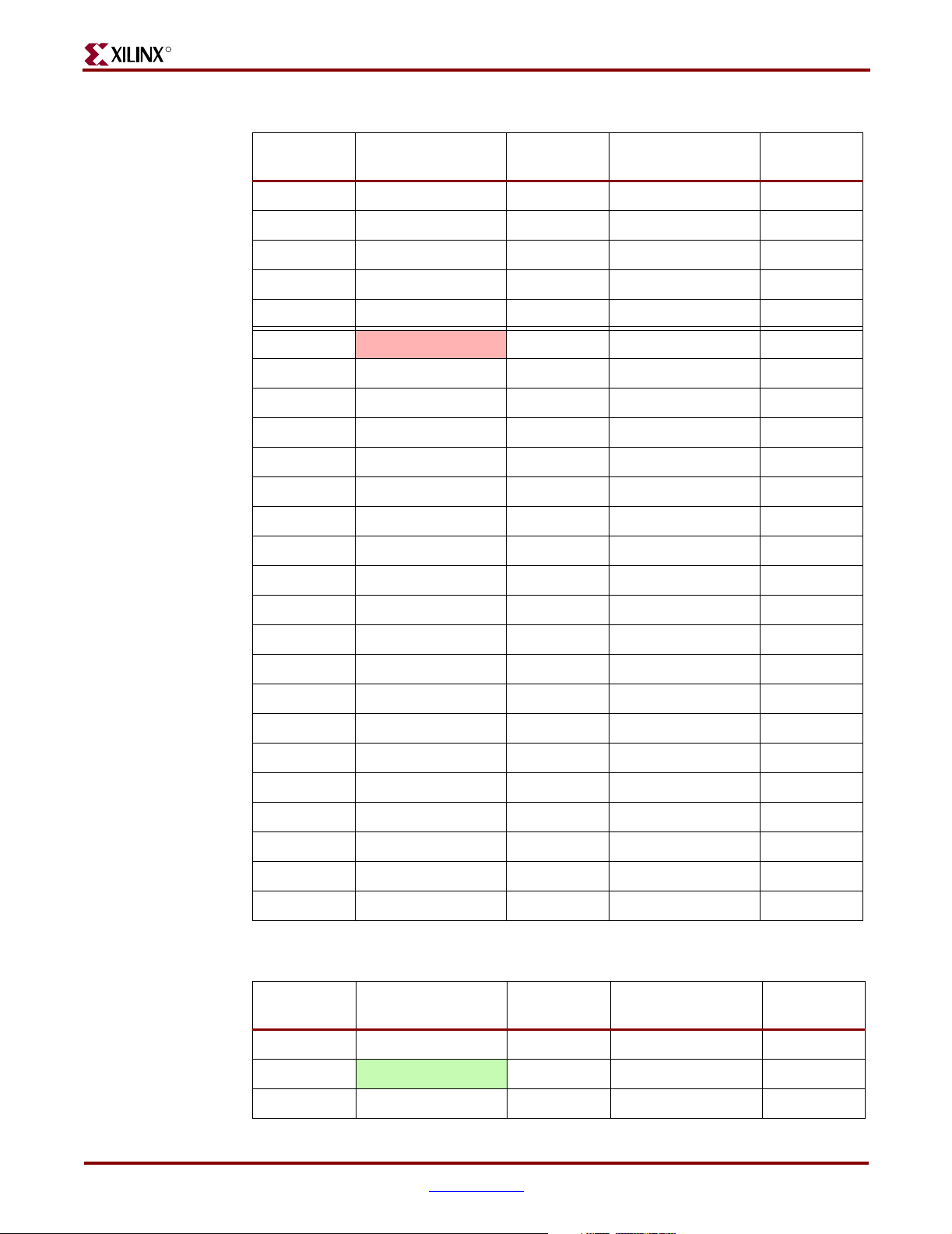

Table 2-3: SPD EEPROM Contents

Byte Description

0 Number of used bytes in SPD EEPROM

1 Total number of bytes on SPD EEPROM

2 Memory type (DDR SDRAM = 07h)

3Number of row addresses

4 Number of column addresses

5 Number of ranks (01h)

6-7 Module data width

8 Module interface voltage (SSTL 2.5V = 04h)

R

9 SDRAM cycle time (tck) (CAS LATENCY = 2.5)

10 SDRAM access time (tac) (CAS LATENCY = 2.5)

11 Module configuration type

12 Refresh rate

13 Primary SDRAM component width

14 Error checking SDRAM component width

15 Minimum clock delay from

Back-to-Back Random Column Addresses

16 Supported burst lengths

17 Number of banks on SDRAM component

18 CAS latencies supported

19 CS latency

20 WE latency

21 SDRAM module attributes

22 SDRAM attributes

23 SDRAM cycle time (tck) (CAS LATENCY =2)

24 SDRAM access time (tac) (CAS LATENCY =2)

25 SDRAM cycle time (tck) (CAS LATENCY =1)

26 SDRAM access time (tac) (CAS LATENCY =1)

27 Minimum ROW PRECHARGE time (trp)

28 Minimum ROW ACTIVE to ROW ACTIVE (trrd)

XUP Virtex-II Pro Development System www.xilinx.com 27

UG069 (v1.0) March 8, 2005

Page 28

R

Chapter 2: Using the System

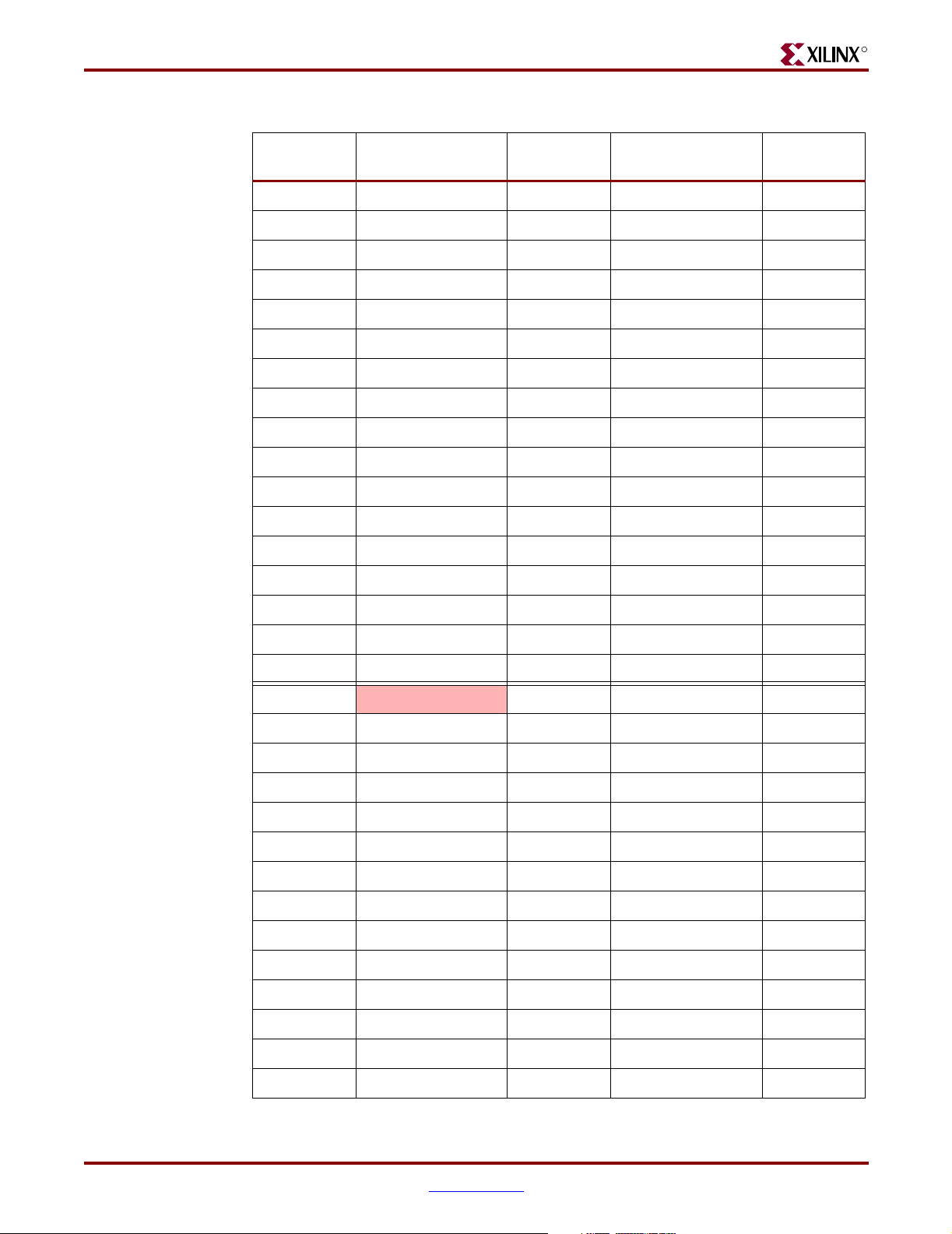

Table 2-3: SPD EEPROM Contents (Continued)

Byte Description

29 Minimum RAS# to CAS# delay (trcd)

30 Minimum RAS# pulse width (tras)

31 Module rank density

32 Command and address setup time (tas, tcms)

33 Command and address hold time (tah, tcmh)

34 Data setup time (tds)

35 Data hold time (tdh)

36-40 Reserved

41 Minimum ACTIVE/AUTO REFRESH time

42 Minimum AUTO REFRESH to ACTIVE/AUTO REFRESH

command period

43 Max cycle time

44 Max DQS-DQ skew

45 Max READ HOLD time

46 Reserved

47 DIMM height

48-61 Reserved

62 SPD revision

63 CHECKSUM for bytes 0-62

64-71 Manufacturer's JEDEC ID code

72 Manufacturing location

73-90 Module part number (ASCII)

91-92 Module revision code

93 Year of manufacture (BCD)

94 Week of manufacturer (BCD)

95-98 Module serial number

99-127 Reserved

128-255 User defined contents

The DIMM module is supplied with three differential clocks. These three clock signals are

matched in length to each other and the DDR SDRAM feedback signals to allow for fully

synchronous operation across all banks of memory. The DDR SDRAM clocks are driven by

Double Data Rate (DDR) output registers, connected to a Digital Clock Manager (DCM)

with an optional external feedback connection. The DDR SDRAM controller logic is

described in DS425

28 www.xilinx.com XUP Virtex-II Pro Development System

, PLB Double Data Rate (DDR) Synchronous DRAM (SDRAM) Controller.

UG069 (v1.0) March 8, 2005

Page 29

Using the DIMM Module DDR SDRAM

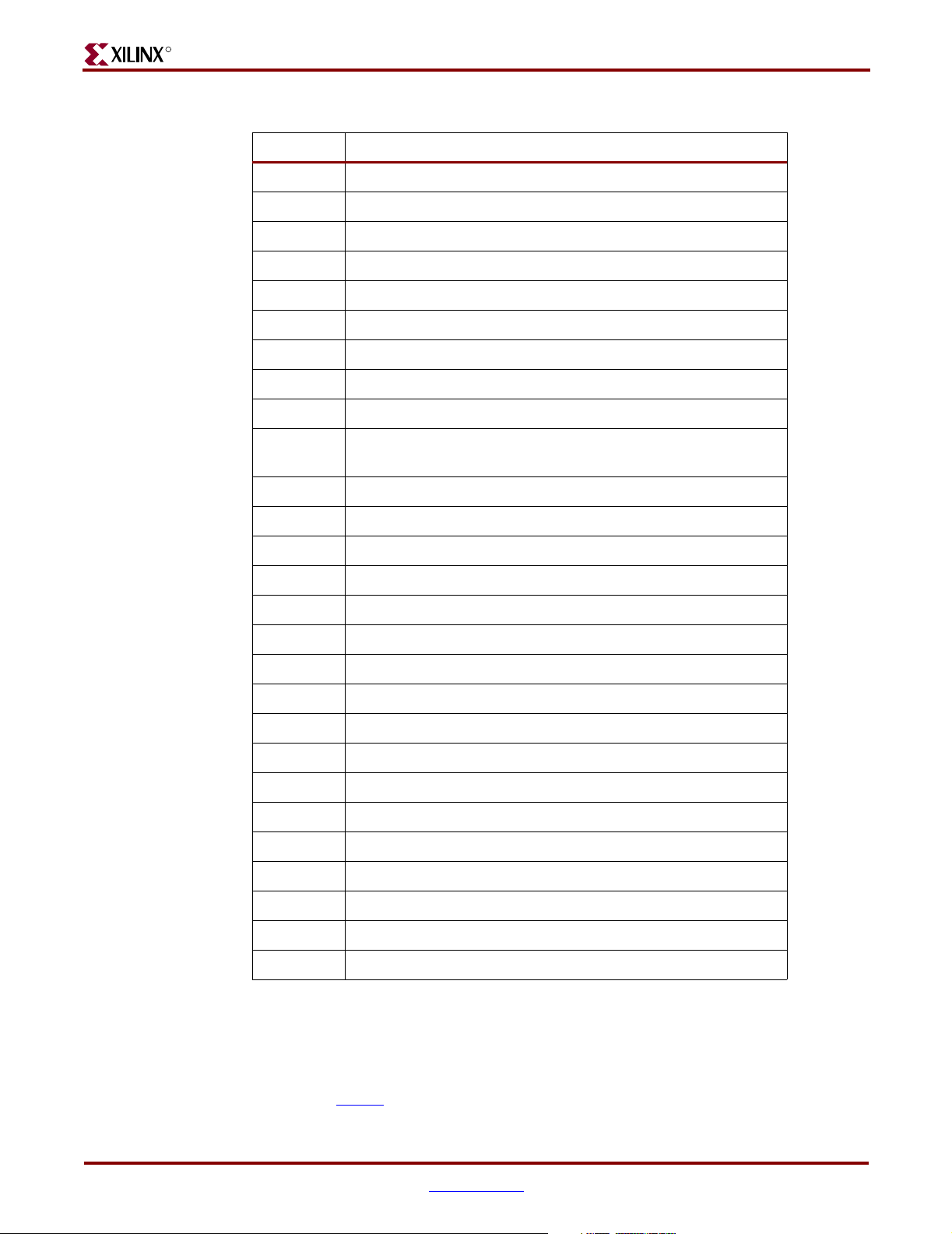

The Xilinx PLB DDR SDRAM controller is a soft IP core designed for Xilinx FPGAs that

support different CAS latencies and memory data widths set by design parameters.

The DDR SDRAM controller logic instantiates DDR input and output registers on the

address, data, and control signals, so the clock to output delays match the clock output

delay. The DDR SDRAM clocking structure as shown in Figure 2-10 is a simplified version

of the clocking structure mentioned in DS425

R

.

ug069_23_021505

Figure 2-10: Clock Generation for the DDR SDRAM

XUP Virtex-II Pro Development System www.xilinx.com 29

UG069 (v1.0) March 8, 2005

Page 30

R

Chapter 2: Using the System

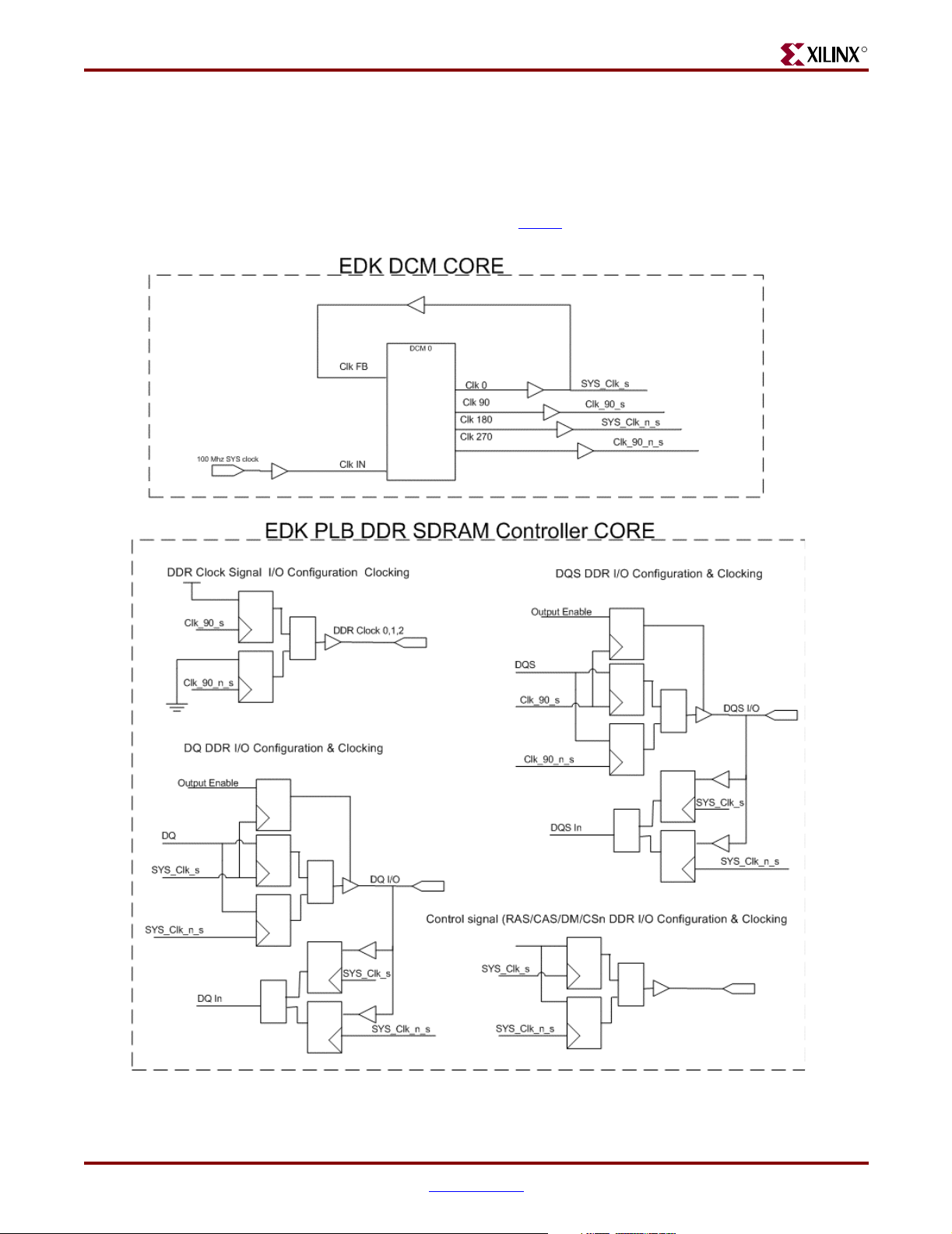

Xilinx has qualified several different types of PC2100 memory modules for use in the XUP

Virtex-II Pro Development System. These modules cover various densities, organizations,

and features. The qualified memory modules are identified in Ta bl e 2-4 .

For an updated list of supported modules, consult the XUP Virtex-II Pro Development

System support Web site at:

http://www.xilinx.com/univ/xupv2p.html

The data bus width, number of ranks, address range, clock latency, and output type are all

parameters that are used by the DDR memory controller design to create the correct

memory controller for the user application.

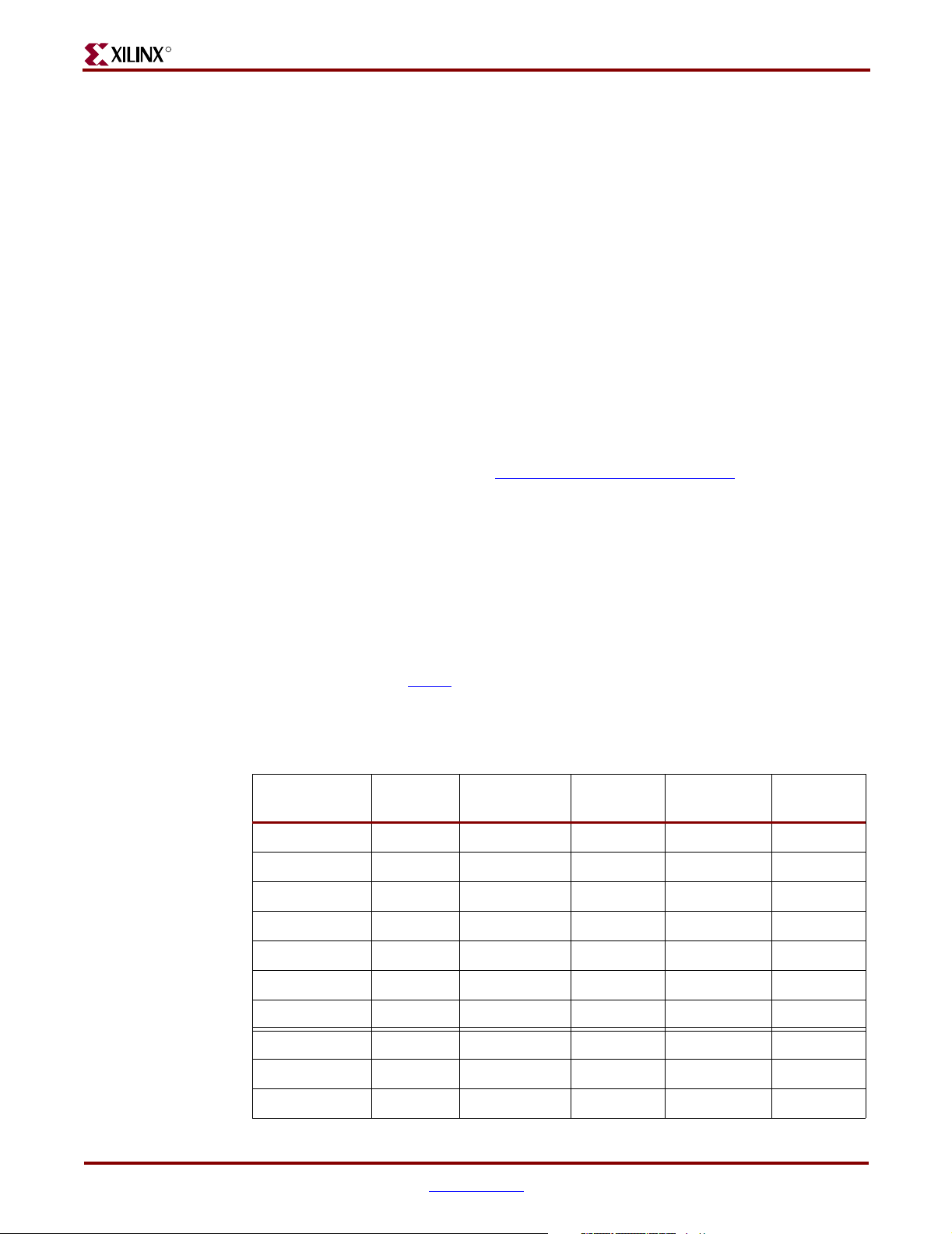

Table 2-4: Qualified SDRAM Memory Modules

Crucial® Technology

Part Number

Memory

Organization

Number of

Ranks

Unbuffered or

Registered

CAS

Latency

CT6472Z265.18T* 512 MB 64M X 72 Dual Unbuffered 2.5

CT6464Z265.16T* 512 MB 64M X 64 Dual Unbuffered 2.5

CT6472Z265.9T* 512 MB 64M X 72 Single Unbuffered 2.5

CT6464Z265.8T* 512 MB 64M X 64 Single Unbuffered 2.5

CT1664Z265.4T* 128 MB 16M X 64 Single Unbuffered 2.5

Notes:

The * in the Crucial part number represents the revision number of the module, which is not

required to order the module.

These memory modules are designed for a maximum clock frequency of at least 133 MHz

and have a CAS latency of 2.5 (18.8 ns). The PLB Double Data Rate Synchronous DRAM

Controller supports CAS latencies of two or three clock cycles.

If the memory system is to operate at 100 MHz, then set the CAS latency parameter in the

controller design to 2 (20 ns). If full speed (133MHz) memory operation is required, then

set the CAS latency parameter in the controller design to 3 (22.6 ns).

Tab le 2 -5 provides the details on the FPGA to DDR SDRAM DIMM module connections.

Table 2-5: DDR SDRAM Connections

Signal Direction

DIMM

Module Pin

FPGA

Pin

I/O Type

SDRAM_DQ[0] I/O 2 C27 SSTL2-II

SDRAM_DQ[1] I/O 4 D28 SSTL2-II

SDRAM_DQ[2] I/O 6 D29 SSTL2-II

SDRAM_DQ[3] I/O 8 D30 SSTL2-II

SDRAM_DQ[4] I/O 94 H25 SSTL2-II

SDRAM_DQ[5] I/O 95 H26 SSTL2-II

SDRAM_DQ[6] I/O 98 E27 SSTL2-II

SDRAM_DQ[7] I/O 99 E28 SSTL2-II

SDRAM_DQS[0] I/O 5 E30 SSTL2-II

SDRAM_DM[0] 0 97 U26 SSTL2-II

30 www.xilinx.com XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Page 31

Using the DIMM Module DDR SDRAM

Table 2-5: DDR SDRAM Connections (Continued)

R

Signal Direction

DIMM

Module Pin

FPGA

Pin

I/O Type

SDRAM_DQ[8] I/O 12 J26 SSTL2-II

SDRAM_DQ[9] I/O 13 G27 SSTL2-II

SDRAM_DQ[10] I/O 19 G28 SSTL2-II

SDRAM_DQ[11] I/O 20 G30 SSTL2-II

SDRAM_DQ[12] I/O 105 L23 SSTL2-II

SDRAM_DQ[13] I/O 106 L24 SSTL2-II

SDRAM_DQ[14] I/O 109 H27 SSTL2-II

SDRAM_DQ[15] I/O 110 H28 SSTL2-II

SDRAM_DQS[1] I/O 14 J29 SSTL2-II

SDRAM_DM[1] 0 107 V29 SSTL2-II

SDRAM_DQ[16] I/O 23 J27 SSTL2-II

SDRAM_DQ[17] I/O 24 J28 SSTL2-II

SDRAM_DQ[18] I/O 28 K29 SSTL2-II

SDRAM_DQ[19] I/O 31 L29 SSTL2-II

SDRAM_DQ[20] I/O 114 N23 SSTL2-II

SDRAM_DQ[21] I/O 117 N24 SSTL2-II

SDRAM_DQ[22] I/O 121 K27 SSTL2-II

SDRAM_DQ[23] I/O 123 K28 SSTL2-II

SDRAM_DQS[2] I/O 25 M30 SSTL2-II

SDRAM_DM[2] 0 119 W29 SSTL2-II

SDRAM_DQ[24] I/O 33 R22 SSTL2-II

SDRAM_DQ[25] I/O 35 M27 SSTL2-II

SDRAM_DQ[26] I/O 39 M28 SSTL2-II

SDRAM_DQ[27] I/O 40 P30 SSTL2-II

SDRAM_DQ[28] I/O 126 P23 SSTL2-II

SDRAM_DQ[29] I/O 127 P24 SSTL2-II

SDRAM_DQ[30] I/O 131 N27 SSTL2-II

SDRAM_DQ[31] I/O 133 N28 SSTL2-II

SDRAM_DQS[3] I/O 36 P29 SSTL2-II

SDRAM_DM[3] 0 129 T22 SSTL2-II

SDRAM_DQ[32] I/O 53 V27 SSTL2-II

XUP Virtex-II Pro Development System www.xilinx.com 31

UG069 (v1.0) March 8, 2005

Page 32

R

Chapter 2: Using the System

Table 2-5: DDR SDRAM Connections (Continued)

Signal Direction

DIMM

Module Pin

FPGA

Pin

I/O Type

SDRAM_DQ[33] I/O 55 Y30 SSTL2-II

SDRAM_DQ[34] I/O 57 U24 SSTL2-II

SDRAM_DQ[35] I/O 60 U23 SSTL2-II

SDRAM_DQ[36] I/O 146 V26 SSTL2-II

SDRAM_DQ[37] I/O 147 V25 SSTL2-II

SDRAM_DQ[38] I/O 150 Y29 SSTL2-II

SDRAM_DQ[39] I/O 151 AA29 SSTL2-II

SDRAM_DQS[4] I/O 56 V23 SSTL2-II

SDRAM_DM[4] 0 149 W28 SSTL2-II

SDRAM_DQ[40] I/O 61 Y26 SSTL2-II

SDRAM_DQ[41] I/O 64 AA28 SSTL2-II

SDRAM_DQ[42] I/O 68 AA27 SSTL2-II

SDRAM_DQ[43] I/O 69 W24 SSTL2-II

SDRAM_DQ[44] I/O 153 W23 SSTL2-II

SDRAM_DQ[45] I/O 155 AB28 SSTL2-II

SDRAM_DQ[46] I/O 161 AB27 SSTL2-II

SDRAM_DQ[47] I/O 162 AC29 SSTL2-II

SDRAM_DQS[5] I/O 67 AA25 SSTL2-II

SDRAM_DM[5] 0 159 W27 SSTL2-II

SDRAM_DQ[48] I/O 72 AB25 SSTL2-II

SDRAM_DQ[49] I/O 73 AE29 SSTL2-II

SDRAM_DQ[50] I/O 79 AA24 SSTL2-II

SDRAM_DQ[51] I/O 80 AA23 SSTL2-II

SDRAM_DQ[52] I/O 165 AD28 SSTL2-II

SDRAM_DQ[53] I/O 166 AD27 SSTL2-II

SDRAM_DQ[54] I/O 170 AF30 SSTL2-II

SDRAM_DQ[55] I/O 171 AF29 SSTL2-II

SDRAM_DQS[6] I/O 78 AC25 SSTL2-II

SDRAM_DM[6] 0 169 W26 SSTL2-II

SDRAM_DQ[56] I/O 83 AF25 SSTL2-II

SDRAM_DQ[57] I/O 84 AG30 SSTL2-II

32 www.xilinx.com XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Page 33

Using the DIMM Module DDR SDRAM

Table 2-5: DDR SDRAM Connections (Continued)

R

Signal Direction

DIMM

Module Pin

FPGA

Pin

I/O Type

SDRAM_DQ[58] I/O 87 AG29 SSTL2-II

SDRAM_DQ[59] I/O 88 AD26 SSTL2-II

SDRAM_DQ[60] I/O 174 AD25 SSTL2-II

SDRAM_DQ[61] I/O 175 AG28 SSTL2-II

SDRAM_DQ[62] I/O 178 AH27 SSTL2-II

SDRAM_DQ[63] I/O 179 AH29 SSTL2-II

SDRAM_DQS[7] I/O 86 AH26 SSTL2-II

SDRAM_DM[7] 0 177 W25 SSTL2-II

SDRAM_CB[0] I/O 44 R28 SSTL2-II

SDRAM_CB[1] I/O 45 U30 SSTL2-II

SDRAM_CB[2] I/O 49 V30 SSTL2-II

SDRAM_CB[3] I/O 51 T26 SSTL2-II

SDRAM_CB[4] I/O 134 T25 SSTL2-II

SDRAM_CB[5] I/O 135 T28 SSTL2-II

SDRAM_CB[6] I/O 142 T27 SSTL2-II

SDRAM_CB[7] I/O 144 U28 SSTL2-II

SDRAM_DQS[8] I/O 47 T23 SSTL2-II

SDRAM_DM[8] 0 140 U22 SSTL2-II

SDRAM_A[0] O 48 M25 SSTL2-II

SDRAM_A[1] O 43 N25 SSTL2-II

SDRAM_A[2] O 41 L26 SSTL2-II

SDRAM_A[3] O 130 M29 SSTL2-II

SDRAM_A[4] O 37 K30 SSTL2-II

SDRAM_A[5] O 32 G25 SSTL2-II

SDRAM_A[6] O 125 G26 SSTL2-II

SDRAM_A[7] O 29 D26 SSTL2-II

SDRAM_A[8] O 122 J24 SSTL2-II

SDRAM_A[9] O 27 K24 SSTL2-II

SDRAM_A[10] O 141 F28 SSTL2-II

SDRAM_A[11] O 118 F30 SSTL2-II

SDRAM_A[12] O 115 M24 SSTL2-II

XUP Virtex-II Pro Development System www.xilinx.com 33

UG069 (v1.0) March 8, 2005

Page 34

R

Chapter 2: Using the System

Table 2-5: DDR SDRAM Connections (Continued)

Signal Direction

DIMM

Module Pin

FPGA

Pin

I/O Type

SDRAM_A[13] O 167 M23 SSTL2-II

SDRAM_CK0 O 137 AC27 SSTL2-II

SDRAM_CK0_Z O 138 AC28 SSTL2-II

SDRAM_CK1 O 16 AD29 SSTL2-II

SDRAM_CK1_Z O 17 AD30 SSTL2-II

SDRAM_CK2 O 76 AB23 SSTL2-II

SDRAM_CK2_Z O 75 AB24 SSTL2-II

CLK_FEEDBACK O – G23 LVCMOS25

CLK_FEEDBACK I – C16 LVCMOS25

SDRAM_CKE0 O 21 R26 SSTL2-II

SDRAM_CKE1 O 111 R25 SSTL2-II

SDRAM_RAS_Z O 154 N29 SSTL2-II

SDRAM_CAS_Z O 65 L27 SSTL2-II

SDRAM_WE_Z O 63 N26 SSTL2-II

SDRAM_S0_Z O 157 R24 SSTL2-II

SDRAM_S1_Z O 158 R23 SSTL2-II

SDRAM_BA0 O 59 M26 SSTL2-II

SDRAM_BA1 O 52 K26 SSTL2-II

SDRAM_SDA I/O 91 AF23 LVCMOS25

SDRAM_SCL O 92 AF22 LVCMOS25

SDRAM_SA0 NA 181 – NA

SDRAM_SA1 NA 182 – NA

SDRAM_SA2 NA 183 – NA

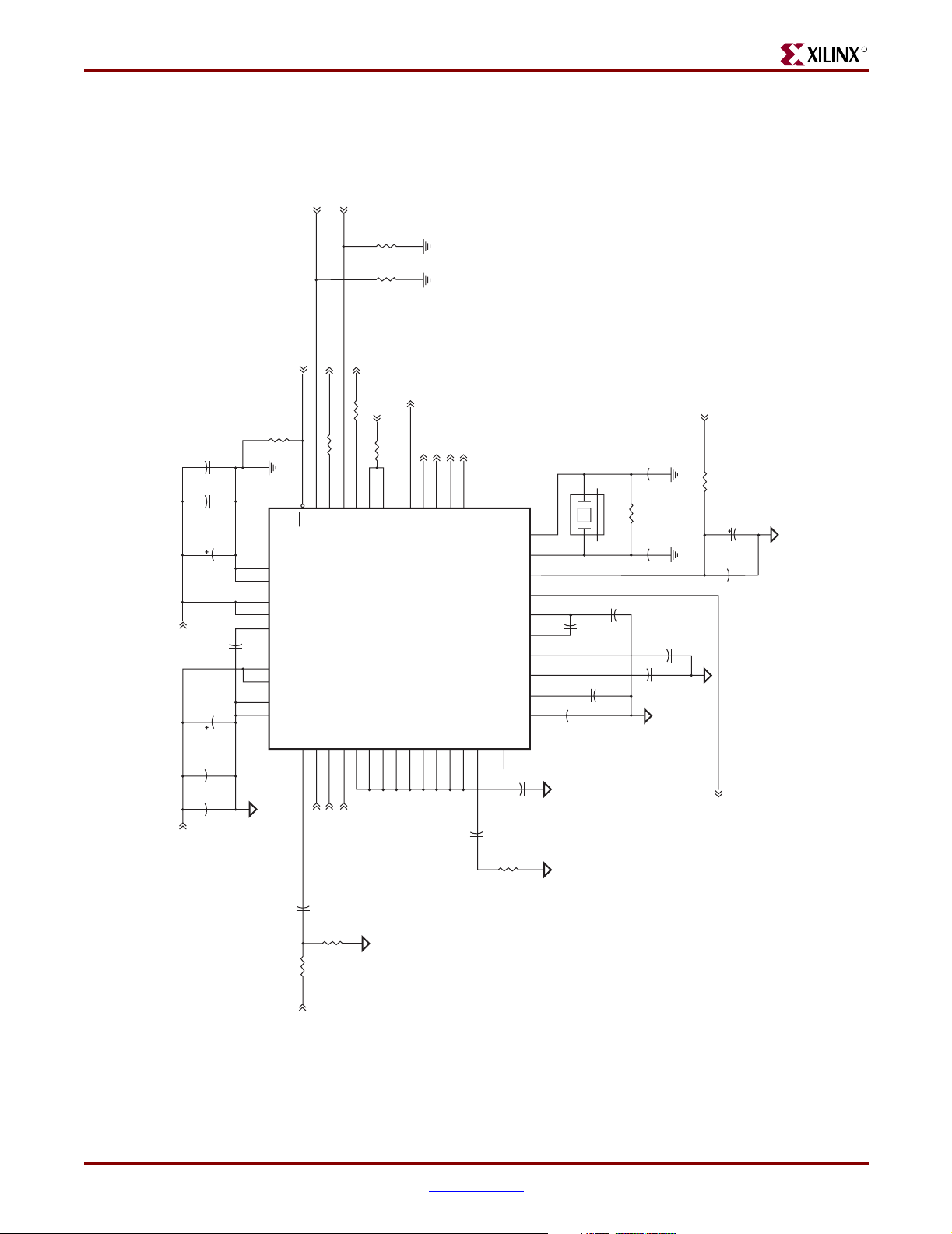

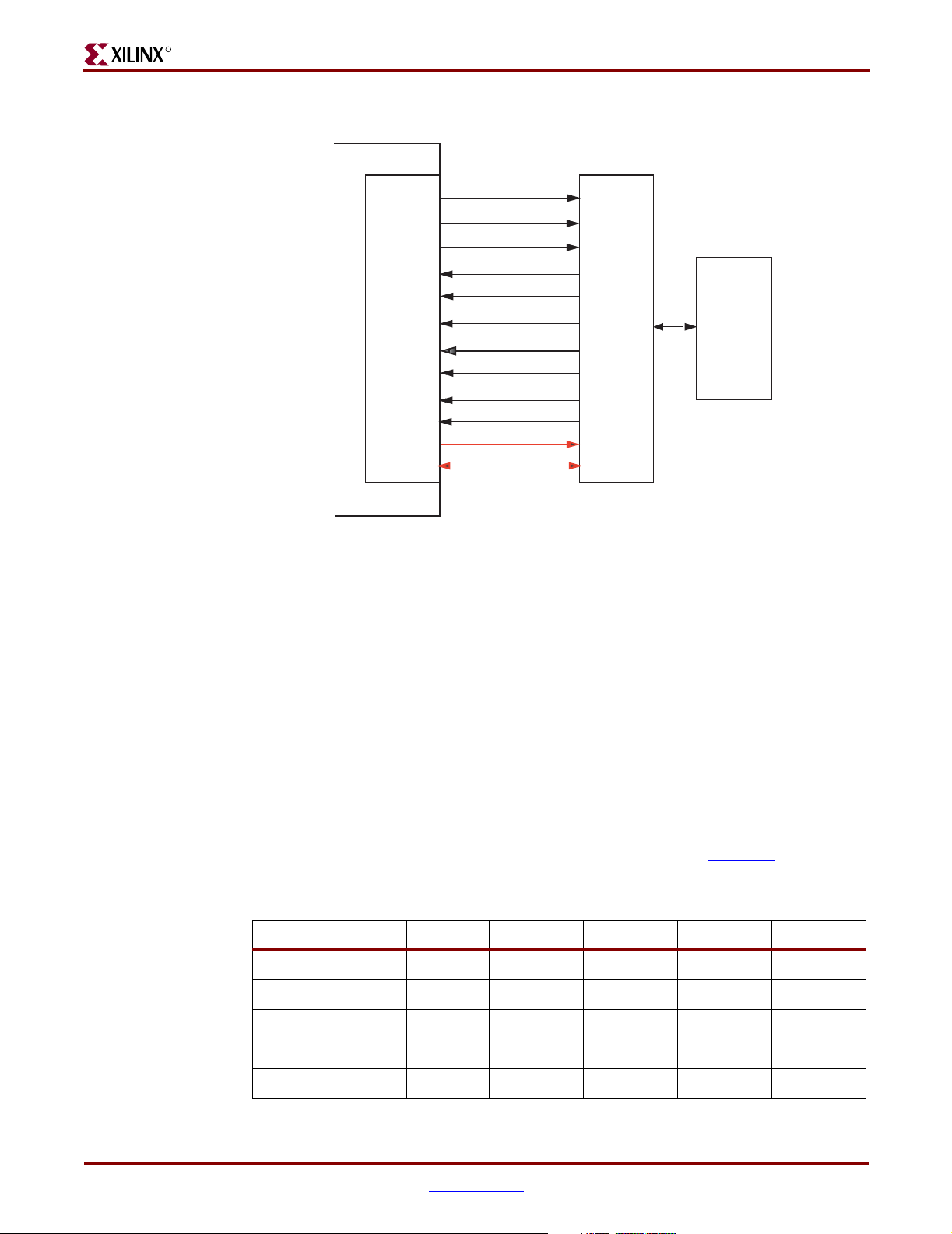

Using the XSGA Output

The XSGA output on the XUP Virtex-II Pro Development System is made up from a triple

8-bit DAC (U29), a high density 15-pin D-Sub connector (J13), and IP placed in the FPGA

fabric. The FMS3818 video DAC is a low-cost DAC tailored to fit graphics and video

applications, with a maximum pixel clock of 180 MHz. The TTL data inputs and control

signals are converted into analog current outputs that can drive 25Ω to 37.5Ω loads,

corresponding to a doubly-terminated 50Ω to 75Ω load. The VGA_OUT_BLANK_Z input

overrides the RGB inputs and blanks the display output. This signal is equipped with a

pull-down resistor (R120) to keep the display blanked when the FPGA is not programmed

or XSGA output is not required by the user application. The XSGA output circuit is shown

in Figure 2-11.

34 www.xilinx.com XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Page 35

Using the XSGA Output

R

Design files supplied by Xilinx generate the required timing signals

VGA_OUT_BLANK_Z, VGA_HSYNCH, VGA_VSYNCH, and VGA_COMP_SYNCH, as

well as memory addressing for bit- and character-mapped display RAM. Charactermapped mode allows for the display of extended ASCII characters in an 8 x 8 pixel block

without having to draw the character pixel by pixel. Compile time parameters are passed

to the Verilog code that defines the XSGA controller operation. The 100 MHz clock is used

as a source for one of the DCMs to create the video clock. By setting appropriate M and D

values for the DCM, various VGA_OUT_PIXEL_CLOCK rates can be created.

XUP Virtex-II Pro Development System www.xilinx.com 35

UG069 (v1.0) March 8, 2005

Page 36

R

J13

123456789

VGA OUTPUT

VGA_RED_OUT

VGA_GREEN_OUT

VGA_BLUE_OUT

R116

1011121314

R117

82R5 1%

15

HD-15PIN VGA DSUB

VGA_GND

82R5 1%

Chapter 2: Using the System

UG069_12_101804

VGA_GND

R115

R114

R113

VGA_HSYNCH

75R0 1%

75R0 1%

75R0 1%

33

IOR

U29

R0R1R2R3R4R5R6R7G0G1G2G3G4G5G6G7B0B1B2B3B4B5B6

40

41424344454647

VGA_VSYNCH

32

IOG

2345678

29

IOB

9

16171819202122

VGA_VCC

C458

VGA_GND

0.1UF

C457

0.1UF

R119

348.1%

GND1

GND2

GND3

GND4

VAA1

VAA2NCNCNCNC

GND5

GND6

39382827151448

R120

GND7

3K3

TRIPLE 8 BIT

VIDEO DAC

FMS3818KRC

GND

1

36

35

34

RSET

CLOCK

VGA_VCC

GND0

VDD

31123013242537

COMP

VREF

BLANK

SYNC

B7

23

11

10

VGA_OUT_RED0

VGA_OUT_RED1

VGA_OUT_RED2

VGA_OUT_RED3

VGA_OUT_RED4

VGA_OUT_RED5

VGA_OUT_RED6

VGA_OUT_RED7

VGA_OUT_GREEN0

VGA_OUT_GREEN1

VGA_OUT_GREEN2

VGA_OUT_GREEN3

VGA_OUT_BLUE0

VGA_OUT_GREEN4

VGA_OUT_BLUE1

VGA_OUT_GREEN5

VGA_OUT_GREEN6

VGA_OUT_GREEN7

VGA_OUT_BLUE2

VGA_OUT_BLUE3

VGA_OUT_BLUE4

VGA_OUT_BLUE5

VGA_OUT_BLUE6

VGA_OUT_BLUE7

VGA_COMP_SYNCH

VGA_OUT_BLANK_Z

R118

20R0 1%

VGA_OUT_PIXEL_CLOCK

Figure 2-11: XSGA Output

36 www.xilinx.com XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Page 37

Using the XSGA Output

R

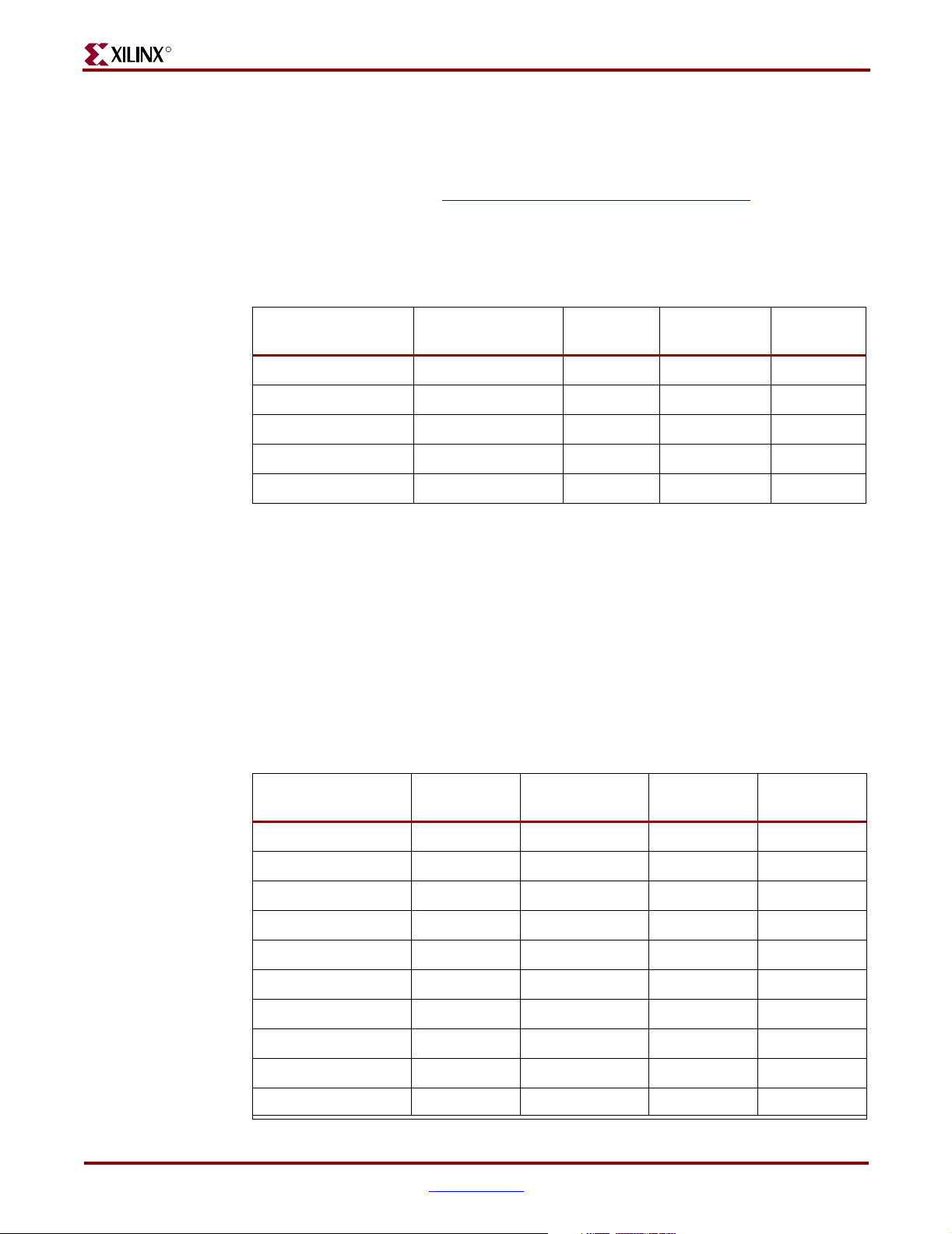

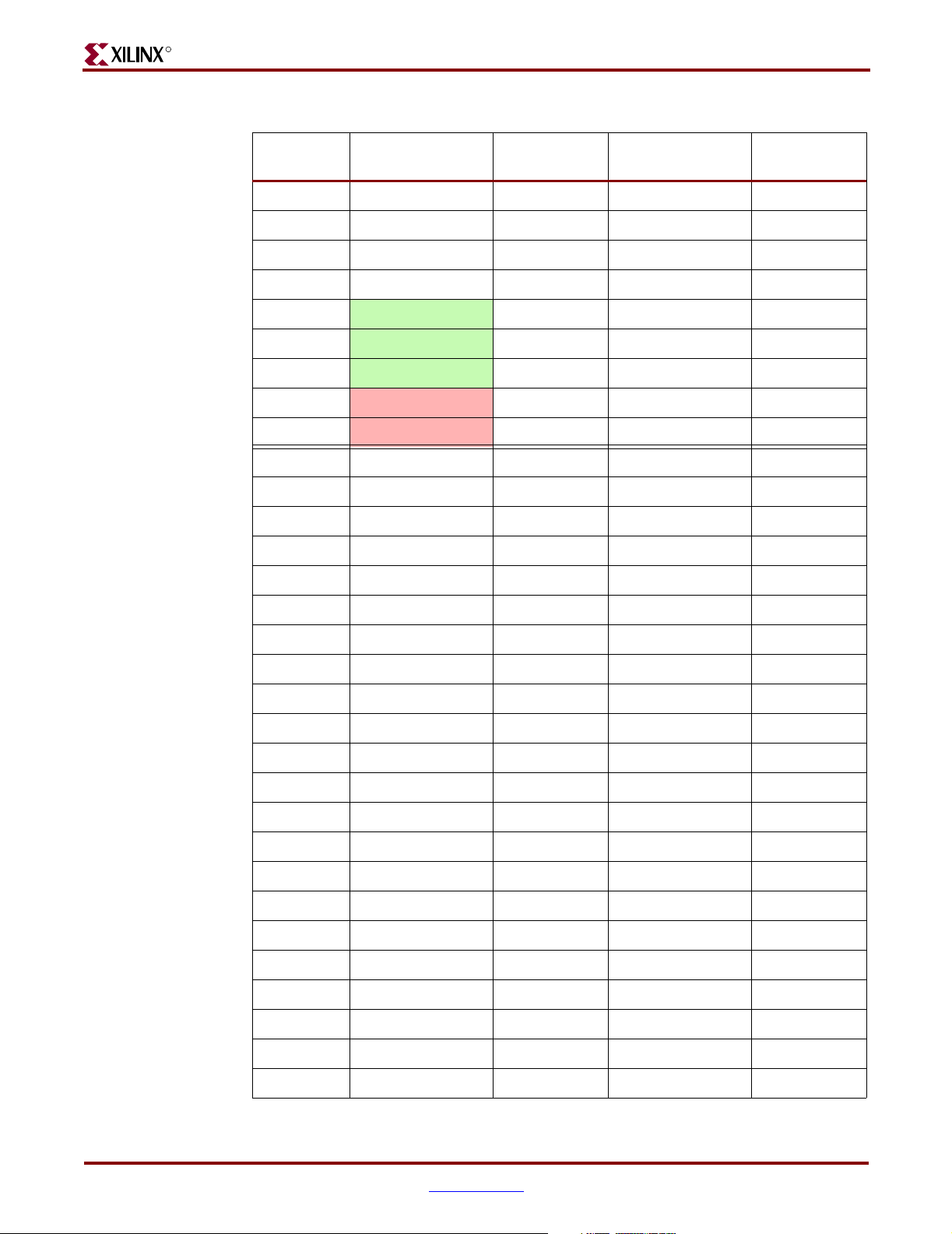

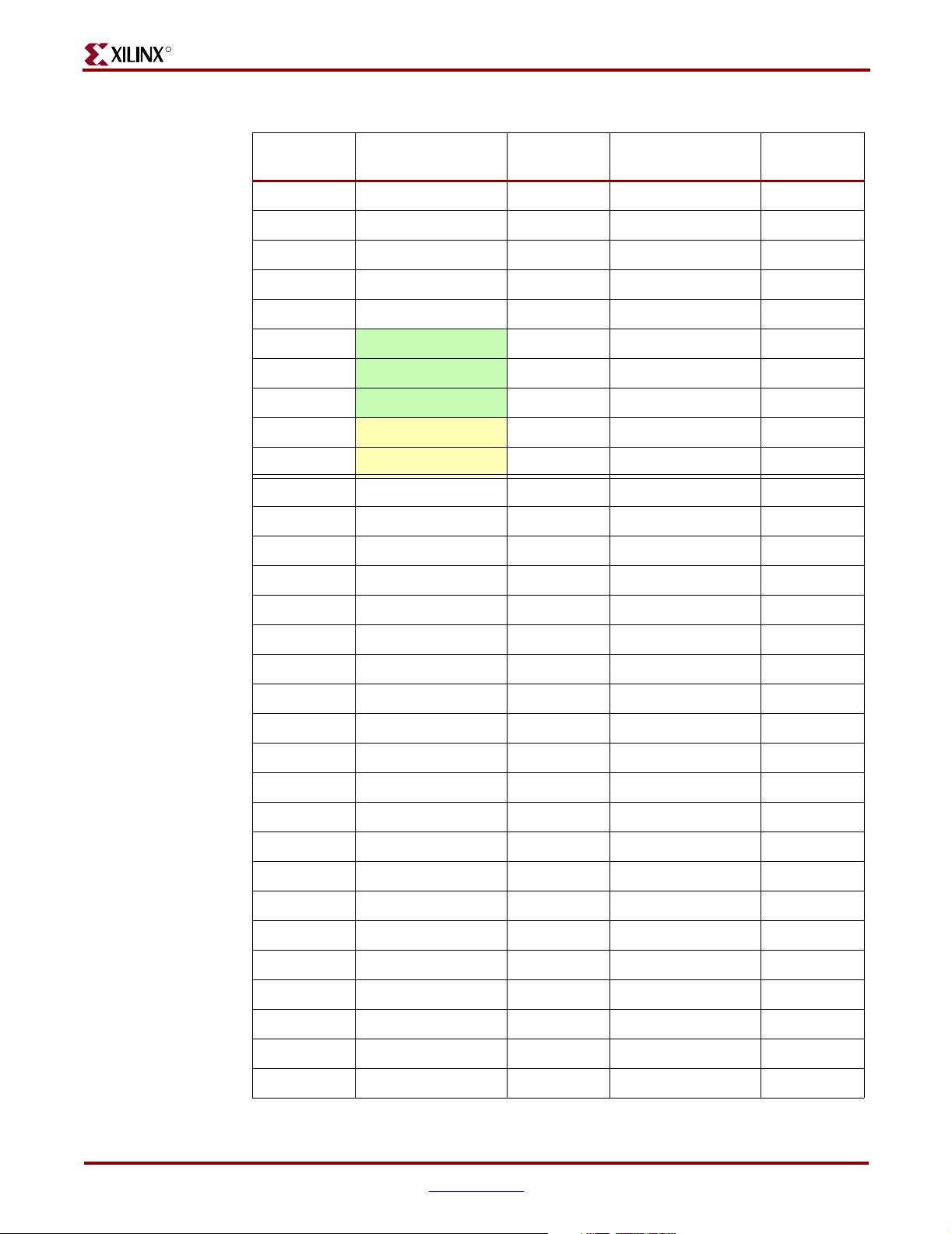

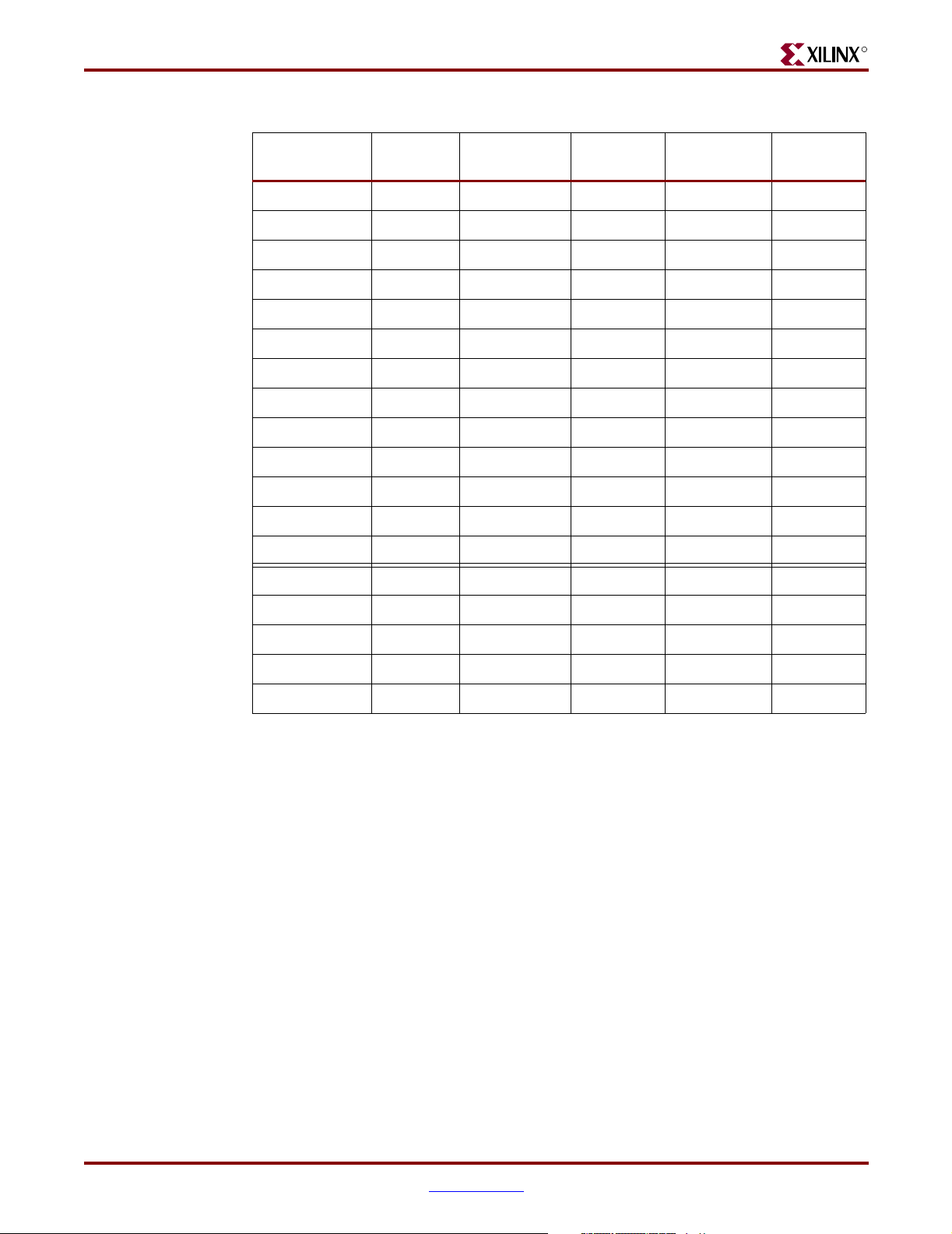

Tab le 2 -6 lists the Verilog parameter values and the DCM settings for various XSGA output

formats.

Note:

The highlighted settings are exact VESA settings; the others are approximations.

Table 2-6: DCM and XSGA Controller Settings for Various XSGA Formats

Verilog Horizontal Timing Parameters

Output

Format

Pixel

Clock

DCM

Settings

H Active H FP H Synch H BP H Total

MHz M D Pixels Pixels Pixels Pixels Pixels

640 x 480 @ 60 Hz 25.00 1 4 640 16 96 48 800

640 x 480 @ 72 Hz 31.25 5 16 640 24 40 128 832

640 x 480 @ 75 Hz 31.25 5 16 640 18 96 42 796

640 x 480 @ 85 Hz 35.71 5 14 640 32 48 108 828

800 x 600 @ 60 Hz 40.00 4 10 800 40 128 88 1056

800 x 600 @ 72 Hz 50.00 1 2 800 56 120 64 1040

800 x 600 @ 75 Hz 50.00 1 2 800 16 80 168 1064

800 x 600 @ 85 Hz 55.00 11 20 800 32 64 144 1040

1024 x 768 @ 60 Hz 65.00 13 20 1024 24 136 160 1344

1024 x 768 @ 72 Hz 75.00 15 20 1024 16 96 172 1308

1024 x 768 @ 75 Hz 80.00 8 10 1024 24 96 184 1328

1024 x 768 @ 85 Hz 95.00 19 20 1024 48 96 208 1376

1280 x 1024 @ 60 Hz 110.00 11 10 1280 52 120 256 1708

1280 x 1024 @ 72 Hz 130.00 13 10 1280 16 144 248 1688

1280 x 1024 @ 75 Hz 135.00 27 20 1280 16 144 248 1688

1280 x 1024 @ 85 Hz 150.00 3 2 1280 40 144 224 1688

1200 x 1600 @ 60 Hz 160.00 16 10 1600 56 192 296 2144

1200 x 1600 @ 70 Hz 180.00 18 10 1600 40 184 256 2080

Verilog Vertical Timing Parameters

Output

Format

Pixel

Clock

DCM

Settings

V Active V FP V Synch V BP V Total

MHz M D Pixels Pixels Pixels Pixels Pixels

640 x 480 @ 60 Hz 25.00 1 4 480 9 2 29 520

640 x 480 @ 72 Hz 31.25 5 16 480 10 3 29 522

640 x 480 @ 75 Hz 31.25 5 16 480 11 2 31 524

640 x 480 @ 85 Hz 35.71 5 14 480 1 3 23 507

800 x 600 @ 60 Hz 40.00 4 10 600 1 4 23 628

800 x 600 @ 72 Hz 50.00 1 2 600 37 6 23 666

XUP Virtex-II Pro Development System www.xilinx.com 37

UG069 (v1.0) March 8, 2005

Page 38

R

Chapter 2: Using the System

Table 2-6: DCM and XSGA Controller Settings for Various XSGA Formats (Continued)

Verilog Horizontal Timing Parameters

Output

Format

Pixel

Clock

DCM

Settings

H Active H FP H Synch H BP H Total

MHz M D Pixels Pixels Pixels Pixels Pixels

800 x 600 @ 75 Hz 50.00 1 2 600 1 2 23 626

800 x 600 @ 85 Hz 55.00 11 20 600 1 3 18 622

1024 x 768 @ 60 Hz 65.00 13 20 768 3 6 29 806

1024 x 768 @ 72 Hz 75.00 15 20 768 1 3 24 796

1024 x 768 @ 75 Hz 80.00 8 10 768 2 4 29 803

1024 x 768 @ 85 Hz 95.00 19 20 768 2 4 38 812

1280 x 1024 @ 60 Hz 110.00 11 10 1024 3 5 42 1074

1280 x 1024 @ 72 Hz 130.00 13 10 1024 2 4 40 1070

1280 x 1024 @ 75 Hz 135.00 27 20 1024 1 3 38 1066

1280 x 1024 @ 85 Hz 150.00 3 2 1024 1 3 28 1056

1200 x 1600 @ 60 Hz 160.00 16 10 1200 1 3 40 1244

1200 x 1600 @ 70 Hz 180.00 18 10 1200 1 3 38 1242

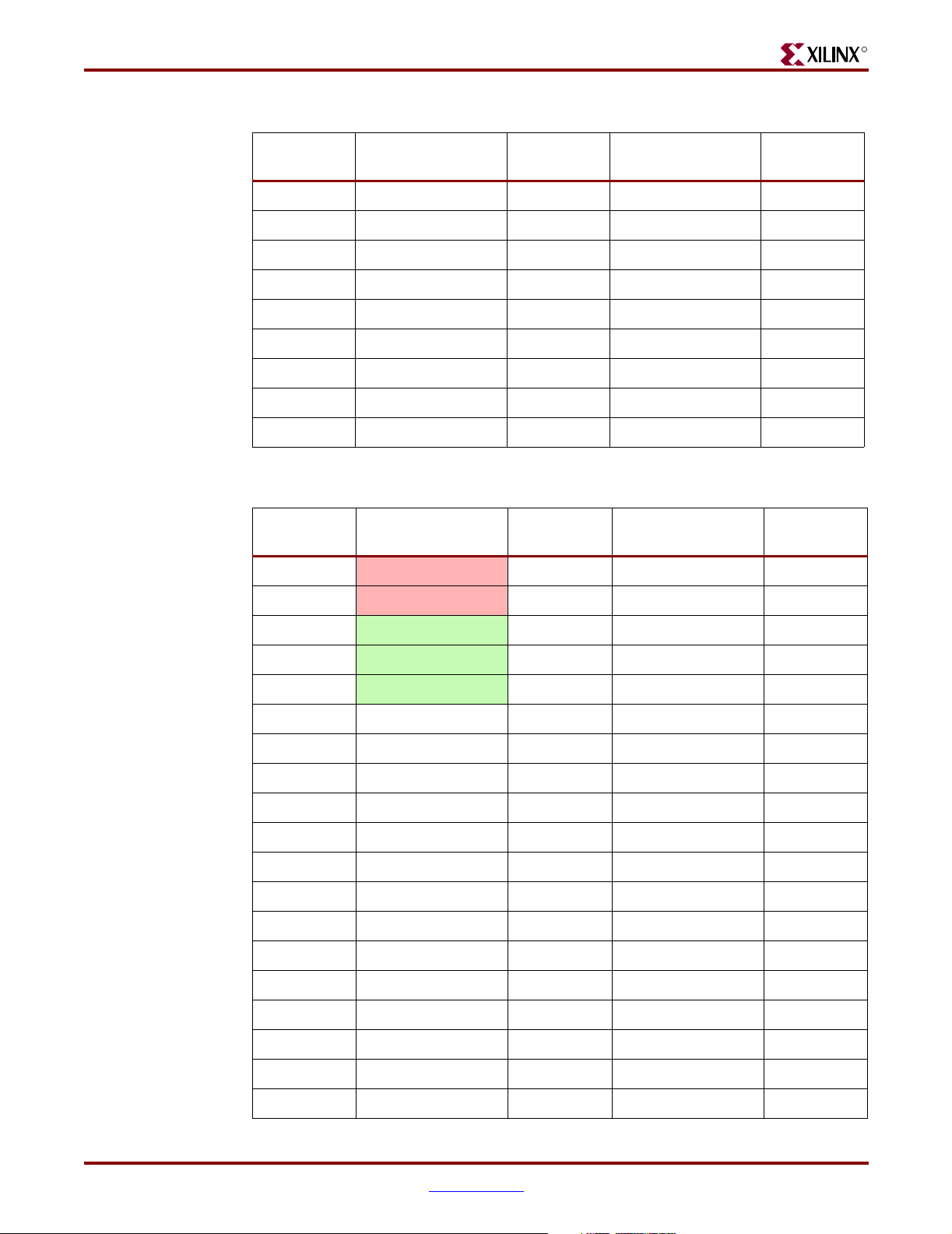

The connections between the FPGA and the XSGA output DAC and connector are listed in

Tab le 2 -7 along with the required I/O characteristics.

Table 2-7: XSGA Output Connections

Signal Direction

Video

DAC or Output

Connector Pin

FPGA

Pin

I/O Type Drive Slew

VGA_OUT_RED[0] O 40 G8 LVTTL 8 mA SLOW

VGA_OUT_RED[1] O 41 H9 LVTTL 8 mA SLOW

VGA_OUT_RED[2] O 42 G9 LVTTL 8 mA SLOW

VGA_OUT_RED[3] O 43 F9 LVTTL 8 mA SLOW

VGA_OUT_RED[4] O 44 F10 LVTTL 8 mA SLOW

VGA_OUT_RED[5] O 45 D7 LVTTL 8 mA SLOW

VGA_OUT_RED[6] O 46 C7 LVTTL 8 mA SLOW

VGA_OUT_RED[7] O 47 H10 LVTTL 8 mA SLOW