Page 1

NS9750 Hardware Reference

90000624_G

Page 2

Page 3

NS9750 Hardware Reference

Part number/version: 90000624_G

Release date: March 2008

www.digiembedded.com

Page 4

©2008 Digi International Inc.

Printed in the United States of America. All rights reserved.

Digi, Digi International, the Digi logo, the Making Device Networking Easy logo, NetSilicon, a Digi

International Company, NET+, NET+OS and NET+Works are trademarks or registered trademarks of Digi

International, Inc. in the United States and other countries worldwide. All other trademarks are the

property of their respective owners.

Information in this document is subject to change without notice and does not represent a committment

on the part of Digi International.

Digi provides this document “as is,” without warranty of any kind, either expressed or implied, including,

but not limited to, the implied warranties of, fitness or merchantability for a particular purpose. Digi may

make improvements and/or changes in this manual or in the product(s) and/or the program(s) described

in this manual at any time.

This product could include technical inaccuracies or typographical errors. Changes are made periodically

to the information herein; these changes may be incorporated in new editions of the publication.

Digi International

11001 Bren Road East

Minnetonka, MN 55343 U.S.A.

United St ates: +1 877 912-3444

Other locations: +1 952 912-3444

www.digiembedded.com

Page 5

Contents

Chapter 1: About NS9750 .......................................................................... .....................1

NS9750 Features ......................................................................... 2

System-level interfaces................................................................. 8

System boot ............................................................................. 10

Reset......................................................................................10

RESET_DONE as an input........................................................11

RESET_DONE as an output......................................................11

System clock.............................................................................13

USB clock................................................................................. 15

Chapter 2:

Pinout and signal descriptions........................................................18

NS9750 Pinout ...........................................................................................17

System Memory interface ......................................................18

System Memory interface signals..............................................22

Ethernet interface............................... ....... ........ ....... ....... ... 25

Clock generation/system pins .................................................26

bist_en_n, pll_test_n, and scan_en_n........................................28

PCI interface...................................................................... 28

GPIO MUX .........................................................................34

LCD module signals..............................................................42

I2C interface......................................................................43

USB interface.....................................................................43

JTAG interface for ARM core/boundary scan................................43

Reserved .......................................................................... 45

Power ground..................................................................... 46

iii

Page 6

Chapter 3: Working with the CPU .................................................................. ....47

About the processor....................................................................48

Instruction sets..........................................................................49

ARM instruction set..............................................................50

Thumb instruction set...........................................................50

Java instruction set ............................................................. 50

System control processor (CP15) registers..........................................51

ARM926EJ-S system addresses .................................................51

Accessing CP15 registers........................................................52

Terms and abbreviations ....................................................... 52

Register summary................................................................ 53

R0: ID code and cache type status registers.................................55

R1: Control register .............................................................58

R2: Translation Table Base register...........................................61

R3: Domain Access Control register...........................................61

R4 register ........................................................................ 62

R5: Fault Status registers... ........ ....... ....... ........ ....... ....... ........ 62

R6: Fault Address register......................................................64

R7: Cache Operations register.................................................64

R8:TLB Operations register.....................................................68

R9: Cache Lockdown register ..................................................69

R10: TLB Lockdown register....................................................73

R11 and R12 registers ....... ........ ....... ....... ........ ....... ....... ........ 74

R13: Process ID register.........................................................75

R14 register............................................................... ........ 77

R15: Test and debug register .................................................. 77

Jazelle (Java) ........................................................................... 77

DSP........................................................................................78

Memory Management Unit (MMU)...................... ........ ....... ....... ........ 78

MMU Features .................................................................... 78

Address translation..............................................................81

MMU faults and CPU aborts.....................................................95

Domain access control .......................................................... 98

Fault checking sequence ....................................................... 99

External aborts..................................................................102

Enabling the MMU...............................................................103

Disabling the MMU ..............................................................104

iv

Page 7

TLB structure....................................................................104

Caches and write buffer..............................................................105

Cache features..................................................................105

Write buffer .....................................................................106

Enabling the caches ............................................................107

Cache MVA and Set/Way formats ............................................109

Noncachable instruction fetches....................................................111

Self-modifying code ............................................................ 1 12

AHB behavior ....................................................................112

Instruction Memory Barrier...........................................................113

IMB operation....................................................................113

Sample IMB sequences ......................................... ....... ....... .. 1 14

Chapter 4:

System Control Module .................................................................115

System Control Module features ....................................................116

Bus interconnection...................................................................116

System bus arbiter.....................................................................116

Arbiter configuration examples ..............................................120

Address decoding ......................................................................123

Programmable timers.................................................................125

Software watchdog timer......................................................125

General purpose timers/counters............. ....... ........ ....... ....... .. 125

Interrupt controller ...................................................................129

Vectored interrupt controller (VIC) flow....................................132

System attributes......................................................................133

PLL configuration ................. ........ ....... ....... ........ ....... ....... .. 1 33

Bootstrap initialization ........................................................134

System configuration registers ......................................................138

AHB Arbiter Gen Configuration register.....................................144

BRC0, BRC1, BRC2, and BRC3 registers......................................145

Timer 0–15 Reload Count registers...........................................146

Timer 0–15 Read register ......................................................147

Interrupt Vector Address Register Level 0–31 ..............................147

Int (Interrupt) Config (Configuration) registers (0–31)....................148

ISRADDR register................................................................150

Interrupt Status Active.........................................................151

v

Page 8

Interrupt Status Raw ...........................................................152

Timer Interrupt Status register...............................................153

Software Watchdog Configuration register .................................153

Software Watchdog Timer register ..........................................155

Clock Configuration register .................................... ....... .......155

Reset and Sleep Control register.............................................157

Miscellaneous System Configuration and Status register .................158

PLL Configuration register..................................................... 1 61

Active Interrupt Level Status register .......................................163

Timer 0–15 Control registers..................................................163

System Memory Chip Select 0 Dynamic Memory Base and Mask registers..

165

System Memory Chip Select 1 Dynamic Memory Base and Mask registers..

166

System Memory Chip Select 2 Dynamic Memory Base and Mask registers..

167

System Memory Chip Select 3 Dynamic Memory Base and Mask registers..

168

System Memory Chip Select 0 Static Memory Base and Mask registers.169

System Memory Chip Select 1 Static Memory Base and Mask registers.170

System Memory Chip Select 2 Static Memory Base and Mask registers.171

System Memory Chip Select 3 Static Memory Base and Mask registers.172

Gen ID register ..................................................................173

External Interrupt 0–3 Control register......................................175

vi

Chapter 5:

Memory Controller ...................................................... .......................177

Features............................................................ .....................178

System overview................................................................179

Low-power operation ..........................................................180

Memory map.................. ........ ....... ....... ........ ....... ....... .......180

Static memory controller.............................................................183

Write protection ................................................................184

Extended wait transfers .......................................................184

Memory mapped peripherals..................................................185

Static memory initialization ..................................................185

Byte lane control ...............................................................211

Address connectivity ...........................................................212

Byte lane control and databus steering .....................................216

Page 9

Dynamic memory controller .........................................................224

Write protection ................................................................224

Access sequencing and memory width ......................................224

Address mapping................................................................225

Registers ................................................................................264

Register map ....................................................................264

Reset values .....................................................................266

Control register .................................................................267

Status register...................................................................269

Configuration register..........................................................269

Dynamic Memory Control register............................................270

Dynamic Memory Refresh Timer register ...................................272

Dynamic Memory Read Configuration register .............................274

Dynamic Memory Precharge Command Period register...................275

Dynamic Memory Active to Precharge Command Period register .......276

Dynamic Memory Self-refresh Exit Time register..........................277

Dynamic Memory Last Data Out to Active Time register .................278

Dynamic Memory Data-in to Active Command Time register ............279

Dynamic Memory Write Recovery Time register ...........................280

Dynamic Memory Active to Active Command Period register............281

Dynamic Memory Auto Refresh Period register ............................282

Dynamic Memory Exit Self-refresh register.................................283

Dynamic Memory Active Bank A to Active Bank B Time register ........284

Dynamic Memory Load Mode register to Active Command Time register..

285

Static Memory Extended Wait register ......................................286

Dynamic Memory Configuration 0–3 registers ..............................287

Dynamic Memory RAS and CAS Delay 0–3 registers ........................291

Static Memory Configuration 0–3 registers..................................292

Static Memory Write Enable Delay 0–3 registers...........................296

Static Memory Output Enable Delay 0–3 registers .........................297

Static Memory Read Delay 0–3 registers.....................................298

Static Memory Page Mode Read Delay 0–3 registers.......................299

Static Memory Write Delay 0–3 registers....................................300

Static Memory Turn Round Delay 0–3 registers.............................301

Chapter 6:

Ethernet Communication Module ......................................315

vii

Page 10

Overview................................................................................316

Ethernet MAC...........................................................................317

Station address logic (SAL)....................................................321

Statistics module ...............................................................321

Ethernet front-end module ..........................................................323

Receive packet processor .....................................................324

Transmit packet processor ....................................................327

Ethernet Slave Interface.......................... ............... ....... .......330

Interrupts ........................................................................331

Resets.............................................................................332

External CAM filtering ................................................................334

Ethernet Control and Status registers..............................................337

Ethernet General Control Register #1 .......................................339

Ethernet General Control Register #2 .......................................342

Ethernet General Status register.............................................344

Ethernet Transmit Status register............................................344

Ethernet Receive Status register.............................................347

MAC Configuration Register #1 ...............................................348

MAC Configuration Register #2 ...............................................351

Back-to-Back Inter-Packet-Gap register.....................................354

Non Back-to-Back Inter-Packet-Gap register...............................355

Collision Window/Retry register .............................................355

Maximum Frame register ......................................................357

PHY Support register...........................................................358

MII Management Configuration register .....................................359

MII Management Command register..........................................360

MII Management Address register ............................................361

MII Management Write Data register ........................................362

MII Management Read Data register .........................................363

MII Management Indicators register..........................................363

Station Address registers ......................................................364

Station Address Filter register................................................366

Register Hash Tables ...........................................................366

Statistics registers..............................................................368

RX_A Buffer Descriptor Pointer register.....................................383

RX_B Buffer Descriptor Pointer register.....................................383

RX_C Buffer Descriptor Pointer register.....................................384

viii

Page 11

RX_D Buffer Descriptor Pointer register ....................................384

Ethernet Interrupt Status register ...........................................385

Ethernet Interrupt Enable register...........................................387

TX Buffer Descriptor Pointer register............................... ....... .. 389

Transmit Recover Buffer Descriptor Pointer register .....................389

TX Error Buffer Descriptor Pointer register.................................390

RX_A Buffer Descriptor Pointer Offset register ............................391

RX_B Buffer Descriptor Pointer Offset register ............................392

RX_C Buffer Descriptor Pointer Offset register ............................393

RX_D Buffer Descriptor Pointer Offset register ............................393

Transmit Buffer Descriptor Pointer Offset register........................394

RX Free Buffer register ........................................................395

TX buffer descriptor RAM......................................................396

Sample hash table code ..............................................................397

Chapter 7:

PCI-to-AHB Bridge ............................................................................403

About the PCI-to-AHB Bridge ........................................................404

PCI-to-AHB bridge functionality ..............................................405

Cross-bridge transaction error handling.....................................407

AHB address decoding and translation ......................................408

PCI address decoding and mapping ..........................................408

Interrupts ........................................................................409

Transaction ordering ...........................................................410

Endian configuration ...........................................................411

Configuration registers.........................................................411

Bridge Configuration registers................................................413

PCI bus arbiter .........................................................................418

PCI arbiter functional description............................................419

Slave interface..................................................................420

PCI Arbiter Configuration registers ..........................................420

PCI system configurations............................................................456

Device selection for configuration ...........................................458

PCI interrupts....................................................................458

PCI central resource functions................................................458

CardBus Support .......................................................................461

Configuring NS9750 for CardBus support....................................463

CardBus adapter requirements ...............................................464

ix

Page 12

CardBus interrupts..............................................................465

Chapter 8:

BBus Bridge ............................................... .................................................467

BBus bridge functions.................................................................468

Bridge control logic ...................................................................469

DMA accesses............................................................. .......471

BBus control logic .....................................................................472

BBus bridge masters and slaves...............................................472

Cycles and BBus arbitration...................................................473

BBus peripheral address map (decoding) ...................................473

Two-channel AHB DMA controller (AHB bus) ......................................474

DMA buffer descriptor..........................................................474

Descriptor list processing......................................................476

Peripheral DMA read access............................................ .......477

Peripheral DMA write access..................................................478

Peripheral REQ signaling.......................................................479

Design Limitations ..............................................................480

Calculating AHB DMA response latency......................................480

Static RAM chip select configuration ........................................482

Interrupt aggregation .................................................................483

Bandwidth requirements ......................... ....... ........ ....... ....... .......483

SPI-EEPROM boot logic................................................................484

Serial Channel B configuration ...............................................485

Memory Controller configuration.. ....... ....... ........ ....... ....... .......486

SDRAM boot algorithm .........................................................488

BBus Bridge Control and Status registers ..........................................490

Buffer Descriptor Pointer register ...........................................491

DMA Channel 1/2 Control register ...........................................491

DMA Status and Interrupt Enable register...................................494

DMA Peripheral Chip Select register.........................................496

BBus Bridge Interrupt Status register........................................498

BBus Bridge Interrupt Enable register .......................................499

x

Chapter 9:

BBus DMA Controller ......................................................................501

About the BBus DMA controllers.....................................................502

DMA context memory .................................................................503

Page 13

DMA buffer descriptor ................................................................504

DMA channel assignments ............................................................509

DMA Control and Status registers ...................................................510

DMA Buffer Descriptor Pointer................................................512

DMA Control register ...........................................................5 14

DMA Status/Interrupt Enable register .......................................516

Chapter 10:

BBus Utility .......................................................... ..................................521

BBus Utility Control and Status registers ..........................................522

Master Reset register...........................................................523

GPIO Configuration registers..................................................524

GPIO Control registers .........................................................529

GPIO Status registers...........................................................532

BBus Monitor register ..........................................................535

BBus DMA Interrupt Status register ..........................................536

BBus DMA Interrupt Enable register..........................................537

USB Configuration register ....................................................538

Endian Configuration register.................................................539

ARM Wake-up register..........................................................541

Chapter 11:

I2C Master/Slave Interface ...................................................543

Overview................................................................................544

Physical I2C bus.................................................................544

I2C external addresses................................................................545

I2C command interface...............................................................545

Locked interrupt driven mode................................................546

Master module and slave module commands...............................546

Bus arbitration ..................................................................547

I2C registers ............................................................................547

Command Transmit Data register ............................................548

Status Receive Data register..................................................549

Master Address register.......... ........ ....... ....... ........ ....... ....... .. 5 50

Slave Address register..........................................................551

Configuration register..........................................................552

Interrupt Codes ........................................................................553

Software driver ........................................................................555

xi

Page 14

Flow charts .............................................................................556

Master module (normal mode, 16-bit).......................................556

Slave module (normal mode, 16-bit) ........................................557

Chapter 12:

LCD Controller ....................................................................................559

LCD features............................................................................560

Programmable parameters....................................................560

LCD panel resolution ...........................................................561

LCD panel support ..............................................................561

Number of colors ...............................................................562

LCD power up and power down sequence support ........................563

LCD controller functional overview.................................................564

Clocks.............................................................................565

Signals and interrupts..........................................................566

AHB interface ..........................................................................568

AHB master and slave interfaces.............................................568

Dual DMA FIFOs and associated control logic...............................568

Pixel serializer ..................................................................569

RAM palette......................................................................573

Grayscaler .......................................................................574

Upper and lower panel formatters...........................................574

Panel clock generator..........................................................574

Timing controller ............ ........ ....... ....... ........ ....... ....... .......574

Generating interrupts..........................................................575

External pad interface signals ................................................575

LCD panel signal multiplexing details .......................................575

Registers ................................................................................579

LCDTiming0......................................................................580

LCDTiming1......................................................................582

LCDTiming2 register............................................................583

LCDTiming3......................................................................587

LCDUPBASE and LCDLPBASE...................................................587

LCDINTRENABLE.................................................................589

LCDControl register.............................................................590

LCDStatus register..............................................................593

LCDInterrupt register ..........................................................594

LCDUPCURR and LCDLPCURR..................................................594

xii

Page 15

LCDPalette register.............................................................595

Interrupts ...............................................................................598

MBERRORINTR — Master bus error interrupt................................598

VCOMPINTR — Vertical compare interrupt..................................598

LBUINTR — Next base address update interrupt ...........................599

Chapter 13:

Serial Control Module: UART ...........................................601

Features................................................................. ................602

Bit-rate generator ..............................................................603

UART mode .............................................................................604

FIFO management ....................................................................605

Transmit FIFO interface .......................................................605

Receive FIFO interface.........................................................606

Serial port performance..............................................................608

Serial port control and status registers ............................................608

Serial Channel B/A/C/D Control Register A ................................611

Serial Channel B/A/C/D Control Register B ................................614

Serial Channel B/A/C/D Status Register A..................................617

Serial Channel B/A/C/D Bit-rate register...................................624

Serial Channel B/A/C/D FIFO Data register ................................629

Serial Channel B/A/C/D Receive Buffer GAP Timer.......................630

Serial Channel B/A/C/D Receive Character GAP Timer ..................632

Serial Channel B/A/C/D Receive Match register...........................634

Serial Channel B/A/C/D Receive Match MASK register ...................635

Serial Channel B/A/C/D Flow Control register.............................636

Serial Channel B/A/C/D Flow Control Force register .....................638

Chapter 14:

Serial Control Module: SPI ..................................................643

Features................................................................. ................644

Bit-rate generator ..............................................................645

SPI mode ................................................................................646

SPI modes ........................................................................646

FIFO management .....................................................................647

Transmit FIFO interface .......................................................647

Receive FIFO interface.........................................................648

Serial port performance..............................................................650

xiii

Page 16

Serial port control and status registers ............................................650

Serial Channel B/A/C/D Control Register A ................................652

Serial Channel B/A/C/D Control Register B ................................655

Serial Channel B/A/C/D Status Register A..................................657

Serial Channel B/A/C/D Bit-rate register...................................660

Serial Channel B/A/C/D FIFO Data register ................................665

Chapter 15:

IEEE 1284 Peripheral Controller ...................................669

Requirements ..........................................................................670

Overview................................................................................670

Compatibility mode ............................................................671

Nibble mode.....................................................................672

Byte mode .......................................................................672

ECP mode ........................................................................673

Data and command FIFOs......................................................675

IEEE 1284 negotiation..........................................................676

BBus slave and DMA interface .......................................................677

BBus slave and DMA interface register map ................................677

IEEE 1284 General Configuration register...................................679

Interrupt Status and Control register........................................681

FIFO Status register ............................................................6 84

Forward Command FIFO Read register ......................................686

Forward Data FIFO Read register.............................................687

Reverse FIFO Write register/Reverse FIFO Write Register — Last.......687

Forward Command DMA Control register ...................................689

Forward Data DMA Control register..........................................690

Printer Data Pins register......................................................691

Port Status register, host......................................................692

Port Control register ...........................................................693

Port Status register, peripheral ..............................................694

Feature Control Register A....................................................694

Feature Control Register B....................................................695

Interrupt Enable register ......................................................695

Master Enable register............................ ........ ....... ....... .......697

Extensibility Byte Requested by Host........................................698

Extended Control register.....................................................698

Interrupt Status register.......................................................699

xiv

Page 17

Pin Interrupt Mask register....................................................700

Pin Interrupt Control register.................................................701

Granularity Count register ....................................................702

Forward Address register......................................................703

Core Phase (IEEE1284) register...............................................704

Chapter 16:

USB Controller Module ............................................. .................707

Overview................................................................................708

USB module architecture.............................................................708

USB device block.......................................................................710

Control and status..............................................................710

Packet and data flow...........................................................711

Logical and physical endpoints ...............................................712

Slew rates........................................................................712

Host block...............................................................................712

Control and status..............................................................712

Packet data flow................................................ ....... ....... .. 7 13

USB device endpoint ..................................................................714

Transmission error handling..........................................................714

Handling USB-IN packet errors................................................715

Handling USB-OUT packet errors.............................................715

USB block registers....................................................................716

USB Global registers...................................................................716

Global Control and Status register...........................................717

Device Control and Status register...........................................718

Global Interrupt Enable register ............................................. 7 20

Global Interrupt Status register ..............................................721

Device IP Programming Control/Status register ...........................724

USB host block registers..............................................................725

Reserved bits....................................................................725

USB host block register address map ........................................725

HCRevision register.............................................................726

HcControl register..............................................................727

HcCommandStatus register ...................................................730

HcInterruptStatus register.....................................................733

HcInterruptEnable register....................................................735

HcInterruptDisable register ...................................................737

xv

Page 18

HcHCCA register ................................................................739

HcPeriodCurrentED register...................................................740

HcControlHeadED register.....................................................741

HcControlCurrentED register..................................................742

HcBulkHeadED register ........................................................743

HcBulkCurrentED register .....................................................744

HcDoneHead register...........................................................746

HcFmInterval register..........................................................747

HcFmRemaining register.......................................................748

HcFmNumber register..........................................................749

HcPeriodicStart register .......................................................750

HcLsThreshold register.........................................................751

Root hub partition registers...................................................752

HcRhDescriptorA register......................................................753

HcRhDescriptorB register......................................................755

HcRhStatus register ............................................................756

HcRhPortStatus[1] register....................................................759

USB Device Block registers...........................................................765

Device Descriptor/Setup Command register................................765

Endpoint Descriptor #0–#11 registers........................................766

USB Device Endpoint FIFO Control and Data registers...........................767

FIFO Interrupt Status registers ...............................................769

FIFO Interrupt Enable registers...............................................776

FIFO Packet Control registers.................................................780

FIFO Status and Control registers ............................................7 81

xvi

Chapter 17:

Timing ............................................................................................................787

Electrical characteristics.............................................................788

Absolute maximum ratings ....................................................788

Recommended operating conditions.........................................788

Maximum power dissipation...................................................789

Typical power dissipation .....................................................789

DC electrical characteristics.........................................................790

Inputs.............................................................................790

Outputs...........................................................................791

Reset and edge sensitive input timing requirements ............................792

Power sequencing .....................................................................794

Page 19

Memory timing ......................................................................... 795

SDRAM burst read (16-bit).....................................................796

SDRAM burst read (16-bit), CAS latency = 3 ................................797

SDRAM burst write (16-bit)....................................................798

SDRAM burst read (32-bit).....................................................799

SDRAM burst read (32-bit), CAS latency = 3 ................................800

SDRAM burst write (32-bit)....................................................801

SDRAM load mode............................................................... 8 02

SDRAM refresh mode ................................... ........ ....... ....... .. 8 03

Clock enable timing ............................................................ 8 03

Static RAM read cycles with 0 wait states ..................................805

Static RAM asynchronous page mode read, WTPG = 1 ....................806

Static RAM read cycle with configurable wait states .....................807

Static RAM sequential write cycles ..........................................808

Static RAM write cycle.........................................................809

Static write cycle with configurable wait states...........................810

Slow peripheral acknowledge timing ........................................811

Ethernet timing ........................................................................813

Ethernet MII timing.............................................................814

Ethernet RMII timing ...........................................................815

PCI timing...............................................................................816

Internal PCI arbiter timing ....................................................818

PCI burst write from NS9750 timing .........................................818

PCI burst read from NS9750 timing ..........................................819

PCI burst write to NS9750 timing.............................................819

PCI burst read to NS9750 timing..............................................820

PCI clock timing.................................................................820

I2C timing...............................................................................821

LCD timing..............................................................................822

Horizontal timing for STN displays...........................................824

Vertical timing for STN displays ..............................................825

Horizontal timing for TFT displays...........................................825

Vertical timing for TFT displays ..............................................825

HSYNC vs VSYNC timing for STN displays....................................826

HSYNC vs VSYNC timing for TFT displays....................................826

LCD output timing ..............................................................826

SPI timing ...............................................................................827

xvii

Page 20

SPI master mode 0 and 1: 2-byte transfer ..................................829

SPI master mode 2 and 3: 2-byte transfer ..................................829

SPI slave mode 0 and 1: 2-byte transfer ....................................830

SPI slave mode 2 and 3: 2-byte transfer ....................................830

IEEE 1284 timing.......................................................................831

IEEE 1284 timing example.....................................................831

USB timing ..............................................................................832

USB differential data timing ..................................................833

USB full speed load timing ....................................................833

USB low speed load.............................................................834

Reset and hardware strapping timing ..............................................835

JTAG timing ............................................................................836

Clock timing ... ....... ........ ....... ........ ....... ....... ........ ....... ....... .......837

USB crystal/external oscillator timing ......................................837

LCD input clock timing.........................................................838

System PLL bypass mode timing..............................................839

Chapter 18:

Product specifications .........................................................845

Packaging ...................................................................................................841

xviii

Page 21

Using This Guide

Using This Guide

Review this section for basic information about the gui de you are using, as

well as general support and contact information. This printed version of the

NS9750 Hardware Reference, Rev. E includes two volumes (90000622_E and

90000623_E). A single PDF (90000624_E) is included on your documentation CD.

About this guide

This guide provides information about the Digi NS9750, a single chip 0.13μm

CMOS network-attached processor. The NS9750 is part of the Digi NET+ARM

family of devices.

The NET+ARM family is part of the NET+Works integrated product family, which

includes the NET+OS network software suite.

Who should read this guide

This guide is for hardware developers, system software developers, and

applications programmers who want to use the NS9750 for development.

To complete the tasks described in this guide, you must:

Understand the basics of hardware and software design, operating

systems, and microprocessor design.

Understand the NS9750 architecture.

xix

Page 22

What’s in this guide

This table shows where you can find specific information in the printed guides.

To read about See Vol

NS9750 key features Chapter 1, “About the NS9750 1

NS9750 ball grid array assignments Chapter 2, “NS9750 Pinout” 1

NS9750 CPU Chapter 3, “Working with the CPU” 1

System functionality Chapter 4, “System Control Module” 1

How the NS9750 works with the Multiport Memory

Controller, an AMBA-compliant SoC peripheral

How the NS9750 works with Ethernet MAC and

Ethernet front-end module

PCI-to-AHB bus functionality, which connects PCI-

based devices to the NS9750 AHB bus

Digi proprietary BBus Chapter 8, “BBus Bridge 2

NS9750 BBus DMA controller subsystem C hapter 9, “BBus DMA Controller” 2

Chip-level support for low-speed peripherals Chapter 10, “BBus Utility” 2

Interface between the ARM CPU and the I2C bus Chapter 11, “I2C Master/Slave Interface” 2

LCD controller Chapter 12, “LCD Controller” 2

UART mode serial controller Chapter 13, “Serial Control Module:

SPI mode serial controller Chapter 14, “Serial Control Module: SPI” 2

IEEE 1284 peripheral port Chapter 15, “IEEE 1284 Peripheral

USB 2.0 Chapter 16, “USB Controller Module” 2

NS9750 electrical characteristics and timing diagrams

and information

Chapter 5, “Memory Controller” 1

Chapter 6, “Ethernet Communication

Module”

Chapter 7, “PCI-to-AHB Bridge” 1

UART”

Controller”

Chapter 17, “Timing” 2

1

2

2

xx

NS9750 packaging information Chapter 18, “Packaging” 2

NS9750 Hardware Reference

Page 23

Conventions used in this guide

This table describes the typographic conventions used in this guide:

This convention Is used for

italic type Emphasis, new terms, variables, and document titles.

monospaced type

_ (underscore) Defines a signal as being active low.

‘b Indicates that the number following this indicator is in binary radix

‘d Indicates that the number following this indicator is in decimal radix

‘h Indicates that the number following this indicator is in hexadecimal

RW1TC Indicates Read/Write 1 to clear.

Related documentation

NS9750 Jumpers and Components provides a hardware description of the

NS9750 development board, and includes information about jumpers,

components, switches, and configuration.

NS9750 Sample Driver Configurations provides sample configurations that

you can use to develop your drivers.

Review the documentation CD-ROM that came with your development kit for

information on third-party products and other components.

Filenames, pathnames, and code examples.

radix

See the NET+OS software documentation for information appropriate to the chi p you

are using.

Documentation updates

Digi occasionally provides documentation updates on the Web site.

www.digiembedded.com

xxi

Page 24

Be aware that if you see differences between the documentation you received in your

package and the documentation on the Web site, the Web site content is the latest

version.

Customer support

To get help with a question or technical problem with this product, or to make

comments and recommendations about our products or documentation, use the

contact information listed in this table:

For Contact information

Technical support United States: +1 877 912-3444

Other locations: +1 952 912-3444

www.digiembedded.com

xxii

NS9750 Hardware Reference

Page 25

About NS9750

CHAPTER 1

The Digi NS9750 is a single chip 0.13μm CMOS network-attached processor. This

chapter provides an overview of the NS9750, which is based on the standard

architecture in the NET+ARM family of devices.

1

Page 26

NS9750 Features

NS9750 Features

The NS9750 uses an ARM926EJ-S core as its CPU, with MMU, DSP extensions, Jazelle

Java accelerator, and 8 kB of instruction cache and 4 kB of data cache in a Harvard

architecture. The NS9750 runs up to 200 MHz, with a 100 MHz system and memory bus

and 50 MHz peripheral bus. The NS9750 offers an extensive set of I/O interfaces and

Ethernet high-speed performance and processing capacity. The NS9750 is designed

specifically for use in high-performance intelligent networked devices and Internet

appliances including high-performance, low-latency remote I/O, int elligent

networked information displays, and streaming and surveillance cameras.

32-bit ARM926EJ-S RISC processor

125 to 200 MHz

5-stage pipe line with interlocking

Harvard architecture

8 kB instruction cache and 4 kB data cache

32-bit ARM and 16-bit Thumb instruction sets. Can be mixed for

performance/code density tradeoffs.

2

MMU to support virtual memory-based OSs, such as Linux, VxWorks, others

DSP instruction extensions, improved divide, single cycle MAC

ARM Jazelle, 1200CM (coffee marks) Java accelerator

EmbeddedICE-RT debug unit

JTAG boundary scan, BSDL support

External system bus interface

32-bit data, 32-bit internal address bus, 28-bit external address bus

Glueless interface to SDRAM, SRAM, EEPROM, buffered DIMM, Flash

4 static and 4 dynamic memory chip selects

1-32 wait states per chip select

A shared Static Extended Wait register allows transfers to have up to 16368

wait states that can be externally terminated

Self-refre sh during system sleep mode

Automatic dynamic bus sizing to 8 bits, 16 bits, 32 bits

NS9750 Hardware Reference

Page 27

About NS9750

Burst mode support with automatic data width adjustment

Two external DMA channels for external peripheral support

System Boot

High-speed boot from 8-bit, 16-bit, or 32-bit ROM or Flash

Hardware-supported low cost boot from serial EEPROM through SPI port

(patent pending)

High performance 10/100 Ethernet MAC

10/100 Mbps MII/RMII PHY interfaces

Full-duplex or half-duplex

Station, broadcast, or multicast address filtering

2 kB RX FIFO

256-byte TX FIFO with on-chip buffer descriptor ring

– Eliminates underruns and decreases bus traffic

Separate TX and RX DMA channels

Intelligent receive-side buffer size selection

Full statistics gathering support

External CAM filtering support

PCI/CardBus port

PCI v2.2, 32-bit bus, up to 33 MHz bus speed

Programmable to:

– PCI device mode

– PCI host mode:

Supports up to 3 external PCI devices

Embedded PCI arbiter or external arbiter

CardBus host mode

www.digiembedded.com

3

Page 28

NS9750 Features

Flexible LCD controller

Supports most commercially available displays:

Formats image data and generates timing control signals

Internal programmable palette LUT and grayscaler support different color

Programmable panel-clock frequency

USB ports

USB v.2.0 full speed (12 Mbps) and low speed (1.5 Mbps)

Configurable to device or OHCI host

– Active Matrix color TFT displays:

Up to 24bpp direct 8:8:8 RGB; 16 colors

– Single and dual panel color STN displays:

Up to 16bpp 4:4:4 RGB; 3375 colors

– Single and dual panel monochrome STN displays:

1, 2, 4bpp palettized gray scale

techniques

– USB host is bus master

– USB device supports one bidirectional control endpoint and 11

unidirectional endpoints

4

All endp oints supported by a dedicated DMA channel; 13 channels total

20 byte RX FIFO and 20 byte TX FIFO

Serial ports

4 serial modules, each independently configurable to UART mode, SPI

master mode, or SPI slave mode

Bit rates from 75 bps to 921.6 kbps: asynchronous x16 mode

Bit rates from 1.2 kbps to 6.25 Mbps: synchronous mode

UART provides:

– High-performance hardware and software flow control

– Odd, even, or no parity

– 5, 6, 7, or 8 bits

– 1 or 2 stop bits

– Receive-side character and buffer gap timers

NS9750 Hardware Reference

Page 29

About NS9750

Inte rnal or external clock support, digital PLL for RX clock extraction

4 receive-side data match detectors

2 dedicated DMA channels per module, 8 channels total

32 byte TX FIFO and 32 byte RX FIFO per module

I2C port

2

I

Bit rates: fast (400 kHz) or normal (100 kHz) with clock stretching

7-bit and 10-bit address modes

Supports I

C v.1.0 configurable to master or slave mode

2

C bus arbitration

1284 parallel peripheral port

All standard modes: ECP, byte, nibble, compatibility (also known as SPP or

“Centronix”)

RLE (run length encoding) decoding of compressed data in ECP mode

Operating clock from 100 kHz to 2 MHz

High performance multiple-master/distributed DMA system

Intelligent bus bandwidth allocation (patent pending)

Syste m bus and perip he ral bus

System bus

Every system bus peripheral is a bus master with a dedicated DMA engine

Peripheral bus

One 13-channel DMA engine supports USB device

– 2 DMA channels support control endpoint

– 11 DMA channels support 11 endpoints

One 12-channel DMA engine supports:

– 4 serial modules (8 DMA channels)

– 1284 parallel port (4 DMA channels)

Al l DMA channels support fly-by mode

External peripheral

One 2-channel DMA engine supports external peripheral connected to

memory bus

www.digiembedded.com

5

Page 30

NS9750 Features

Each DMA channel supports memory-to-memory transfers

Power management (patent pending)

Power save during normal operation

Power save during sleep mode

Vector interrupt controller

Decrease d bus traffic and rapid interrupt service

Hardware interrupt prioritization

General purpose timers/counters

16 independent 16-bit or 32-bit programmable timers or counters

Mode selectable into:

– Disables unused modules

– Sets memory controller to refresh

– Disables all modules except selected wakeup mo dules

– Wakeup on valid packets or characters

– Each with an I/O pin

– Internal timer mode

– External gated timer mode

– External event counter

6

Can be concatenated

Resolution to measure minute-range events

Source clock selectable: internal clock or external pulse event

Each can be individually enabled/disabled

System timers

Watchdog timer

System bus monitor timer

System bus arbiter timer

Peripheral bus monitor timer

General purpose I/O

50 programmable GPIO pins (muxed with other functions)

Software-readable powerup status registers for every pin for customer-

defined bootstrapping

NS9750 Hardware Reference

Page 31

External interrupts

4 external programmable interrupts

– Rising or falling edge-sens itive

– Low level- or high level-sensitive

Clock generator

Low cost external crystal

On-chip phase locked loop (PLL)

Software programmable PLL parameters

Optional external oscillator

Separate PLL for USB

Operating grades/Ambient temperatures

200 MHz: 0 – 70

162 MHz: -40 – +85

125 MHz: 0 – 70

o

C

o

C

o

C

About NS9750

www.digiembedded.com

7

Page 32

System-level interfaces

NS9750

I2C

Clocks & Reset

JTAG

Ethernet

Controls

Data

Address

PCI/CardBus

Power & Ground

GPIO

System

Memory

USB Host or Device

Serial

1284

LCD

Ext. DMA

Ext. IRQ

Timers/Counters

USB Host control

System-level interfaces

Figure 1 shows the NS9750 system-level interfaces.

8

Figure 1: System-level hardware interfaces

Ethe rnet MII/RMII interface to external PHY

System memory interface

– Glueless connection to SDRAM

– Glueless connection to buffered PC100 DIMM

– Glueless connection to SRAM

– Glueless connection to Flash memory or ROM

PCI muxed with CardBus interface

USB host or device interface

2

I

C interface

50 GPIO pins muxed with:

– Four 8-pin-each serial ports, each programmable to UART or SPI

NS9750 Hardware Reference

Page 33

About NS9750

– 1284 port

– Up to 24-bit TFT or STN color and monochrome LCD controller

– Two external DMA channels

– Four external interrupt pins programmed to rising or falling edge, or to high

or low level

– Sixteen 16-bit or 32-bit programmable timers or counters

– Two control signals to support USB host

JTAG development interface

Cl ock interfaces for crystal or external oscillator

– System clock

– USB clock

Clock interface for optional LCD external oscillator

Power and ground

www.digiembedded.com

9

Page 34

System boot

NS9750

Memory

CTL

External

System

Memory

Flash or

ROM

Memory Bus

Peripheral Bus to AHB Bus Bridge

AHB

Serial

EEPROM

SPI

System boot

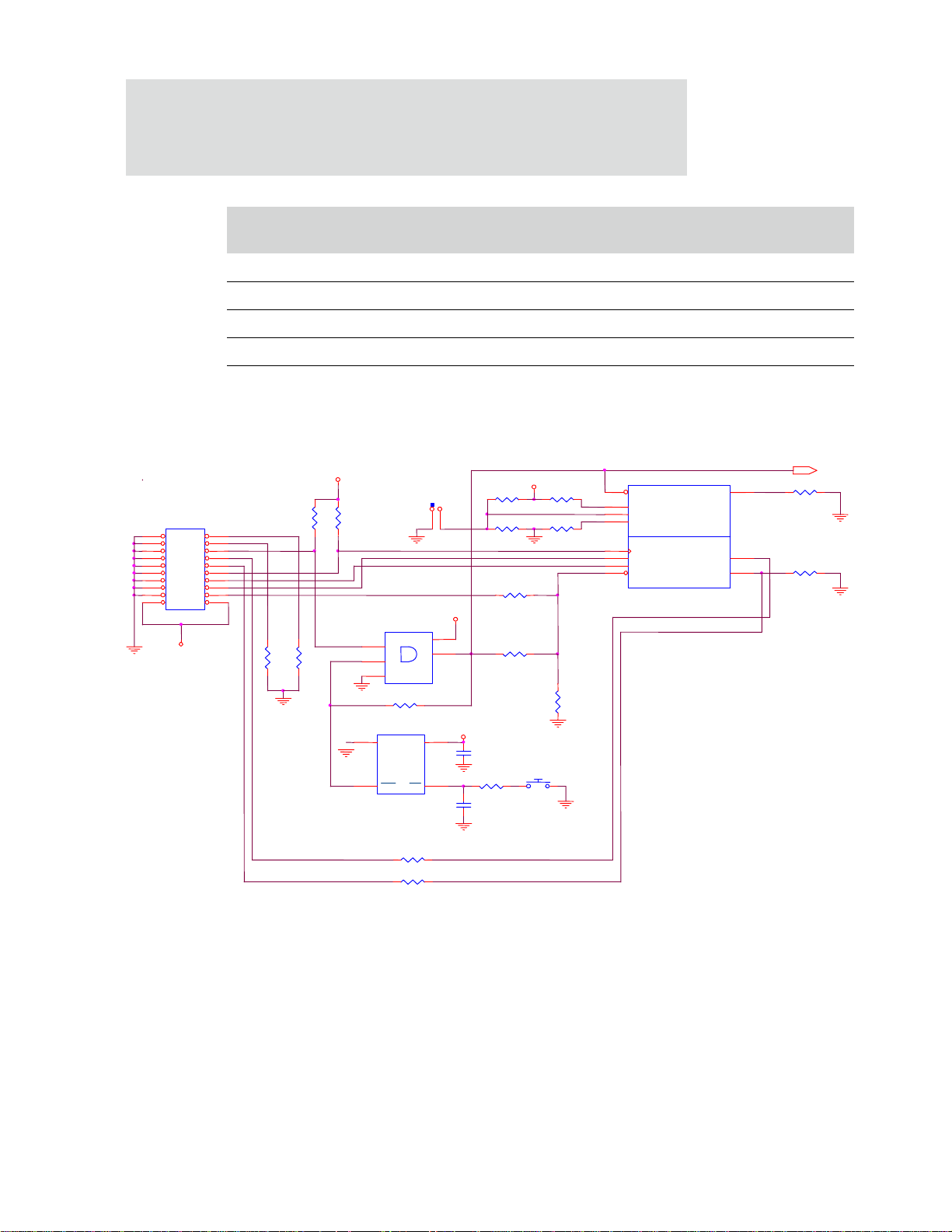

There are two ways to boot the NS9750 system (see Figure 2):

From a fast Flash over the system memory bus

From an inexp ensive, but slower, serial EEPROM through SPI port B.

Both boot methods are glueless. The bootstrap pin,

RESET_DONE, indicates where to

boot on a system powerup. Flash boot can be done from 8-bit, 16-bit, or 32-bit ROM

or Flash.

Serial EEPROM boot is supported by NS9750 hardware. A configuration header in the

EEPROM specifies total number of words to be fetched from EEPROM, as well as a

system memory configuration and a memory controller configuration. The boot

engine configures the memory controller and system memory, fetches data from lowcost serial EEPROM, and writes the data to externa l system memory, holding the CPU

in reset.

Reset

10

Figure 2: Two methods of booting NS9750 system

Master reset using an external reset pin resets NS9750. Only the AHB bus error status

registers retain their values; software read resets these error status registers. The

NS9750 Hardware Reference

Page 35

input reset pin can be driven by a system reset circuit or a simple power-on reset

circuit.

RESET_DONE as an input

Used at bootup only:

When set to 0, the system boots from SDRAM through the serial SPI EEPROM.

When set to 1, the system boots from Flash/ROM. This is the default.

RESET_DONE as an output

Sets to 1, per Step 6 in the boot sequence.

If the system is booting from serial EEPROM through the SPI port, the boot program

must be loaded into the SDRAM before the CPU is released from reset. The memory

controller is powered up with dy_cs_n[0] enabled with a default set of SDRAM

configurations. The default address range for

chip selects are disabled.

About NS9750

dy_cs_n[0] is from 0x0000 0000. The other

Boot sequence

1 When the system reset turns to inactive, the reset signal to the CPU is still held

active.

2 An I/O module on the peripheral bus (BBus) reads from a serial ROM device that

contains the memory controller settings and the boot program.

3 The BBus-to-AHB bridge requests and gets the system bus.

4 The memory controller settings are read from the serial EEPROM and used to

initialize the memory controller.

5 The BBus-to-AHB bridge loads the boot program into the SDRAM, starting at

address 0.

6 The reset signal going to the CPU is released once the boot program is loaded.

RESET_DONE is now set to 1.

7 The CPU begins to execute code from addres s 0x0000 0000.

www.digiembedded.com

11

Page 36

Reset

C14 100nF

Adding R5 will enable BOOT from Serial EE memory

connected to SPI port B to SDRAM located on dy_cs_n[0].

RESET_DONE remains “LOW” until BOOT is completed.

RESET_DONE = 1 indicates that the CPU is ready.

Otherwise, BOOT is from parallel ROM/FLASH connected to

st_cs_n[1].

RESET_

NS9750

RESET_DONE

RESETn

RESET delay required following valid

power applied to the NS9750 to allow

clock circuits to stabilize.

RST-

VCC

GND

U6

MAX809S_SOT23D

2

3

1

R5

2R4K

3R3V

RESET_DONE

Figure 3 shows a sample reset circuit.

Figure 3: Sample reset circuit

You can use one of five software resets to reset the NS9750. Select the reset by

setting the appropriate bit in the appropriate register.

Watchdog timer can issue reset upon watchdog timer expiration (see

AHB bus arbiter can issue reset upon AHB bus arbiter timer expiration.

AH B bus monit o r can issue reset upon AHB bus monitor timer expiration.

Software reset can reset individual internal modules or all modules except

The system is reset whenever software sets the PLL SW change bit to 1 (see

12

"Software Watchdog Timer register" on page 293).

memory and CPU (see "Reset and Sleep Control register" on page 295).

"PLL Configuration register" on page 299).

NS9750 Hardware Reference

Page 37

Hardware reset duration is 4 ms for PLL to stabilize. Software duration depends on

speed grade, as shown in Table 1.

Speed grade CPU clock cycles Duration

200 MHz 128 640 ns

162 MHz 128 790 ns

125 MHz 128 1024 ns

Table 1: Software reset duration

The minimum reset pulse width is 10 crystal clocks.

System clock

The system clock is provided to the NS9750 by either a crystal or an external

oscillator. Table 2 shows sample clock frequency settings for each chip speed grade.

About NS9750

Speed cpu_clk hclk (main bus) bbus_clk

200 MHz 200 (199.0656) 99.5328 49.7664

162 MHz 162.2016 81.1008 40.5504

125 MHz 125.3376 62.6688 31.3344

Table 2: Sample clock frequency settings with 29.4912 MHz crystal

If an oscillator is used, it must be connected to the

x1_sys_osc input (C8 pin) on the

NS9750. If a crystal is used, it must be connected with a circuit such as the one shown

in Figure 4.

www.digiembedded.com

13

Page 38

System clock

C19

10pF

S_PLL_BP_

GPIO19_PLL_BP

C20

10pF

X2

20-40MHz

X1_SYS

X2_XTAL

X1_SYS_OSC is qualified for an external LVTTL clock up to

400 MHz in PLL bypass mode. The system PLL is bypassed

by pulling down GPIO19. In PLL bypass mode, the ARM9

CPU is ½ the frequency of X!_SYS_OSC.

When the PLL is enabled, the clock input range is 20 - 40

MHz.

X1_SYS_OSC

Add R10 to bypass SYS PLL

R12

1M

R11

100

X2_SYS

R10

2R4K

R13

330 OHM

NS9750

X2_SYS_OSC

Figure 4: System clock

The PLL parameters are initialized on powerup reset, and can be changed by

software from f

200 MHZ to 100 MHz, the AHB system bus may change from 100 MHz to 50 MHz, and

the peripheral BBus may change from 50 MHz to 25 MHz. If changed by software, the

system resets automatically after the PLL stabilizes (approximately 4 ms).

The system clock provides clocks for CPU, AHB system bus, peripheral BBus, PCI/

CardBus, LCD, timers, memory controller, and BBus modules (serial modules and 1284

parallel port).

The Ethernet MAC uses external clocks from a MII PHY or a RMII PHY. For a MII PHY,

these clocks are input signals:

transmit clock. For a RMII, there is only one clock, and it connects to the

T3. In this case, the transmit clock,

PCI/CardBus, LCD controller, serial modules (UART, SPI), and 1284 port can optionally

use external clock signals.

14

max

to 1/2 f

. For a 200 MHz grade, then, the CPU may change from

max

rx_clk on pin T3 for receive clock and tx_clk on pin V3 for

tx_clk, should be tied low.

NS9750 Hardware Reference

rx_clk on pin

Page 39

USB clock

Y1_PWR

**

**

Y1_OUT

**

TANK_LC

3R3V

C17

10pF

**

3412

X1

48.0000MHz

C16

100pF_5%

NS9750

L4

1uH_5%

TANK_RC

X2_USB_OSC

Y1

EC2600_TTS_48M

4

2

1 3

VCC

GND

TEST OUT

R7

68R1

NOTE: ** = OPTIONAL

Crystal circuit

C15

10pF

X1_IN

X1_USB_OSC

R8 1.5M

Tank Circuit

X1_USB

**

**

C9

100nF

R9

100 OHM

**

X2_USB

R6

100

TB1

BEAD_0805_601

**

X1 is a 48-MHz 3rd harmonic crystal. It has

the same physical characteristics as a 16

MHz crystal. The circuit may have a tendency

to oscillate at 16 MHz unless precautions are

taken. A LC-tank circuit is added to provide a

“low impedance” for the 16 MHz oscillation to

ground.

About NS9750

USB is clocked by a separate PLL driven by an external 48 MHz crystal, or it can be

driven directly by an external 48 MHz oscillator.

Figure 5: USB clock

www.digiembedded.com

15

Page 40

Page 41

NS9750 Pinout

CHAPTER 2

The NS9750 offers a connection to an external bus expansion module, as well as a

glueless connection to SDRAM, PC100 DIMM, flash, EEPROM, and SRAM memories, and

an external bus expansion module. It includes a versatile embedded LCD controller, a

PCI/CardBus port, a USB port, and four multi-function serial ports. The NS9750

provides up to 50 general purpose I/O (GPIO) pins and configurable power

management with sleep mode.

17

Page 42

Pinout and signal descriptions

Pinout and signal descriptions

Each pinout table applies to a specific interface, and contains the following

information:

Heading Description

Pin # Pin number assignment for a specific I/O signal

Signal Pin name for each I/O signal. Some signals have multiple funct ion modes and are

identified accordingly. The mode is configured through firmware using one or more

configuration registers.

_n in the signal name indicates that this signal is active low.

U/D U or D indicates whether the pin is a pullup resistor or a pulldown resistor:

U — Pullup (input current source)

D — Pulldown (input current sink)

If no value appears, that pin is neither a pullup nor pulldown resistor.

I/O The type of signal: input, output, or input/output.

OD (mA) The output drive of an output buffer. NS9750 uses one of three drivers:

2 mA

4 mA

8 mA

More detailed signal descriptions are provided for selected modules.

System Memory interface

Pin # Signal Name U/D

A21 addr[0] 8 O Address bus signal

B20 addr[1] 8 O Address bus signal

C19 addr[2] 8 O Address bus signal

A20 addr[3] 8 O Address bus signal

B19 addr[4] 8 O Address bus signal

Table 3: System Memory interface pinout

18

NS9750 Hardware Reference

OD

(mA) I/O Description

Page 43

OD

Pin # Signal Name U/D

(mA)

I/O Description

C18 addr[5] 8 O Address bus signal

A19 addr[6] 8 O Address bus signal

A17 addr[7] 8 O Address bus signal

C16 addr[8] 8 O Address bus signal

B16 addr[9] 8 O Address bus signal

A16 addr[10] 8 O Address bus signal

D15 addr[11] 8 O Address bus signal

C15 addr[12] 8 O Address bus signal

B15 addr[13] 8 O Address bus signal

A15 addr[14] 8 O Address bus signal

C14 addr[15] 8 O Address bus signal

B14 addr[16] 8 O Address bus signal

A14 addr[17] 8 O Address bus signal

NS9750 Pinout

A13 addr[18] 8 O Address bus signal

B13 addr[19] 8 O Address bus signal

C13 addr[20] 8 O Address bus signal

A12 addr[21] 8 O Address bus signal

B12 addr[22] 8 O Address bus signal

C12 addr[23] 8 O Address bus signal

D12 addr[24] 8 O Address bus signal

A11 addr[25] 8 O Address bus signal

B11 addr[26] 8 O Address bus signal

C11 addr[27] 8 O Address bus signal

G2 clk_en[0] 8 O SDRAM clock enable

H3 clk_en[1] 8 O SDRAM clock enable

G1 clk_en[2] 8 O SDRAM clock enable

Table 3: System Memory interface pinout

www.digiembedded.com

19

Page 44

Pinout and signal descriptions

Pin # Signal Name U/D

H2 clk_en[3] 8 O SDRAM clock enable

A10 clk_out[0] 8 O SDRAM reference clock. Connect to clk_in[0]

A9 clk_out[1] 8 O SDRAM clock

A5 clk_out[2] 8 O SDRAM clock

A4 clk_out[3] 8 O SDRAM clock

G26 data[0] 8 I/O Data bus signal

H24 data[1] 8 I/O Data bus signal

G25 data[2] 8 I/O Data bus signal

F26 data[3] 8 I/O Data bus signal

G24 data[4] 8 I/O Data bus signal

F25 data[5] 8 I/O Data bus signal

E26 data[6] 8 I/O Data bus signal

OD

(mA)

I/O Description

using series termination.

20

F24 data[7] 8 I/O Data bus signal

E25 data[8] 8 I/O Data bus signal

D26 data[9] 8 I/O Data bus signal

F23 data[10] 8 I/O Data bus signal

E24 data[11] 8 I/O Data bus signal

D25 data[12] 8 I/O Data bus signal

C26 data[13] 8 I/O Data bus signal

E23 data[14] 8 I/O Data bus signal

D24 data[15] 8 I/O Data bus signal

C25 data[16] 8 I/O Data bus signal

B26 data[17] 8 I/O Data bus signal

D22 data[18] 8 I/O Data bus signal

C23 data[19] 8 I/O Data bus signal

B24 data[20] 8 I/O Data bus signal

Table 3: System Memory interface pinout

NS9750 Hardware Reference

Page 45

OD

Pin # Signal Name U/D

(mA)

I/O Description

A25 data[21] 8 I/O Data bus signal

C22 data[22] 8 I/O Data bus signal

D21 data[23] 8 I/O Data bus signal

B23 data[24] 8 I/O Data bus signal

A24 data[25] 8 I/O Data bus signal

A23 data[26] 8 I/O Data bus signal

B22 data[27] 8 I/O Data bus signal

C21 data[28] 8 I/O Data bus signal

A22 data[29] 8 I/O Data bus signal

B21 data[30] 8 I/O Data bus signal

C20 data[31] 8 I/O Data bus signal

E1 data_mask[0] 8 O SDRAM data mask signal

F2 data_mask[1] 8 O SDRAM data mask signal

NS9750 Pinout

G3 data_mask[2] 8 O SDRAM data mask signal

F1 data_mask[3] 8 O SDRAM data mask signal

C5 clk_in[0] I SDRAM feedback clock. Connect to clk_out[0].

D2 clk_in[1] I Connect to GND

E3 clk_in[2] I Connect to GND

E2 clk_in[3] I Connect to GND

B4 byte_lane_sel_n[0] 8 O Static memory byte_lane_enable[0] or

write_enable_n[0] for byte-wide device signals

F4 byte_lane_sel_n[1] 8 O Static memory byte_lane_enable[1] or

write_enable_n[1] for byte-wide device signals

D1 byte_lane_sel_n[2] 8 O Static memory byte_lane_enable[2] or

write_enable_n[2] for byte-wide device signals