Page 1

Part number/version: 90000353_G

Release date: September 2007

www.digiembedded.com

NS7520 Hardware Reference

Page 2

©2001-2007 Digi International Inc.

Printed in the United States of America. All rights reserved.

Digi, Digi International, the Digi logo, NetSilicon, a Digi International Company, NET+, NET+OS and

NET+Works are trademarks or registered trademarks of Digi International, Inc. in the United States and

other countries worldwide. All other trademarks are the property of their respective owners.

Information in this document is subject to change without notice and does not represent a committment

on the part of Digi International.

Digi provides this document “as is,” without warranty of any kind, either expressed or implied, including,

but not limited to, the implied warranties of, fitness or merchantability for a particular purpose. Digi may

make improvements and/or changes in this manual or in the product(s) and/or the program(s) described

in this manual at any time.

This product could include technical inaccuracies or typographical errors. Changes are made periodically

to the information herein; these changes may be incorporated in new editions of the publication.

ii

Page 3

Using This Guide

Using This Guide

This guide provides information about the NS7520 32-bit networked

microprocessor. The NS7520 is part of the NET+ARM line of SoC (System-onChip) products, and supports high-bandwidth applications for intelligent

networked devices.

The NET+ARM family is part of the NET+Works integrated product family, which

includes the NET+OS network software suite.

Conventions used in this guide

This table describes the typographic conventions used in this guide:

This convention Is used for

italic type Emphasis, new terms, variables, and document titles.

monospaced type

_ (underscore) Defines a signal as being active low.

‘b Indicates that the number following this indicator is in binary radix

‘d Indicates that the number following this indicator is in decimal radix

‘h Indicates that the number following this indicator is in hexadecimal

Filenames, pathnames, and code examples.

radix

iii

Page 4

Digi information

Related documentation

For additional documentation, see the Documentation folder in the NET+OS Start

menu.

Documentation updates

Digi occasionally provides documentation updates on the Web site

(www.digiembedded.com/support).

Be aware that if you see differences between the documentation you received in your

package and the documentation on the Web site, the Web site content is the latest

version.

Support

To get help with a question or technical problem with this product, or to make

comments and recommendations about our products or documentation, use the

contact information listed in this table:

iv

For Contact information

Technical support www.digiembedded.com/

United States: +1 877 912-3444

Other locations: +1 952 912-3444

NS7520 Hardware Reference, Rev G 9/2007

Page 5

Contents

Chapter 1: About the NS7520 .................................................................................... 1

NS7520 Features ......................................................................... 2

Key features and operating modes of the major NS7520 modules ........ 2

NS7520 module block diagram......................................................... 5

Operating frequency .................................................................... 6

Chapter 2:

Packaging ................................................................................. 8

Pinout detail tables and signal descriptions........................................ 11

Chapter 3:

ARM Thumb concept ................................................................... 30

CPU performance ....................................................................... 30

Working with ARM exceptions ........................................................ 31

Pinout and Packaging .........................................................................7

System bus interface ............................................................ 12

Chip select controller ........................................................... 16

Ethernet interface MAC......................................................... 18

“No connect” pins ............................................................... 21

General-purpose I/O ............................................................ 21

System clock and reset ......................................................... 24

System mode (test support).................................................... 25

JTAG test (ARM debugger) ..................................................... 26

Power supply ..................................................................... 28

Working with the CPU .....................................................................29

Summary of ARM exceptions ................................................... 32

Exception priorities.............................................................. 32

v

Page 6

Exception vector table.......................................................... 33

Detail of ARM exceptions ....................................................... 34

Entering and exiting an exception (software action) ...................... 37

Hardware Interrupts.................................................................... 39

FIRQ and IRQ lines ............................................................... 39

Interrupt controller.............................................................. 39

Interrupt sources................................................................. 40

Chapter 4:

BBus Module ................................................................................................43

BBus masters and slaves ............................................................... 44

Cycles and BBus arbitration ........................................................... 44

Address decoding ....................................................................... 45

Chapter 5:

SYS Module ...................................................................................................47

Signal description....................................................................... 48

JTAG support ............................................................................ 48

ARM debug ............................................................................... 48

System clock generation (NS7520 clock module) .................................. 49

External oscillator vs. internal PLL circuit................................... 49

NS7520 clock module block diagram.......................................... 50

Using the external oscillator.......................................................... 50

External oscillator mode hardware configuration .......................... 50

Using the PLL circuit ................................................................... 51

PLL mode hardware configuration ............................................ 52

Setting the PLL frequency............................................................. 54

PLL Settings register: Setting the PLL frequency on bootup .............. 54

PLL Control register: Setting the PLL frequency with the PLL Control

register ............................................................................ 57

Reset circuit sources ................................................................... 59

NS7520 bootstrap initialization....................................................... 59

Chapter 6:

GEN Module ..................................................................................................61

Module configuration................................................................... 62

GEN module hardware initialization ................................................. 62

GEN module registers .................................................................. 63

vi

Page 7

System Control register......................................................... 63

System Status register .......................................................... 68

Software Service register....................................................... 69

Timer Control registers ......................................................... 70

Timer Status registers........................................................... 73

PORTA Configuration register.................................................. 73

PORTC Configuration register.................................................. 77

Interrupts ................................................................................ 80

Interrupt controller registers .................................................. 81

Chapter 7:

Memory Controller Module ........................................................ 85

About the MEM module ................................................................ 86

MEM module hardware initialization................................................. 86

Pin configuration................................................................. 86

MEM module configuration ............................................................ 87

Setting the chip select address range ........................................ 88

Memory Module Configuration register....................................... 89

Chip Select Base Address register ............................................. 92

Chip Select Option Register A ................................................. 97

Chip Select Option Register B.................................................101

Static memory (SRAM) controller ...................................................102

Single cycle read/write ........................................................102

Burst cycles ......................................................................104

NS7520 DRAM address multiplexing .................................................105

Using the internal multiplexer................................................105

Using the external multiplexer ...............................................108

DRAM refresh ...........................................................................109

FP/EDO DRAM controller .............................................................109

Single cycle read/write ........................................................110

FP/EDO DRAM burst cycles ....................................................111

SDRAM ...................................................................................111

NS7520 SDRAM interconnect ..................................................112

SDRAM A10/AP support ........................................................116

Command definitions...........................................................117

Memory timing fields — SDRAM ...............................................118

BSIZE configuration.............................................................118

SDRAM Mode register ...........................................................119

vii

Page 8

SDRAM read cycles..............................................................120

SDRAM write cycles.............................................................122

Peripheral page burst size ...........................................................124

Chapter 8:

DMA Module ...............................................................................................127

DMA module ............................................................................128

Fly-by operation transfers.....................................................128

Memory-to-memory operation ................................................129

DMA buffer descriptor ................................................................130

DMA channel assignments ............................................................132

DMA channel registers ................................................................133

Address map .....................................................................133

Buffer Descriptor Pointer register ...........................................136

DMA Control register ...........................................................136

DMA Status/Interrupt Enable register .......................................142

Ethernet transfer considerations....................................................144

Ethernet transmitter considerations................................................145

Ethernet receiver considerations ...................................................145

External peripheral DMA support....................................................146

Signal description...............................................................147

External DMA configuration ...................................................147

Memory-to-memory mode .....................................................147

DMA controller reset ..................................................................148

viii

Chapter 9:

Ethernet Module ....................................................................................149

Ethernet front-end (EFE) .............................................................150

Transmit and receive FIFOs ...................................................151

EFE transmit processing .......................................................151

EFE receive processing.........................................................151

Receive buffer descriptor selection .........................................152

External CAM filtering ................................................................153

MAC module ............................................................................154

MAC module block diagram ...................................................154

DMA channel assignments ............................................................156

EFE configuration ......................................................................156

Ethernet General Control register (EGCR) bit definitions ................158

Page 9

Ethernet General Status register (EGSR) bit definitions ..................164

Ethernet FIFO Data register ...................................................167

Ethernet Transmit Status register............................................168

Ethernet Receive Status register .............................................173

MAC Configuration Register 1 .................................................176

MAC Configuration Register 2 .................................................178

Back-to-Back Inter-Packet-Gap register.....................................182

Non-Back-to-Back Inter-Packet-Gap register ...............................183

Collision Window/Collision Retry register ..................................184

Maximum Frame register ......................................................185

PHY Support register ...........................................................186

Test register .....................................................................187

MII Management Configuration register .....................................189

MII Management Command register..........................................191

MII Management Address register ............................................192

MII Management Write Data register ........................................193

MII Management Read Data register .........................................194

MII Management Indicators register..........................................195

SMII Status register .............................................................196

Station Address registers ......................................................196

Station Address Filter register ................................................199

Register hash table .............................................................200

Chapter 10:

Serial Controller Module ........................................................ 207

Supported features ....................................................................208

Bit-rate generator .....................................................................209

Serial protocols ........................................................................210

UART mode .............................................................................210

SPI mode ................................................................................211

FIFO management ..............................................................212

General-purpose I/O configurations ................................................220

Serial port performance ..............................................................221

Configuration...........................................................................221

Serial Channel registers ..............................................................223

Serial Channel 1, 2 Control Register A ......................................223

Serial Channel 1, 2 Control Register B ......................................229

Serial Channel 1, 2 Status Register A ........................................233

ix

Page 10

Serial Channel 1, 2 Bit-Rate registers .......................................241

Serial Channel 1, 2 FIFO registers............................................250

Serial Channel 1, 2 Receive Buffer Gap Timer .............................250

Serial Channel 1, 2 Receive Character Gap Timer.........................252

Serial Channel 1,2 Receive Match register..................................254

Serial Channel 1, 2 Receive Match MASK register..........................254

Chapter 11:

Electrical Characteristics .......................................................257

DC characteristics .....................................................................258

Recommended operating conditions.........................................258

Input/Output characteristics .................................................259

Pad pullup and pulldown characteristics....................................259

Absolute maximum ratings ....................................................261

AC characteristics .....................................................................261

AC electrical specifications ...................................................261

Oscillator Characteristics.............................................................263

Timing Diagrams .......................................................................265

Timing_Specifications ..........................................................265

Reset_timing ....................................................................266

SRAM timing .....................................................................267

SDRAM timing....................................................................277

FP DRAM timing .................................................................283

Ethernet timing .................................................................290

JTAG timing......................................................................292

External DMA timing............................................................294

Serial internal/external timing ...............................................297

GPIO timing ......................................................................299

Chapter 12:

NS7520 Errata .......................................................................................301

How to identify the NS7520 ..........................................................302

NS7520 errata ..........................................................................303

Clock speed errata using PLL in boundary scan mode ....................303

UART CTS-related transmit data errors .....................................303

EDO burst errata ................................................................304

NS7520 clock speed erratum ..................................................306

SPI slave mode errata ..........................................................308

x

Page 11

Error in “No Connect” pin terminations.....................................308

Serial port error in 7-bit mode ...............................................309

SDRAM 256 MB mask failure ...................................................309

Erroneous timeouts when loading timer ....................................309

Station Address Logic: Multicast and broadcast packet filtering ........310

Station Address Logic: Unicast packets .....................................310

Corrupt Ethernet receive packets............................................311

Transmit buffer closed bit is not functional ................................312

Transmit FIFO timing issue ....................................................312

External use of TA_ and TEA_ ................................................313

xi

Page 12

xii

Page 13

About the NS7520

About the NS7520

CHAPTER 1

This chapter provides an overview of the NS7520. The NS7520 is a high-

performance, highly integrated, 32-bit system-on-a-chip ASIC designed for use in

intelligent networked devices and Internet appliances. The NS7520 is based on the

standard architecture in the NET+ARM family of devices.

NET+ARM is the hardware foundation of the NET+Works family of integrated hardware

and software solutions for device networking. These comprehensive platforms

include drivers, popular operating systems, networking software, development tools,

APIs, and complete development boards.

www.digiembedded.com

1

Page 14

NS7520 Features

NS7520 Features

The NS7520 can support most any networking scenario, and includes a 10/100 BaseT

Ethernet MAC and two independent serial ports (each of which can run in UART or SPI

mode).

The CPU is an ARM7TDMI (ARM7) 32-bit RISC processor core with a rich complement of

support peripherals and memory controllers, including:

Glueless connection to different types of memory; for example, flash,

SDRAM, EEPROM, and others.

Programmable timers

13-channel DMA controller

External bus expansion module

16 general-purpose I/O (GPIO) pins

Key features and operating modes of the major NS7520 modules

2

CPU core

– ARM7 32-bit RISC processor

– 32-bit internal bus

– 32-bit ARM mode and 16-bit Thumb mode

– 15 general-purpose 32-bit registers

– 32-bit program counter (PC) and status register

– Five supervisor modes, one user mode

13-channel DMA controller

– Two channels dedicated to Ethernet transmit and receive

– Four channels dedicated to two serial modules’ transmit and receive

– Four channels for external peripherals (only two channels — either 3 and 5

or 4 and 6 — can be configured at one time)

– Three channels available for memory-to-memory transfers

– Flexible buffer management

NS7520 Hardware Reference, Rev G 9/2007

Page 15

About the NS7520

General-purpose I/O pins

– 16 programmable GPIO interface pins

– Four pins programmable with level-sensitive interrupt

Serial ports

– Two fully independent serial ports (UART, SPI)

– Digital phase lock loop (DPLL) for receive clock extractions

– 32-byte transmit/receive FIFOs

– Internal programmable bit-rate generators

– Bit rates 75–230400 in 16X mode

– Bit rates 1200 bps–4 Mbps in 1X mode

– Flexible baud rate generator, external clock for synchronous operation

– Receive-side character and buffer gap timers

– Four receive-side data match detectors

Power and operating voltages

– 500 mW maximum at 55 MHz (all outputs switching)

– 418 mW maximum at 46 MHz (all outputs switching)

– 291 mW maximum at 36 MHz (all outputs switching)

– 3.3 V — I/O

– 1.5 V — Core

Integrated 10/100 Ethernet MAC

– 10/100 Mbps MII-based PHY interface

– 10 Mbps ENDEC interface

– Support for TP-PMD and fiber-PMD devices

– Full-duplex and half-duplex modes

– Optional 4B/5B coding

– Station, broadcast, and multicast address detection filtering

– 512-byte transmit FIFO, 2 Kbyte receive FIFO

– Intelligent receive-side buffer size selection

www.digiembedded.com

3

Page 16

NS7520 Features

Programmable timers

Operating frequency

– Two independent timers (2μs–20.7 hours)

– Watchdog timer (interrupt or reset on expiration)

– Programmable bus monitor or timer

– 36, 46, or 55 MHz internal clock operation from 18.432 MHz quartz crystal

or crystal oscillator

– f

= 36, 46, or 55 MHz (grade-dependent)

MAX

– System clock source by external quartz crystal or crystal oscillator, or clock

signal

– Programmable PLL, which allows a range of operating frequencies from 10

to f

MAX

– Maximum operating frequency from external clock or using PLL

multiplication f

Bus interface

MAX

– Five independent programmable chip selects with 256 Mb addressing per

chip select

– All chip selects support SRAM, FP/EDO DRAM, SDRAM, flash, and EEPROM

without external glue

– Supports 8-, 16-, and 32-bit peripherals

– External address decoding and cycle termination

– Dynamic bus sizing

– Internal DRAM/SDRAM controller with address multiplexer and

programmable refresh frequency

– Internal refresh controller (CAS before RAS)

4

– Burst-mode support

– 0–63 wait states per chip select

– Address pins that configure chip operating modes; see "NS7520 bootstrap

initialization" on page 59.

NS7520 Hardware Reference, Rev G 9/2007

Page 17

NS7520 module block diagram

Debugger

PLL

System

Clock

JTAG Debug

Interface

ARM7TDMI

FIRQ

IRQ

2 timers

Watchdog

timer

Power

3.3V

1.5V

BBUS

D

M

A

D

M

A

D

M

A

D

M

A

Serial-A

UART

SPI

Serial-B

UART

SPI

4

level

interrupt

inputs

16 GPIO

Ethernet

controller

802.3

compliant

External

memory

controller

NS7520

Reset

Address bus

Serial transceivers and other

devices

MII

Memory

devices

Flash

SRAM

FP DRAM

SDRAM

Boot

config

Figure 1 is an overview of the NS7520, including all the modules.

About the NS7520

Figure 1: NS7520 overview

www.digiembedded.com

5

Page 18

Operating frequency

Operating frequency

The NS7520 is available in grades operating at three maximum operating frequencies:

36 MHz, 46 MHz, and 55 MHz. The operating frequency is set during bootstrap

initialization, using pins A[8:0]. These address pins load the PLL settings register on

powerup reset. A[8:7] determines IS (charge pump current); A[6:5] determines FS

(output divider), and A[4:0] defines ND (PLL multiplier). Each bit in A[8:0] can be set

individually.

See "Setting the PLL frequency," beginning on page 54, for more detailed

information.

6

NS7520 Hardware Reference, Rev G 9/2007

Page 19

Pinout and Packaging

Pinout and Packaging

CHAPTER 2

The NS7520 can be used in any embedded environment requiring networking

services in an Ethernet LAN. The NS7520 contains an integrated ARM RISC processor,

10/100 Ethernet MAC, serial ports, memory controllers, and parallel I/O. The NS7520

can interface with another processor using a register or shared RAM interface. The

NS7520 provides all the tools required for any embedded networking application.

www.digiembedded.com

7

Page 20

Packaging

Packaging

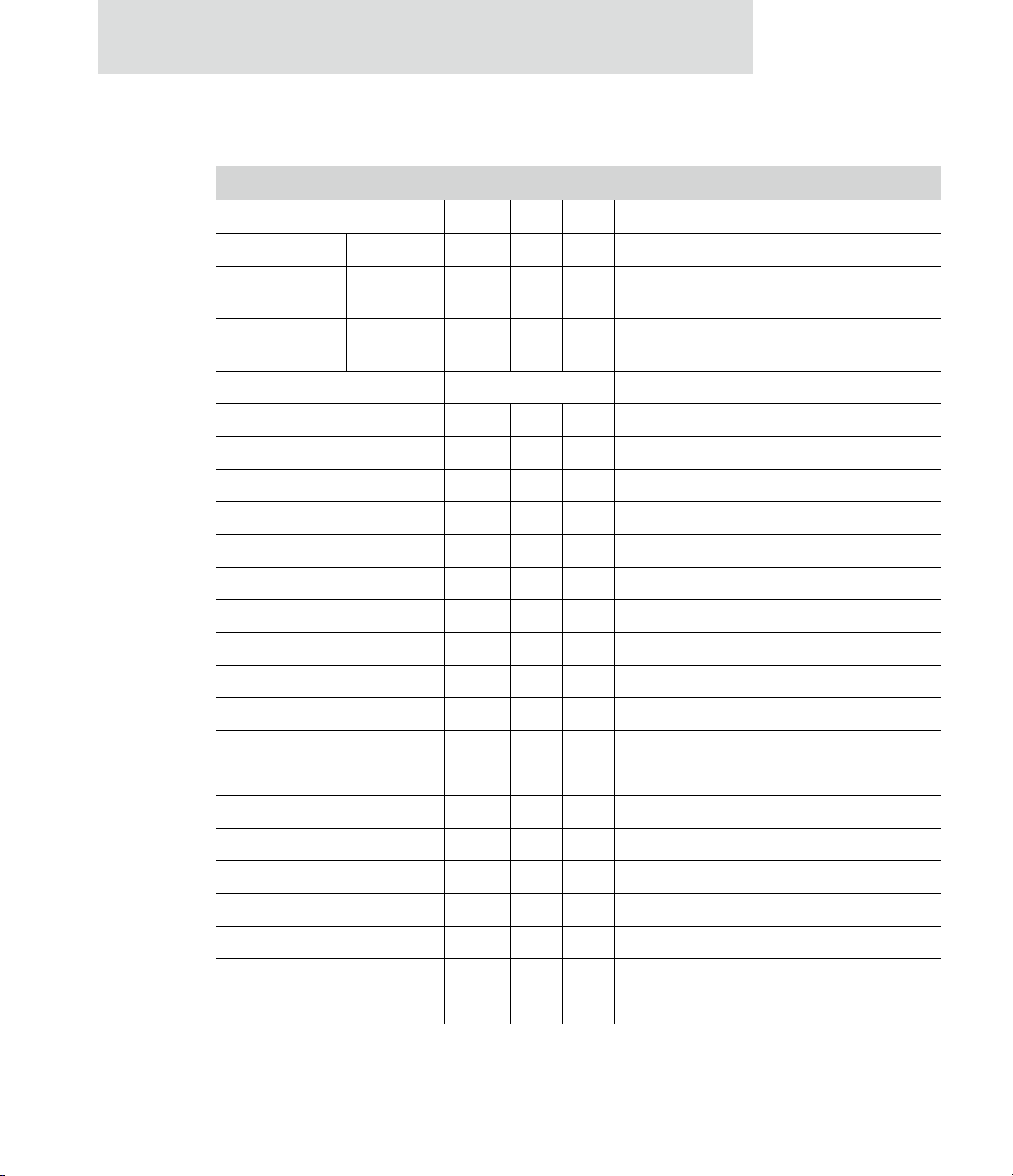

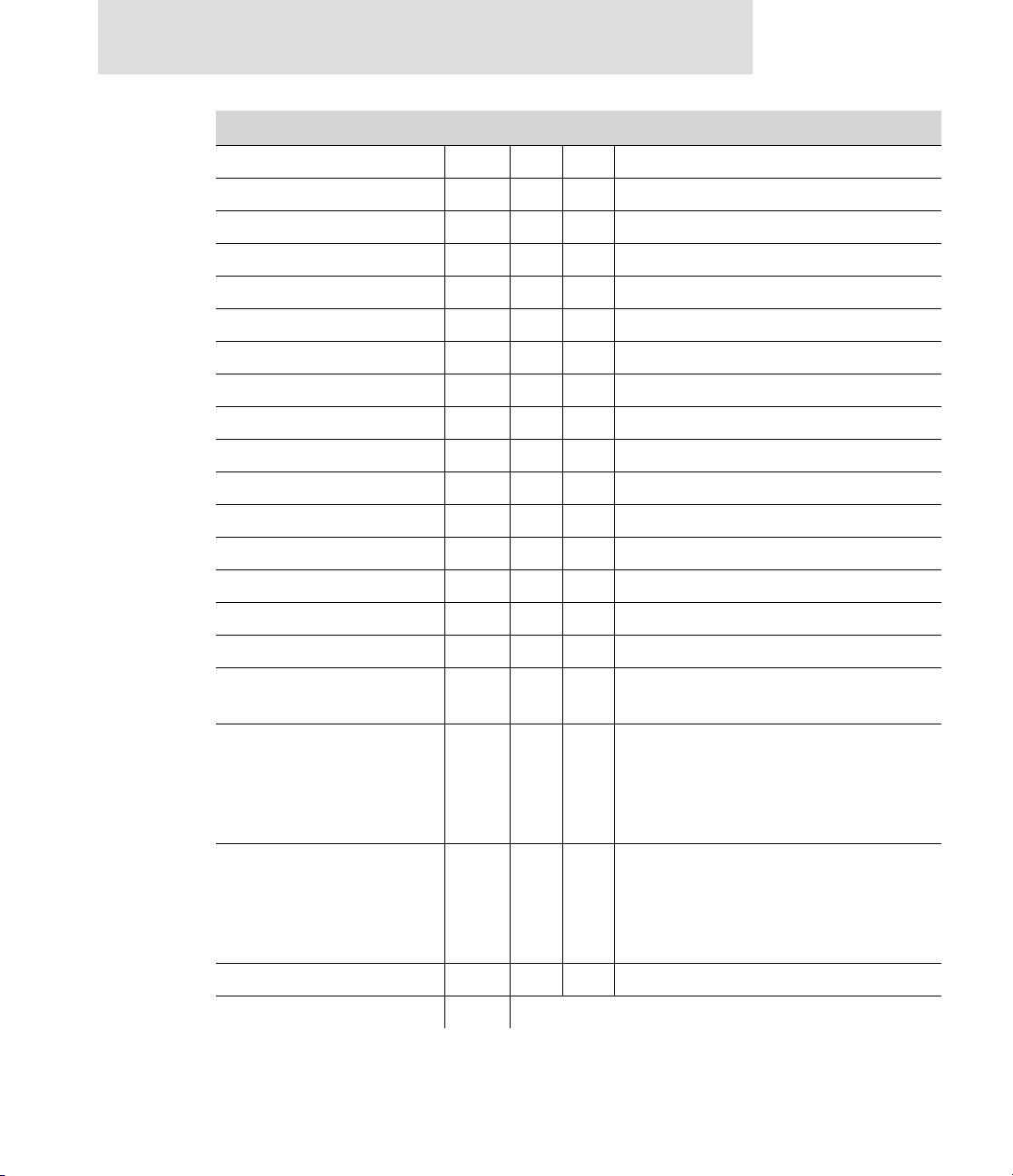

Table 1 provides the NS7520 packaging dimensions. Figure 2 shows the pinout and

NS7520 dimensions. Figure 3 shows the NS7520 BGA layout.

Symbol Min Nom Max

A——1.4

A1 0.35 0.40 0.45

A2——0.95

b 0.45 0.50 0.55

D 13.0 BSC

D1 11.2 BSC

E 13.0 BSC

E1 11.2 BSC

e 0.8 BSC

8

aaa 0.1

Table 1: NS7520 packaging dimensions

NS7520 Hardware Reference, Rev G 9/2007

Page 21

177 PFBGA

Pinout and Packaging

Figure 2: NS7520 pinout and dimensions

www.digiembedded.com

9

Page 22

Packaging

A17

H

A9

D25

D22

M8

D3D26

B1

VCCPY10

PORTC1

GNDPY6

XTAL2

E4

14

H1

N1

CS2_

A19

M10

L2

TXER

PLLVSS

F3

N9

XTALB1

BUSY_

A8

D15

D16

P1

N12

OE_

D20

D

GNDPY4

Top View, Balls Facing Down

TDI

B11

B8

R5

P9

VCCPY4

CS1_

VDDC03

D10

BE0_

B9

L13

M3

A20

SCANEN_

C15

C5

C6

R9

J15

D11

R8

N6

7

PORTC3

D12

D8

6

GNDPY7

E12

D29

H14

G1

BCLK

D19

R15

J4

B13

M15

C8

2

A13

C12

P13

D2

BE1_

P10

N13

V1.0

D7

GNDPY9

F12

A14

RXD0

RXDV

PORTA6

D24

R6

VCCPY7

PORTA0

GNDPY1

K2 D2

M1

N10

TXD3

A13

NC6

A2

TS_

TMS

RXCRS

CAS0_

A10

A24

M11

F4

E1

VCCPY1

TXD2

K12

B

12

RESV1-

M9

J12

J13

RXD1

RESET_

VSSC02

E13

R

PORTC7

GNDPY2

C3

G13

A9

TRST_

R11

M4

10

CAS3_

CAS2_

VDDC01

A26/0WE_ A27/0OE_

R10

K4

B6

C9

M5

VCCPY8

A10

R2

GNDPY14

8

XTALB2

A11

N7

H15

D12

A0

F14

B4

OSCVCC1

RXD2

PORTA4

A4

C1

D11

P14

CS3_

BISTEN_

D13

J3

P2

GNDPY13

13

PORTA7

C13

F1

L3

G12

A5

D7

P3 B3

VCCPY9

E

3

L14

G

A15

BE2_

B10

H12

N4

A18

VDDC04

D4

D3 A3

G14

B12

GUIDE PIN

VSSOSC2

TA_

L1

E2

GNDPY10

TXEN

PORTA1

M12

D4

K

A21

XTAL1

K13

GNDPY5

D1

VCCPY6

PORTC2

B7

VSSC01

D28

B15

M6

A11

PLLVDD

D10

D8

D1

R12

H3

VCCPY5

C

RESV2+

A25

PLLTST_

A15

R13

VSSC03

J

TXCOL

D13

C10

G4

VDDC02

GNDPY8

TXD0

A6

PORTC4

E5

N11

RXER

A23

TCK

C7

15

E14

G2

D23

K1

R14

G15

C14

D6

A1

N8

L

RXCLKPORTA2

A8

A12P12

C4

GNDPY11

A14J14

CS4_

D21

NC2

A4

BE3_

NS7520, 177 PFBGA

GNDPY3

D18

L12

P6

4

PORTA5

P4

1

PORTA3

CS0_

TEA_

P11

M14

B2

N14

R7

M13

J1

OSCVCC2

F

K14

A3

A16

N5

PORTC0

TDO

B14

F15

D27

P5

N3

M7

PORTC6

BR_

VSSOSC1

9

11

A1

MDC

D9

P7

E3

R1

N15 L15

R3

N

D30

A5

R4

H13

L4

BG_

F2

M

NC3

D14

TXCLK

C11

A7

D17

PORTC5

VCCPY2

MDIO

A2

E15

A12

K3

J2

D5

D31

VCCPY3

P

F13

D15

D5

B5

M2

D6

NC1

D0

P15

D14

RXD3

NC4

A22

5

A6

H4

TXD1

P8

N2

A

VSSC04

RW_

H2 C2

NC5

A7

G3

D9

CAS1_

GNDPY12

WE_

K15

Figure 3: NS7520 BGA layout

10

NS7520 Hardware Reference, Rev G 9/2007

Page 23

Pinout detail tables and signal descriptions

Each pinout table applies to a specific interface and contains the following

information:

Column Description

Signal The pin name for each I/O signal. Some signals have multiple function modes and are identified

accordingly. The mode is configured through firmware using one or more configuration

registers.

Pin The pin number assignment for a specific I/O signal.

U next to the pin number indicates that the pin is a pullup resistor (input current source).

D next to the pin number indicates that the pin is a pulldown resistor (input current sink).

No value next to the pin indicates that the pin has neither a pullup nor pulldown resistor.

See Figure 28, "Internal pullup characteristics," on page 260 and Figure 29, "Internal pulldown

characteristics," on page 260 for an illustration of the characteristics of these pins. Use the

figures to select the appropriate value of the complimentary resistor to drive the signal to the

opposite logic state. For those pins with no pullup or pulldown resistor, you must select the

appropriate value per your design requirements.

_ An underscore (bar) indicates that the pin is active low.

Pinout and Packaging

I/O The type of signal — input, output, or input/output.

OD The output drive strength of an output buffer. The NS7520 uses one of three drivers:

2 mA

4 mA

8 mA

Notes:

NO CONNECT as a description for a pin means do not connect to this pin.

The 177th pin (package ball) is for alignment of the package on the PCB.

www.digiembedded.com

11

Page 24

Pinout detail tables and signal descriptions

System bus interface

Symbol Pin I/O OD Description

BCLK A6 O 8 Synchronous bus clock

External bus Other External bus Other

ADDR27 CS0OE_ N10 U I/O 4 Addr bit 27 Logical AND of CS0_ and

ADDR26 CS0WE_ P10 U I/O 4 Addr bit 26 Logical AND of CS0_ and

External bus External bus

ADDR25 M10 U I/O 4 Remainder of address bus (through ADDR0)

ADDR24 R10 U I/O 4

ADDR23 N9 U I/O 4

ADDR22 R9 U I/O 4

ADDR21 M9 U I/O 4

ADDR20 N8 U I/O 4

OE_

WE_

12

ADDR19 P8 U I/O 4

ADDR18 M7 U I/O 4

ADDR17 R7U I/O 4

ADDR16 N7 U I/O 4

ADDR15 R6 U I/O 4

ADDR14 M6 U I/O 4

ADDR13 P6 U I/O 4

ADDR12 N6 U I/O 4

ADDR11 M5 U I/O 4

ADDR10 P5 U I/O 4

ADDR9 N5 U I/O 4

ADDR8 R4 U I/O 4

ADDR7 R3 U I/O 4

Table 2: System bus interface pinout

NS7520 Hardware Reference, Rev G 9/2007

Page 25

Symbol Pin I/O OD Description

ADDR6 R2 U I/O 4

ADDR5 M4 U I/O 4

ADDR4 N4 U I/O 4

ADDR3 R1 U I/O 4

ADDR2 M3 U I/O 4

ADDR1 N2 U I/O 4

ADDR0 P1 U I/O 4

DATA31 N1 I/O 4 Data bus

DATA30 M1 I/O 4

DATA29 L3 I/O 4

DATA28 L2 I/O 4

DATA27 L4 I/O 4

DATA26 L1 I/O 4

DATA25 K3 I/O 4

Pinout and Packaging

DATA24 K2 I/O 4

DATA23 K1 I/O 4

DATA22 J2 I/O 4

DATA21 J3 I/O 4

DATA20 J1 I/O 4

DATA19 H3 I/O 4

DATA18 H4 I/O 4

DATA17 H1 I/O 4

DATA16 H2 I/O 4

DATA15 G4 I/O 4

DATA14 G1 I/O 4

DATA13 G3 I/O 4

DATA12 G2 I/O 4

Table 2: System bus interface pinout

www.digiembedded.com

13

Page 26

Pinout detail tables and signal descriptions

Symbol Pin I/O OD Description

DATA11 F4 I/O 4

DATA10 F2 I/O 4

DATA9 F3 I/O 4

DATA8 E1 I/O 4

DATA7 E2 I/O 4

DATA6 E3 I/O 4

DATA5 D1 I/O 4

DATA4 C1 I/O 4

DATA3 B1 I/O 4

DATA2 D4 I/O 4

DATA1 D3 I/O 4

DATA0 C2 I/O 4

BE3_ D9 I/O 2 Byte enable D31:D24

BE2_ A9 I/O 2 Byte enable D23:D16

14

BE1_ C9 I/O 2 Byte enable D15:D08

BE0_ B9 I/O 2 Byte enable D07:D00

TS_ A8 U I/O 4 DO NOT USE

Add an external 820 ohm pullup to 3.3 V.

TA_ D8 U I/O 4 Data transfer acknowledge

Add an external 820 ohm pullup to 3.3 V.

TA_ is bidirectional. It is used in input mode to

terminate a memory cycle externally. It is used in

output mode for reference purposes only.

TEA_ C8 U I/O 4 Data transfer error acknowledge

Add an external 820 ohm pullup to 3.3 V.

TEA_ is bidirectional. It is used in input mode to

terminate a memory cycle externally. It is used in

output mode for reference purposes only.

RW_ D6 I/O 2 Transfer direction

BR_ D7 NO CONNECT

Table 2: System bus interface pinout

NS7520 Hardware Reference, Rev G 9/2007

Page 27

Pinout and Packaging

Symbol Pin I/O OD Description

BG_ C7 NO CONNECT

BUSY_ B7 NO CONNECT

Table 2: System bus interface pinout

Signal descriptions

Mnemonic Signal Description

BCLK Bus clock Provides the bus clock. All system bus interface signals are

referenced to the BCLK signal.

ADDR[27:0] Address bus Identifies the address of the peripheral being addressed by

the current bus master. The address bus is bi-directional.

DATA[31:0] Data bus Provides the data transfer path between the NS7520 and

external peripheral devices. The data bus is bi-directional.

Recommendation: Less than x32 (S)DRAM/SRAM

memory configurations. Unconnected data bus pins will

float during memory read cycles. Floating inputs can be a

source of wasted power.

For other than x32 DRAM/SRAM configurations, the

unused data bus signals should be pulled up.

TS_ Transfer start NO CONNECT

BE_ Byte enable Identifies which 8-bit bytes of the 32-bit data bus are active

during any given system bus memory cycle. The BE_

signals are active low and

bi-directional.

TA_ Transfer acknowledge Indicates the end of the current system bus memory cycle.

This signal is driven to 1 prior to

tri-stating its driver.

TA_ is bi-directional.

Table 3: System bus interface signal description

www.digiembedded.com

15

Page 28

Pinout detail tables and signal descriptions

Mnemonic Signal Description

TEA_ Transfer error acknowledge Indicates an error termination or burst cycle termination:

RW_ Read/write indicator Indicates the direction of the system bus memory cycle.

BR_ Bus request NO CONNECT

BG_ Bus grant NO CONNECT

BUSY_ Bus busy NO CONNECT

Table 3: System bus interface signal description

In conjunction with TA_ to signal the end of a burst

cycle.

Independently of TA_ to signal that an error occurred

during the current bus cycle. TEA_ terminates the

current burst cycle.

This signal is driven to 1 prior to tri-stating its driver.

TEA_ is bi-directional. The NS7520 or the external

peripheral can drive this signal.

RW_ high indicates a read operation; RW_ low indicates a

write operation. The RW_ signal is bi-directional.

Chip select controller

The NS7520 supports five unique chip select configurations:

Symbol Pin I/O OD Description

CS4_ B4 O 4 Chip select/DRAM RAS_

CS3_ A4 O 4 Chip select/DRAM RAS_

CS2_ C5 O 4 Chip select/DRAM RAS_

CS1_ B5 O 4 Chip select/DRAM RAS_

CS0_ D5 O 4 Chip select (boot select)

CAS3_ A1 O 4 FP/EDO DRAM column strobe

CAS2_ C4 O 4 FP/EDO DRAM column strobe

Table 4: Chip select controller pinout

16

D31:D24/SDRAM RAS_

D23:D16/SDRAM CAS_

NS7520 Hardware Reference, Rev G 9/2007

Page 29

Pinout and Packaging

Symbol Pin I/O OD Description

CAS1_ B3 O 4 FP/EDO DRAM column strobe

D15:D08/SDRAM WE_

CAS0_ A2 O 4 FP/EDO DRAM column strobe

D07:D00/SDRAM A10(AP)

WE_ C6 O 4 Write enable for NCC Ctrl’d cycles

OE_ B6 O 4 Output enable for NCC Ctrl’d cycles

Table 4: Chip select controller pinout

Signal descriptions

Mnemonic Signal Description

CS0_

CS1_

CS2_

CS3_

CS4_

CAS0_

CAS1_

CAS2_

CAS3_

WE_ Write enable Active low signal that indicates that a memory write cycle

Chip select 0

Chip select 1

Chip select 2

Chip select 3

Chip select 4

Column address strobe

signals

Unique chip select outputs supported by the NS7520. Each

chip select can be configured to decode a portion of the

available address space and can address a maximum of 256

Mbytes of address space. The chip selects are configured

using registers in the memory module.

A chip select signal is driven low to indicate the end of the

current memory cycle. For FP/EDO DRAM, these signals

provide the RAS signal.

Activated when an address is decoded by a chip select

module configured for DRAM mode. The CAS_ signals

are active low and provide the column address strobe

function for DRAM devices.

The CAS_ signals also identify which 8-bit bytes of the 32bit data bus are active during any given system bus memory

cycle.

For SDRAM, CAS[3:1]_ provides the SDRAM command

field. CAS0_ provides the

auto-precharge signal.

For non-DRAM settings, these signals are 1.

is in progress. This signal is activated only during write

cycles to peripherals controlled by one of the chip selects in

the memory module.

Table 5: Chip select controller signal description

www.digiembedded.com

17

Page 30

Pinout detail tables and signal descriptions

Mnemonic Signal Description

OE_ Output enable Active low signal that indicates that a memory read cycle is

Table 5: Chip select controller signal description

Ethernet interface MAC

in progress. This signal is activated only during read cycles

from peripherals controlled by one of the chip selects in the

memory module.

Note:

ENDEC values for general-purpose output and TXD refer to bits in the

Ethernet General Control register. ENDEC values for general-purpose input

and RXD refer to bits in the Ethernet General Status register.

In this table, GP designates general-purpose.

Symbol Pin I/O OD Description

MII ENDEC MII ENDEC

MDC GP output D10 O 2 MII management

clock

MDIO GP output B10 U I/O 2 MII data State of UTP_STP bit

TXCLK C10 I TX clock

TXD3 GP output A12 O 2 TX data 3 State of AUI_TP[0] bit

TXD2 GP output B11 O 2 TX data 2 State of AUI_TP[1] bit

TXD1 GP output D11 O 2 TX data 1 Inverted state of PDN bit,

TXD0 TXD A11 O 2 TX data 0 Transmit data

TXER GP output A13 O 2 TX code error State of LNK_DIS_ bit

TXEN B12 O 2 TX enable

State of (LPBK bit XOR

(Mode=SEEQ))

open collector

18

TXCOL A14 I Collision

RXCRS D12 I Carrier sense

RXCLK C12 I RX clock

RXD3 GP input D14 I RX data 3 Read state in bit 12

Table 6: Ethernet interface MAC pinout

NS7520 Hardware Reference, Rev G 9/2007

Page 31

Pinout and Packaging

Symbol Pin I/O OD Description

RXD2 GP input B15 I RX data 2 Read state in bit 15

RXD1 GP input A15 I RX data 1 Read state in bit 13

RXD0 RXD B13 I RX data 0 Receive data

RXER GP input C15 I RX error Read state in bit 11

RXDV GP input D15 I RX data valid Read state in bit 10

Table 6: Ethernet interface MAC pinout

Signal descriptions

The Ethernet MII (media independent interface) provides the connection between the

Ethernet PHY and the MAC (media access controller).

Mnemonic Signal Description

MDC MII management clock Provides the clock for the MDIO serial data channel. The

MDC signal is an NS7520 output. The frequency is derived

from the system operating frequency per the CLKS field

setting (see the CLKS field in Table 69: "MII Management

Configuration register bit definition" on page 189).

MDIO Management data IO A bi-directional signal that provides a serial data channel

between the NS7520 and the external Ethernet PHY

module.

TXCLK Transmit clock An input to the NS7520 from the external PHY module.

TXCLK provides the synchronous data clock for transmit

data.

TXD3

TXD2

TXD1

TXD0

TXER Transmit coding error Output asserted by the NS7520 when an error has occurred

TXEN Transmit enable Asserted when the NS7520 drives valid data on the TXD

Transmit data signals Nibble bus used by the NS7520 to drive data to the external

Ethernet PHY. All transmit data signals are synchronized

to TXCLK.

In ENDEC mode, only TXD0 is used for transmit data.

in the transmit data stream.

outputs. This signal is synchronized to TXCLK.

Table 7: Ethernet interface MAC signal description

www.digiembedded.com

19

Page 32

Pinout detail tables and signal descriptions

Mnemonic Signal Description

COL Transmit collision Input signal asserted by the external Ethernet PHY when a

CRS Receive carrier sense Asserted by the external Ethernet PHY whenever the

RXCLK Receive clock An input to the NS7520 from the external PHY module.

collision is detected.

receive medium is non-idle.

The receive clock provides the synchronous data clock for

receive data.

RXD3

RXD2

RXD1

RXD0

Receive data signals Nibble bus used by the NS7520 to input receive data from

the external Ethernet PHY. All receive data signals are

synchronized to RXCLK.

In ENDEC mode, only RXD0 is used for receive data.

RXER Receive error Input asserted by the external Ethernet PHY when the

Ethernet PHY encounters invalid symbols from the

network.

RXDV Receive data valid Input asserted by the external Ethernet PHY when the PHY

drives valid data on the RXD inputs.

Table 7: Ethernet interface MAC signal description

20

NS7520 Hardware Reference, Rev G 9/2007

Page 33

“No connect” pins

Pin Description

R13 Add a 15K ohm pulldown to GND (15K ohm is the recommended value; 10–

P12 Add a 15K ohm pulldown to GND (15K ohm is the recommended value; 10–

N12 Tie to GND

R15 XTALB2: NO CONNECT

M11 NO CONNECT

P11 NO CONNECT

N11 NO CONNECT

R12 NO CONNECT

R14 NO CONNECT

P13 NO CONNECT

Pinout and Packaging

20K ohms is acceptable)

20K ohms is acceptable)

Table 8: “No connect” pins

Note:

General-purpose I/O

GPIO

signal

PORTA7 TXDA J14 U I/O 2 Channel 1 TXD

PORTA6 DTRA_ DREQ1_ J13 U I/O 2 Channel 1 DTR_ DMA channel 3/5

PORTA5 RTSA_ J15 U I/O 2 Channel 1 RTS_

Table 9: GPIO pinout

If your design implements 10–20K ohm pullups instead of pulldowns on

R13 and P12, and a pullup on N12 instead of GND, no action is required.

Serial

signal

Other

signal

Pin I/O OD

www.digiembedded.com

Serial channel

description

Other

description

Req

21

Page 34

Pinout detail tables and signal descriptions

GPIO

signal

PORTA4 RXCA/RIA_/

Serial

signal

OUT1A_

Other

signal

Serial channel

Pin I/O OD

description

J12 U I/O 2 Pgm’able Out/

Channel 1

Other

description

RXCLK/Channel

1 ring signal/

Channel 1 SPI

clock (CLK)

PORTA3 RXDA DACK1_ H15 U I/O 2 Channel 1 RXD DMA channel 3/5

ACK

PORTA2 DSRA_ AMUX H12 U I/O 2 Channel 1 DSR_ DRAM addr mux

PORTA1 CTSA_ DONE1_

(O)

PORTA0 TXCA/

DONE1_ (I) G12 U I/O 2 Pgm’able Out/

OUT2A_/

DCDA_

H13 U I/O 2 Channel 1 CTS_ DMA channel 3/5

DONE_Out

DMA channel 3/5

Channel 1 DCD/

DONE_In

Channel 1 SPI

enable (SEL_)/

Channel 1

TXCLK

PORTC7 TXDB G13 U I/O 2 Channel 2 TXD GEN interrupt out

PORTC6 DTRB_ DREQ2_ G14 U I/O 2 Channel 2 DTR_ DMA channel 4/6

Req

22

PORTC5 RTSB_ REJECT_ F15 U I/O 2 Channel 2 RTS_ CAM reject

PORTC4 RXCB/RIB_/

OUT1B_

RESET_ F12 U I/O 2 Pgm’able Out/

Channel 2

RXCLK/Channel

2 ring signal/

RESET output

See Note 1

following this

table.

Channel 2 SPI

clock (CLK)

PORTC3

RXDB LIRQ3/

DACK2_

F13 U I/O 2 Channel 2 RXD Level sensitive

IRQ/DMA

2

channel 4/6 ACK

PORTC2

DSRB_ LIRQ2/

RSPF_

E15 U I/O 2 Channel 2 DSR_ Level sensitive

IRQ/CAM

2

request

Table 9: GPIO pinout

NS7520 Hardware Reference, Rev G 9/2007

Page 35

Pinout and Packaging

GPIO

signal

PORTC12CTSB_ LIRQ1/

PORTC0

2

Serial

signal

TXCB/

OUT2B_/

DCDB_

Other

signal

DONE2_

(O)

LIRQ0/

DONE2_(I)

Serial channel

Pin I/O OD

E12 U I/O 2 Channel 2 CTS_ Level sensitive

E14 U I/O 2 Pgm’able Out/

description

Channel 2 DCD/

Channel 2 SPI

enable (SEL_)/

Channel 2

TXCLK

Other

description

IRQ/DMA

channel 4/6

DONE_out

Level sensitive

IRQ/DMA

channel 4/6

DONE_in

Table 9: GPIO pinout

Notes:

1 RESET output indicates the reset state of the NS7520. PORTC4 persists beyond

the negation of RESET_ for approximately 512 clock cycles if the PLL is disabled.

When the PLL is enabled, PORTC4 persists beyond the negation of RESET_ to

allow for PLL lock for 100 microseconds times the ratio of the VCO to XTALA.

Note that this GPIO is left in output mode active following a hardware

RESET.

2 *PORTC[3:0] pins provide level-sensitive interrupts. The inputs do not need to

be synchronous to any clock. The interrupt remains active until cleared by a

change in the input signal level.

Signal descriptions

See Chapter 6, "GEN Module," for signal and configuration information for PORTA and

PORTC.

www.digiembedded.com

23

Page 36

Pinout detail tables and signal descriptions

System clock and reset

Symbol Pin I/O OD Description

XTALA1 K14 I ARM/system oscillator circuit

XTALA2 K12 O

PLLVDD (1.5V) L15 P PLL clean power

PLLVSS L12 P PLL return

RESET_ A10 I System reset

Table 10: System clock pinout

Signal descriptions

The NS7520 has three clock domains:

System clock (SYSCLK)

Bit rate generation and programmable timer reference clock (XTALA1/2)

System bus clock (BCLK)

24

The SYS module provides the NS7520 with these clocks, as well as system reset and

backup resources.

Mnemonic Signal Description

XTALA1

XTALA2

PLLVDD

PLLVSS

RESET_ System reset Resets the NS7520 hardware.

Oscillator input

Oscillator output

Clean PLL power

Connect directly to the

GND plane

A standard parallel quartz crystal or crystal oscillator can

be attached to these pins to provide the main input clock to

the NS7520.

Power and ground for PLL circuit.

Table 11: Clock generation and reset signal description

NS7520 Hardware Reference, Rev G 9/2007

Page 37

This figure shows the timing and specification for RESET_ rise/fall times:

tR ma x = 18 ns

Vi n = 0.8V to 2.0V

tF max = 18ns

Vi n = 2.0V to 0.8V

tF tR

System mode (test support)

PLLTST_, BISTEN_, and SCANEN_ primary inputs control different test modes for both

functional and manufacturing test operations. See Chapter 5, "SYS Module," for more

information.

Symbol Pin I/O OD Description

PLLTST_ N15 I Encoded with BISTEN_ and SCANEN_

Pinout and Packaging

Add an external pullup to 3.3V or pulldown to

GND.

Table 12: System mode and system reset pinout

BISTEN_ M15 I Encoded with PLLTST_ and SCANEN_

Add an external pullup to 3.3V or pulldown to

GND.

SCANEN_ L13 I Encoded with BISTEN_ and PLLTST_

Add an external pullup to 3.3V or pulldown to

GND.

www.digiembedded.com

25

Page 38

Pinout detail tables and signal descriptions

JTAG test (ARM debugger)

JTAG boundary scan allows a tester to check the soldering of all signal pins and tristate all outputs.

Symbol Pin I/O OD Description

TDI N14 U I Test data in

TDO M13 O 2 Test data out

TMS M12 U I Test mode select

TRST_ M14 I Test mode reset

TCK P15 I Test mode clock

Table 13: JTAG test pinout

Requires external termination when not being

used (see Figure 4, "TRST_ termination," on

page 27 for an illustration of the termination

circuit on the development PCB).

Add an external pullup to 3.3V.

26

Signal descriptions

Mnemonic Signal Description

TDI Test data in TDI operates the JTAG standard. Consult the JTAG

specifications for use in boundary-scan testing. These

signals meet the requirements of the Raven and Jeeni

debuggers.

TDO Test data out TDO operates the JTAG standard. Consult the JTAG

specifications for use in boundary-scan testing. These

signals meet the requirements of the Raven and Jeeni

debuggers.

TMS Test mode select TMS operates the JTAG standard. Consult the JTAG

specifications for use in boundary-scan testing. These

signals meet the requirements of the Raven and Jeeni

debuggers.

Table 14: ARM debugger signal description

NS7520 Hardware Reference, Rev G 9/2007

Page 39

Pinout and Packaging

NS7520

TRSTNS7520

Mnemonic Signal Description

TRST_ Test mode reset TRST_ operates the JTAG standard. Consult the JTAG

specifications for use in boundary-scan testing. These

signals meet the requirements of the Raven and Jeeni

debuggers.

TCK Test mode clock TCK operates the JTAG standard. Consult the JTAG

specifications for use in boundary-scan testing. These

signals meet the requirements of the Raven and Jeeni

debuggers.

Table 14: ARM debugger signal description

Figure 4: TRST_ termination

www.digiembedded.com

27

Page 40

Pinout detail tables and signal descriptions

Power supply

Signal Pin Description

Oscillator VCC (3.3V) N13, C3 Oscillator power supply

Core VCC (1.5V) R8, L14, C14, C13 Core power supply

I/O VCC (3.3V) E4, K4, M2, N3, P3, R5, H14, F14, B8, A3 I/O power supply

GND D2, F1, J4, P4, P7, M8, P9, R11, K15, G15,

E13, D13, B14, C11, A7, A5, B2, P2, P14,

K13

Ground

Table 15: Power supply pinout

See the DC and AC electrical specifications in Chapter 11, "Electrical Characteristics,"

for more information.

28

NS7520 Hardware Reference, Rev G 9/2007

Page 41

Working with the CPU

Working with the CPU

CHAPTER 3

The CPU uses an ARM7TDMI core processor, which provides high performance while

maintaining low power consumption and small size. This chapter describes the ARM

Thumb concept and provides an overview of ARM exceptions and hardware interrupts.

www.digiembedded.com

29

Page 42

ARM Thumb concept

ARM Thumb concept

The ARM7TDMI processor uses a unique architectural strategy known as Thumb, which

makes the processor ideally suited to high-volume applications with memory

restrictions or applications for which code density is an issue.

Thumb code’s primary attribute is a super-reduced instruction set. The ARM7TDMI

processor has essentially two instruction sets:

Standard 32-bit ARM set

16-bit Thumb set

Thumb’s 16-bit instruction length allows it to approach twice the density of standard

ARM code while retaining most of the ARM’s performance advantage over a

traditional 16-bit processor using 16-bit registers. Thumb code operates on the same

32-bit register set as the ARM code, but consumes only 65% of the same code

compiled in ARM mode.

Thumb instructions operate with the standard ARM register configuration, allowing

interoperability between ARM and Thumb states. Each 16-bit Thumb instruction has a

corresponding 32-bit ARM instruction with the same effect on the processor model.

Thumb architecture provides a Thumb instruction decoder in front of the standard

32-bit ARM processor. The Thumb instruction decoder basically remaps each 16-bit

Thumb instruction into a 32-bit standard ARM instruction. The Thumb instruction set

typically requires 30% more instructions to perform the same task as 32-bit

instructions, but the Thumb instruction can fit twice as many instructions in the code

space. The net result is a 35% decrease in overall code density.

CPU performance

The ARM7TDMI core does not contain cache, and runs as fast as instructions can be

fetched. The performance rating for the ARM RISC depends on system bus speed and

cycle time. Performance is also affected by the size of the system bus and the type of

code (ARM or Thumb) being executed.

30

NS7520 Hardware Reference, Rev G 9/2007

Page 43

Working with the CPU

The ARM instruction set yields a 0.9 Dhrystone (2.1) rating MIPS/MHz of instruction

executions; the Thumb instruction set yields 0.75 Dhrystones MIPS/MHz. The MHz

rating reflects the rate at which instructions can be fetched from external flash

memory, as shown in this table:

System bus

size Code style RISC speed

Thumb mode

16-bit Thumb 25 MHz 25 MHz 1 120 ns N/A

16-bit Thumb 25 MHz 25 MHz 0 80 ns N/A

16-bit Thumb 36 MHz 36 MHz 3 125 ns N/A

16-bit Thumb 46 MHz 46 MHz 4 109 ns N/A

16-bit Thumb 55 MHz 55 MHz 5 108 ns N/A

ARM mode

32-bit ARM 36 MHz 36 MHz 3 125 ns 6.8

32-bit ARM 46 MHz 46 MHz 4 109 ns 8.6

32-bit ARM 55 MHz 55 MHz 5 108 ns 10.4

System bus

speed

Wait

states

Instruction

cycle time

Table 16: ARM performance

Working with ARM exceptions

Dhrystone

rating

Exceptions occur when the normal flow of a program is halted temporarily; for

example, to service an interrupt from a peripheral. Each ARM exception causes the

ARM processor to save some state information, then jump to a location in low

memory (referred to as the vector table; see "Exception vector table" on page 33).

Before an exception can be handled, the current processor state must be preserved

so the original program can resume when the handler routine has finished.

www.digiembedded.com

31

Page 44

Working with ARM exceptions

Summary of ARM exceptions

The ARM processor can be interrupted by any of seven basic exceptions:

Reset exception. After a reset condition, the ARM7TDMI saves the current

values of the PC (program counter) and CPSR (Current Processor Status

register).

Undefined exception. The ARM7TDMI takes the undefined instruction trap

when it finds an instruction it cannot handle.

SWI instruction. The ARM7TDMI uses the software interrupt instruction

(SWI) to enter supervisor mode, usually to request a specific supervisor

instruction.

Abort exception. An abort exception indicates that the current memory

access cannot be completed. There are two types of abort exception:

– Prefetch. Occurs during an instruction prefetch.

– Data. Occurs during a data operand access.

IRQ. An interrupt request (IRQ) exception is a normal interrupt serviced by

the ARM7TDMI controller.

FIRQ. A fast interrupt request (FIRQ) exception supports a data transfer or

channel process. An FIRQ interrupt is generated only by the GEN module

timers and watchdog timer.

Exception priorities

Several exceptions can occur at the same time. If this happens, a fixed-priority

system determines the order in which they are handled:

Highest priority

1 Reset

2 Data abort

3 FIRQ

4 IRQ

5 Prefetch abort

6 Undefined instruction, SWI

Lowest priority

32

NS7520 Hardware Reference, Rev G 9/2007

Page 45

Not all exceptions can occur at the same time, however.

Undefined instructions and SWIs are mutually exclusive, as they each

correspond to particular (non-overlapping) decoding of the current

instruction.

If a data abort occurs at the same time as FIRQ and the FIRQ is enabled

(that is, the CPSR F flag is clear), the data abort takes priority. ARM7TDMI

enters the data abort handler and immediately goes to the FIRQ vector. A

normal return from FIRQ causes the data abort handler to resume

execution.

Placing data abort at a higher priority than FIRQ is necessary to ensure

that the transfer error does not escape detection. The time for this

exception entry should be added to worst-case FIRQ latency

calculations.

Exception vector table

All exceptions result in the ARM processor vectoring to an address in low memory,

using the exception vector table. The exception vector table always exists and always

starts at base address 0.

Working with the CPU

Vector

address

’h0 RESET Reset vector; for initialization and startup

’h4 Undefined Undefined instruction encountered

’h8 SWI Software interrupt; used for entry point into the kernel

’hC Abort (prefetch) Bus error (no response or error) fetching instructions

’h10 Abort (data) Bus error (no response or error) fetching data

’h14 Reserved Reserved

’h18 IRQ Interrupt from ARM7TDMI interrupt controller

’h1C FIRQ Fast interrupt from ARM7TDMI controller

Vector Description

Table 17: Exception vector table

www.digiembedded.com

33

Page 46

Working with ARM exceptions

All internal ARM7TDMI internal peripherals are presented to the CPU using the IRQ or

FIRQ interrupt inputs. The ARM can mask various ARM7TDMI peripheral interrupts at

the global level, using the ARM7TDMI interrupt controller. The ARM also can mask

interrupts at the micro-level, using configuration features with the peripheral

modules.

All IRQ interrupts are disabled when the I bit is set in the ARM CPSR. When the I bit is

cleared, those interrupts enabled in the ARM7TDMI interrupt controller can assert the

IRQ input to the ARM processor.

The ARM processor sets the I bit automatically when entering an interrupt service

routine (ISR), which disables recursive interrupts. The ISR’s first task is to read the

Interrupt Status register, which identifies all active sources for the IRQ interrupt.

Firmware sets the priorities for servicing interrupts at bootup, using the bits defined

in the Interrupt Status register.

Detail of ARM exceptions

Reset exception

34

A reset exception is the highest priority exception. When the ARM7TDMI is held in

reset, the processor abandons the executing instruction and continues to fetch

instructions from incrementing word addresses.

When the ARM7TDMI is removed from reset, the processor performs these steps:

1 Overwrites R14_svc and SPSR_svc (Saved Processor Status register) by copying the

current values of the PC and CPSR into them. The values of the saved PC and

SPSR are not defined.

2 Forces the CPSR M field to 10011 (supervisor mode), sets the I and F bits in the

CPSR, and clears the CPSR T bit (back to ARM mode).

3 Forces the PC to fetch the next instruction from address ’h00.

4 Resumes execution in ARM state.

Undefined exception

When the ARM7TDMI encounters an instruction it cannot handle, it takes the

undefined instruction trap. The undefined instruction trap can extend either the

Thumb or ARM instruction set by software emulation.

NS7520 Hardware Reference, Rev G 9/2007

Page 47

Working with the CPU

After emulating the failed instruction, the trap handler should execute the following

instruction irrespective of the state (Thumb or ARM):

MOVS PC, R14_und.

This instruction restores the PC and CPSR, and returns to the instruction following the

undefined instruction.

SWI exception

An SWI is used for entering supervisor mode, usually to request a particular supervisor

function. An SWI handler should return by executing this instruction irrespective of

the state (ARM or Thumb):

MOVS PC, R14_SVC.

This instruction restores the PC and CPSR, and returns to the instruction following the

SWI.

Abort exception

An abort indicates that the current memory access cannot be completed, and is

signaled by the external ABORT input. The ARM7TDMI checks for the abort exception

during memory access cycles.

There are two types of abort exception:

Prefetch abort. Occurs during an instruction prefetch. If a prefetch abort

occurs, the prefetch instruction is marked as invalid but the exception is

not taken until the instruction reaches the head of the pipeline. If the

instruction is not executed (for example, if a branch occurs while the

instruction is in the pipeline), the abort does not take place.

Data abort. Occurs during a data operand access. If a data abort occurs, the

action taken depends on the instruction type:

– Single data transfer instructions (LDR, STR) write back modified base

registers; the abort handler must be aware of this.

– A swap instruction (SWP) is aborted as though it had not been executed.

– Block data transfer instructions (LDM, STM) complete. If write-back is set,

the base is updated. If the instruction would have overwritten the base with

data (that is, the base is in the transfer list), the overwriting is prevented.

All register overwriting is prevented after an abort is indicated, which

means that

R15 (always the last register to be transferred) is preserved in an

aborted LDM instruction.

www.digiembedded.com

35

Page 48

Working with ARM exceptions

The abort mechanism allows the implementation of a demand-paged virtual memory

system. In this type of system, the processor is allowed to generate arbitrary

addresses. When the data at an address is unavailable, the memory management unit

(MMU) signals an abort. The abort handler must then work out the cause of the abort,

make the requested data available, and retry the aborted instruction. The

application program needs no knowledge of the amount of memory available to it,

and its state is not affected by the abort.

The handler executes one of the following instructions, irrespective of the state (ARM

or Thumb), after fixing the cause of the abort:

For a prefetch abort: SUBS PC, R14_abt, #4

For a data abort: SUBS PC, R14_abt, #8

IRQ exception

An IRQ exception is a normal interrupt sourced by the ARM7TDMI interrupt controller.

IRQ has a lower priority than FIRQ, and is masked out when an FIRQ sequence is

entered. IRQ can be disabled at any time by setting the I bit in CPSR to 1; this can be

done only from privileged (non-user) mode.

36

The IRQ handler should leave the interrupt by executing the following instruction

irrespective of the state (ARM or Thumb):

SUBS PC, R14_irq, #4.

FIRQ exception

An FIRQ exception supports a data transfer or channel process. In ARM state, FIRQ has

enough registers to remove the need for register saving, which minimizes context

switching overhead.

Only two peripherals can generate an FIRQ interrupt: the GEN module built-in timers

and the GEN module watchdog timer.

The FIRQ handler should leave the interrupt by executing the following instruction

irrespective of the state (ARM or THUMB):

SUBS PC, R14_firq, #4.

The FIRQ interrupt can be disabled by setting the CPSR F flag to 1, only in non-user

mode. If the F flag is clear, the ARM7TDMI checks for a low level on the output of the

FIRQ synchronizer at the end of each instruction.

NS7520 Hardware Reference, Rev G 9/2007

Page 49

Entering and exiting an exception (software action)

The ARM7TDMI performs specific steps when handling exceptions.

Entering an exception

When handling an exception, ARM7TDMI does this:

1 Preserves the address of the next instruction in the appropriate Link register.

– If the exception has been entered from the ARM state, the address of the

next instruction is copied into the Link register. The address is either

current

"Exception entry/exit by exception type" on page 38.)

– If the exception has been entered from Thumb state, the value written into

the Link register is the current PC offset by a value that lets the program

continue from the correct place on return from the exception.

The exception handler does not need to determine from which state the

exception was entered. With an SWI, for example,

returns to the next instruction whether executed in ARM or Thumb state.

PC + 4 or PC + 8, depending on the exception. (See Table 18:

Working with the CPU

MOVS PC, R14_SVC always

2 Copies the CPSR into the appropriate SPSR.

3 Forces the CPSR mode bits to a value that depends on the exception.

4 Forces the PC to fetch the next instruction from the relevant exception vector.

5 Sets the I (for IRQ interrupts) or F (for FIRQ interrupts) bits to disable interrupts

to prevent unmanageable nesting of exceptions.

Note:

If the processor is in Thumb state when an exception occurs, it

automatically switches into ARM state when the PC is loaded with the

exception vector address.

Exiting an exception

On completion, ARM7TDMI does this:

1 Moves the Link register, minus the offset where appropriate, to the PC. The

offset value varies depending on the type of exception.

2 Copies the SPSR back to the CPSR.

3 Clears the interrupt disable flags, if they were set on entry.

www.digiembedded.com

37

Page 50

Working with ARM exceptions

Note:

An explicit switch back to Thumb state is never needed. Restoring the

CPSR from the SPSR automatically sets the T bit to the value it held

immediately before the exception.

Exception entry/exit summary

In the variable

Return/

exception

BL

RESET NA NA NA 4

UNDEF

SWI

ABORT P

ABORT D

IRQ

FIRQ

R14_x, R14 is the Link register; _x is the previous state of the processor.

Return instruction

MOV PC, R14

MOVS PC, R14_und

MOVS PC, R14_svc

SUBS PC, R14_abt, #4

SUBS PC, R14_abt, #8

SUBS PC, R14_irq, #4

SUBS PC, R14_firq, #4

Previous state

ARM R14_x

PC+4 PC+2 1

PC+4 PC+2 1

PC+4 PC+2 1

PC+4 PC+4 1

PC+8 PC+8 3

PC+4 PC+4 2

PC+4 PC+4 2

Previous state

Thumb R14_x

Notes

38

Table 18: Exception entry/exit by exception type

Notes:

Where PC is the address of the BL/SWI/undefined instruction fetch that had the

1

prefetch abort. BL is a branch with link instruction.

2 Where PC is the address of the instruction that was not executed since FIRQ or

IRQ took priority.

3 Where PC is the address of the load or store instruction that generated the data

abort.

4 The value saved in R14_svc upon reset is unpredictable.

NS7520 Hardware Reference, Rev G 9/2007

Page 51

Hardware Interrupts

Two wires that go into the ARM7 CPU core can interrupt the processor:

IRQ (normal interrupt)

FIRQ (fast interrupt)

Although the interrupts are basically the same, FIRQ can interrupt IRQ.

FIRQ and IRQ lines

The FIRQ line adds a simple, two-tier priority scheme to the interrupt system. Most

sources of interrupts on the ARM7TDMI come from the IRQ line. The only potential

sources for FIRQ interrupts in the ARM7TDMI come from the two built-in timers and

the watchdog timer; there is no way to generate an FIRQ signal externally. These

timers are controlled by registers in the GEN module (see "Timer Control registers,"

beginning on page 70):

The built-in timers are controlled using the Timer Control registers

(’hFFB0 0010/18). The corresponding bit in the Interrupt Enable register must

be set for either IRQ or FIRQ to function.

Working with the CPU

The watchdog timer is controlled using the System Control register

(’hFFB0 0000).

Interrupt controller

Interrupts come from many different sources on the ARM7TDMI, and are managed by

the interrupt controller within the GEN module. Interrupts can be enabled or disabled

on a per-source basis using the Interrupt Enable register (’hFFB0 0030), which serves as

a mask for the interrupt sources and ultimately controls whether an interrupt from an

ARM7TDMI module can reach the IRQ line.

There are two read-only registers in the interrupt controller:

Interrupt Status Register Raw. Indicates the source of an ARM7TDMI

interrupt regardless of the state of the Interrupt Enable register. All

interrupts that are active in their respective module will be visible in the

Interrupt Status Register Raw.

www.digiembedded.com

39

Page 52

Hardware Interrupts

Interrupt Status Register Enabled. Identifies the current state of all

interrupt sources that are enabled. This register is defined by performing a

logical AND of the Interrupt Status Register Raw and the Interrupt Enable

register. All bits in the Interrupt Status Register Enabled are ORed together.

The output is fed directly to the IRQ line, which then interrupts the ARM.

Interrupt sources

Each interrupt source is enabled and disabled within its respective module (and

submodule) within the NS7520 ASIC. The interrupt controller in the GEN module,

however, does not latch any of the interrupt signals.

Note:

Interrupt causes are latched in their respective submodule until cleared.

Interrupt sources include the following:

DMA interrupts. All [13] DMA channels, including the four sub-channels of

the Ethernet receiver, have five possible interrupt sources. See Chapter 8,

"DMA Module."

Ethernet receive and transmit interrupts. There are three interrupts for

Ethernet receive and four interrupts for Ethernet transmit; all interrupts

are part of the Ethernet General Status register. These interrupts are used

only when the Ethernet receiver and transmitter are in interrupt mode

rather than DMA mode. See Chapter 9, "Ethernet Module."

Serial interrupts. The Serial Channel Status register has many interrupt

sources. See Chapter 10, "Serial Controller Module."

Watchdog timer interrupts. When the watchdog timer expires, the system

can generate either an IRQ interrupt, an FIRQ interrupt, or a system reset.

The interrupt type and length of the timer are configured using the GEN

module System Control register. The watchdog is strobed using the Software

Service register. See Chapter 6, "GEN Module."

Timer 1 and Timer 2 interrupts. Two types of interrupts can be generated

by Timers 1 and 2. The interrupt type is configured in the Timer Control

register; the interrupt itself is contained within the Timer Status register.

See Chapter 6, "GEN Module."

40

NS7520 Hardware Reference, Rev G 9/2007

Page 53