Page 1

User Manual

DA14531 USB Development Kit

Hardware

UM-B-125

Abstract

This document outlines the system design, configuration options, and supported features of

DA14531 USB Development Kit rev.C (3 76-13-C).

Page 2

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

2 of 32

© 2020 Dialog Semiconductor

Contents

Abstract ................................................................................................................................................ 1

1 Terms and Definitions ................................................................................................................... 4

2 References ..................................................................................................................................... 4

3 Introduction.................................................................................................................................... 5

4 System Overview ........................................................................................................................... 5

4.1 Features ................................................................................................................................ 5

4.2 System and Components Description (Top View) ................................................................ 6

4.3 System and Components Description (Bottom View) ........................................................... 7

5 USB Kit System ............................................................................................................................. 8

5.1 Overview ............................................................................................................................... 8

5.2 DA14531 System .................................................................................................................. 9

5.3 DA14531 GPIO Assignment ............................................................................................... 10

5.4 Default Configuration .......................................................................................................... 11

5.5 1-wire Bootable UART ........................................................................................................ 12

5.6 Optional 2-/4-Wire UART .................................................................................................... 13

5.7 Crystals ............................................................................................................................... 14

5.8 Antenna and RF Port .......................................................................................................... 15

5.9 SPI Data Flash Memory (U2) .............................................................................................. 16

5.10 Reset Circuit ........................................................................................................................ 17

5.11 General Purpose Push Button ............................................................................................ 18

5.12 Debugging Port DIP Switch ................................................................................................ 19

5.13 MikroBUS™ Module ............................................................................................................ 20

5.14 User Controlled LED ........................................................................................................... 21

5.15 GND Test Point ................................................................................................................... 21

5.16 Over Voltage Protection Circuit (OVP) ................................................................................ 22

5.17 Debug Interface (U4) ........................................................................................................... 23

5.18 Power Measurements ......................................................................................................... 24

5.19 Operation from a Wall Adapter or Power Pack ................................................................... 25

5.20 Operation from a Coin Cell Battery ..................................................................................... 26

Appendix A Schematics .................................................................................................................... 27

Appendix B Components Placement on PCB ................................................................................ 29

Appendix C PCB Layer Chart ........................................................................................................... 30

Revision History ................................................................................................................................ 31

Page 3

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

3 of 32

© 2020 Dialog Semiconductor

Figures

Figure 1: DA14531 USB Kit ................................................................................................................... 5

Figure 2: USB Kit - Top Side ................................................................................................................. 6

Figure 3: USB Kit - Bottom Side ............................................................................................................ 7

Figure 4: Block diagram of DA14531 USB Development Kit ................................................................ 9

Figure 5: DA14531 Section Schematic ................................................................................................. 9

Figure 6: Default DIP Switch Configuration ......................................................................................... 11

Figure 7: Single Pin UART Multiplexer ................................................................................................ 12

Figure 8: DIP Switch Configuration for UART ..................................................................................... 13

Figure 9: RF Section ............................................................................................................................ 15

Figure 10: SPI Data Flash ................................................................................................................... 16

Figure 11: SPI Flash Package Options ............................................................................................... 16

Figure 12: Reset Circuit ....................................................................................................................... 17

Figure 13: RESET Push Button (SW1) ............................................................................................... 17

Figure 14: General Purpose Push Button ........................................................................................... 18

Figure 15: General Purpose Push Button SW2................................................................................... 18

Figure 16: DIP Switch Configuration ................................................................................................... 19

Figure 17: MikroBus™ Pin Assignment ............................................................................................... 20

Figure 18: Guides for Proper MikroBus™ Click Board Insertion ......................................................... 20

Figure 19: MikroBus™ Pin Assignment (Bottom View) ....................................................................... 21

Figure 20: General Purpose LED ........................................................................................................ 21

Figure 21: GND Support Point............................................................................................................. 21

Figure 22: Over Voltage Protection Circuit .......................................................................................... 22

Figure 23: Debugging Processor - UART and JTAG Interface (U4) ................................................... 23

Figure 24: Power Measurement Header ............................................................................................. 24

Figure 25: Current Measurement Header (J2) .................................................................................... 24

Figure 26: Operation with a Battery Pack ............................................................................................ 25

Figure 27: Resistor R48 ....................................................................................................................... 25

Figure 28: Resistors R50 and R51 ...................................................................................................... 26

Figure 29: DA14531 SoC and Peripherals .......................................................................................... 27

Figure 30: Debug Interface (UART/JTAG) .......................................................................................... 28

Figure 31: Components Placement, Top Side on the Left and Bottom Side on the Right .................. 29

Figure 32: PCB Cross Section ............................................................................................................ 30

Tables

Table 1: DA14531 USB Development Kit Pin Assignment ................................................................. 10

Table 2: Default Configuration DIP Settings........................................................................................ 11

Table 3: UART Configuration DIP Settings ......................................................................................... 13

Table 4: Y1 (32 MHz Crystal) Characteristics ..................................................................................... 14

Table 5: Y2 (32 kHz Crystal) Characteristics ...................................................................................... 14

Table 6: RF Components Names and Values ..................................................................................... 15

Table 7: DIP Switch Configuration ...................................................................................................... 19

Page 4

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

4 of 32

© 2020 Dialog Semiconductor

1 Terms and Definitions

CIB Communication Interface Board

DCR Direct Current Resistor

DMIPS Dhrystone Million Instructions per Second

ESR Effective Series Resistance

GPIO General Purpose Input Output

I2C Inter-Integrated Circuit

JTAG Join Test Action Group

LDO Low Dropout

MISO Master In Slave Out

MOSI Master Out Slave In

OTP One Time Programmable

OVP Over Voltage Protection

PC Personal Computer

PCB Printed Circuit Board

PCBA Printed Circuit Board Assembly

PLL Phase-Locked Loop

QSPI Quad Serial Peripheral Interface

RF Radio Frequency

RFIO Radio Frequency Input Output

SDK Software Development Kit

SIMO Single-Inductor Multiple-Output

SMA Sub-Miniature version A

SMD Surface-Mount Device

SoC System on Chip

SOIC Small Outline Integrated Circuit

SPI Serial Peripheral Interface

SW Software

UART Universal Asynchronous Receiver-Transmitter

USB Universal Serial Bus

2 References

[1] DA14531, Datasheet, Dialog Semiconductor.

[2] AN-B-052, DA1458x/68x Development kit J-Link Interface, Application Note, Dialog

Semiconductor.

[3] AN-B-072, DA14531 Booting Options, Application Note, Dialog Semiconductor.

[4] AN-B-027, Designing Printed Antennas for Bluetooth Smart, Application Note, Dialog

Semiconductor.

Page 5

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

5 of 32

© 2020 Dialog Semiconductor

3 Introduction

This document describes Dialog’s DA14531 USB Kit (board reference number 376-13-C). This kit

offers a low-cost development board with basic functionality. The development kit is implemented on

a single PCB. The block diagram, the actual board, the various sections and settings as well as the

connectivity are presented. The purpose of this cost-effective USB kit is to provide users with the

capability for:

● Software development

● Programming DA14531 via JTAG or UART using Dialog's DA14531 SDK

● Connecting MikroBUS™ modules

Figure 1: DA14531 USB Kit

4 System Overview

4.1 Features

The features of DA14531 USB kit include:

■ Highly integrated DA14531 Bluetooth® Smart SoC from Dialog Semiconductor

■ Access on GPIOs provided from the chip, when no MikroBUS™ is plugged in

■ The ability to be connected directly to PC USB without extra cables

■ Reset push button

■ General purpose LED and button

■ Using USB LDO 3V3 as a power source

■ Unpopulated coin cell battery holder as a powering option

■ JTAG and UART interface over USB (on-board SEGGER J-Link)

■ 2 Mbit SPI flash on board

■ 2.4GHz printed antenna and option for SMA connector

■ 32 MHz main crystal and option for 32.768 kHz low-power crystal

■ Low cost

■ Compact design

Page 6

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

6 of 32

© 2020 Dialog Semiconductor

4.2 System and Components Description (Top View)

Figure 2: USB Kit - Top Side

This USB development kit is based on the DA14531 SoC in an FCGQFN-24 package. The marked

and numbered sections of the system are:

1. Type-A USB connector (J1)

2. OVP Circuit

3. LDO 3.3 V (U3)

4. Unpopulated power selection header (J2)

5. J-Link status LED (green)

6. Reset button (SW1)

7. User button (SW2)

8. Debug interface μController (U4)

9. Inverter for J-Link reset (U6)

10. Multiplexer for 1-pin UART (U5)

11. System configuration DIP-switch (S1)

12. Unpopulated MikroBus™ socket (or breakout header in general)

13. 2 Mbit SPI Flash (U2)

14. Unpopulated 32.468 kHz crystal (Y2)

15. DA14531 Bluetooth® Smart SoC

16. 32 MHz crystal

17. Printed Antenna

18. GND test-point

19. Unpopulated SMA connector (J5)

20. User LED (orange)

Page 7

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

7 of 32

© 2020 Dialog Semiconductor

4.3 System and Components Description (Bottom View)

Figure 3: USB Kit - Bottom Side

The bottom side of the USB development kit provides information about the MikroBus™ pins

assignment, the SEGGER ID, and the date code. Test points have been placed for monitoring

various signal behaviors and voltage levels of the components. The marked and numbered sections

of the system are:

21. Unpopulated resistor for bypass mode

22. GPIO numbers (add P0_ before the number for the full name)

23. J-Link debugger serial number

24. Pads to solder a coin cell holder

Page 8

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

8 of 32

© 2020 Dialog Semiconductor

5 USB Kit System

5.1 Overview

● Board name/number:

○ DA14531 USB development kit/376-13-C

● SoC:

○ DA14531 in FCGQFN-24 package

● Flash memory:

○ MX25R2035F (2 Mbit) QSPI Flash Memory in 8-pin U-SON (2 mm × 3 mm) package. Note

that it is accessed in plain SPI mode.

○ 3.3 V power supply (VHIGH)

● Clock inputs:

○ 32 MHz crystal

○ Optional low power 32.768 kHz crystal

● Power

○ 3.3 V LDO powering VHIGH on DA14531 (buck mode configuration)

● Ports:

○ USB port for debugging purposes

● Interfaces:

○ UART-J-Link CDC UART Port (listed under Ports in Device Manager)

○ JTAG-J-Link Driver (listed under Universal Serial Bus Controllers in Device Manager)

○ DIP switch to select between interfaces and isolate the signals for accurate power

measurements

● Connectivity expansion connectors:

○ One MikroBUS™ module can be plugged to J3/J4. Note that most GPIOs are already used

for booting and debugging, so compatibility with any random Click™ board is not guaranteed

Page 9

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

9 of 32

© 2020 Dialog Semiconductor

5.2 DA14531 System

Figure 4: Block diagram of DA14531 USB Development Kit

Dialog’s DA14531 is an ultra-low power SoC integrating a 2.4 GHz Bluetooth Low Energy transceiver

and an ARM® CortexM0+™ microcontroller with 48 kB RAM and 32 kB One-Time Programmable

(OTP) ROM. It can be used as a standalone application processor or as a data pump in hosted

systems.

The DA14531 SoC also includes a cryptography engine, a power management unit, digital and

analog peripherals, and a radio transceiver.

The DA14531 has dedicated hardware for the Link Layer implementation of BLE and interface

controllers for enhanced connectivity capabilities. The radio transceiver, the baseband processor,

and the qualified Bluetooth® low energy stack is fully compliant with the Bluetooth® Low Energy 5.1

standard.

Figure 5: DA14531 Section Schematic

The DA14531 SoC power management subsystem consists of:

● VHIGH: LDO/Battery input (buck configuration, default is 3.3 V from LDO)

○ A 2.2 μF decoupling capacitor (C1) is required close to the pin

● VLOW: 1.1 V typical output (buck configuration)

○ A 10 μF decoupling capacitor (C2) is required close to the pin

● The inductor needed for DC-DC operation is placed externally. A low DCR 2.2 µH inductor (L1) is

connected between LX and VLOW pins

C2

10uF

C1

2.2UF

L1

2.2uH

Z8

1.8pF

RF1

J5

NP_142-0761-861

1

234

Z4

NP

RF4

Z2

2.4pF

Z5

10pF

Y1

32.0000MHZ

1

3

24

Z1

1.6nH

Z3

NP

RF3

ANT1

antenna_zor_left

Y2

NP_32.768KHZ

V_HIGH

DA14531

24-pin FCGQFN

U1

DA14531-QFN24

XTAL32Mm

4

RFIOm

18

RFIOp

1

GND_DCDC

21

XTAL32Mp

3

P0_8

17

P0_1

11

P0_0/RST

10

P0_2/SWCLK

12

P0_3/XTAL32kp

13

P0_11

8

GND

20

GNDRF2

2

P0_4/XTAL32km

14

P0_5

24

P0_10/SWDIO

9

P0_7

15

P0_6

22

Lx

6

VBAT_LOW

5

VSS

23

VBAT_HIGH

7

GNDRF1

19

P0_9

16

V_LOW

RF2

P0_1

P0_0

P0_8

P0_7

P0_6

P0_5

P0_2

P0_11

P0_10

P0_9

P0_3

P0_4

R5 36

R4 36

R1 36

R2 36

R6 36

R3 36

R12 36

R11 36

R8 36

R7 36

R10 36

R9 36

TP1

VLOW

TP2

GND

Z6

1.8pF

Z7

3.3nH

Page 10

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

10 of 32

© 2020 Dialog Semiconductor

5.3 DA14531 GPIO Assignment

Most of the available signals are utilized or extracted on the breakout connectors.

Table 1 shows the pin assignment on the development kit peripheral function and the related pin

name on the FCGQFN24 package of the DA14531.

Table 1: DA14531 USB Development Kit Pin Assignment

UART

2-wires

JTAG

SPI Flash

Full

UART

XTAL

32KHz

Single

UART

Other

GPIOs

P0_0

UTX

(Note 1)

SWDIO

(Note 1)

MOSI

UTX

(Note 1)

UTX/URX

(Note 1)

SW1/

RESET

P0_1

URX

(Note 1)

/CS

URX

(Note 1)

P0_2

SWCLK

P0_3

MISO

UCTS

(Note 1)

XTAL

(Note 1)

UTX/URX

(Note 1)

P0_4

SCK

URTS

(Note 1)

XTAL

(Note 1)

P0_5

SWDIO

(Note 1)

UTX/URX

P0_6

P0_7

P0_8

P0_9

LED

P0_10

SWDIO

P0_11

BUTTON

Note 1 This option is available for the pin and can be implemented on the board but requires software,

hardware, and/or OTP modifications.

Page 11

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

11 of 32

© 2020 Dialog Semiconductor

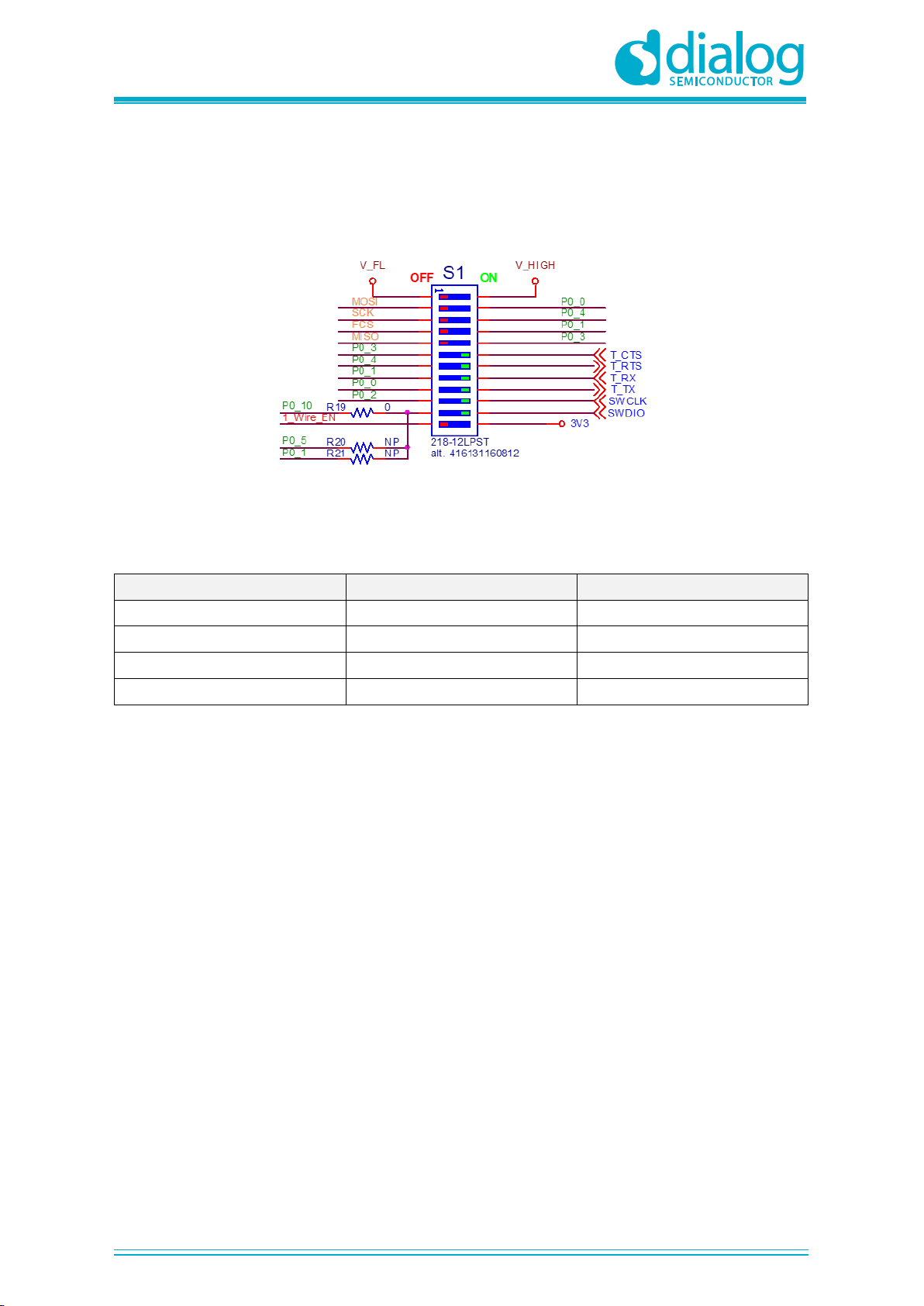

5.4 Default Configuration

Since GPIOs P0_0 to P0_6 support multiple functions, the default system is limited to a subset of the

possible options. Figure 6 shows the default DIP switch configuration.

Figure 6: Default DIP Switch Configuration

This allows the system to boot from external flash or 1-wire UART and communicate through JTAG

for debugging.

Table 2: Default Configuration DIP Settings

DIP number

DA14531 GPIO

Related Function

2

P0_0

QSPI MOSI

4

P0_1

QSPI CS

10

P0_2

SWD CLK

5

P0_3

QSPI MISO

3

P0_4

QSPI CLK

12

P0_5 (enable)

1-wire UART

11

P0_10

SWD DIO

Page 12

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

12 of 32

© 2020 Dialog Semiconductor

5.5 1-wire Bootable UART

Since most UART communication is typically half-duplex, it is possible to use a single pin for both the

Rx and the Tx channel. DA14531 has dedicated hardware that supports this function and two related

boot steps predefined. An analog multiplexer shown in Figure 7 (controlled by position #12 on the

DIP switch) connects the UART signals to P0_5 (which is the first option on boot sequence for 1-wire

UART).

The external Tx is connected to the external Rx through a 1 K series resistor. This means that any

data transmitted from the host PC will be repeated (looped-back) to the Rx channel. Dialog’s

SmartSnippets Toolbox will automatically filter out the looped data. Non-Dialog tools should take

precautions for this.

The host serial port settings required are:

● Baud rate 115.2 kbps

● 8 bits

● No parity

● 1 stop bit

Figure 7: Single Pin UART Multiplexer

C9

100nF

P0_5

U5

FSA2259UMX

5

1B0

2

1B1

4

S1

3

1A

8

S2

7

2B0

9

2A

10

2B1

1

VCC

6

GND

R14

1.00k

T_TX

T_RX

R49

100.0K

1_Wire_EN

3V3

Page 13

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

13 of 32

© 2020 Dialog Semiconductor

5.6 Optional 2-/4-Wire UART

It is possible to use a 2-wire of 4-wire UART for booting or other activities, but it is not possible to

boot from the SPI flash in this configuration. To enable the UART and also disable SPI, it is required

to modify the DIP switch as shown in Figure 8.

Figure 8: DIP Switch Configuration for UART

The flow control signals (RTS and CTS) are not needed for booting.

Table 3: UART Configuration DIP Settings

DIP number

DA14531 GPIO

Related Function

9

P0_0

UART Tx

8

P0_1

UART Rx

6

P0_3

UART CTS

7

P0_4

UART RTS

The host serial port settings required are:

● Baud rate 115.2 kbps

● 8 bits

● No parity

● 1 stop bit

For more details check application note AN-B-052 ([2]) and AN-B-072 ([3]).

Page 14

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

14 of 32

© 2020 Dialog Semiconductor

5.7 Crystals

The DA14531 SoC has two Digitally Controlled Crystal Oscillators, one at 32 MHz (XTAL32M) and

the other at 32.768 kHz (XTAL32K). XTAL32K has no trimming capabilities and is used as the clock

for low power sleep modes, while XTAL32M can be trimmed.

XTAL32K is by default left unpopulated, because it `cannot be used together with an SPI flash

connected to the same GPIOs. The internal RCX low power oscillator is capable to operate with

reasonable accuracy in most practical cases. XTAL32K may be required for applications that need to

have higher accuracy in low power clock timekeeping or as the source for a Real Time Clock. In that

case the crystal can be populated but the on-board flash will not be usable as a boot device. The

firmware in that case can reside on the OTP memory. Using external flash at different pins as boot

device is also possible with the use of a suitable bootloader in OTP memory.

The crystals selected for the basic development kit are specified in Table 4 and Table 5.

Table 4: Y1 (32 MHz Crystal) Characteristics

Reference Designator

Value

Part Number

XRCGB32M000F1H00R0

Frequency

32 MHz

Accuracy

±10 ppm

Load Capacitance (CL)

6 pF

Equivalent Series Resistance (ESR)

60 Ω

Drive Level (PD)

150 μW

Table 5: Y2 (32 kHz Crystal) Characteristics

Reference Designator

Value

Part Number

SC20S-7PF20PPM

Frequency

32.768 KHz

Accuracy

±20 ppm

Load Capacitance (CL)

7 pF

Shunt Capacitance (C0)

1.3 pF

Motional Resistance (ESR)

70 kΩ max

Drive Level (PD)

0.1 μW max

Page 15

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

15 of 32

© 2020 Dialog Semiconductor

5.8 Antenna and RF Port

A printed ZOR-antenna (ANT1) is used by default as the radiating element for the DA14531 USB

development kit. For more details please refer to the application note AN-B-027 ([4]).

To perform conducted RF measurements, please proceed to:

● Remove Z5

● Assemble Z4, 10 pF

● Assemble J5, SMA 50 Ω board edge type SMT female connector (Cinch Connectivity solutions

Johnson 142-0761-861)

Figure 9: RF Section

RF measurements were performed to increase the efficiency of the antenna. The values of the RF

matching components are shown in Table 6.

Table 6: RF Components Names and Values

Component Name

Component Value

Manufacturer Part Number

Z1

1.6 nH

LQP15MN1N5W02D

Z2

2.4 pF

GJM1555C1H2R4BB01D

Z3 - Not populated

Page 16

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

16 of 32

© 2020 Dialog Semiconductor

5.9 SPI Data Flash Memory (U2)

The DA14531 USB development kit includes an external SPI Data Flash memory (Figure 10).

The selected flash for the DA14531 USB development kit is Macronix MX25R2035FZUIL0 (2 Mbit).

The DA14531 USB development kit can also support other types of external SPI flash in USON-8 2

mm × 3 mm, SOIC-8 150 mil, and SOIC-8 208 mil packages (Figure 11).

Figure 10: SPI Data Flash

Figure 11: SPI Flash Package Options

C3

1.0uF

V_FLV_FL

U2

MX25R2035FZUIL0

CS

1

VCC

8

SO/SIO12RST/SIO3

7

WP

3

SCLK

6

GND

4

SI/SIO0

5

PAD

9

U2X

NP

SI/SIO0

5

SCK

6

RST/Hold/SIO3

7

CS

1

WP/SIO2

3

VCC

8

GND

4

SO/SIO1

2

U2Y

NP

SI/SIO0

5

SCK

6

RST/SIO3

7

CS

1

WP/SIO2

3

VCC

8

GND

4

SO/SIO1

2

R30

10.0k

SCK

MISO

FCS

MOSI

V_FL

Page 17

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

17 of 32

© 2020 Dialog Semiconductor

5.10 Reset Circuit

The DA14531 can allocate the power-on-reset input to any GPIO using high or low polarity. This

configuration is done by the application software after the boot sequence has finished. However, the

only option for a hardware reset before the boot sequence has started is fixed to P0_0 with a high

polarity. Since hardware reset is important for development, SW1 is by default connected to P0_0

with high polarity (Figure 12).

There is also an option to connect the button SW1 to GPIO P0_8 through resistor R17.

The JTAG debugger can also drive a hardware reset (T_RST through resistor R48).

Figure 12: Reset Circuit

Figure 13: RESET Push Button (SW1)

R17 NP

P0_8

P0_0

V_HIGH

R37 4.7k

T_RST

R48 4.7k

SW1

EVP-AKE31A

1

2

M1

M2

M3

Page 18

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

18 of 32

© 2020 Dialog Semiconductor

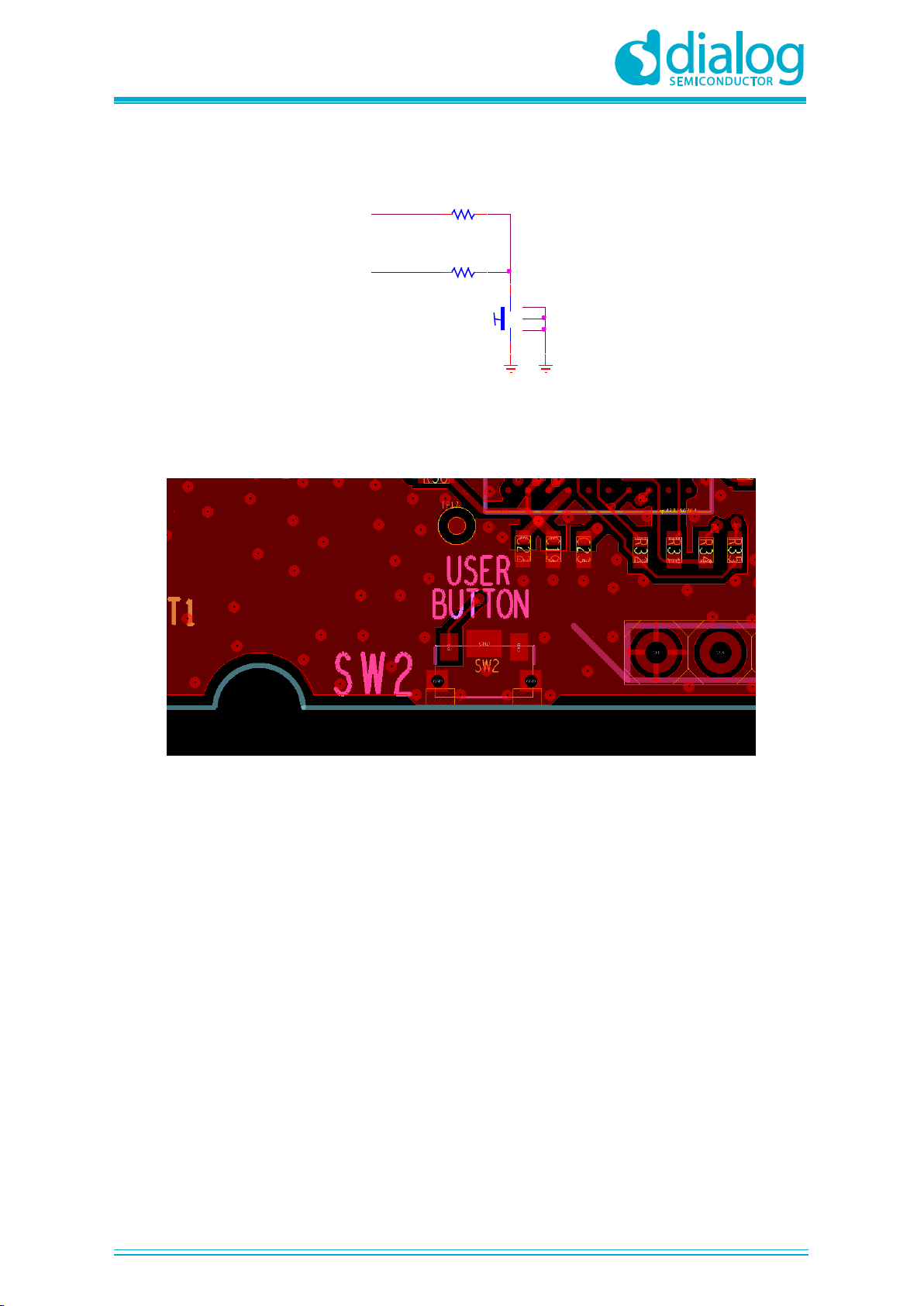

5.11 General Purpose Push Button

Figure 14: General Purpose Push Button

The general purpose push button SW2 is connected by default to GPIO P0_11 and can be

connected to P0_10 by soldering resistor R33 (Figure 14).

Figure 15: General Purpose Push Button SW2

P0_11

R16 270

SW2

EVP-AKE31A

1

2

M1M2M3

R33 NP

PB

P0_10

Page 19

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

19 of 32

© 2020 Dialog Semiconductor

5.12 Debugging Port DIP Switch

Figure 16: DIP Switch Configuration

DIP-switch S1 serves a triple purpose (Table 7):

● Allows selection between SPI-Flash and UART as booting options (sharing the same GPIOs)

● Place all switches in the “OFF” position so that the sleep current can be measured accurately

● Place some switches in “OFF” position so that the signals can be used for other purposes. For

example, if we need more than two analog inputs, these are restricted to use P0_1 or P0_2,

assuming the other two options (P0_3 and P0_4) are already utilized.

Table 7: DIP Switch Configuration

DIP number

DA14531

Related Function

Default State

1

VBAT_HIGH (VHIGH)

Ext. FLASH power

ON

2

P0_0

QSPI MOSI

ON

3

P0_4

QSPI CLK

ON

4

P0_1

QSPI CS

ON

5

P0_3

QSPI MISO

ON

6

P0_3

UART CTS

OFF

7

P0_4

UART RTS

OFF

8

P0_1

UART Rx

OFF

9

P0_0

UART Tx

OFF

10

P0_2

SWD CLK

ON

11

P0_10

SWD DIO

ON

12

P0_5 (enable)

1-wire UART

ON

P0_10

R19 0

R20 NP

P0_5

P0_1

R21 NP

3V3

1_Wire_EN

T_TX

T_RX

T_CTS

T_RTS

P0_3

P0_4

P0_0

P0_1

FCS P0_1

MISO P0_3

P0_4SCK

P0_2

SWDIO

SWCLK

S1

218-12LPST

OFF ON

V_HIGHV_FL

alt. 416131160812

P0_0MOSI

Page 20

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

20 of 32

© 2020 Dialog Semiconductor

5.13 MikroBUS™ Module

The DA14531 USB development kit supports MikroBUS™ modules. Two 8-pin 2.54 mm sockets

shall be installed on J3 and J4. A possible female socket type is Sullins Connector Solutions

PPTC081LFBN-RC.

Figure 18 shows the notch on the silkscreen which indicates the correct placement for the module.

For more information, please check MikroBus™ standard specifications.

The pin assignment is printed at the bottom side of the DA14531 USB kit (Figure 19).

A MikroBUS™ module requires a power supply of 5 V, 3.3 V or both, depending on the module. The

voltage for the 5.0 V MikroBUS™ pins is taken from the output of the OVP circuit. The 3.3 V pin is

driven from the output of the LDO, which also feeds the debugger section and VHIGH pin on DA14531.

The current measurement point (J2, see section 5.18) allows the total current flowing from the LDO

to DA14531 and any MikroBUS™ peripherals to be measured.

Figure 17: MikroBus™ Pin Assignment

Figure 18: Guides for Proper MikroBus™ Click Board Insertion

PWM

INT

RX

TX

SCL

SDA

+5V

GND

AN

RST

CS

SCK

MISO

MOSI

+3.3V

GND

J3

NP

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

J4

NP

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

VBUSV_HIGH

P0_11

P0_9

P0_5

P0_6

P0_2

P0_8P0_0

P0_3

P0_4

P0_1

P0_7

Page 21

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

21 of 32

© 2020 Dialog Semiconductor

Figure 19: MikroBus™ Pin Assignment (Bottom View)

5.14 User Controlled LED

A general-purpose LED (D7, orange) is assigned to GPIO P0_9 (Figure 20). It can be disabled by

removing resistor R15.

Figure 20: General Purpose LED

5.15 GND Test Point

The ground clip of an oscilloscope can be attached to the test point TP28.

Figure 21: GND Support Point

VLED

D7

Led_Orange

2 1

R15 270

TP13

VLED

P0_9

Page 22

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

22 of 32

© 2020 Dialog Semiconductor

5.16 Over Voltage Protection Circuit (OVP)

The DA14531 USB development kit can be used as a portable standalone device. The power supply

can be a power bank or a mobile charger. Figure 22 shows the schematic of the OVP circuit.

Overvoltage can be caused not only by the connection of an unsuitable charger, but also from

transient voltage surge caused by insertion of a long-length cable. For a normal operation of the

DA14531 USB development kit, the input voltage should be between 4.75 V and 5.25 V, as defined

in the USB standard, electrical specification.

The OVP circuit can protect the device from transient or permanent overvoltage up to 20 V.

When activated, it will disconnect VBUS from VBUS_IN until the condition that caused the activation

is corrected. Note that it will not protect the DA14531 USB development kit from an erroneous

insertion of power with inverted polarity.

Figure 22: Over Voltage Protection Circuit

TP25

5V

C7

100nF

VBUS_IN

C6

2.2UF

R23

4.7k

DIODES Inc.

Q2

DMP3099L-7

3

1

2

D2

BZX84C5V6-7-F

1

3

R27

2.2k

R26

10.0k

Q1

BC807-25_215

3

1

2

VBUS

Page 23

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

23 of 32

© 2020 Dialog Semiconductor

5.17 Debug Interface (U4)

Two debugging options (JTAG/UART) are available on the DA14531 SoC and both are implemented

with the SAM3U2CA microprocessor (U4) (Figure 23), running the SEGGER J-Link-OB firmware.

The functions served by U4 are:

● SWD debugger interface (SEGGER J-Link-OB)

○ SWCLK connected to DA14531 P0_2

○ SWDIO connected to DA14531 P0_10

● UART connection (for 1-pin, 2-pin, or 4-pin)

● A hardware reset on DA14531 can be asserted through the T_RESETn signal

The UART port supports hardware flow control (RTS/CTS). It is detected automatically by the J-LinkOB firmware, regardless of the setting on the host machine terminal. The behavior of the UART

interface depends on the implementation in the J-Link-OB firmware and is subject to changes by

SEGGER Microcontroller © with updates to the firmware. For troubleshooting the possible issues

with the JTAG Debugger, see the DA14531 datasheet ([1]). For troubleshooting the possible issues

with the serial port, see AN-B-072 ([3]).

The JTAG operating status is indicated via LED D8 (blinking when there is activity).

The SAM3U2CA (U4) chip is supplied with 3.3 V from U3. A 12 MHz crystal (Y3) is required for the

chip operation. U6 inverts T_RESETn to generate an active high signal (T_RST).

Figure 23: Debugging Processor - UART and JTAG Interface (U4)

T_RTS

T_TX

T_RX

T_CTS

C28

10uF

XOUT

PA15

PA18

PA22

DFSDM

DFSDP

S_RXD

S_TXD

PA29

TDIout

TDIin

VBG

PA4

NRSTB

TRSTout

TRSTin

PA17

TRSTout

TRSTin

TDIout

TDIin

Needed by Segger software

TDI

FWUP

ERASE

XIN

R35 330

C26

100nF

C32 10nF

R40 36

R25 330

R44

10.0k

R43

10.0k

R42 0

TFBGA-100

ATSAM3U2CA-CU

U4

XIN

A2

XOUT

A3

XIN32

A10

NRST

B7

XOUT32

B10

TMS/SWDIO

C7

NRSTB

C8

JTAGSEL

C9

TST

D7

FWUP

D8

TCK/SWCLK

A7

TDO/TRACESWO

B8

TDI

B9

ERASE

D6

VBG

A1

DFSDP

C1

DHSDP

C2

VDDBU

C10

DFSDM

D1

DHSDM

D2

VDDPLL

D3

VDDCORE1

D4

VDDIO3

E6

VDDCORE2

E7

VDDIO1F3VDDIO2

F5

VDDCORE4F9VDDCORE5G5VDDCORE6

H1

ADVREF

J3

VDDANA

K2

AD12BVREF

K4

PB17

A4

PB21

A5

PB23

A6

VDDIN

A8

VDDOUT

A9

VDDCORE3

B1

GNDUTM I

B2

VDDUTM I

B3

PB10

B4

PB18

B5

PB24

B6

GNDPLL

C3

PB14

C4

PB19

C5

PB22

C6

PB20

D5

PA11/PGMD3/URXD

D9

PA12/PGMD4/UTXD

D10

PA29

E1

GND2

E2

PA28

E3

PB9

E4

GNDBU

E5

PA10/PGMD2

E8

PA9/PGMD1

E9

PA8/PGMD0

E10

PB1

F1

PB12

F2

PA31

F4

GND1

F6

PB16

F7

PA6/PGMM2

F8

PA7/PGMM3

F10

PB11

G1

PB2

G2

PB0

G3

PB13

G4

GND3

G6

PB15

G7

PA3/PGMNVALID

G8

PA5/PGMM1

G9

PA4/PGMM0

G10

PB5

H2

PA27

H3

PA22/PGMD14

H4

PA13/PGMD5

H5

PA15/PGMD7

H6

PA18/PGMD10

H7

PA24

H8

PA1/PGMRDY

H9

PA2/PGMNOE

H10

PB6

J1

PB8

J2

PA30

J4

PB3

J5

PA16/PGMD8

J6

PA19/PGMD11

J7

PA21/PGMD13

J8

PA26

J9

PA0/PGMNCMD

J10

PB7

K1

GNDANA

K3

PB4

K5

PA14/PGMD6

K6

PA17/PGMD9

K7

PA20/PGMD12

K8

PA23/PGMD15

K9

PA25

K10

C29

10pF

R28 330

R24 330

C20

100nFC23

100nF

R34 330

R29 330

R46

100.0k

C22

100nF

C30 18pF

C24

100nF

C31 18pF

C19

100nF

R39

6.8k

R31 150

R22 150

C25

100nF

R38

330

C21

100nF

R45

10.0k

R32 150

R41 36

VDD_COREVDD_CORE

Y3

12.0000MHZ

SWDIO

SWCLK

J1

+5V

1

D-

2

D+

3

GND

4

VBUS_IN

USBDM

D1

CPDQC24VEU-H F

21

USBDP

S_nRTS

S_nCTS

U6

NC7SZ04P5X

NC

1

I

2

GND3O

4

VCC

5

T_RESETn

T_RST

C10 100nF

TP4

3V3

3V3

TP3

VLDO

C8

NP

TP6

DBLED

C4

1.0uF

3V3

U3

NCP114ASN330T1G

IN

1

GND

2

EN3NC

4

OUT

5

LP1

500mA_470 OHM

LP2

500mA_470 OHM

VLDO

C5

1.0uF

VBUS

3.3V LDO

R36

100.0k

TP18

LDO_EN

TP35

TRTS

TP33

TCTS

TP36

TTX

TP34

TRX

TP21

SWDIO

TP22

SWCLK

C27

10uF

TP11

ERASE

TP8

TDI

TP9

TCK_SWCLK

TCK/SWCLK

TP30

SWO/TDO

SWO/TDO

TP10

TMS_SWDIO

TMS/SWDIO

TP12

NRST

3V3

3V3

3V3

3V3

3V3

D8

Led_Green

21

TP5

VDD_CORE

D3

CPDQC5V0CSP-H F

2

1

D4

CPDQC5V0CSP-H F

2

1

TP7

GND

Page 24

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

24 of 32

© 2020 Dialog Semiconductor

5.18 Power Measurements

If the power consumption of the DA14531 USB development kit needs to be measured accurately, a

3-pin header (for example, a Molex 0878980306) must be placed on J2 and resistor R50 must be

removed.

For accurate sleep current measurements, it may be needed to move all segments of the DIP switch

S1 to the “OFF” position in order to eliminate the small leakages through the debug GPIOs.

Figure 24: Power Measurement Header

Figure 25: Current Measurement Header (J2)

An ampere meter can be connected to pin 1 and pin 2 of header J2 for measuring the current

supplied by the onboard LDO (U3). Note that the maximum current must not be allowed to raise

above ~150 mA which is a total current consumption for DA14531 and all the peripherals connected

to VHIGH, because the same LDO also supplies U4 which is rather power-hungry (~115 mA).

Similarly, the ampere meter can be connected to pin 2 and pin 3 of header J2 to measure the current

supplied by BT1, if this option is installed.

R50 0

R51 NP

J2

NP_hdr_254_1x03_SRSW

BYPASS

MODE

V_LOW

VLDO

V_HIGH

R18 NP

D6

CPDQC24VEU-HF

2

1

+

BT1

NP

Page 25

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

25 of 32

© 2020 Dialog Semiconductor

5.19 Operation from a Wall Adapter or Power Pack

It is possible to power the DA14531 USB development kit from any source with a type-A female

powered connector. It may be necessary to remove resistor R48 (Figure 27) in order to stop any

resets issued by the JTAG debugger trying to find a target.

Figure 26: Operation with a Battery Pack

Figure 27: Resistor R48

Page 26

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

26 of 32

© 2020 Dialog Semiconductor

5.20 Operation from a Coin Cell Battery

It is possible to power the BLE system and maybe a few low-power peripherals on the DA14531 USB

development kit with an external battery. A CR2032 battery holder (type BLP2032SM-GTR from

MPD or similar) can be soldered at the bottom of the PCB for this purpose.

Users must also perform the following steps:

● Move segments 6 to 12 of the DIP switch S1 to the “OFF” position

● If the application does need the SPI flash, move also segments 1 to 5 of the DIP switch S1 to the

“OFF” position

● Remove R50 and place R51, or move the jumper from position 1-2 to position 2-3, if pin header

J2 is installed (Figure 28)

Figure 28: Resistors R50 and R51

Page 27

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

27 of 32

© 2020 Dialog Semiconductor

Appendix A Schematics

Figure 29: DA14531 SoC and Peripherals

P0_11

P0_10

C2

10uF

C1

2.2UF

R20

NP

P0_5

R21

NP

P0_1

R19

0

PWM

INT

RX

TX

SCL

SDA

+5V

GND

AN

RSTCSSCK

MISO

MOSI

+3.3V

GND

J3

NP

112233445566778

8

J4

NP

112233445566778

8

P0_2

V_HIGH

VBUS

MikroBUS SOCKET

(NOT POPULATED)

3V3

P0_11

P0_9

P0_5

P0_6

1_Wire_EN

T_TXT_RXT_CTST_RTS

P0_3

P0_4

P0_0

P0_1

C3

1.0uF

C9

100nF

Z8

1.8pF

FCS

P0_1

MISO

P0_3

DEVELOPMENT OPTIONS

(DEFAULT: FLASH,JTAG,1-wire UART)

SWCLK

P0_2

P0_4

SCK

P0_10

P0_8

SWDIO

RF1

J5

NP_142-0761-861

1

234

RF4

Z5

10pF

Z4

NP

V_FL

V_FL

Z2

2.4pF

RF3

Y1

32.0000MHZ

1 3

2

4

V_HIGH

Z1

1.6nH

Z3

NP

ANT1

antenna_zor_left

Y2

NP_32.768KHZ

V_LOW

DA14531

24-pin FCGQFN

U1

DA14531-QFN24

XTAL32Mm

4

RFIOm

18

RFIOp

1

GND_DCDC

21

XTAL32Mp

3

P0_8

17

P0_111P0_0/RST10P0_2/SWCLK

12

P0_3/XTAL32kp

13

P0_11

8

GND

20

GNDRF2

2

P0_4/XTAL32km

14

P0_5

24

P0_10/SWDIO

9

P0_715P0_6

22

Lx

6

VBAT_LOW

5

VSS

23

VBAT_HIGH

7

GNDRF1

19

P0_9

16

U2

MX25R2035FZU IL0

CS

1

VCC

8

SO/SIO1

2

RST/SIO3

7

WP

3

SCLK

6

GND

4

SI/SIO0

5

PAD

9

U2Y

NP

SI/SIO0

5

SCK

6

RST/SIO3

7

CS1WP/SIO2

3

VCC

8

GND

4

SO/SIO1

2

U2X

NP

SI/SIO0

5

SCK

6

RST/Hold/SIO3

7

CS1WP/SIO2

3

VCC

8

GND

4

SO/SIO1

2

FCS

MOSI

R30

10.0k

SPI FLASH

SCK

MISO

P0_5

1-WIRE UART

S1

218-12LPST

V_FL

OFF

ON

V_HIGH

RF2

V_FL

P0_1

P0_0

L1

2.2uH

P0_8

P0_7

P0_6

P0_5

P0_2

alt. 416131160812

P0_11

P0_10

P0_9

R17

NP

P0_8

P0_0

R37

4.7k

V_HIGH

R5

36

P0_3

P0_4

R1

36

R4

36

R336R2

36

R11

36

R636R7

36

R12

36

R936R836R10

36

R50

0

R51

NP

TP1

VLOW

J2

NP_hdr_254_1x03_SRSW

R48

4.7k

T_RST

MOSI

P0_0

TP2

GND

L?

LB

L?

L

L?

LS

R16

270

U5

FSA2259UMX

5

1B021B1

4S13

1A

8

S2

7

2B0

9

2A

10

2B1

1

VCC

6

GND

R14

1.00k

T_TXT_RX

1_Wire_EN

P0_4

P0_3

P0_0

R49

100.0K

3V3

P0_7

P0_1

Z7

3.3nH

Z6

1.8pF

R15

270

VLED

P0_9

D7

Led_Orange

2

1

TP13

VLED

BYPASS

MODE

V_HIGH

POWER OPTIONS

V_LOW

VLDO

R18

NP

USER LED

D6

CPDQC24VEU-HF

21

+

BT1

NP

SW1

EVP-AKE31A

12

M1M2M3

POR/RESET BUTTON

PB

SW2

EVP-AKE31A

12

M1M2M3

R33

NP

P0_10

USER BUTTON

Page 28

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

28 of 32

© 2020 Dialog Semiconductor

Figure 30: Debug Interface (UART/JTAG)

T_RTST_TXT_RXT_CTS

TP25

5V

C28

10uF

XOUT

PA22

PA15

PA18

DFSDP

DFSDM

S_TXD

S_RXD

TDIout

TDIin

PA29

VBG

NRSTB

PA4

TRSTin

TRSTout

TRSTin

PA17

TDIout

TDIin

TRSTout

Needed by Segger software

FWUP

TDI

ERASE

XIN

C26

100nF

R35

330

R40

36

C32

10nF

R25

330

R44

10.0k

R42

0

R43

10.0k

TFBGA-100

ATSAM3U2CA-CU

U4

XINA2XOUT

A3

XIN32

A10

NRST

B7

XOUT32

B10

TMS/SW DIO

C7

NRSTB

C8

JTAGSEL

C9

TST

D7

FWUP

D8

TCK/SW CLKA7TDO/T RACESWOB8TDI

B9

ERASE

D6

VBGA1DFSDPC1DHSDP

C2

VDDBU

C10

DFSDMD1DHSDM

D2

VDDPLL

D3

VDDCOR E1

D4

VDDIO3

E6

VDDCOR E2

E7

VDDIO1

F3

VDDIO2

F5

VDDCOR E4

F9

VDDCOR E5

G5

VDDCOR E6

H1

ADVREF

J3

VDDANA

K2

AD12BVREF

K4

PB17A4PB21A5PB23

A6

VDDIN

A8

VDDOUT

A9

VDDCOR E3

B1

GNDUTMI

B2

VDDUTMI

B3

PB10

B4

PB18B5PB24

B6

GNDPLL

C3

PB14C4PB19C5PB22C6PB20

D5

PA11/PGMD3/ URXD

D9

PA12/PGMD4/ UTXD

D10

PA29

E1

GND2

E2

PA28

E3

PB9

E4

GNDBU

E5

PA10/PGMD2

E8

PA9/PGMD1E9PA8/PGMD0

E10

PB1

F1

PB12

F2

PA31

F4

GND1

F6

PB16

F7

PA6/PGMM2F8PA7/PGMM3

F10

PB11

G1

PB2G2PB0

G3

PB13

G4

GND3

G6

PB15

G7

PA3/PGMNVALI D

G8

PA5/PGMM1G9PA4/PGMM0

G10

PB5

H2

PA27

H3

PA22/PGMD14

H4

PA13/PGMD5H5PA15/PGMD7

H6

PA18/PGMD10

H7

PA24

H8

PA1/PGMRD YH9PA2/PGMNOE

H10

PB6J1PB8

J2

PA30

J4

PB3

J5

PA16/PGMD8

J6

PA19/PGMD11J7PA21/PGMD13

J8

PA26

J9

PA0/PGMNC MD

J10

PB7

K1

GNDANA

K3

PB4

K5

PA14/PGMD6K6PA17/PGMD9

K7

PA20/PGMD12K8PA23/PGMD15

K9

PA25

K10

R24

330

C29

10pF

C20

100nF

R28

330

C23

100nF

R34

330

C22

100nF

R29

330

C30

18pF

R46

100.0k

C31

18pF

C24

100nF

C19

100nF

R39

6.8k

R22

150

R31

150

C25

100nF

R38

330

C21

100nF

R45

10.0k

VDD_CORE

R32

150

VDD_CORE

R41

36

Y3

12.0000MHZ

SWDIOSW CLK

VBUS_IN

J1

+5V

1D-2D+3

GND

4

D1

CPDQC24VEU -HF

2

1

USBDP

USBDM

S_nCTS

S_nRTS

U6

NC7SZ04P5X

NC1I2GND

3

O

4

VCC

5

C10

100nF

T_RST

3V3

TP4

3V3

TP3

VLDO

C8

NP

C7

100nF

VBUS_IN

DIODES Inc.

C6

2.2UF

Q2

DMP3099L-7

3

1

2

R23

4.7k

D2

BZX84C5V6-7-F

13

R27

2.2k

R26

10.0k

Q1

BC807-25_215312

OVP CIRCUIT

TP6

DBLED

C4

1.0uF

VBUS

3V3

U3

NCP114ASN330T1G

IN1GND2EN

3

NC

4

OUT

5

LP1

500mA_470 OHM

VBUS

LP2

500mA_470 OHM

VLDO

3.3V LDO

C5

1.0uF

TP18

LDO_EN

R36

100.0k

TP36

TTX

TP35

TRTS

TP34

TRX

TP33

TCTS

TP22

SWCLK

TP21

SWDIO

TP11

ERASE

C27

10uF

TCK/SW CLK

TP8

TDI

TP30

SWO/TDO

SWO/TD O

TP9

TCK_SWCLK

TP10

TMS_SWDIO

TMS/SW DIO

3V3

3V3

3V3

TP12

NRST

3V3

3V3

D8

Led_Green

2

1

TP5

VDD_COR E

D4

CPDQC5V0C SP-HF

2 1

D3

CPDQC5V0C SP-HF

2 1

TP7

GND

Page 29

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

29 of 32

© 2020 Dialog Semiconductor

Appendix B Components Placement on PCB

Figure 31: Components Placement, Top Side on the Left and Bottom Side on the Right

Page 30

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

30 of 32

© 2020 Dialog Semiconductor

Appendix C PCB Layer Chart

● Dimensions: 100 mm × 26.5 mm × 11 mm

● Number of layers: 4

● PCB thickness: 1.55 mm

● Material: FR-4

● Solder mask TOP/BOTTOM: Green

● Silkscreen TOP/BOTTOM: White

● Surface finish: Che Ni/Au

Figure 32: PCB Cross Section

Page 31

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

31 of 32

© 2020 Dialog Semiconductor

Revision History

Revision

Date

Description

1.1

09-Mar-2020

Updated Figure 8

1.0

22-Nov-2019

Initial version.

Page 32

UM-B-125

DA14531 USB Development Kit Hardware

User Manual

Revision 1.1

09-Mar-2020

CFR0012

32 of 32

© 2020 Dialog Semiconductor

Status Definitions

Status

Definition

DRAFT

The content of this document is under review and subject to formal approval, which may result in modifications or

additions.

APPROVED

or unmarked

The content of this document has been approved for publication.

Disclaimer

Unless otherwise agreed in writing, the Dialog Semiconductor products (and any associated software) referred to in this document are not

designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications

where failure or malfunction of a Dialog Semiconductor product (or associated software) can reasonably be expected to result in personal injury,

death or severe property or environmental damage. Dialog Semiconductor and its suppliers accept no liability for inclusion and/or use of Dialog

Semiconductor products (and any associated software) in such equipment or applications and therefore such inclusion and/or use is at the

customer’s own risk.

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or

warranties, express or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no

responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including, without limitation, the

specification and the design of the related semiconductor products, software and applications. Notwithstanding the foregoing, for any automotive

grade version of the device, Dialog Semiconductor reserves the right to change the information published in this document, including, without

limitation, the specification and the design of the related semiconductor products, software and applications, in accordance with its standard

automotive change notification process.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes

no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further

testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog

Semiconductor excludes all liability in this respect.

Nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications

referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document is subject to Dialog Semiconductor’s Standard

Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog, Dialog Semiconductor and the Dialog logo are trademarks of Dialog Semiconductor Plc or its subsidiaries. All other product or service

names and marks are the property of their respective owners.

© 2020 Dialog Semiconductor. All rights reserved.

RoHS Compliance

Dialog Semiconductor’s suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European

Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our

suppliers are available on request.

Contacting Dialog Semiconductor

United Kingdom (Headquarters)

Dialog Semiconductor (UK) LTD

Phone: +44 1793 757700

Germany

Dialog Semiconductor GmbH

Phone: +49 7021 805-0

The Netherlands

Dialog Semiconductor B.V.

Phone: +31 73 640 8822

North America

Dialog Semiconductor Inc.

Phone: +1 408 845 8500

Japan

Dialog Semiconductor K. K.

Phone: +81 3 5769 5100

Taiwan

Dialog Semiconductor Taiwan

Phone: +886 281 786 222

Hong Kong

Dialog Semiconductor Hong Kong

Phone: +852 2607 4271

Korea

Dialog Semiconductor Korea

Phone: +82 2 3469 8200

China (Shenzhen)

Dialog Semiconductor China

Phone: +86 755 2981 3669

China (Shanghai)

Dialog Semiconductor China

Phone: +86 21 5424 9058

Email:

enquiry@diasemi.com

Web site:

www.dialog-semiconductor.com

Loading...

Loading...