Page 1

E586-ICP

E586-IPE

System Board

User’s Manual

- D23540520 -

Page 2

v Copyright 1994, by DFI Inc.

All rights reserved.

No part of this document may be copied or reproduced

in any form or by any means without the prior written

consent of DFI, Inc.

DFI, Inc. makes no warranties with respect to this

documentation and disclaims any implied warranties of

merchantability, quality, or fitness for any particular

purpose. The information in this document is subject to

change without notice. DFI, Inc. reserves the right to

make revisions to this publication and to make changes

to any and/or all parts of its content, at any time,

without obligation to notify any person or entity of such

changes. Further, DFI, Inc. assumes no responsibility

for any errors that may appear in this document.

DFI is a registered trademark, and E586-ICP/E586-IPE

is a trademark of Diamond Flower, Inc. All other

product names mentioned are trademarks or registered

trademarks of their respective companies.

Page 3

v FCC Statement on Class B

This equipment has been tested and found to comply

with the limits for a Class B digital device, pursuant to

Part 15 of the FCC rules. These limits are designed to

provide reasonable protection against harmful interference when the equipment is operated in a residential

installation. This equipment generates, uses, and can

radiate radio frequency energy and if not installed and

used in accordance with the instruction manual may

cause harmful interference to radio communications.

However, there is no guarantee that interference will not

occur in a particular installation. If this equipment does

cause harmful interference to radio or television reception, which can be determined by turning the equipment

off and on, the user is encouraged to try to correct the

interference by one or more of the following measures:

• Reorient or relocate the receiving antenna.

• Increase the separation between the equipment and

the receiver.

• Connect the equipment into an outlet on a circuit

different from that to which the receiver is

connected.

• Consult the dealer or an experienced radio TV

technician for help.

Notice:

1. The changes or modification not expressly approved

by the party responsible for compliance could void

the user's authority to operate the equipment.

2. Shielded interface cables must be used in order to

comply with the emission limits.

Page 4

v Table of Contents v

Introduction .................................................................................

Features and Specifications .................................................

Package Checklist .................................................................

Installation Overview .................................................................

Preparing the Area ................................................................

Handling the System Board ..................................................

Tips in Handling the System Board ...............................

Hardware Installation .............................................................

Memory Installation .........................................................

Installing the Modules ..............................................

Board Configuration ........................................................

Jumper Settings .......................................................

Cache Configuration ................................................

Jumper Settings for Cache Memory .................

CPU Installation ..............................................................

Jumper Settings for CPU ........................................

Installing Upgrade CPUs ........................................

Installing the System Board ..................................................

Installing the PS/2 Mouse Port .............................................

Initial Setup Program .................................................................

Award BIOS CMOS Setup Utilities ......................................

Standard CMOS Setup ..................................................

BIOS Features Setup .....................................................

Chipset Features Setup .................................................

PCI Slot Configuration ...................................................

Load BIOS Defaults .......................................................

Load Setup Defaults ......................................................

Password Setting ...........................................................

IDE HDD Auto Detection ...............................................

Save & Exit Setup ..........................................................

Exit Without Saving ........................................................

1-1

1-2

1-2

2-1

2-1

2-2

2-2

2-2

2-2

2-6

2-7

2-9

2-13

2-15

2-16

2-17

2-18

2-22

2-24

3-1

3-2

3-2

3-5

3-7

3-8

3-9

3-9

3-10

3-11

3-11

3-12

Page 5

EISA Configuration Utility .......................................................

Troubleshooting Checklist ......................................................

4-1

5-1

Appendix A: Types of Modules ..............................................

Appendix B: System Error Report .........................................

Appendix C: Memory & I/O Maps ...........................................

Appendix D: EISA I/O Pin Assignments ................................

Appendix E: PCI I/O Pin Assignments ..................................

Appendix F: Connector Pin Assignments ............................

Appendix G: Award BIOS Hard Disk Table ...........................

A-1

B-1

C-1

D-1

E-1

F-1

G-1

Page 6

This page left intentionally blank.

Page 7

Read Me First

The E586-ICP/E586-IPE system board requires the installation

of the ECU (EISA Configuration Utility), found on the

provided EISA Configuration Utility diskette, for proper

operation of this system board.

The ECU configures the EISA devices and maintains system

parameters by storing them in the Extended CMOS Memory, so

the BIOS can initialize the system and expansion boards

inserted in the EISA slots once you power up your system.

The Extended CMOS Memory is equipped with an internal

battery that needs to be constantly charged. In a small number

of cases, the internal battery may have drained and the

information stored in the Extended CMOS Memory lost during

shipment. If this happens, you will get the message "EISA

CMOS Inoperational" when you power up your system.

Simply run the ECU software, bundled with the system board,

to reconfigure the system. Save the configuration and reboot

your system. Refer to the EISA Configuration Utility section on

page 4-1 for more detailed information.

Page 8

EISA/PCI System Board

v Introduction

The E586-ICP/E586-IPE system board offers several

advanced features integrated into the system board. It is

designed based on the new PCI (Peripheral Component

Interconnect) local bus and EISA (Extended Industry

Standard Architecture) standards.

The E586-ICP/E586-IPE supports 273-pin Zero Insertion Force socket for PentiumTM processors running at

60MHz or 66MHz bus speed. It also supports an optional Flash EPROM. Flash EPROM is a memory chip

for the storage of BIOS which can be erased in bulk or

modified using a software utility.

The E586-ICP/E586-IPE comes with an EISA Configuration Utility (ECU) that must be installed and run to

configure the board and the EISA expansion boards that

will be inserted in the EISA expansion slots.

The E586-ICP/E586-IPE system board is equipped with

four EISA and four PCI local bus slots. One EISA slot

and one PCI slot are shared, meaning you may use only

one or the other of these three slots. Therefore, in

accord with the PCI standard, seven slots are useable.

The E586-ICP/E586-IPE is also equipped with one

mini-DIN-6 connector for the PS/2 mouse and an optional IDE disk interface, only if installed with the

Symphony SL82C101P chip.

The E586-ICP/E586-IPE can be configured to twentytwo different sizes from 2MB to 128MB using 256Kx36,

512Kx36, 1Mx36, 2Mx36, 4Mx36 and 8Mx36 HSIM

modules.

1-1 u Introduction

Page 9

Features and Specifications

• Microprocessor

PentiumTM Processor

• Chipset

Intel 82430 PCI: system

Symphony SL82C101P: PCI IDE (optional)

• BIOS

Award system BIOS

• Cache Memory

256K or 512K Burst (sync) SRAM for 3-1-1-1

Level 2 cache access (E586-ICP)

256K or 512K Async SRAM for 3-2-2-2 Level 2

cache access (E586-IPE)

Supports direct map write-back or write-through

cache subsystem

Integrated cache tag RAM

• Memory Onboard

2MB to 128MB

E586-ICP/E586-IPE

• DRAM Type

256Kx36, 512Kx36, 1Mx36, 2Mx36, 4Mx36 and

8Mx36 SIMM

Supports single and/or double density SIMMs

Supports DRAM access time of 60ns or 70ns

Supports page mode

• ZIF Socket

273-pin ZIF socket (Intel Socket 4)

Introduction u 1-2

Page 10

EISA/PCI System Board

• Slots

Three 32-bit PCI slots

One shared - PCI/EISA slot

Three 32-bit EISA slots

• Connectors

A mini-DIN-6 connector for the PS/2 mouse

One IDE disk interface (optional; only if installed

with the Symphony SL82C101P chip)

• Tooling Holes

Baby AT form factor

• PCB

4 layers

Package Checklist

The E586-ICP/E586-IPE package contains the following

items:

• The E586-ICP/E586-IPE system board

• The E586-ICP/E586-IPE user’s manual

• One EISA Configuration Utility diskette

• One DB-25S hole cover holding the PS/2 mouse port

• One 40-pin IDE hard disk cable (optional)

If any of these items is missing or damaged, please

contact your dealer or sales representative for assistance.

1-3 u Introduction

Page 11

v Installation Overview

This chapter summarizes the steps in installing the

E586-ICP/E586-IPE system board into your system unit.

It also includes a description of the area in which you

must work and directions for memory installation.

Before installing the system board, obtain the memory

you plan to install.

Preparing the Area

Before unpacking the system board, make sure the

location you have selected is relatively free of dust and

static. Excessive exposure to dust, static electricity,

direct sunlight, excessive humidity, extreme cold and

water can damage the operational capabilities of your

system board. Avoid soft surfaces such as beds and

carpeted floors which can hinder air circulation. These

areas also attract static electricity which can damage

some circuits on your system board.

E586-ICP/E586-IPE

Be sure that the power source has a properly grounded,

three-pronged socket. It is essential that the power

connection be properly grounded for correct functioning

of your system board. For further protection, we recommend that you use a surge protection socket. This will

protect the system board from damage that may result

from a power surge on the line.

Move items that generate magnetic fields away from

your system board, since magnetic fields can also damage your system board. Once you have selected the ideal

location, unpack the E586-ICP/E586-IPE system board

carefully.

Installation Overview u 2-1

Page 12

EISA/PCI System Board

Handling the System Board

It is quite easy to inadvertently damage your system

board even before installing it to your system unit.

Static electrical discharge can damage computer components without causing any signs of physical damage. You

must take extra care in handling the system board to

ensure that no static build-up is present.

Tips in Handling the System Board

1) To prevent electrostatic build-up, leave the board in

its anti-static bag until you are ready to install it.

2) Wear an antistatic wriststrap.

3) Do all preparation work on a static-free surface with

components facing up.

4) Hold the system board by its edges only. Be careful

not to touch any of the components, contacts or

connections, especially gold contacts on the board.

5) Avoid touching the pins or contacts on all modules

and connectors. Hold modules and connectors by

their ends.

Hardware Installation

Memory Installation

The E586-ICP/E586-IPE system board can support 2MB

to 128MB of memory using HSIMMs. HSIMM is an

acronym for High Density Single In-line Memory Module.

2-2 u Installation Overview

Page 13

E586-ICP/E586-IPE

An HSIMM consists of several RAM chips soldered

onto a small circuit board. An HSIMM connects to the

system board via a 72-pin card-edge connector.

The HSIMM sockets are divided into two banks on the

system board. The E586-ICP/E586-IPE system board

uses 256Kx36, 512Kx36, 1Mx36, 2Mx36, 4Mx36 and

8Mx36 HSIM modules.

You will need 2 to 4 pieces of HSIM modules, depending on the amount of memory you intend to install.

Your system board can be configured with 2MB, 4MB,

6MB, 8MB, 10MB, 12MB, 16MB, 18MB, 20MB,

24MB, 32MB, 34MB, 36MB, 40MB, 48MB, 64MB,

66MB, 68MB, 72MB, 80MB, 96MB or 128MB of

onboard memory.

To install the HSIM modules, first populate Bank 1 and

then Bank 2. Failure to do so will cause the system

board to work improperly.

The following table summarizes the bank locations and

modules needed for the corresponding memory sizes.

Each bank consists of 2 HSIMM sockets.

Memory Size Bank 1 Bank 2

2MB 256Kx36 4MB 256Kx36 256Kx36

4MB 512Kx36 6MB 256Kx36 512Kx36

6MB 512Kx36 256Kx36

8MB 512Kx36 512Kx36

8MB 1Mx36 -

Installation Overview u 2-3

Page 14

EISA/PCI System Board

Memory Size Bank 1 Bank 2

10MB 256Kx36 1Mx36

10MB 1Mx36 256Kx36

12MB 512Kx36 1Mx36

12MB 1Mx36 512Kx36

16MB 1Mx36 1Mx36

16MB 2Mx36 18MB 256Kx36 2Mx36

18MB 2Mx36 256Kx36

20MB 512Kx36 2Mx36

20MB 2Mx36 512Kx36

24MB 1Mx36 2Mx36

24MB 2Mx36 1Mx36

32MB 2Mx36 2Mx36

32MB 4Mx36 34MB 256Kx36 4Mx36

34MB 4Mx36 256Kx36

36MB 512Kx36 4Mx36

36MB 4Mx36 512Kx36

40MB 1Mx36 4Mx36

40MB 4Mx36 1Mx36

48MB 2Mx36 4Mx36

48MB 4Mx36 2Mx36

64MB 4Mx36 4Mx36

64MB 8Mx36 66MB 256Kx36 8Mx36

66MB 8Mx36 256Kx36

68MB 512Kx36 8Mx36

68MB 8Mx36 512Kx36

72MB 1Mx36 8Mx36

72MB 8Mx36 1Mx36

80MB 2Mx36 8Mx36

80MB 8Mx36 2Mx36

96MB 4Mx36 8Mx36

96MB 8Mx36 4Mx36

128MB 8Mx36 8Mx36

2-4 u Installation Overview

Page 15

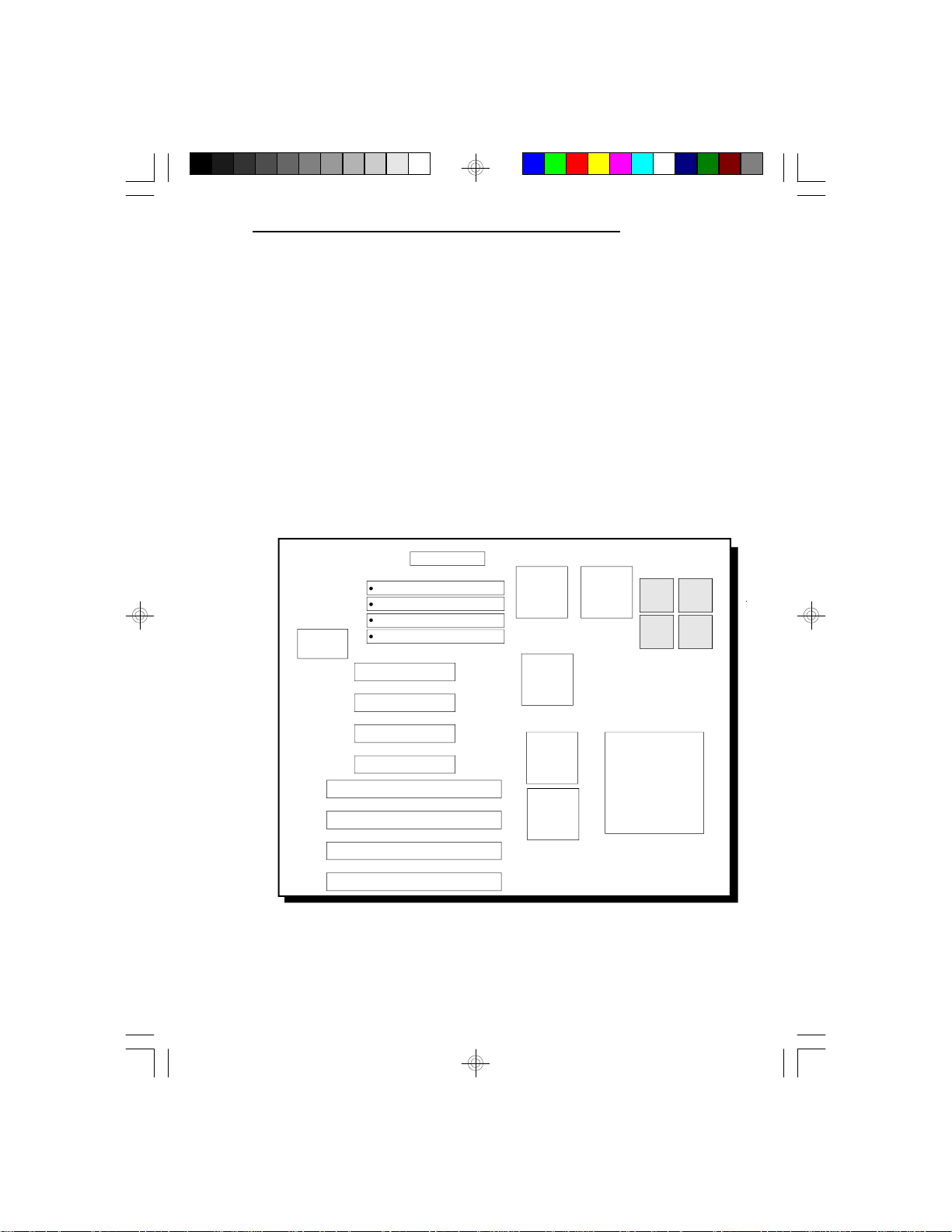

E586-ICP/E586-IPE

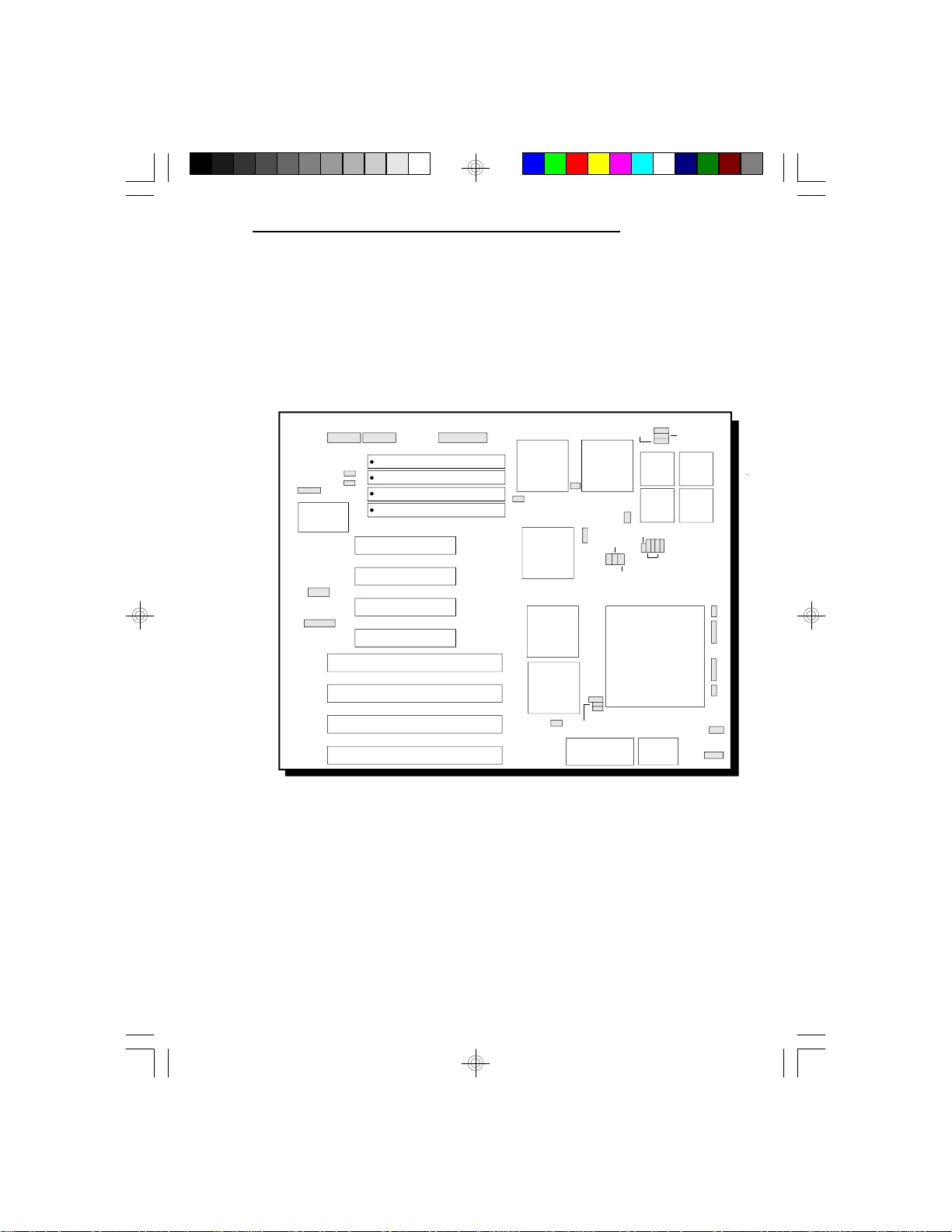

Bank 2

Bank 1

SL82C101P

82433LX 82433LX

Pin 1 of the HSIMM socket

82434

82375

82374

ZIF

Socket

Locations of the HSIMM Sockets on the System Board

Installation Overview u 2-5

Page 16

EISA/PCI System Board

Installing the Modules

HSIMMs simply snap into a socket on the system board.

Pin 1 of the HSIMM must correspond with Pin 1 of the

socket.

1. Position the HSIM module above the HSIMM

socket with the chips of the module facing the center

of the system board.

2. Seat the module at an angle into the bank. Make

sure it is completely seated. Tilt the module upright

until it locks in place in the socket.

2-6 u Installation Overview

Page 17

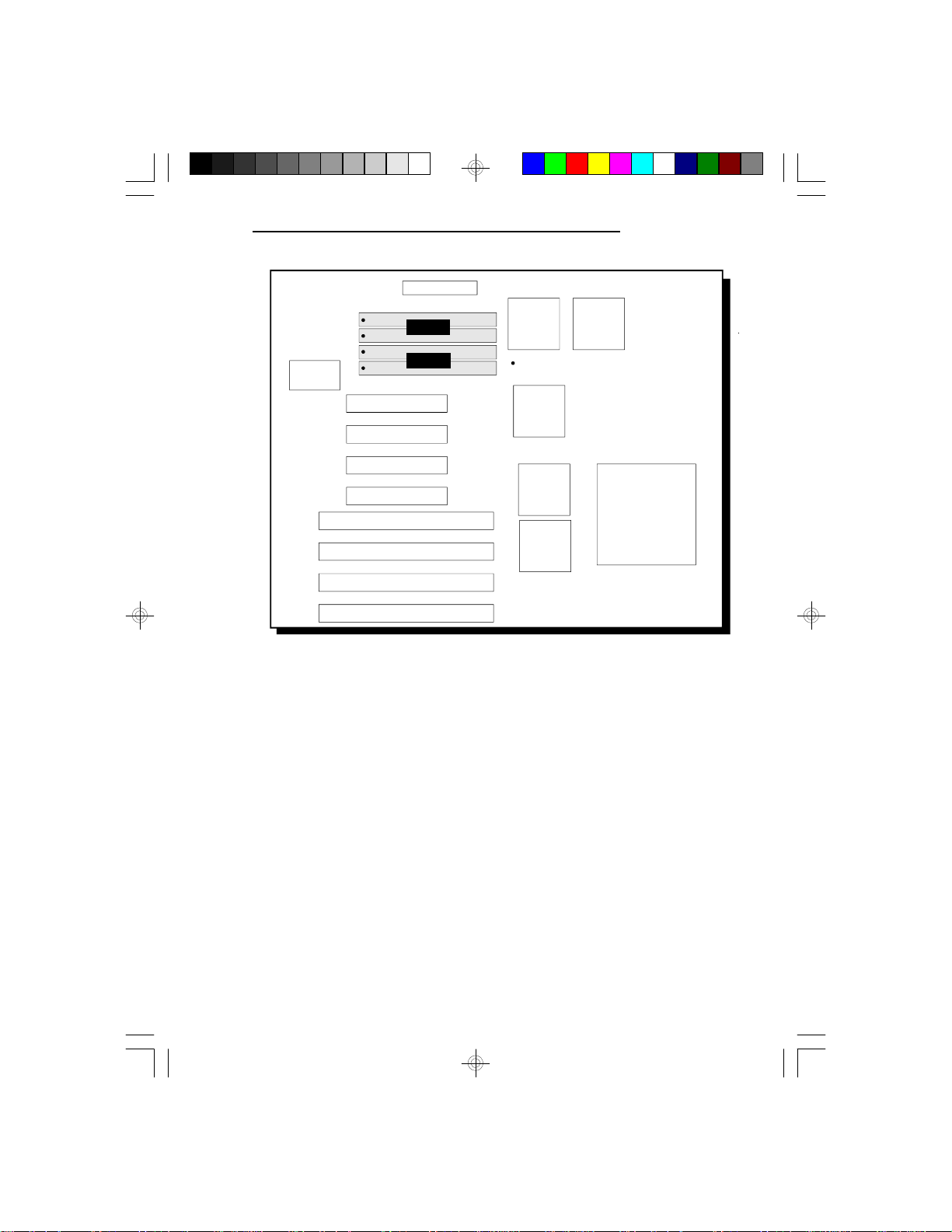

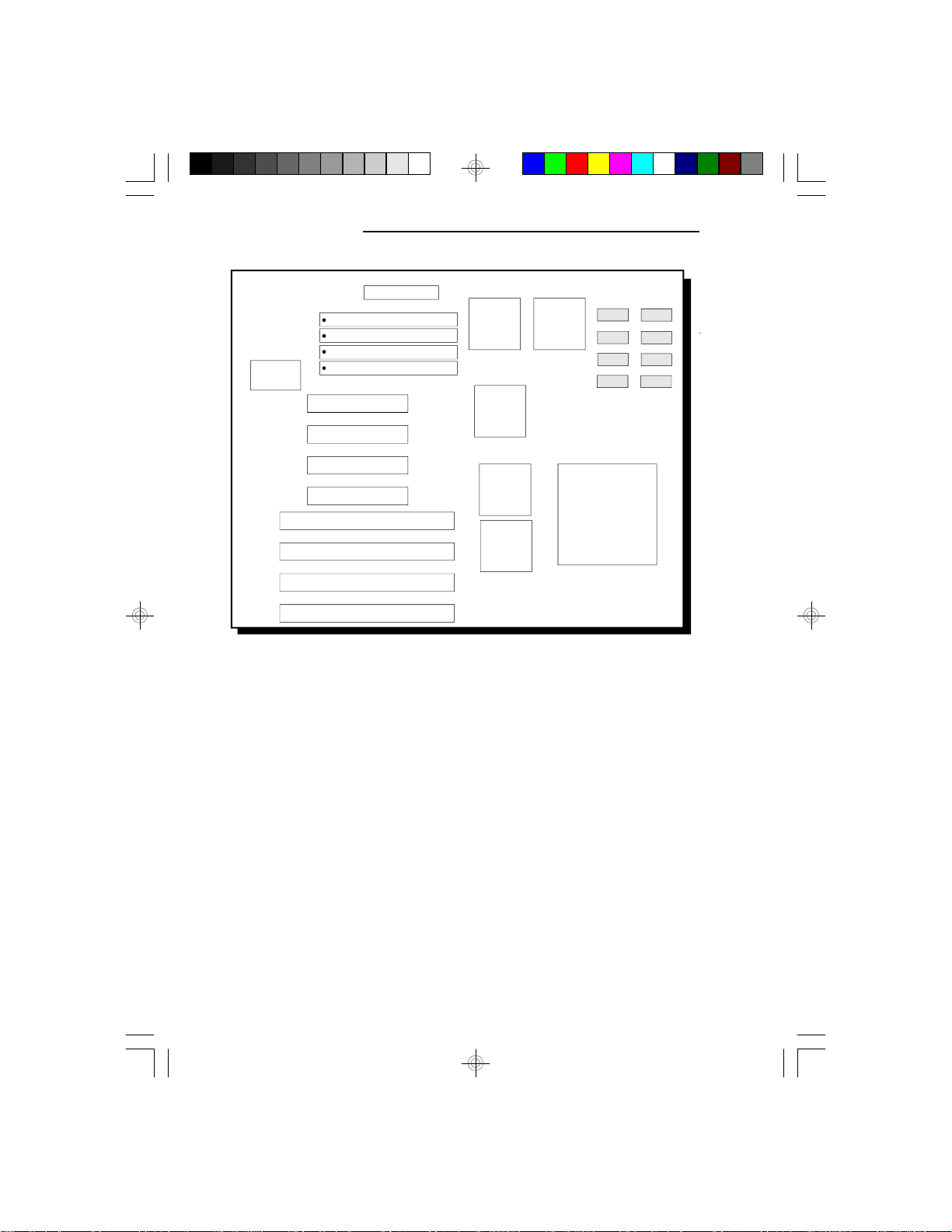

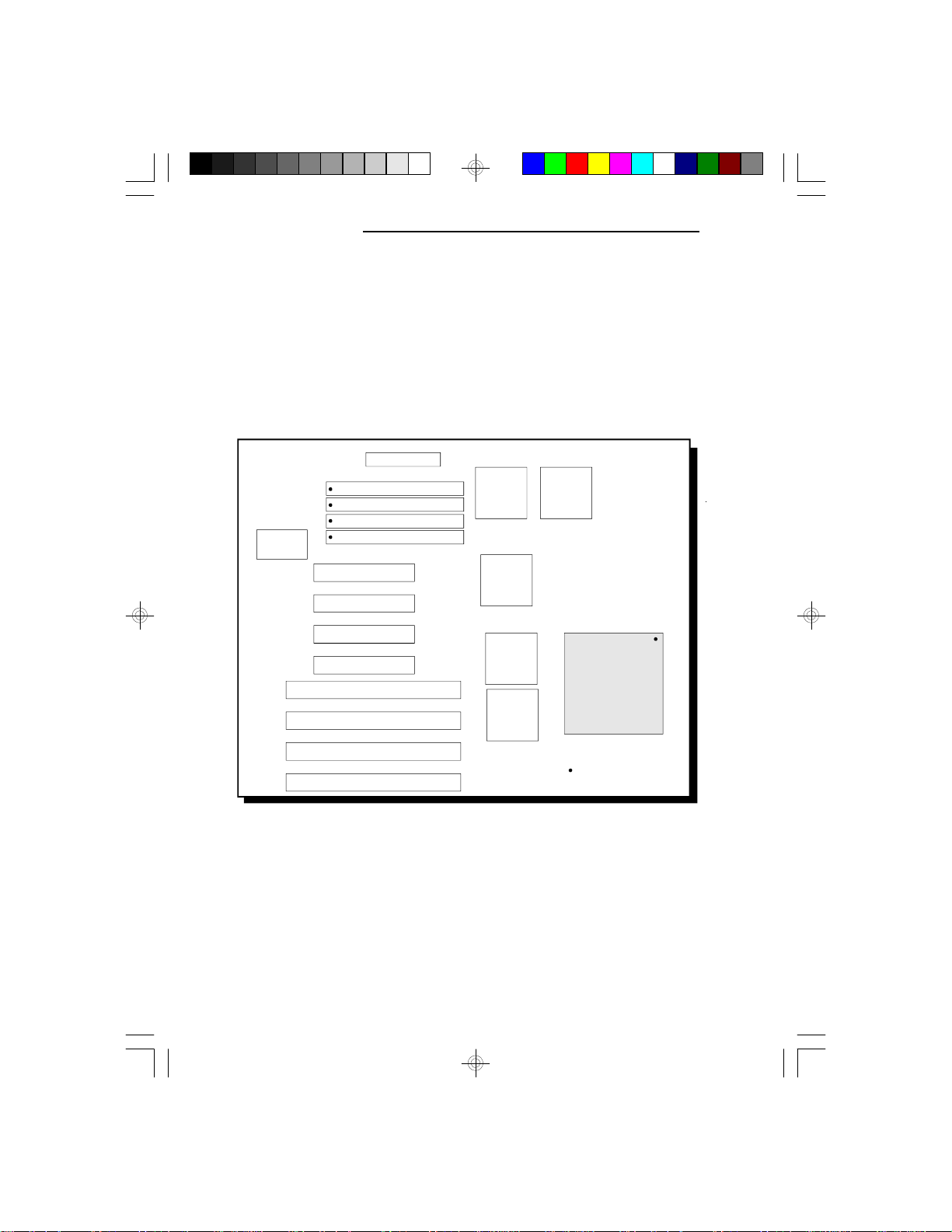

Board Configuration

The E586-ICP/E586-IPE is designed with jumpers and

connectors onboard. Make sure that the jumpers are set

correctly before installing the system board into your

system unit.

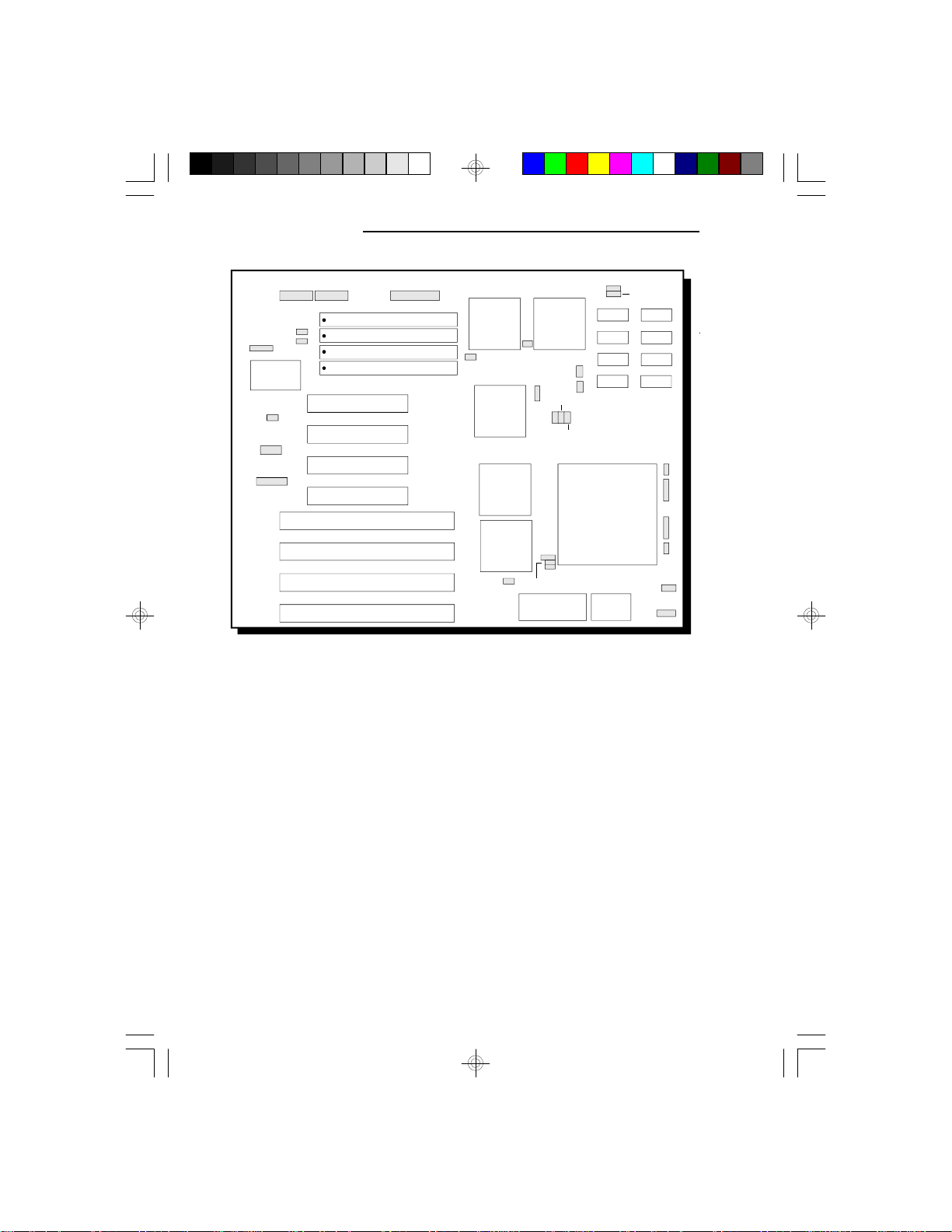

E586-ICP/E586-IPE

J1

SL82C101P

JP1

JP2

PL1 PL2

JP3

JP5

PCI Slot - Slave

PCI Slot - Master/Slave

PCI Slot - Master/Slave

PCI Slot - Master/Slave

EISA Slot

EISA Slot

EISA Slot

EISA Slot

J2

82433LX

JP6

82434

82375

82374

JP7

JP8

JP13

JP10

JP12

JP11

EPROM

82433LX

JP14

Flash

Locations of Jumpers and Connectors

on the E586-ICP System Board

JP15

JP18

JP16

JP22

JP24

JP27

JP19-JP21

ZIF

Socket

JP23

JP25

J3

J4

J6

J7

JP26

JP28

Installation Overview u 2-7

Page 18

EISA/PCI System Board

J1

SL82C101P

JP70

JP1

JP2

PL1 PL2

JP3

JP5

PCI Slot - Slave

PCI Slot - Master/Slave

PCI Slot - Master/Slave

PCI Slot - Master/Slave

EISA Slot

EISA Slot

EISA Slot

EISA Slot

J2

82433LX

JP8

JP6

JP10

82434

JP12

82375

82374

JP11

JP7

JP13

EPROM

Locations of Jumpers and Connectors

on the E586-IPE System Board

82433LX

JP15

JP16

JP14

Flash

JP17

JP18

JP22

ZIF

Socket

JP23

J3

J4

J6

J7

JP26

JP28

2-8 u Installation Overview

Page 19

Jumper Settings

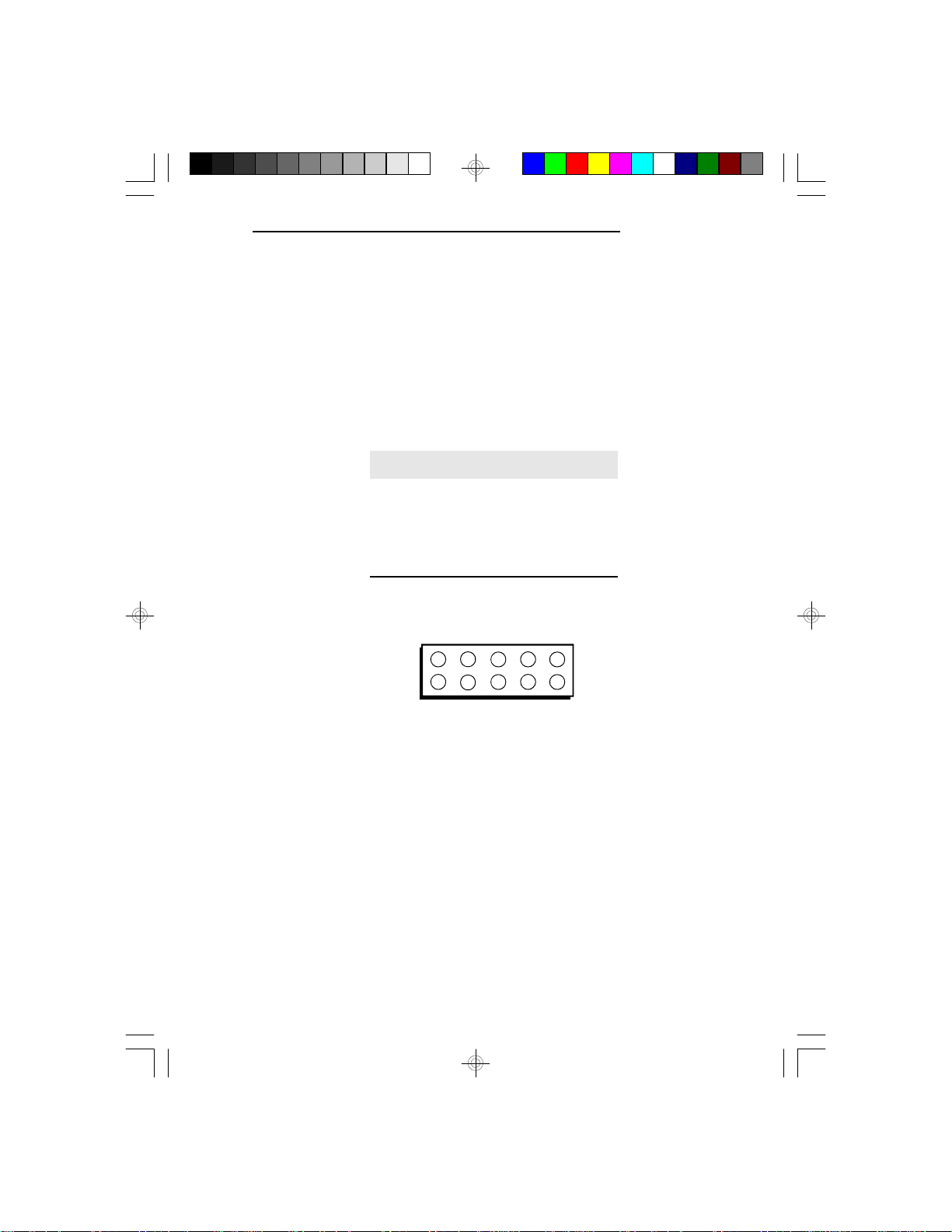

Jumper JP1

PCI Edge-Triggered Interrupt

Jumper JP1 is used to select the PCI edge-triggered

interrupt of the E586-ICP/E586-IPE system board. Set

JP1 according to the table shown below.

E586-ICP/E586-IPE

JP1

1-2 On

3-4 On

5-6 On

7-8 On

9-10 On

IRQ

15

2

1

A A B C

IRQ

14

INT

Int. A

Int. A

Int. B

Int. C

Int. D

IRQ

11

IRQ

10

IRQ

IRQ15

IRQ14

IRQ11

IRQ10

IRQ9

IRQ

9

10

9

D

Installation Overview u 2-9

Page 20

EISA/PCI System Board

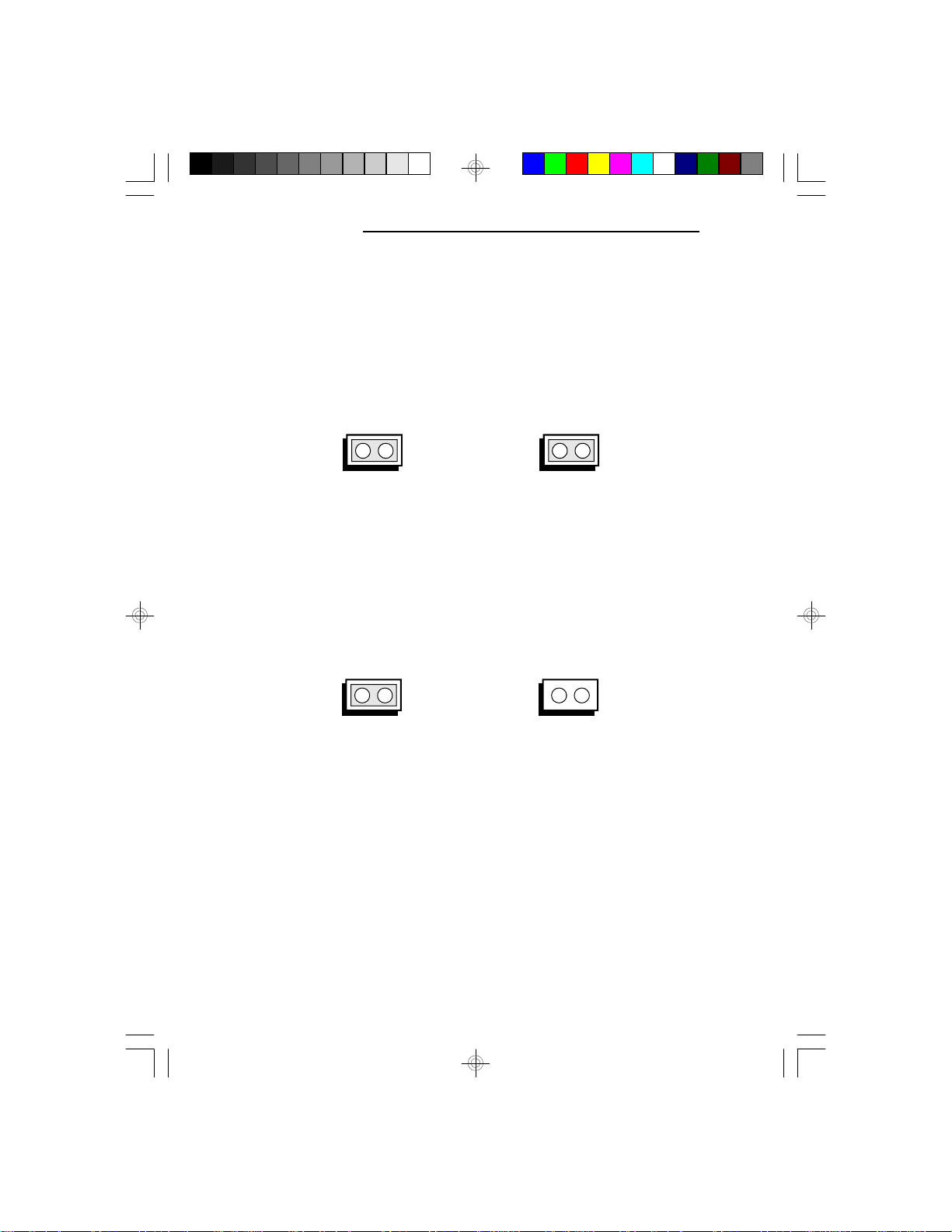

Jumpers JP3 and JP5

Built-in IDE

The E586-ICP/E586-IPE system board is equipped with

a built-in IDE disk interface, only if installed with the

Symphony SL82C101P chip. Set JP5 to On to enable the

built-in IDE. Set JP3 to On to disable the built-in IDE.

JP3 JP5

On: IDE Disabled

(Default)

Jumpers JP6 and JP8

Parity Enable/Disable

Set Jumpers JP6 and JP8 to On to enable the SRAM’s

parity bit.

On: Parity Enabled

(Default)

On: IDE Enabled

Off: Parity Disabled

2-10 u Installation Overview

Page 21

Jumper JP7

PS/2 Mouse

The E586-ICP/E586-IPE package includes a DB-25S

hole cover that holds the PS/2 mouse port. The PS/2

mouse port uses IRQ12. If you set Jumper JP7 to

IRQ12 enable, make sure you connect the PS/2 mouse

port to Connector J1.

Jumper JP11

Display Type Select

Jumper JP11 sets the display adapter to color or mono.

This jumper must match the type of display adapter

installed. If you change your video adapter, make sure

this jumper is changed accordingly.

E586-ICP/E586-IPE

Off: IRQ12 DisabledOn: IRQ12 Enabled

(Default)

321

1-2 On: Color

(Default)

Installation Overview u 2-11

321

2-3 On: Mono

Page 22

EISA/PCI System Board

Jumper JP13

Password Clear

If you set a password in the “Password Setting” option

and forget your password, power off your system and

set Jumper JP13 to On to clear the password stored in

your CMOS. Now power on your system. After your

system has detected the floppy or hard drive, turn it off

again and set JP13 to Off.

Jumper JP26

Flash EPROM

Jumper JP26 should be set to match the type of Flash

EPROM installed on the E586-ICP/E586-IPE system

board. See page 2-7 and 2-8 for the location of the Flash

EPROM installed on your system board.

On: Clear Password

321

1-2 On: Flash EPROM

(Default)

Off: Normal

(Default)

321

2-3 On: Normal EPROM

2-12 u Installation Overview

Page 23

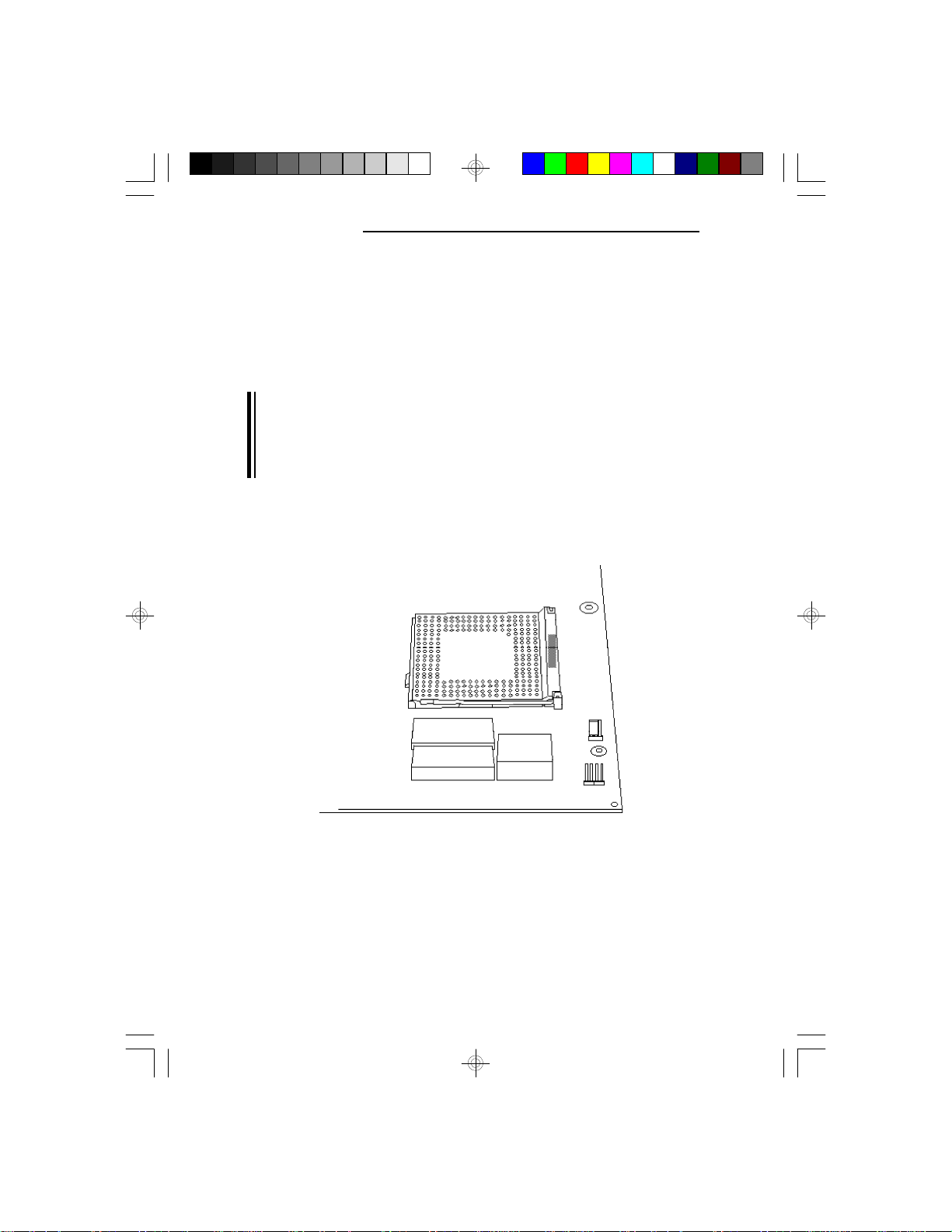

Cache Configuration

The E586-ICP/E586-IPE system board can be configured to two different cache sizes: 256KB and 512KB.

256KB of cache memory is the default size.

The system board supports direct map write-back or

write-through cache subsystem with tag RAM integrated

into the chipset.

The E586-ICP uses Burst SRAM for fast 3-1-1-1 Level

2 cache access. The E586-IPE uses Async SRAM for

3-2-2-2 Level 2 cache access.

E586-ICP/E586-IPE

82433LX 82433LX

SL82C101P

82434

82375

82374

SRAM

SRAM

ZIF

Socket

Locations of the SRAMs on the E586-ICP System Board

Installation Overview u 2-13

SRAM

SRAM

Page 24

EISA/PCI System Board

SL82C101P

Locations of the SRAMs on the E586-IPE System Board

82433LX 82433LX

82434

82375

82374

SRAM

SRAM

SRAM

SRAM

ZIF

Socket

SRAM

SRAM

SRAM

SRAM

2-14 u Installation Overview

Page 25

Jumper Setting for Cache Memory

Jumper JP15

Level 1 Cache

The Level 1 cache of the PentiumTM processor supports

Write Back and Write Through cache subsystem. Set

JP15 as shown below.

On: Write Through Off: Write Back

Jumpers JP22 and JP23

Level 2 Cache

If you have upgraded the cache size of your E586-ICP/

E586-IPE system board, change Jumpers JP22 and JP23

as shown below.

E586-ICP/E586-IPE

(Default)

L2 Cache

1-2: On

JP23

2-3 On

2-3 On

1-2 On

321

512KB

256KB*

None

321

JP22

2-3 On

1-2 On

1-2 On

2-3: On

Installation Overview u 2-15

Page 26

EISA/PCI System Board

CPU Installation

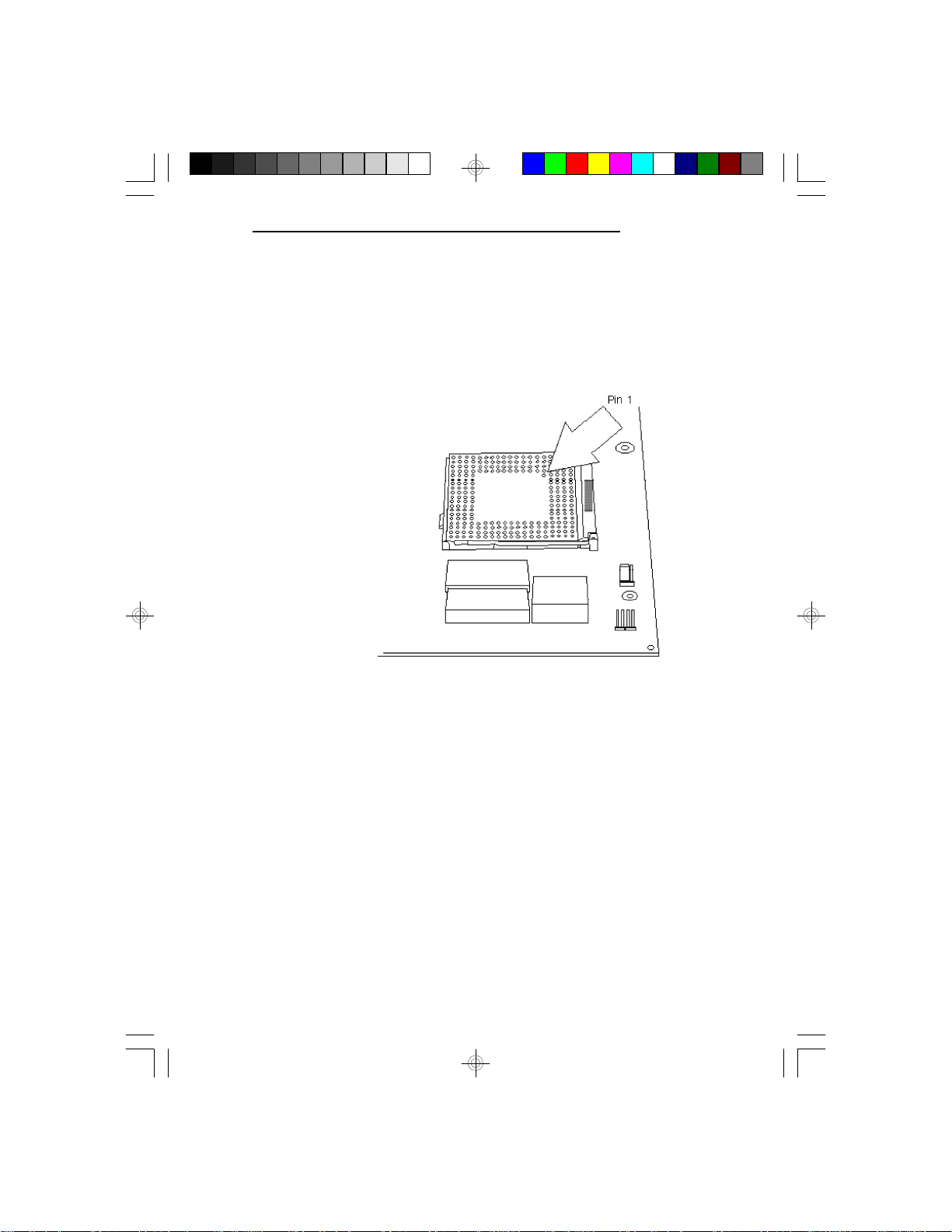

The E586-ICP/E586-IPE is equipped with a 273-pin

Zero Insertion Force (ZIF) socket on location U29 of

the system board. Make sure the jumpers are set

correctly before applying power, or you may damage the

CPU or system board.

SL82C101P

82433LX 82433LX

82434

U29

82375

ZIF

Socket

82374

Location of Pin 1

Location of the ZIF Socket on the E586-ICP/E586-IPE System Board

2-16 u Installation Overview

Page 27

Jumper Settings for CPU

Jumper JP18

CPU Speed

Set Jumper JP18 according to the speed of the CPU

installed on the E586-ICP/E586-IPE system board.

E586-ICP/E586-IPE

On: 60MHz

Off: 66MHz

(Default)

The jumpers below are for factory testing only and

should always be set to their default configurations.

Reconfiguring these jumpers will cause problems with

your E586-ICP or E586-IPE system board.

JP10: 2-3 On

JP12: On

JP14 and JP16 : Off

JP17 and JP70: Off (E586-IPE)

JP19-JP21, JP24 & JP25: 2-3 On (E586-ICP)

JP27: Off (E586-ICP)

Installation Overview u 2-17

Page 28

EISA/PCI System Board

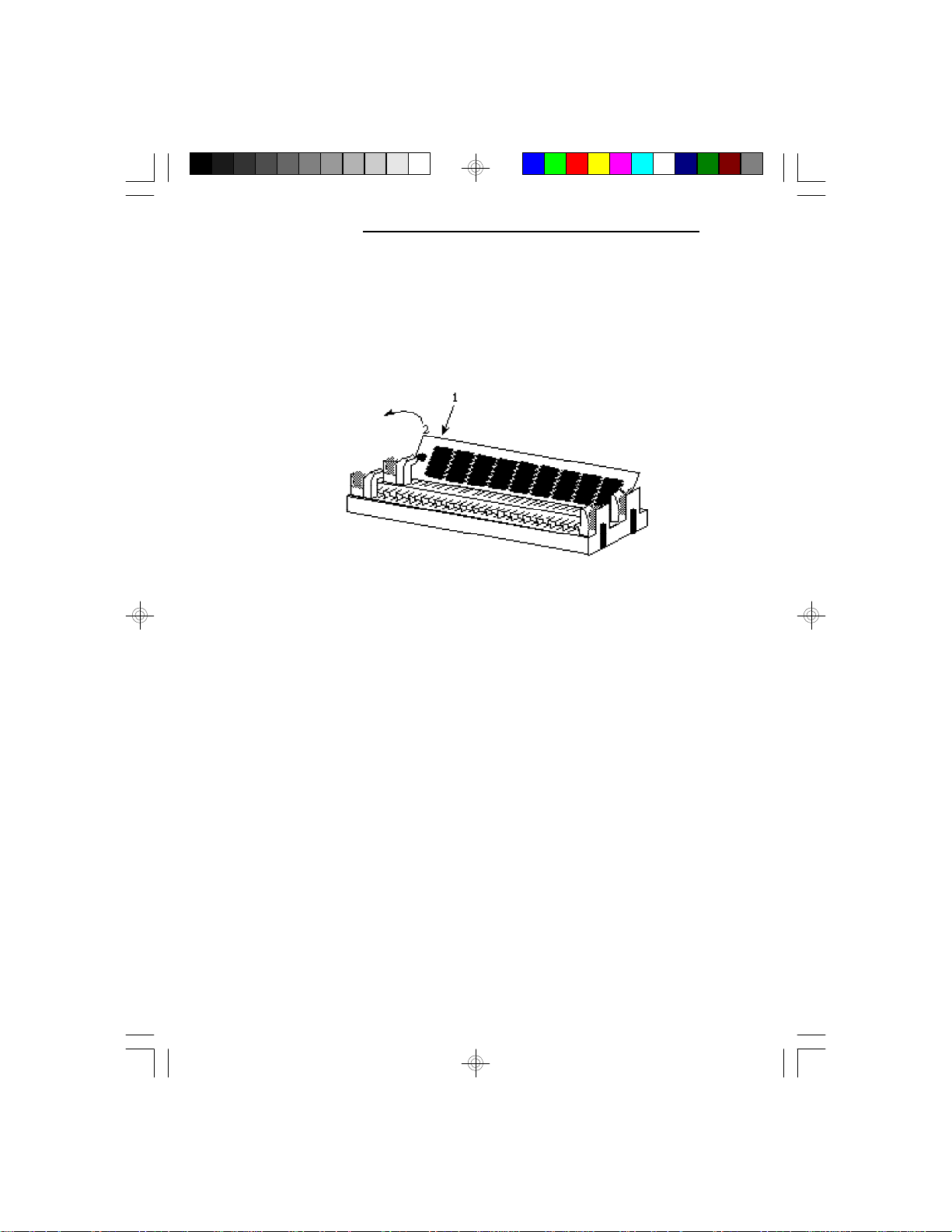

Installing Upgrade CPUs

The E586-ICP/E586-IPE is equipped with a 273-pin

Zero Insertion Force (ZIF) socket at location U29 of the

system board.

Warning:

Open the socket only if actually installing a CPU. The

warranty on the original CPU will be voided if the S/N

seal is broken. Installation of the PentiumTM Processor

will not affect the original system warranty.

The 273-pin ZIF socket consists of four rows of pin

holes on each side.

Zero Insertion Force (ZIF) Socket

2-18 u Installation Overview

Page 29

E586-ICP/E586-IPE

To install, simply move the handle upward. Remove the

original CPU from the socket. Position the CPU above

the socket. Make sure pin 1 of the CPU is aligned with

pin 1 of the socket. Lower the chip until the pins are

inserted properly in their corresponding holes.

Pin 1 of the ZIF Socket

Installation Overview u 2-19

Page 30

EISA/PCI System Board

Lifting the Handle

Positioning the CPU Above the ZIF Socket

2-20 u Installation Overview

Page 31

E586-ICP/E586-IPE

Gently push the handle down until the handle locks into

place. You will hear a click when the handle is secure.

When you want to remove the chip, simply lift the

handle and remove the chip.

Warning:

The cables (floppy drive, hard drive, CD-ROM, etc.)

must be routed clear of the CPU with a minimum of

0.25" horizontal clearance to allow heat dissipation.

A minimum of 1.4" vertical clearance (measured above

the socket surface) must be kept free above the CPU.

Do not run cables or other obstructions in this area.

Adequate airflow for cooling must be provided over the

CPU. For PentiumTM Processors, the airflow must be

adequate to keep the system temperature below 40oC,

measured 0.5 inch above the CPU and assuming a room

temperature of 25oC.

Installation Overview u 2-21

Page 32

EISA/PCI System Board

Installing the System Board

Before installing the system board into your system unit,

you should prepare the tools you will use:

You will need:

• one medium size, flat-bladed screwdriver

• one medium Philips screwdriver

Step 1

Unlock your system unit. Turn off the power and disconnect all power cords and cables.

Step 2

Remove the system unit cover. Refer to the manufacturer's instructions if necessary.

Step 3

Remove expansion cards seated in any of the expansion

slots and detach all connectors from the old system

board.

Step 4

Loosen the screws holding the original system board and

remove the board from the system. Save the screws.

2-22 u Installation Overview

Page 33

Step 5

Step 6

Step 7

Step 8

E586-ICP/E586-IPE

Insert the SIM modules into the SIMM banks on the

E586-ICP/E586-IPE. The quantity and location of the

SIM modules is dependent upon the memory

configuration and type of modules you intend to use.

Set the corresponding jumpers.

Install the prepared E586-ICP/E586-IPE system board

into the case and replace the screws.

Reinstall all cards and connectors and replace the system

unit cover. Reconnect all power cords and cables.

Installation Overview u 2-23

Page 34

EISA/PCI System Board

Installing the PS/2 Mouse Port

The E586-ICP/E586-IPE package includes a DB-25S

hole cover that holds the PS/2 mouse port attached with

a ribbon cable.

To install:

1. Use the two screws provided with the package to

secure the DB-25S hole cover to the DB-25S hole

normally found at the rear of a system chassis.

2. Connect the cable to Connector J1 of the system

board.

2-24 u Installation Overview

Page 35

v Initial Setup Program

After you power up your system, the BIOS message

appears on your screen and the memory count begins.

After the memory test, the following message will

appear on the screen:

Press CTRL-ALT-ESC/DEL to enter setup

If the message disappears before you respond, restart

your system or press the “Reset” button. You may also

restart the system by pressing the <Ctrl> <Alt> <Del>

keys. If you do not press these keys at the correct time

and the system does not boot, the following error message will appear:

Press F1 to continue, Ctrl-Alt-Esc or Del to enter Setup

If you have set a password and selected “System” in the

Security Option of the BIOS Feature Setup menu, you

will be prompted for the password everytime the system

is rebooted or any time you try to enter Setup. Type in

the correct password and press <Enter>.

E586-ICP/E586-IPE

If you selected “Setup” in the Security Option, you will

be prompted for the password only when you try to

enter Setup. Refer to the “BIOS Features Setup” section

for more information.

Initial Setup Program u 3-1

Page 36

EISA/PCI System Board

Award BIOS CMOS Setup Utility

Press <Ctrl> <Alt> <Esc> or <Del> to enter the Setup

utility. A screen similar to the one below will appear.

Use the arrow keys to highlight the option you want and

press <Enter>.

Standard CMOS Setup

Use the arrow keys to highlight the “Standard CMOS

Setup” and press <Enter>, a screen similar to the one on

the next page will appear.

3-2 u Initial Setup Program

Page 37

E586-ICP/E586-IPE

Date and Time

Sets the time and date for the system. Press <F3> for

the calendar.

Drive C and Drive D

If you have added a hard drive, you must select the

appropriate type for the drive. The E586-ICP/E586-IPE

has 46 pre-set types and one user-definable type. Use the

<Page Up> or <Page Down> keys to select the appropriate type for the drive.

The table in Appendix G gives a complete listing of the

available drive types. Any given hard drive must be set

to one specific drive-type number. Please refer to your

hard drive documentation to find the appropriate type

number.

Initial Setup Program u 3-3

Page 38

EISA/PCI System Board

If none of the pre-set types is appropriate for your hard

drive, choose “User”, which is the user-definable type.

To use this type, highlight either hard disk C or D,

depending on your hard drive configuration. Use the

arrow keys until type “User” is showing. Fill in all the

parameters as specified by the drive manufacturer. If

either of the drives is not present, select “None” and

press <Enter>.

Drive A and Drive B

These options are used to select the type of floppy disk

drives installed in your system. If either of the drives is

not present, select “None”. Make sure you choose the

correct drive type; otherwise, your system might improperly format the device.

Video

This is used to select the type of video adapter installed

in your system.

Halt on

This option selects when the system will halt if an error

is detected during power up.

No Errors: The system boot will not stop for any

errors detected.

All Errors: The system will stop whenever the BIOS

detects a non-fatal error.

All, But Keyboard: The system will stop for any

All, But Diskette: The system will stop for any

3-4 u Initial Setup Program

errors except a keyboard error.

errors except a disk error.

Page 39

All, But Disk/Key: The system will stop for any

Memory

The lower right hand corner shows the base memory

size, extended memory size, expanded memory size and

the other memory size of your system. You cannot alter

these items; your computer automatically detects and

displays them.

The Other Memory size refers to the memory located in

the 640K to 1024K address space. This is the memory

used for different applications. DOS uses this area to

load device drivers to keep as much base memory free

for application programs. Most use this for the Shadow

RAM.

When you are through making changes in the Standard

CMOS Setup, press <Esc> to return to the main menu.

BIOS Features Setup

E586-ICP/E586-IPE

errors except a keyboard or disk

error.

Use the arrow keys to highlight the “BIOS Features

Setup” and press <Enter>, a screen similar to the one on

the next page will appear.

Initial Setup Program u 3-5

Page 40

EISA/PCI System Board

The Virus Warning option may be set to “enabled” or

“disabled”. When enabled, the BIOS issues a warning

when any program or virus sends a Disk Format command or attempts to write to the boot sector of the hard

disk drive.

If you choose “System” in the Security Option, you will

be prompted for a password every time you cold boot

your system or access setup. If you choose “Setup”, you

will be prompted for a password only when trying to

access setup.

If the changes you made are incorrect or you change

your mind, press <F6> or <F7> to return to the default

settings. Press <Esc> after making the changes to return

to the main menu.

3-6 u Initial Setup Program

Page 41

Chipset Features Setup

The E586-ICP/E586-IPE uses the Intel 82430 chipset.

The Chipset Features Setup allows you to modify some

functions to optimize system performance.

If you press <Enter>, a screen similar to the one below

will appear.

E586-ICP/E586-IPE

Use the arrow keys to move the highlight bar to the

option you wish to change or modify. Use the <Page

Up>, <Page Down>, <+> or <-> keys to make the

corresponding changes.

If the changes you made are incorrect or you change

your mind, press <F6> or <F7> to return to the default

settings. Press <Esc> after making the changes to return

to the main menu.

Initial Setup Program u 3-7

Page 42

EISA/PCI System Board

PCI Slot Configuration

Use the arrow keys to highlight the "PCI Slot Configuration" and press <Enter>, a screen similar to the one

below will appear.

The INT of each PCI slot must be set according to the

INT of the PCI add-on card installed on the slot. Subsequently, you must select an IRQ for the INT you have

selected for the slot.

Use the arrow keys to move the highlight bar to the

option you wish to change or modify. Use the <Page

Up>, <Page Down>, <+> or <-> keys to make the

corresponding changes.

If the changes you made are incorrect or you change

your mind, press <F6> or <F7> to return to the default

settings. Press <Esc> after making the changes to return

to the main menu.

3-8 u Initial Setup Program

Page 43

Load BIOS Defaults

If, for some reason, the CMOS becomes corrupted, the

system can be reconfigured with the default values

stored in the ROM chips. The BIOS Setup default values

should provide optimum performance for the system.

You should use these values unless you are possibly

having hardware problems.

Highlight this option on the main menu and press <Enter>. The message below will appear.

Load BIOS Defaults (Y/N)? N

Type “Y” and press <Enter> to return to the BIOS

setup default values. After pressing <Enter>, you will be

returned to the main menu.

Load Setup Defaults

The Setup defaults are similar to the BIOS Setup defaults. These defaults are the most stable values for the

system and should be used if you are possibly having

hardware problems.

E586-ICP/E586-IPE

Highlight this option on the main menu and press <Enter>. The message below will appear.

Load Setup Defaults (Y/N)? N

Type “Y” and press <Enter> to return to the Setup

default values. After pressing <Enter>, you will be

returned to the main menu.

Initial Setup Program u 3-9

Page 44

EISA/PCI System Board

Password Setting

If you want to set a password, make sure that the

Security Option under the BIOS Features Setup is set to

“System” or “Setup”. Refer to the BIOS Features Setup

option for more information.

Use the arrow keys to highlight the Password Setting

option and press <Enter>. The message below will

appear.

Type in the password. You are limited to eight characters. Type in a password that is eight characters long or

shorter. When done, the message below will appear:

You are asked to verify the password. Type in exactly

the same password. If you type in a wrong password,

you will be prompted to enter the correct password

again. Otherwise, enter a new password.

Enter Password:

Confirm Password:

To delete or disable the password function, simply press

<Enter> instead of typing in a new password. If for

some reason, you forget your password, a jumper can be

set to clear the password. Refer to Jumper .... on page

... for more information.

Press the <Esc> key to return to the main menu.

3-10 u Initial Setup Program

Page 45

IDE HDD Auto Detection

This option detects the hard disk parameters for the hard

disk drives installed in your system. Highlight this option

and press <Enter>. A screen similar to the one below

will appear.

The screen displays the parameters detected and allows

you to accept or reject the parameters. Type “Y” and

press <Enter> to accept the parameters or press <Esc>

to abort. If you select “Y”, the parameters of the hard

disk will be displayed in the Standard CMOS Setup.

E586-ICP/E586-IPE

Save & Exit Setup

When all the changes have been made, highlight “Save &

Exit Setup” and press <Enter>. The message below will

appear:

Save to CMOS and Exit (Y/N)? N

Initial Setup Program u 3-11

Page 46

EISA/PCI System Board

Type “Y” and press <Enter>. The following message

will appear:

Type “Y” and press <Enter>. The modifications you

have made will be written into the CMOS memory, and

the system will reboot. You will once again see the

initial diagnostics on the screen. If you wish to make

additional changes to the setup, press <Ctrl> <Alt>

<Esc> or <Del> after memory testing is done.

Exit Without Saving

When you do not want to save the changes you have

made, highlight this option and press <Enter>. The

message below will appear:

Type “Y” and press <Enter>. The system will reboot

and you will once again see the initial diagnostics on the

screen. If you wish to make any changes to the setup,

press <Ctrl> <Alt> <Esc> or <Del> after memory

testing is done.

Reboot System (Y/N)? N

Quit Without Saving (Y/N)? N

3-12 u Initial Setup Program

Page 47

v EISA Configuration Utility

Overview

The E586-ICP/E586-IPE system board requires the use

of the EISA Configuration Utility (ECU). The ECU is

used to configure EISA (Extended Industry Standard

Architecture) computer systems.

EISA system boards and EISA adapter cards are much

more complex than the designs of ISA (Industry Standard Architecture) boards and adapter cards, making the

setup of jumpers and switches more complicated. The

ECU was created to automate this configuration process.

The CFG files that come with each EISA expansion

board are copied onto the ECU diskette. The ECU then

stores this configuration data in the system’s Extended

CMOS Memory. The CFG file tells the ECU what

choices the user has in configuring the card and what

system resources to reserve for the card. The

E586-ICP/E586-IPE system board uses the

“DFI0400.CFG” file.

E586-ICP/E586-IPE

File Structure

The ECU uses three different files: the CFG, CMS and

INF files.

CFG Files

Each EISA expansion board comes with a CFG file. A

board’s CFG file contains detailed information about the

board as well as the functions the board can perform.

For the E586-ICP/E586-IPE system board, choose the

"DFI0400.CFG" file to be configured.

EISA Configuration Utility u 4-1

Page 48

EISA/PCI System Board

CMS File

The CMS file contains a copy of the configuration

information that is written into the system’s Extended

CMOS Memory. Each CMS file should have a

corresponding INF file.

INF File

The INF file contains detailed information about a

configuration such as switch and jumper settings,

software statements, connection statements, and resource

allocation. The INF file is used by the “Display/Print”

command to recall information on a saved configuration.

Each INF file should have a corresponding CMS file.

Initial Configuration

Every EISA system board and expansion board comes

with a CFG file. Prior to running the ECU, make sure

that all CFG files for expansion boards you are using are

in the same directory as the ECU file. If you did not

receive the CFG file for your expansion board, please

contact your dealer or the board manufacturer.

If you are installing an EISA hard drive controller/SCSI

host adapter, you will need to run the ECU from a

bootable floppy diskette because the system will not see

the hard drive until the EISA expansion board is

configured. To run the ECU after the hard drive

controller/SCSI host adapter is installed:

1. Create a directory on the disk drive where you want

to install the EISA configuration files. Change to this

directory.

4-2 u EISA Configuration Utility

Page 49

2. Copy your EISA Configuration Utility diskette and

the CFG files for all of your EISA boards to this

directory.

3. To run the ECU, make sure that you are in the

directory created in step 1 and type CFG.

Main Menu

The ECU outlines the six steps that involved in configuring a EISA system, steps 1, 2, 3 and 5 are optional. To

select a step, use the arrow keys to move to a step of

your choice and press <Enter>. You may also select a

step by pressing its number. If you are using a mouse,

move the mouse pointer to the selected option and click

the left-mouse button once.

Note:

For a mouse to work in the ECU, you must have a

previously installed mouse driver.

The utility also includes an online Help menu which may

be accessed anytime by pressing the <F1> key.

E586-ICP/E586-IPE

EISA Configuration Utility u 4-3

Page 50

EISA/PCI System Board

EISA CONFIGURATION UTILITY, Release 2.01 - (C)1992 American Megatrends Inc.

Step 1: About EISA Configuration

Step 2: Add and Remove Boards

Step 3: Change Configuration Settings

Step 4: Save Configuration

Step 5: View Switch/Jumper Settings

Step 6: Exit

[Select=Enter] [Exit=Esc] [Help=F1] [Utilities=F9]

Step 1: About EISA Configuration

This step displays information for users who are new to

EISA and EISA Configuration.

Step 2: Add and Remove Boards

This step is optional. Use this step to manually add or

delete boards not detected automatically. Most boards

are automatically detected and added by the ECU.

Choose Add and Remove Boards and a screen similar

to the one shown on the next page will appear.

4-4 u EISA Configuration Utility

Page 51

E586-ICP/E586-IPE

This box allows you to add, remove or move boards.

Step 2 - Add and Remove Boards

System - DFI E586-ICP/E586-IPE SYSTEM BOARD

Slot 1 - Empty

Slot 2 - Empty

Slot 3 - Empty

Slot 4 - Empty

Slot 5 - Empty

Slot 6 - Empty

Slot 7 - Empty

Slot 8 - Empty

- Press INSERT to add a board that was not deleted or has not been installed yet.

- Press DEL to remove the selected board.

- Press F7 to move the selected board to a different slot.

- Press Esc when finished with this step.

[Add=INSERT] [Remove=DEL] [Move=F7] [Done=ESC] [HELP=F1]

Add

This option allows you to add a new board to the

current configuration.

a. Press <Insert> to select the Add option and a screen

similar to the one shown below will appear.

Select the Board to Add

Directory: A:\*.CFG

!DFI0400.CFG - DFI E586-ICP/E586-IPE SYSTEM BOARD

!DFI0300.CFG - DFI EB3486-TN EISA SYSTEM BOARD

!DFI1001.CFG - DFI EISANet - 500 EtherNet Adapter

!DFI0001.CFG - EISA SYSTEM BOARD

!DFI0200.CFG - EISA SYSTEM BOARD

[Select=ENTER] [Cancel=ESC] [Add ISA=INSERT]

EISA Configuration Utility u 4-5

Page 52

EISA/PCI System Board

b. Select the board you want to add and press <Enter>.

If you wish to add an ISA board, choose Add ISA

option by pressing <Insert> at the “Select the Board

to Add” screen. An ISA Board Database box similar

to the one shown on the screen below will appear.

Note:

You must define an ISA board before it will appear

in the ISA Database definition box. See the “Define

ISA Board” section for further information.

If you do not want to add a board, choose Cancel to

go back to the Add and Remove Boards.

Step 2 - Add and Remove Boards

ISA Board Database

System - DFI EB3486-TN EISA SYSTEM BOARD

Slot 1 - Empty

Slot 2 - Empty

Slot 3 - Empty

Slot 4 - Empty

Slot 5 - Empty

Slot 6 - Empty

Slot 7 - Empty

Slot 8 - Empty

Select the ISA board to load or press <Esc> to exit.

a

[ ] WG-1200VL

- Press INSERT to add a board that was not deleted or has not been installed yet.

- Press DEL to remove the selected board.

- Press F7 to move the selected board to a different slot.

- Press Esc when finished with this step.

[Add=INSERT] [Remove=DEL] [Move=F7] [Done=ESC] [HELP=F1]

[Ok=ENTER] [Cancel=ESC]

Highlight the board you want to add in the configuration

and press <Enter>. A Slot Selection box similar to one

shown on the next page will appear.

4-6 u EISA Configuration Utility

Page 53

E586-ICP/E586-IPE

Step 2 - Add and Remove Boards

Adding a board

Performing syntax check on "AMIFFF1.CFG

System - DFI EB3486-TN EISA SYSTEM BOARD

Slot 1 - Empty

Slot 2 - Empty

Slot 3 - Empty

Slot 4 - Empty

Slot 5 - Empty

Slot 6 - Empty

Slot 7 - Empty

Slot 8 - Empty

- Press INSERT to add a board that was not deleted or has not been installed yet.

- Press DEL to remove the selected board.

- Press F7 to move the selected board to a different slot.

- Press Esc when finished with this step.

[Add=INSERT] [Remove=DEL] [Move=F7] [Done=ESC] [HELP=F1]

Select a slot for:

WG-1200VL

Board slot type is ISA16.

Slot Type

Slots are listed in recommended order.

[Select=ENTER]

1 EISA Yes

2 EISA Yes

3 EISA Yes

3 EISA Yes

5 EISA Yes

Slot Selection

Bus Master

You must select a slot for each adapter board. The slots

are listed in the recommended order of preference.

Select the slot that corresponds to the actual slot where

the adapter board being configured resides and press

<Enter>. Choose OK to continue the configuration

process.

Remove

This option allows you to remove a board from the

current configuration.

a. Select the board you want to remove from the

configuration and press <Delete>. A screen similar to

the one shown on the next page will appear.

EISA Configuration Utility u 4-7

Page 54

EISA/PCI System Board

Step 2 - Add and Remove Boards

System - DFI EB3486-TN EISA SYSTEM BOARD

Do you really want to remove:

Slot 1 - Empty

WG-1200VL

Slot 2 - Empty

Slot 3 - Empty

Slot 4 - Empty

[Ok=ENTER] [Cancel=ESC]

Slot 5 - Empty

Slot 6 - Empty

Slot 7 - Empty

Slot 8 - Empty

- Press INSERT to add a board that was not deleted or has not been installed yet.

- Press DEL to remove the selected board.

- Press F7 to move the selected board to a different slot.

- Press Esc when finished with this step.

[Add=INSERT] [Remove=DEL] [Move=F7] [Done=ESC] [HELP=F1]

Confirm

b. Press <Enter> to confirm removal or <Esc> to cancel.

Move

This option allows you to move an adapter board to

another slot.

a. Select the board you want to move and press <F7>.

A Slot Selection box similar to the one shown on the

next page will appear.

4-8 u EISA Configuration Utility

Page 55

Step 2 - Add and Remove Boards

E586-ICP/E586-IPE

System - DFI E586-ICP/E586-IPE SYSTEM BOARD

Slot 1 - Empty

Slot 2 - Empty

Slot 3 - WG-1200VL

Slot 4 - Empty

Slot 5 - Empty

Slot 6 - Empty

Slot 7 - Empty

Slot 8 - Empty

- Press INSERT to add a board that was not deleted or has not been installed yet.

- Press DEL to remove the selected board.

- Press F7 to move the selected board to a different slot.

- Press Esc when finished with this step.

[Add=INSERT] [Remove=DEL] [Move=F7] [Done=ESC] [HELP=F1]

Select a slot for:

WG-1200VL

Board slot type is ISA16.

Slot Type

1 EISAYes

2 EISAYes

4 EISAYes

5 EISAYes

6 EISAYes

Slots are listed in recommended order.

[Select=ENTER]

b. Select the slot that corresponds to the actual slot

where the adapter board to be moved will reside, and

press <Enter>.

c. If you are finish with this step, choose Done to

return to the main menu.

Step 3: Change Configuration Settings

Use this step to view or change configuration settings

for any board that is installed. If you skip this step, all

settings will remain set to their default values.

Slot Selection

Bus Master

1. Choose Change Configuration Settings and a box

similar to the one shown on the next page will

appear.

EISA Configuration Utility u 4-9

Page 56

EISA/PCI System Board

System - DFI E586-ICP/E586-IPE SYSTEM BOARD

Slot 1 - DFI EISANet-500 EtherNet Adapter

Slot 2 - Empty

Slot 3 - Empty

Slot 4 - Empty

Slot 5 - Empty

Slot 6 - Empty

Slot 7 - Empty

Slot 8 - Empty

- This step is optional, you may skip it by pressing ESC and all configuration

settings will remain unchanged.

- Press ENTER to view or change a board's configuration settings.

- Press ESC when you are satisfied with the current settings.

[Select=ENTER] [Done=ESC] [Advanced Options=F9] [HELP=F1]

2. Select the slot you want to change from the

configuration and press <Enter>.

a. If you want to change your system memory,

choose System Board and press <Enter>. Select

System Board Memory and press <Enter>. A

System Board Memory Functions box similar to

the one shown on the next page will appear. If

you do not want to change anything, press <Esc>

to go back to the previous screen.

Step 3 - Change Configuration Settings

4-10 u EISA Configuration Utility

Page 57

E586-ICP/E586-IPE

Edit Settings for: DFI E586-ICP/E586-IPE SYSTEM BOARD

System Board Memory

Use SIMM Memory Module for the 486 System Board.

[Select=ENTER] [Cancel=ESC]

System Board Memory Functions

( ) 2MB

( ) 4MB

( ) 6MB

( ) 8MB

( ) 10MB

( ) 12MB

( ) 16MB

( ) 18MB

( ) 20MB

( ) 24MB

( ) 32MB

( ) 34MB

( ) 36MB

( ) 40MB

b. Select the memory that was installed in your

system board and press <Enter>.

Note:

You can only choose up to a maximum range of

64MB under EISA Configuration.

EISA Configuration Utility u 4-11

Page 58

EISA/PCI System Board

DFI EISANet-500 I/O Addresses

Slot-Specific Only (Default)

DFI EISANet-500 EPROM

EPROM Disabled (Default)

Bus Master

Bus Release After Preempt

23 BCLK Cycles

DFI EISANet-500 Interrupt

Interrupt Edge/Level

Edge Triggered Interrupt

Ethernet

Packet Reception

Receive Own Packets

Connector Selection

Thin Ethernet (BNC1) [ETHERNet-500ECT]

[Done=ESC] [Change=ENTER] [Resources=F6] [PgUp] [PgDn] [Help=F1]

This menu box contains a list of all “choice” settings and

may have one or more resource settings. To change a

function’s choice setting:

a. Use the up and down arrow keys to highlight a

function and then press <Enter>. The first section

“DFI EISANet-500 I/O Addresses” box was already

shown on the next page.

Edit Settings for: DFI EISANet-500 Ethernet Adapter

4-12 u EISA Configuration Utility

Page 59

E586-ICP/E586-IPE

Edit Settings for: DFI EISANet-500 Ethernet Adapter

This board supports both slot-specific and ISA compatible I/O

DFI EISANet-500 I/O Addresses

addressing. The ISA mode should only be used for software

Slot-Specific Only (Default)

compatibility with ISA drivers.

DFI EISANet-500 EPROM

EPROM Disabled (Default)

Bus Master

Bus Release After Preempt

23 BCLK Cycles

[Select=Enter] [Cancel=ESC]

DFI EISANet-500 Iterrupt

Interrupt Edge/Level

Edge Triggered Interrupt

Ethernet

Packet Reception

Receive Own Packets

Connector Selection

Thin Ethernet (BNC1) [ETHERNet-500ECT]

[Done=ESC] [Change=ENTER] [Resources=F6] [PgUp] [PgDn] [Help=F1]

( ) Slot-Specific only (Default)

( ) Slot-Specific and ISA

b. An option box will appear for you to choose.

Choose Slot-Specific Only (Default) and press

<Enter>.

c. The same step should be done if you want to

change the following functions.

Note:

Some function may only have one choice

setting and therefore cannot be changed.

3. To change a function’s Resource settings, use the

up and down arrow keys to highlight a function

and then press <F6>. When you are satisfied with

the current settings, press <Esc> to return to the

previous menu.

Note:

Not all functions have resource settings.

EISA Configuration Utility u 4-13

Page 60

EISA/PCI System Board

Advanced Options

This option allows you to view detailed information

about the system board and the adapter boards installed

in the system.

a. Choose Advanced Options and a box similar to the

one shown below will appear.

Advanced Options

Global Resource Map

Board Details

System Details

System - DFI EB3486-TN EISA SYSTEM BOARD

Physical Board ID Map

Slot 1 - DFI EISANet-500 Ethernet Adapter

Slot 2 - Empty

Slot 3 - Empty

[Select=ENTER] [Done=ESC]

Slot 4 - Empty

Slot 5 - Empty

Slot 6 - Empty

Slot 7 - Empty

Slot 8 - Empty

- This step is optional, you may skip it by pressing ESC and all configuration

settings will remain unchanged.

- Press ENTER to view or change a board's configuration settings.

- Press ESC when you are satisfied with the current settings.

[Select=ENTER] [Done=ESC] [Advanced Options=F9] [HELP=F1]

Step 3 - Change Configuration Settings

Global Resource Map

The Global Resource Map allows you to view the

DMA Channels, IRQ line, I/O port address and

memory address of a board.

4-14 u EISA Configuration Utility

Page 61

Board Details

This option informs you about the slot number, ID

and the board slot type of a board.

System Details

This option allows you to view the slot type, the

amperage used and EISA CMOS size of the boards

installed in the system.

Physical Board ID Map

The Physical Board ID Map allows you to view the

boards that are physically present in the system.

b. Press <Esc> to return to the main menu.

Step 4: Save Configuration

This option allows you to save the configuration in the

CMS and INF file.

E586-ICP/E586-IPE

a. After you have finished modifying the configuration,

go to the main menu and choose Save Configuration.

b. A box will appear informing you that the

configuration has been saved into the INF and CMS

file.

EISA Configuration Utility u 4-15

Page 62

EISA/PCI System Board

Step 5: View Switch/Jumper Settings

This step allows you to set DIP switches and jumpers on

any board that is switch or jumper configurable.

a. After saving the configuration, choose View Switch/

Jumper Settings if you want to configure the switch

or jumper from your board. Press <Enter> and a box

similar to the one shown below will appear.

EISA CONFIGURATION UTILITY, Release 2.01 - (C)1992 American Megatrends Inc.

Step 5: View Switch of Jumper Settings

After saving the configuration it is important that

you do the following steps before using this system:

1.Note the switch and jumper settings verify that all switches and

2.Note the software statements to see if any of the boards in your

The screen that follow provide this information.

[ Ok=ENTER ]

Step 1: About EISA Configuration

Step 2: Add and Remove Boards

jumpers on the boards in your system are set correctly. Some boards

have switches and jumpers that need to be set manually.

Step 3: Change Configuration Settings

configuration need special drivers to be loaded.

Step 4: Save Configuration

Step 5: View Switch/Jumper Settings

Step 6: Exit

[Select=Enter] [Exit=Esc] [Help=F1] [Utilities=F9]

b. Press <Enter> to display the information. If your

board has no switches or jumpers, a box will appear

informing you that the board has no switches or

jumpers.

c. To print the configuration, press <F7> and a Confirm

Print box similar to the one shown on the next page

will appear.

4-16 u EISA Configuration Utility

Page 63

Page 1 of 6: Switches and Jumpers for Slot 0

Slot 0 - DFI E586-ICP/E586-IPE SYSTEM BOARD

This board has no

[Done=ESC] [Print=F7] [PgUp] [PgDn] [Help=F1]

d. Type the filename you want to print and press

<Enter>.

e. Press <Esc> to return to the main menu.

Step 6: Exit

Switch/Jumper View

Confirm Print

Print to: (•) Printer

( ) File

Filename: Config. PRN

Ok=ENTER Cancel=ESC

E586-ICP/E586-IPE

This step exits to the operating system. If any

configuration settings were changed, you are given the

option of rebooting the system so that the system

settings will take effect.

a. From the menu option, choose Exit and press

<Enter>. A box will appear asking “Do you really

want to exit?”

Choose:

Yes - to exit to DOS.

Cancel - to return to the main menu.

Reboot - Reboot the system so that changes will

take effect.

EISA Configuration Utility u 4-17

Page 64

EISA/PCI System Board

Utilities Configuration

This screen controls how a configuration is produced.

Several options are available, each one can be enabled or

disabled by pressing SPACE when an option is

highlighted. To configure the Utilities:

From the main menu, press <F9> and a Utilities box

similar to the one shown below will appear.

EISA CONFIGURATION UTILITY, Release 2.01 - (C)1992 American Megatrends Inc.

Press <Space> to change settings.

[ ] Remote Mode (make a configuration for another system)

[ ] Advanced/Dealer Mode (show functions marked as EXP)

[ ] Force new configuration (ignore previous settings)

[ ] Load CFG files manually from directory list

[ ] Load CFG files listed in CFGLIST.DAT

[ ] Ignore ID mismatches between installed boards and CMOS

[ F5 ] = Restore configuration from backup (CMS file)

[ F6 ] = Display Physical Board ID Map

[ F7 ] = Define ISA Board

[OK=ENTER] [Cancel=ESC]

Utilities

Step 6: Exit

[Select=Enter] [Exit=Esc] [Help=F1] [Utilities=F9]

Remote Mode

The Remote Mode of the configuration should be turned

off if you are working on this computer. If you want to

produce a configuration for a computer other than this

one, turn on the Remote Mode. If Remote Mode is off,

configuration information will be stored in this

computer’s EISA CMOS RAM as well as a CMS file

and INF file.

4-18 u EISA Configuration Utility

Page 65

E586-ICP/E586-IPE

If Remote Mode is on, the configuration will be stored

in the files only. These files can be copied to another

computer and the configuration can be copied to that

system's EISA CMOS RAM using the “Restore

configuration from backup” option on this screen.

Advanced Dealer

Some EISA boards have CFG files that contain option

that are not ordinarily configured by end users. If this

mode is turned on, any functions that are marked as

EXP (expert) will be visible and can be changed.

Force New Configuration

When turned on, this mode will ignore any existing

configuration settings in CMOS or in the CMS file. All

settings will be set to their defaults.

Load CFG Files Manually from Directory List

When this mode is turned on, the ECU will not

automatically detect and add boards to the configuration.

You will be prompted to select boards one by one.

Load CFG Files Listed in CFGLIST.DAT

If you prefer to specify a list of CFG files to load, you

may create a file called CFGLIST.DAT that contain the

filename of the CFG files to be added. Turning this

option on causes the ECU to use this file.

EISA Configuration Utility u 4-19

Page 66

EISA/PCI System Board

Ignore ID Mismatches Between Installed Boards and CMOS

Normally the ECU will only configure boards that are

physically present in the system. If a board was present

in a previous configuration but was then physically

removed, the ECU will normally not load the CFG files

for this board. Turning this option on causes the ECU to

load CFG files for all boards that were in the previous

configuration regardless of whether or not they are

physically installed.

Define ISA Board

In addition to EISA adapter boards, you can install ISA

adapter boards by choosing this option. Most ISA

adapter boards do not have a CFG file. Without a CFG

file, the ECU cannot automatically reserve system

resources for ISA adapter boards. These boards must be

configured manually. To configure an ISA board:

1. Choose Configure Define ISA Board and an ISA

Board Definition box similar to the one shown below

will appear.

Board Name: WG-1200VL

Manufacturer: DFI

Board Type: Slot Type:

[Save=F10] [Load=F9] [New=F2] [Delete=F4] [Quit=ESC]

( )Video Board

( )Multifunction Board

( )Mass Storage Device

DMA

-

-

-

-

ISA Board Definition

IRQ Ports Memory

-

-

-

-

-

-

-

4-20 u EISA Configuration Utility

( )16 bit

( )8 bit

( )8 or 16 bit

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

Page 67

E586-ICP/E586-IPE

2. Highlight “Board Name” and press <Enter>. The

cursor will appear for you to type-in the name of the

board. After typing-in the board name, press

<Enter>.

3. Highlight “Manufacturer” and press <Enter>. The

cursor will appear for you to type-in the name of the

manufacturer. After typing-in the manufacturer’s

name, press <Enter>.

4. Highlight “Board Type” and press <Enter>. Select

the appropriate option for the board and press

<Enter>.

5. Highlight “Slot Type” and press <Enter>. Select the

slot type appropriate for the board and press <Enter>.

6. It is necessary to define an ISA board when you want

to prevent other boards in the system from using the

same IRQ levels, DMA channels, I/O Port address or

Memory address that your ISA board uses.

“DMA” allows you to define up to four (4) DMA

channels.

a. Select one of the DMA options and press

<Enter>. The ISA DMA Definition box similar

to the one shown on the next page will appear.

EISA Configuration Utility u 4-21

Page 68

EISA/PCI System Board

Board Name: WG-1200VL

Manufacturer: DFI

Board Type: Slot Type:

[Save=F10] [Load=F9] [New=F2] [Delete=F4] [Quit=ESC]

( )Video Board

( )Multifunction Board

( )Mass Storage Device

DMA

-

-

-

-

ISA Board Definition

ISA DMA Definition

[ ] [ ] 1

[ ] 2

[ ] 3

[ ] 4

[ ] 5

[ ] 6

[ ] 7

Size:

Timing:

-

-

-

-

-

-

-

-

[ ] Byte

[ ] Word

[ ] Default

[ ] Type A

[ ] Type B

Channel:

-

-

-

-

[Ok=ENTER] [Cancel=ESC] [Erase=F4]

-

-

-

( )16 bit

( )8 bit

( )8 or 16 bit

-

-

-

-

-

-

-

-

b. Move the cursor to the appropriate DMA channel,

size and timing of the ISA board, and press

<Enter>.

c. Choose OK to save the changes you have just

made.

d. Choose Erase to delete the previously saved DMA

definition.

e. Choose Cancel to return to the ISA Board

Definition box without saving the changes.

4-22 u EISA Configuration Utility

Page 69

E586-ICP/E586-IPE

7. “IRQ” allows you to define up to seven (7) IRQ

levels. Select one of the IRQ options and press

<Enter>.

a. An ISA IRQ Definition box similar to the one

shown below will appear.

Board Name: WG-1200VL

Manufacturer: DFI

Board Type: Slot Type:

[Save=F10] [Load=F9] [New=F2] [Delete=F4] [Quit=ESC]

( )Video Board

( )Multifunction Board

( )Mass Storage Device

DMA

-

-

-

-

ISA Board Definition

Level:

ISA IRQ Definition

Trigger:

[ ] [ ] 3

[ ] 4

[ ] 5

[ ] 6

[ ] 7

[ ] 9

[ ] 10

IRQ

[ ] 11

[ ] 12

-

[ ] 14

-

[ ] 15

-

-

-

[OK=ENTER] [Cancel=ESC] [Erase=F4]

-

-

[ ] Edge

[ ] Level

Ports Memory

-

-

-

-

-

-

-

-

( )16 bit

( )8 bit

( )8 or 16 bit

-

-

-

-

-

-

-

-

b. Select the appropriate IRQ level and type of

interrupt trigger to be used. Press <Enter>.

c. Choose OK to save the changes you have just

made.

d. Choose Erase to delete the previously saved IRQ

definition.

e. Choose Cancel to return to the ISA Board

Definition box without saving the changes.

EISA Configuration Utility u 4-23

Page 70

EISA/PCI System Board

8. “Ports” allows you to define up to eight (8) ranges of

I/O ports addresses.

a. Select one of the I/O Port options and press

<Enter>. The ISA Port Definition box similar to

the one shown below will appear.

Board Name: WG-1200VL

Manufacturer: DFI

Board Type: Slot Type:

[Save=F10] [Load=F9] [New=F2] [Delete=F4] [Quit=ESC]

( )Video Board

( )Multifunction Board

( )Mass Storage Device

DMA

[OK=ENTER] [Cancel=ESC] [Erase=F4]

-

-

-

-

ISA Board Definition

ISA Port Definition

Start:

End:

IRQ Ports Memory

-

-

-

-

-

-

-

Size:

[ ] Byte

h

0

0

[ ] Word

h

-

-

-

-

-

-

-

-

( )16 bit

( )8 bit

( )8 or 16 bit

-

-

-

-

-

-

-

-

b. Select the starting and ending port address and the

timing setting of the selected port address. Press

<Enter>.

c. Choose OK to save the changes you have just

made.

d. Choose Erase to delete the previously saved Port

definition.

e. Choose Cancel to return to the ISA Board

Definition box without saving the changes.

4-24 u EISA Configuration Utility

Page 71

E586-ICP/E586-IPE

9. “Memory” allows you to define up to eight (8)

memory addresses.

a. Select one of the Memory options and press

<Enter>. An ISA Memory Definition box similar

to the one shown below will appear.

Board Name: WG-1200VL

Manufacturer: DFI

Board Type: Slot Type:

[Save=F10] [Load=F9] [New=F2] [Delete=F4] [Quit=ESC]

( )Video Board

( )Multifunction Board

( )Mass Storage Device

Address:

DMA

-

-

-

-

ISA Board Definition

ISA Memory Definition

0 KB

Size:

0 h

[ ] RAM

IRQ Ports Memory

[ ] ROM

-

[ ] Don't Cache

-

[ ] Cache

-

-

-

[OK=ENTER] [Cancel=ESC] [Erase=F4]

-

-

Use:

Width:

-

Decode:

-

-

-

-

-

-

-

( )16 bit

[ ] System

( )8 bit

[ ] Expanded

( )8 or 16 bit

[ ] Other

[ ] Virtual

[ ] Byte

[ ] Word

-

[ ] 24 Bit

-

[ ] 20 Bit

-

-

-

-

-

-

b. Select the appropriate options in the ISA Memory

Definition box and press <Enter>.

c. Choose OK to save the changes you have just

made.

d. Choose Erase to delete the previously saved

Memory definition.

e. Choose Cancel to return to the ISA Board

Definition box without saving the changes.

EISA Configuration Utility u 4-25

Page 72

EISA/PCI System Board

10. After you have finished configuring the board,

choose Save to save the configuration in an ISA

CFG file.

11. Choose Load to edit a previously saved ISA CFG

file. A Load ISA Board Definition box will appear.

Highlight the ISA board to be edited and press

<Enter>.

12. Choose New to start a new ISA board configuration.

13. Choose Delete to remove an ISA board definition

from the ECU’s internal ISA board database. An

ISA Board Database box similar to the one shown

below will appear.

Board Name: WG-1200VL

Manufacturer: DFI

Board Type: Slot Type:

[Save=F10] [Load=F9] [New=F2] [Delete=F4] [Quit=ESC]

( )Video Board

( )Multifunction Board

Select the ISA board to delete or press <Esc> to exit.

( )Mass Storage Device

a

DMA

[ ] WG-1200VL

[Ok=ENTER] [Cancel=ESC]

IRQ Ports Memory

-

-

-

-

-

-

-

-

-

-

-

14. Quit returns you to the main menu without saving

any changes.

4-26 u EISA Configuration Utility

ISA Board Definition

ISA Board Database

-

-

-

-

-

-

-

-

( )16 bit

( )8 bit

( )8 or 16 bit

-

-

-

-

-

-

-

-

Page 73

v Troubleshooting Checklist

If you experience difficulty with the E586-ICP/E586-IPE

system board, please refer to the checklist below. If you

still cannot isolate the problem, please contact your

dealer.

1) Check the jumper settings to ensure that the jumpers

are properly set. If in doubt, refer to the “Board

Configuration” section.

2) Verify that all SIM modules are seated securely into

the bank sockets.

3) Make sure that the SIM modules are in the correct

locations.

4) Check that all populated memory banks are filled

with valid size HSIMMs.

5) If your board fails to function, place the board on a

flat surface and seat all socketed components (gently

press each component into the socket).

E586-ICP/E586-IPE

Troubleshooting Checklist u 5-1

Page 74

EISA/PCI System Board

v Appendix A: Types of Modules

The E586-ICP/E586-IPE system board allows you to

populate memory with 256Kx36, 512Kx36, 1Mx36,

2Mx36, 4Mx36 and 8Mx36 HSIM modules. The following modules have been tested with this board. Most

untested brands will work but a few may fail to do so.

For HSIM 256Kx36 Modules

Brand Chip Number

OKI M51C256A-70

For HSIM 512Kx36 Modules

Brand Chip Number

OKI M514256B-70J

For HSIM 1Mx36 Modules

Brand Chip Number

Toshiba TC511000AJL

OKI GT-1M*36B

Fujitsu 81C1000A-70

A-1 u Appendix A

Page 75

For HSIM 2Mx36 Modules

Brand Chip Number

OKI M511000B

For HSIM 4Mx36 Modules

Brand Chip Number

OKI M514100A-70S

For HSIM 8Mx36 Modules

Brand Chip Number

OKI M514100AL-70K

E586-ICP/E586-IPE

Appendix A u A-2

Page 76

EISA/PCI System Board

v Appendix B: System Error Report

POST (hex)

C0

1

2

3

4

Name

Turn off chipset

cache

Processor test 1

Processor test 2

Initialize chips

Test memory refresh

toggle

Description

OEM specific-cache control.

Processor status (1FLAGS) verification.

Test the following processor status flags

carry, zero, sign, overflow.

The BIOS will set each of these flags,

verify they are set, then turn each flag

off and verify it is off.

Read/Write/Verify all CPU registers

except SS,SP and BP with data pattern

FF and 00.

Disable NMI, PIE, AIE, UEI, SQWV.

Disable video, parity checking, DMA.

Reset math coprocessor.

Clear all page registers, CMOS

shutdown byte.

Initialize timer 0, 1 and 2, including set

EISA timer to a known state.

Initialize DMA controllers 0 and 1.

Initialize interrupt controllers 0 and 1.

Initialize EISA extended registers.

RAM must be periodically refreshed in

order to keep the memory from decaying.

This function assures that the memory

refresh function is working properly.

5

6

7

B-1 u Appendix B

Blank video, initialize

keyboard

Reserved

Test CMOS interface

and battery status

Keyboard controller initialization.

Verifies CMOS is working correctly,

detects bad battery.

Page 77

E586-ICP/E586-IPE

POST (hex)

BE

C1

C5

C6

8

9

A

B

Name

Chipset default

initialization

Memory presence

test

Early shadow

Cache presence

test

Setup low memory

Early cache

initialization

Setup interrupt

vector table

Test CMOS RAM

checksum

Description

Program chipset registers with power on

BIOS defaults.

OEM Specific-Test to size on-board

memory.

OEM Specific-Early Shadow enable for

fast boot.

External cache size detection.

Early chip set initialization.

Memory presence test.

OEM chip set routines.

Clear low 64K of memory.

Test first 64K memory.

Cyrix CPU initialization.

Cache initialization.

Initialize first 120 interrupt vectors with

SPURIOUS_INT_HDLR and initialize

INT 00h-1Fh according to INT_TBL.

Test CMOS RAM checksum, if bad, or

insert key pressed, load defaults.

C

D

E

Initialize keyboard

Initialize video

interface

Test video

memory

Detect type of keyboard controller

(optional).

Set NUM_LOCK status.

Detect CPU clock.

Read CMOS location 14h to find out

type of video in use.

Detect and initialize video adapter.

Test video memory, write sign-on

message to screen.

Setup shadow RAM - Enable shadow

according to Setup.

Appendix B u B-2

Page 78

EISA/PCI System Board

POST (hex)

F

10

11

12-13

14

15

16

17

18

Name

Test DMA

controller 0

Test DMA

controller 1

Test DMA page

registers

Reserved