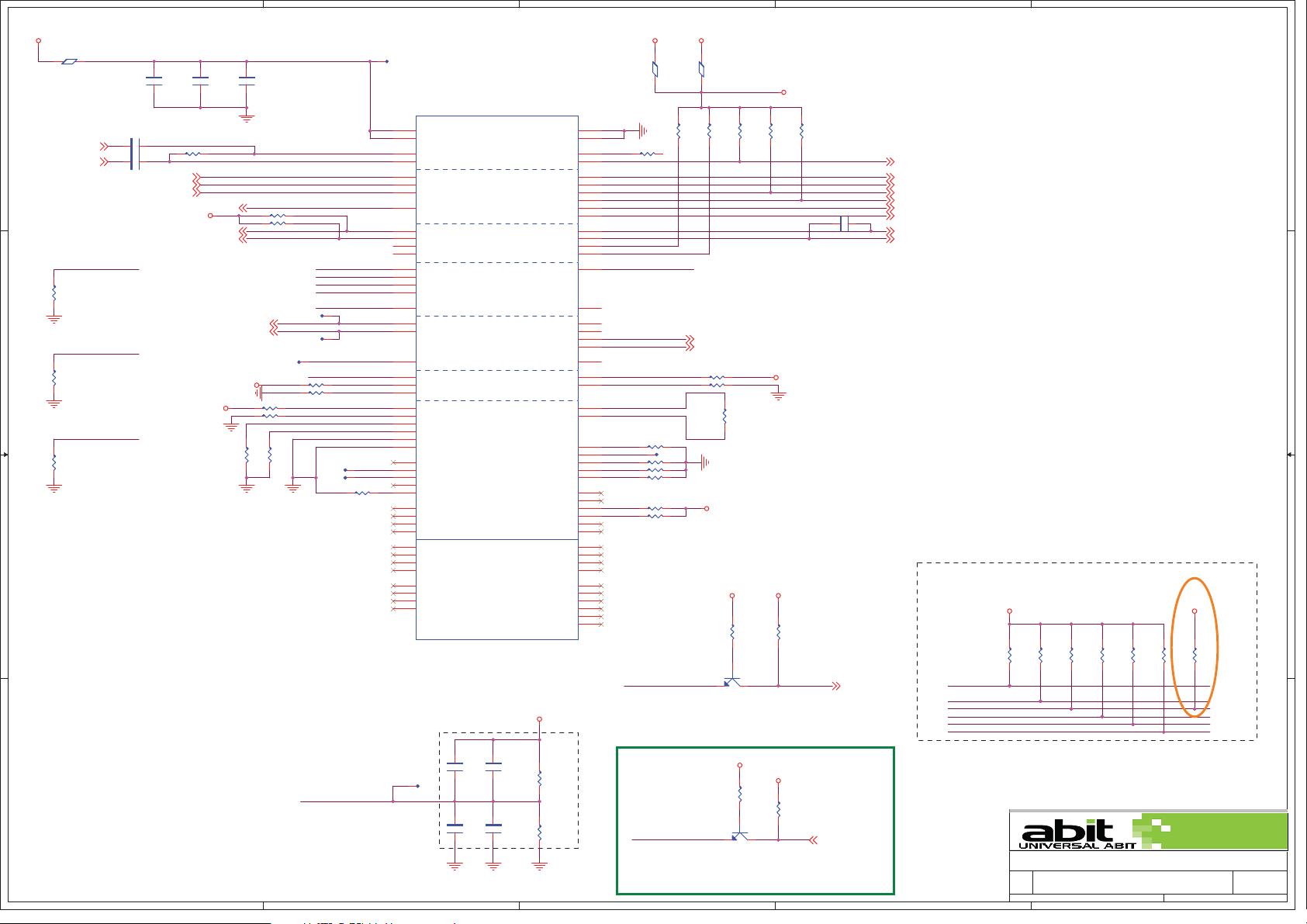

Desktop Motherboard AX78 Schematics

5

4

3

2

1

AX78 V0.2 SCHEMATICS

D D

C C

B B

TITLE

SYSTEM BLOCK DIAGRAM

POWER DISTRIBUTION

K8 CPU

DDR2 DIMM SOCKET

AMD RX780

CLOCK GEN.

PCI-E X16

PCI-E x4/x1

AMD SB600

PCI SLOT 1,2,3

SATAII 1-4 and IDE & AK2001

LPC I/O W83627DHG

FPIO , FWH , SMB ,FDC , ATX

KB , MS & FP-USB 1,2,3

HD-AUDIO ALC888

PCIE GbE LAN

FAN & HW MONITOR

PWM ISL6323 & ISL6613

W83304CG

MECHANCAL

SHEET

2

3

4~8

9~12

13~15

16

17

18

19~22

23

24

25

26

27

28

29

30

31~32

33~34

35

A A

5

4

http://laptop-motherboard-schematic.blogspot.com/

3

Title

INDEX

Size Document Number Re v

Custom

2

Date: Sheet

AX78

1

0.2

of

135Tuesday, August 28, 2007

5

4

3

2

1

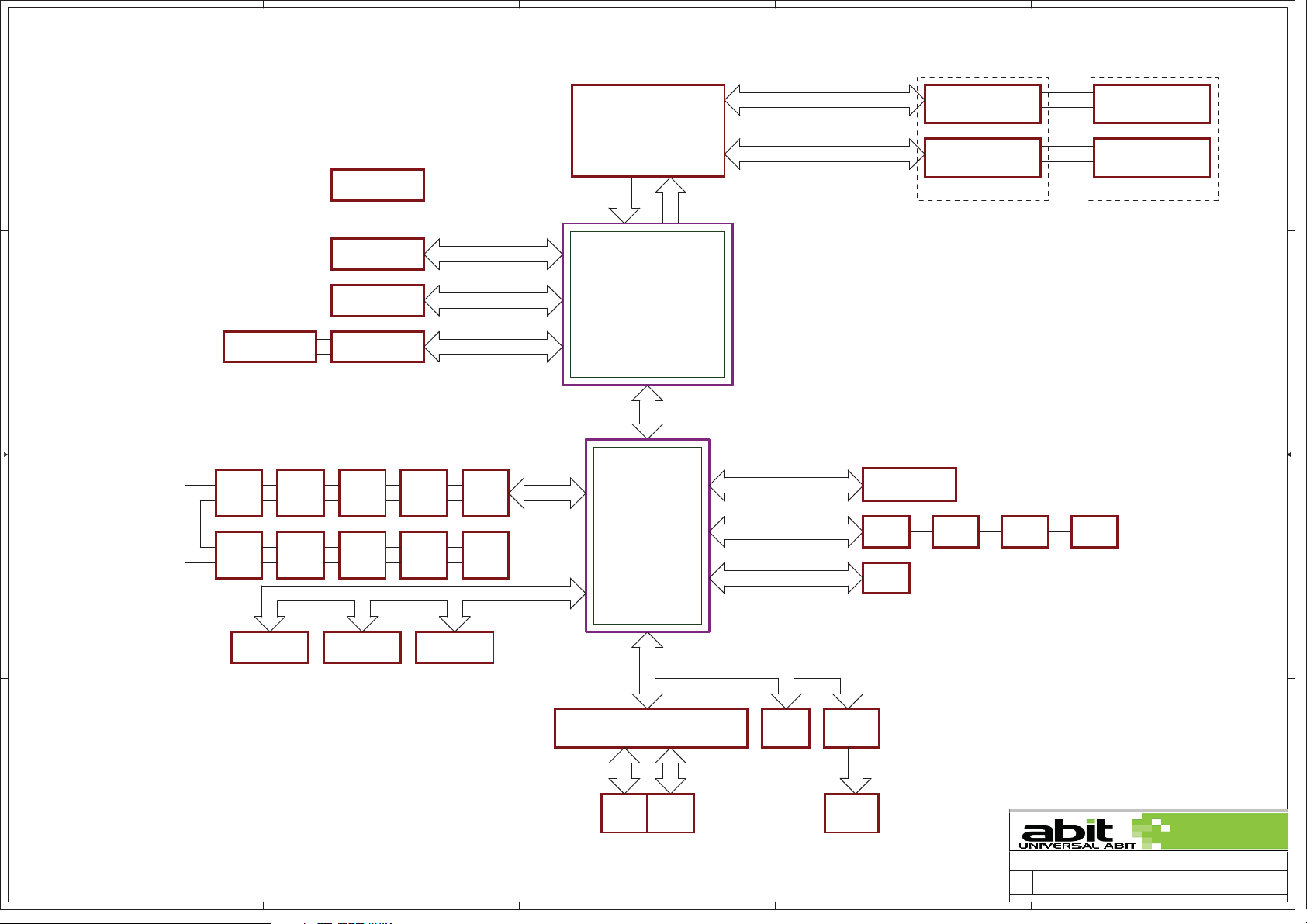

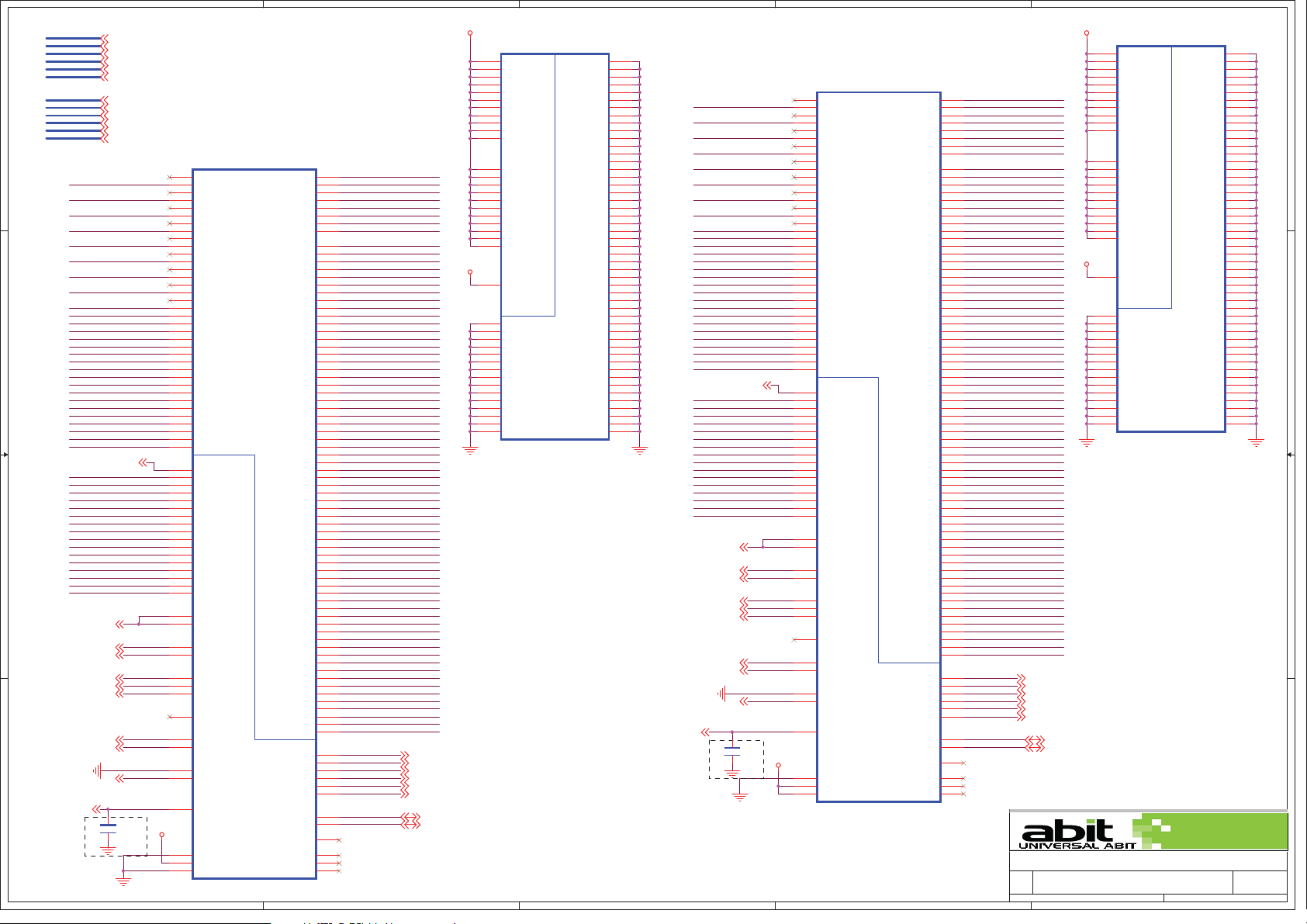

U-ABIT AX78 BLOCK DIAGRAM

''5,,

LINK

AMD

AM2/AM2g2

M2 SOCKET

OUT

IN

ATI NB

RX780

128bit

''5,,

16x16

D D

([WH UQDO&ORFN*HQHU DWRU

,&6/356

3&,(;6/27

3&,(;6/27

C C

3&,(;6/27

0$59(//

(

;

;3&,(,17(5)$&(

3&,(;,17(5)$&(

HyperTransport

81%8))(5('''5,,

',00

81%8))( 5('''5,,

',00

DDRII FIRST LOGICAL DIMM DDRII SECOND LOGI CAL DIMM

81%8))( 5('''5,,

',00

81%8))( 5('''5,,

',00

A-Link

;3&,(

A-Link

86%86%86%86%

86%

86%

ATI SB

SB600

86%86% 86% 86%86%

B B

PCI BUS

+'$8',2, )

6$7$,,,)

$7$,)

5HDO7HN

$/&

&+

6$7$ 6$7$ 6$7$ 6$7$

,'(

3&,6/27

A A

5

3&,6/27 3&,6/27

4

/3&%86

:'+*

http://laptop-motherboard-schematic.blogspot.com/

)/233<

.%'

0286(

3

)/$6+

%,26

$.

/('

',63/$<

Title

BLOCK_DIAGRAM

Size Document Number Re v

Custom

2

Date: Sheet

AX78

1

0.2

of

235Tuesday, August 28, 2007

5

4

3

2

1

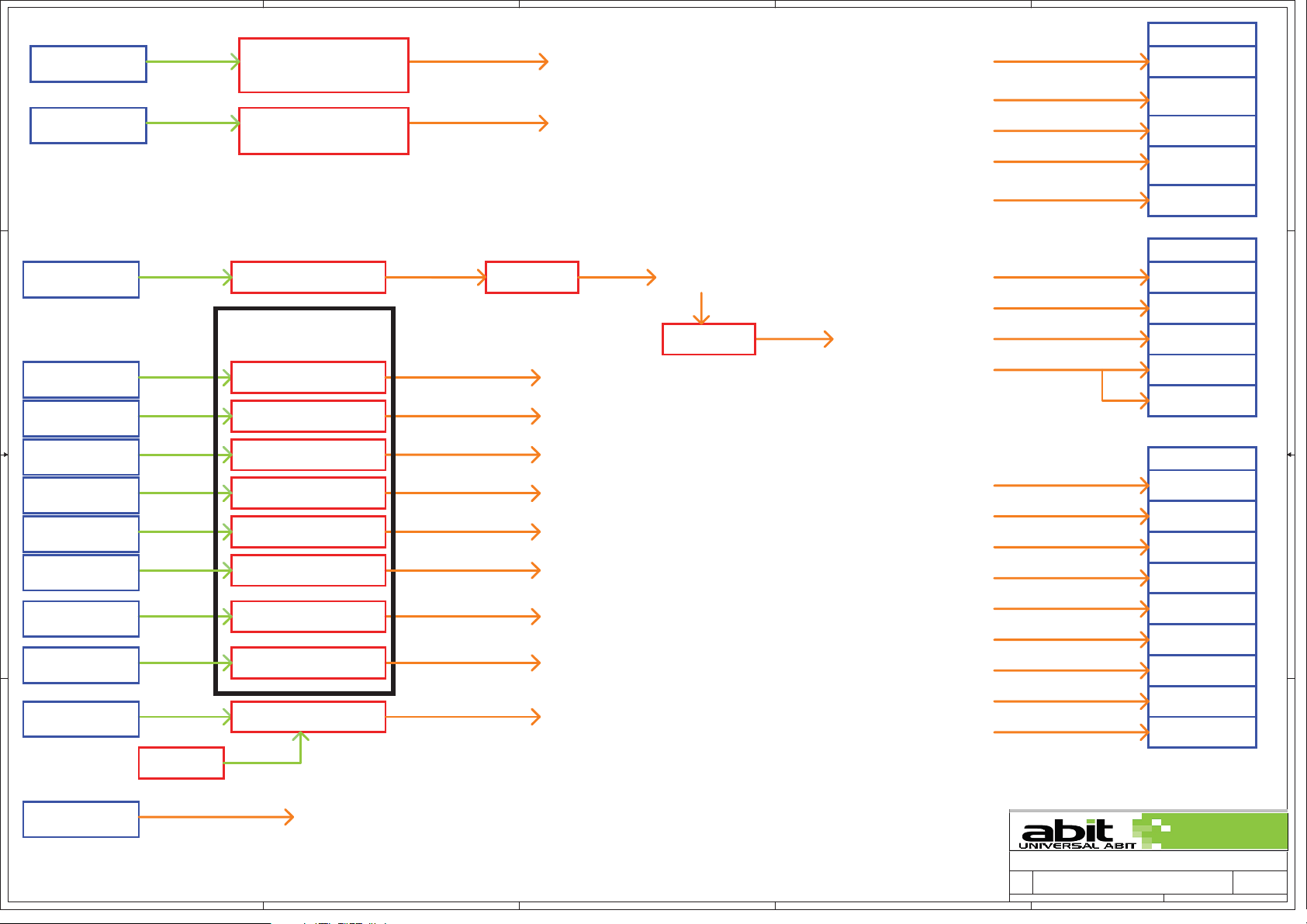

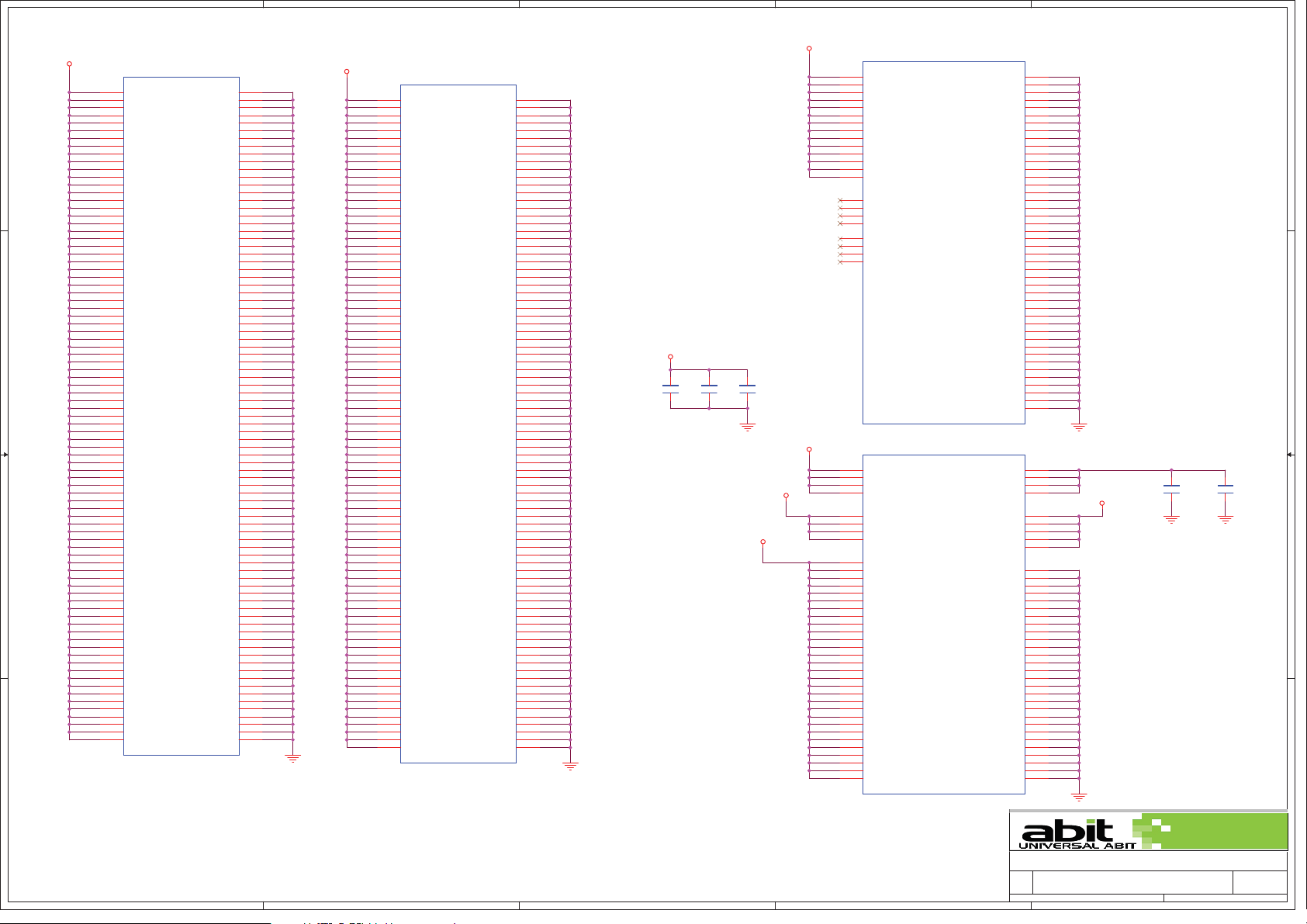

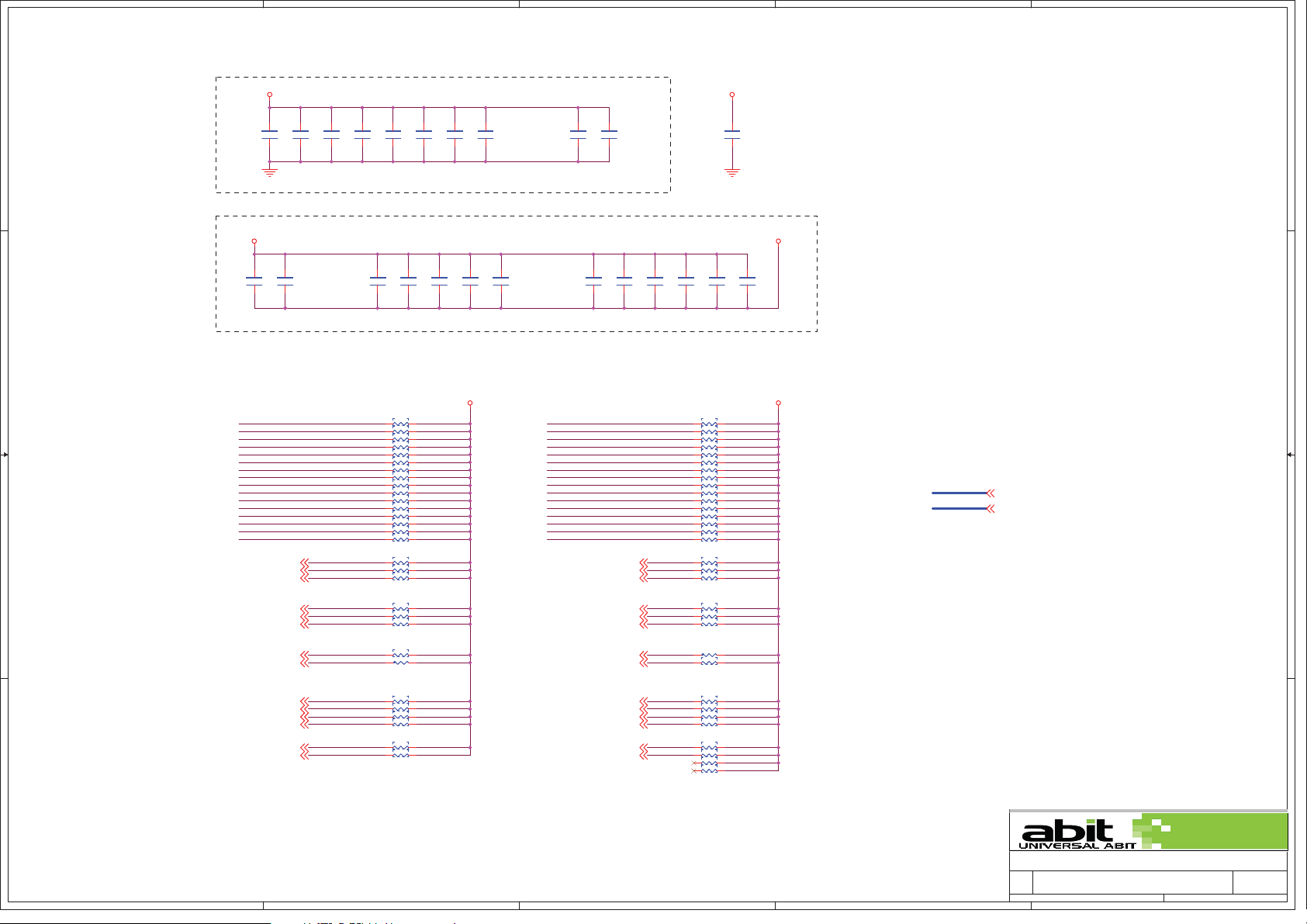

VCORE PWM

+12V

ISL6323 and

ISL6612A

D D

VCC5

W83304CG

VCCP 95A+VCCP_NB 20A

0.8~1.55V

V2P5_VDDA

2.5V

VCCP

V2P5_VDDA

VDDMEM

VTTMEM

V1P2_LDT

AMD M2 CPU

VDDCORE

default

95A+20A

VDDA

2.5V 0.2A

VDDIO

1.8V 10A

VTT

0.9V 2A

VLDT

1.2V 0.5A

W83304CG

NB RX780

3VDUAL

C C

VCC3

3VDUAL

VCC3

VCCP

VCC5SB/VCC

B B

VCC3

VCC5SB/VCC3

VCC3

VCC3

VDDIO_DRV

LR1_DRV

LR2_DRV

VLDT_DRV

LR4_DRV

5VSB_DRV

LR3_DRV

3.3VSB_DRV

VAGP_DRV

W83320SG

DDR_VREF

83320DS

V1P8 1.5A

V1P2_DUAL

V1P2_LDT

VCCP OVP

5VDUAL

V1P1_VREF

3VDUAL

V1P2_SB

V1P1_NB

0.42A

1.3A

12A

VDDMEM

83310DS

10A

VTTMEM

2A

V1P2_LDT

1P1_PCIE

V1P1_NB

V1P8

1P2_SB

1P2_SB

1P2_SB

1P2_SB

1P2_SB

VCC3

3VDUAL

V1P2_DUAL

V1P2_DUAL

VDDHT

1.2V 0.5A

PCI-E CORE

1.1V 3A

NB CORE

1.1V 3A

NB 1.8V

1.8V 0.6A

PCI-E VDDA18

1.8V 0.9A

SB SB600

X4 PCI -E

1.2V 0.8A

SATA I/O

1.2V 0.2A

SATA PLL

1.2V 0.01A

PCI-E PVDD

1.2V 80mA

SB CORE

1.2V 0.6A

3.3V I/O

3.3V 0.45A

3.3V S5 PW

3.3V 0.01A

USB CORE I/O

1.2V 0.2A

1.2V S5 PW

1.2V 0.22A

V1P1_VREF

A A

V1P1_NB

5

V1P1_PCIE 1.1V 3A

4

http://laptop-motherboard-schematic.blogspot.com/

3

Title

POWER DISTRIBUTION

Size Document Number Re v

Custom

2

Date: Sheet

AX78

1

0.2

of

335Tuesday, August 28, 2007

5

4

3

2

1

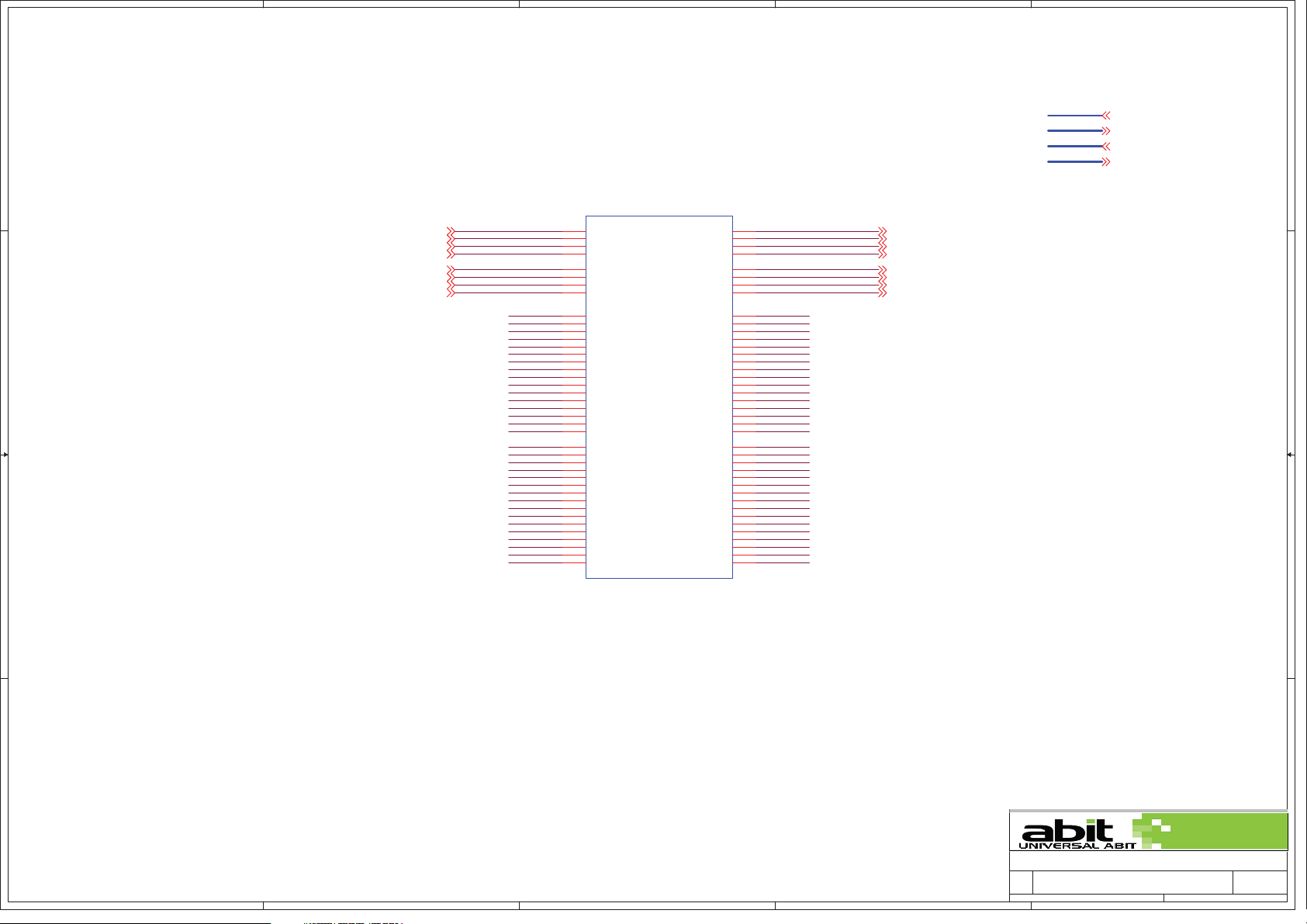

D D

RXCLKP113

RXCLKN113

RXCLKP013

RXCLKN013

RXCTLP113

RXCTLN113

RXCTLP013

RXCTLN013

C C

B B

RXCLKP1

RXCLKN1

RXCLKP0

RXCLKN0

RXCTLP1

RXCTLN1

RXCTLP0

RXCTLN0

RXCADP15

RXCADN15

RXCADP14

RXCADN14

RXCADP13

RXCADN13

RXCADP12

RXCADN12

RXCADP11

RXCADN11

RXCADP10

RXCADN10

RXCADP9

RXCADN9

RXCADP8

RXCADN8

RXCADP7

RXCADN7

RXCADP6

RXCADN6

RXCADP5

RXCADN5

RXCADP4

RXCADN4

RXCADP3

RXCADN3

RXCADP2

RXCADN2

RXCADP1

RXCADN1

RXCADP0

RXCADN0

U3A

N6

L0_CLKIN_H1

P6

L0_CLKIN_L1

N3

L0_CLKIN_H0

N2

L0_CLKIN_L0

V4

L0_CTLIN_H1

V5

L0_CTLIN_L1

U1

L0_CTLIN_H0

V1

L0_CTLIN_L0

U6

L0_CADIN_H15

V6

L0_CADIN_L15

T4

L0_CADIN_H14

T5

L0_CADIN_L14

R6

L0_CADIN_H13

T6

L0_CADIN_L13

P4

L0_CADIN_H12

P5

L0_CADIN_L12

M4

L0_CADIN_H11

M5

L0_CADIN_L11

L6

L0_CADIN_H10

M6

L0_CADIN_L10

K4

L0_CADIN_H9

K5

L0_CADIN_L9

J6

L0_CADIN_H8

K6

L0_CADIN_L8

U3

L0_CADIN_H7

U2

L0_CADIN_L7

R1

L0_CADIN_H6

T1

L0_CADIN_L6

R3

L0_CADIN_H5

R2

L0_CADIN_L5

N1

L0_CADIN_H4

P1

L0_CADIN_L4

L1

L0_CADIN_H3

M1

L0_CADIN_L3

L3

L0_CADIN_H2

L2

L0_CADIN_L2

J1

L0_CADIN_H1

K1

L0_CADIN_L1

J3

L0_CADIN_H0

J2

L0_CADIN_L0

AM2+

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

HT LINK

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

TXCADP15

TXCADN15

TXCADP14

TXCADN14

TXCADP13

TXCADN13

TXCADP12

TXCADN12

TXCADP11

TXCADN11

TXCADP10

TXCADN10

TXCADP9

TXCADN9

TXCADP8

TXCADN8

TXCADP7

TXCADN7

TXCADP6

TXCADN6

TXCADP5

TXCADN5

TXCADP4

TXCADN4

TXCADP3

TXCADN3

TXCADP2

TXCADN2

TXCADP1

TXCADN1

TXCADP0

TXCADN0

TXCLKP1

TXCLKN1

TXCLKP0

TXCLKN0

TXCTLP1

TXCTLN1

TXCTLP0

TXCTLN0

TXCLKP1 13

TXCLKN1 13

TXCLKP0 13

TXCLKN0 13

TXCTLP1 1 3

TXCTLN1 13

TXCTLP0 1 3

TXCTLN0 13

TXCADP[15..0] 13

RXCADP[15..0] 13

TXCADN[15..0] 13

RXCADN[15..0] 13

A A

5

4

http://laptop-motherboard-schematic.blogspot.com/

3

Title

K8 CPU-HTT

Size Document Number Re v

Custom

2

Date: Sheet

AX78

1

0.2

of

435Tuesday, August 28, 2007

5

U3B

MEM_A0_CLK29,12

D D

C C

B B

A A

MEM_A0_CLK*29,12

MEM_A1_CLK210,12

MEM_A1_CLK*210,12

MEM_A0_CLK09,12

MEM_A0_CLK*09,12

MEM_A1_CLK010,12

MEM_A1_CLK*010,12

MEM_A0_CLK19,12

MEM_A0_CLK*19,12

MEM_A1_CLK110,12

MEM_A1_CLK*110,12

MEM_A0_CS*19,11

MEM_A0_CS*09,11

MEM_A0_ODT9,11

MEM_A1_CS*110,11

MEM_A1_CS*010,11

MEM_A1_ODT10,11

MEM_A_CAS*9,10,11,12

MEM_A_W E*9,10,11,12

MEM_A_RAS*9,10,11,12

MEM_A_BA29,10,11,12

MEM_A_BA19,10,11,12

MEM_A_BA09,10,11,12

MEM_A1_CK E10,11

MEM_A0_CK E9,11

MEM_A_ADD15

MEM_A_ADD14

MEM_A_ADD13

MEM_A_ADD12

MEM_A_ADD11

MEM_A_ADD10

MEM_A_ADD9

MEM_A_ADD8

MEM_A_ADD7

MEM_A_ADD6

MEM_A_ADD5

MEM_A_ADD4

MEM_A_ADD3

MEM_A_ADD2

MEM_A_ADD1

MEM_A_ADD0

MEM_A_DQS 7

MEM_A_DQS*7

MEM_A_DQS 6

MEM_A_DQS*6 MEM_A_DQS 8

MEM_A_DQS 5

MEM_A_DQS*5

MEM_A_DQS 4

MEM_A_DQS*4

MEM_A_DQS 3

MEM_A_DQS*3

MEM_A_DQS 2

MEM_A_DQS*2

MEM_A_DQS 1

MEM_A_DQS*1

MEM_A_DQS 0

MEM_A_DQS*0

MEM_A_DM7

MEM_A_DM6

MEM_A_DM5

MEM_A_DM4

MEM_A_DM3

MEM_A_DM2

MEM_A_DM1

MEM_A_DM0

AG21

AG20

AE20

AE19

U27

U26

V27

W27

W26

W25

U24

V24

G19

H19

G20

G21

AC25

AA24

AE28

AC28

AD27

AA25

AE27

AC27

E20

AB25

AB27

AA26

N25

Y27

AA27

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

U25

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

G15

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

L27

T25

T27

F19

F15

MA_CLK_H7

MA_CLK_L7

MA_CLK_H6

MA_CLK_L6

MA_CLK_H5

MA_CLK_L5

MA_CLK_H4

MA_CLK_L4

MA_CLK_H3

MA_CLK_L3

MA_CLK_H2

MA_CLK_L2

MA_CLK_H1

MA_CLK_L1

MA_CLK_H0

MA_CLK_L0

MA0_CS_L1

MA0_CS_L0

MA0_ODT1

MA0_ODT0

MA1_CS_L1

MA1_CS_L0

MA1_ODT1

MA1_ODT0

MA_RESET_L

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

AM2+

MEM CHA

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DQS_H8

MA_DQS_L8

MA_DM8

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

4

MEM_A_DATA63

AE14

MEM_A_DATA62

AG14

MEM_A_DATA61

AG16

MEM_A_DATA60

AD17

MEM_A_DATA59

AD13

MEM_A_DATA58

AE13

MEM_A_DATA57

AG15

MEM_A_DATA56

AE16

MEM_A_DATA55

AG17

MEM_A_DATA54

AE18

MEM_A_DATA53

AD21

MEM_A_DATA52

AG22

MEM_A_DATA51

AE17

MEM_A_DATA50

AF17

MEM_A_DATA49

AF21

MEM_A_DATA48

AE21

MEM_A_DATA47

AF23

MEM_A_DATA46

AE23

MEM_A_DATA45

AJ26

MEM_A_DATA44

AG26

MEM_A_DATA43

AE22

MEM_A_DATA42

AG23

MEM_A_DATA41

AH25

MEM_A_DATA40

AF25

MEM_A_DATA39

AJ28

MEM_A_DATA38

AJ29

MEM_A_DATA37

AF29

MEM_A_DATA36

AE26

MEM_A_DATA35

AJ27

MEM_A_DATA34

AH27

MEM_A_DATA33

AG29

MEM_A_DATA32

AF27

MEM_A_DATA31

E29

MEM_A_DATA30

E28

MEM_A_DATA29

D27

MEM_A_DATA28

C27

MEM_A_DATA27

G26

MEM_A_DATA26

F27

MEM_A_DATA25

C28

MEM_A_DATA24

E27

MEM_A_DATA23

F25

MEM_A_DATA22

E25

MEM_A_DATA21

E23

MEM_A_DATA20

D23

MEM_A_DATA19

E26

MEM_A_DATA18

C26

MEM_A_DATA17

G23

MEM_A_DATA16

F23

MEM_A_DATA15

E22

MEM_A_DATA14

E21

MEM_A_DATA13

F17

MEM_A_DATA12

G17

MEM_A_DATA11

G22

MEM_A_DATA10

F21

MEM_A_DATA9

G18

MEM_A_DATA8

E17

MEM_A_DATA7

G16

MEM_A_DATA6

E15

MEM_A_DATA5

G13

MEM_A_DATA4

H13

MEM_A_DATA3

H17

MEM_A_DATA2

E16

MEM_A_DATA1

E14

MEM_A_DATA0

G14

J28

MEM_A_DQS*8

J27

MEM_A_DM8

J25

MEM_A_ECC7

K25

MEM_A_ECC6

J26

MEM_A_ECC5

G28

MEM_A_ECC4

G27

MEM_A_ECC3

L24

MEM_A_ECC2

K27

MEM_A_ECC1

H29

MEM_A_ECC0

H27

http://laptop-motherboard-schematic.blogspot.com/

3

U3C

MEM_B0_CLK29,12

MEM_B0_CLK*29,12

MEM_B1_CLK210,12

MEM_B1_CLK*210,12

MEM_B0_CLK09,12

MEM_B0_CLK*09,12

MEM_B1_CLK010,12

MEM_B1_CLK*010,12

MEM_B0_CLK19,12

MEM_B0_CLK*19,12

MEM_B1_CLK110,12

MEM_B1_CLK*110,12

MEM_B0_CS*19,11

MEM_B0_CS*09,11

MEM_B0_ODT9,11

MEM_B1_CS*110,11

MEM_B1_CS*010,11

MEM_B1_ODT10,11

MEM_B_CAS*9,10,11,12

MEM_B_W E*9,10,11,12

MEM_B_RAS*9,10,11,12

MEM_B_BA29,10,11,12

MEM_B_BA19,10,11,12

MEM_B_BA09,10,11,12

MEM_B1_CKE10,11

MEM_B0_CKE9,11

MEM_B_ADD15

MEM_B_ADD14

MEM_B_ADD13

MEM_B_ADD12

MEM_B_ADD11

MEM_B_ADD10

MEM_B_ADD9

MEM_B_ADD8

MEM_B_ADD7

MEM_B_ADD6

MEM_B_ADD5

MEM_B_ADD4

MEM_B_ADD3

MEM_B_ADD2

MEM_B_ADD1

MEM_B_ADD0

MEM_B_DQS 7

MEM_B_DQS*7

MEM_B_DQS 6

MEM_B_DQS 5

MEM_B_DQS*5

MEM_B_DQS 4

MEM_B_DQS*4

MEM_B_DQS 3

MEM_B_DQS*3

MEM_B_DQS 2

MEM_B_DQS*2

MEM_B_DQS 1

MEM_B_DQS*1

MEM_B_DQS 0

MEM_B_DQS*0

MEM_B_DM7

MEM_B_DM6

MEM_B_DM5

MEM_B_DM4

MEM_B_DM3

MEM_B_DM2

MEM_B_DM1

MEM_B_DM0

AJ19

AK19

AL19

AL18

U31

U30

W29

W28

Y31

Y30

V31

W31

A18

A19

C19

D19

AE30

AC31

AF31

AD29

AE29

AB31

AG31

AD31

B19

AC29

AC30

AB29

N31

AA31

AA28

M31

M29

N28

N29

AE31

N30

P29

AA29

P31

R29

R28

R31

R30

T31

T29

U29

U28

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

D31

C31

C24

C23

D17

C17

C14

C13

AJ14

AH17

AJ23

AK29

C30

A23

B17

B13

MB_CLK_H7

MB_CLK_L7

MB_CLK_H6

MB_CLK_L6

MB_CLK_H5

MB_CLK_L5

MB_CLK_H4

MB_CLK_L4

MB_CLK_H3

MB_CLK_L3

MB_CLK_H2

MB_CLK_L2

MB_CLK_H1

MB_CLK_L1

MB_CLK_H0

MB_CLK_L0

MB0_CS_L1

MB0_CS_L0

MB0_ODT1

MB0_ODT0

MB1_CS_L1

MB1_CS_L0

MB1_ODT1

MB1_ODT0

MB_RESET_L

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK2

MB_BANK1

MB_BANK0

MB_CKE1

MB_CKE0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

AM2+

MEM CHB

2

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DQS_H8

MB_DQS_L8

MB_DM8

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_B_DATA63

MEM_B_DATA62

MEM_B_DATA61

MEM_B_DATA60

MEM_B_DATA59

MEM_B_DATA58

MEM_B_DATA57

MEM_B_DATA56

MEM_B_DATA55

MEM_B_DATA54

MEM_B_DATA53

MEM_B_DATA52

MEM_B_DATA51

MEM_B_DATA50

MEM_B_DATA49

MEM_B_DATA48

MEM_B_DATA47

MEM_B_DATA46

MEM_B_DATA45

MEM_B_DATA44

MEM_B_DATA43

MEM_B_DATA42

MEM_B_DATA41

MEM_B_DATA40

MEM_B_DATA39

MEM_B_DATA38

MEM_B_DATA37

MEM_B_DATA36

MEM_B_DATA35

MEM_B_DATA34

MEM_B_DATA33

MEM_B_DATA32

MEM_B_DATA31

MEM_B_DATA30

MEM_B_DATA29

MEM_B_DATA28

MEM_B_DATA27

MEM_B_DATA26

MEM_B_DATA25

MEM_B_DATA24

MEM_B_DATA23

MEM_B_DATA22

MEM_B_DATA21

MEM_B_DATA20

MEM_B_DATA19

MEM_B_DATA18

MEM_B_DATA17

MEM_B_DATA16

MEM_B_DATA15

MEM_B_DATA14

MEM_B_DATA13

MEM_B_DATA12

MEM_B_DATA11

MEM_B_DATA10

MEM_B_DATA9

MEM_B_DATA8

MEM_B_DATA7

MEM_B_DATA6

MEM_B_DATA5

MEM_B_DATA4

MEM_B_DATA3

MEM_B_DATA2

MEM_B_DATA1

MEM_B_DATA0

MEM_B_DQS 8MEM_B_DQS*6

MEM_B_DQS*8

MEM_B_DM8

MEM_B_ECC7

MEM_B_ECC6

MEM_B_ECC5

MEM_B_ECC4

MEM_B_ECC3

MEM_B_ECC2

MEM_B_ECC1

MEM_B_ECC0

1

MEM_A_ECC[0..7] 9,10

MEM_A_DATA[63..0] 9,10

MEM_A_DM[0..8] 9,10

MEM_A_DQS[0..8] 9,10

MEM_A_DQS*[0..8] 9,10

MEM_A_ADD[15..0] 9,10,11,12

MEM_B_ECC[0..7] 9,10

MEM_B_DATA[63..0] 9,10

MEM_B_DM[0..8] 9,10

MEM_B_DQS[0..8] 9,10

MEM_B_DQS*[0..8] 9,10

MEM_B_ ADD[15..0] 9,10 ,11,12

Title

K8 CPU-DDR2

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

AX78

1

0.2

of

535Tuesday, August 28, 2007

5

4

3

2

1

V2P5_VDDA VDDMEMV1P8_DUAL

L0805

FB2 31OHM

D D

CK_CPU_P16

CK_CPU_N16

0402

R62

X10K

C C

0402

R66

X10K

0402

R65

X10K

B B

V2P5_VDDA_B

C68 3900PF

X7R 16V

C71 3900PF

X7R 16V

CPU_HTTRESET#

CPU_HTTPWROK

CPU_HTTSTOP#

0603

0603

0603

CPU_HTTPWROK22

CPU_HTTSTOP#22

CPU_HTTRESET#22

C60

0805

0.22UF

Y5V

16V

0603-1%

R73 169

CPU_HTTPWROK

CPU_HTTSTOP#

CPU_HTTRESET#

CPU_PRESENT#30

V1P8_CPU

CPU_SIC19

CPU_SID19

V1P8_CPU

C61

4.7UF

Y5V

10V

CLKIN+

VDDMEM

C64

0603

3900PF

X7R

16V

0402

R249

0402

R266

COREFB+31

COREFB-31

0603-1%

R71 511

0603-1%

R72 511

0603

0603

R70

330

1K

1K

A

B

H

0603-1%

R108 40.2

0603-1%

R106 40.2

R67

330

CLKIN-

CPU_TDI

CPU_TRST#

CPU_TCK

CPU_TMS

CPU_DBREQ#

MEM_CPU_VREF

TP18

TP17

0402

R109

K

L0805

FB5

31OHM

L0805

FB6

X31OHM

V1P8_CPU

U3D

C10

VDDA_1

D10

VDDA_2

A8

CLKIN_H

B8

CLKIN_L

C9

PWROK

D8

LDTSTOP_L

C7

RESET_L

AL3

CPU_PRESENT_L

AL6

SIC

AK6

SID

AK4

SA0

AL4

ALERT_L

AL10

TDI

AJ10

TRST_L

AH10

TCK

AL9

TMS

A5

DBREQ_L

G2

VDD_FB_H

G1

VDD_FB_L

E12

VTT_SENSE

F12

M_VREF

AH11

M_ZN

AJ11

M_ZP

A10

TEST25_H

B10

TEST25_L

F10

TEST19

E9

TEST18

AJ7

TEST13

F6

TEST9

D6

TEST17

E7

TEST16

F8

TEST15

C5

AH9

AJ5

AH7

AJ6

AD25

AE24

AE25

AJ18

AJ20

AK3

C18

C20

TEST14

TEST12

E5

TEST7

TEST6

TEST3

TEST2

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD9

RSVD10

1K

MISC.

PLATFORM_TYPE

CORE_TYPE

PVIEN/VID1

THERMTRIP_L

PROCHOT_L

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

INT. MISC.

KEY/VSS1

KEY/VSS2

VID5

VID4

SVC/VID3

SVD/VID2

VID0

THERMDC

THERMDA

TDO

DBRDY

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

H22

AE9

F2

G5

D2

D1

C1

E3

E2

E1

AG9

AG8

AK7

AL7

AK10

B6

AK11

AL11

G4

G3

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

L30

L31

V29

W30

F3

G24

G25

H25

L25

L26

R82

VID5

VID4

SVC

SVD

PVEN

VID0

THERMTRIPJ

CPU_PROCHOT#

CPU_TDO

FBCLKOUT-

R76

R79

R107 330

R81

R75 X330

R119 330

0402

0402

0402

0603

0402

0603

0603

X0

0603

R120

330

R110 44.2

R83 44.2

1K

TP16

1K

1K

VDDNBFB+ 31

VDDNBFB- 31

AM2+

THERMTRIPJ

VDDMEM

0603

R114

330

0603-1%

0603-1%

0603-1%

V1P8_CPU

V1P8_CPU

SOT23

E C

Q64

MMBT3904LT1

200mA

40V

0603

R137

330

R74

80.6

0402

R334

1K

B

0402

0402

R48

R47

1K

1K

CORE_T YPE 25,32

PWM_VID5 31

PWM_VID4 31

PWM_SVC 31

PWM_SVD 31

PWM_PVEN 31,32

C186 X3300PF

X7R 16V

0603

PWM_VID0 31

THRMDC 25,30

THRMDA 25,30

V1P2_LDT

LAYOUT: Route FBCLKOUT_H/L

differentially with 20/8/5/8/20

spacing and trace width.

PLACE WITHIN 0.5 INCH OF CPU

3VDUAL

0402

R328

10K

THERMTRIP# 21

CPU_DBREQ#

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

V1P8_CPU

0603

R113

X220

0603

R121

X220

HDT CONNECTOR

0603

0603

R122

R115

X220

X220

V0.2

VDDMEM

0603

0603

R116

X220

R123

X220

0603

R514

X220

C628

C629

0603

0603

0.1UF

L

Y5V

0603

16V

C626

0.1UF

Y5V

16V

0603

A A

MEM_CPU_VREF

1000PF

X7R

16V

C627

1000PF

X7R

16V

0603-1%

R508

100

http://laptop-motherboard-schematic.blogspot.com/

0603-1%

R507

100

CPU_PROCHOT#

SOLDER SIDE

5

4

3

V1P8_CPU

0402

SOT23

B

E C

Q16

MMBT3904LT1

200mA

40V

R68

10K

3VDUAL

0402

R69

4.7K

VREG_PROCHOT# 21

Title

K8 CPU-CTR & TP

Size Document Number Re v

Custom

2

Date: Sheet

AX78

1

0.2

of

635Tuesday, August 28, 2007

5

4

3

2

1

C168

0.1UF

Y5V

16V

VDDMEM

VTTMEM

VCCP_NB

V1P2_LDT

E10

F11

G10

G12

H20

H21

AD18

AD19

AE7

AE8

AJ1

AJ2

AJ3

AJ4

A12

B12

C12

D12

M24

M26

M28

M30

P24

P26

P28

P30

T24

T26

T28

T30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

A4

A6

B5

B7

C6

C8

D7

D9

E8

F9

H3

H4

U3G

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDNB_6

VDDNB_7

VDDNB_8

VDDNB_9

VDDNB_10

VDDNB_11

VDDNB_12

VDDNB_13

VDDNB_14

NC1

NC2

NC3

NC4

NC6

NC7

NC8

NC9

AM2+

U3H

VLDT_A_1

VLDT_A_2

VLDT_A_3

VLDT_A_4

VTT_1

VTT_2

VTT_3

VTT_4

VDDIO_1

VDDIO_2

VDDIO_3

VDDIO_4

VDDIO_5

VDDIO_6

VDDIO_7

VDDIO_8

VDDIO_9

VDDIO_10

VDDIO_11

VDDIO_12

VDDIO_13

VDDIO_14

VDDIO_15

VDDIO_16

VDDIO_17

VDDIO_18

VDDIO_19

VDDIO_20

VDDIO_21

VDDIO_22

VDDIO_23

VDDIO_24

VDDIO_25

VDDIO_26

VDDIO_27

VDDIO_28

VDDIO_29

AM2+

AA11

VSS_171

AA13

VSS_172

AA15

VSS_173

AA17

VSS_174

AA19

VSS_175

AA21

VSS_176

AA23

VSS_177

AB2

VSS_178

AB3

VSS_179

AB8

VSS_180

AB10

VSS_181

AB12

VSS_182

AB14

VSS_183

AB16

VSS_184

AB18

VSS_185

AB20

VSS_186

AB22

VSS_187

AC7

VSS_188

AC9

VSS_189

AC11

VSS_190

AC13

VSS_191

AC15

VSS_192

AC17

VSS_193

AC19

VSS_194

AC21

VSS_195

AC23

VSS_196

AD8

VSS_197

AD10

VSS_198

AD12

VSS_199

AD14

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VLDT_B_1

VLDT_B_2

VLDT_B_3

VLDT_B_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

AD16

AD20

AD22

AD24

AE4

AE5

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

H1

H2

H5

H6

AG12

AH12

AJ12

AK12

AL12

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

AK20

AK22

AK24

AK26

AK28

AK30

AL5

VTTMEM

0805

C81

4.7UF

Y5V

10V

0603

C80

0.1UF

Y5V

16V

POWER/GND3

POWER/GND4

VCCP

U3E

B3

VDD_1

C2

VDD_2

C4

VDD_3

D3

VDD_4

H11

H23

K11

K13

K15

K17

K19

K21

K23

M11

M13

M15

M17

M19

M21

M23

N10

N12

N14

N16

N18

N20

N22

P11

P13

P15

P17

P19

P21

P23

R10

R12

R14

R16

R18

R20

R22

T11

T13

D5

VDD_5

E4

VDD_6

E6

VDD_7

F5

VDD_8

F7

VDD_9

G6

VDD_10

G8

VDD_11

H7

VDD_12

VDD_13

VDD_14

J8

VDD_15

J12

VDD_16

J14

VDD_17

J16

VDD_18

J18

VDD_19

J20

VDD_20

J22

VDD_21

J24

VDD_22

K7

VDD_23

K9

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

L4

VDD_32

L5

VDD_33

L8

VDD_34

L10

VDD_35

L12

VDD_36

L14

VDD_37

L16

VDD_38

L18

VDD_39

L20

VDD_40

L22

VDD_41

M2

VDD_42

M3

VDD_43

M7

VDD_44

M9

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

VDD_50

VDD_51

VDD_52

N8

VDD_53

VDD_54

VDD_55

VDD_56

VDD_57

VDD_58

VDD_59

VDD_60

P7

VDD_61

P9

VDD_62

VDD_63

VDD_64

VDD_65

VDD_66

VDD_67

VDD_68

VDD_69

R4

VDD_70

R5

VDD_71

R8

VDD_72

VDD_73

VDD_74

VDD_75

VDD_76

VDD_77

VDD_78

VDD_79

T2

VDD_80

T3

VDD_81

T7

VDD_82

T9

VDD_83

VDD_84

VDD_85

AM2+

POWER/GND1

D D

C C

B B

A A

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

A3

A7

A9

A11

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

VCCP

T15

T17

T19

T21

T23

U10

U12

U14

U16

U18

U20

U22

V11

V13

V15

V17

V19

V21

V23

W10

W12

W14

W16

W18

W20

W22

Y11

Y13

Y15

Y17

Y19

Y21

Y23

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AC4

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AD2

AD3

AD7

AD9

AD11

AD23

AE10

AE12

AF7

AF9

AF11

AG4

AG5

AG7

AH2

AH3

U3F

VDD_86

VDD_87

VDD_88

VDD_89

VDD_90

U8

VDD_91

VDD_92

VDD_93

VDD_94

VDD_95

VDD_96

VDD_97

VDD_98

V9

VDD_99

VDD_100

VDD_101

VDD_102

VDD_103

VDD_104

VDD_105

VDD_106

W4

VDD_107

W5

VDD_108

W8

VDD_109

VDD_110

VDD_111

VDD_112

VDD_113

VDD_114

VDD_115

VDD_116

Y2

VDD_117

Y3

VDD_118

Y7

VDD_119

Y9

VDD_120

VDD_121

VDD_122

VDD_123

VDD_124

VDD_125

VDD_126

VDD_127

VDD_128

VDD_129

VDD_130

VDD_131

VDD_132

VDD_133

VDD_134

VDD_135

VDD_136

VDD_137

VDD_138

VDD_139

VDD_140

VDD_141

VDD_142

VDD_143

VDD_144

VDD_145

VDD_146

VDD_147

VDD_148

VDD_149

VDD_150

VDD_151

VDD_152

VDD_153

VDD_154

VDD_155

VDD_156

VDD_157

VDD_158

VDD_159

VDD_160

VDD_161

VDD_162

VDD_163

VDD_164

VDD_165

VDD_166

VDD_167

VDD_168

VDD_169

VDD_170

AM2+

POWER/GND2

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W7

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

Y14

Y16

Y18

Y20

Y22

AA4

AA5

AA7

AA9

LAYOUT: Place HTT bypass caps on

topside near connected CPU HTT link.

V1P2_LDT

C166

0.1UF

Y5V

16V

0603

C169

0.1UF

Y5V

16V

0603

0603

http://laptop-motherboard-schematic.blogspot.com/

Title

K8 CPU-PWR & GND PART A

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

AX78

1

0.2

of

735Tuesday, August 28, 2007

5

4

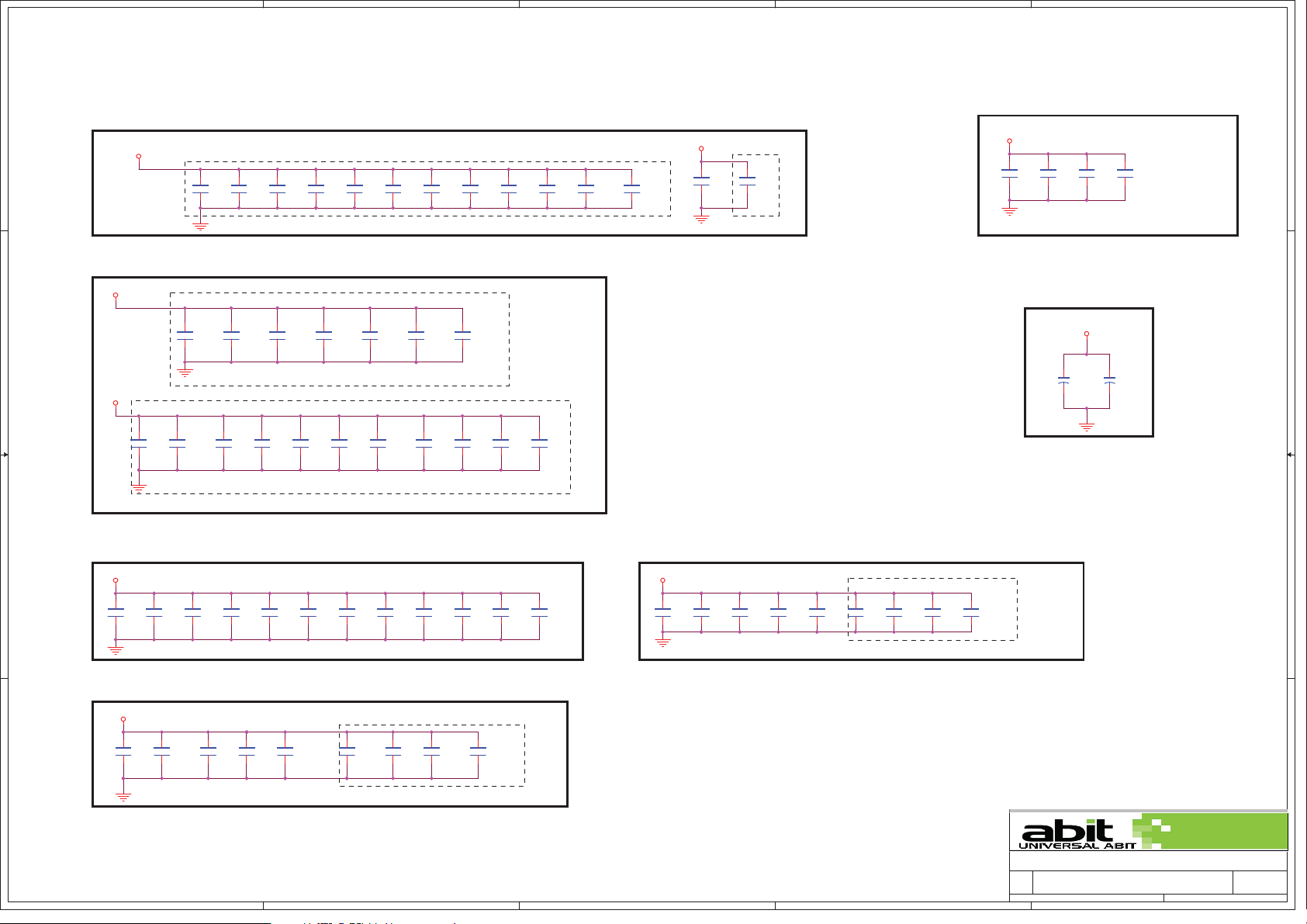

Bottomside Decoupling

3

2

1

D D

VCCP

PLACE UNDER THE CPU SOC KET

0805

C616

10UF

X5R

6.3V

0805

C598

10UF

X5R

6.3V

0805

C617

10UF

X5R

6.3V

0805

C624

10UF

X5R

6.3V

0805

C618

10UF

X5R

6.3V

0805

C603

10UF

X5R

6.3V

0805

C623

10UF

X5R

6.3V

0805

C611

10UF

X5R

6.3V

0805

C619

10UF

X5R

6.3V

0805

C625

10UF

X5R

6.3V

0805

C612

10UF

X5R

6.3V

0805

C609

10UF

X5R

6.3V

SOLDER SIDE

VCCP

C602

C604

C610

C597

0805

0805

10UF

10UF

X5R

C C

6.3V

X5R

6.3V

0805

10UF

X5R

6.3V

0805

10UF

X5R

6.3V

0805

C595

10UF

X5R

6.3V

0805

C601

10UF

X5R

6.3V

0805

C596

10UF

X5R

6.3V

VDDMEM

C53

0805

10UF

Y5V

10V

SOLDER SIDE

0603

C614

0.22UF

Y5V

16V

SOLDER SIDE

VCCP

0603

C605

0.1UF

X7R

16V

0603

C613

0.1UF

X7R

16V

0603

C615

0.1UF

X7R

16V

0603

C606

0.1UF

X7R

16V

0603

C630

0.1UF

X7R

16V

0603

C620

0.1UF

X7R

16V

0603

C599

0.1UF

X7R

16V

0603

C594

0.1UF

X7R

16V

0603

C593

0.1UF

X7R

16V

0603

C621

0.1UF

X7R

16V

0603

C608

0.1UF

X7R

16V

V1P2_LDT

0805

Place near CPU SOCKET

C174

4.7UF

Y5V

10V

TC-D

SC2

+

X120UF

2V

0603

VCCP

C211

0.22UF

Y5V

16V

TC-D

+

0603

SC1

X120UF

2V

C167

0.22UF

Y5V

16V

C175

4.7UF

Y5V

10V

0805

SOLDER SIDE

B B

VTTMEM

VCCP_NB

0805

C77

4.7UF

Y5V

10V

0805

C198

4.7UF

Y5V

10V

0805

C54

4.7UF

Y5V

10V

0805

C197

4.7UF

Y5V

10V

0603

C46

0.22UF

Y5V

16V

0603

C42

0.22UF

Y5V

16V

0603

C84

0.22UF

Y5V

16V

0603

C191

0.22UF

Y5V

16V

0603

C83

1000PF

X7R

16V

0603

C40

1000PF

X7R

16V

0603

C195

1000PF

X7R

16V

0603

C184

1000PF

X7R

16V

0805

C59

10UF

X5R

6.3V

0805

C72

10UF

X5R

6.3V

0603

C69

0.22UF

Y5V

16V

0603

C57

0.22UF

Y5V

16V

0603

C65

0.1UF

Y5V

16V

0805

C73

10UF

X5R

6.3V

0805

PLACE NEAR CPU SOCKET AL ONG VTT P OUR

VDDMEM

C87

10UF

0805

0805

Y5V

10V

A A

5

C171

10UF

Y5V

10V

0603

C86

0.22UF

Y5V

16V

0603

C172

0.22UF

Y5V

16V

0603

C187

0.22UF

Y5V

16V

0603

PLACE NEAR CPU, BETWEEN CPU AND DIMM

C600

0.01UF

Y5V

16V

0805

C592

4.7UF

Y5V

10V

4

C622

C607

4.7UF

Y5V

10V

0603

0.22UF

Y5V

16V

0805

SOLDER SIDE

http://laptop-motherboard-schematic.blogspot.com/

3

C62

C56

0603

0.1UF

10UF

Y5V

X5R

16V

6.3V

SOLDER SIDE

2

C67

0603

0.1UF

Y5V

16V

Title

K8 CPU-PWR & GND PART B

Size Document Number Re v

Custom

Date: Sheet

AX78

0.2

of

835Tuesday, August 28, 2007

1

5

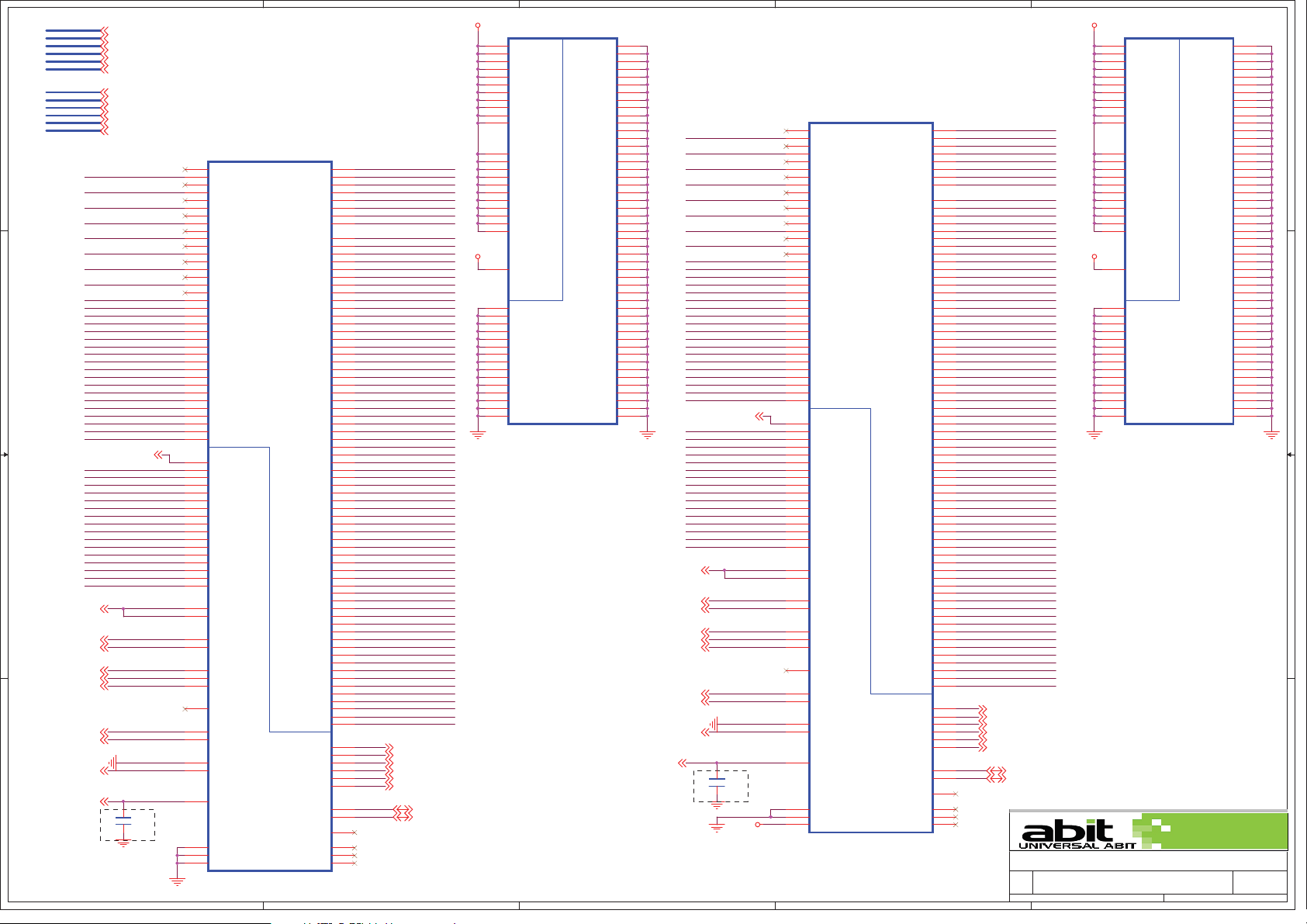

MEM_A_ECC[0..7] 5,10

MEM_A_DATA[63..0] 5,10

MEM_A_DM[0..8] 5,10

MEM_A_DQS[0..8] 5,10

MEM_A_DQS*[0..8] 5,10

MEM_A_ADD[15..0] 5,10,11,12

MEM_B_ECC[0..7] 5,10

MEM_B_DATA[63..0] 5,10

MEM_B_DM[0..8] 5,10

D D

C C

B B

MEM_A0_CK E5,11

MEM_A_BA15,10,11,12

MEM_A_BA05,10,11,12

MEM_A_W E*5,10,11,12

MEM_A_RAS*5,10,11,12

MEM_A_CAS*5,10,11,12

MEM_A0_CS*15,11

MEM_A0_CS*05,11

MEM_A0_ODT5,11

A A

DIMM_VREF10,12

PLACE CLOSE

TO DIMM PIN

MEM_B_DQS[0..8] 5,10

MEM_B_DQS*[0..8] 5,10

MEM_B_ADD[15..0] 5,10,11,12

MEM_A_DM8

MEM_A_DM7

MEM_A_DM6

MEM_A_DM5

MEM_A_DM4

MEM_A_DM3

MEM_A_DM2

MEM_A_DM1

MEM_A_DM0

MEM_A_DQS*8

MEM_A_DQS 8

MEM_A_DQS 7

MEM_A_DQS*6

MEM_A_DQS 6

MEM_A_DQS*5

MEM_A_DQS 5

MEM_A_DQS*4

MEM_A_DQS 4

MEM_A_DQS*3

MEM_A_DQS 3

MEM_A_DQS*2

MEM_A_DQS 2

MEM_A_DQS*1

MEM_A_DQS 1

MEM_A_DQS*0

MEM_A_DQS 0

MEM_A_BA25,10,11,12

MEM_A_ADD15

MEM_A_ADD14

MEM_A_ADD13

MEM_A_ADD12

MEM_A_ADD11

MEM_A_ADD10

MEM_A_ADD9

MEM_A_ADD8

MEM_A_ADD7

MEM_A_ADD6

MEM_A_ADD5

MEM_A_ADD4

MEM_A_ADD3

MEM_A_ADD2

MEM_A_ADD1

MEM_A_ADD0

C28

0603

0.1UF

Y5V

16V

5

165

164

233

232

224

223

212

211

203

202

156

155

147

146

135

134

126

125

45

46

113

114

104

105

92

93

83

84

36

37

27

28

15

16

54

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

171

52

190

71

73

192

74

18

76

193

77

195

101

240

239

DIMM1A

DQS17-(B)

DQS17(B)

DQS16-(B)

DQS16(B)

DQS15-(B)

DQS15(B)

DQS14-(B)

DQS14(B)

DQS13-(B)

DQS13(B)

DQS12-(B)

DQS12(B)

DQS11-(B)

DQS11(B)

DQS10-(B)

DQS10(B)

DQS9-(B)

DQS9(B)

DQS8-(B)

DQS8(B)

DQS7-(B)

DQS7(B)

DQS6-(B)

DQS6(B)

DQS5-(B)

DQS5(B)

DQS4-(B)

DQS4(B)

DQS3-(B)

DQS3(B)

DQS2-(B)

DQS2(B)

DQS1-(B)

DQS1(B)

6

DQS0-(B)

7

DQS0(B)

A16(I)/BA2

A15(I)

A14(I)

A13(I)

A12(I)

A11(I)

A10(I)

A9(I)

A8(I)

A7(I)

A6(I)

A5(I)

A4(I)

A3(I)

A2(I)

A1(I)

A0(I)

CKE1(I)

CKE0(I)

BA1 (I)

BA0 (I)

WE#(I)

RAS#(I)

CAS#(I)

RESET#(I)

CS-1(I)

CS-0(I)

ODT1(I)

ODT0(I)

1

VREF(B)

SA2 (I)

SA1 (I)

SA0 (I)

ORANGE

DDR DIMM II-240PIN

CHA DIMM1 000

CB7(B)

CB6(B)

CB5(B)

CB4(B)

CB3(B)

CB2(B)

CB1(B)

CB0(B)

DQ63(B)

DQ62(B)

DQ61(B)

DQ60(B)

DQ59(B)

DQ58(B)

DQ57(B)

DQ56(B)

DQ55(B)

DQ54(B)

DQ53(B)

DQ52(B)

DQ51(B)

DQ50(B)

DQ49(B)

DQ48(B)

DQ47(B)

DQ46(B)

DQ45(B)

DQ44(B)

DQ43(B)

DQ42(B)

DQ41(B)

DQ40(B)

DQ39(B)

DQ38(B)

DQ37(B)

DQ36(B)

DQ35(B)

DQ34(B)

DQ33(B)

DQ32(B)

DQ31(B)

DQ30(B)

DQ29(B)

DQ28(B)

DQ27(B)

DQ26(B)

DQ25(B)

DQ24(B)

DQ23(B)

DQ22(B)

DQ21(B)

DQ20(B)

DQ19(B)

DQ18(B)

DQ17(B)

DQ16(B)

DQ15(B)

DQ14(B)

DQ13(B)

DQ12(B)

DQ11(B)

DQ10(B)

DQ9(B)

DQ8(B)

DQ7(B)

DQ6(B)

DQ5(B)

DQ4(B)

DQ3(B)

DQ2(B)

DQ1(B)

DQ0(B)

CK2(I)

CK-2(I)

CK1(I)

CK-1(I)

CK0(I)

CK-0(I)

SCL(B)

SDA(B)

RC0(B)

NC1(B)

NC2(B)

NC3(B)

168

167

162

161

49

48

43

42

236

235

230

229

117

116

111

110

227

226

218

217

108

107

99

98

215

214

209

208

96

95

90

89

206

205

200

199

87

86

81

80

159

158

153

152

40

39

34

33

150

149

144

143

31

30

25

24

141

140

132

131

22

21

13

12

129

128

123

122

10

9

4

3

220

221

137

138

185

186

120

119

55

19

102

68

4

MEM_A_ECC7

MEM_A_ECC6

MEM_A_ECC5

MEM_A_ECC4

MEM_A_ECC3

MEM_A_ECC2

MEM_A_ECC1

MEM_A_ECC0

MEM_A_DATA63

MEM_A_DATA62

MEM_A_DATA61

MEM_A_DATA60

MEM_A_DATA59

MEM_A_DATA58

MEM_A_DATA57

MEM_A_DATA56

MEM_A_DATA55

MEM_A_DATA54

MEM_A_DATA53

MEM_A_DATA52

MEM_A_DATA51

MEM_A_DATA50

MEM_A_DATA49

MEM_A_DATA48

MEM_A_DATA47

MEM_A_DATA46

MEM_A_DATA45

MEM_A_DATA44

MEM_A_DATA43

MEM_A_DATA42

MEM_A_DATA41

MEM_A_DATA40

MEM_A_DATA39

MEM_A_DATA38

MEM_A_DATA37

MEM_A_DATA36

MEM_A_DATA35

MEM_A_DATA34

MEM_A_DATA33

MEM_A_DATA32

MEM_A_DATA31

MEM_A_DATA30

MEM_A_DATA29

MEM_A_DATA28

MEM_A_DATA27

MEM_A_DATA26

MEM_A_DATA25

MEM_A_DATA24

MEM_A_DATA23

MEM_A_DATA22

MEM_A_DATA21

MEM_A_DATA20

MEM_A_DATA19

MEM_A_DATA18

MEM_A_DATA17

MEM_A_DATA16

MEM_A_DATA15

MEM_A_DATA14

MEM_A_DATA13

MEM_A_DATA12

MEM_A_DATA11

MEM_A_DATA10

MEM_A_DATA9

MEM_A_DATA8

MEM_A_DATA7

MEM_A_DATA6

MEM_A_DATA5

MEM_A_DATA4

MEM_A_DATA3

MEM_A_DATA2

MEM_A_DATA1

MEM_A_DATA0

MEM_A0_CLK2 5,12

MEM_A0_CLK*2 5,12

MEM_A0_CLK1 5,12

MEM_A0_CLK*1 5,12

MEM_A0_CLK0 5,12

MEM_A0_CLK*0 5,12

SMBCLK 10 ,16,21,26,33

SMBDATA 10,16 ,21,26,33

4

3

DIMM1B

194

VDDQ11 (P)

191

VDDQ10 (P)

181

VDDQ9 (P)

175

VDDQ4 (P)

170

VDDQ3 (P)

78

VDDQ8 (P)

75

VDDQ7 (P)

72

VDDQ6 (P)

62

VDDQ5 (P)

56

VDDQ2 (P)

51

VDDQ1 (P)

197

VDD10(P)

189

VDD9(P)

187

VDD11(P)

184

VDD8(P)

178

VDD7(P)

172

VDD6 (P)

69

VDD5 (P)

67

VDD4 (P)

64

VDD3 (P)

59

VDD2 (P)

53

VDD1 (P)

VCC3 VCC3

238

VDDSPD(P)

201

VSS49(P)

204

VSS50(P)

207

VSS51(P)

210

VSS52(P)

213

VSS53(P)

216

VSS54(P)

219

VSS55(P)

222

VSS56(P)

225

VSS57(P)

228

VSS58(P)

231

VSS59(P)

234

VSS60(P)

237

VSS61(P)

26

VSS63(P)

151

VSS64(P)

DDR DIMM II-240PIN

http://laptop-motherboard-schematic.blogspot.com/

VSS1(P)

VSS2(P)

VSS3(P)

VSS4(P)

VSS5(P)

VSS6(P)

VSS7(P)

VSS8(P)

VSS9(P)

VSS10(P)

VSS11(P)

VSS12(P)

VSS13(P)

VSS62(P)

VSS14(P)

VSS15(P)

VSS16(P)

VSS17(P)

VSS18(P)

VSS19(P)

VSS20(P)

VSS21(P)

VSS22(P)

VSS23(P)

VSS24(P)

VSS25(P)

VSS26(P)

VSS27(P)

VSS28(P)

VSS29(P)

VSS30(P)

VSS31(P)

VSS32(P)

VSS33(P)

VSS34(P)

VSS35(P)

VSS36(P)

VSS37(P)

VSS38(P)

VSS39(P)

VSS40(P)

VSS41(P)

VSS42(P)

VSS43(P)

VSS44(P)

VSS45(P)

VSS46(P)

VSS47(P)

VSS48(P)

2

5

8

11

14

17

20

23

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

100

103

106

109

112

115

118

121

124

127

130

133

136

139

142

145

148

154

157

160

163

166

169

198

DIMM_VREF10,12

MEM_B0_CKE5,11

MEM_B_BA15,10,11,12

MEM_B_BA05,10,11,12

MEM_B_W E*5,10,11,12

MEM_B_RAS*5,10,11,12

MEM_B_CAS*5,10,11,12

MEM_B0_CS*15,11

MEM_B0_CS*05,11

MEM_B0_ODT5,11

PLACE CLOSE

TO DIMM PIN

MEM_B_DM8

MEM_B_DM7

MEM_B_DM6

MEM_B_DM5

MEM_B_DM4

MEM_B_DM3

MEM_B_DM2

MEM_B_DM1

MEM_B_DM0

MEM_B_DQS*8

MEM_B_DQS 8

MEM_B_DQS*7

MEM_B_DQS 7

MEM_B_DQS*6

MEM_B_DQS 6

MEM_B_DQS*5

MEM_B_DQS 5

MEM_B_DQS*4

MEM_B_DQS 4

MEM_B_DQS*3

MEM_B_DQS 3

MEM_B_DQS*2

MEM_B_DQS 2

MEM_B_DQS*1

MEM_B_DQS 1

MEM_B_DQS*0

MEM_B_DQS 0

MEM_B_BA25,10,11,12

MEM_B_ADD15

MEM_B_ADD14

MEM_B_ADD13

MEM_B_ADD12

MEM_B_ADD11

MEM_B_ADD10

MEM_B_ADD9

MEM_B_ADD8

MEM_B_ADD7

MEM_B_ADD6

MEM_B_ADD5

MEM_B_ADD4

MEM_B_ADD3

MEM_B_ADD2

MEM_B_ADD1

MEM_B_ADD0

C20

0603

0.1UF

Y5V

16V

VCC3

DIMM2A

165

DQS17-(B)

164

DQS17(B)

233

DQS16-(B)

232

DQS16(B)

224

DQS15-(B)

223

DQS15(B)

212

DQS14-(B)

211

DQS14(B)

203

DQS13-(B)

202

DQS13(B)

156

DQS12-(B)

155

DQS12(B)

147

DQS11-(B)

146

DQS11(B)

135

DQS10-(B)

134

DQS10(B)

126

DQS9-(B)

125

DQS9(B)

45

DQS8-(B)

46

DQS8(B)

113

DQS7-(B)

114

DQS7(B)

104

DQS6-(B)

105

DQS6(B)

92

DQS5-(B)

93

DQS5(B)

83

DQS4-(B)

84

DQS4(B)

36

DQS3-(B)

37

DQS3(B)

27

DQS2-(B)

28

DQS2(B)

15

DQS1-(B)

16

DQS1(B)

6

DQS0-(B)

7

DQS0(B)

54

A16(I)/BA2

173

A15(I)

174

A14(I)

196

A13(I)

176

A12(I)

57

A11(I)

70

A10(I)

177

A9(I)

179

A8(I)

58

A7(I)

180

A6(I)

60

A5(I)

61

A4(I)

182

A3(I)

63

A2(I)

183

A1(I)

188

A0(I)

171

CKE1(I)

52

CKE0(I)

190

BA1 (I)

71

BA0 (I)

73

WE#(I)

192

RAS#(I)

74

CAS#(I)

18

RESET#(I)

76

CS-1(I)

193

CS-0(I)

77

ODT1(I)

195

ODT0(I)

1

VREF(B)

101

SA2 (I)

240

SA1 (I)

239

SA0 (I)

DDR DIMM II-240PIN

ORANGE

CHA DIMM2 001

3

2

CB7(B)

CB6(B)

CB5(B)

CB4(B)

CB3(B)

CB2(B)

CB1(B)

CB0(B)

DQ63(B)

DQ62(B)

DQ61(B)

DQ60(B)

DQ59(B)

DQ58(B)

DQ57(B)

DQ56(B)

DQ55(B)

DQ54(B)

DQ53(B)

DQ52(B)

DQ51(B)

DQ50(B)

DQ49(B)

DQ48(B)

DQ47(B)

DQ46(B)

DQ45(B)

DQ44(B)

DQ43(B)

DQ42(B)

DQ41(B)

DQ40(B)

DQ39(B)

DQ38(B)

DQ37(B)

DQ36(B)

DQ35(B)

DQ34(B)

DQ33(B)

DQ32(B)

DQ31(B)

DQ30(B)

DQ29(B)

DQ28(B)

DQ27(B)

DQ26(B)

DQ25(B)

DQ24(B)

DQ23(B)

DQ22(B)

DQ21(B)

DQ20(B)

DQ19(B)

DQ18(B)

DQ17(B)

DQ16(B)

DQ15(B)

DQ14(B)

DQ13(B)

DQ12(B)

DQ11(B)

DQ10(B)

DQ9(B)

DQ8(B)

DQ7(B)

DQ6(B)

DQ5(B)

DQ4(B)

DQ3(B)

DQ2(B)

DQ1(B)

DQ0(B)

CK2(I)

CK-2(I)

CK1(I)

CK-1(I)

CK0(I)

CK-0(I)

SCL(B)

SDA(B)

RC0(B)

NC1(B)

NC2(B)

NC3(B)

2

VDDMEMVDDMEM

MEM_B_ECC7

168

MEM_B_ECC6

167

MEM_B_ECC5

162

MEM_B_ECC4

161

MEM_B_ECC3

49

MEM_B_ECC2

48

MEM_B_ECC1

43

MEM_B_ECC0

42

MEM_B_DATA63

236

MEM_B_DATA62

235

MEM_B_DATA61

230

MEM_B_DATA60

229

MEM_B_DATA59

117

MEM_B_DATA58

116

MEM_B_DATA57

111

MEM_B_DATA56

110

MEM_B_DATA55

227

MEM_B_DATA54

226

MEM_B_DATA53

218

MEM_B_DATA52

217

MEM_B_DATA51

108

MEM_B_DATA50

107

MEM_B_DATA49

99

MEM_B_DATA48

98

MEM_B_DATA47MEM_A_DQS*7

215

MEM_B_DATA46

214

MEM_B_DATA45

209

MEM_B_DATA44

208

MEM_B_DATA43

96

MEM_B_DATA42

95

MEM_B_DATA41

90

MEM_B_DATA40

89

MEM_B_DATA39

206

MEM_B_DATA38

205

MEM_B_DATA37

200

MEM_B_DATA36

199

MEM_B_DATA35

87

MEM_B_DATA34

86

MEM_B_DATA33

81

MEM_B_DATA32

80

MEM_B_DATA31

159

MEM_B_DATA30

158

MEM_B_DATA29

153

MEM_B_DATA28

152

MEM_B_DATA27

40

MEM_B_DATA26

39

MEM_B_DATA25

34

MEM_B_DATA24

33

MEM_B_DATA23

150

MEM_B_DATA22

149

MEM_B_DATA21

144

MEM_B_DATA20

143

MEM_B_DATA19

31

MEM_B_DATA18

30

MEM_B_DATA17

25

MEM_B_DATA16

24

MEM_B_DATA15

141

MEM_B_DATA14

140

MEM_B_DATA13

132

MEM_B_DATA12

131

MEM_B_DATA11

22

MEM_B_DATA10

21

MEM_B_DATA9

13

MEM_B_DATA8

12

MEM_B_DATA7

129

MEM_B_DATA6

128

MEM_B_DATA5

123

MEM_B_DATA4

122

MEM_B_DATA3

10

MEM_B_DATA2

9

MEM_B_DATA1

4

MEM_B_DATA0

3

220

221

137

138

185

186

120

119

55

19

102

68

MEM_B0_CLK2 5,12

MEM_B0_CLK*2 5,12

MEM_B0_CLK1 5,12

MEM_B0_CLK*1 5,12

MEM_B0_CLK0 5,12

MEM_B0_CLK*0 5,12

SMBCLK 10 ,16,21,26,33

SMBDATA 10 ,16,21 ,26,33

Title

DDR2 SLOT 1 & 2

Size Document Number Re v

Custom

Date: Sheet

DIMM2B

194

VDDQ11 (P)

191

VDDQ10 (P)

181

VDDQ9 (P)

175

VDDQ4 (P)

170

VDDQ3 (P)

78

VDDQ8 (P)

75

VDDQ7 (P)

72

VDDQ6 (P)

62

VDDQ5 (P)

56

VDDQ2 (P)

51

VDDQ1 (P)

197

VDD10(P)

189

VDD9(P)

187

VDD11(P)

184

VDD8(P)

178

VDD7(P)

172

VDD6 (P)

69

VDD5 (P)

67

VDD4 (P)

64

VDD3 (P)

59

VDD2 (P)

53

VDD1 (P)

238

VDDSPD(P)

201

VSS49(P)

204

VSS50(P)

207

VSS51(P)

210

VSS52(P)

213

VSS53(P)

216

VSS54(P)

219

VSS55(P)

222

VSS56(P)

225

VSS57(P)

228

VSS58(P)

231

VSS59(P)

234

VSS60(P)

237

VSS61(P)

26

VSS63(P)

151

VSS64(P)

DDR DIMM II-240PIN

AX78

1

2

VSS1(P)

5

VSS2(P)

8

VSS3(P)

11

VSS4(P)

14

VSS5(P)

17

VSS6(P)

20

VSS7(P)

23

VSS8(P)

29

VSS9(P)

32

VSS10(P)

35

VSS11(P)

38

VSS12(P)

41

VSS13(P)

44

VSS62(P)

47

VSS14(P)

50

VSS15(P)

65

VSS16(P)

66

VSS17(P)

79

VSS18(P)

82

VSS19(P)

85

VSS20(P)

88

VSS21(P)

91

VSS22(P)

94

VSS23(P)

97

VSS24(P)

100

VSS25(P)

103

VSS26(P)

106

VSS27(P)

109

VSS28(P)

112

VSS29(P)

115

VSS30(P)

118

VSS31(P)

121

VSS32(P)

124

VSS33(P)

127

VSS34(P)

130

VSS35(P)

133

VSS36(P)

136

VSS37(P)

139

VSS38(P)

142

VSS39(P)

145

VSS40(P)

148

VSS41(P)

154

VSS42(P)

157

VSS43(P)

160

VSS44(P)

163

VSS45(P)

166

VSS46(P)

169

VSS47(P)

198

VSS48(P)

0.2

of

935Tuesday, August 28, 2007

1

5

MEM_A_ECC[0..7] 5,9

MEM_A_DATA[63..0] 5,9

MEM_A_DM[0..8] 5,9

MEM_A_DQS[0..8] 5,9

MEM_A_DQS*[0..8] 5,9

MEM_A_ADD[15..0] 5,9,11,12

MEM_B_ECC[0..7] 5,9

MEM_B_DATA[63..0] 5,9

D D

C C

B B

A A

DIMM_VREF9,12

PLACE CLOSE

TO DIMM PIN

MEM_B_DM[0..8] 5,9

MEM_B_DQS[0..8] 5,9

MEM_B_DQS*[0..8] 5,9

MEM_B_ADD[15..0] 5,9,11,12

MEM_A_DM8

MEM_A_DM7

MEM_A_DM6

MEM_A_DM5

MEM_A_DM4

MEM_A_DM3

MEM_A_DM2

MEM_A_DM1

MEM_A_DM0

MEM_A_DQS*8

MEM_A_DQS 8

MEM_A_DQS*7

MEM_A_DQS 7

MEM_A_DQS*6

MEM_A_DQS 6

MEM_A_DQS*5

MEM_A_DQS 5

MEM_A_DQS*4

MEM_A_DQS 4

MEM_A_DQS*3

MEM_A_DQS 3

MEM_A_DQS*2

MEM_A_DQS 2

MEM_A_DQS*1

MEM_A_DQS 1

MEM_A_DQS*0

MEM_A_DQS 0

MEM_A_BA25,9,11,12

MEM_A_ADD15

MEM_A_ADD14

MEM_A_ADD13

MEM_A_ADD12

MEM_A_ADD11

MEM_A_ADD10

MEM_A_ADD9

MEM_A_ADD8

MEM_A_ADD7

MEM_A_ADD6

MEM_A_ADD5

MEM_A_ADD4

MEM_A_ADD3

MEM_A_ADD2

MEM_A_ADD1

MEM_A_ADD0

MEM_A1_CK E5,11

MEM_A_BA15,9,11,12

MEM_A_BA05,9,11,12

MEM_A_W E*5,9,11,12

MEM_A_RAS*5,9,11,12

MEM_A_CAS*5,9,11,12

MEM_A1_CS*15,11

MEM_A1_CS*05,11

MEM_A1_ODT5,11

0603

C23

0.1UF

Y5V

16V

DIMM3A

165

DQS17-(B)

164

DQS17(B)

233

DQS16-(B)

232

DQS16(B)

224

DQS15-(B)

223

DQS15(B)

212

DQS14-(B)

211

DQS14(B)

203

DQS13-(B)

202

DQS13(B)

156

DQS12-(B)

155

DQS12(B)

147

DQS11-(B)

146

DQS11(B)

135

DQS10-(B)

134

DQS10(B)

126

DQS9-(B)

125

DQS9(B)

45

DQS8-(B)

46

DQS8(B)

113

DQS7-(B)

114

DQS7(B)

104

DQS6-(B)

105

DQS6(B)

92

DQS5-(B)

93

DQS5(B)

83

DQS4-(B)

84

DQS4(B)

36

DQS3-(B)

37

DQS3(B)

27

DQS2-(B)

28

DQS2(B)

15

DQS1-(B)

16

DQS1(B)

6

DQS0-(B)

7

DQS0(B)

54

A16(I)/BA2

173

A15(I)

174

A14(I)

196

A13(I)

176

A12(I)

57

A11(I)

70

A10(I)

177

A9(I)

179

A8(I)

58

A7(I)

180

A6(I)

60

A5(I)

61

A4(I)

182

A3(I)

63

A2(I)

183

A1(I)

188

A0(I)

171

CKE1(I)

52

CKE0(I)

190

BA1 (I)

71

BA0 (I)

73

WE#(I)

192

RAS#(I)

74

CAS#(I)

18

RESET#(I)

76

CS-1(I)

193

CS-0(I)

77

ODT1(I)

195

ODT0(I)

1

VREF(B)

VCC3

101

SA2 (I)

240

SA1 (I)

239

SA0 (I)

GREEN

DDR DIMM II-240PIN

5

CHB DIMM 1 010

CB7(B)

CB6(B)

CB5(B)

CB4(B)

CB3(B)

CB2(B)

CB1(B)

CB0(B)

DQ63(B)

DQ62(B)

DQ61(B)

DQ60(B)

DQ59(B)

DQ58(B)

DQ57(B)

DQ56(B)

DQ55(B)

DQ54(B)

DQ53(B)

DQ52(B)

DQ51(B)

DQ50(B)

DQ49(B)

DQ48(B)

DQ47(B)

DQ46(B)

DQ45(B)

DQ44(B)

DQ43(B)

DQ42(B)

DQ41(B)

DQ40(B)

DQ39(B)

DQ38(B)

DQ37(B)

DQ36(B)

DQ35(B)

DQ34(B)

DQ33(B)

DQ32(B)

DQ31(B)

DQ30(B)

DQ29(B)

DQ28(B)

DQ27(B)

DQ26(B)

DQ25(B)

DQ24(B)

DQ23(B)

DQ22(B)

DQ21(B)

DQ20(B)

DQ19(B)

DQ18(B)

DQ17(B)

DQ16(B)

DQ15(B)

DQ14(B)

DQ13(B)

DQ12(B)

DQ11(B)

DQ10(B)

DQ9(B)

DQ8(B)

DQ7(B)

DQ6(B)

DQ5(B)

DQ4(B)

DQ3(B)

DQ2(B)

DQ1(B)

DQ0(B)

CK2(I)

CK-2(I)

CK1(I)

CK-1(I)

CK0(I)

CK-0(I)

SCL(B)

SDA(B)

RC0(B)

NC1(B)

NC2(B)

NC3(B)

168

167

162

161

49

48

43

42

236

235

230

229

117

116

111

110

227

226

218

217

108

107

99

98

215

214

209

208

96

95

90

89

206

205

200

199

87

86

81

80

159

158

153

152

40

39

34

33

150

149

144

143

31

30

25

24

141

140

132

131

22

21

13

12

129

128

123

122

10

9

4

3

220

221

137

138

185

186

120

119

55

19

102

68

4

MEM_A_ECC7

MEM_A_ECC6

MEM_A_ECC5

MEM_A_ECC4

MEM_A_ECC3

MEM_A_ECC2

MEM_A_ECC1

MEM_A_ECC0

MEM_A_DATA63

MEM_A_DATA62

MEM_A_DATA61

MEM_A_DATA60

MEM_A_DATA59

MEM_A_DATA58

MEM_A_DATA57

MEM_A_DATA56

MEM_A_DATA55

MEM_A_DATA54

MEM_A_DATA53

MEM_A_DATA52

MEM_A_DATA51

MEM_A_DATA50

MEM_A_DATA49

MEM_A_DATA48

MEM_A_DATA47

MEM_A_DATA46

MEM_A_DATA45

MEM_A_DATA44

MEM_A_DATA43

MEM_A_DATA42

MEM_A_DATA41

MEM_A_DATA40

MEM_A_DATA39

MEM_A_DATA38

MEM_A_DATA37

MEM_A_DATA36

MEM_A_DATA35

MEM_A_DATA34

MEM_A_DATA33

MEM_A_DATA32

MEM_A_DATA31

MEM_A_DATA30

MEM_A_DATA29

MEM_A_DATA28

MEM_A_DATA27

MEM_A_DATA26

MEM_A_DATA25

MEM_A_DATA24

MEM_A_DATA23

MEM_A_DATA22

MEM_A_DATA21

MEM_A_DATA20

MEM_A_DATA19

MEM_A_DATA18

MEM_A_DATA17

MEM_A_DATA16

MEM_A_DATA15

MEM_A_DATA14

MEM_A_DATA13

MEM_A_DATA12

MEM_A_DATA11

MEM_A_DATA10

MEM_A_DATA9

MEM_A_DATA8

MEM_A_DATA7

MEM_A_DATA6

MEM_A_DATA5

MEM_A_DATA4

MEM_A_DATA3

MEM_A_DATA2

MEM_A_DATA1

MEM_A_DATA0

4

VDDMEM

VCC3

MEM_A1_CLK2 5,12

MEM_A1_CLK*2 5,12

MEM_A1_CLK1 5,12

MEM_A1_CLK*1 5,12

MEM_A1_CLK0 5,12

MEM_A1_CLK*0 5,12

SMBCLK 9,1 6,21,26,33

SMBDATA 9,16,21 ,26,33

DIMM3B

194

VDDQ11 (P)

191

VDDQ10 (P)

181

VDDQ9 (P)

175

VDDQ4 (P)

170

VDDQ3 (P)

78

VDDQ8 (P)

75

VDDQ7 (P)

72

VDDQ6 (P)

62

VDDQ5 (P)

56

VDDQ2 (P)

51

VDDQ1 (P)

197

VDD10(P)

189

VDD9(P)

187

VDD11(P)

184

VDD8(P)

178

VDD7(P)

172

VDD6 (P)

69

VDD5 (P)

67

VDD4 (P)

64

VDD3 (P)

59

VDD2 (P)

53

VDD1 (P)

238

VDDSPD(P)

201

VSS49(P)

204

VSS50(P)

207

VSS51(P)

210

VSS52(P)

213

VSS53(P)

216

VSS54(P)

219

VSS55(P)

222

VSS56(P)

225

VSS57(P)

228

VSS58(P)

231

VSS59(P)

234

VSS60(P)

237

VSS61(P)

26

VSS63(P)

151

VSS64(P)

DDR DIMM II-240PIN

3

2

VSS1(P)

5

VSS2(P)

8

VSS3(P)

11

VSS4(P)

14

VSS5(P)

17

VSS6(P)

VSS7(P)

VSS8(P)

VSS9(P)

VSS10(P)

VSS11(P)

VSS12(P)

VSS13(P)

VSS62(P)

VSS14(P)

VSS15(P)

VSS16(P)

VSS17(P)

VSS18(P)

VSS19(P)

VSS20(P)

VSS21(P)

VSS22(P)

VSS23(P)

VSS24(P)

VSS25(P)

VSS26(P)

VSS27(P)

VSS28(P)

VSS29(P)

VSS30(P)

VSS31(P)

VSS32(P)

VSS33(P)

VSS34(P)

VSS35(P)

VSS36(P)

VSS37(P)

VSS38(P)

VSS39(P)

VSS40(P)

VSS41(P)

VSS42(P)

VSS43(P)

VSS44(P)

VSS45(P)

VSS46(P)

VSS47(P)

VSS48(P)

20

23

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

100

103

106

109

112

115

118

121

124

127

130

133

136

139

142

145

148

154

157

160

163

166

169

198

DIMM_VREF9,12

PLACE CLOSE

TO DIMM PIN

MEM_B1_CKE5,11

MEM_B_BA15,9,11,12

MEM_B_BA05,9,11,12

MEM_B_W E*5,9,11,12

MEM_B_RAS*5,9,11,12

MEM_B_CAS*5,9,11,12

MEM_B1_CS*15,11

MEM_B1_CS*05,11

MEM_B1_ODT5,11

MEM_B_DM8

MEM_B_DM7

MEM_B_DM6

MEM_B_DM5

MEM_B_DM4

MEM_B_DM3

MEM_B_DM2

MEM_B_DM1

MEM_B_DM0

MEM_B_DQS*8

MEM_B_DQS 8

MEM_B_DQS*7

MEM_B_DQS 7

MEM_B_DQS*6

MEM_B_DQS 6

MEM_B_DQS*5

MEM_B_DQS 5

MEM_B_DQS*4

MEM_B_DQS 4

MEM_B_DQS*3

MEM_B_DQS 3

MEM_B_DQS*2

MEM_B_DQS 2

MEM_B_DQS*1

MEM_B_DQS 1

MEM_B_DQS*0

MEM_B_DQS 0

MEM_B_BA25,9,11,12

MEM_B_ADD15

MEM_B_ADD14

MEM_B_ADD13

MEM_B_ADD12

MEM_B_ADD11

MEM_B_ADD10

MEM_B_ADD9

MEM_B_ADD8

MEM_B_ADD7

MEM_B_ADD6

MEM_B_ADD5

MEM_B_ADD4

MEM_B_ADD3

MEM_B_ADD2

MEM_B_ADD1

MEM_B_ADD0

C26

0.1UF

0603

Y5V

16V

http://laptop-motherboard-schematic.blogspot.com/

3

DIMM4A

165

DQS17-(B)

164

DQS17(B)

233

DQS16-(B)

232

DQS16(B)

224

DQS15-(B)

223

DQS15(B)

212

DQS14-(B)

211

DQS14(B)

203

DQS13-(B)

202

DQS13(B)

156

DQS12-(B)

155

DQS12(B)

147

DQS11-(B)

146

DQS11(B)

135

DQS10-(B)

134

DQS10(B)

126

DQS9-(B)

125

DQS9(B)

45

DQS8-(B)

46

DQS8(B)

113

DQS7-(B)

114

DQS7(B)

104

DQS6-(B)

105

DQS6(B)

92

DQS5-(B)

93

DQS5(B)

83

DQS4-(B)

84

DQS4(B)

36

DQS3-(B)

37

DQS3(B)

27

DQS2-(B)

28

DQS2(B)

15

DQS1-(B)

16

DQS1(B)

6

DQS0-(B)

7

DQS0(B)

54

A16(I)/BA2

173

A15(I)

174

A14(I)

196

A13(I)

176

A12(I)

57

A11(I)

70

A10(I)

177

A9(I)

179

A8(I)

58

A7(I)

180

A6(I)

60

A5(I)

61

A4(I)

182

A3(I)

63

A2(I)

183

A1(I)

188

A0(I)

171

CKE1(I)

52

CKE0(I)

190

BA1 (I)

71

BA0 (I)

73

WE#(I)

192

RAS#(I)

74

CAS#(I)

18

RESET#(I)

76

CS-1(I)

193

CS-0(I)

77

ODT1(I)

195

ODT0(I)

1

VREF(B)

VCC3

101

SA2 (I)

240

SA1 (I)

239

SA0 (I)

DDR DIMM II-240PIN

CHB DIMM 2 011

GREEN

2

CB7(B)

CB6(B)

CB5(B)

CB4(B)

CB3(B)

CB2(B)

CB1(B)

CB0(B)

DQ63(B)

DQ62(B)

DQ61(B)

DQ60(B)

DQ59(B)

DQ58(B)

DQ57(B)

DQ56(B)

DQ55(B)

DQ54(B)

DQ53(B)

DQ52(B)

DQ51(B)

DQ50(B)

DQ49(B)

DQ48(B)

DQ47(B)

DQ46(B)

DQ45(B)

DQ44(B)

DQ43(B)

DQ42(B)

DQ41(B)

DQ40(B)

DQ39(B)

DQ38(B)

DQ37(B)

DQ36(B)

DQ35(B)

DQ34(B)

DQ33(B)

DQ32(B)

DQ31(B)

DQ30(B)

DQ29(B)

DQ28(B)

DQ27(B)

DQ26(B)

DQ25(B)

DQ24(B)

DQ23(B)

DQ22(B)

DQ21(B)

DQ20(B)

DQ19(B)

DQ18(B)

DQ17(B)

DQ16(B)

DQ15(B)

DQ14(B)

DQ13(B)

DQ12(B)

DQ11(B)

DQ10(B)

DQ9(B)

DQ8(B)

DQ7(B)

DQ6(B)

DQ5(B)

DQ4(B)

DQ3(B)

DQ2(B)

DQ1(B)

DQ0(B)

CK-2(I)

CK-1(I)

CK-0(I)

SCL(B)

SDA(B)

RC0(B)

NC1(B)

NC2(B)

NC3(B)

2

CK2(I)