68 4

࣭

ࢽ

࣠

;࣪

ࣔ

࣍

࣎

5 1

3

27

1

2

3

D

C

B

A

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

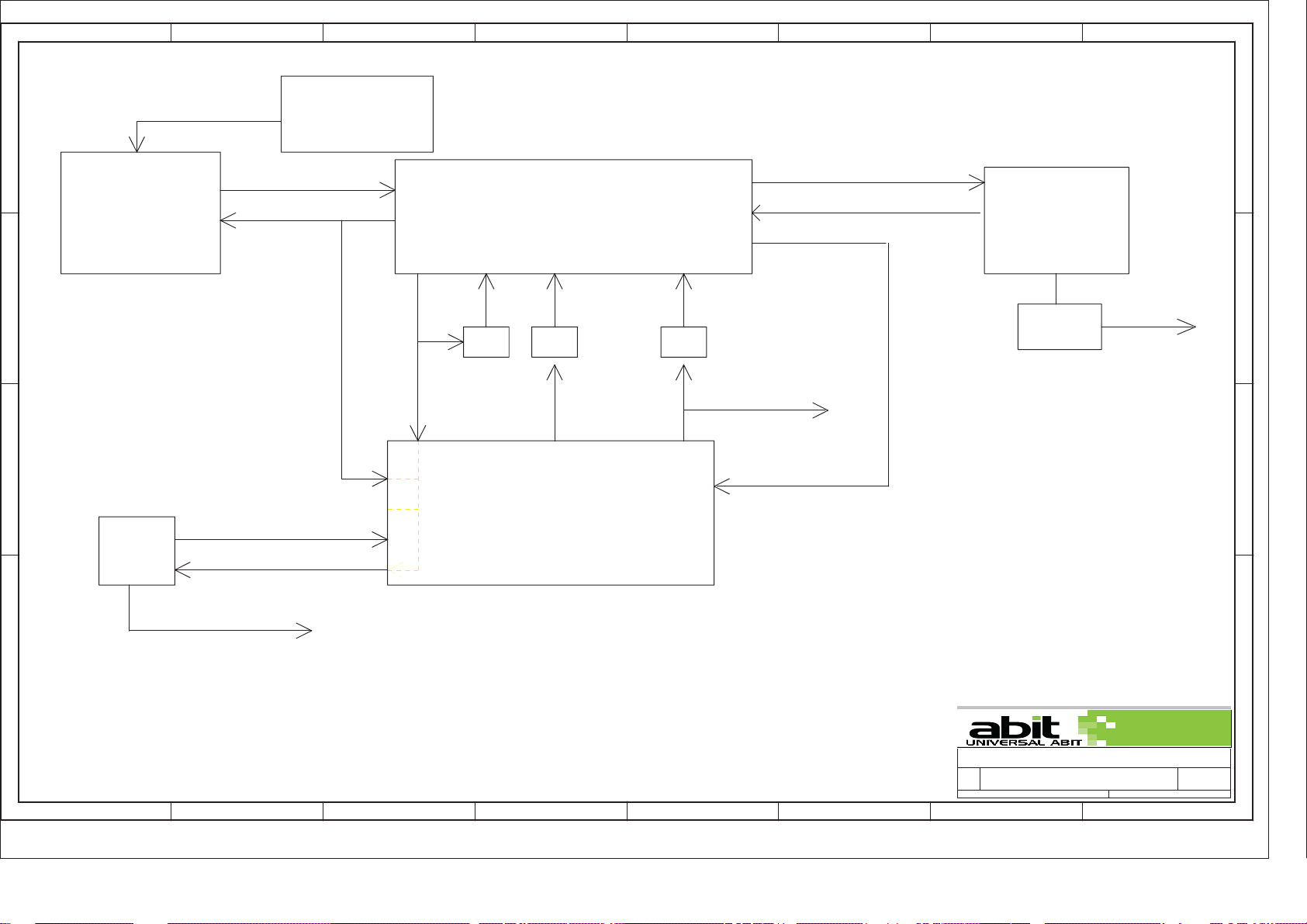

COVER

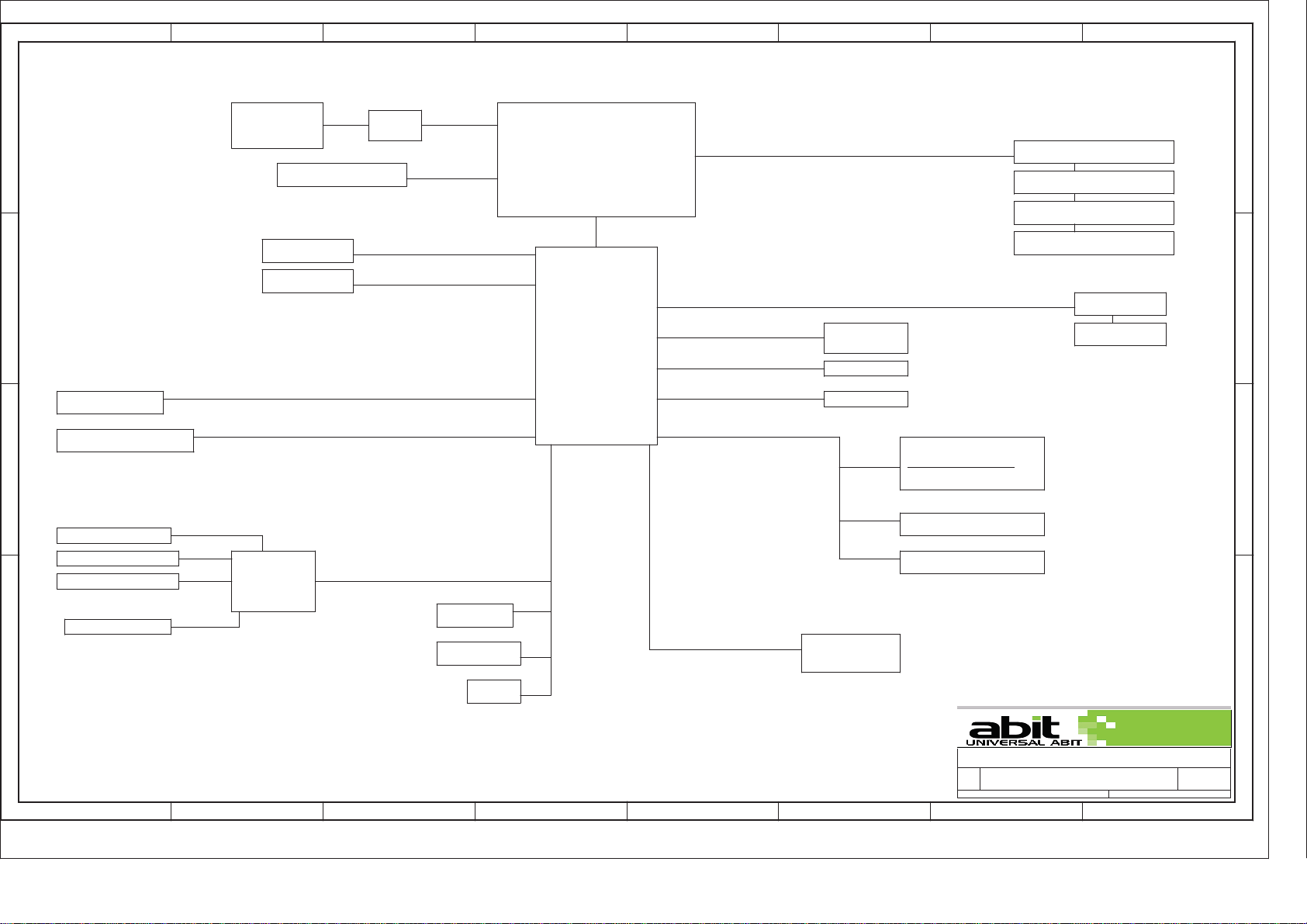

BLOCK DIAGRAM

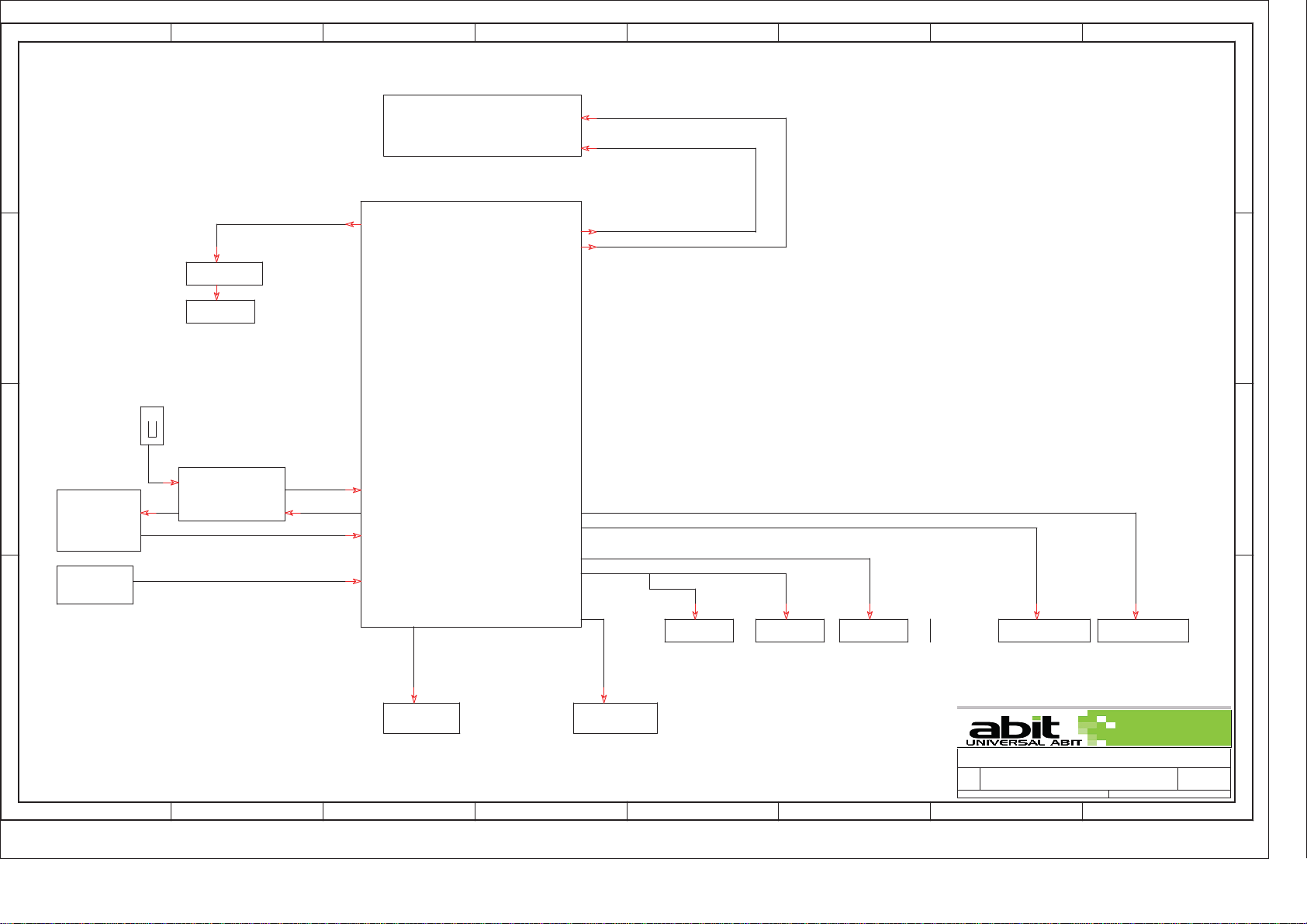

RESET MAP

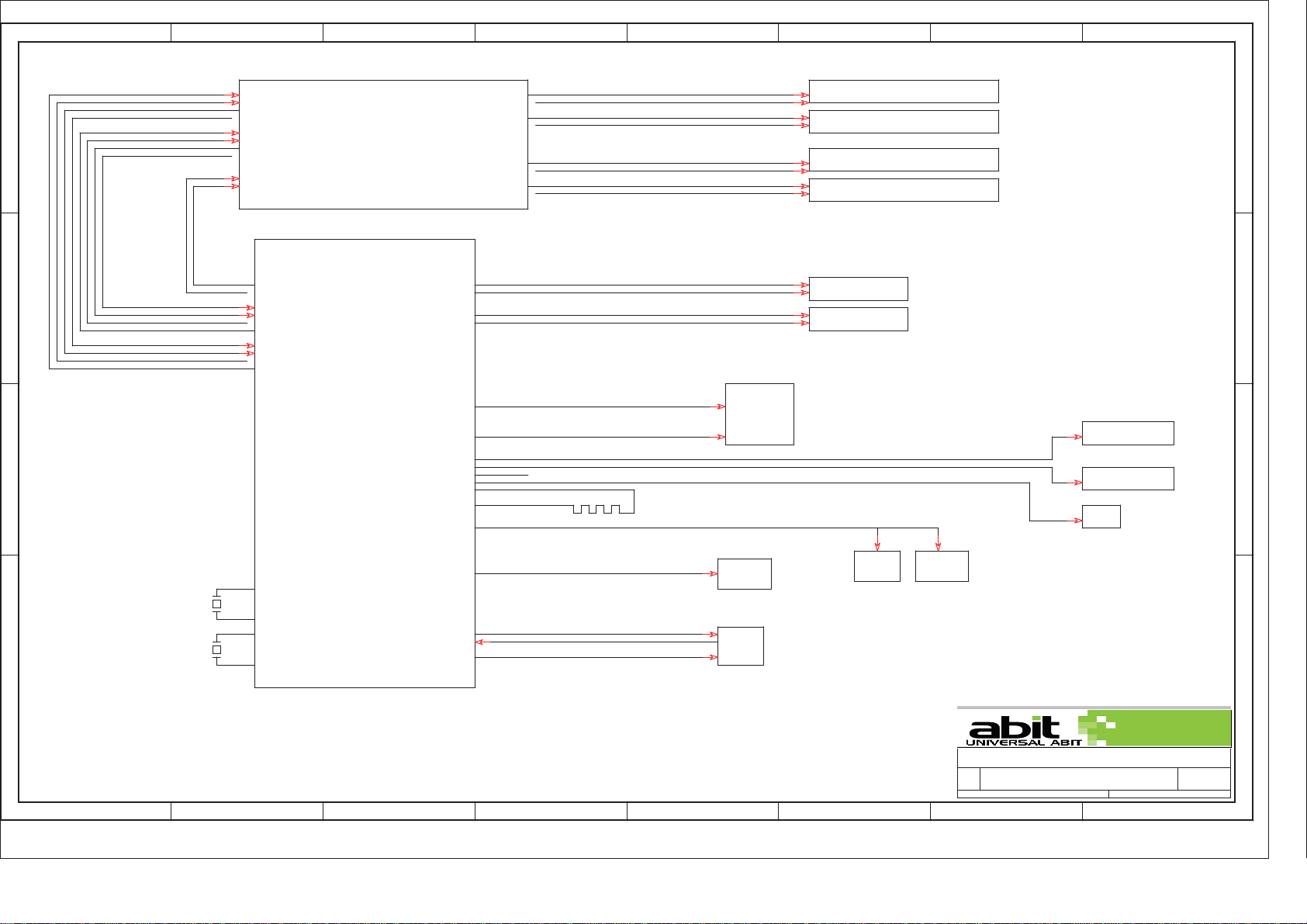

CLOCK DIAGRAM

GPIO TABLE

PCI DEVICE TABLE / VID TABLE

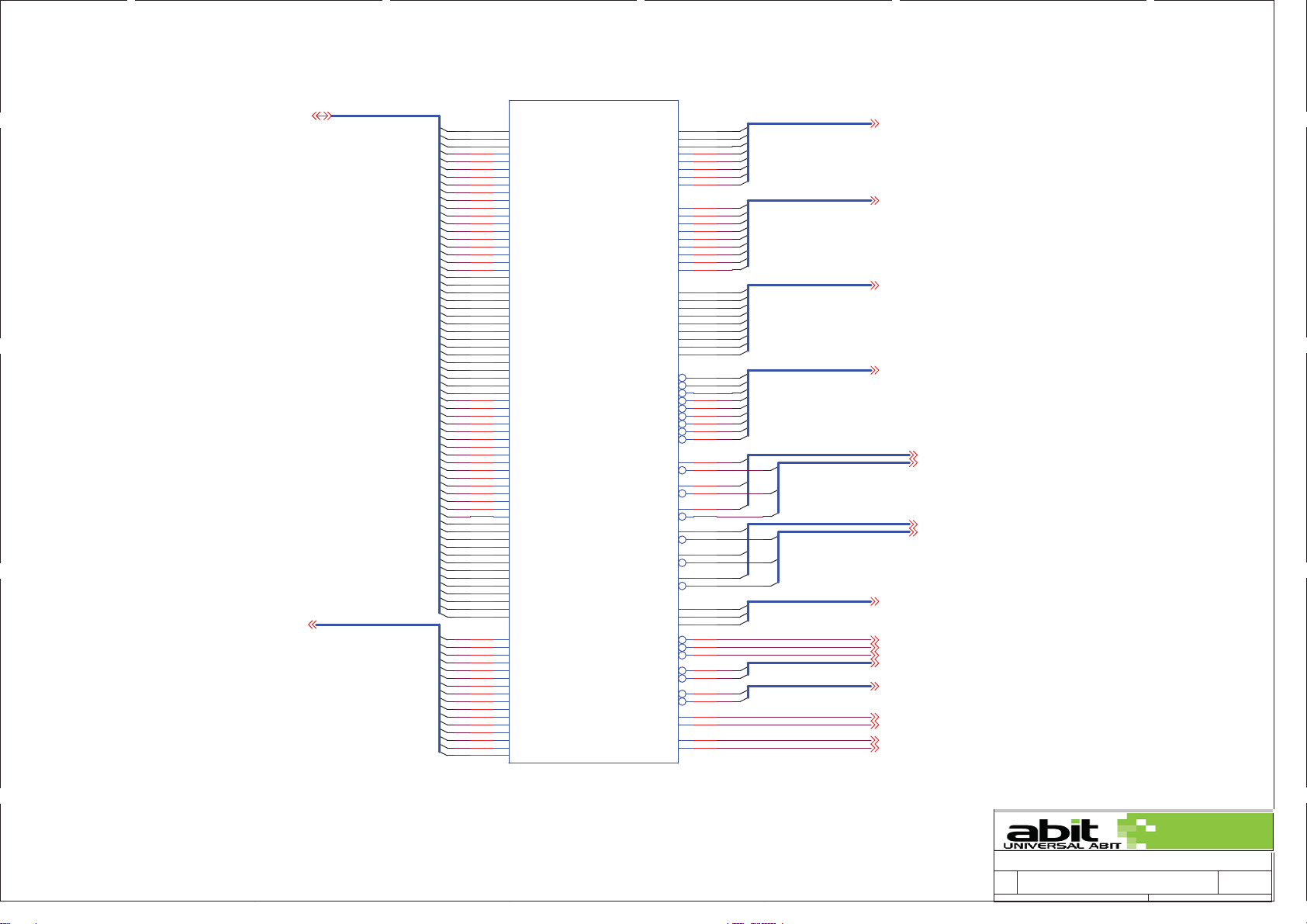

AM2 940 K8CPU PART 1

AM2 940 K8CPU PART 2

AM2 940 K8CPU PART 3

AM2 940 K8CPU PART 4

AM2 940 K8CPU PART 5

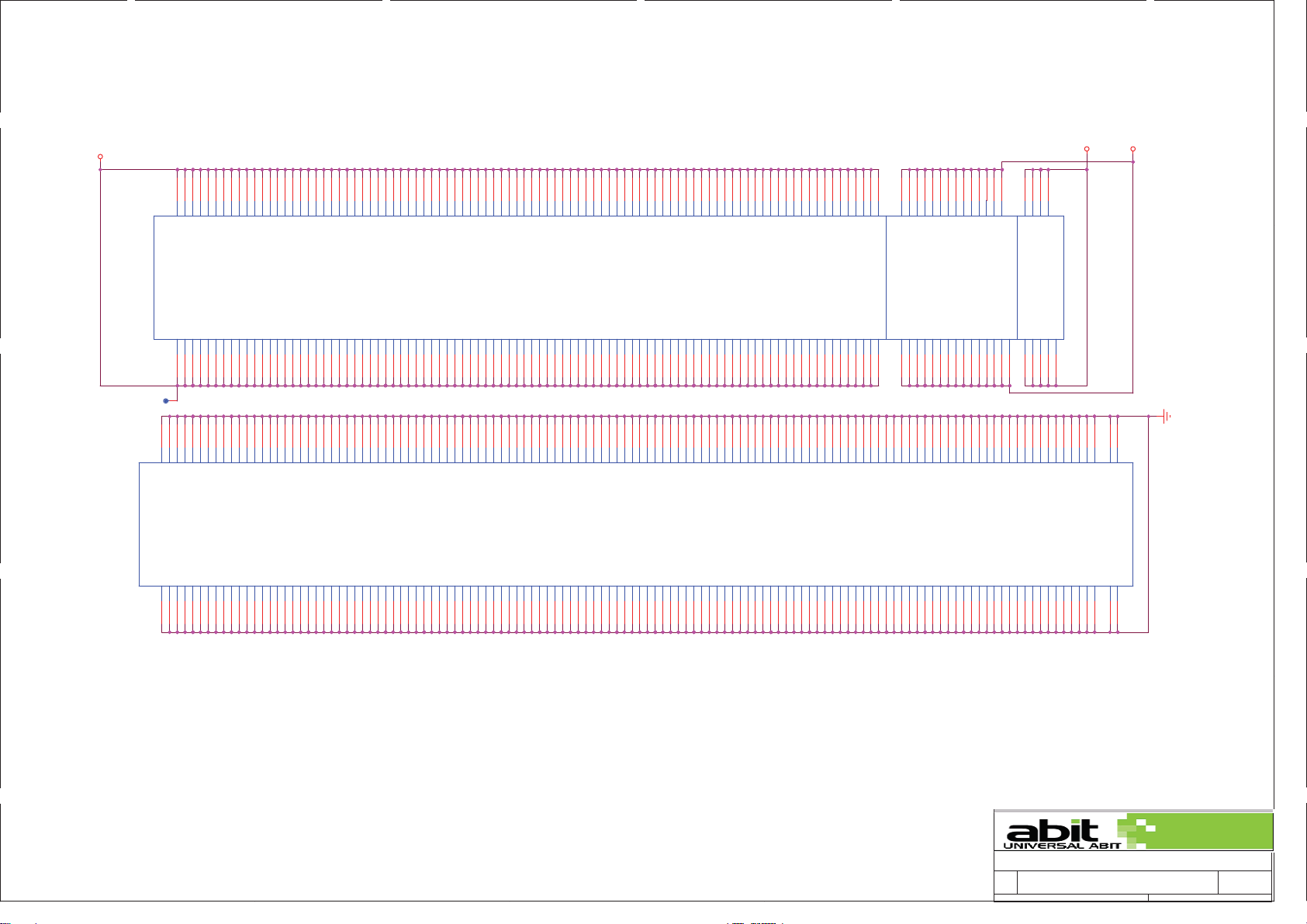

CPU DECOUPLING

DDR ADD/CTL TERMINATION

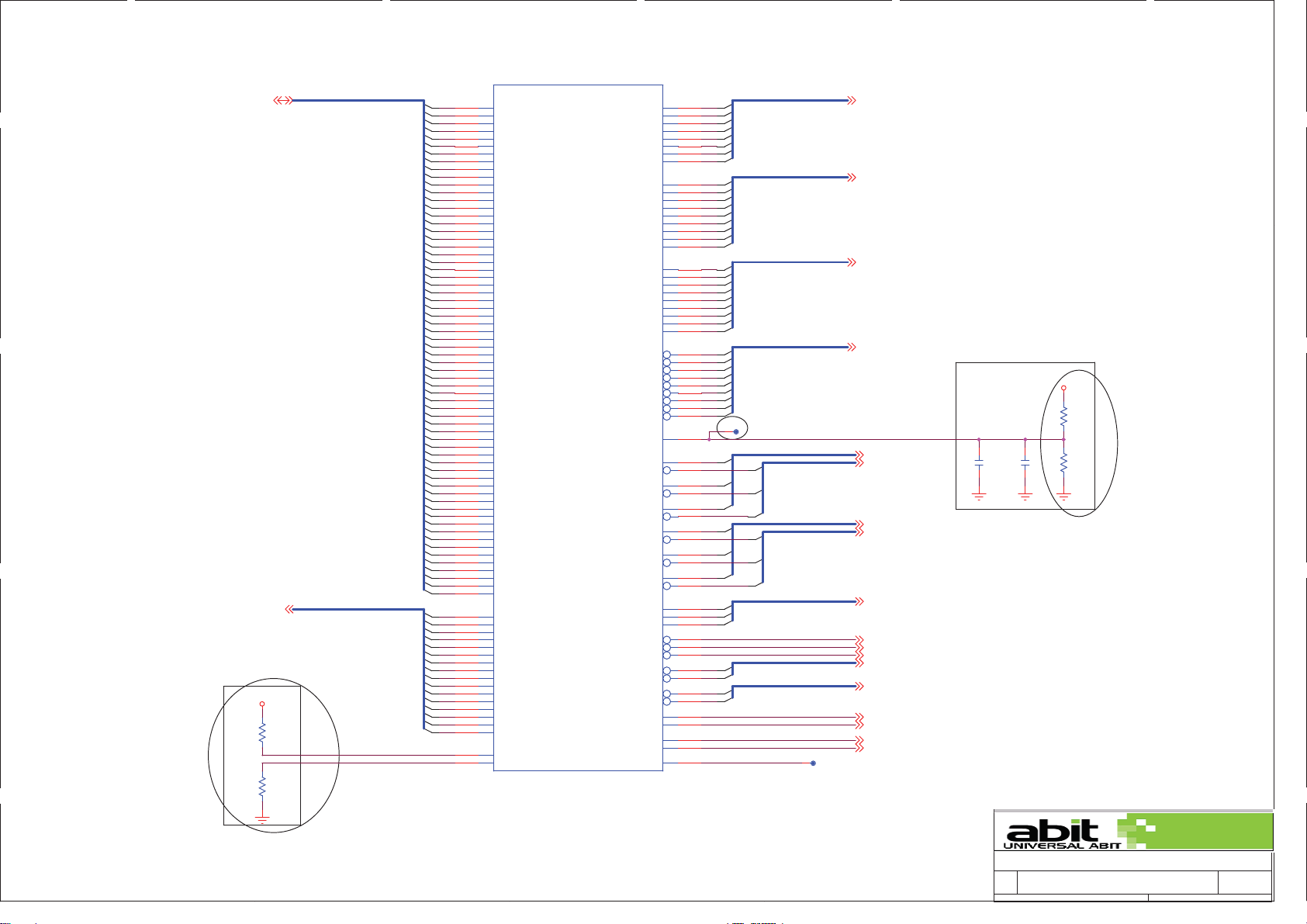

DDR DIMM 0

DDR DIMM 1

DDR DIMM 2

DDR DIMM 3

MCP68 HT/CLKS

MCP68 PEX X16

MCP68 PEX X1/RGMII/HDMI/DAC

MCP68 PCI

MCP68 SATA / IDE

MCP68 AUDIO / USB / MISC

MCP68 PWR / GND

MCP68 DECOUPLING/SPI

PCI EXPRESS X16 CONNECTOR

PCI EXPRESS X1 CONNECTOR

PCI CONNECTOR 1-2

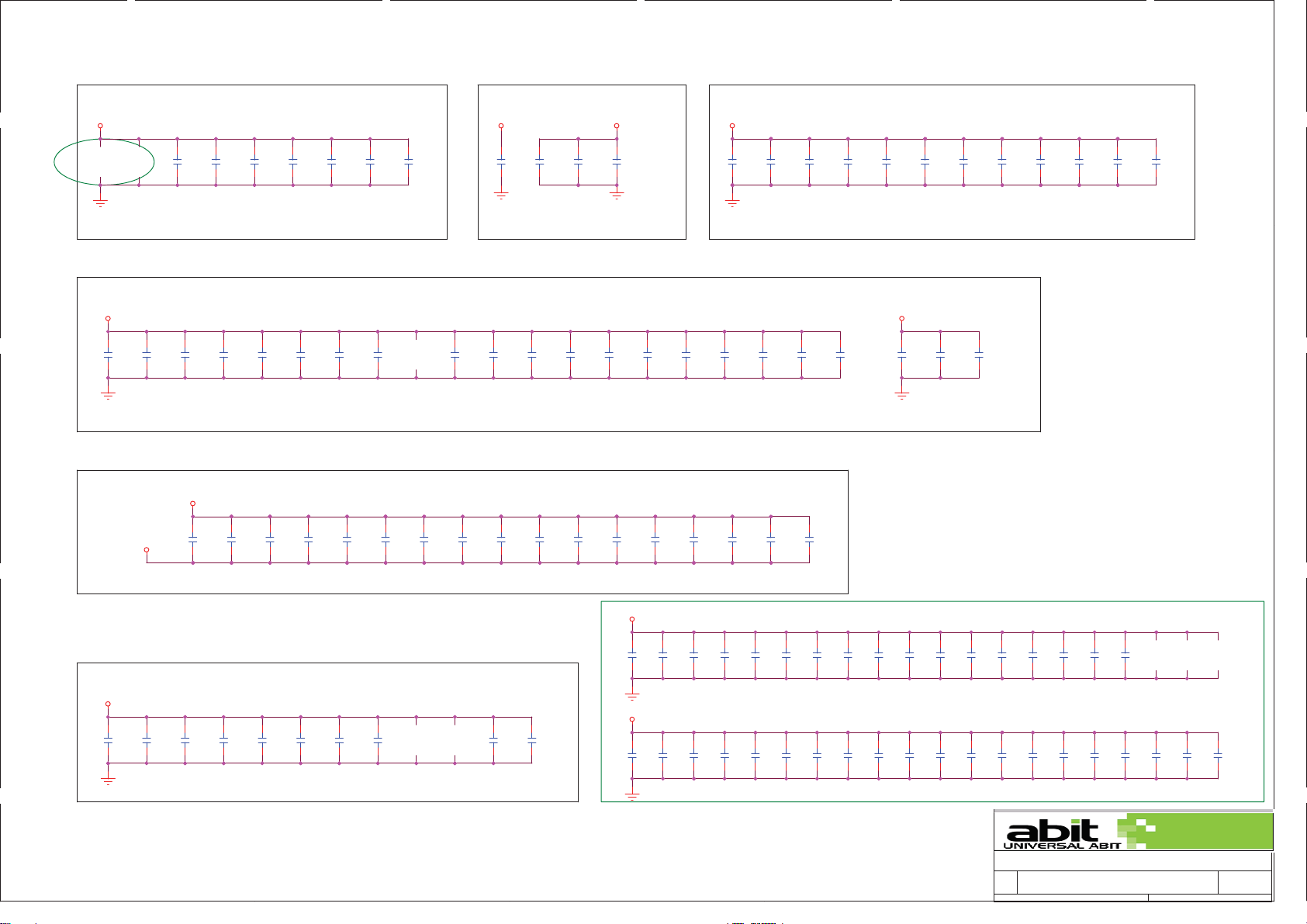

PCI TERMINATION/DECOUPLING

SIO-W83627DHG

Ti43AB22A-1394

GBIT LAN PHY 88E1116

AUDIO ALC888

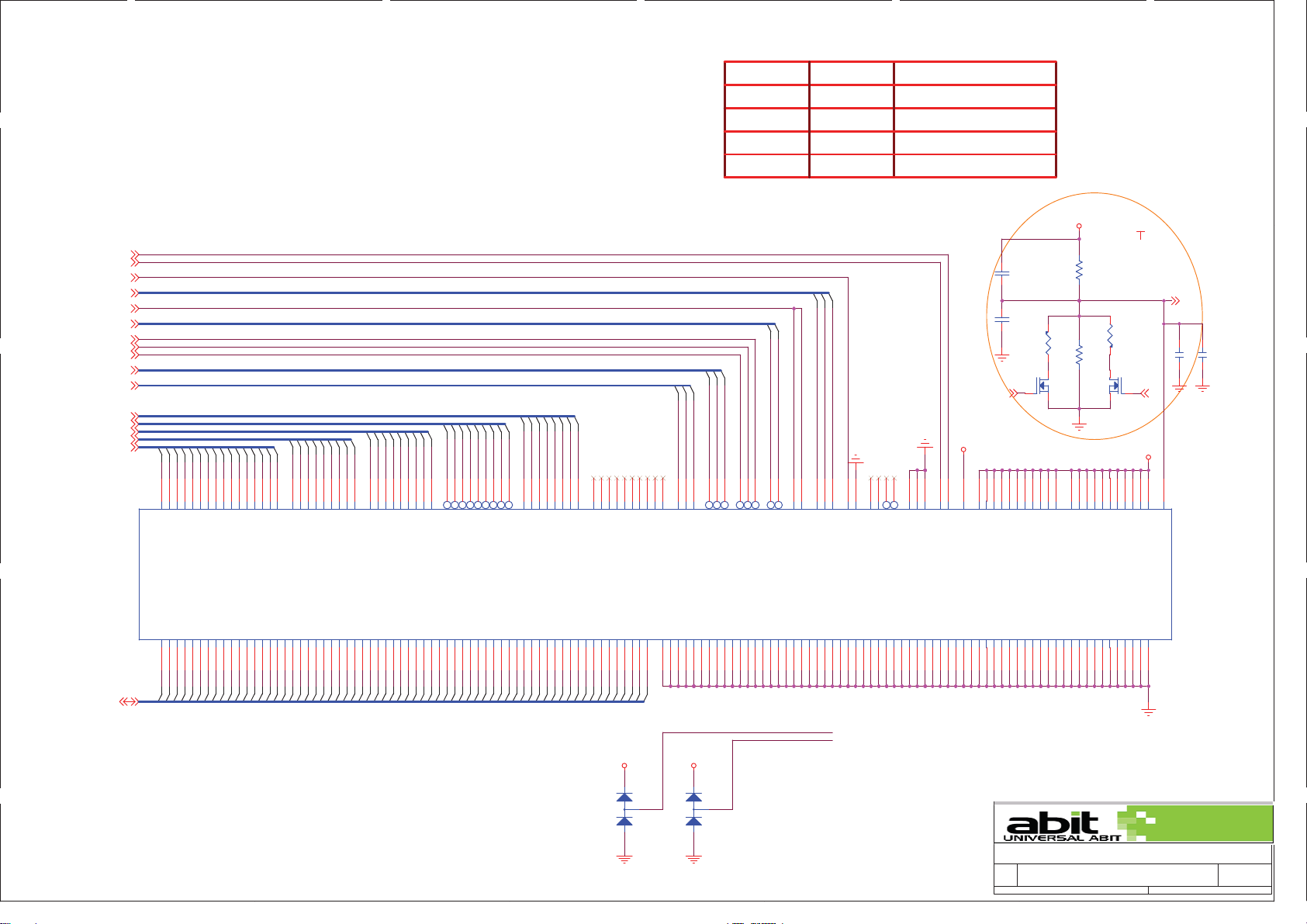

PWM RT8801 & RT9605

W83303AG

C51/MCP51 CORE&DDRII

PWR CON/F-PNL/VBAT/SPKR

PWR SEQU & VID BUFFER

OVP/FAN/CPU CHANGE

ACPI VREG

RGB & HDMI PORT

USB+RJ45/1394 CONN

DAC & DVI

K/M+FLASH+FDC+FP-USB

MEM VDD/MEM VTT/LAN

IDE 1/2

MCP68 CORE-AUX-HT-VREGS

MOUNTING HOLES

AN52

MCP65 CRB ATX

http://laptop-motherboard-schematic.blogspot.com/

5678

4

D

C

B

A

Title

COVER

Size Document Number Rev

Custom

3 1

Date: Sheet

AN52

2

V0.1

142Friday, March 02, 2007

of

8

7

6 432 1

5

BLOCK DIAGRAM

D

PRIMARY IDE

X4 - SATA CONN

FLOPPY CONN

PS2/KBRD CONN

PARALLEL CONN

POWER

SUPPLY

CONNECTOR

THERM MONITOR

PEX X16

PEX X1

ATA 133

INTEGRATED SATA CONTROLLERS (X2)

SIO

W83627DHG

VREG

PCI EXPRESS

PCI EXPRESS

LPC BUS 33MHZ

AM2 SOCKET 940

NFORCE

MCP68

692 BGA

HT 16X16 1GHZ

128-BIT 400/533/667/800MHZ

PCI 33MHZ

HDA 7.1 AUDIO

RGB

HDMI

X12 USB2

ALC888

RGB

HDMI

BACK PANEL CONN

USB2 PORTS 4-5

X2/GBIT LAN

USB2 PORTS 0-3

FRONT PANEL HDR

USB2 PORTS 6-7

USB2 PORTS 8-9

DDRII SDRAM CONN 0

DDRII SDRAM CONN 1

DDRII SDRAM CONN 2

DDRII SDRAM CONN 3

PCI SLOT 1

PCI SLOT 2

D

CC

BB

SERIAL CONN

8

LPC HDR

4MB FLASH

TPM

76

MII/RGMII

http://laptop-motherboard-schematic.blogspot.com/

435

MII/RGMII

88E1116

Title

BLOCK DIAGRAM

Size Document Number Rev

Custom

Date: Sheet

AN52

21

242Friday, March 02, 2007

of

AA

V0.1

8

7

6 432 1

5

AM2 SOCKET 940

D

PWR CONN

PWR GOOD

PWRGD SB

CIRCUIT

PWR SWTCH

PS ON

PEX0 X16

PEX1 X1

SIO

PSIN* PSOUT*

PSON*

SUSB*

PWRBTN*

SLP_S3*

POWER_GOOD

PWRGD_SB

PE_RESET*

PWR BUTTON

SLP S3*

PWRGD

PWRGD_SB

MIIRESET*

HT MCP RST*

HT MCP PWRGD

MCP68/65

CPU PWRGD

CPU RST*

PCI RST0*

PCI RST1*

PCI RST2*

PCI RST3*

LPC_RST*

HDA_RESET*

HT_MCP_RST*

HT_MCP_PWRGD

PCIRST_SLOT1*

PCIRST_SLOT2*

PCIRST_IDE*

LPCRST_FLASH*

LPCRST_SIO*

SIO PRI IDE

FLASH

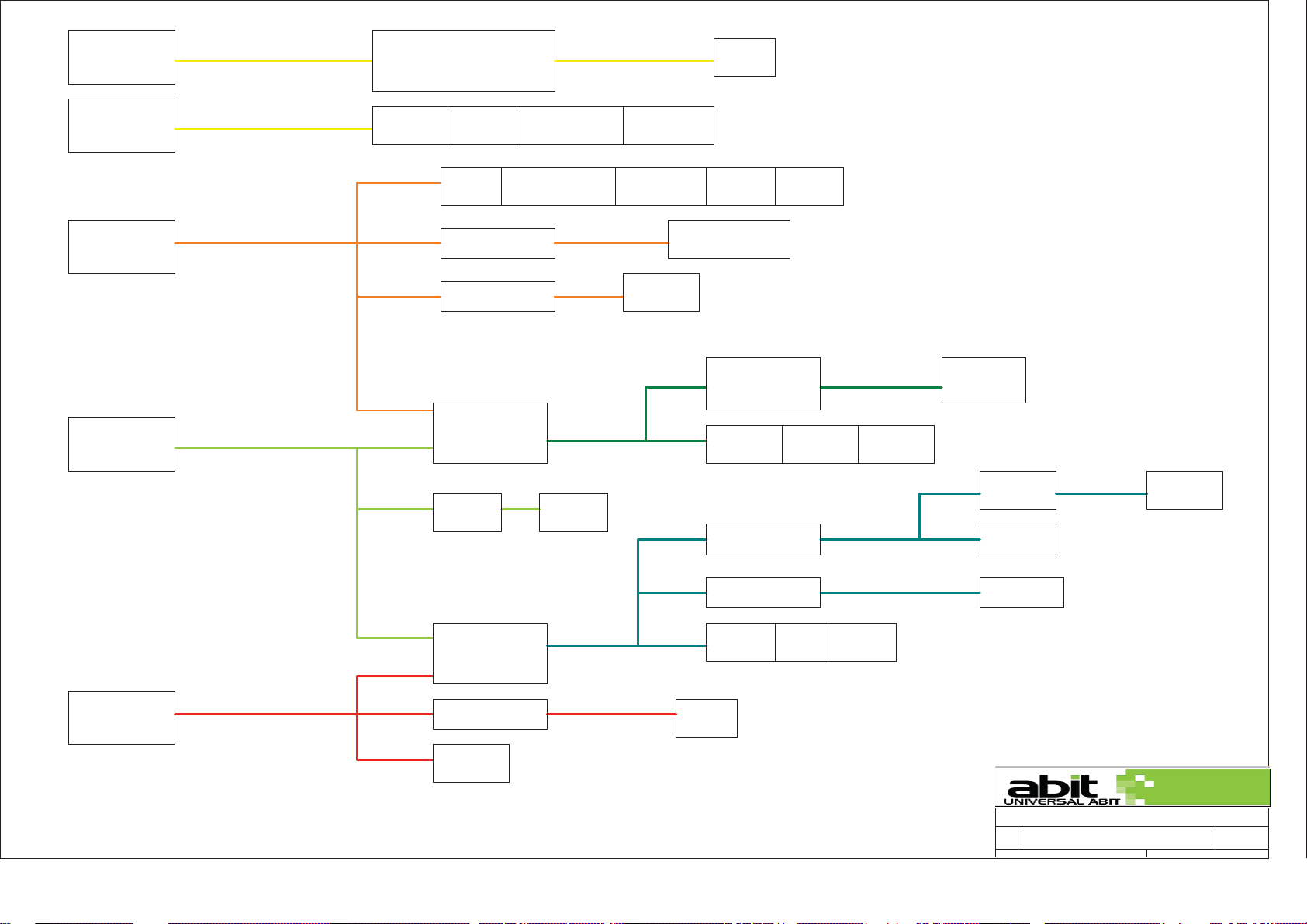

RESET MAP

PCI SLOT 2

D

CC

BB

PCI SLOT 1

AA

LAN_PHY

RESET*

8

76

AUDIO_PHY

RESET*

http://laptop-motherboard-schematic.blogspot.com/

435

Title

RESET MAP

Size Document Number Rev

Custom

Date: Sheet

AN-M2

21

342Friday, March 02, 2007

of

V0.1

8

7

6 432 1

5

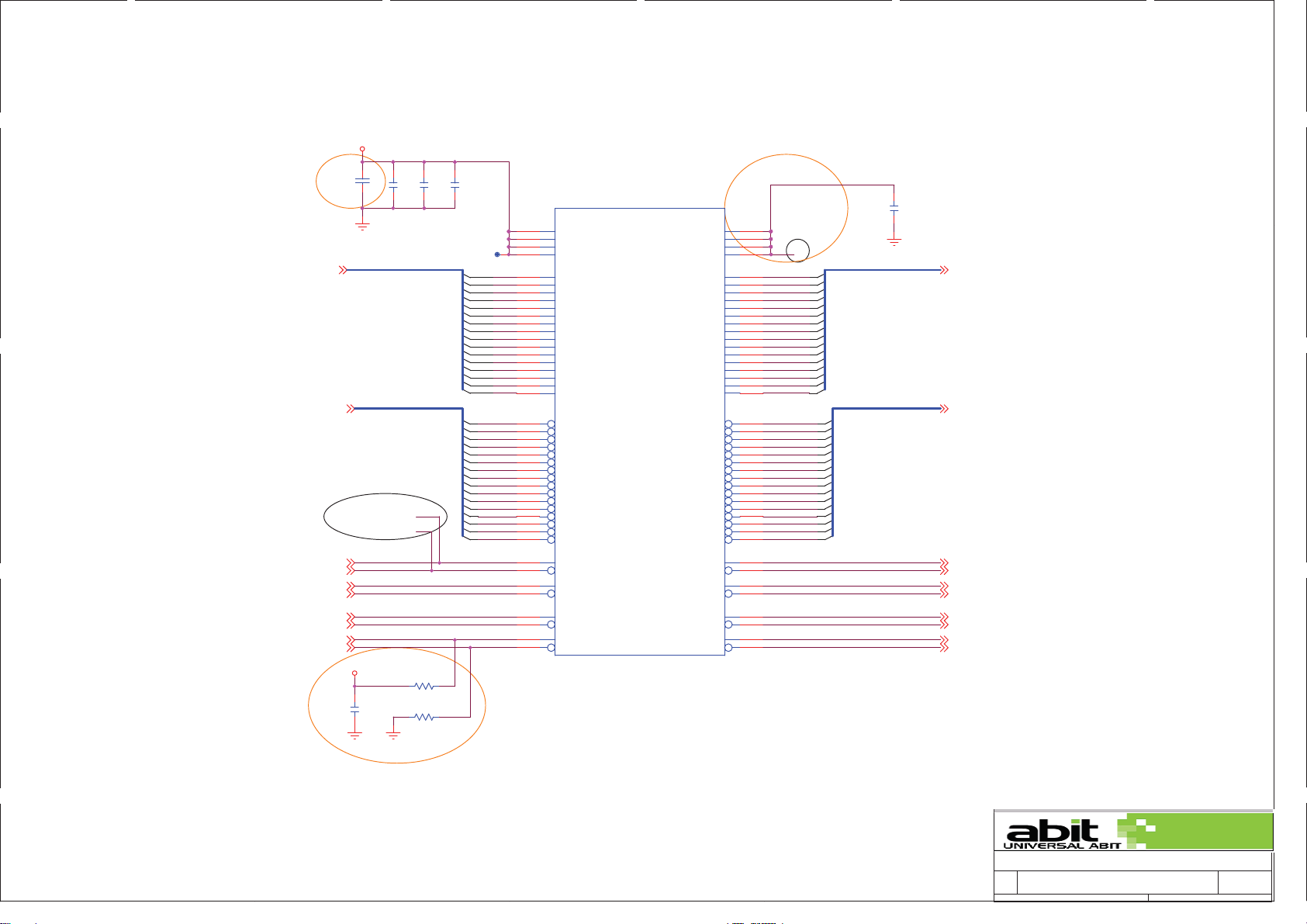

AM2 SOCKET 940

HT_CPU_TXCLK0

HT_CPU_TXCLK0*

HT_CPU_RXCLK0

D

HT_CPU_RXCLK0*

HT_CPU_TXCLK1

HT_CPU_TXCLK1*

HT_CPU_RXCLK1

HT_CPU_RXCLK1*

CPUCLK_IN*

CPUCLK_IN

CLKOUT_200MHZ

CLKOUT_200MHZ*

HT_CPU_RXCLK1*

HT_CPU_RXCLK1

HT_CPU_TXCLK1*

HT_CPU_TXCLK1

HT_CPU_RXCLK0*

HT_CPU_RXCLK0

HT_CPU_TXCLK0*

HT_CPU_TXCLK0

MEMORY_A0_CLK[2:0]

MEMORY_A0_CLK[2:0]*

MEMORY_B0_CLK[2:0]

MEMORY_B0_CLK[2:0]*

MEMORY_A1_CLK[2:0]

MEMORY_A1_CLK[2:0]*

MEMORY_B1_CLK[2:0]

MEMORY_B1_CLK[2:0]*

MCP68/65

PE0_REFCLK

PE0_REFCLK*

PE1_REFCLK

PE1_REFCLK*

BUF_SIO

14MHZ OR 24MHZ*

LPC_CLK0

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLKIN

LPC_CLK1

CHANNEL A0 0-63

CHANNEL B0 64-127

CHANNEL A1 0-63

CHANNEL B1 64-127

SIO

DIMM 0

DIMM 1

DIMM 2

DIMM 3

PE0 X16

PE1 X1

PCI SLOT 1

PCI SLOT 2

TPM

D

CC

BB

FLASH LPC

HEADER

Title

CLOCK DIAGRAM

Size Document Number Rev

Custom

Date: Sheet

AN52

21

442Friday, March 02, 2007

of

AA

V0.1

32.0 KHZ

25 MHZ

RTC_XTAL

XTAL_IN

XTAL_OUT

HDA_BITCLK

RGMII_TXCLK

RGMII_RXCLK

BUF_25MHZ

HDA

CODEC

LAN

PHY

http://laptop-motherboard-schematic.blogspot.com/

8

76

435

8

ழ೯܂

7

6 432 1

5

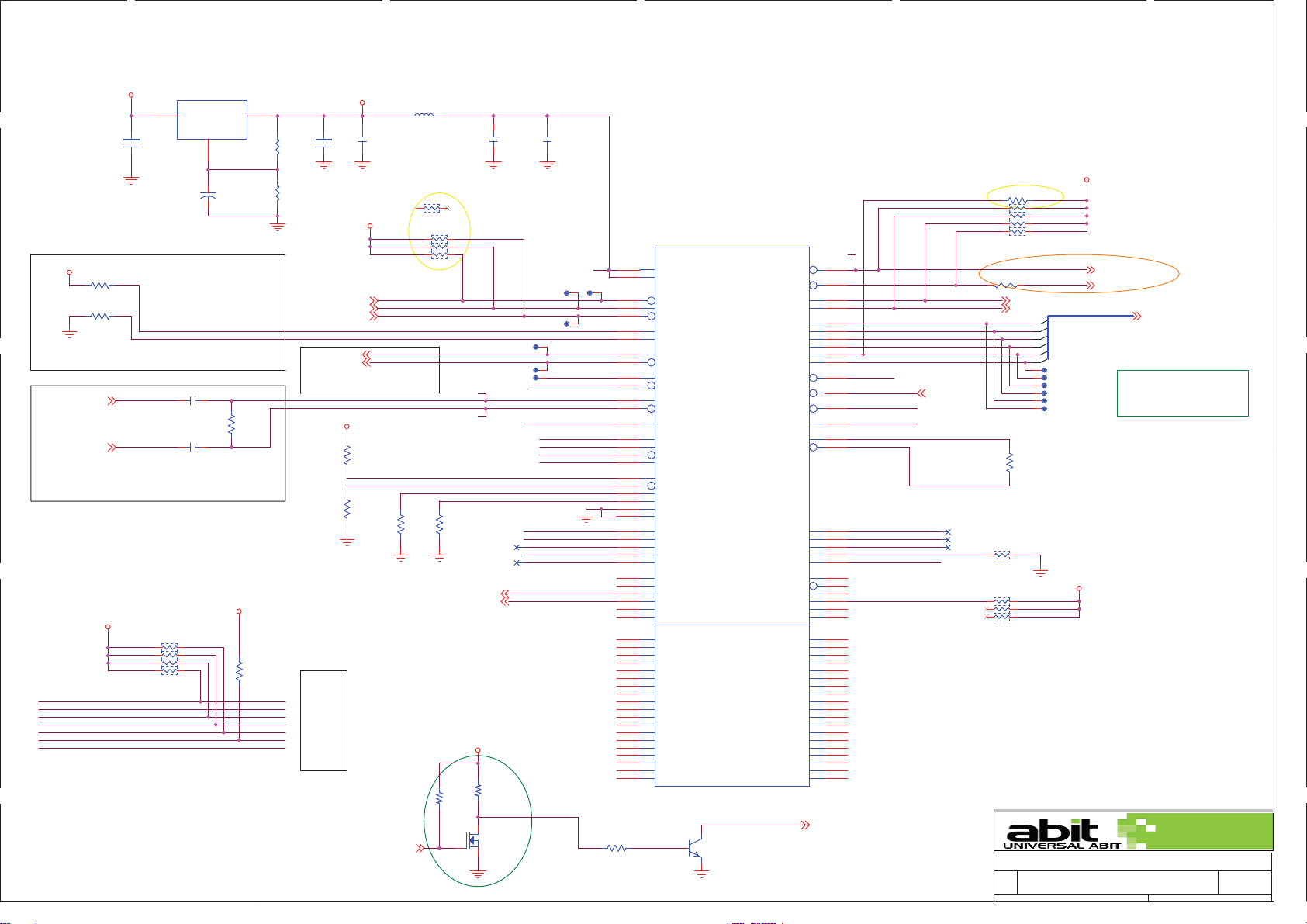

SIO_PSIN*

D

1

PWR_ON

FPIO

POWER UP

D

PSIN#/GP56(68)

PSOUT#/GP57(67)

W83627DHG

PSON#

PWRGD

ATX

PS_ON*

PWRBTN*

S3#

PWRGD_PS

W83303AD_PS_OUT*

6

2

PWRBTN*(G4)

SLP_S3*(G8)

MCP55

MEMVLD(J3)

SLP_S5*(H8)

3

MEMVLD

S5#

4

PWRGD

MCP55_PWRGD

CPUVDD_EN(J2)

MCPVDD/HT_EN(J4)

MCPVDD/HT_VLD(H3)

159

HT_VLD

CPUVDD_EN

CPU_VLD

12

5

SEQ SEQSEQ

V1P2_HT

S5# 5VDRV

S3#

PS_IN#

8

PWRGD

W83304CG

PS_OUT*

LR1_DRV

LR1_SEN

FAULT#

HTVDD_EN

13

14

10

CPUVDD_EN(12)

CPU_VLD(4)CPU_VLD(J1)

RT8801

RT9605B

VCCP

11

CC

BB

Power Supply

8

7

76

http://laptop-motherboard-schematic.blogspot.com/

435

Title

POWER SEQ MAP

Size Document Number Rev

Custom

Date: Sheet

AN52

21

542Friday, March 02, 2007

of

AA

V0.1

VCC12A

VCC12

(14.1A)

(6.45A)

VCC12

RT8801B+RT9605A

108N03(3)+108N03*2(3)

PCI/3

(1.5A)

FAN/4

(1.2A)

PCIEx16/1

(2.75A)

PCIEx1/2

(1A)

CPUVCCP(1.35V)

(100A)

(8.15A)

(1.5A)

VCC3

(14.05A)

VCC3

(1.2A)

(3.38A)

PHD55N03(2)

(6.71A)

VCC5SB

VCC5 CPU

VCC5SB

(20.81A)

VCC5

(1.32A)

(0.53A)

(0.04A)

(6.14A)

(13.01A)

(0.3A)

(7.5A)

W83304CG

PHD55N03(2)

RT9179

W83304CG

PHD55N03(2)

RC1117ST

PCI/3

(7.5A)

PCIEx16/1

W83304CG

PHD55N03

W83320

(3A)

V1P2_LDT

V1P2

3VDUAL

ALC622

(0.038A)

(13.01A)

5VDUAL

V2P5_VDDA

http://laptop-motherboard-schematic.blogspot.com/

PCIEx1/2

(3A)

MCP65S

(6.75A)

(0.23A)

(1.09A)

(6.87A)

(0.10A)

(6.04A)

MCP65SPCI/1

(0.62A)

CPU/MCP65S

(0.5A)

(0.7A)

W83304CG

55N03(1)

MCP65S

(0.56A)

W83320

PHD55N03(2)

RC1117ST

USB X10

(5A)

(0.3A)

ALC622

(0.03A)

88E3018

(0.01A)

KB/MS

(1A)

V1P2_DUAL

88E8056

(0.52A)

(1.25A)

(15.25A)

VDD_MEM

(1.8V)

(14A)

V2P5_DUAL_LAN

ALC622

(0.038mA)

MCP65S

(0.23A)

(2A)

W83310

DIMM/4

(14A)

88E3018

(0.10A)

Title

Size Document Number Rev

Custom

Date: Sheet

VTT_MEM

POWER DELIVERY

AN52

DIMM/4

(2A)

642Friday, March 02, 2007

V0.1

of

5

A

4

3

2

1

D D

V_HT

V_HT

V_HT

V_HT

CPU produce it itself

+1.2V_HT_CPU

2.5 V

AJ1

AJ2

AJ3

AJ4

˛˧˖ˣ˨˲˗˪ˡ˄ˈ

Y5

˛˧˖ˣ˨˲˗˪ˡ˄ˇ

AB6

˛˧˖ˣ˨˲˗˪ˡ˄ˆ

AB5

˛˧˖ˣ˨˲˗˪ˡ˄˅

AD6

˛˧˖ˣ˨˲˗˪ˡ˄˄

AF6

˛˧˖ˣ˨˲˗˪ˡ˄˃

AF5

˛˧˖ˣ˨˲˗˪ˡˌ

AH6

˛˧˖ˣ˨˲˗˪ˡˋ

AH5

˛˧˖ˣ˨˲˗˪ˡˊ

Y1

˛˧˖ˣ˨˲˗˪ˡˉ

AA2

˛˧˖ˣ˨˲˗˪ˡˈ

AB1

˛˧˖ˣ˨˲˗˪ˡˇ

AC2

˛˧˖ˣ˨˲˗˪ˡˆ

AE2

˛˧˖ˣ˨˲˗˪ˡ˅

AF1

˛˧˖ˣ˨˲˗˪ˡ˄

AG2

˛˧˖ˣ˨˲˗˪ˡ˃

AH1

˛˧˖ˣ˨˲˗˪ˡʽ˄ˈ

Y4

˛˧˖ˣ˨˲˗˪ˡʽ˄ˇ

AA6

˛˧˖ˣ˨˲˗˪ˡʽ˄ˆ

AB4

˛˧˖ˣ˨˲˗˪ˡʽ˄˅

AC6

˛˧˖ˣ˨˲˗˪ˡʽ˄˄

AE6

˛˧˖ˣ˨˲˗˪ˡʽ˄˃

AF4

˛˧˖ˣ˨˲˗˪ˡʽˌ

AG6

˛˧˖ˣ˨˲˗˪ˡʽˋ

AH4

˛˧˖ˣ˨˲˗˪ˡʽˊ

W1

˛˧˖ˣ˨˲˗˪ˡʽˉ

AA3

˛˧˖ˣ˨˲˗˪ˡʽˈ

AA1

˛˧˖ˣ˨˲˗˪ˡʽˇ

AC3

˛˧˖ˣ˨˲˗˪ˡʽˆ

AE3

˛˧˖ˣ˨˲˗˪ˡʽ˅

AE1

˛˧˖ˣ˨˲˗˪ˡʽ˄

AG3

˛˧˖ˣ˨˲˗˪ˡʽ˃

AG1

AD1

AC1

AD5

AD4

W2

W3

Y6

W6

12

CT46

4.7UF/0805Y/10V-LF

C0805

?

10V

10%

I

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

HTCPU_DWN[15..0]

HTCPU_DWN*[15..0]

HTCPU_DWNCLK0

HTCPU_DWNCLK0*

HTCPU_DWNCLK1

HTCPU_DWNCLK1*

HTCPU_DWNCNTL0

HTCPU_DWNCNTL0*

HTCPU_DWNCNTL1

HTCPU_DWNCNTL1*

HTCPU_DWN[15..0] 18

HTCPU_DWN*[15..0] 18

HTCPU_DWNCLK0 18

HTCPU_DWNCLK0* 18

HTCPU_DWNCLK1 18

HTCPU_DWNCLK1* 18

HTCPU_DWNCNTL0 18

HTCPU_DWNCNTL0* 18

HTCPU_DWNCNTL1 18

HTCPU_DWNCNTL1* 18

V1P2_LDT

V0.1 220PF ->2200PF

2200PF/X7R/16V-LF

HTCPU_UP[15..0]18

12

C84

C85

x0.1UF/16V-LF

C0603

X5R

16V

10%

HTCPU_UP[15..0]

C C

v0.2

Layout add Text

HTCPU_UPCLK0

HTCPU_UPCLK0*

HTCPU_UPCLK1

HTCPU_UPCLK1*

HTCPU_UPCNTL0

HTCPU_UPCNTL0*

HTCPU_UPCNTL1

HTCPU_UPCNTL1*

V1P2_LDT

12

C81

0.1UF/X7R/16V-LF

C0603

X5R

16V

10%

HTCPU_UP*[15..0]

1 2

HTCPU_UP*[15..0]18

HTCPU_UPCLK018

B B

HTCPU_UPCLK0*18

HTCPU_UPCLK118

HTCPU_UPCLK1*18

HTCPU_UPCNTL018

HTCPU_UPCNTL0*18

HTCPU_UPCNTL118

HTCPU_UPCNTL1*18

W

X

R89

R90

51.1-1%-LF

12

C83

0.1UF/X7R/16V-LF

C0603

X5R

16V

10%

51.1-1%-LF

12

V0.1

12

C82

x0.1UF/16V-LF

C0603

X5R

16V

10%

U7A

SK-C940P-M2

V_HT

H1

V_HT

H2

V_HT

H5

J

15

˛˧˖ˣ˨˲˨ˣ˄ˈ

14

˛˧˖ˣ˨˲˨ˣ˄ˇ

13

˛˧˖ˣ˨˲˨ˣ˄ˆ

12

˛˧˖ˣ˨˲˨ˣ˄˅

11

˛˧˖ˣ˨˲˨ˣ˄˄

10

˛˧˖ˣ˨˲˨ˣ˄˃

9

˛˧˖ˣ˨˲˨ˣˌ

8

˛˧˖ˣ˨˲˨ˣˋ

7

˛˧˖ˣ˨˲˨ˣˊ

6

˛˧˖ˣ˨˲˨ˣˉ

5

˛˧˖ˣ˨˲˨ˣˈ

4

˛˧˖ˣ˨˲˨ˣˇ

3

˛˧˖ˣ˨˲˨ˣˆ

2

˛˧˖ˣ˨˲˨ˣ˅

1

˛˧˖ˣ˨˲˨ˣ˄

0

˛˧˖ˣ˨˲˨ˣ˃

15

˛˧˖ˣ˨˲˨ˣʽ˄ˈ

14

˛˧˖ˣ˨˲˨ˣʽ˄ˇ

13

˛˧˖ˣ˨˲˨ˣʽ˄ˆ

12

˛˧˖ˣ˨˲˨ˣʽ˄˅

11

˛˧˖ˣ˨˲˨ˣʽ˄˄

10

˛˧˖ˣ˨˲˨ˣʽ˄˃

9

˛˧˖ˣ˨˲˨ˣʽˌ

8

˛˧˖ˣ˨˲˨ˣʽˋ

7

˛˧˖ˣ˨˲˨ˣʽˊ

6

˛˧˖ˣ˨˲˨ˣʽˉ

5

˛˧˖ˣ˨˲˨ˣʽˈ

4

˛˧˖ˣ˨˲˨ˣʽˇ

3

˛˧˖ˣ˨˲˨ˣʽˆ

2

˛˧˖ˣ˨˲˨ˣʽ˅

1

˛˧˖ˣ˨˲˨ˣʽ˄

0

˛˧˖ˣ˨˲˨ˣʽ˃

V_HT

H6

HT_RXD<15>

U6

HT_RXD<14>

T4

HT_RXD<13>

R6

HT_RXD<12>

P4

HT_RXD<11>

M4

HT_RXD<10>

L6

HT_RXD<9>

K4

HT_RXD<8>

J6

HT_RXD<7>

U3

HT_RXD<6>

R1

HT_RXD<5>

R3

HT_RXD<4>

N1

HT_RXD<3>

L1

HT_RXD<2>

L3

HT_RXD<1>

J1

HT_RXD<0> HT_TXD<0>

J3

HT_RXD<15>*

V6

HT_RXD<14>*

T5

HT_RXD<13>*

T6

HT_RXD<12>*

P5

HT_RXD<11>*

M5

HT_RXD<10>*

M6

HT_RXD<9>*

K5

HT_RXD<8>*

K6

HT_RXD<7>*

U2

HT_RXD<6>*

T1

HT_RXD<5>*

R2

HT_RXD<4>*

P1

HT_RXD<3>*

M1

HT_RXD<2>*

L2

HT_RXD<1>*

K1

HT_RXD<0>* HT_TXD<0>*

J2

HT_RXCLK<0>

N3

HT_RXCLK<0>*

N2

HT_RXCLK<1>

N6

HT_RXCLK<1>*

P6

HT_RXCTL<0>

U1

HT_RXCTL<0>*

V1

HT_RXCTL<1>

V4

HT_RXCTL<1>*

V5

SOCKET_940_M2

SEC 1 OF 6

HT_TXD<15>

HT_TXD<14>

HT_TXD<13>

HT_TXD<12>

HT_TXD<11>

HT_TXD<10>

HT_TXD<9>

HT_TXD<8>

HT_TXD<7>

HT_TXD<6>

HT_TXD<5>

HT_TXD<4>

HT_TXD<3>

HT_TXD<2>

HT_TXD<1>

HT_TXD<15>*

HT_TXD<14>*

HT_TXD<13>*

HT_TXD<12>*

HT_TXD<11>*

HT_TXD<10>*

HT_TXD<9>*

HT_TXD<8>*

HT_TXD<7>*

HT_TXD<6>*

HT_TXD<5>*

HT_TXD<4>*

HT_TXD<3>*

HT_TXD<2>*

HT_TXD<1>*

HT_TXCLK<0>

HT_TXCLK<0>*

HT_TXCLK<1>

HT_TXCLK<1>*

HT_TXCTL<0>

HT_TXCTL<0>*

HT_TXCTL<1>

HT_TXCTL<1>*

I230

http://laptop-motherboard-schematic.blogspot.com/

A

Title

MCP68/65 HT/CLKS

Size Document Number Rev

A3

5

4

3

2

Date: Sheet

AN52

1

V0.1

742Friday, March 02, 2007

of

5

A

4

3

2

1

M2 CPU VDDA

@250mA

VCC5

D D

0805

V1P2_LDT

R75

1 2

1%

R0603

44.2-1%-LF

R81

1 2

R0603

1%

44.2-1%-LF

C C

CPU_CLK18

CPU_CLK*18

PLACE WITHIN 1 INCH

5MIL TRACE 10MIL SPACE

CPU_CLK

CPU_CLK*

U3 RC1117ST/SOT223-LF

CT3

4.7UF/0805Y/10V-LF

SOT223

ADJ(I)

G

C29

x0.1UF

C65

12

C0603

X7R

3900PF/X7R/16V-LF

50V

10%

C67

12

C0603

X7R

3900PF/X7R/16V-LF

50V

10%

OUT(O)IN(I)

124-1%-LF

124-1%-LF

1 2

R67

169-1%-LF

1%

R0603

OI

R42

R1

1%

R43

R2

1%

ROUTE AS DIF 5/5/5/20

B B

VDDMEM

RN22-1 330-8P4R-LF

1 8

RN22-2 330-8P4R-LF

2 7

RN22-3 330-8P4R-LF

3 6

RN22-4 330-8P4R-LF

4 5

CPU_DBREQ*

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST*

CPU_TDO

5

VDDMEM

HDT CONNECTOR

R129

220-LF

5%

R0603

1 2

V2P5_VDDA

CT20

0805

4.7UF/0805Y/10V-LF

HTCPU_RST*18

HTCPU_PWRGD18

HTCPU_STOP*18

CPU_CORE_FB35

CPU_CORE_FB*35

ROUTE AS DIFF PAIR

10/5/10 10

VDDMEM

R62

560-1%-LF

1%

R0603

1 2

R63

560-1%-LF

1%

R0603

1 2

DISABLEΚHigh

from SIO / GPIO

FB3

30 OHM/100MHz/3A/0603-LF

1 2

12

C16

C0603

X5R

16V

10%

0.1UF/X7R/16V-LF

L06033000MA FB

RN3-1 1K-8P4R-LF

1 8

VDDMEM

RN3-3 1K-8P4R-LF

3 6

RN3-2 1K-8P4R-LF

2 7

RN3-4 1K-8P4R-LF

4 5

HTCPU_RST*

HTCPU_PWRGD

HTCPU_STOP*

CPU_CORE_FB

CPU_CORE_FB*

CPU_TEST25

CPU_TEST25*

R59

R55

220-LF

220-LF

5%

5%

R0603

R0603

1 2

1 2

CPU_THERMDC32

CPU_THERMDA32

1

R50

4.7K-0402-LF

2

PROCHOT_EN*32

G

4

V2P5_CPU_VDDA

12

CT24

C0805

?

10V

10%

4.7UF/0805Y/10V-LF

V0.2 330->1K

F

G

3VDUAL

1

R49

4.7K-0402-LF

2

VREG_PROCHOT

DS

Q10

2N7002/100mA-LF

12

C62

C0603

X7R

50V

10%

3900PF/X7R/16V-LF

U7B

SK-C940P-M2

K

N

M

A

B

TP_CPU_VDDIOFB

C

D

TP_CPU_VDDIOFB*

CLKIN

CLKIN*

NC

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST*

CPU_TDI

CPU_TEST19

CPU_TEST18

TP_CPU_TEST17

TP_CPU_TEST16

TP_CPU_TEST15

TP_CPU_TEST14

TP_CPU_TEST12

CPU_THERMDC

CPU_THERMDA

O

HT_REF1

HT_REF0

http://laptop-motherboard-schematic.blogspot.com/

1 2

VDDA

C10

VDDA

D10

RESET*

C7

PWROK

C9

LDTSTOP*

D8

HTREF1

V8

HTREF0

V7

VDD_FB

G2

VDD_FB*

G1

VDDIO_FB

AK11

VDDIO_FB*

AL11

CLKIN

A8

CLKIN*

B8

DBRDY

B6

TMS

AL9

TCK

AH10

TRST*

AJ10

TDI

AL10

TEST25

A10

TEST25*

B10

TEST19

F10

TEST18

E9

TEST13

AJ7

TEST9

F6

TEST17

D6

TEST16

E7

TEST15

F8

TEST14

C5

TEST12

AH9

TEST7

E5

TEST6

AJ5

TEST5/THERMDC

AG9

TEST4/THERMDA

AG8

TEST3

AH7

TEST2

AJ6

RSVD

AD25

RSVD

AE24

RSVD

AE25

RSVD

AE27

RSVD

AE28

RSVD

AF31

RSVD

AG31

RSVD

AJ18

RSVD

AJ20

RSVD

AK3

RSVD

AK4

RSVD

AL4

RSVD

B19

RSVD

C18

RSVD

C20

RSVD

E20

RSVD

F2

RSVD

F3

RSVD RSVD

G24

I235

R56

VREG_PROCHOT_R

5%R0603

220-LF

3

Q17

MMBT3904

B

TR-SOT23

SOCKET_940_M2

SEC 2 OF 6

CPU_PROCHOT*

C

E

THERMTRIP*

PROCHOT*

SID

SIC

VID<5>

VID<4>

VID<3>

VID<2>

VID<1>

VID<0>

PSI*

CPU_PRESENT*

DBREQ*

TDO

TEST29

TEST29*

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28

TEST28*

TEST27

TEST26

TEST10

TEST8

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

V

AK7

AL7

AK6

AL6

D2

D1

C1

E3

E2

E1

TP_CPU_PSI*

F1

CPU_PRSNT*

AL3

CPU_DBREQ*

A5

CPU_TDO

AK10

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

G25

G3

G4

G5

H25

L25

L26

L30

L31

U24

V24

V29

V31

W25

W26

W30

W31

Y30

Y31

CPU_PROCHOT* 18

RN19-1 330-8P4R-LF

RN19-4 330-8P4R-LF

RN19-3 330-8P4R-LF

RN19-2 330-8P4R-LF

R117 0-LF

THERM_SID

THERM_SIC

˖ˣ˨˲˩˜˗ˈ

˖ˣ˨˲˩˜˗ˇ

˖ˣ˨˲˩˜˗ˆ

˖ˣ˨˲˩˜˗˅

˖ˣ˨˲˩˜˗˄

˖ˣ˨˲˩˜˗˃

mcp55

mcp55

CPU_GND 38

NC

FBCLKOUT

FBCLKOUT*

LAYOUT: ROUTE 80 OHM DIFF IMPEDENCE

LAYOUT: PLACE WITHIN 0.5 INCH OF CPU

TP_CPU_TEST24

TP_CPU_TEST23

TP_CPU_TEST22

CPU_TEST21

TP_CPU_TEST20

CPU_TEST26

RN21-1 330-8P4R-LF

NC

1 8

RN21-2 330-8P4R-LF

2 7

RN21-3 330-8P4R-LF

3 6

RN21-4 330-8P4R-LF

4 5

2

P

Q

R

S

T

U

8/5/8/20LAYOUT: PLACE 169 OHM WITHIN 0.5INCH OF CPU

VDDMEM

CPU_THERMTRIP* 18,43

CPU_PROCHOT* 18

CPU_VID[5..0]

CPU_PRSNT* PULL VOTLAGE

CAN BE ANY VOLTAGE

V0.1

CPU_VID[5..0] 37

V0.2

R493 330-LF

1 2

1 8

4 5

3 6

2 7

CPU_THERMTRIP*

CPU_PROCHOT*

THERM_SID 23

THERM_SIC 23

R68

80.6-1%-LF

1%

R0603

5

4

3

2

1

0

1 2

VDDMEM

Title

MCP68/65 HT/CLKS

Size Document Number Rev

A3

Date: Sheet

AN52

842Thursday, March 08, 2007

of

1

V0.1

A

5

A

D D

MEM_A_DATA[63..0]13,15

C C

B B

MEM_A_ADD[15..0]13,15,17

MEM_A_ADD[15..0]

4

MEM_A_DATA[63..0]

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ˠ˘ˠ˲˔˲˗˔˧˔ˉˆ

ˠ˘ˠ˲˔˲˗˔˧˔ˉ˅

ˠ˘ˠ˲˔˲˗˔˧˔ˉ˄

ˠ˘ˠ˲˔˲˗˔˧˔ˉ˃

ˠ˘ˠ˲˔˲˗˔˧˔ˈˌ

ˠ˘ˠ˲˔˲˗˔˧˔ˈˋ

ˠ˘ˠ˲˔˲˗˔˧˔ˈˊ

ˠ˘ˠ˲˔˲˗˔˧˔ˈˉ

ˠ˘ˠ˲˔˲˗˔˧˔ˈˈ

ˠ˘ˠ˲˔˲˗˔˧˔ˈˇ

ˠ˘ˠ˲˔˲˗˔˧˔ˈˆ

ˠ˘ˠ˲˔˲˗˔˧˔ˈ˅

ˠ˘ˠ˲˔˲˗˔˧˔ˈ˄

ˠ˘ˠ˲˔˲˗˔˧˔ˈ˃

ˠ˘ˠ˲˔˲˗˔˧˔ˇˌ

ˠ˘ˠ˲˔˲˗˔˧˔ˇˋ

ˠ˘ˠ˲˔˲˗˔˧˔ˇˊ

ˠ˘ˠ˲˔˲˗˔˧˔ˇˉ

ˠ˘ˠ˲˔˲˗˔˧˔ˇˈ

ˠ˘ˠ˲˔˲˗˔˧˔ˇˇ

ˠ˘ˠ˲˔˲˗˔˧˔ˇˆ

ˠ˘ˠ˲˔˲˗˔˧˔ˇ˅

ˠ˘ˠ˲˔˲˗˔˧˔ˇ˄

ˠ˘ˠ˲˔˲˗˔˧˔ˇ˃

ˠ˘ˠ˲˔˲˗˔˧˔ˆˌ

ˠ˘ˠ˲˔˲˗˔˧˔ˆˋ

ˠ˘ˠ˲˔˲˗˔˧˔ˆˊ

ˠ˘ˠ˲˔˲˗˔˧˔ˆˉ

ˠ˘ˠ˲˔˲˗˔˧˔ˆˈ

ˠ˘ˠ˲˔˲˗˔˧˔ˆˇ

ˠ˘ˠ˲˔˲˗˔˧˔ˆˆ

ˠ˘ˠ˲˔˲˗˔˧˔ˆ˅

ˠ˘ˠ˲˔˲˗˔˧˔ˆ˄

ˠ˘ˠ˲˔˲˗˔˧˔ˆ˃

ˠ˘ˠ˲˔˲˗˔˧˔˅ˌ

ˠ˘ˠ˲˔˲˗˔˧˔˅ˋ

ˠ˘ˠ˲˔˲˗˔˧˔˅ˊ

ˠ˘ˠ˲˔˲˗˔˧˔˅ˉ

ˠ˘ˠ˲˔˲˗˔˧˔˅ˈ

ˠ˘ˠ˲˔˲˗˔˧˔˅ˇ

ˠ˘ˠ˲˔˲˗˔˧˔˅ˆ

ˠ˘ˠ˲˔˲˗˔˧˔˅˅

ˠ˘ˠ˲˔˲˗˔˧˔˅˄

ˠ˘ˠ˲˔˲˗˔˧˔˅˃

ˠ˘ˠ˲˔˲˗˔˧˔˄ˌ

ˠ˘ˠ˲˔˲˗˔˧˔˄ˋ

ˠ˘ˠ˲˔˲˗˔˧˔˄ˊ

ˠ˘ˠ˲˔˲˗˔˧˔˄ˉ

ˠ˘ˠ˲˔˲˗˔˧˔˄ˈ

ˠ˘ˠ˲˔˲˗˔˧˔˄ˇ

ˠ˘ˠ˲˔˲˗˔˧˔˄ˆ

ˠ˘ˠ˲˔˲˗˔˧˔˄˅

ˠ˘ˠ˲˔˲˗˔˧˔˄˄

ˠ˘ˠ˲˔˲˗˔˧˔˄˃

ˠ˘ˠ˲˔˲˗˔˧˔ˌ

ˠ˘ˠ˲˔˲˗˔˧˔ˋ

ˠ˘ˠ˲˔˲˗˔˧˔ˊ

ˠ˘ˠ˲˔˲˗˔˧˔ˉ

ˠ˘ˠ˲˔˲˗˔˧˔ˈ

ˠ˘ˠ˲˔˲˗˔˧˔ˇ

ˠ˘ˠ˲˔˲˗˔˧˔ˆ

ˠ˘ˠ˲˔˲˗˔˧˔˅

ˠ˘ˠ˲˔˲˗˔˧˔˄

ˠ˘ˠ˲˔˲˗˔˧˔˃

15

ˠ˘ˠ˲˔˲˔˗˗˄ˈ

14

ˠ˘ˠ˲˔˲˔˗˗˄ˇ

13

ˠ˘ˠ˲˔˲˔˗˗˄ˆ

12

ˠ˘ˠ˲˔˲˔˗˗˄˅

11

ˠ˘ˠ˲˔˲˔˗˗˄˄

10

ˠ˘ˠ˲˔˲˔˗˗˄˃

9

ˠ˘ˠ˲˔˲˔˗˗ˌ

8

ˠ˘ˠ˲˔˲˔˗˗ˋ

7

ˠ˘ˠ˲˔˲˔˗˗ˊ

6

ˠ˘ˠ˲˔˲˔˗˗ˉ

5

ˠ˘ˠ˲˔˲˔˗˗ˈ

4

ˠ˘ˠ˲˔˲˔˗˗ˇ

3

ˠ˘ˠ˲˔˲˔˗˗ˆ

2

ˠ˘ˠ˲˔˲˔˗˗˅

1

ˠ˘ˠ˲˔˲˔˗˗˄

0

ˠ˘ˠ˲˔˲˔˗˗˃

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

U7C

SK-C940P-M2

MA_DATA<63>

MA_DATA<62>

MA_DATA<61>

MA_DATA<60>

MA_DATA<59>

MA_DATA<58>

MA_DATA<57>

MA_DATA<56>

MA_DATA<55>

MA_DATA<54>

MA_DATA<53>

MA_DATA<52>

MA_DATA<51>

MA_DATA<50>

MA_DATA<49>

MA_DATA<48>

MA_DATA<47>

MA_DATA<46>

MA_DATA<45>

MA_DATA<44>

MA_DATA<43>

MA_DATA<42>

MA_DATA<41>

MA_DATA<40>

MA_DATA<39>

MA_DATA<38>

MA_DATA<37>

MA_DATA<36>

MA_DATA<35>

MA_DATA<34>

MA_DATA<33>

MA_DATA<32>

MA_DATA<31>

MA_DATA<30>

MA_DATA<29>

MA_DATA<28>

MA_DATA<27>

MA_DATA<26>

MA_DATA<25>

MA_DATA<24>

MA_DATA<23>

MA_DATA<22>

MA_DATA<21>

MA_DATA<20>

MA_DATA<19>

MA_DATA<18>

MA_DATA<17>

MA_DATA<16>

MA_DATA<15>

MA_DATA<14>

MA_DATA<13>

MA_DATA<12>

MA_DATA<11>

MA_DATA<10>

MA_DATA<9>

MA_DATA<8>

MA_DATA<7>

MA_DATA<6>

MA_DATA<5>

MA_DATA<4>

MA_DATA<3>

MA_DATA<2>

MA_DATA<1>

MA_DATA<0>

MA_ADD<15>

MA_ADD<14>

MA_ADD<13>

MA_ADD<12>

MA_ADD<11>

MA_ADD<10>

MA_ADD<9>

MA_ADD<8>

MA_ADD<7>

MA_ADD<6>

MA_ADD<5>

MA_ADD<4>

MA_ADD<3>

MA_ADD<2>

MA_ADD<1>

MA_ADD<0>

SOCKET_940_M2

SEC 3 OF 6

3

MA_CHECK<7>

MA_CHECK<6>

MA_CHECK<5>

MA_CHECK<4>

MA_CHECK<3>

MA_CHECK<2>

MA_CHECK<1>

MA_CHECK<0>

MA_DM<8>

MA_DM<7>

MA_DM<6>

MA_DM<5>

MA_DM<4>

MA_DM<3>

MA_DM<2>

MA_DM<1>

MA_DM<0>

MA_DQS<8>

MA_DQS<7>

MA_DQS<6>

MA_DQS<5>

MA_DQS<4>

MA_DQS<3>

MA_DQS<2>

MA_DQS<1>

MA_DQS<0>

MA_DQS<8>*

MA_DQS<7>*

MA_DQS<6>*

MA_DQS<5>*

MA_DQS<4>*

MA_DQS<3>*

MA_DQS<2>*

MA_DQS<1>*

MA_DQS<0>*

MA0_CLK<0>

MA0_CLK<0>*

MA0_CLK<1>

MA0_CLK<1>*

MA0_CLK<2>

MA0_CLK<2>*

MA1_CLK<0>

MA1_CLK<0>*

MA1_CLK<1>

MA1_CLK<1>*

MA1_CLK<2>

MA1_CLK<2>*

MA_BANK<2>

MA_BANK<1>

MA_BANK<0>

MA_RAS*

MA_CAS*

MA_WE*

MA0_CS<1>*

MA0_CS<0>*

MA1_CS<1>*

MA1_CS<0>*

MA_CKE<1>

MA_CKE<0>

MA0_ODT<0>

MA1_ODT<0>

K25

J26

G28

G27

L24

K27

H29

H27

J25

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

J28

AD15

AG18

AG24

AG27

D29

C25

E19

F15

J27

AE15

AG19

AG25

AG28

C29

D25

F19

G15

U27

U26

G19

H19

AG21

AG20

V27

W27

G20

G21

AE20

AE19

N25

Y27

AA27

AA26

AB25

AB27

AC25

AA24

AD27

AA25

L27

M25

AC28

AC27

MEM_A_ECC[7..0]

7

ˠ˘ˠ˲˔˲˘˖˖ˊ

6

ˠ˘ˠ˲˔˲˘˖˖ˉ

5

ˠ˘ˠ˲˔˲˘˖˖ˈ

4

ˠ˘ˠ˲˔˲˘˖˖ˇ

3

ˠ˘ˠ˲˔˲˘˖˖ˆ

2

ˠ˘ˠ˲˔˲˘˖˖˅

1

ˠ˘ˠ˲˔˲˘˖˖˄

0

ˠ˘ˠ˲˔˲˘˖˖˃

MEM_A_DM[8..0]

8

ˠ˘ˠ˲˔˲˗ˠˋ

7

ˠ˘ˠ˲˔˲˗ˠˊ

6

ˠ˘ˠ˲˔˲˗ˠˉ

5

ˠ˘ˠ˲˔˲˗ˠˈ

4

ˠ˘ˠ˲˔˲˗ˠˇ

3

ˠ˘ˠ˲˔˲˗ˠˆ

2

ˠ˘ˠ˲˔˲˗ˠ˅

1

ˠ˘ˠ˲˔˲˗ˠ˄

0

ˠ˘ˠ˲˔˲˗ˠ˃

MEM_A_DQS[8..0]

8

ˠ˘ˠ˲˔˲˗ˤ˦ˋ

7

ˠ˘ˠ˲˔˲˗ˤ˦ˊ

6

ˠ˘ˠ˲˔˲˗ˤ˦ˉ

5

ˠ˘ˠ˲˔˲˗ˤ˦ˈ

4

ˠ˘ˠ˲˔˲˗ˤ˦ˇ

3

ˠ˘ˠ˲˔˲˗ˤ˦ˆ

2

ˠ˘ˠ˲˔˲˗ˤ˦˅

1

ˠ˘ˠ˲˔˲˗ˤ˦˄

0

ˠ˘ˠ˲˔˲˗ˤ˦˃

MEM_A_DQS*[8..0]

8

ˠ˘ˠ˲˔˲˗ˤ˦ʽˋ

7

ˠ˘ˠ˲˔˲˗ˤ˦ʽˊ

6

ˠ˘ˠ˲˔˲˗ˤ˦ʽˉ

5

ˠ˘ˠ˲˔˲˗ˤ˦ʽˈ

4

ˠ˘ˠ˲˔˲˗ˤ˦ʽˇ

3

ˠ˘ˠ˲˔˲˗ˤ˦ʽˆ

2

ˠ˘ˠ˲˔˲˗ˤ˦ʽ˅

1

ˠ˘ˠ˲˔˲˗ˤ˦ʽ˄

0

ˠ˘ˠ˲˔˲˗ˤ˦ʽ˃

0

ˠ˘ˠ˲˔˃˲˖˟˞˃

1

ˠ˘ˠ˲˔˃˲˖˟˞˄

2

ˠ˘ˠ˲˔˃˲˖˟˞˅

0

ˠ˘ˠ˲˔˄˲˖˟˞˃

1

ˠ˘ˠ˲˔˄˲˖˟˞˄

2

ˠ˘ˠ˲˔˄˲˖˟˞˅

MEM_A_BA[2..0]

2

ˠ˘ˠ˲˔˲˕˔˅

1

ˠ˘ˠ˲˔˲˕˔˄

0

ˠ˘ˠ˲˔˲˕˔˃

MEM_A_RAS*

MEM_A_CAS*

MEM_A_WE*

MEM_A0_CS*[1..0]

1

ˠ˘ˠ˲˔˃˲˖˦ʽ˄

0

ˠ˘ˠ˲˔˃˲˖˦ʽ˃

MEM_A1_CS*[1..0]

1

ˠ˘ˠ˲˔˄˲˖˦ʽ˄

0

ˠ˘ˠ˲˔˄˲˖˦ʽ˃

MEM_A1_CKE

MEM_A0_CKE

MEM_A0_ODT

MEM_A1_ODT

MEM_A0_CLK[2..0]

MEM_A0_CLK*[2..0]

0

ˠ˘ˠ˲˔˃˲˖˟˞ʽ˃

1

ˠ˘ˠ˲˔˃˲˖˟˞ʽ˄

2

ˠ˘ˠ˲˔˃˲˖˟˞ʽ˅

MEM_A1_CLK[2..0]

MEM_A1_CLK*[2..0]

0

ˠ˘ˠ˲˔˄˲˖˟˞ʽ˃

1

ˠ˘ˠ˲˔˄˲˖˟˞ʽ˄

2

ˠ˘ˠ˲˔˄˲˖˟˞ʽ˅

2

MEM_A_ECC[7..0] 13,15

MEM_A_DM[8..0] 13,15

MEM_A_DQS[8..0] 13,15

MEM_A_DQS*[8..0] 13,15

MEM_A0_CLK[2..0] 13,17

MEM_A0_CLK*[2..0] 13,17

MEM_A1_CLK[2..0] 15,17

MEM_A1_CLK*[2..0] 15,17

MEM_A_BA[2..0] 13,15,17

MEM_A_RAS* 13,15,17

MEM_A_CAS* 13,15,17

MEM_A_WE* 13,15,17

MEM_A0_CS*[1..0] 13,17

MEM_A1_CS*[1..0] 15,17

MEM_A1_CKE 15,17

MEM_A0_CKE 13,17

MEM_A0_ODT 13,17

MEM_A1_ODT 15,17

1

I160

http://laptop-motherboard-schematic.blogspot.com/

A

Title

MCP68/65 HT/CLKS

Size Document Number Rev

A3

5

4

3

2

Date: Sheet

AN52

1

V0.1

942Friday, March 02, 2007

of

5

A

MEM_B_DATA[63..0]14,16

MEM_B_DATA[63..0]

D D

C C

B B

MEM_B_ADD[15..0]14,16,17

LAYOUT: 5MIL TRACE 10 MIL SPACE

LAYOUT: PLACE WITHIN 1 INCH OF CPU

VDDMEM

MEM_B_ADD[15..0]

R118

40.2-1%-LF

1%

R0603

1 2

R116

40.2-1%-LF

1%

R0603

V0.1 39.2-1%ohm ->40.2-1%ohm

4

CPU_MEMZN

CPU_MEMZP

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

13

12

11

10

ˠ˘ˠ˲˕˲˗˔˧˔ˉˆ

ˠ˘ˠ˲˕˲˗˔˧˔ˉ˅

ˠ˘ˠ˲˕˲˗˔˧˔ˉ˄

ˠ˘ˠ˲˕˲˗˔˧˔ˉ˃

ˠ˘ˠ˲˕˲˗˔˧˔ˈˌ

ˠ˘ˠ˲˕˲˗˔˧˔ˈˋ

ˠ˘ˠ˲˕˲˗˔˧˔ˈˊ

ˠ˘ˠ˲˕˲˗˔˧˔ˈˉ

ˠ˘ˠ˲˕˲˗˔˧˔ˈˈ

ˠ˘ˠ˲˕˲˗˔˧˔ˈˇ

ˠ˘ˠ˲˕˲˗˔˧˔ˈˆ

ˠ˘ˠ˲˕˲˗˔˧˔ˈ˅

ˠ˘ˠ˲˕˲˗˔˧˔ˈ˄

ˠ˘ˠ˲˕˲˗˔˧˔ˈ˃

ˠ˘ˠ˲˕˲˗˔˧˔ˇˌ

ˠ˘ˠ˲˕˲˗˔˧˔ˇˋ

ˠ˘ˠ˲˕˲˗˔˧˔ˇˊ

ˠ˘ˠ˲˕˲˗˔˧˔ˇˉ

ˠ˘ˠ˲˕˲˗˔˧˔ˇˈ

ˠ˘ˠ˲˕˲˗˔˧˔ˇˇ

ˠ˘ˠ˲˕˲˗˔˧˔ˇˆ

ˠ˘ˠ˲˕˲˗˔˧˔ˇ˅

ˠ˘ˠ˲˕˲˗˔˧˔ˇ˄

ˠ˘ˠ˲˕˲˗˔˧˔ˇ˃

ˠ˘ˠ˲˕˲˗˔˧˔ˆˌ

ˠ˘ˠ˲˕˲˗˔˧˔ˆˋ

ˠ˘ˠ˲˕˲˗˔˧˔ˆˊ

ˠ˘ˠ˲˕˲˗˔˧˔ˆˉ

ˠ˘ˠ˲˕˲˗˔˧˔ˆˈ

ˠ˘ˠ˲˕˲˗˔˧˔ˆˇ

ˠ˘ˠ˲˕˲˗˔˧˔ˆˆ

ˠ˘ˠ˲˕˲˗˔˧˔ˆ˅

ˠ˘ˠ˲˕˲˗˔˧˔ˆ˄

ˠ˘ˠ˲˕˲˗˔˧˔ˆ˃

ˠ˘ˠ˲˕˲˗˔˧˔˅ˌ

ˠ˘ˠ˲˕˲˗˔˧˔˅ˋ

ˠ˘ˠ˲˕˲˗˔˧˔˅ˊ

ˠ˘ˠ˲˕˲˗˔˧˔˅ˉ

ˠ˘ˠ˲˕˲˗˔˧˔˅ˈ

ˠ˘ˠ˲˕˲˗˔˧˔˅ˇ

ˠ˘ˠ˲˕˲˗˔˧˔˅ˆ

ˠ˘ˠ˲˕˲˗˔˧˔˅˅

ˠ˘ˠ˲˕˲˗˔˧˔˅˄

ˠ˘ˠ˲˕˲˗˔˧˔˅˃

ˠ˘ˠ˲˕˲˗˔˧˔˄ˌ

ˠ˘ˠ˲˕˲˗˔˧˔˄ˋ

ˠ˘ˠ˲˕˲˗˔˧˔˄ˊ

ˠ˘ˠ˲˕˲˗˔˧˔˄ˉ

ˠ˘ˠ˲˕˲˗˔˧˔˄ˈ

ˠ˘ˠ˲˕˲˗˔˧˔˄ˇ

ˠ˘ˠ˲˕˲˗˔˧˔˄ˆ

ˠ˘ˠ˲˕˲˗˔˧˔˄˅

ˠ˘ˠ˲˕˲˗˔˧˔˄˄

ˠ˘ˠ˲˕˲˗˔˧˔˄˃

ˠ˘ˠ˲˕˲˗˔˧˔ˌ

ˠ˘ˠ˲˕˲˗˔˧˔ˋ

ˠ˘ˠ˲˕˲˗˔˧˔ˊ

ˠ˘ˠ˲˕˲˗˔˧˔ˉ

ˠ˘ˠ˲˕˲˗˔˧˔ˈ

ˠ˘ˠ˲˕˲˗˔˧˔ˇ

ˠ˘ˠ˲˕˲˗˔˧˔ˆ

ˠ˘ˠ˲˕˲˗˔˧˔˅

ˠ˘ˠ˲˕˲˗˔˧˔˄

ˠ˘ˠ˲˕˲˗˔˧˔˃

ˠ˘ˠ˲˕˲˔˗˗˄ˈ

ˠ˘ˠ˲˕˲˔˗˗˄ˇ

ˠ˘ˠ˲˕˲˔˗˗˄ˆ

ˠ˘ˠ˲˕˲˔˗˗˄˅

ˠ˘ˠ˲˕˲˔˗˗˄˄

ˠ˘ˠ˲˕˲˔˗˗˄˃

9

ˠ˘ˠ˲˕˲˔˗˗ˌ

8

ˠ˘ˠ˲˕˲˔˗˗ˋ

7

ˠ˘ˠ˲˕˲˔˗˗ˊ

6

ˠ˘ˠ˲˕˲˔˗˗ˉ

5

ˠ˘ˠ˲˕˲˔˗˗ˈ

4

ˠ˘ˠ˲˕˲˔˗˗ˇ

3

ˠ˘ˠ˲˕˲˔˗˗ˆ

2

ˠ˘ˠ˲˕˲˔˗˗˅

1

ˠ˘ˠ˲˕˲˔˗˗˄

0

ˠ˘ˠ˲˕˲˔˗˗˃

U7D

SK-C940P-M2

MB_DATA<63>

AH13

MB_DATA<62>

AL13

MB_DATA<61>

AL15

MB_DATA<60>

AJ15

MB_DATA<59>

AF13

MB_DATA<58>

AG13

MB_DATA<57>

AL14

MB_DATA<56>

AK15

MB_DATA<55>

AL16

MB_DATA<54>

AL17

MB_DATA<53>

AK21

MB_DATA<52>

AL21

MB_DATA<51>

AH15

MB_DATA<50>

AJ16

MB_DATA<49>

AH19

MB_DATA<48>

AL20

MB_DATA<47>

AJ22

MB_DATA<46>

AL22

MB_DATA<45>

AL24

MB_DATA<44>

AK25

MB_DATA<43>

AJ21

MB_DATA<42>

AH21

MB_DATA<41>

AH23

MB_DATA<40>

AJ24

MB_DATA<39>

AL27

MB_DATA<38>

AK27

MB_DATA<37>

AH31

MB_DATA<36>

AG30

MB_DATA<35>

AL25

MB_DATA<34>

AL26

MB_DATA<33>

AJ30

MB_DATA<32>

AJ31

MB_DATA<31>

E31

MB_DATA<30>

E30

MB_DATA<29>

B27

MB_DATA<28>

A27

MB_DATA<27>

F29

MB_DATA<26>

F31

MB_DATA<25>

A29

MB_DATA<24>

A28

MB_DATA<23>

A25

MB_DATA<22>

A24

MB_DATA<21>

C22

MB_DATA<20>

D21

MB_DATA<19>

A26

MB_DATA<18>

B25

MB_DATA<17>

B23

MB_DATA<16>

A22

MB_DATA<15>

B21

MB_DATA<14>

A20

MB_DATA<13>

C16

MB_DATA<12>

D15

MB_DATA<11>

C21

MB_DATA<10>

A21

MB_DATA<9>

A17

MB_DATA<8>

A16

MB_DATA<7>

B15

MB_DATA<6>

A14

MB_DATA<5>

E13

MB_DATA<4>

F13

MB_DATA<3>

C15

MB_DATA<2>

A15

MB_DATA<1>

A13

MB_DATA<0>

D13

MB_ADD<15>

N28

MB_ADD<14>

N29

MB_ADD<13>

AE31

MB_ADD<12>

N30

MB_ADD<11>

P29

MB_ADD<10>

AA29

MB_ADD<9>

P31

MB_ADD<8>

R29

MB_ADD<7>

R28

MB_ADD<6>

R31

MB_ADD<5>

R30

MB_ADD<4>

T31

MB_ADD<3>

T29

MB_ADD<2>

U29

MB_ADD<1>

U28

MB_ADD<0>

AA30

M_ZN

AH11

M_ZP VTT_SENSE

AJ11

SOCKET_940_M2

SEC 4 OF 6

I234

http://laptop-motherboard-schematic.blogspot.com/

3

MB_CHECK<7>

MB_CHECK<6>

MB_CHECK<5>

MB_CHECK<4>

MB_CHECK<3>

MB_CHECK<2>

MB_CHECK<1>

MB_CHECK<0>

MB_DM<8>

MB_DM<7>

MB_DM<6>

MB_DM<5>

MB_DM<4>

MB_DM<3>

MB_DM<2>

MB_DM<1>

MB_DM<0>

MB_DQS<8>

MB_DQS<7>

MB_DQS<6>

MB_DQS<5>

MB_DQS<4>

MB_DQS<3>

MB_DQS<2>

MB_DQS<1>

MB_DQS<0>

MB_DQS<8>*

MB_DQS<7>*

MB_DQS<6>*

MB_DQS<5>*

MB_DQS<4>*

MB_DQS<3>*

MB_DQS<2>*

MB_DQS<1>*

MB_DQS<0>*

M_VREF

MB0_CLK<0>

MB0_CLK<0>*

MB0_CLK<1>

MB0_CLK<1>*

MB0_CLK<2>

MB0_CLK<2>*

MB1_CLK<0>

MB1_CLK<0>*

MB1_CLK<1>

MB1_CLK<1>*

MB1_CLK<2>

MB1_CLK<2>*

MB_BANK<2>

MB_BANK<1>

MB_BANK<0>

MB_RAS*

MB_CAS*

MB_WE*

MB0_CS<1>*

MB0_CS<0>*

MB1_CS<1>*

MB1_CS<0>*

MB_CKE<1>

MB_CKE<0>

MB0_ODT<0>

MB1_ODT<0>

K29

K31

G30

G29

L29

L28

H31

G31

J29

AJ14

AH17

AJ23

AK29

C30

A23

B17

B13

J31

AK13

AK17

AK23

AL28

D31

C24

D17

C14

J30

AJ13

AJ17

AL23

AL29

C31

C23

C17

C13

F12

U31

U30

A18

A19

AJ19

AK19

W29

W28

C19

D19

AL19

AL18

N31

AA31

AA28

AB29

AC29

AC30

AE30

AC31

AE29

AB31

M31

M29

AD29

AD31

E12

MEM_B_ECC[7..0]

7

ˠ˘ˠ˲˕˲˘˖˖ˊ

6

ˠ˘ˠ˲˕˲˘˖˖ˉ

5

ˠ˘ˠ˲˕˲˘˖˖ˈ

4

ˠ˘ˠ˲˕˲˘˖˖ˇ

3

ˠ˘ˠ˲˕˲˘˖˖ˆ

2

ˠ˘ˠ˲˕˲˘˖˖˅

1

ˠ˘ˠ˲˕˲˘˖˖˄

0

ˠ˘ˠ˲˕˲˘˖˖˃

MEM_B_DM[8..0]

8

ˠ˘ˠ˲˕˲˗ˠˋ

7

ˠ˘ˠ˲˕˲˗ˠˊ

6

ˠ˘ˠ˲˕˲˗ˠˉ

5

ˠ˘ˠ˲˕˲˗ˠˈ

4

ˠ˘ˠ˲˕˲˗ˠˇ

3

ˠ˘ˠ˲˕˲˗ˠˆ

2

ˠ˘ˠ˲˕˲˗ˠ˅

1

ˠ˘ˠ˲˕˲˗ˠ˄

0

ˠ˘ˠ˲˕˲˗ˠ˃

MEM_B_DQS[8..0]

8

ˠ˘ˠ˲˕˲˗ˤ˦ˋ

7

ˠ˘ˠ˲˕˲˗ˤ˦ˊ

6

ˠ˘ˠ˲˕˲˗ˤ˦ˉ

5

ˠ˘ˠ˲˕˲˗ˤ˦ˈ

4

ˠ˘ˠ˲˕˲˗ˤ˦ˇ

3

ˠ˘ˠ˲˕˲˗ˤ˦ˆ

2

ˠ˘ˠ˲˕˲˗ˤ˦˅

1

ˠ˘ˠ˲˕˲˗ˤ˦˄

0

ˠ˘ˠ˲˕˲˗ˤ˦˃

MEM_B_DQS*[8..0]

8

ˠ˘ˠ˲˕˲˗ˤ˦ʽˋ

7

ˠ˘ˠ˲˕˲˗ˤ˦ʽˊ

6

ˠ˘ˠ˲˕˲˗ˤ˦ʽˉ

5

ˠ˘ˠ˲˕˲˗ˤ˦ʽˈ

4

ˠ˘ˠ˲˕˲˗ˤ˦ʽˇ

3

ˠ˘ˠ˲˕˲˗ˤ˦ʽˆ

2

ˠ˘ˠ˲˕˲˗ˤ˦ʽ˅

1

ˠ˘ˠ˲˕˲˗ˤ˦ʽ˄

0

ˠ˘ˠ˲˕˲˗ˤ˦ʽ˃

L

0

ˠ˘ˠ˲˕˃˲˖˟˞˃

1

ˠ˘ˠ˲˕˃˲˖˟˞˄

2

ˠ˘ˠ˲˕˃˲˖˟˞˅

0

ˠ˘ˠ˲˕˄˲˖˟˞˃

1

ˠ˘ˠ˲˕˄˲˖˟˞˄

2

ˠ˘ˠ˲˕˄˲˖˟˞˅

MEM_B_BA[2..0]

2

ˠ˘ˠ˲˕˲˕˔˅

1

ˠ˘ˠ˲˕˲˕˔˄

0

ˠ˘ˠ˲˕˲˕˔˃

MEM_B_RAS*

MEM_B_CAS*

MEM_B_WE*

MEM_B0_CS*[1..0]

1

ˠ˘ˠ˲˕˃˲˖˦ʽ˄

0

ˠ˘ˠ˲˕˃˲˖˦ʽ˃

MEM_B1_CS*[1..0]

1

ˠ˘ˠ˲˕˄˲˖˦ʽ˄

0

ˠ˘ˠ˲˕˄˲˖˦ʽ˃

MEM_B1_CKE

MEM_B0_CKE

MEM_B0_ODT

MEM_B1_ODT

MEM_VTT_SENSE

MEM_CPU_VREF

MEM_B0_CLK[2..0]

MEM_B0_CLK*[2..0]

0

ˠ˘ˠ˲˕˃˲˖˟˞ʽ˃

1

ˠ˘ˠ˲˕˃˲˖˟˞ʽ˄

2

ˠ˘ˠ˲˕˃˲˖˟˞ʽ˅

MEM_B1_CLK[2..0]

MEM_B1_CLK*[2..0]

0

ˠ˘ˠ˲˕˄˲˖˟˞ʽ˃

1

ˠ˘ˠ˲˕˄˲˖˟˞ʽ˄

2

ˠ˘ˠ˲˕˄˲˖˟˞ʽ˅

H

2

MEM_B_ECC[7..0] 14,16

MEM_B_DM[8..0] 14,16

MEM_B_DQS[8..0] 14,16

MEM_B_DQS*[8..0] 14,16

MEM_B0_CLK[2..0] 14,17

MEM_B0_CLK*[2..0] 14,17

MEM_B1_CLK[2..0] 16,17

MEM_B1_CLK*[2..0] 16,17

MEM_B_BA[2..0] 14,16,17

MEM_B_RAS* 14,16,17

MEM_B_CAS* 14,16,17

MEM_B_WE* 14,16,17

MEM_B0_CS*[1..0] 14,17

MEM_B1_CS*[1..0] 16,17

MEM_B1_CKE 16,17

MEM_B0_CKE 14,17

MEM_B0_ODT 14,17

MEM_B1_ODT 16,17

ROUTE AS A 15MIL TRACE

12

12

BC49

0.1UF/X7R /16V-LF

C0603

X5R

16V

10%

BC50

1000PF/X7R/16V-LF

C0603

X7R

25V

10%

1

VDDMEM

BR28

100-1%-LF

1%

R0603

1 2

BR27

100-1%-LF

1%

R0603

1 2

V0.1 15-1%ohm ->100-1%ohm

1 2

A

Title

MCP68/65 HT/CLKS

Size Document Number Rev

A3

5

4

3

2

Date: Sheet

AN52

1

V0.1

10 42Friday, March 02, 2007

of

5

A

4

3

2

1

D D

Y18

Y20

Y22

VDDMEMVTTMEM

3

4

VCCP

AL12

AK12

AJ12

AH12

Y29

Y28

Y26

Y24

V30

V28

V26

V25

T30

T28

T26

T24

P30

P28

Y23

W22

V23

U22

T23

R22

P23

P21

N22

N20

M23

M21

L22

L20

AF11

AE12

AD23

AD11

AC22

AC20

AC18

AC16

AC14

AC12

AB23

AB21

AB19

AB17

AB15

AB13

AA22

AA20

Y21

Y19

Y17

Y15

Y13

Y11Y9Y7Y3Y2

W20

W18

W16

W14

W12

W10W8W5W4V21

V19

V17

V15

V13

V11V9U20

U18

U16

U14

U12

U10U8T21

T19

T17

T15

T13

T11T9T7T3T2

R20

R18

R16

R14

R12

R10R8R5R4P19

P17

P15

P13

P11P9P7

N18

VTT

VTT

VTT

P24

W15

VDDIO

P26

W19

W17

VTT

A12

W21

VTT

B12

VTT

C12

VTT

VTT

D12

Y10Y8W23

VTT

AG12

Y12

Y14

I108

Y16

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

SOCKET_940_M2

SEC 5 OF 6

U7E

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

C C

SK-C940P-M2

Z

H26

H24

H22

AA16

AA14

AA12

AA10

AA8A6A4

H30

H28

AA18

J11J9J7J5J4

AB7

J13

AB9

J15

AB11

J17

AC4

J19

AC5

J21

AC8

AC10

AD2

AD3

AD7

K10K8K3K2J23

AD9

K12

AE10

K14

AF7

K16

AF9

K18

AG4

K20

AG5

K22

AG7

K24

AH2

K26

AH3

K28

K30

M10M8L23

L21

L19

L17

L15

L13

L11L9L7

M12

M14

M16

M18

M20

F11F9F7F5E10E8E6E4D9D7D5D3C8C6C4C2B7B5B3

M22

VDD

H11H7G12

G10G8G6

N17

N15

N13

N11N9N7N5N4

VDD

N19

VDD

J12J8H23

N21

VDD

J14

VDD

J16

VDD

J18

VDD

J20

VDD

VDD

VDD

VDD

VDD

VDD

VDD

K15

K13

K11K9K7

J24

J22

P22

P20

P18

P16

P14

P12

P10P8P3P2N23

VDD

K17

VDD

K19

VDD

K21

R11R9R7

VDD

R13

VDD

R15

VDD

R17

VDD

R19

VDD

L10L8L5L4K23

R21

VDD

L12

VDD

L14

VDD

L16

T10T8R23

VDD

L18

T12

VDD

T14

VDD

T16

VDD

T18

VDD

T20

VDD

M11M9M7M3M2

T22

VDD

M13

VDD

M15

VDD

M17

VDD

VDD

U11U9U7U5U4

VDD

N10N8M19

U13

VDD

N12

U15

VDD

N14

U17

VDD

N16

U19

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

AD30

V20

AF30

M24

M26

W9W7V22

M28

W11

VDDIO

M30

W13

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

AD28

AD26

AC24

AB30

AB28

AB26

AB24

V18

V16

V14

V12

V10V3V2

U23

U21

PADVSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SEC 6 OF 6

SOCKET_940_M2

B B

U7F

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SK-C940P-M2

A3

AA9

AA7

AA5

AA4

A11A9A7

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B24

B22

B20

B18

B16

B14

B11B9B4

B26

B28

D18

D16

D14C3B30

D30

D28

D26

D24

D22

D20

F24

F22

F20

F18

F16

F14F4E11

H10H8G11G9F30

F28

F26

VSS

VSS

H12

VSS

VSS

H14

VSS

VSS

H16

VSS

VSS

H18

PADVSS

PADVSS

PADVSS

1

2

http://laptop-motherboard-schematic.blogspot.com/

Title

MCP68/65 HT/CLKS

Size Document Number Rev

A3

5

4

3

2

Date: Sheet

AN52

1

V0.1

11 42Friday, March 02, 2007

of

A

5

A

4

3

2

1

PLACE NEAR THE CPU SOCKET PLACE NEAR CPU SOCKET ALONG VTT POURPLACE NEAR CPU, BETWEEN CPU AND DIMM

D D

VDDMEM

12

BCT3

4.7UF/0805Y/10V-LF

C0805

?

6.3V

10%

12

BCT14

4.7UF/0805Y/10V-LF

C0805

?

6.3V

10%

12

C12

0.22UF/16V-LF

C0603

X7R

16V

10%

12

C189

0.22UF/16V-LF

C0603

X7R

16V

10%

12

BC39

0.22UF/16V-LF

C0603

X7R

16V

10%

12

12

BC42

C163

180PF-LF

180PF-LF

C0603

C0603

C0G

C0G

50V

50V

5%

5%

V1P2

12

BCT2

4.7UF/0805Y/10V-LF

C0805

?

6.3V

10%

12

CT36

4.7UF/0805Y/10V-LF

C0805

?

6.3V

10%

12

C93

0.22UF/16V-LF

C0603

X7R

16V

10%

V1P2_LDT

12

C87

0.22UF/16V-LF

C0603

X7R

16V

10%

VTTMEM

12

CT43

4.7UF/0805Y/10V-LF

C0805

?

6.3V

10%

12

CT16

4.7UF/0805Y/10V-LF

C0805

?

6.3V

10%

12

CT47

4.7UF/0805Y/10V-LF

C0805

?

6.3V

10%

12

CT22

4.7UF/0805Y/10V-LF

C0805

?

6.3V

10%

12

C222

0.22UF/16V-LF

C0603

X7R

16V

10%

12

C142

0.22UF/16V-LF

C0603

X7R

16V

10%

12

C38

0.22UF/16V-LF

C0603

X7R

16V

10%

12

C50

0.22UF/16V-LF

C0603

X7R

16V

10%

12

C44

1000PF/X7R/16V-LF

C0603

X7R

6.3V

10%

CT23

12

4.7UF/0805Y/10V-LF

C0805

?

6.3V

10%

12

C171

1000PF/X7R/16V-LF

C0603

X7R

6.3V

10%

12

C143

1000PF/X7R/16V-LF

C0603

X7R

6.3V

10%

PLACE UNDER THE CPU SOCKET

VCCP

VDDMEM

12

BCT16

10UF/X5R/6.3V/0805 -L F

C0805

X5R

6.3V

20%

12

BCT15

10UF/X5R/6.3V/0805 -L F

C0805

X5R

6.3V

20%

12

BCT6

C C

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

BCT11

10UF/X5R/6.3V/0805 -L F

C0805

X5R

6.3V

20%

BCT10

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

12

12

12

BCT18

10UF/X5R/6.3V/080 5-L F

C0805

X5R

6.3V

20%

12

BCT17

10UF/X5R/6.3V/0805 -L F

C0805

X5R

6.3V

20%

12

BCT5

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

12

BCT7

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

12

BCT4

10UF/X5R/6.3V/0805 -L F

C0805

X5R

6.3V

20%

12

BCT9

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

12

BCT8

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

12

BCT13

10UF/X5R/6.3V/0805 -L F

C0805

X5R

6.3V

20%

12

BCT12

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

12

C71

0.22UF/16V-LF

C0603

X7R

16V

10%

12

C230

0.22UF/16V-LF

C0603

X7R

16V

10%

12

BC37

0.22UF/16V-LF

C0603

X7R

16V

10%

12

BC36

0.01UF/X7R/16V-LF

C0603

X7R

<VOLTAGE>

10%

12

BC51

10PF/NPO/50V-LF

C0603

?

50V

5%

12

CT42

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

12

CT21

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

12

BC45

C0603

X7R

16V

10%

0.22UF/16V-LF

PLACE NEAR DIMM SOCKET ALONG VTT POUR INBETWEEN RPACKS

VTTMEM

VDDMEM

12

C66

0.1UF/X7R/16V-LF

C0603

X7R

16V

10%

12

C164

0.1UF/X7R /16V-LF

C0603

X7R

16V

10%

12

C179

0.1UF/X7R/16V-LF

C0603

X7R

16V

10%

X0.1UF/X7R/16V-LF

12

12

12

C172

C174

0.1UF/X7R/16V-LF

C0603

C0603

X7R

X7R

16V

16V

10%

10%

X0.1UF/X7R/16V-LF

12

C154

0.1UF/X7R/16V-LF

C0603

X7R

16V

10%

X0.1UF/X7R/16V-LF

12

C146

C0603

X7R

16V

10%

C170

C0603

X7R

16V

10%

12

C135

0.1UF/X7R/16V-LF

C0603

X7R

16V

10%

12

C131

C0603

X7R

16V

10%

0.1UF/X7R /16V-LF

12

C127

0.1UF/X7R /16V-LF

C0603

X7R

16V

10%

X0.1UF/X7R/16V-LF

12

C86

0.1UF/X7R/16V-LF

C0603

X7R

16V

10%

12

C103

0.1UF/X7R /16V-LF

C0603

X7R

16V

10%

12

C98

C0603

X7R

16V

10%

12

C117

0.1UF/X7R/16V-LF

C0603

X7R

16V

10%

12

C80

0.1UF/X7R/16V-LF

C0603

X7R

16V

10%

12

C75

0.1UF/X7R /16V-LF

C0603

X7R

16V

10%

B B

VCCP

12

CT35

C0805

X5R

6.3V

20%

12

BC41

C0603

X7R

16V

0.1UF/X7R /16V-LF

10%

12

12

CT25

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

X10UF/X5R /6.3V/0805-LF

12

12

C69

0.1UF/X7R/16V-LF

C0603

X7R

16V

10%

X0.1UF/X7R/16V-LF

CT17

C0805

X5R

6.3V

20%

C226

C0603

X7R

16V

10%

12

12

CT14

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

10UF/X5R/ 6.3V/0805-LF

12

12

BC48

0.01UF/X7R/16V-LF

C0603

X7R

<VOLTAGE>

10%

0.01UF/X7R/16V-LF

CT29

C0805

X5R

6.3V

20%

C57

C0603

X7R

<VOLTAGE>

10%

12

12

CT18

CT38

10UF/X5R/ 6.3V/0805-LF

C0805

C0805

X5R

X5R

6.3V

6.3V

20%

20%

X10UF/X5R /6.3V/0805-LF

12

12

C56

BC43

0.01UF/X7R/16V-LF

C0603

C0603

X7R

X7R

<VOLTAGE>

<VOLTAGE>

10%

10%

X0.01UF/X7R/16V-L F

12

12

CT37

CT39

10UF/X5R/6.3V/0805-LF

C0805

C0805

X5R

X5R

6.3V

6.3V

20%

20%

10UF/X5R/ 6.3V/0805-LF

12

12

BC38

BC44

0.01UF/X7R/16V-LF

C0603

C0603

X7R

X7R

<VOLTAGE>

<VOLTAGE>

0.01UF/X7R/16V-LF

10%

10%

12

CT40

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

12

12

C49

C47

0.01UF/X7R/16V-LF

C0603

C0603

X7R

X7R

<VOLTAGE>

<VOLTAGE>

10%

10%

X0.01UF/X7R/16V-L F

12

C70

0.01UF/X7R/16V-LF

C0603

X7R

<VOLTAGE>

10%

X0.01UF/X7R/16V-L F

12

C42

C0603

X7R

<VOLTAGE>

10%

PLACE NEAR DIMM SOCKET ALONG VTT POUR

VTTMEM

12

12

C51

1000PF/X7R/16V-LF

C0603

X7R

6.3V

10%

12

C35

C0603

X5R

16V

X0.1UF/X7R/16V-LF

10%

0.1UF/X7R/16V-LF

C223

C0603

X5R

16V

10%

12

C201

C0603

X5R

16V

X0.1UF/X7R/16V-LF

10%

12

CT30

4.7UF/0805Y/10V-LF

C0805

?

6.3V

10%

180PF-LF

12

12

12

CT27

CT28

10UF/X5R/6.3V/0805 -L F

C0805

C0805

X5R

X5R

6.3V

6.3V

20%

20%

10UF/X5R/6.3V/0805 -L F

12

12

C190

1000PF/X7R/16V-LF

C0603

X7R

6.3V

10%

12

C52

180PF-LF

C0603

C0G

50V

5%

X0.01UF/X7R/16V-L F

C188

C0603

C0G

50V

5%

12

C40

C0603

X7R

<VOLTAGE>

10%

12

C193

0.01UF/X7R/16V-LF

C0603

X7R

<VOLTAGE>

10%

VCCP

12

C58

0.1UF/X7R/16V-LF

C0603

X7R

16V

10%

12

BC46

C0603

X7R

16V

10%

X0.1UF/X7R/16V-LF

12

12

CT6

CT26

10UF/X5R/ 6.3V/0805-LF

C0805

C0805

X5R

X5R

6.3V

6.3V

20%

20%

10UF/X5R/ 6.3V/0805-LF

12

12

BC40

C55

0.1UF/X7R /16V-LF

C0603

C0603

X7R

X7R

16V

16V

10%

10%

X0.1UF/X7R/16V-LF

CT45

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

10UF/X5R/6.3V/0805 -L F

20%

12

C48

0.1UF/X7R /16V-LF

C0603

X7R

16V

10%

12

CT9

C0805

X5R

6.3V

20%

12

BC47

C0603

X7R

16V

10%

X0.1UF/X7R/16V-LF

12

CT34

10UF/X5R/ 6.3V/0805-LF

C0805

X5R

6.3V

20%

10UF/X5R/ 6.3V/0805-LF

12

C68

0.1UF/X7R /16V-LF

C0603

X7R

16V

10%

http://laptop-motherboard-schematic.blogspot.com/

A

Title

MCP68/65 HT/CLKS

Size Document Number Rev

A3

5

4

3

2

Date: Sheet

AN52

1

V0.1

12 42Friday, March 02, 2007

of

5

A

4

3

2

1

VTT_P

0

D D

0

1

VTT_N

0

1

0

1

DIMM 1

SMB_MEM_SCL14,15,16,23,35,43

SMB_MEM_SDA14,15,16,23,35,43

MEM_A0_ODT9,17

MEM_A_BA[2..0]9,15,17

MEM_A0_CKE9,17

MEM_A0_CS*[1..0]9,17

MEM_A_CAS*9,15,17

C C

MEM_A_RAS*9,15,17

MEM_A_WE*9,15,17

MEM_A0_CLK*[2..0]9,17

MEM_A0_CLK[2..0]9,17

MEM_A_ECC[7..0]9,15

MEM_A_DQS*[8..0]9,15

MEM_A_DQS[8..0]9,15

MEM_A_DM[8..0]9,15

MEM_A_ADD[15..0]9,15,17

B B

SMB_MEM_SCL

SMB_MEM_SDA

MEM_A0_ODT

MEM_A_BA[2..0]

MEM_A0_CKE

MEM_A0_CS*[1..0]

MEM_A_CAS*

MEM_A_RAS*

MEM_A_WE*

MEM_A0_CLK*[2..0]

MEM_A0_CLK[2..0]

MEM_A_ECC[7..0]

MEM_A_DQS*[8..0]

MEM_A_DQS[8..0]

MEM_A_DM[8..0]

MEM_A_ADD[15..0]

ˠ˘ˠ˲˔˲˔˗˗˃ ˠ˘ˠ˲˔˲˔˗˗˄˃ˠ˘ˠ˲˔˲˔˗˗˄˄ˠ˘ˠ˲˔˲˔˗˗˄˅ˠ˘ˠ˲˔˲˔˗˗˄ˆˠ˘ˠ˲˔˲˔˗˗˄ˇ

585960

616263

177

179

180

182

183

188

A9

A8

A6

A3

A1

1.8V

DIMM240

A7

A5

A4

A2

57

70

A11

A10/AP

174

176

196

A13

A14

A12

ˠ˘ˠ˲˔˲˗ˠ˃ˠ˘ ˠ˲˔˲˗ˠ˄ˠ˘ˠ˲˔˲˗ˠ˅ˠ˘ˠ˲˔˲˗ˠˆˠ˘ ˠ˲˔˲˗ˠˇˠ˘ˠ˲˔˲˗ˠˈˠ˘ˠ˲˔˲˗ˠˉˠ ˘ˠ˲˔˲˗ˠˊ

ˠ˘ˠ˲˔˲˔˗˗˄ˈˠ˘ˠ˲˔˲˔˗˗˄ˠ˘ˠ˲˔˲˔˗˗˅ˠ˘ˠ˲˔˲˔˗˗ˆˠ˘ˠ˲˔˲˔˗˗ˇˠ˘ˠ˲˔˲˔˗˗ˈˠ˘ˠ˲˔˲˔˗˗ˉˠ˘ˠ˲˔˲˔˗˗ˊˠ˘ˠ˲˔˲˔˗˗ˋˠ˘ˠ˲˔˲˔˗˗ˌ

125

134

146

155

173

A15

DM0/DQS9

DM2/DQS11

DM3/DQS12

DM1/DQS10

ˠ˘ˠ˲˔˲˗ˤ˦˃

ˠ˘ˠ˲˔˲˗ˤ˦˄

ˠ˘ˠ˲˔˲˗ˤ˦˅

ˠ˘ˠ˲˔˲˗ˤ˦ˆ

ˠ˘ˠ˲˔˲˗ˠˋ

7

16

28

37

164

202

211

223

232

DQS0

DQS1

DQS2

DQS3

DM6/DQS15

DM7/DQS16

DM5/DQS14

DM8/DQS17

DM4/DQS13

ˠ˘ˠ˲˔˲˗ˤ˦ˇ

84

DQS4

ˠ˘ˠ˲˔˲˗ˤ˦ˈ

93

DQS5

ˠ˘ˠ˲˔˲˗ˤ˦ˉ

105

DQS6

ˠ˘ˠ˲˔˲˗ˤ˦ˊ

114

DQS7

ˠ˘ˠ˲˔˲˗ˤ˦ˋ

46

NC/DQS8

CLOSEST DIMM TO CPU

CHANNEL "A" LOWER 64 BITS

ˠ˘ˠ˲˔˲˗ˤ˦ʽˇ

ˠ˘ˠ˲˔˲˗ˤ˦ʽˈ

92

DQS5*

ˠ˘ˠ˲˔˲˗ˤ˦ʽˉ

104

*

DQS6

ˠ˘ˠ˲˔˲˗ˤ˦ʽˊ

113

DQS7*

NC/DQS8*

ˠ˘ˠ˲˔˲˗ˤ˦ʽˋ

ˠ˘ˠ˲˔˲˘˖˖˃ˠ˘ˠ˲˔˲˘˖˖˄ˠ˘ˠ˲˔˲˘˖˖˅ˠ˘ˠ˲˔˲˘˖˖ˆˠ˘ˠ˲˔˲˘˖˖ˇˠ˘ˠ˲˔˲˘˖˖ˈˠ˘ˠ˲˔˲˘˖˖ˉ

42

434445

NC/CB0

NC/CB1

ˠ˘ˠ˲˔˲˗ˤ˦ʽ˃

6

DQS0*

ˠ˘ˠ˲˔˲˗ˤ˦ʽ˄

15

DQS1*

ˠ˘ˠ˲˔˲˗ˤ˦ʽ˅

ˠ˘ˠ˲˔˲˗ˤ˦ʽˆ

27

36

DQS2*

DQS3*

83

DQS4*

48

49

NC/CB2

NC/CB3

161

162

NC/CB4

NC/CB5

ˠ˘ˠ˲˔˲˘˖˖ˊ

167

168

NC/CB6

NC/CB7

19

126

NC

NC/DQS9*

135

147

156

NC/DQS11*

NC/DQS12*

NC/DQS10*

203

212

224

NC/DQS15*

NC/DQS14*

NC/DQS13*

165

233

NC/DQS16*

NC/DQS17*

ˠ˘ˠ˲˔˃˲˖˟˞˃

012

185

CK0

ˠ˘ˠ˲˔˃˲˖˟˞˄

137

CK1

ˠ˘ˠ˲˔˃˲˖˟˞˅

220

CK2

ˠ˘ˠ˲˔˃˲˖˟˞ʽ˃

012

186

CK0*

ˠ˘ˠ˲˔˃˲˖˟˞ʽ˄

138

221

CK1*

ˠ˘ˠ˲˔˃˲˖˟˞ʽ˅

CK2*

73

WE*

192

RAS*

ˠ˘ˠ˲˔˃˲˖˦ʽ˃

0

747576

193

S0*

CAS*

ˠ˘ˠ˲˔˃˲˖˦ʽ˄

1

S1*

52

CKE0

171

CKE1

ˠ˘ˠ˲˔˲˕˔˃ˠ˘ˠ˲˔˲˕˔˄

012

71

BA0

190

BA1

ˠ˘ˠ˲˔˲˕˔˅

54

A16/BA2

195

ODT0

77

ODT1

102103

TESTVSS

55

PAR_IN

ERR_OUT*

18

RESET*

VTT_VREF

(VDDR / 2)*102%_0.922

(VDDR / 2)*98%_0.882

(VDDR / 2)*100%_0.899 *

(VDDR / 2)*96%_0.8561

V0.1

C19

0.1UF/16V-LF

C26

0.1UF/16V-LF

R33

4.02K-1%-LF

DS

G

VTT_P46 VTT_N 46

VCC3 VDDMEM

53

64

238

VDDSPD

VDD

VDD

VDD

676869

VDD

VDD

172

VDD

178

184

187

189

VDD

VDD

VDDA0VDD

101

119

120

239

240

SA0

SA1

SCL

SA2

SDA

VDDMEM

1 2

R37

210-1%-LF

Q7

1 2

2N7002/100mA-LF

51

56

197

VDD

VDDQ

VDDQ

R34

200-1%-LF

MEM_VREF

72

VDDQ

VDDQ

VDDQ

+1.8V_SUS

R36

2.26K-1%-LF

Q6

DS

G

78

170

175

VDDQ

VDDQ

VDDQ

12

2N7002/100mA-LF

1

181

191

194

VREF

VDDQ

VDDQ

VDDQ

MEM_VREF 14,15,16

12

C24

C23

0.1UF/16V/0402-LF

C0402

C0402

X7R

X5R

25V

16V

0.1UF/16V /0402-LF

10%

10%

SK-D240P

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

9

101112

122

2 2

3 3

4 4

DQ7

123

128

129

5 5

6 6

7 7

8 8

DIMM1

Default

3

4

ˠ˘ˠ˲˔˲˗˔˧˔˃ ˠ˘ˠ˲˔˲˗˔˧˔˄˃ˠ˘ˠ˲˔˲˗˔˧˔˄˄ˠ˘ˠ˲˔˲˗˔˧˔˄˅ˠ˘ˠ˲˔˲˗˔˧˔˄ˆˠ˘ˠ˲˔˲˗˔˧˔˄ˇˠ˘ˠ˲˔˲˗˔˧˔˄ˈˠ˘ˠ˲˔˲˗˔˧˔˄ˉˠ˘ˠ˲˔˲˗˔˧˔˄ˊˠ˘ˠ˲˔˲˗˔˧˔˄ˋˠ˘ˠ˲˔˲˗˔˧˔˄ˌˠ˘ˠ˲˔˲˗˔˧˔˄ ˠ˘ˠ˲˔˲˗˔˧˔˅˃ˠ˘ˠ˲˔˲˗˔˧˔˅˄ˠ˘ˠ˲˔˲˗˔˧˔˅˅ˠ˘ˠ˲˔˲˗˔˧˔˅ˆˠ˘ˠ˲˔˲˗˔˧˔˅ˇˠ˘ˠ˲˔˲˗˔˧˔˅ˈˠ˘ˠ˲˔˲˗˔˧˔˅ˉˠ˘ˠ˲˔˲˗˔˧˔˅ˊˠ˘ˠ˲˔˲˗˔˧˔˅ˋˠ˘ˠ˲˔˲˗˔˧˔˅ˌˠ˘ˠ˲˔˲˗˔˧˔˅ ˠ˘ˠ˲˔˲˗˔˧˔ˆ˃ˠ˘ˠ˲˔˲˗˔˧˔ˆ˄ˠ˘ˠ˲˔˲˗˔˧˔ˆ˅ˠ˘ˠ˲˔˲˗˔˧˔ˆˆˠ˘ˠ˲˔˲˗˔˧˔ˆˇˠ˘ˠ˲˔˲˗˔˧˔ˆˈˠ˘ˠ˲˔˲˗˔˧˔ˆˉˠ˘ˠ˲˔˲˗˔˧˔ˆˊˠ˘ˠ˲˔˲˗˔˧˔ˆˋˠ˘ˠ˲˔˲˗˔˧˔ˆˌˠ˘ˠ˲˔˲˗˔˧˔ˆ ˠ˘ˠ˲˔˲˗˔˧˔ˇ˃ˠ˘ˠ˲˔˲˗˔˧˔ˇ˄ˠ˘ˠ˲˔˲˗˔˧˔ˇ˅ˠ˘ˠ˲˔˲˗˔˧˔ˇˆˠ˘ˠ˲˔˲˗˔˧˔ˇˇˠ˘ˠ˲˔˲˗˔˧˔ˇˈˠ˘ˠ˲˔˲˗˔˧˔ˇˉˠ˘ˠ˲˔˲˗˔˧˔ˇˊˠ˘ˠ˲˔˲˗˔˧˔ˇˋˠ˘ˠ˲˔˲˗˔˧˔ˇˌˠ˘ˠ˲˔˲˗˔˧˔ˇ ˠ˘ˠ˲˔˲˗˔˧˔ˈ˃ˠ˘ˠ˲˔˲˗˔˧˔ˈ˄ˠ˘ˠ˲˔˲˗˔˧˔ˈ˅ˠ˘ˠ˲˔˲˗˔˧˔ˈˆˠ˘ˠ˲˔˲˗˔˧˔ˈˇˠ˘ˠ˲˔˲˗˔˧˔ˈˈˠ˘ˠ˲˔˲˗˔˧˔ˈˉˠ˘ˠ˲˔˲˗˔˧˔ˈˊˠ˘ˠ˲˔˲˗˔˧˔ˈˋˠ˘ˠ˲˔˲˗˔˧˔ˈˌˠ˘ˠ˲˔˲˗˔˧˔ˈ ˠ˘ˠ˲˔˲˗˔˧˔ˉ˃ˠ˘ˠ˲˔˲˗˔˧˔ˉ˄ˠ˘ˠ˲˔˲˗˔˧˔ˉ˅

0 0

1 1

MEM_A_DATA[63..0]9,15

MEM_A_DATA[63..0]

DQ8

DQ9

13

9 9

DQ12

DQ10

DQ11

21

222324

131

10 10

11 11

12 12

DQ14

DQ15

DQ20

DQ21

DQ22

DQ23

DQ28

DQ29

DQ30

DQ13

DQ16

DQ17

DQ18

DQ19

DQ24

25

30

313233

132

140

141

143

144

149

150

13 13

14 14

15 151617 0

18 1

19 2

20 3

21 4

22 5

23 6

24 7

25 82627 0

DQ31

DQ25

DQ26

DQ27

DQ32

DQ33

34

39

40

80

81

152

153

158

159

28 1

29 2

30 3

31 4

32 5

33 6

DQ39

DQ44

DQ45

DQ46

DQ41

DQ42

DQ43

90

95

969798

42 5

43 6

DQ47

208

209

214

215

44 7

45 84647 0

48 1

DQ38

DQ36

DQ37

DQ34

DQ35

DQ40

86

87

89

199

200

205

206

34 7

35 83637 0

38 1

39 2

40 3

41 4

DQ48

49 2

DQ50

DQ51

DQ49

99

107

108

50 3

51 4

DQ54

DQ55

DQ56

DQ52

DQ53

110

217

218

226

227

52 5

53 6

54 75556575859606162

DQ57

DQ58

111

116

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

41

47

50

65

SMB_MEM_SDA

SMB_MEM_SCL

VSS

66

79

82

85

88

DQ60

DQ61

DQ62

DQ63

DQ59

2

5

8

14

17

20

26

29

35

117

229

230

235

236

ˠ˘ˠ˲˔˲˗˔˧˔ˉˆˠ˘ˠ˲˔˲˗˔˧˔ˉˠ˘ˠ˲˔˲˗˔˧˔ˊˠ˘ˠ˲˔˲˗˔˧˔ˋˠ˘ˠ˲˔˲˗˔˧˔ˌ

63

38

VSS

VSS

VSS

VSS

VSS

VSS

VSS

91

94

100

VSS

VSS

106

109

112

115

118

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

121

124

127

130

133

136

139

142

145

148

VSS

VSS

VSS

151

154

157

160

163

166

169

198

201

204

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

207

210

213

216

219

222

225

228

I278

231

234

237

3VDUAL 3VDUAL

http://laptop-motherboard-schematic.blogspot.com/

K

KA

K

KA

A

D9

BAV99-LF

Prevent ESD issue

5

4

D8

BAV99-LF

A

2

Title

MCP68/65 HT/CLKS

Size Document Number Rev

A3

Date: Sheet

AN52

V0.1

13 42Friday, March 02, 2007

of

1

A

3

5

A

4

3

2

1

D D

ˠ˘ˠ˲˕˲˗ˤ˦ʽ˃

ˠ˘ˠ˲˕˲˗ˤ˦ʽ˄

ˠ˘ˠ˲˕˲˗ˤ˦ʽ˅

ˠ˘ˠ˲˕˲˗ˤ˦ˋ

6

15

27

46

DQS0*

DQS1*

DQS2*

NC/DQS8

8

DQ39

DQ35

DQ3

DQ36

DQ37

878889

199

200

205

206

38 1

39 2

ˠ˘ˠ˲˕˲˗ˤ˦ʽˆ

36

DQS3*

DQ40

40 3

CHANNEL "B" UPPER 64 BITS

ˠ˘ˠ˲˕˲˘˖˖˃ˠ˘ˠ˲˕˲˘˖˖˄ˠ˘ˠ˲˕˲˘˖˖˅ˠ˘ˠ˲˕˲˘˖˖ˆˠ˘ˠ˲˕˲˘˖˖ˇˠ˘ˠ˲˕˲˘˖˖ˈˠ˘ˠ˲˕˲˘˖˖ˉ

DQ46

214

42

434445

NC/CB0

NC/CB1

DQ47

DQ48

98

215

48 1

48

NC/CB2

DQ49

99

49 2

50 3

49

161

NC/CB3

NC/CB4

DQ50

DQ51

107

108

51 4

5

52

ˠ˘ˠ˲˕˲˗ˤ˦ʽˇ

83

DQS4*

DQ41

90

41 4

ˠ˘ˠ˲˕˲˗ˤ˦ʽˈ

92

DQS5*

DQ42

95

42 5

ˠ˘ˠ˲˕˲˗ˤ˦ʽˉ

104

*

DQS6

DQ43

96

43 6

ˠ˘ˠ˲˕˲˗ˤ˦ʽˊ

113

DQS7*

DQ44

208

44 7

45 84647 0

ˠ˘ˠ˲˕˲˗ˤ˦ʽˋ

NC/DQS8*

DQ45

209

ˠ˘ˠ˲˕˲˘˖˖ˊ

19

126

162

167

168

NC

NC/CB5

NC/CB6

NC/CB7

NC/DQS9*

DQ56

DQ57

DQ52

DQ53

DQ54

DQ55

110

111

217

218

226

227

53 6

54 75556575859606162

135

147

156

NC/DQS10*

NC/DQS11*

NC/DQS12*

DQ60

DQ58

DQ59

116

117

229

ˠ˘ˠ˲˕˲˕˔˃ˠ˘ˠ˲˕˲˕˔˄

ˠ˘ˠ˲˕˲˕˔˅

012

ˠ˘ˠ˲˕˃˲˖˦ʽ˃

ˠ˘ˠ˲˕˃˲˖˦ʽ˄

0

1

189

VDDA0VDD

VSS

VSS

198

197

VDD

VSS

201

VSS

204

51

VDDQ

VSS

207

56

VDDQ

VSS

210

MEM_VREF

72

78

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSS

213

216

219

222

12

C20

0.1UF/16V /0402-LF

C0402

X5R

16V

10%

VDDMEM

170

175

181

191

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSS

225

228

231

234

194

VDDQ

VSS

237

1

VREF

?

MEM_VREF13,15,16

ˠ˘ˠ˲˕˃˲˖˟˞˃

012

ˠ˘ˠ˲˕˃˲˖˟˞˄

ˠ˘ˠ˲˕˃˲˖˟˞˅

ˠ˘ˠ˲˕˃˲˖˟˞ʽ˃

012

ˠ˘ˠ˲˕˃˲˖˟˞ʽ˄

ˠ˘ˠ˲˕˃˲˖˟˞ʽ˅

VCC3

525354

73

CK0*

VSS

138

23

CK1*

VSS

221

26

CK2*

VSS

747576

192

193

WE*

CAS*

RAS*

VSS

VSS

VSS

VSS

VSS

29

35

38

41

137

165

185

203

212

224

233

NC/DQS14*

NC/DQS15*

NC/DQS16*

NC/DQS13*

DQ61

DQ62

DQ63

230

235

236

ˠ˘ˠ˲˕˲˗˔˧˔ˉˆˠ˘ˠ˲˕˲˗˔˧˔ˉˠ˘ˠ˲˕˲˗˔˧˔ˊˠ˘ˠ˲˕˲˗˔˧˔ˋˠ˘ˠ˲˕˲˗˔˧˔ˌ

63

186

220

CK2

CK1

CK0

NC/DQS17*

VSS

VSS

VSS

VSS

VSS

VSS

2

5

8

14

17

20

71

171

190

S1*

S0*

BA0

BA1

CKE0

CKE1

A16/BA2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

47

50

65

66

79

82

85

91

195

ODT0

VSS

94

77

ODT1

VSS

97

18

55

RESET*

ERR_OUT*

VSS

VSS

VSS

109

112

115

101

119

120

239

240

SA0

SA1

SA2

SDA

VSS

VSS

VSS

VSS

VSS

118

121

124

127

130

133

102103

TESTVSS

PAR_IN

VSS

VSS

100

106

64

676869

172

178

184

VDD

VSS

151

VDD

VSS

154

VDD

VSS

157

187

VDD

VDD

VDD

VSS

VSS

VSS

160

163

166

169

238

SCL

VDD

VDD

VDDSPD

VSS

VSS

VSS

VSS

VSS

VSS

136

139

142

145

148

DIMM 2

SMB_MEM_SCL13,15,16,23,35,43

SMB_MEM_SDA13,15,16,23,35,43

MEM_B0_ODT10,17

MEM_B_BA[2..0]10,16,17

MEM_B0_CKE10,17

MEM_B0_CS*[1..0]10,17

MEM_B_CAS*10,16,17

MEM_B_RAS*10,16,17

C C

MEM_B_WE*10,16,17

MEM_B0_CLK*[2..0]10,17

MEM_B0_CLK[2..0]10,17

MEM_B_ECC[7..0]10,16

MEM_B_DQS*[8..0]10,16

MEM_B_DQS[8..0]10,16

MEM_B_DM[8..0]10,16

MEM_B_ADD[15..0]10,16,17

B B

MEM_B_DATA[63..0]10,16

MEM_B_DATA[63..0]

SMB_MEM_SCL

SMB_MEM_SDA

MEM_B0_ODT

MEM_B_BA[2..0]

MEM_B0_CKE

MEM_B0_CS*[1..0]

MEM_B_CAS*

MEM_B_RAS*

MEM_B_WE*

MEM_B0_CLK*[2..0]

MEM_B0_CLK[2..0]

MEM_B_ECC[7..0]

MEM_B_DQS*[8..0]

MEM_B_DQS[8..0]

MEM_B_DM[8..0]

MEM_B_ADD[15..0]

ˠ˘ˠ˲˕˲˔˗˗˃ ˠ˘ˠ˲˕˲˔˗˗˄˃ˠ˘ˠ˲˕˲˔˗˗˄˄ˠ˘ˠ˲˕˲˔˗˗˄˅ˠ˘ˠ˲˕˲˔˗˗˄ˆˠ˘ˠ˲˕˲˔˗˗˄ˇ

57

585960

616263

70

177

179

180

182

183

188

A7

A5

A4

A2

A1

1.8V

DIMM240

SK-D240P

DQ0

DQ1

DIMM2

Default

DQ2

3

4

9