Page 1

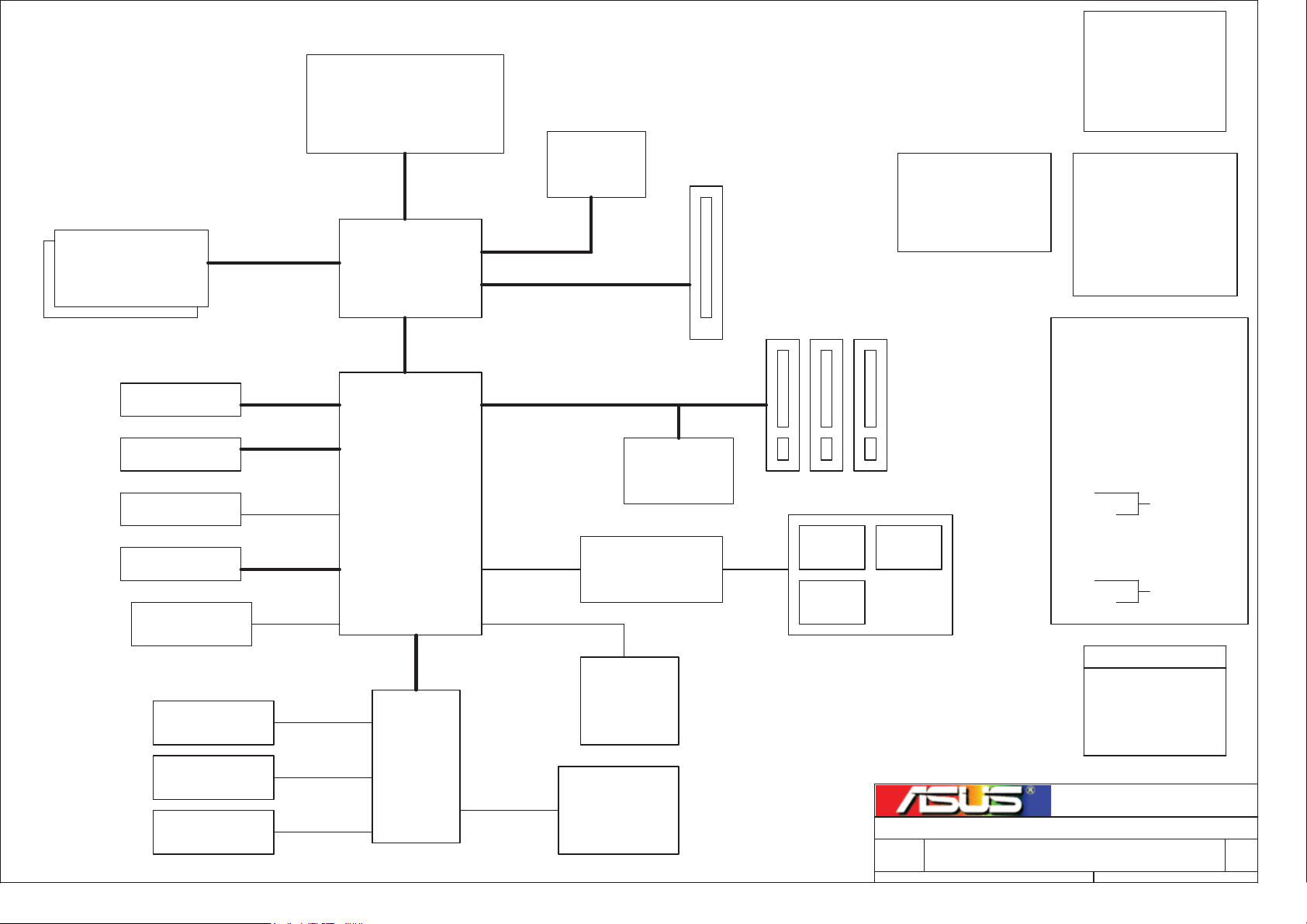

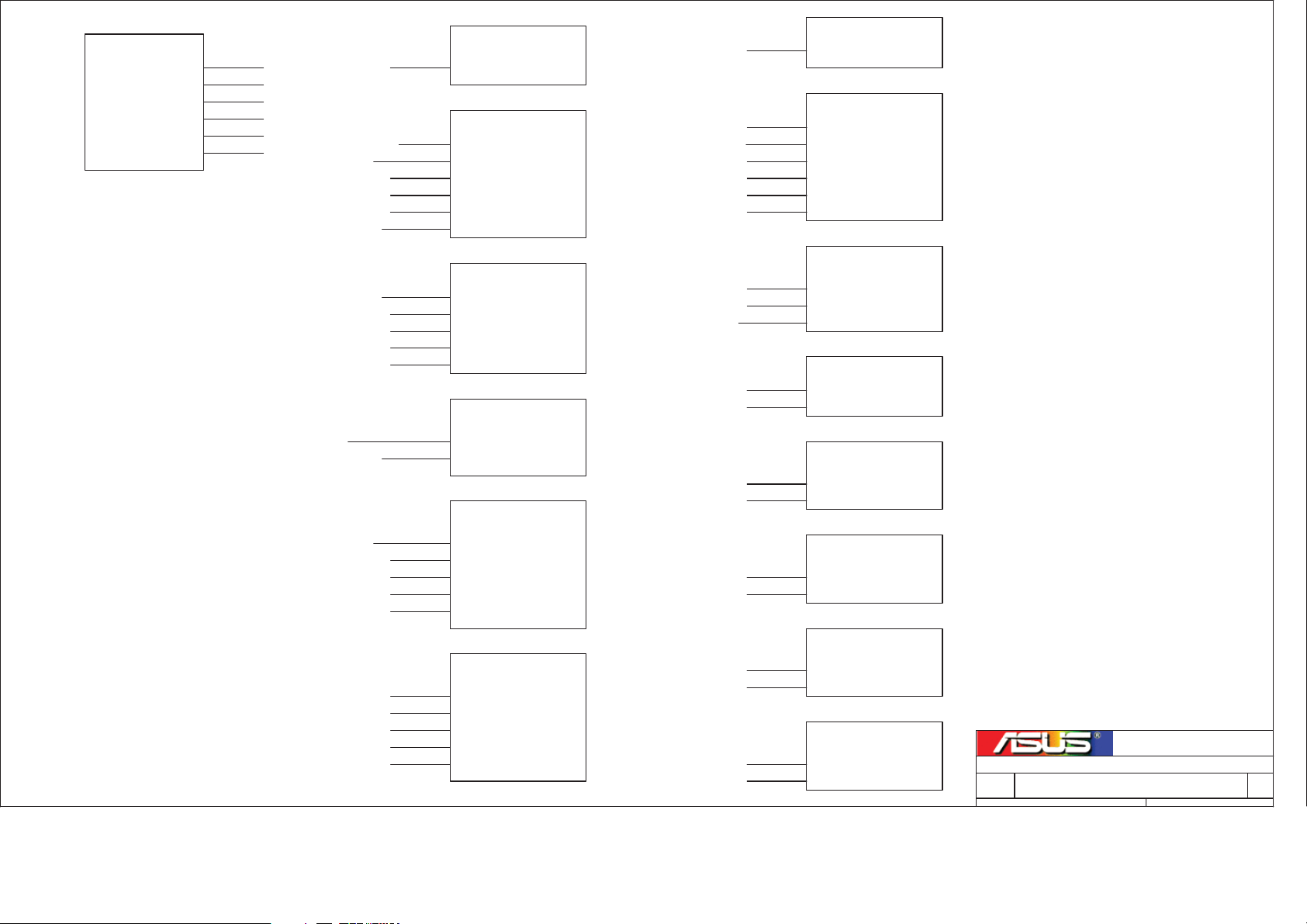

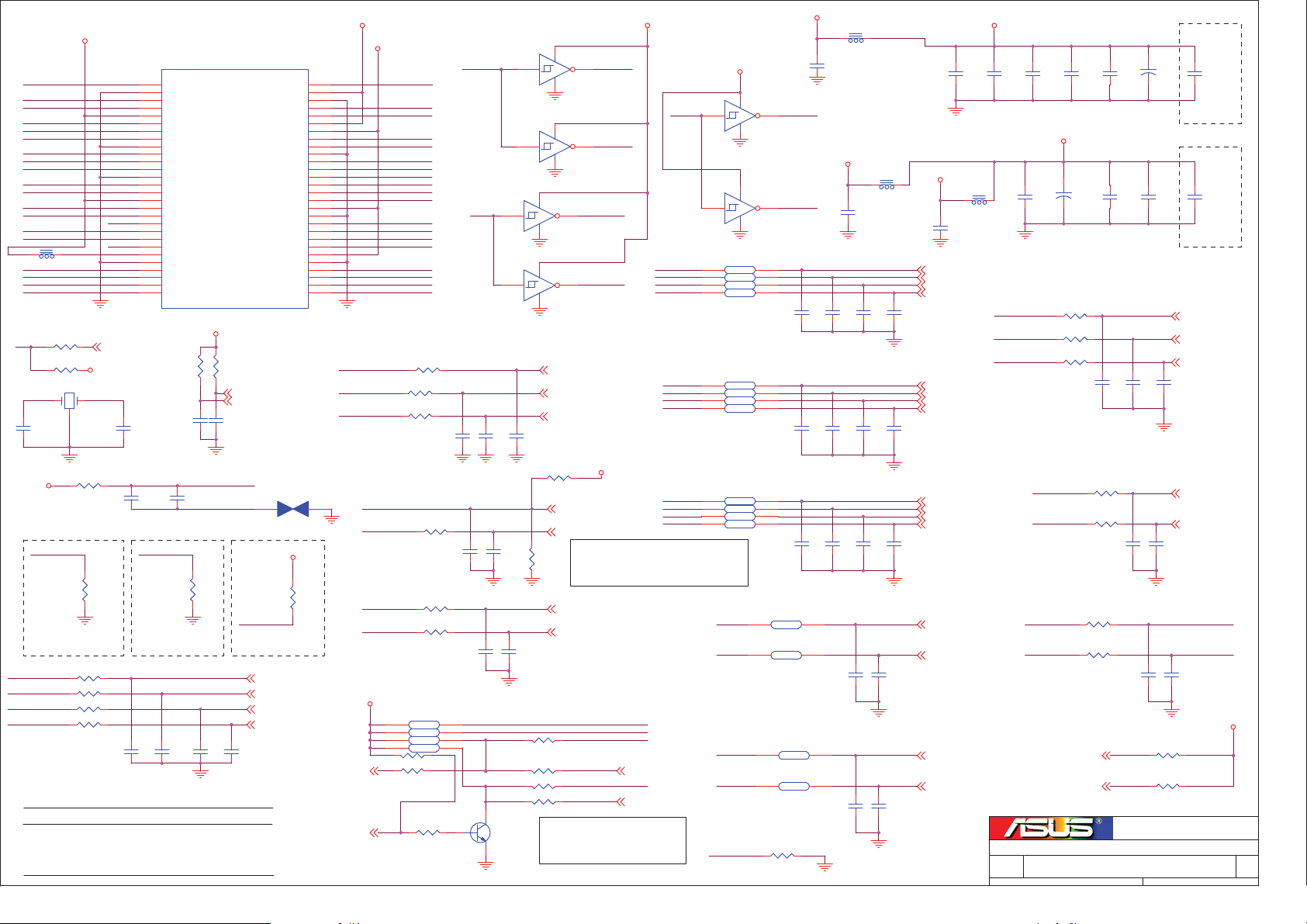

Kelut/

Kamet2

DDR SDRAM

DIMM*2

PAGE: 16,17,18

Primary IDE

Secondary IDE

8*USB2.0/1.1

2*S-ATA

PS/2

KB,Mouse

Parallel Port*1

Serial Port*1

MEM BUS

400/333/

266/200 MHz

PAGE:24

PAGE:24

PAGE:27

PAGE:22

PAGE:33

PAGE:33

PAGE:33

FDD

PAGE:24

S2K BUS

400/333/266

MHz

133MB/S

133MB/S

480Mb/S

150MB/S

2MB/S

115.2Kb/S

CPU

AMD K7

SOCKET A 462P

North Bridge

KM400A

PAGE: 13,14,15

V-Link 8X BUS

533MHz

South Bridge

VT8237CD

PAGE: 20,21,22,23

LPC BUS

33MHz

Super I/O

W83697HF

PAGE:32

PAGE: 11,12

ISA BUS

64Mb/S

INTERNAL

VGA

133M

PIXELS/S

AGP 8X BUS

533MHz

PCI BUS 33MHz

AC-LINK

12.288MHz

6CH AC97 Codec

REALTEK ALC658D

10/100 Mbps

VIA VT6103

FLASH ROM

W29C040P-70B

PAGE:36

LAN

PHY

BIOS

AGP SLOT

PAGE:19

PCI 1394

VIA VT6307

PAGE:30,31

PAGE:28

PAGE:26

PAGE:32

A7V8X-LA

Revision : 2.01-B03(Kelut)

2.01-C03(Kamet2)

CLK GEN. and

BUFFER

ICS 950910AF

PCI Slot * 3

PAGE:25

MIC

Line

Out

(or CYPRESS 28341-3)

Line

In

PAGE:28

a

http://laptop-motherboard-schematic.blogspot.com/

Asustek Computer INC.

Size Project Name

A4

Date: Sheet

PAGE:10

ATX Power

+5VSB

+3V

+5V

CPU DC-DC

RICHTEK

RT9241BCS

INPUT

+12V

+1.85V~1.1V

System

Regulator

INPUT

+5VSB

+3VSB +2.5VSB

+3V

+3V

+3V

+3VSB

+3V_DUAL

+2.5V_DUAL

+5V

+5VSB

PCB LAYER

L1 : Component (S1)

L2 : VCC

L3 : GND

L4 : Component (S4)

Title :

Engineer:

A7V8X-LA

Cyrus Chen

+12V

-5V

-12V

PAGE:7

OUTPUT

PAGE:9

OUTPUT

+3VSB

+2.5V

VDDQ

+3V_DUAL

+2.5V_DUAL

VTT_DDR

+5V_DUAL

PAGE:7,8

BLOCK

of

140Monday, October 13, 2003

Rev

2.00

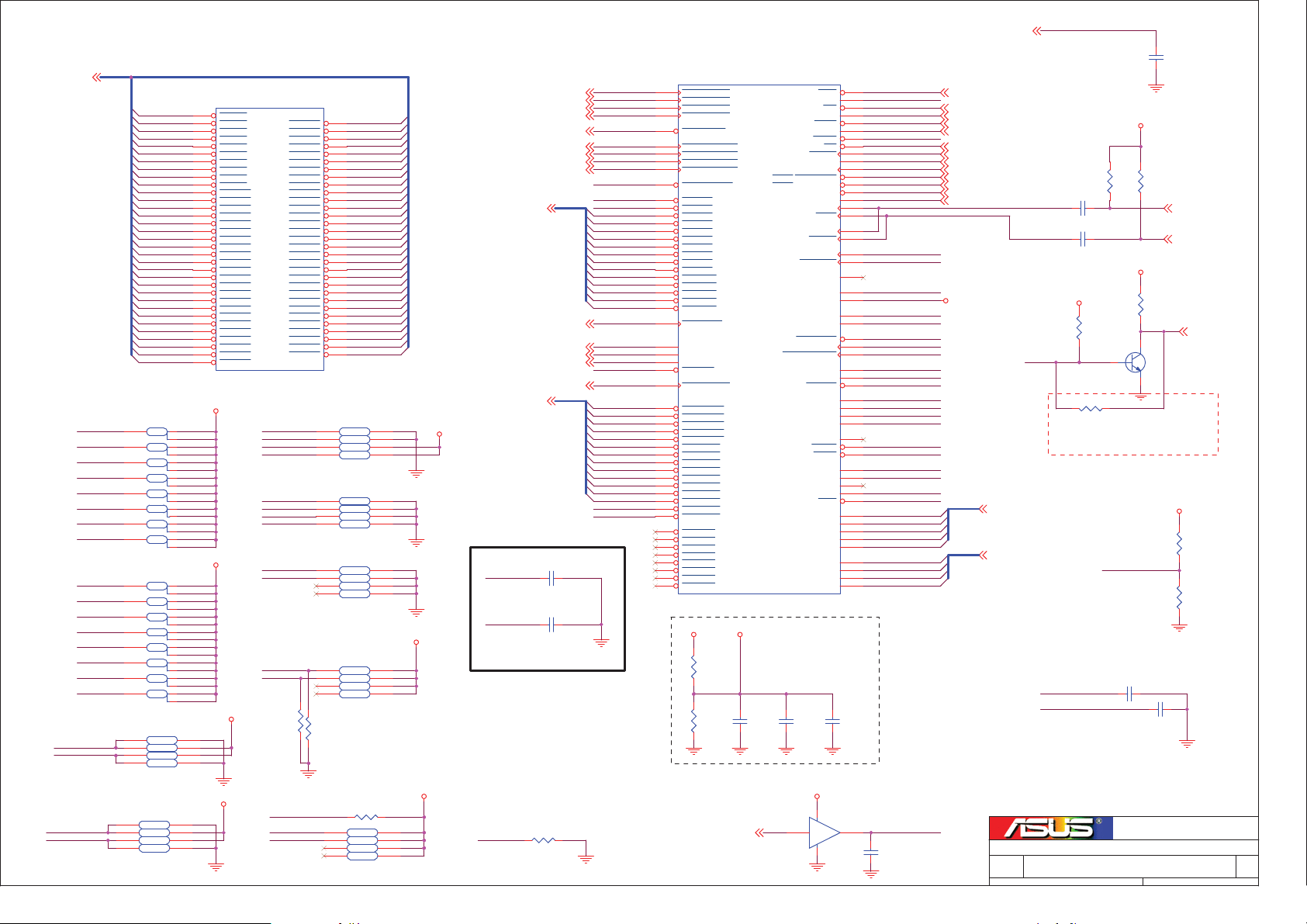

Page 2

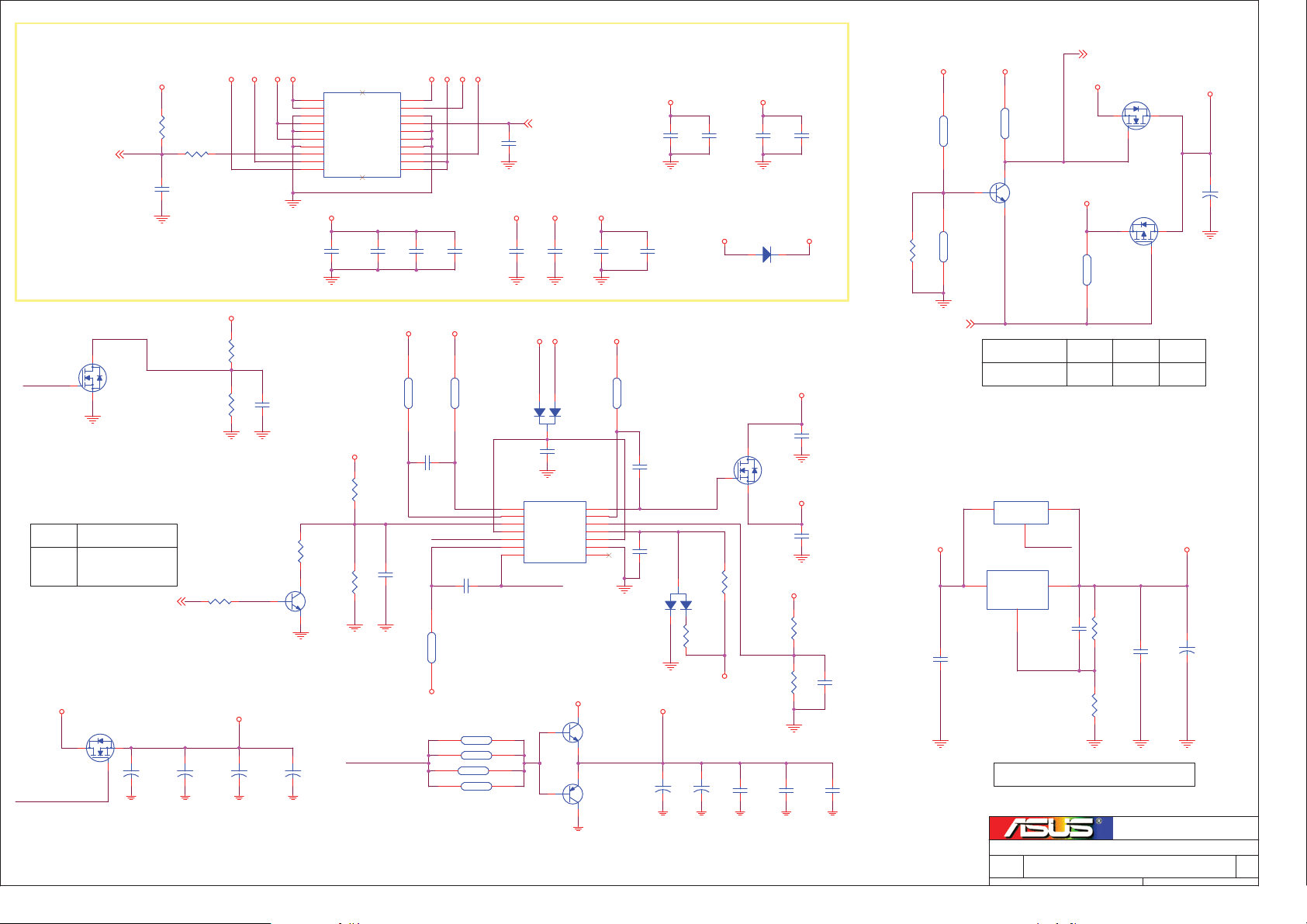

Sheet Index

Sheet

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

Sheet Title

BLOCK

CONTENT

CLOCK DISTRIBUTION CLOCK DISTRIBUTION

RESET MAP RESET MAP

POWER CONSUMPTION POWER CONSUMPTION

POWER SUPPLY BLOCK DIAGRAM

ATX & SYS PWR

SYS PWR

CPU PWR

CLOCK

CPU_1

CPU_2

NORTH BRIDGE_1

NORTH BRIDGE_2

NORTH BRIDGE_3

DDR DAMPING

DDR TERMINATION18

AGP8X

VT8237_1

VT8237_2

VT8237_3

VT8237_4

IDE & FLOPPY

LAN PHY

USB PORT

AC97 AUDIO CODEC

BOM TABLE OF CODEC

IEEE1394

IEEE1394 CONNECTOR IEEE1394 CONNECTOR

SUPER IO

KB,MOUSE & IO CONNECTOR

FID & VID

FAN

VGA CONNECTOR

PANEL & AS016

EMI CAP. & SCREW HOLES

INI & ID TABLE

GPIO TABLE

Description

BLOCK

SHEET INDEX & HISTORY OF MAIN BOARD VERSION

POWER SUPPLY BLOCK DIAGRAM

ATX & SYS PWR

SYS PWR

CPU PWR

CLOCK GEN. ICS 950910AF

CPU (AMD K7 SOCKET A 462P)

CPU (AMD K7 SOCKET A 462P)

HOST BUS

MEMORY PART

AGP, VLINK, VGA

SERIES RESISTOR

DDR SOCKET 1 , 2DDR DIMM

TERMINATION

AGP 8X SLOT

IDE, USB0-5, POWER&GND

PCI , MII , AC97 INTERFACE

SATA , USB6,7 INTERFACE

STRAPING, PULL-UP RESISTOR

IDE1,IDE2 CONNECTOR & FLOPPY

PCI SLOT 1,2,3PCI SLOT

VIA VT6103

USB CONNECTOR

REALTEK ALC658D

BOM TABLE OF CODEC

VIA VT6307

Windbond W83697HF

KB,MOUSE & IO CONNECTOR

FID & VID

FAN

VGA CONNECTOR

PANEL & AS016

EMI CAP. & SCREW HOLES

INI & ID TABLE

GPIO TABLE

92.6.3 1.02

Revision History

Change NoteDate Version

1. Fix LAN LED issue

2. Fix power noise issue

http://laptop-motherboard-schematic.blogspot.com/

BIOS/PANEL

a

Title :

ASUSTEK COMPUTER INC

Size Project Name

A3

Date: Sheet

Engineer:

A7V8X-LA

CONTENT

Cyrus Chen

240Monday, October 13, 2003

of

Rev

2.00

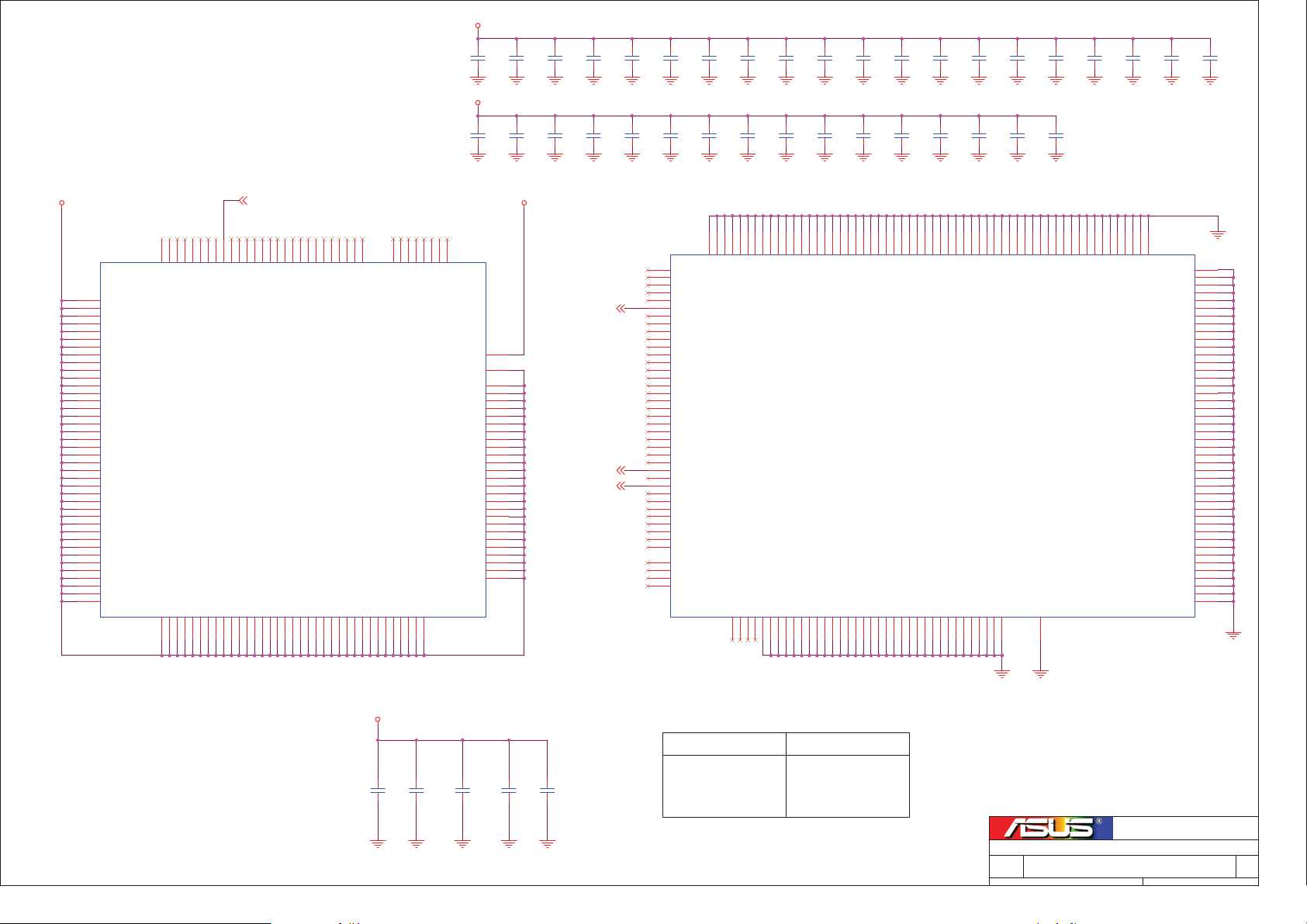

Page 3

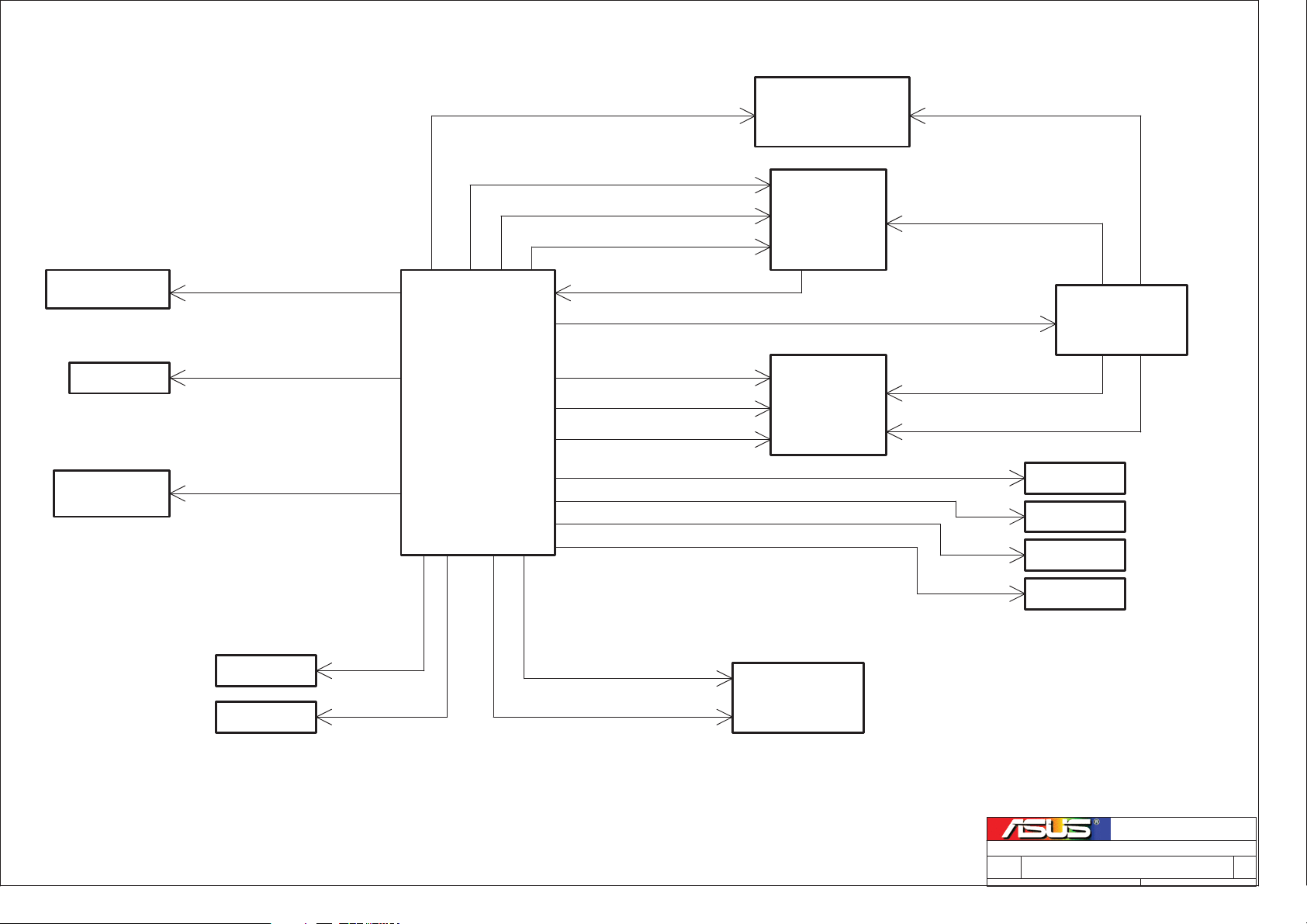

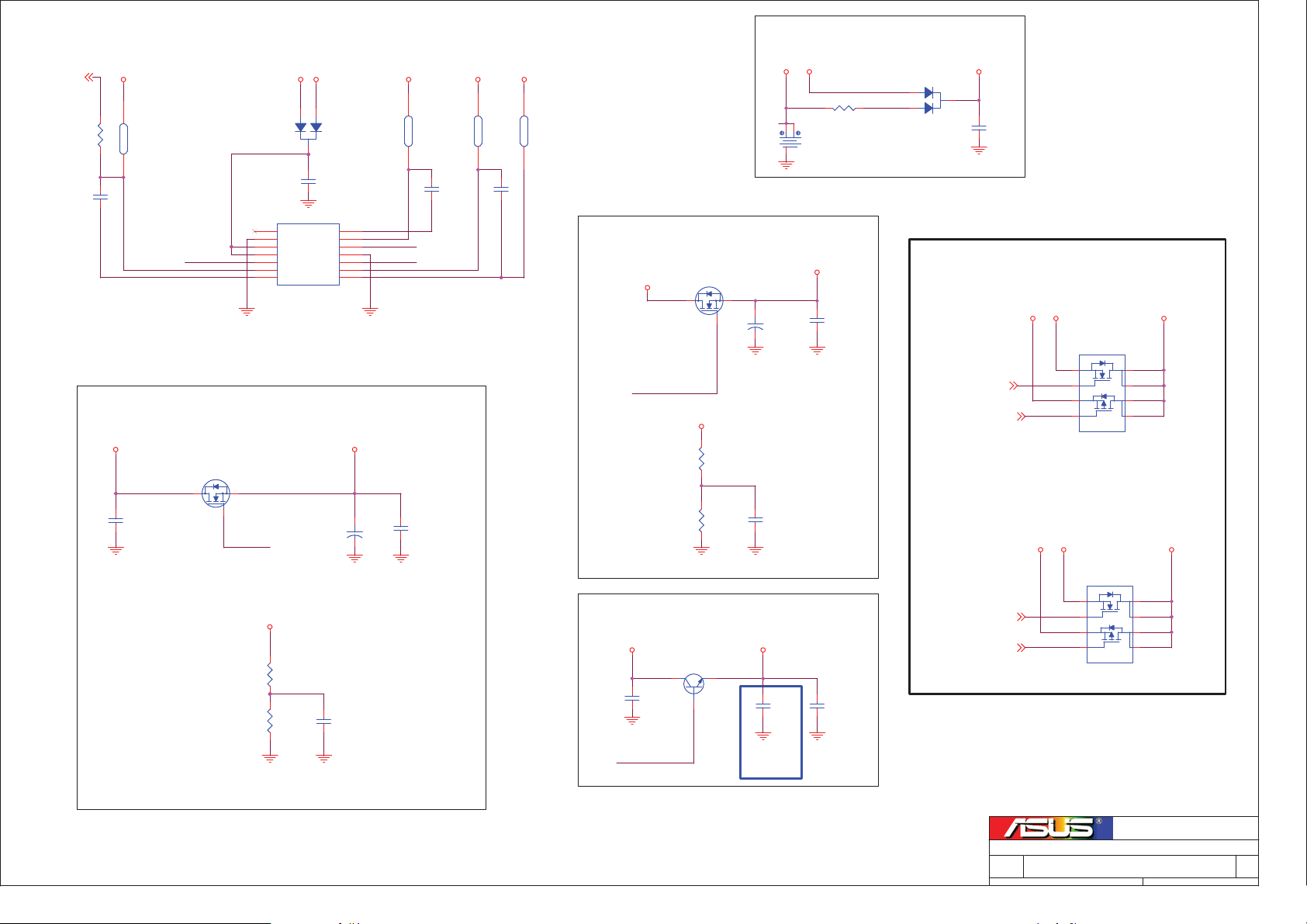

DMPDL

HFOFSBUPS

WU!9348DE

Buimpo0Cbsupo

L8!Qspdfttps

WJB

Xjocpoe!

X947:8IG

BHQ!TMPU

JDT!:61:21BG

Lfzcpbse

Npvtf

QDJ!TMPU3

QDJ!TMPU2

QDJ!TMPU4

JFFF!24:5

EES!EJNN2-3

WJB

LN511B

TO85MWD25

25N!Dmpdl

Cvggfs

25/429NI{25NBQJDDML`DQV31102770244!NI{DQVDML,.

AC97 CODEC

ALC 658D

31102770

EDML\1//6^,.

HDML`TMPU

2440211

NI{

77NI{

25N`BD:8 25/429NI{

IDML`OC,.

HDML`OC

31102770244!NI{

77NI{

NDML`GC

NDML`PVU

http://laptop-motherboard-schematic.blogspot.com/

WDML 77NI{

59NDML`VTC 59NI{

QDJDML`TC

QDJDML`T2 44NI{

QDJDML`T4

QDJDML`24:5

44NI{

44NI{QDJDML`T3

44NI{

44NI{

25NHDMLSFG`OC

25/429NI{

25/429NI{

25N`TC`PTD 25/429NI{

25/429NI{25NBQJDDML`TC

LC`DML

NT`DML

QDJDML`TJP 44NI{

59NI{59NDML`TJP

a

Title :

ASUSTEK COMPUTER INC.

Size Project Name

A3

Date: Sheet of

Engineer:

A7V8X-LA

CLOCK DISTRIBUTION

Cyrus Chen

340Monday, October 13, 2003

Rev

2.00

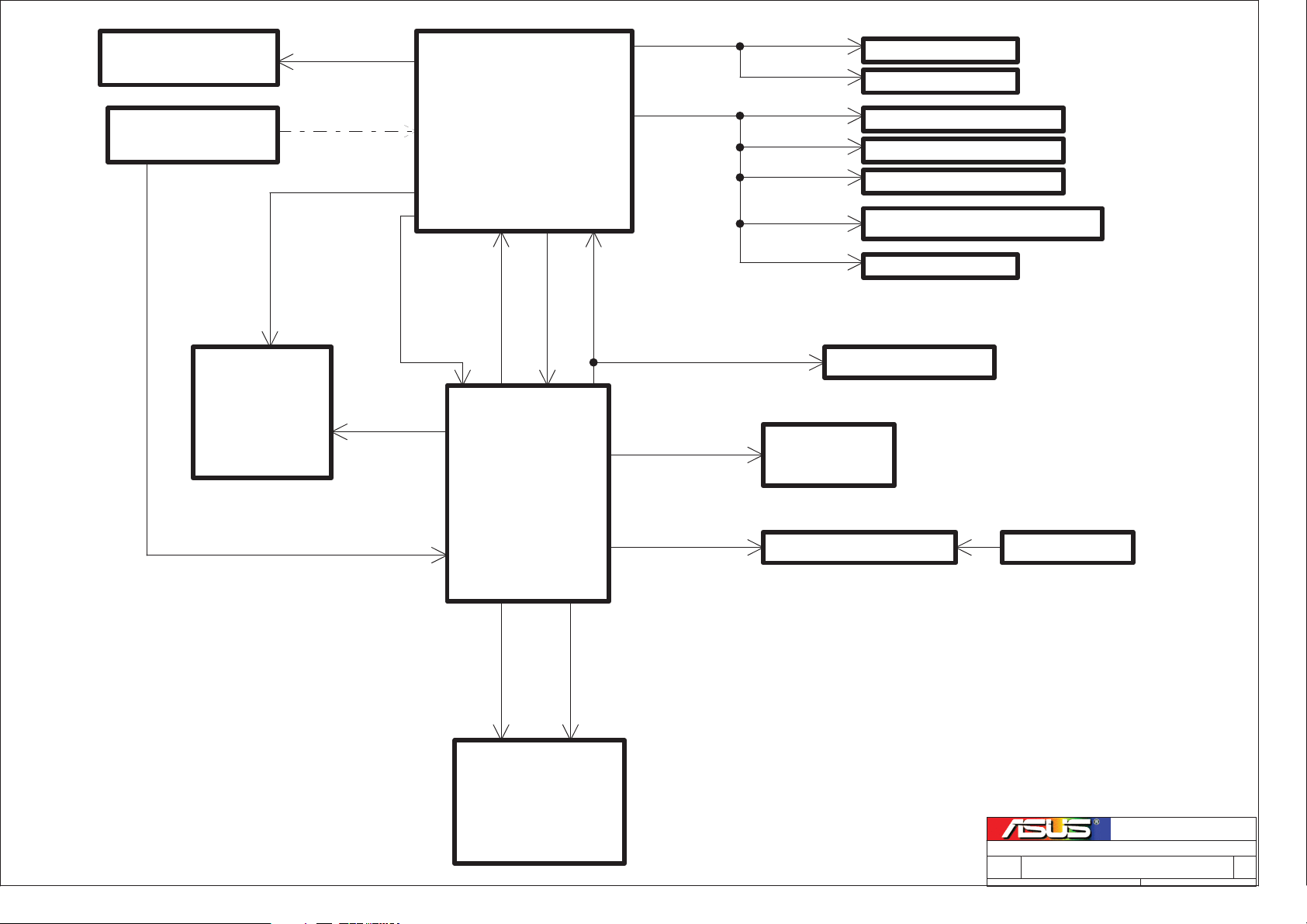

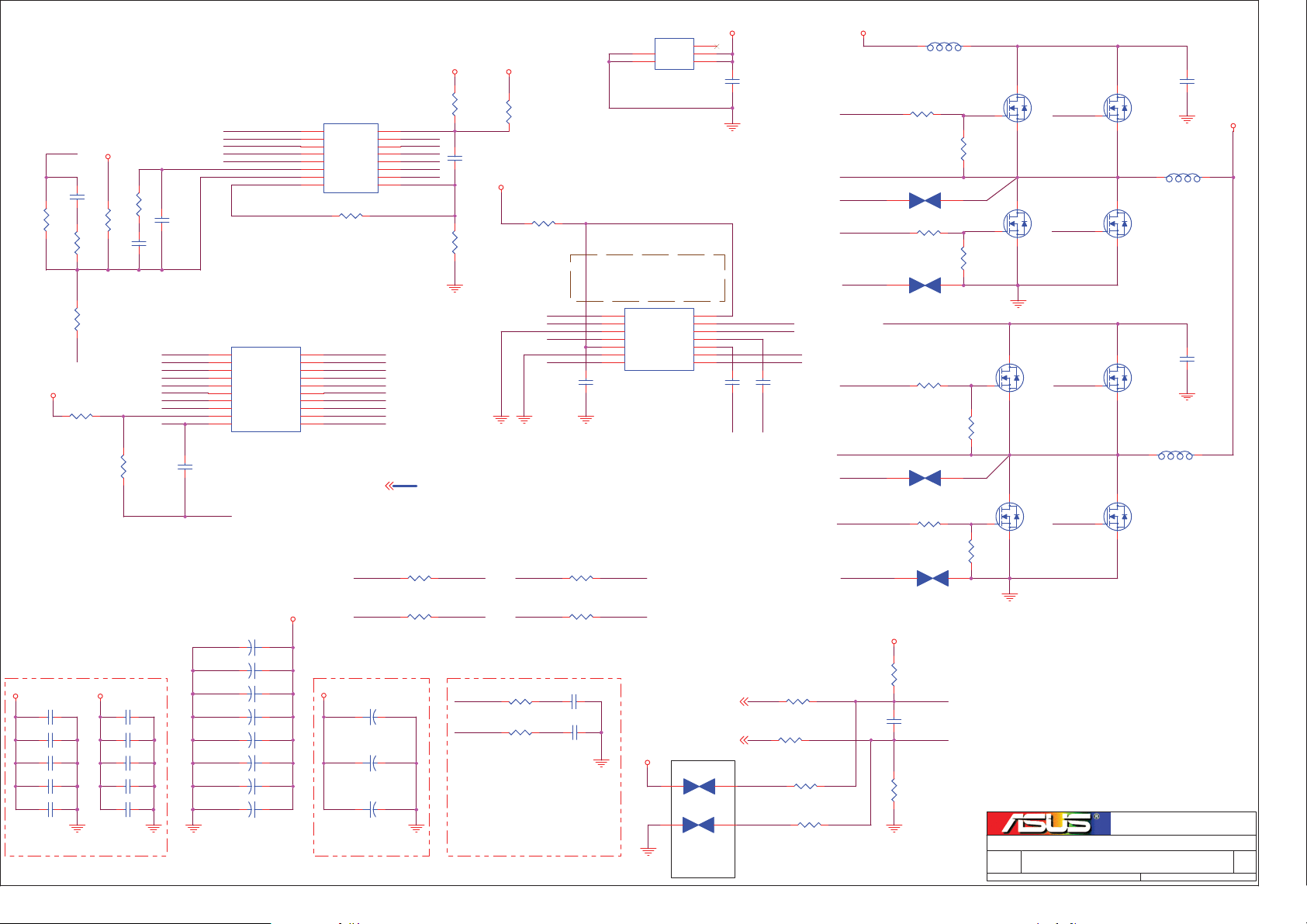

Page 4

POWER SUPPLY

PANEL

4:PSON#

RESETCON#

5:K7_PWROK

ASIC AS-16

POWER CONTROL

RESET BUFFER

8:IDERST#

8:PCIRST#

8:SIORST#

PRI_IDE

SEC_IDE

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

5V level

5V level

5V level

5V level

5V level

WINBOND SIO W83697HF

5V level

PROCESSOR

K7

7:CPURST#

2:PWRBTN#

8:1394RST#

VIA 1394

http://laptop-motherboard-schematic.blogspot.com/

3V level

1:RSMRST#

5:SB_PWROK

3:SUSB#,SUSC#

7:PCIRST_SB#

SB

7:PCIRST_AGP#

AC97_RST#

AGP SLOT 3V level

AC97 CODEC

ALC 658D

VIA

VT 8237CD

PHYRST#

LAN PHY VT6103

RC Reset

6:PWROK_NB

KM400A

7:PCIRST_SB#

NB

VIA

Title :

ASUSTeK COMPUTER INC

Size Project Name

A3

Date: Sheet

Engineer:

A7V8X-LA

RESET MAP

Cyrus Chen

440Monday, October 13, 2003

of

Rev

2.00

Page 5

ATX POWER

CWT-300W

+12V

+5VSB

-12V

+5V

+3V

-5V

30A 150W

14A 46.2W

15A 180W

2A 10W

0.5A 6W

0.5A 2.5W

VCORE

(1.6~1.7V)

VCORE

VDDQ(+1.5V)

+2.5V

+3V

+2.5VSB

+2.5V_DUAL

BATT(+3V)

+2.5V

+3V

+2.5VSB

+3VSB

VTT_DDR(+1.25V)

+2.5V_DUAL

VDDQ(+1.5V)

+3V

+5V

+12V

+3VSB

AMD Athlon

48A

KM400A

2.5A(NB+SB)

VT8237

2.5A(NB+SB)

DDR DIMM X 2

0.9A/each

3A/each

AGP SLOT

2A

6A

2A

1A

0.375A

+3VSB

BATT

VCORE

+3V

+5V

+12V

+5VSB

+12V

+3VSB

+3V_DUAL

+5V

+5VSB

+5V

+5VSB

+5V

+12V

LAN PHY(VT6103)

SIO(W83697HF)

1394(VT6307)

USB PORT X 8

0.5A/each

0.04A/each

PS2 KB/MS

0.3A 1.5W

0.1A 5W

HD

0.7A 3.5W

0.7A 8.4W

+3V

+5V

+12V

-12V

+3VSB

PCI SLOT X 3

7.6A/each

5A/each

0.5A/each

0.1A/each

0.375A/each

http://laptop-motherboard-schematic.blogspot.com/

+5V

+12V

+5V

+12V

CD ROM

0.7A 3.5W

0.7A 8.4W

FLOPPY

0.475A 2.8W

0.25A 3W

a

Title :

<OrgName>

Size Project Name

B

Date: Sheet

Engineer:

A7V8X-LA

Power consumption

Cyrus Chen

540Monday, October 13, 2003

Rev

2.00

of

Page 6

POWER SUPPLY

NOTE:

Linear REG

+5VSB HP882P

+5VSB

+5V

http://laptop-motherboard-schematic.blogspot.com/

+3.3V

+3.3V

S0,S3,S5

OP+AP9915H

OP+AP9915H x 2

AP2301N

AP9916H

+2.5V(3A)

+1.5V(4A)

OP+MMBT3904

S0,S3

S0

S0

+2.5VSB+3.3VSB(1A)

S0,S3,S5

OP+AP9915H

Switch REG

+2.5V_DUAL(5A)

S0,S3 S0,S3

OP+2SD1802

+HM772

VTT_DDR(1.5A)+3.3VDUAL

+12V

+5V

RT9241BCS

and

HIP6302CB-T

dual lay

VCORE(45A)

S0

a

Title :

Asustek Computer INC.

Size Project Name

A3

Date: Sheet

Engineer:

A7V8X-LA

POWER SUPPLY

Cyrus Chen

640Monday, October 13, 2003

of

Rev

2.00

Page 7

+5VSB -5V

R1438

0Ohm

1KOhm

(1%)

+12V

+2.5V_DUAL

1KOhm

1 2

R9

1 2

R8

(1%)

12

GNDGND

PSON#

+5V

12

R1437

4.7K

C242

0.1UF

1 2

12

GND

VTT_DDR_REF

ATX_PWROK<37>

32

3

D

Q3403

1

1

2N7002

G

S

2

GND

DDR Voltage Selection

1

2.5V

2.6V(For DDR400)

0

2 3

D

2

AP9916H

+2.5V_REF

Q30

S

3

G

1

1

DDR_GPO<21>

12

+

CE25

Do Not Stuff

/

8.2KOhm

12

+

CE26

1000UF/6.3V

R475

+2.5V_DUAL

12

12

+

CE27

1000UF/6.3V

60.4KOhm

PMBS3904

DDR_GPO

+3V_DUAL

+2.5V_DUAL_GATE

˥˸˸˸˷

+3V_DUAL ==> +2.5V_DUAL

ATX POWER

+3V

+5V

1

C23

0.1UF

R144

1%

Q3

B

GND

(1%)

1 2

3

C

E

2

12

+

1000UF/6.3V

CE3

1

2

3

4

5

6

7

8

9

10

ATXPWR

+3V1

+3V2

GND1

+5V1

GND2

+5V2

GND3

PWR0K

5VSB

+12V

+5V

12

GND

R107

1.96KOhm

1%

R106

6.49KOhm

1%

2122

hold1hold2

C6

0.1UF

+3VSB

1 2

1 2

GND

VTT_DDR_GATE

+3V3

-12V

GND4

PSON

GND5

GND6

GND7

-5V

+5V3

+5V4

20P

12

C7

Do Not Stuff

/

+2.5V_DUAL

12

GND

11

12

13

14

15

16

17

18

19

20

12

1K

RN4402A

1 2

+2.5V_DUAL_FB

+2.5V_REF

C21

0.1UF

VTT_DDR

+5V

+3V

C8

Do Not Stuff

/

+5VSB

RN4402B

C16

12

1000P

VTT_DDR_REF

VTT_DDR_FB

1K

RN4402C

5 6

1 2

3 4

5 6

7 8

-12V

12

C9

0.1UF/25V

GND

12

-5V

12

GND

C2

0.1UF

C10

Do Not Stuff

/

PSON# <37>

+5VSB

12

C11

Do Not Stuff

/

GND

+3V

GND

Around the ATX Power Connector

-12V

12

12

C5

C631

Do Not Stuff

0.1UF/25V

/

GND

12

12

C12

C13

Do Not Stuff

0.1UF

/

+5V

http://laptop-motherboard-schematic.blogspot.com/

+12V

CPUPLL_VDD

+5VSB

CPUPLL_VDD

1

1K

3 4

+2.5V_DUAL_GATE

C24

12

1000P

RN1A

1K

RN1B

1K

RN1C

1K

RN1D

1K

2

D1

12

3

GND

U32

1

OUT_1

2

IN_1-

3

IN_1+

4

V+

5

IN_2+

6

IN_2-

7

OUT_2

LM324DR

VTT_DDR_GATE

1

BAT54CW

C19

0.1UF

OUT_4

IN_4-

IN_4+

GND

IN_3+

IN_3

OUT_3

+2.5V_DUAL

2

C

B

E

3

B

1

RN4402D

14

13

12

11

10

9

8

Q4

2SD1802T-TL

3

E

Q6

HM772

C

2

1K

7 8

GND

C4412

12

1000P

12

C22

0.1UF

D2

BAT54AW

GND

VTT_DDR

12

+

1000UF/6.3V

CPUPLL_REF

3

1

2

1 2

CE6

1000UF/6.3V

R3

10Ohm

12

+

R527Do Not Stuff /X

-12V

CE7

+2.5V_DUAL ==> VTT_DDR

1

1

1 2

1 2

32

3

D

G

2

12

C25

4.7U

(0805)

+12V

12

GND

D8

Do Not Stuff

/

Q5

2N7002

S

1KOhm

1KOhm

C4

Do Not Stuff

/

+5V

C17

0.1UF

CPUPLL_VDD

+5VSB

R86

1%

1 2

R162

1%

1 2

GND

12

C49

4.7U

(0805)

12

C633

0.1UF/25V

+5VSB

12

12

C20

Do Not Stuff

/

12

C225

0.1UF

12

10uF/10V

(0805)

C43

+3V and +3VSB DUAL SWITCH

+12V_GATE <8>

+3V

S

3

G

1

+3VSB

2 3

2

RN141D

8.2K

7 8

S0,S1

S3

10

R450

8.2KOhm

RN141C

8.2K

RN141B

8.2K

+12V

RN141A

8.2K

1 2

3

Q36

C

1

B

PMBS3904

E

2

+3VSB

5 6

34

1 2

GND

+5VSB_GATE<8,37>

+5VSB_GATE

+5VSB ==> +3VSB

GND

+5VSB

Q39

Do Not Stuff

/X

Q37

AMS1085

12

C719

0.1UF

a

<OrgName>

Size Project Name

A3

Date: Sheet

23

OUTVIN

ADJ

1

+3VSB_ADJ

23

VOUTVIN

ADJ

1

+3VSB_ADJ

0.1UF

12

R484

C3

124Ohm

1%

1 2

R485

210Ohm

1%

1 2

GND

AMS1085 AND AMS2910 DUAL LAY

Title :

Engineer:

A7V8X-LA

Q1

1

S

GND

D

2

AP9916H

Q2

1

1

12

C469

+3V_DUAL

23

D

3

GND

G

AP2301N

S4,S5STATE

1

+3VSB

12

+

CE47

1000UF/6.3V

0.1UF

GND

ATX & SYS PWR

Cyrus Chen

740Monday, October 13, 2003

of

12

CE1

+

1000UF/6.3V

Rev

2.00

Page 8

BATT

VDDQ_GPO<22>

1 2

12

RN2D

1K

7 8

VDDQ_FB

VDDQ_GATE

VDDQ_REF

R16

Do Not Stuff

/X

C32

1000P

+3V ===> VDDQ

+3V VDDQ

Q7

S

2 3

D

3

2

12

C36

0.1UF

AP9915H

G

1

1

VDDQ_GATE

+3VSB

R12

1.8KOhm

1%

R15

1.47KOhm

1%

VDDQ_REF=3.3*1.5/(1.5+1.8)=1.5V

1

2

3

4

5

6

7

1 2

1 2

2

D3

U3

OUT_1

IN_1IN_1+

V+

IN_2+

IN_2OUT_2

LM324DR

1000UF/6.3V

VDDQ_REF

3

12

OUT_4

OUT_3

1

C29

IN_4-

IN_4+

GND

IN_3+

IN_3

0.1UF

CE53

12

BAT54CW

14

13

12

11

10

9

8

C39

0.1UF

+2.5V_GATE

+2.5V_FB

+2.5VREF

12

+

+2.5VREF

+2.5VSB_FB

+2.5VSB_GATE

12

(0805)

RN2A

1K

1 2

12

C34

Do Not Stuff

/

˥˸˸˸˷

C30

1000P

+2.5VSB+12VVDDQ +2.5V+5VSB

+5VSB

RN2B

3 4

RN2C

1K

C31

1K

5 6

12

1000P

BAT1 +3VSB BATT

12

R11 1K

13

2

BAT1

Battery_holder

BAT2

D22

1

2

BAT54CW

3

12

C26

0.1UF

+3V ===> +2.5V

CE11

C35

1UF/10V

+2.5V

12

12

C37

Do Not Stuff

C0805

/

˥˸˸˸˷

C515

Do Not Stuff

C1206

/X

+5V_DUAL_BACK

+5VSB +5V_DUAL_BACK+5V

Q3407

1

+12V_GATE<7>

+5VSB_GATE<7,37>

2

3

S1 D1

N

G1

S2G2D2

P

CEM2030A

8

7

D1

6

54

D2

+5V_DUAL

+5V+5VSB +5V_DUAL

Q3408

1

+12V_GATE<7>

+5VSB_GATE<7,37>

2

3

S1 D1

N

G1

S2G2D2

P

CEM2030A

8

7

D1

6

54

D2

+3V

+2.5V_GATE

AP9915H

R154

1.8KOhm

1%

R155

5.6KOhm

1%

Q9

2 3

D

2

1

1

+3VSB

+2.5VREF

1 2

1 2

S

3

12

G

+

1000UF/6.3V

C41

0.1UF

1 2

+3VSB ===> +2.5VSB

+3VSB +2.5VSB

Q8

E12

3

C33

0.1UF

C

B

PMBS3904

12

Lay in

Back

Side

12

+2.5VSB_GATE

INCREASE Q7, Q9 POLYGON

http://laptop-motherboard-schematic.blogspot.com/

a

Title :

<OrgName>

Size Project Name

A3

Date: Sheet

Engineer:

A7V8X-LA

SYS PWR

Cyrus Chen

840Monday, October 13, 2003

of

Rev

2.00

Page 9

+5V

FB+

12

C678

12

R98

4.7KOhm

VCORE

CB1 10UF/10V

CB3 10UF/10V

CB5 Do Not Stuff/

CB7 Do Not Stuff/

CB9 10UF/10V

1 2

1 2

1 2

1 2

1 2

Do Not Stuff

/

R468

Do Not Stuff

1 2

R477

332KOhm

/X

1 2

FB-

R480

12.1KOhm

/

VCORE

CB2 10UF/10V

1 2

CB4 10UF/10V

1 2

CB6 10UF/10V

1 2

CB8 10UF/10V

1 2

CB10 10UF/10V

1 2

1 2

1 2

R104

Do Not Stuff

/

CPU_12V

1 2

DVD setting

(0.191/1.8)*(1.8+12.1)=9.1894V

Placed near the socket(1206)

Vcore we use HIP6302 and

RT9241 dual lay.

Normally used RT9241

K7_VID4

K7_VID3

K7_VID2

K7_VID1

K7_VID0

VCORECOMP

VCOREFB

R464

12.1KOhm

1 2

12

C677

0.033U

X7R

12

C676

22P

NPO

VCORE_EN_R

http://laptop-motherboard-schematic.blogspot.com/

K7_VID4

K7_VID3

K7_VID2

K7_VID1

K7_VID0

VCORECOMP

VCOREFB

VCORE_EN_R

DVD ISN1

S.S

R105

1.8KOhm

U35

1

VID4

2

VID3

3

VID2

4

VID1

5

VID0

6

COMP

7

FB

8

ADJ

9

DVD

10 11

SS ISN2

RT9241BCS

12

C682

0.1U

X7R

FB-

+

+

+

+

+

+

+

+

CAP EL 1500UF/6.3V 8*20

Placed near the socket

PGOOD

PWM1

PWM2

VSEN

VCORE

CE12Do Not Stuff/

12

CE14Do Not Stuff/

12

CE8Do Not Stuff

12

CE281500UF/6.3V

12

CE151500UF/6.3V

12

CE171500UF/6.3V/

12

CE181500UF/6.3V

12

CE201500UF/6.3V

12

VDD

ISP1

ISP2

GND

ISN1

PWM CONTROLLER

U34

1

2

3

4

5

6

7

8 9

20

19

18

17

16

15

14

13

12

/X

VID4

VCC

VID3

PGOOD

VID2

ISEN1

VID1

PWM1

VID0

PWM2

COMP

ISEN2

FB

VSEN

FS/DIS GND

Do Not Stuff

1 2

R465 750Ohm

VCC+5V UGATE2

VRMPG1

ISP1

PWM1

PWM2

ISP2

VCOREFB

FB-

ISN2

K7_VID[0..4]<34>

L+12V

CE13 1200UF/16V

+

1 2

CE16 1200UF/16V

+

1 2

CE19 1200UF/16V

+

1 2

CAP EL 1200U/16V 10*25

16

15

14

13

12

11

10

VCC+5V

VRMPG1

ISP1

PWM1

PWM2

ISP2

VCOREFB

R112

1 2

3.9KOhm

R116

1 2

3.9KOhm

R82

Do Not Stuff

R0805

/X

˥˸˸˸˷

1 2

12

C674

1U

R109

0Ohm

1 2

PHASE1

PHASE2

+5V

CPU_12V

P2

G2

R43 1Ohm

R45 1Ohm

+5VSB

FB-

Snubber Circuit

Place near Drain to Source

of low-side MOSFET

CAP 4700PF/50V (0603)X7R (472)

RES 1 OHM 1/4W (1206)

R459

10Ohm

R0805

1 2

1 2

ISP1

R463

10Ohm

R0805

12

12

Adjust Voltage diff.

between VCC and PVCC

PWM1

PWM2

LGATE1

LGATE2

12

C685

1u

R113

1 2

3.9KOhm

R132

1 2

3.9KOhm

C51 4700P

1 2

C52 4700P

1 2

ATX12V

NC

2

4

1

123

POWER_CON_4P

U36

1

PWM1

2

3

4

5

6

7 8

VCC

PWM2

PHASE1

GND

UGATE1

LGATE1

BOOT1

PVCC

BOOT2

PGND

UGATE2

LGATE2 PHASE2

RT9602CS

PWM DRIVER

P1ISP2

G1ISN1ISN2

VCORE

1 2

1 2

Place near CPU

Pin M8 P8

JP1

Do Not Stuff

JP2

Do Not Stuff

CPU_12V

MH2

4

3

12

C28

0.1UF/25V

14

13

12

11

10

9

12

C686

0.1U

PHASE1

PHASE2

CAP 0.1UF/16V (0603) X7R (104)

VCOREFB+<11>

VCOREFB-<11>

/

/

VCORE_P8

PHASE1

UGATE1

PHASE2

12

C687

0.1U

CAP 0.1UF/16V (0603) X7R (104)

R46

0

1 2

R47

0

1 2

R49

Do Not Stuff

˥˸˸˸˷

/

1 2

R51

Do Not Stuff

˥˸˸˸˷

1 2

PHASE1

P1

LGATE1

UGATE2

PHASE2

P2

LGATE2

G2

/

CPU_12V

UGATE1

JP5 place near

Q11 D pin

R24 0Ohm

G1

JP3 place near

Q12 S pin

L+12V

JP8 place near

Q14 D pin

JP4 place near

Q16 S pin

VCORE

1 2

12

1 2

L1

1UH

R20

RUGATE1

1 2

4.3Ohm

JP5 Do Not Stuff

/

1 2

1 2

JP3 Do Not Stuff

/

1 2

R36

1 2

4.3Ohm

JP8

/

1 2

Do Not Stuff

R39

1 2

0Ohm

JP4

/

1 2

Do Not Stuff

R44

10Ohm

FB+

C53

˥˸˸˸˷

Do Not Stuff

/

FB-

R50

10Ohm

L+12V

21

1 2

RLGATE1

1 2

RUGATE2

RLGATE2

R23

10K

R27

10K

1 2

1 2

R38

10K

R41

10K

23

2

D

Q11

1

1

G

1

1

G

2

1

1

G

3

2

1

1

G

3

a

S

3

23

2

D

S

3

23

D

S

23

D

S

RUGATE1

AP70T03H

Q12

RLGATE1

STD90NH02L

Q14

RUGATE2

AP70T03H

Q16

RLGATE2

STD90NH02L

23

2

1

1

G

3

23

2

1

1

G

3

23

2

1

1

G

3

23

2

1

1

G

3

Vcore:

Static loading spec is 48A

@1.75V +/- 50mV

Dynamic loading spec is

30A/us +150mV -100mV

Title :

<OrgName>

Size Project Name

A3

Date: Sheet of

Engineer:

A7V8X-LA

D

S

˥˸˸˸˷

D

S

˥˸˸˸˷

D

S

D

S

˥˸˸˸˷

Q10

Do Not Stuff

/X

Q13

Do Not Stuff

/X

Q15

Do Not Stuff

/X

˥˸˸˸˷

Q17

Do Not Stuff

/X

12

C42

1u

L2

1.6UH/30A

12

C48

1u

L3

21

1.6UH/30A

CPU PWR

Cyrus Chen

940Monday, October 13, 2003

VCORE

CAP 1U/16V (1206) X7R (105)

21

CAP 1U/16V (1206) X7R (105)

Rev

2.00

Page 10

+3V

FS0/14M_SB

CLK_XI

CLK_XO

RGCLK_SLOT

RVCLK

RGCLK_NB

FS1/PCI_F

RPCICLK_1394

RPCICLK_SIO

RPCICLK_S3

RPCICLK_S1

RPCICLK_SB

RPCICLK_S2

FS3/48M

FS2/48M_SIO

L24 120Ohm/100Mhz

21

IREF_CLK

PD#

SMBCLK

SMBDATA

R25 Do Not Stuff

PD#

1 2

R61 Do Not Stuff

1 2

12

CLK_XI CLK_XO

12

C447

12P

+3V

RPCICLK_1394

VSS48M

VDD48M

/

SUSB# <21,37>

/

+3V

X1

GND

3

14.31818MHZ

GND

1 2

R40 2.2Ohm

R594

10KOhm

1 2

GND GND

U30

1

FS0/REF0

2

VSSR

3

XIN

4

XOUT

5

VDDAGP

6

AGP0

7

SELP4_K7/AGP1

8

AGP2

9

VSSAGP

10

FS1/PCI_F

11

SELSDR_DDR/PCI1

12

MULTSEL/PCI2

13

VSSPCI

14

PCI3

15

PCI4

16

VDDPCI

17

PCI5

18

PCI6

19

VSS48M

20

FS3/48M

21

FS2/24_48M

22

VDD48M

23

VDD

24

VSS

25

IREF

26

PD#/SRESET#

27

SCLK

28 29

SDATA DDRC5/SDRAM11

CY28341

4.7KOhm

12

C448

18P

12

C45

4.7U

C0805

RVCLK

10KOhm

Select DDR Mode Select K7 Mode

R14M_SB2

14M_NB

FS2/48M_SIO

FS3/48M

R338 33Ohm

1 2

R316 33Ohm

1 2

R339 22Ohm

1 2

R337 22Ohm

1 2

12

C706

Do Not Stuff

12

CLOCK GEN. Frequency table

FS3

FS2

1

1

1

1

1

1

1

1

FS1

1

0

FS0

1

1

0

Use ICS 950910AF

or CYPRESS 28341-3

VTTPWRGD#/REF1

+3V

R604

R605

4.7KOhm

1 2

1 2

SMBCLK <17,21,23>

SMBDATA <17,21,23>

12

12

C4803

Do Not Stuff

/X

12

R591

C477

Do Not Stuff

C46

0.1UF

1 2

12

GND

C4804

Do Not Stuff

/X

GND

VDD48M

VSS48M

12

C907

Do Not Stuff

/

RPCICLK_SIO

Select 6 x

IREF

C508

Do Not Stuff

/

CPU

66.670 200

166.67

66.67

66.67

133.33

1000

66.67

VDDR

VSSC

CPUT/CPUOD_T

CPUC/CPUOD_C

VDDC

VDDI

CPUCS_C

CPUCS_T

VSSI

FBOUT

BUF_IN

DDRT0/SDRAM0

DDRC0/SDRAM1

DDRT1/SDRAM2

DDRC1/SDRAM3

VDDD2

VSSD2

DDRT2/SDRAM4

DDRC2/SDRAM5

DDRT3/SDRAM6

DDRC3/SDRAM7

VDDD1

VSSD1

DDRT4/SDRAM8

DDRC4/SDRAM9

DDRT5/SDRAM10

JP6

/X

1 2

Do Not Stuff

+3V

R303

10KOhm

1 2

14MAPICCLK_SB <21>

14MGCLKREF_NB <15>

48MCLK_SIO <32>

48MCLK_USB <21>

PCIAGP

33.331

33.33

33.33

33.33

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

GNDGND

14M_CPU

RPCICLK_1394

RPCICLK_SIO

GND

CPU_FSB0<12>

CPU_FSB1<12>

+3V

CLK_+2.5V

RMCLK_OUT

RMCLK_FB

R14M_SB

R14M_AC97

+3V

RN5C

RN5D

RN5A

RN5B

+3V

147

SN74LVC14

R14M_AC97

RCPUCLK+

RCPUCLK-

RHCLK_NBRHCLK_NB+

RMCLK_FB

RMCLK_OUT

RDCLK5+

RDCLK5RDCLK2+

RDCLK2-

RDCLK3+

RDCLK3RDCLK0+

RDCLK0-

RDCLK1+

RDCLK1RDCLK4+

RDCLK4-

FS0/14M_SB

14M_1

1 2

GND

3 4

GND

147

SN74LVC14

VCC

5 6

GND

U29C

GND

147

SN74LVC14

VCC

9 8

GND

U29D

GND

VCC

GND

U29A

147

SN74LVC14

VCC

GND

U29B

14M_1

14M_2

14M_CPU

R14M_SB2

RPCICLK_S3

RPCICLK_S1

RPCICLK_SB

RPCICLK_S2

http://laptop-motherboard-schematic.blogspot.com/

R348 39Ohm

1 2

R524 22Ohm

1 2

R596 22Ohm

1 2

R386 22

1 2

R340 33Ohm

1 2

R541 22Ohm

1 2

5 6

10KOhm

7 8

10KOhm

1 2

10KOhm

3 4

10KOhm

1 2

R67 10K

1 2

R5 0Ohm

/FOR FSB200

1 2

R22

4.7K

C482

15P

C639

12

GND GND

12

Do Not Stuff

/

C641

Do Not Stuff

B

1

12

12

C

GND

C422

15P

12

C640

Do Not Stuff

/

GND

3

Q3404

PMBS3904

E

2

14MAPICCLK_CPU <11>

PCICLK_1394 <30>

PCICLK_SIO <32>

12

C507

Do Not Stuff

R292

GND

1 2

Do Not Stuff/

MCLK_OUT <14>

MCLK_FB <14>

R310

Do Not Stuff

/

1 2

GND

14M_SB_OSC <21>

12

GND

14M_AC97 <28>

C642

22P

1 2

R29 10K

1 2

R31 10K

1 2

R28 10K

1 2

R30 10K

Place R28, R29 close to

CLOCK GEN,

R30, R31 close to SB.

RDCLK0+

RDCLK0RDCLK1+

RDCLK1-

CLK_+2.5V

RDCLK4+

RDCLK4RDCLK5+

RDCLK5-

R292, R310 can tune the

reference input duty cycle.

Recommend value from 330 to 1K.

FS3/48M

FS2/48M_SIO

FS0/14M_SB

DA0 <23>

FS1/PCI_F

DA2 <23>

14M_2

+3V

147

SN74LVC14

VCC

11 10

GND

U29E

GND

147

SN74LVC14

VCC

13 12

GND

U29F

GND

7 8

22Ohm

5 6

22Ohm

3 4

22Ohm

1 2

22Ohm

5 6

0Ohm

7 8

0Ohm

1 2

0Ohm

3 4

0Ohm

5 6

0Ohm

7 8

0Ohm

1 2

0Ohm

3 4

0Ohm

RDCLK2+

RDCLK2-

RDCLK3+

RDCLK3-

IREF_CLK

14M_NB

R14M_SB

RN4D

RN4C

RN4B

RN4A

RN10C

RN10D

RN151A

RN151B

RN151C

RN151D

RN109A

RN109B

5 6

0Ohm

7 8

0Ohm

1 2

0Ohm

3 4

0Ohm

R304

1 2

475Ohm

1%

+3V_DUAL

12

GND

12

C421

15P

12

C4805

Do Not Stuff

/

12

C675

Do Not Stuff

/

RN109C

RN109D

RN10A

RN10B

GND

Do Not Stuff

C55

Do Not Stuff

/

+2.5V_DUAL

GND

12

C420

15P

12

C688

Do Not Stuff

/

12

C672

Do Not Stuff

/

C624

Do Not Stuff

/

C700

Do Not Stuff

/

L5

/

12

12

12

21

Do Not Stuff

C612

Do Not Stuff

/

12

C419

15P

12

C689

Do Not Stuff

/

12

C650

Do Not Stuff

/

12

GND

12

GND

L93

21

/

12

C921

15P

GND

12

C681

Do Not Stuff

/

GND

12

C644

Do Not Stuff

/

GND

C616

Do Not Stuff

/

C692

Do Not Stuff

/

12

C59

0.1UF

GND

+2.5V

L91

120Ohm/100Mhz

12

C617

Do Not Stuff

/

GND

PCICLK_S3 <25>

PCICLK_S1 <25>

PCICLK_SB <21>

PCICLK_S2 <25>

DCLK0+ <17>

DCLK0- <17>

DCLK1+ <17>

DCLK1- <17>

DCLK4+ <17>

DCLK4- <17>

DCLK5+ <17>

DCLK5- <17>

DCLK2+ <17>

DCLK2- <17>

DCLK3+ <17>

DCLK3- <17>

+3V

12

C60

0.1UF

21

GND

RGCLK_SLOT

RGCLK_NB

RVCLK

a

12

C61

0.1UF

CLK_+2.5V

12

C654

0.1UF

RHCLK_NB+

RHCLK_NB-

RCPUCLK+

RCPUCLK-

12

C62

0.1UF

12

+

CE34

100U/10V

R601 33Ohm

1 2

R602 33Ohm

1 2

R603 33Ohm

1 2

R325 22

1 2

R324 22

1 2

R7 10Ohm

1 2

R13 10Ohm

1 2

CPUCLK+<11>

CPUCLK-<11>

12

0.1UF

12

0.1UF

12

C881

Do Not Stuff

/

C505

20P

C805

12

+

C63

12

C691

12

C431

Do Not Stuff

/

12

12

Do Not Stuff

/

R559 Do Not Stuff/

1 2

R560 Do Not Stuff/

1 2

Title :

ASUSTEK COMPUTER INC

Size Project Name

A3

Date: Sheet

Engineer:

A7V8X-LA

CE4

10U

C625

0.1UF

12

C430

Do Not Stuff

/

GND

12

C912

20P

GND

12

GND

Cyrus Chen

12

C57

Do Not Stuff

/

Lay on the

back side

12

C1

Do Not Stuff

/

GCLK_SLOT <19>

GCLK_NB <15>

VCLK_SB <21>

HCLK_NB+ <13>

HCLK_NB- <13>

CPUCLK+

CPUCLK-

C512

Do Not Stuff

/

VCORE

CLOCK

10 40Monday, October 13, 2003

of

Rev

2.00

Page 11

14MAPICCLK_CPU<10>

SDATA#[0..63]<13>

U7A

AA35

SDATA0

W37

SDATA1

W35

SDATA2

Y35

SDATA3

U35

SDATA4

U33

SDATA5

S37

SDATA6

S33

SDATA7

AA33

SDATA8

AE37

SDATA9

AC33

SDATA10

AC37

SDATA11

Y37

SDATA12

AA37

SDATA13

AC35

SDATA14

S35

SDATA15

Q37

SDATA16

Q35

SDATA17

N37

SDATA18

9 SDATA#45

J33

SDATA19

G33

SDATA20

G37

SDATA21

E37

SDATA22

G35

SDATA23

Q33

SDATA24

N33

SDATA25

L33

SDATA26

N35

SDATA27

L37

SDATA28

J37

SDATA29

A37

SDATA30

E35

SDATA31

E31

SDATA32

VCORE

RP1F

RP1C

RP1E

RP1D

RP1B

RP1A

RP1G

RP1H

VCORE

RP2H

RP2B

RP2G

RP2A

RP2C

RP2F

RP2D

RP2E

VCORE

RN21A

RN21B

RN21C

RN21D

SDATA63

SDATA62

SDATA61

SDATA60

SDATA59

SDATA58

SDATA57

SDATA56

SDATA55

SDATA54

SDATA53

SDATA52

SDATA51

SDATA50

SDATA49

SDATA48

SDATA47

SDATA46

SDATA45

SDATA44

SDATA43

SDATA42

SDATA41

SDATA40

SDATA39

SDATA38

SDATA37

SDATA36

SDATA35

SDATA34

SDATA33

462P

DOUTVAL#

FILLVAL#

AIN#1

AIN#0

SCANCLK1

SCANINTVL

SCANCLK2

SCANSFTEN

AOUT#0

AOUT#1

PICD0#

PICD1#

R35

2KOhm

1 2

1 2

A15

A17

A11

C17

C19

E19

A21

C21

A9

C9

A13

E9

C15

E11

E13

E17

C25

E23

C29

A29

C31

C33

C35

A35

A23

C27

C23

E21

A25

A27

E29

1 2

3 4

5 6

7 8

1 2

5 6

3 4

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R34

2KOhm

SDATA#63

SDATA#62

SDATA#61

SDATA#60

SDATA#59

SDATA#58

SDATA#57

SDATA#56

SDATA#55

SDATA#54

SDATA#53

SDATA#5

SDATA#51

SDATA#50

SDATA#49

SDATA#48

SDATA#46

SDATA#44

SDATA#43

SDATA#42

SDATA#41

SDATA#40

SDATA#39

SDATA#38

SDATA#37

SDATA#36

SDATA#35

SDATA#34

SDATA#33

330

330

330

330

330

330

330

330

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

150

150

150

150

RN17A

RN17B

RN17C

RN17D

RN18A

RN18C

RN18B

RN18D

RN19A

RN19B

RN19C

RN19D

RN20A

RN20B

RN20C

RN20D

2

VCORE

/

/

/

/

+2.5V

A20M#

INIT#

INTR

IGNNE#

NMI_SB

SMI#

STPCLK#

CPURST#

FLUSH#

PLLBP#

PLLTEST#

DBREQ#

TRST#

TCK

TDI

TMS

K7CLKOUT+

K7CLKOUT-

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17 SDATA#47

SDATA#18

SDATA#1

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

7 5

680Ohm

10

3 5

680Ohm

10

6 5

680Ohm

10

4 5

680Ohm

10

2 5

680Ohm

10

1 5

680Ohm

10

8 5

680Ohm

10

9 5

680Ohm

10

9 5

680Ohm

10

2 5

680Ohm

10

8 5

680Ohm

10

1 5

680Ohm

10

3 5

680Ohm

10

7 5

680Ohm

10

4 5

680Ohm

10

6 5

680Ohm

10

1 2

100

3 4

100

5 6

100

7 8

100

AOUT#[2..14]<13>

NMI_SB

INTR

DICLK#0<13>

DICLK#1<13>

DICLK#2<13>

DICLK#3<13>

DIVAL#<13>

DOCLK#0<13>

DOCLK#1<13>

DOCLK#2<13>

DOCLK#3<13>

AIN#[2..14]<13>

AINCLK#<13>

CFWDRST<13>

CONNECT<13>

PROCRDY<13>

AOUTCLK#<13>

C4801

1 2

Do Not Stuff

C4802

1 2

Do Not Stuff

/

/

DOUTVAL#

AIN#0

AIN#1

AIN#2

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

FILLVAL#

AOUT#14

AOUT#13

AOUT#12

AOUT#11

AOUT#10

AOUT#9

AOUT#8

AOUT#7

AOUT#6

AOUT#5

AOUT#4

AOUT#3

AOUT#2

AOUT#1

AOUT#0

http://laptop-motherboard-schematic.blogspot.com/

W33

AN33

AE35

C37

C11

AL31

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AJ33

AJ21

AL23

AN23

AJ31

C13

J35

E27

E15

A33

A19

A31

E25

E33

L35

Y33

E3

G3

G5

A3

E1

G1

C3

C5

C1

E7

A5

E5

A7

C7

J3

J1

U7B

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

SADDOUTCLK

SADDOUT14

SADDOUT13

SADDOUT12

SADDOUT11

SADDOUT10

SADDOUT9

SADDOUT8

SADDOUT7

SADDOUT6

SADDOUT5

SADDOUT4

SADDOUT3

SADDOUT2

SADDOUT1

SADDOUT0

SCHECK7

SCHECK6

SCHECK5

SCHECK4

SCHECK3

SCHECK2

SCHECK1

R85

121Ohm

1%

1 2

R87

121Ohm

1%

1 2

462P

VREF_SYSVCORE

12

C165

1UF/10V

A20M

FERR

INIT

INTR

IGNNE

NMI

RESET

SMI

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

ZN

ZP

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TCK

TDI

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3SCHECK0

VREF_SYS

12

12

C166

1UF/10V

AE1

AG1

AJ3

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3U37

C167

0.1UF

FERR

NMI_SB

CPURST#

PICD0#

PICD1#

K7CLKOUT+

K7CLKOUT-

VREFMODE

ZN

ZP

PLLBP#

PLLBPCLK+

PLLBPCLK-

PLLMON1

PLLMON2

PLLTEST#

SCANCLK1

SCANCLK2

SCANINTVL

SCANSFTEN

DBREQ#

FLUSH#

TCK

TDI

TMS

TRST#

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_FID0

CPU_FID1

CPU_FID2

CPU_FID3

A20M# <21>

INIT# <21>

INTR <21>

IGNNE# <21>

NMI_SB <21>

SMI# <21>

STPCLK# <21>

K7_PWROK <37>

14MAPICCLK_CPU <10>

PICD0 <21>

PICD1 <21>

VCOREFB- <9>

VCOREFB+ <9>

VREF_SYS

CPU_VID[0..4] <34>

CPU_FID[0..3] <34>

14MAPICCLK_CPU

FERR

CPUCLK+

CPUCLK-

VCORE

R78

60.4

C110

1 2

12

680P

C111

12

680P

VCORE

R33

1KOhm

/X

Q35

1 2

B

1

PMBS3904

R188

1 2

Do Not Stuff

/

BIOS set to 1.5V

VREFMODE

C112

1 2

15P

+3V

1 2

1 2

3

C

E

2

1 2

C109

Do Not Stuff

1 2

/

R79

60.4

CPUCLK+ <10>

CPUCLK- <10>

R189

510Ohm

VCORE

C113

15P

FERR# <21>

R76

Do Not Stuff

/

1 2

R77

330

1 2

PLLBPCLK+

PLLBPCLK-

1 2

100

3 4

100

5 6

100

7 8

100

RN23A

RN23B

RN23C

RN23D

VCORE

ZN

PLLMON1

PLLMON2

R83 39Ohm 1%

1 2

1 2

56

3 4

56

5 6

56

7 8

56

RN22A

RN22B

RN22C

RN22D

VCORE

+5V

147

U27F

ZP

R84

1 2

56.2Ohm

1%

PCIRST_SB#<15,19,21,37>

VCC

13 12

GND

7407

12

CPURST#

C18

/

Do Not Stuff

a

Title :

ASUSTEK COMPUTER INC

Size Project Name

A3

Date: Sheet

Engineer:

A7V8X-LA

CPU_1

Cyrus Chen

11 40Monday, October 13, 2003

of

Rev

2.00

Page 12

VCORE

12

VCORE

12

C121

0.1UF

C141

0.1UF

12

12

12

12

C122

0.1UF

12

C142

0.1UF

12

12

12

C123

0.1UF

C143

0.1UF

C124

0.1UF

12

C144

0.1UF

12

C125

0.1UF

12

C145

0.1UF

12

C126

C127

0.1UF

0.1UF

12

12

C146

C147

0.1UF

0.1UF

12

12

12

C128

0.1UF

C148

0.1UF

C129

0.1UF

12

C149

0.1UF

12

12

12

C130

0.1UF

C150

0.1UF

C131

0.1UF

12

C151

0.1UF

12

C132

C133

0.1UF

0.1UF

12

12

C152

0.1UF

C153

0.1UF

12

12

12

C134

0.1UF

C154

0.1UF

C135

0.1UF

12

C155

0.1UF

12

12

12

C136

0.1UF

C156

0.1UF

C137

0.1UF

C138

0.1UF

12

12

C139

C140

0.1UF

0.1UF

VCORE CPUPLL_VDD

AD30

AD8

AF10

AF28

AF30

H12

H16

H20

H24

P30

T30

X30

AB30

AF14

AF18

AF22

AF26

AM34

AK36

AK34

AK30

AK26

AK22

AK18

AK14

AK10

AL5

AH26

AM30

AH22

AH18

AH14

AH10

AH4

AH2

AF36

AF34

AD6

AM26

AD4

AD2

M8

R8

V8

Z8

U7C

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

462P

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

AB36

AB34

AB32Z6Z4Z2X36

AF32

VCC_SRAM5

VCC_CORE45

AF6

AF8

AH30

AH8

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

X34

AM22

X32V6V4V2T36

CPU_FSB1 <10>

AJ9

AK8

AL9

AM8

F30F8H10

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

T34

H28

H30

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_CORE56

VCC_CORE57

VCC_CORE58

T32R6R4R2AM18

H32H6H8

VCC_SRAM23

VCC_SRAM24

VCC_CORE59

VCC_CORE60

P36

K30K8AJ7

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_CORE61

VCC_CORE62

VCC_CORE63

P34

P32M4M6

AL7

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_CORE66

VCC_CORE64

VCC_CORE65

M2

AN7

VCC_SRAM31

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

K36

K34

K32H4H2

G25

G17G9N7Y7AG7

KEY4

KEY6

KEY8

KEY10

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

AM14

F36

F34

F32

AG15

AG29

KEY12

KEY14

KEY16

KEY18

VCC_A

VCC_Z

VCC_CORE101

VCC_CORE100

VCC_CORE99

VCC_CORE98

VCC_CORE97

VCC_CORE96

VCC_CORE95

VCC_CORE94

VCC_CORE93

VCC_CORE92

VCC_CORE91

VCC_CORE90

VCC_CORE89

VCC_CORE88

VCC_CORE87

VCC_CORE86

VCC_CORE85

VCC_CORE84

VCC_CORE83

VCC_CORE82

VCC_CORE81

VCC_CORE80

VCC_CORE79

VCC_CORE78

VCC_CORE77

VCC_CORE76

VCC_CORE75

AJ23

AC7

AJ5

B4

B8

B12

B16

B20

B24

B28

AM2

B32

B36

D2

D4

D8

D12

D16

D20

D24

AM10

D28

D32

F12

F16

F20

F24

F28

H14

H18

H22

H26

U7D

AA31

NC1

AC31

NC2

AE31

NC3

AG23

NC6

AG25

NC7

CPU_FSB0<10>

DXP<32>

DXN<32>

AG31

AG5

AJ11

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

N31

Q31

S31

U31

W31

Y31

AG19

G21

AG21

G19

AN27

AL27

AN25

AL25

NC8

NC9

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

J31

NC24

J5

NC25

L31

NC27

NC28

NC29

NC30

S7

NC31

NC32

U7

NC33

NC34

W7

NC35

NC36

Y5

NC37

NC42

NC43

NC44

NC45

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

M30P8R30T8V30X8Z30

VSS1

VSS2

VSS3

VSS4

VSS5

SIDE_NC1

SIDE_NC2

1234567891011121314151617181920212223242526272829303132333435

VSS6

VSS7

VSS8

462P

SIDE_NC3

SIDE_NC4

SIDE_G5

VSS9

VSS10

VSS11

SIDE_G6

SIDE_G7

SIDE_G8

AB8

AF12

VSS12

VSS13

SIDE_G9

SIDE_G10

AF16

AF20

AF24

VSS14

VSS15

SIDE_G11

SIDE_G12

AM36

AK32

AK28

VSS16

VSS17

VSS18

SIDE_G13

SIDE_G14

SIDE_G15

AK24

AK20

AK16

VSS19

VSS20

VSS21

SIDE_G16

SIDE_G17

SIDE_G18

AK12

AK4

AK2

VSS22

VSS23

VSS25

SIDE_G19

SIDE_G20

SIDE_G21

AH36

AM32

AH34

VSS26

VSS27

VSS28

SIDE_G22

SIDE_G23

SIDE_G24

AH32

AH28

AH24

VSS29

VSS30

VSS31

SIDE_G25

SIDE_G26

SIDE_G27

AH20

AH16

AH12

VSS32

VSS33

VSS34

SIDE_G28

SIDE_G29

SIDE_G30

AF4

AF2

AD36

VSS35

VSS37

VSS38

SIDE_G31

SIDE_G32

SIDE_G33

AD34

AB6

AD32

VSS39

VSS40

VSS41

SIDE_G34

SIDE_G35

SIDE_G36

36

AB4

VSS42

VSS43

AB2

VSS44

Z36

VSS45

Z34

AE7

Z32X6AM28X4X2

VSS46

VSS47

VSS48

VSS49

VSS_Z

VSS50

VSS51

V36

VSS52

V34

V32T6T4T2R36

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

R34

AM24

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

R32

P6

P4

P2

M36

M34

M32

K6

K4

K2

AM20

H36

H34

F26

F22

F18

F14

F10

F6

F4

F2

AM16

D36

D34

D30

D26

D22

D18

D14

D10

D6

B34

AM12

B30

B26

B22

B18

B14

B10

B6

B2

AM4

AK6

AM6

CPUPLL_VDD

12

C159

1U

CPUPLL_VDD

12

12

C160

0.1UF

C162

0.01U

http://laptop-motherboard-schematic.blogspot.com/

CPU FSB Frequency CPU_FSB1 CPU_FSB0

12

12

C163

C15

100P

10UF/10V

1206

200 Mhz 0 0

166 Mhz 0 1

133 Mhz 1 1

RESERVED 1 0

a

Title :

ASUSTEK COMPUTER INC

Size Project Name

A3

Date: Sheet

Engineer:

A7V8X-LA

CPU_2

Cyrus Chen

12 40Monday, October 13, 2003

of

Rev

2.00

Page 13

NORTH BRIDGE 1 of 3 ( HOST BUS)

Change L7, L8, L11,

L12 to 09-023100010

LCL FILTER

DICLK#_0

L7

21

0.26Ohm/100MHz

L8

21

12

C168

3.3pf

0.26Ohm/100MHz

DICLK#0 <11>

AIN#[2..14]<11>

AOUT#[2..14]<11>

AOUTCLK#<11>

DOCLK#[0..3]<11>

DIVAL#<11>

CFWDRST<11>

CONNECT<11>

PROCRDY<11>

HCLK_NB+<10>

HCLK_NB-<10>

HEATSINK1

2

HEAT SINK

(change to 13-070100720)

NB Heatsink

CBOLT

A_INCLK#

HCLK_NB+_D

HCLK_NB-_D

TESTIN1

S2KCOMP

S2KVREF

TESTIN0

1

AIN#2

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

DICLK#_0

DICLK#_1

DICLK#_2

DICLK#_3

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

+2.5V

C16

D17

C15

D15

C13

N26

N24

N25

R22

R23

R26

R24

R25

G23

C19

D14

C14

G21

N21

U26

U24

U22

E17

A14

A15

E16

B14

E15

A16

A13

B15

P22

P26

T22

P24

T24

T23

A19

A24

L24

B24

F23

L22

E13

E14

F22

E10

L21

F17

F12

T26

V26

T25

V25

V24

V23

V22

U8A

AIN2#

AIN3#

AIN4#

AIN5#

AIN6#

AIN7#

AIN8#

AIN9#

AIN10#

AIN11#

AIN12#

AIN13#

AIN14#

AINCLK#

AOUT2#

AOUT3#

AOUT4#

AOUT5#

AOUT6#

AOUT7#

AOUT8#

AOUT9#

AOUT10#

AOUT11#

AOUT12#

AOUT13#

AOUT14#

AOUTCLK#

DICLK0#

DICLK1#

DICLK2#

DICLK3#

DOCLK0#

DOCLK1#

DOCLK2#

DOCLK3#

DINVAL#

CFWDRST

CONNECT

PROCRDY

HCLK

HCLK#

TESTIN1

S2KCOMP

S2KVREF0

S2KVREF1

TESTIN0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

+2.5V VCORE

J14

M21

J13

J15

J17

J16

VTT2

VTT1

VTT3

VTT5

VTT4

VDS2K

VSS2K

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

K21

B13

D13

F14

T21

B16

D16

B19

D19

J18

VTT6

B22

K18

VSS9

D22

L18

VTT8

VTT7

VSS10

VSS11

B25

M18

VTT9

VSS12

E23

P18

N18

VTT10

VSS13

E25

H23

R18

VTT12

VTT11

VSS14

VSS15

H25

VSS16

L23

L25

+2.5V +2.5VHCLK

F10

F15

F19

F20

P21

R21

V21

W21

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VSS17

VSS18

VSS19

VSS20

VSS21

AGND1

P23

P25

U23

U25

F21

G22

AVDD1

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

TESTIN0

TESTIN1

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

KM400

B17

D20

B20

C20

A20

C21

E19

B21

B18

E18

A17

C18

A18

D18

C17

E20

A21

D21

C22

A26

C25

C23

D24

B26

E21

A23

B23

A22

D23

A25

C26

C24

E26

F26

G25

G26

J26

H26

G24

H24

E22

E24

D25

D26

F25

F24

J25

H22

L26

M26

M25

M23

M24

K23

N22

M22

J24

K22

K25

K26

J23

N23

J22

K24

C11

D11

E11

A12

B12

C12

D12

E12

W22

R93

Do Not Stuff

/

1 2

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#4

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#5

SDATA#60

SDATA#61

SDATA#62

SDATA#63

+2.5V

R94

Do Not Stuff

/

1 2

8

9

+3V +2.5V

R91

R92

Do Not Stuff

Do Not Stuff

/X

/X

1 2

1 2

SDATA#[0..63] <11>

Lay in

Back

Side

R74

R75

1KOhm

1KOhm

1 2

1 2

12

C175

1UF/10V

DICLK#_1

DICLK#_2

DICLK#_3

A_INCLK#

http://laptop-motherboard-schematic.blogspot.com/

S2K BUS COMPENSATION

12

VCORE

1 2

49.9Ohm

C177

0.1UF

+2.5V

12

C186

1UF/10V

R88

1%

12

12

C250

0.1UF

C179

1UF/10V

12

S2KCOMP

R88 ==> 300 Ohm 1% for KM400

49.9 Ohm 1% for KM400A

VCCH : HOST CPU INTERFACE POWER

12

C176

1UF/10V

12

12

C116

C185

1UF/10V

1UF/10V

Lay in

Back

Side

L9

0.26Ohm/100MHz

L11

0.26Ohm/100MHz

L13

0.26Ohm/100MHz

L35

0.26Ohm/100MHz

VCORE

12

C187

1UF/10V

21

21

21

21

C251

0.1UF

12

C188

0.1UF

L10

12

C169

5P

12

C170

3.3pf

12

C171

5P

12

C184

5P

NORTH BRIDGE S2K REFERENCE

VOTAGE (1/2VCORE)

S2KVREF

AVDDHCLK/AGNDHCLK : POWER/GROUND FOR

12

12

INTERNAL CPU CLOCK LOGIC

C27

1UF/10V

C181

0.1UF

a

ASUSTEK COMPUTER INC.

Size Project Name

A3

Date: Sheet

12

+2.5VHCLK

12

0.26Ohm/100MHz

L12

0.26Ohm/100MHz

L14

0.26Ohm/100MHz

L36

0.26Ohm/100MHz

C172

0.01U

C182

0.01U

21

21

21

21

12

+2.5V

21

12

DICLK#1 <11>

DICLK#2 <11>

DICLK#3 <11>

AINCLK# <11>

VCORE

R89

121Ohm

1 2

R90

C173

121Ohm

0.1UF

1 2

L25

120Ohm/100Mhz

C183

Do Not Stuff

/

Lay in

Back

Side

Title :

Engineer:

A7V8X-LA

Lay in

Back

1%

Side

12

C174

0.1UF/25V

1%

NORTH BRIDGE_1

Cyrus Chen

13 40Monday, October 13, 2003

of

Rev

2.00

Page 14

NORTH BRIDGE 2 of 3 ( MEMORY)

+2.5V_DUAL

AA7V9V10

V11

V12

V13

V14

VCC3_2

VSS25

AE4

AC7

VCC3_3

VCC3_4

VCC3_5

VSS26

VSS27

VSS28

AE7

AC10

VCC3_6

VCC3_7

VSS29

VSS30

AE10

AC13

V15

AE13

U8B

VCC3_1

MAA[0..14]<17,18>

CKE0<16>

CKE1<16>

CKE2<16>

CKE3<16>

CS#0<16>

CS#1<16>

CS#2<16>

CS#3<16>

SRASA#<16>

SCASA#<16>

SWEA#<16>

DQM[0..7]<16>

DQS[0..7]<16>

MAA0

AC11

AB12

AC12

AB14

AB16

AB17

AB15

AC18

AE17

AC17

AB10

AC9

AF17

AB18

AB19

AC21

AD24

AB22

AC24

AB20

AF24

AD6

AC5

AC6

AB6

AB7

AD5

AB11

AD7

AB9

AD25

AD22

AF19

AE15

AF12

AB8

AF4

AD26

AF22

AD19

AF15

AE12

AC8

AD4

AA10

AA18

Y26

Y24

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

CS0#

CS1#

CS2#

CS3#

CS4#

CS5#

SRASA#

SCASA#

SWEA#

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

MVREF1

MVREF0

VSS22

AC3

VSS23

AE2

VSS24

AC4

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

SRASA#

SCASA#

SWEA#

DQM0

DQM1 MD51

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

MVREF0

V16

V17

VCC3_8

VCC3_9

VSS31

VSS32

Y23

AC16

V18

T18

VCC3_12

VCC3_10

VCC3_11

VSS33

VSS34

VSS35

AE16

Y25

AA15

AA21

U18

VCC3_13

VCC3_14

VSS36

VSS37

AC19

AE19

AC22

VCC3_15

VSS38

VSS39

VSS40

AE22

AC25

+2.5VMCLK

VSS41

AE25

AA22Y21

AVDD2AGND2

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DCLKO

DCLKIN

VSS42

AA13

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

KM400

W23

W24

AA25

AB26

W26

W25

AA26

AA24

AB25

AB24

AF25

AE24

AB23

AC26

AE26

AF26

AD23

AE23

AD21

AF21

AC23

AF23

AE21

AB21

AC20

AF20

AF18

AD18

AD20

AE20

AE18

AD17

AF16

AC15

AC14

AE14

AD16

AD15

AD14

AF14

AF13

AD12

AD11

AF11

AD13

AB13

AE11

AD10

AF10

AE9

AE8

AF7

AF9

AD9

AF8

AD8

AE6

AF5

AE3

AF1

AF6

AE5

AF3

AF2

Y22

AA23

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

1 2

R97

22Ohm

MD[0..63] <16>

MCLK_OUT <10>

MCLK_FB <10>

12

C480

Do Not Stuff

/

+2.5V_DUAL

12

C223

1UF/10V

AVMCLK/AGNDMCLK : POWER/GROUND FOR

DRAM CLCOK DESKEW CIRCUIT

+2.5VMCLK

120Ohm/100Mhz

MVERF0/1 : SSTL_2 RECEIVER VREF

FOR DDR

MVREF0

12

C205

Do Not Stuff

/

+2.5V

21

L16

12

C191

1UF/10V

12

C208

0.1UF

Do Not Stuff

+2.5V_DUAL

1 2

1 2

L20

/X

R95

1KOhm

1%

R96

1KOhm

1%

+2.5V_DUAL

21

VCC3 : +2.5V LEVEL POWER

+2.5V_DUAL

12

12

C213

1UF/10V

+2.5V_DUAL

12

12

12

C192

1UF/10V

C178

0.1UF

12

C241

0.1UF

12

C190

1UF/10V

12

C193

1UF/10V

C214

1UF/10V

/X

C194

Do Not Stuff

12

C215

1UF/10V

Lay in

Back

Side

12

C195

Do Not Stuff

CBOLT

http://laptop-motherboard-schematic.blogspot.com/

a

Title :

ASUSTEK COMPUTER INC.

Size Project Name

A3

Date: Sheet

Engineer:

A7V8X-LA

NORTH BRIDGE_2

Cyrus Chen

14 40Monday, October 13, 2003

Rev

2.00

of

Page 15

NORTH BRIDGE 3 of 3 (AGP,VLINK,VGA)

J6N6P6R6T6U6K9L9M9N9P9

U8C

VCC1_1

VCC1_2

VCC1_3

VCC1_4

VCC1_5

VCC1_6

VCC1_7

VCC1_8

VCC1_9

VCC1_12

VCC1_10

VSS49

VSS50

VSSQQ

VSS51

VSS52

AA3

VCC1_11

VSS53

VSS54

L11

AA5

CBOLT

GAD[0..31]<19>

GC/BE#0<19>

GC/BE#1<19>

GC/BE#2<19>

GC/BE#3<19>

GAD_STBF0<19>

GAD_STBS0<19>

GAD_STBF1<19>

GAD_STBS1<19>

GSB_STBF<19>

GSB_STBS<19>

GFRAME#<19>

GIRDY#<19>

GTRDY#<19>

GSTOP#<19>

GDEVSEL#<19>

GGNT#<19>

GREQ#<19>

GST0<19>

GST1<19>

GST2<19>

DBIL<19>

DBIH_PIPE#<19>

GWBF#<19>

GRBF#<19>

GCLK_NB<10>

AGPVREF_GC<19>

AGP8XDET#<19>

GSERR#<19>

GAD0

W2

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GSBA0<19>

GSBA1<19>

GSBA2<19>

GSBA3<19>

GSBA4<19>

GSBA5<19>

GSBA6<19>

GSBA7<19>

GPAR<19>

AGPNCOMP

GD0/FPD10

W1

GD1/FPD11

V3

GD2/FPDVICLK

W3

GD3/FPD09

V1

GD4/FPD08

U2

GD5/FPD07

U1

GD6/FPD06

U3

GD7/FPD05

T4

GD8/FPDVIDET

T5

GD9/FPDVIHS

R3

GD10/FPD01

P2

GD11/FPD23

R1

GD12/FPD00

P1

GD13/FPD22

P3

GD14/FPD21

N3

GD15/FPD20

N2

GD16/FPD18

M1

GD17/FPD17

M3

GD18/FPD16

M5

GD19/FPDE

L1

GD20/FPD14

L4

GD21/FPCLK

L2

GD22/FPD13

L3

GD23/FPD15

J1

GD24/DVP1D09

H5

GD25

J3

GD26/DVP1D10

H4

GD27

H1

GD28/DVP1D07

H3

GD29/DVP1D06

H2

GD30/DVP1D08

G4

GD31/DVP1D04

T1

GCBE0#/FPD03

P4

GCBE1#/SB_DA

N1

GCBE2#/FPD19

K3

GCBE3#/DVP1D11

T3

ADSTB0F/FPD04

T2

ADSTB0S/FPD02

K2

ADSTB1F/FPD12

K1

ADSTB1S/FPDET

D2

SBA0#/DVP1VS

D3

SBA1#/DVP1DE

E3

SBA2#/DVP1D00

D1

SBA3#/DVP1HS

G3

SBA4#/DVP1D05

F1

SBA5#/DVP1D03

G1

SBA6#/DVP1CLK

G2

SBA7#/DVP1CLK_N

E1

SBSTBF/DVP1D01

E2

SBSTBS/DVP1D02

N5

GFRAME/FPHS

P5

GIRDY/SB_CK

R5

GTRDY

U5

GSTOP/FPDVICLK_N

N4

GDEVSEL/FPVS

U4

GPAR/FPDVIVS

E4

GGNT/DVI_DDCDA

F5

GREQ/DVI_DDCCK

G5

ST0

F3

ST1/DVP1DET

J5

ST2

J4

DBIL

K5

DBIH/PIPE#

L5

WBF/FPCLK_N

K4

RBF

V5

GCLK

C1

AGPCOMP

M6

AGPVREF0

H6

AGPVREF1

G6

AGP8XDET#

R4

GSERR/FPDVIDE

VSS43

VSS44

F2J2M2R2V2F4M4V4J9

VSS45

VSS46

VSS47

VSS48

B1C2R9

VCCQQ

AGP I/F

VSS55

VSS56

L12

L13

L14

Y6T9U9

VCC2_1

VCC2_2

VSS57

VSS58

L15

L16

AA6

AA8

VDD28

VCC2_4

VCC2_3

VSS59

VSS60

VSS61

M11

M12

K6L6V6W6AA11

AA9

VDD30

VDD31

VDD32

VDD29

VSS62

VSS63

VSS64

VSS65

M13

M14

M15

M16

AA12

AA19

AA20F8F9

F16

F18

H21

J21

AA16

AA17

AA14

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD45

VDD46

VDD44

VLINK I/F

CRT I/F

TFT FLAT PANEL / EXTERNAL

TV ENCODER I/F

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

N11

N12

N13

N14

N15

N16

P11

P12

P13

P14

P15

P16

R11

R12

VSS80

R13

+3VVDDQ +2.5V

VSS81

R14

J10

VCC5_1

VSS82

R15

J11

J12

AD3

VCC5_2

VCC5_3

VSUS25

TVCLKIN/DVP0DET

VSS83

VSS84

VSS85

VSS86

R16

T11

T12

T13

C4

C3

B4

A4

VCCDAC

VCCRGB

PLLVDD1

PLLVDD2

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VD7

VBE

UPCMD

UPSTB

UPSTB#

DNCMD

DNSTB

DNSTB#

LCOMPP

LVREF

INTA#

RSET

HSYNC

VSYNC

SPCLK2

SPD2

TVD00/DVP0D00

TVD01/DVP0D01

TVD02/DVP0D02

TVD03/DVP0D03

TVD04/DVP0D04

TVD05/DVP0D05

TVD06/DVP0D06

TVD07/DVP0D07

TVD08/DVP0D08

TVD09/DVP0D09

TVD10/DVP0D10

TVD11/DVP0D11

TVVS/DVP0VS

TVHS/DVP0HS

TVCLK/DVP0DCLK