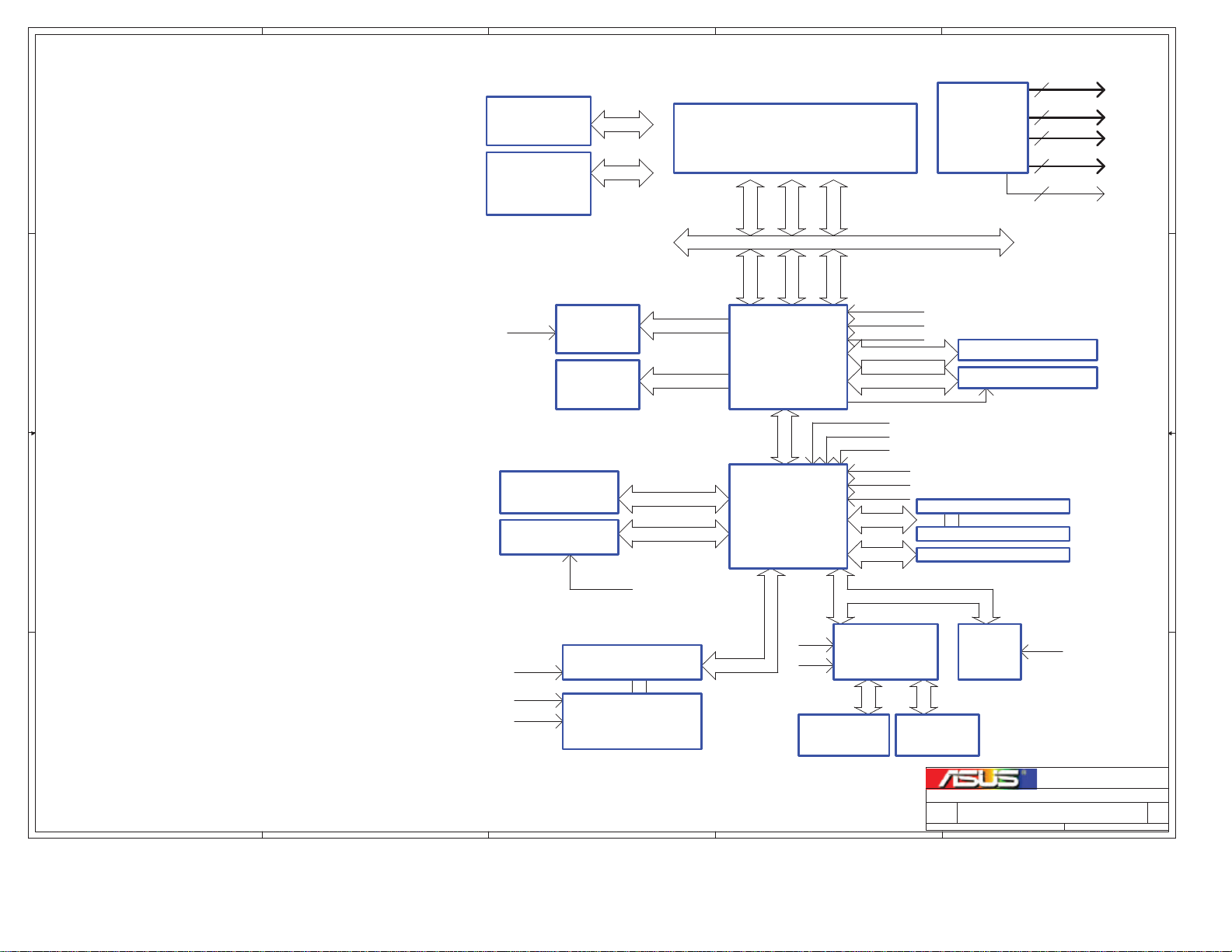

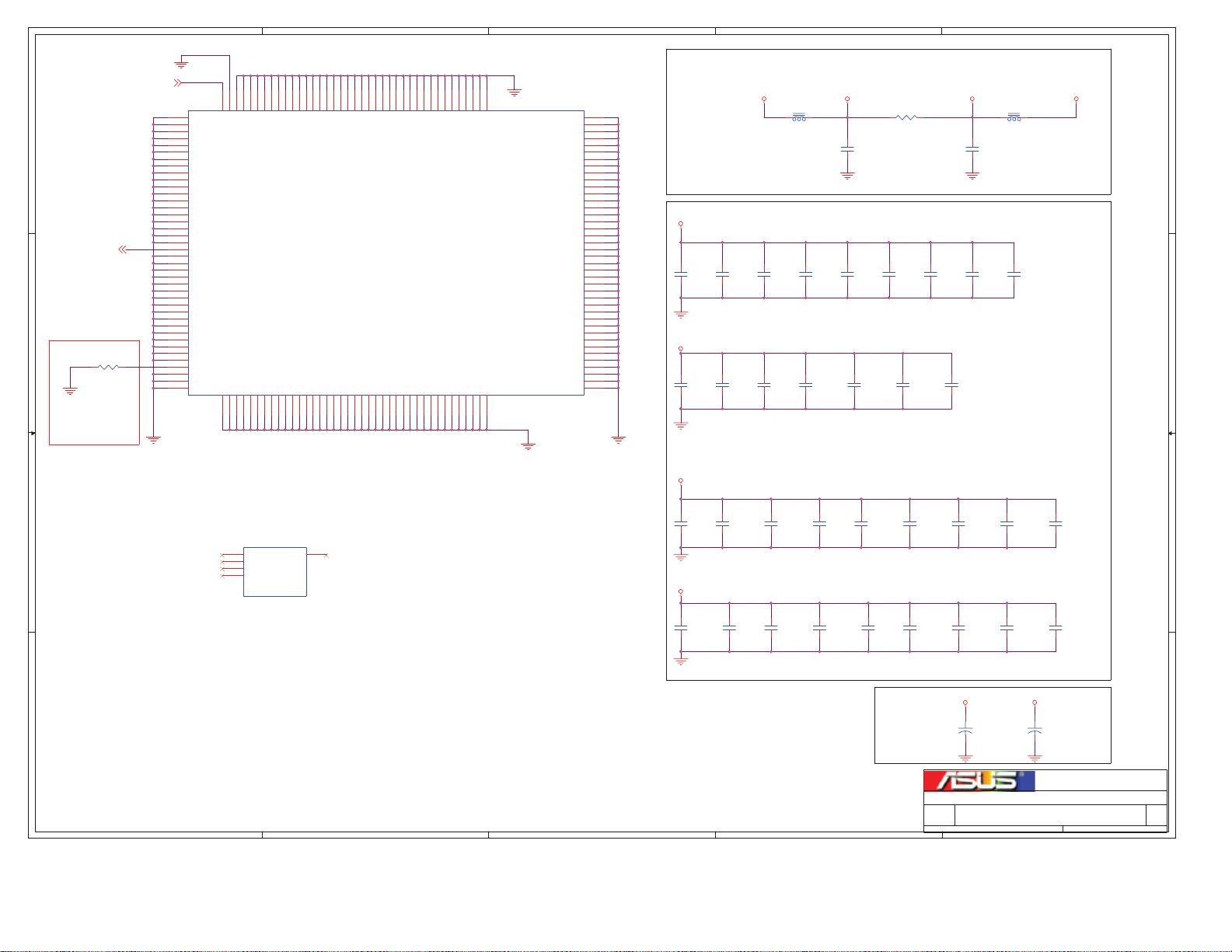

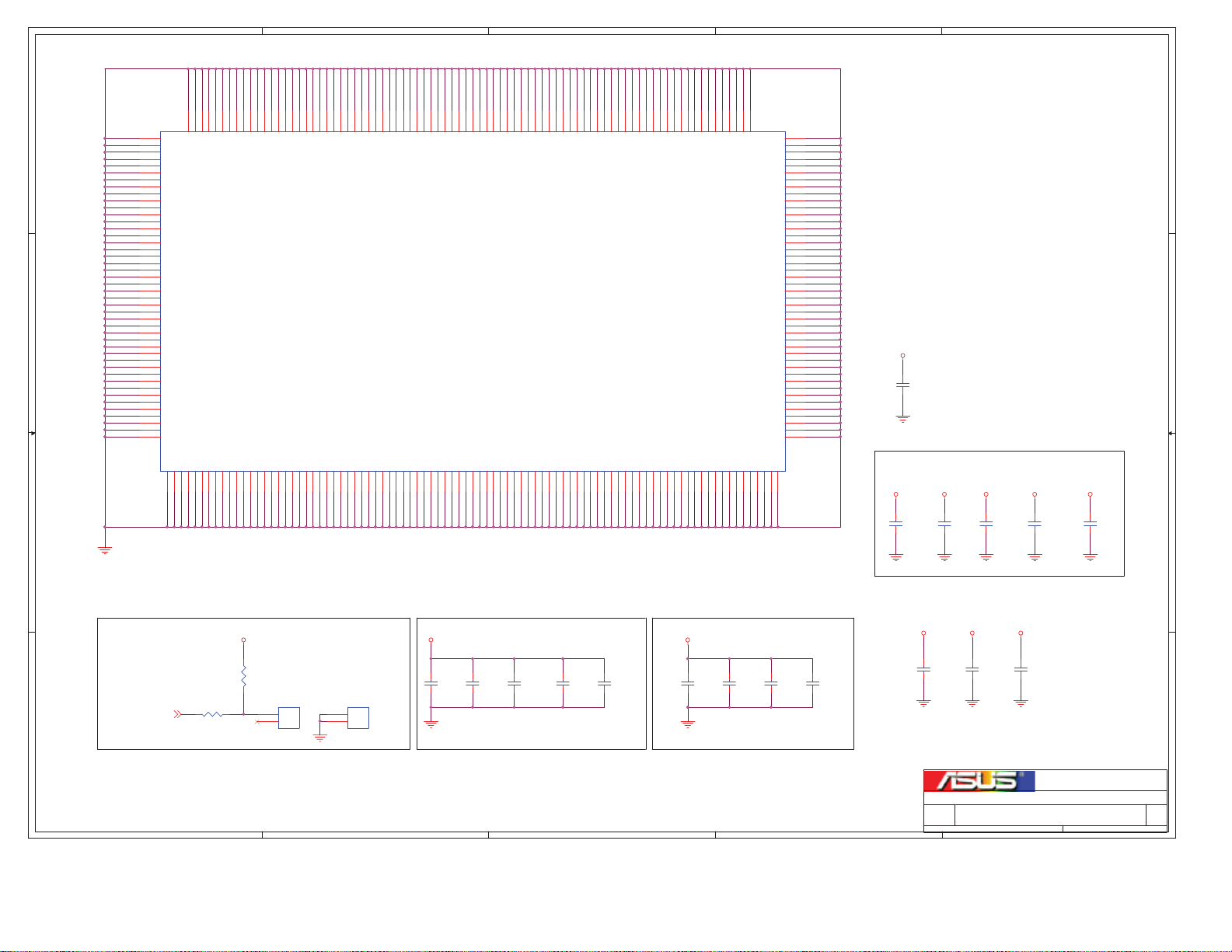

Desktop Motherboard 2-X02 Schematics

5

4

3

2

1

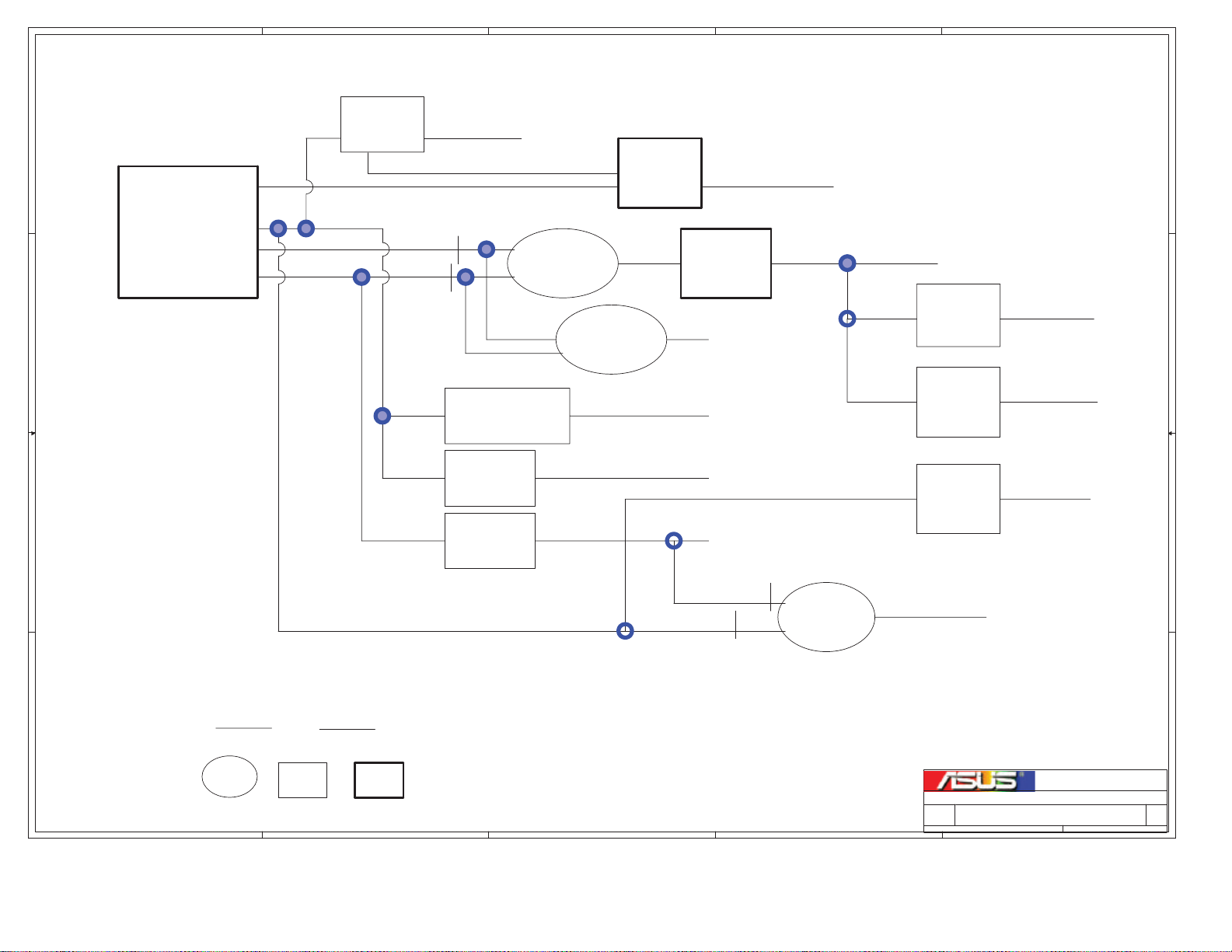

Phoenix 2 Project

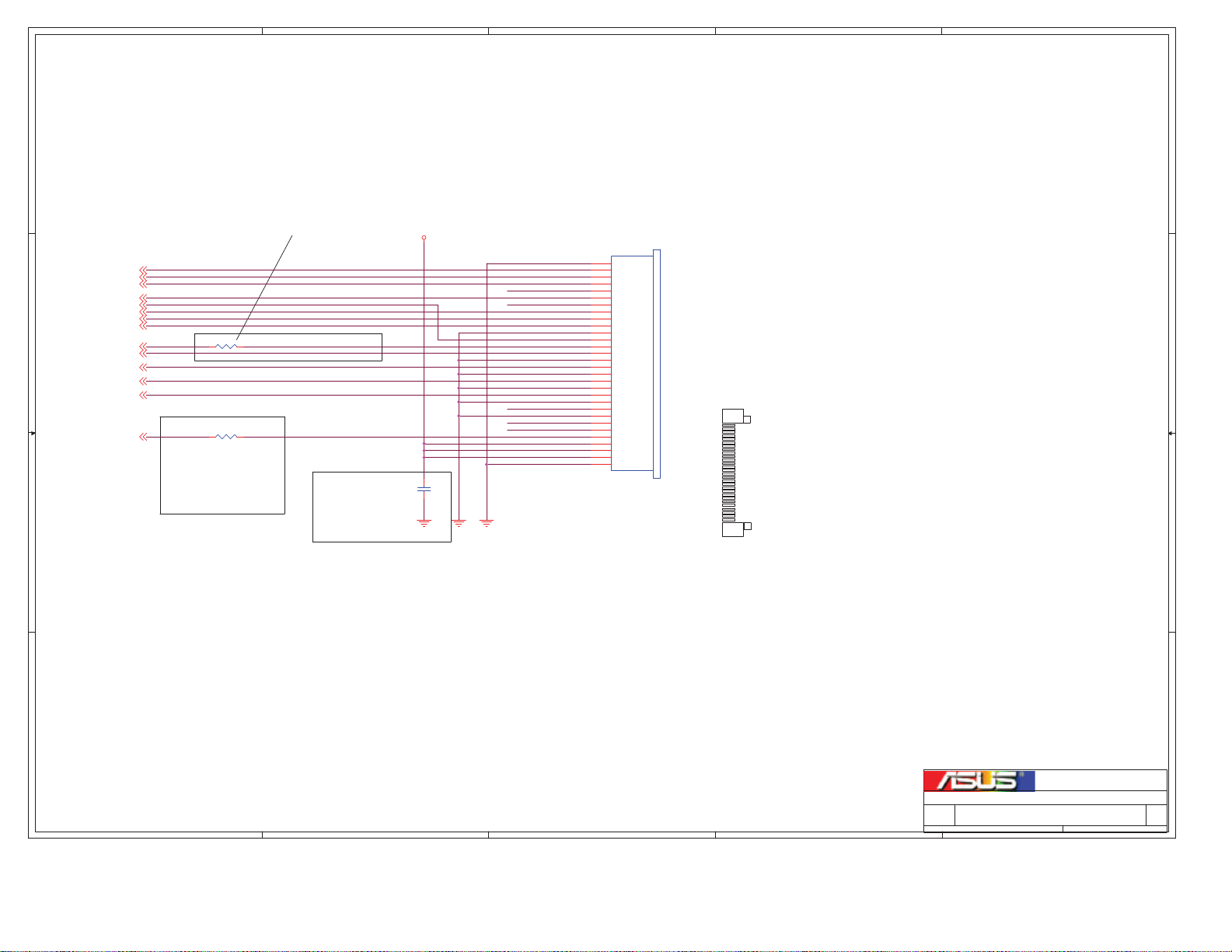

CLOCK

Rev.X02-00(3/18/2003)-In progress

D D

Page : 49

Intel Pentium 4 processor /VRM on Board

Northwood/Prescott

478 Pin Package

1.5V &

STANDBY

Page 1. COVER

Page 2. CLOCK DISTRIBUTION

Page 3. RESET MAP

Page 4. POWER DISTRIBUTION

Page 5. POWER FLOW

Page 6. POWER SEQUENCE

Page 7. CLOCK

C C

Page 8. P4-478 CPU-1

Page 9. P4-478 CPU-2

Page 10. P4-478 CPU-ITP

Page 11. Springdal -1

Page 12. Springdal -2

Page 13. Springdal -3

Page 14. Springdal -4

Page 15. Springdal -5

Page 16. DDR SOCKET A0

Page 17. DDR_TERMINATION

B B

Page 18. DDR SOCKET B0

Page 19. DDR_TERMINATION

Page 20. AGP 8X

Page 21. ICH5-1

Page 22. ICH5-2

Page 23. IDE

Page 24. USB 2.0 PORT

Page 31. POWER GOOD & RESET

Page 32. POWER CONNECTOR

Page 33. SMsC LPC IO

Page 34. FLOPPY

Page 35. KB, MOUSE

Page 36. PARALLE PORT

Page 37. SERIAL PORT

Page 38. VGA PORT

Page 39. SMBUS

Page 40. AC97 CODEC

Page 41. AC97 DEBOUNCE

Page 42. AC97 AMP & CONN

Page 43. AC97 CONN

Page 44. BATTERY

Page 45. EMI

Page 46. OTHER

Page 47. 2.5VSTBY & 1.5V & 1.25V

Page 48. DUAL POWER & VCCVID

Page 49. VRM10 CPU VCORE

Page 50. VTT_GMCH & GMCH_VDAC

Page 51. LED CONTROL

Page 52. PCB Stackup

Page 25. PCI SLOT

Page 26. BCM 4401 NIC

A A

Page 27. RJ45 + USB

Page 28. DELL D-LED

http://laptop-motherboard-schematic.blogspot.com/

REGULATOR

Page : 47,48,50

66MHz

High-Spee d U S B

AD1980 AC'97 CODEC

Page : 40,41,42,43

33MHz

25MHz

33MHz

VGA Conn

AGP 8X

SLOT

8 ports

Page : 24,27,29

350Mpixels/s

Page : 38

Page : 20

480Mb/s

AC'97 LINK

14.318MHz

PCI CONN

Broadcom 4401

10/100Mbit NIC

Page : 25

RJ45 port

Page : 26,27

ADDR

CNTL

CNTL

ADDR

Springdale-G

GMCH

932 FC-BGA

A0 -> A1 -> A2

Page : 11,12,13,14,15

HUB LINK

ICH5

460 mBGA

A0 -> A1 -> A2

Page : 21,22

48MHz

PCI BUS

33MHz

LPT / COM1 / FDD

Page : 34,36,37 Page : 35

DATA

HOST BUS

DATA

133/166/200MHz

66MHz

48MHz

Channel 1

Channel 2

266/333/400MHz

33MHz

48MHz

100MHz

14.318MHz

66MHz

32.768KHz

IDE BUS

Serial ATA

LPC BUS

SMsC 47M102

LPC Super I/O

B -> C

Page : 33 Page : 30

Keyboard/Mouse

MISC HEADER

Page 29. FRONT PANEL

Page 30. FWH

5

4

3

2

CK-409

ICS952621

AF -> BF -> CF

Page : 7Page : 8,9,10

DDR #1

DDR #2

PRIMARY IDE

SECONDARY IDE

SATA 1

FWH

82802AB

32 PLCC

<Core Design>

ASUStek Computer Inc.

Size Project Name

A3

Phoenix 2

Date: Sheet

66MHZ

100/133/200MHz

33MHz

14.318MHz

48MHz

Page : 16,17

Page : 18,19

Page : 23

Page : 23

Page : 23

33MHz

Title :

Engineer:

BLOCK DIAGRAM

1

Jason Lin

152Tuesday, March 18, 2003

of

Rev

X01

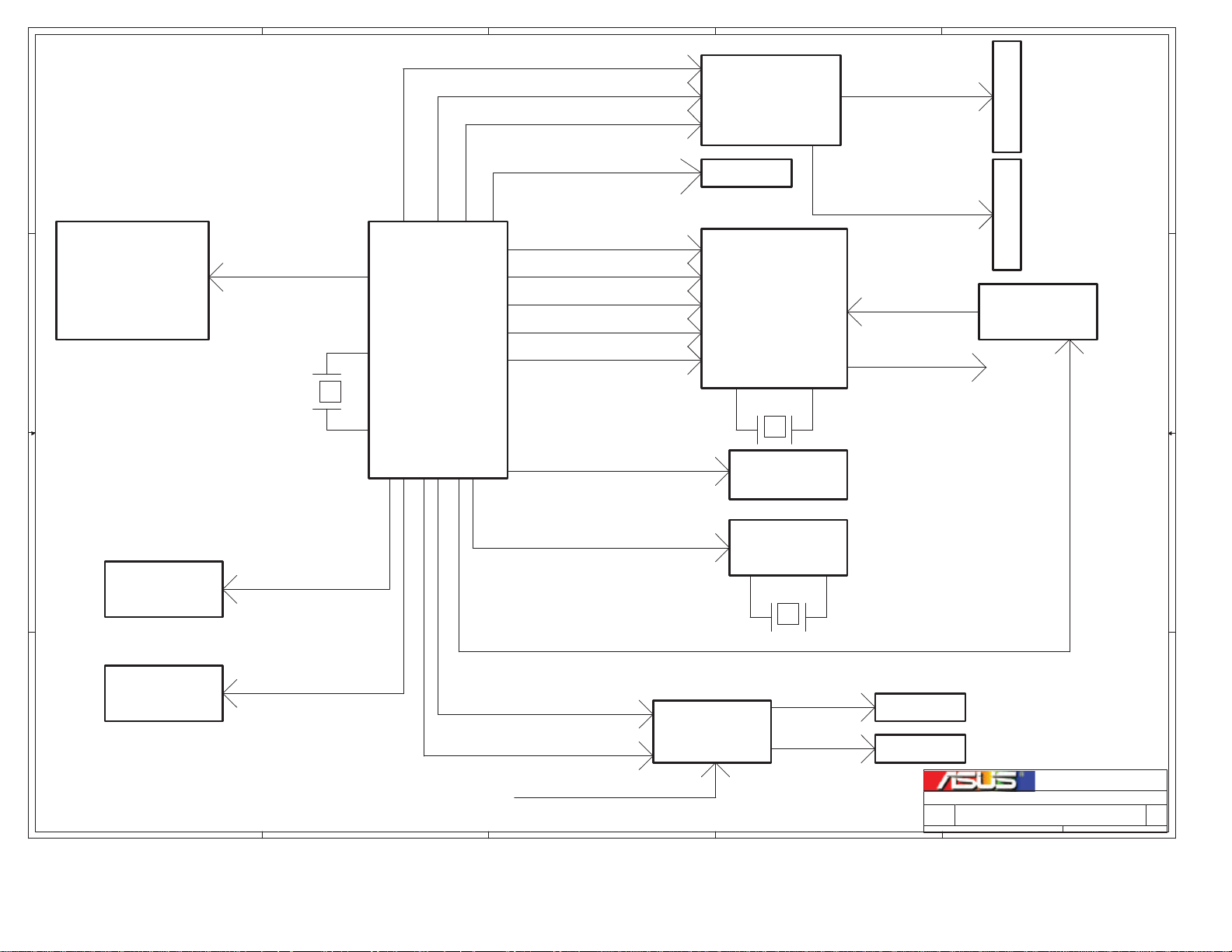

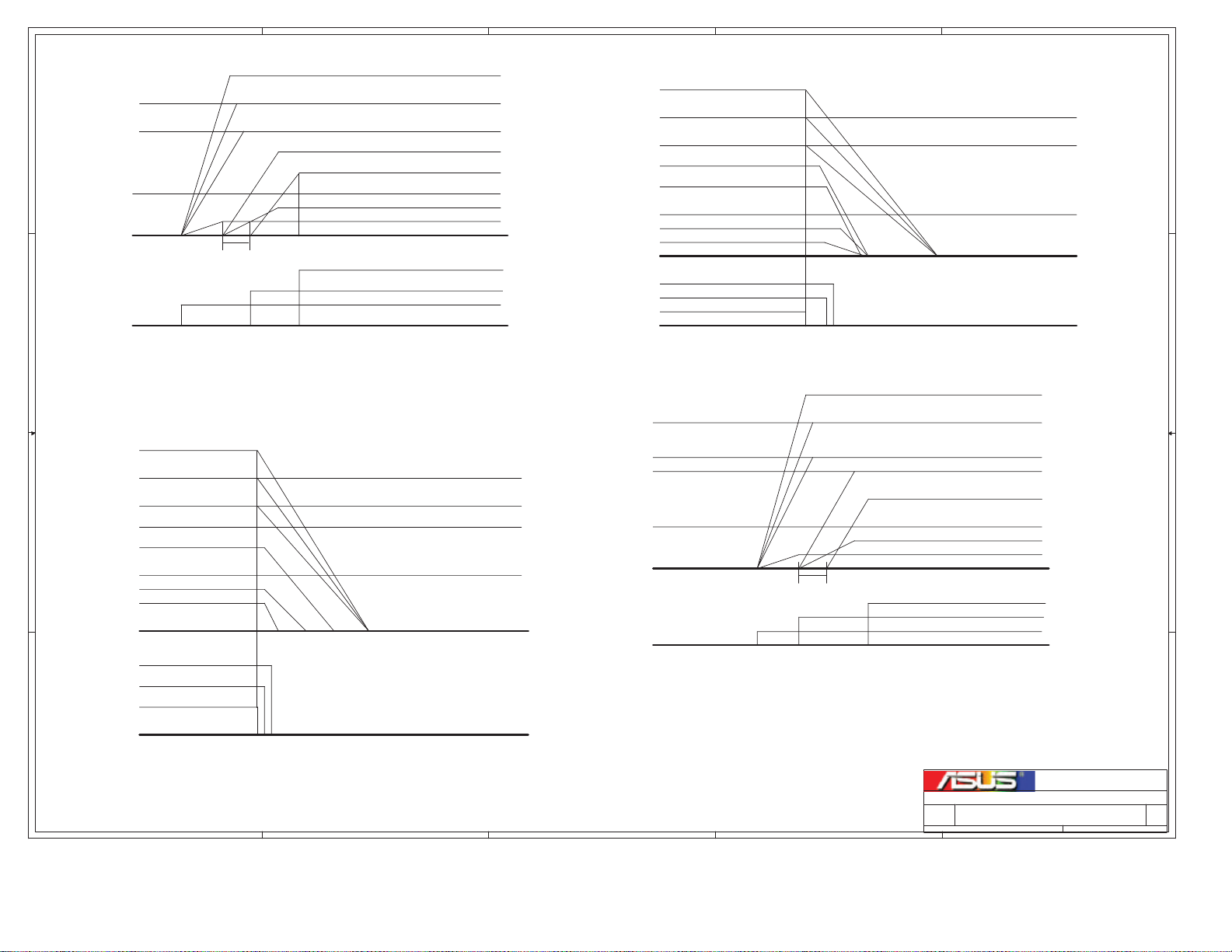

5

4

3

2

1

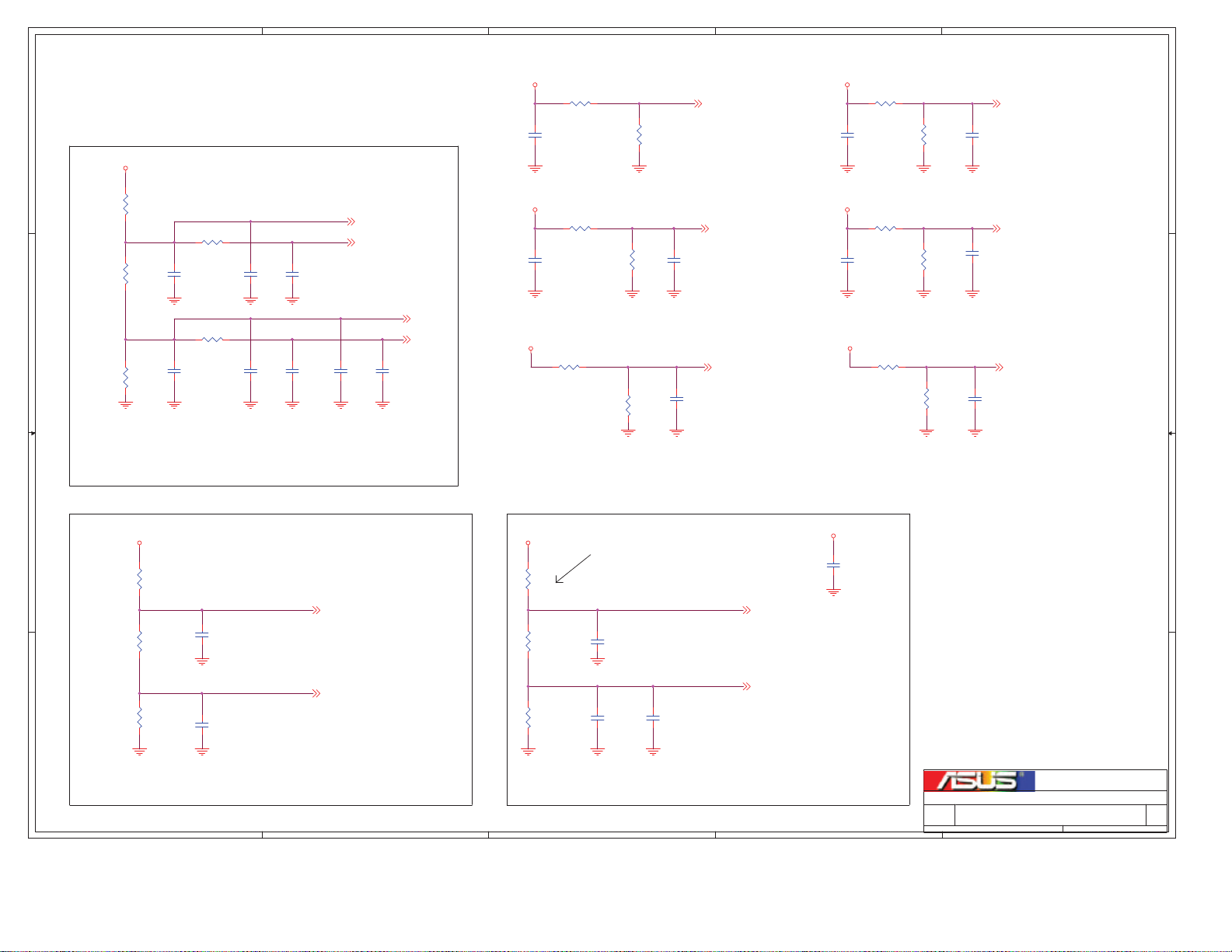

MCHHCLK/#

100/133/200MHz

Intel

CK66M_MCH

CK48M_VGA

D D

CK66M_AGP

P4 Processor

Northwood

&

Prescott

478 Pin Package

C C

CPUHCLK/#

100/133/200 MHz

14.318MHz

CLOCK CHIP

CK409

ICS952621

AF -> BF -> CF

48PIN

ICH_100M/# 100MHz

PCICLK_ICH

CK66M_ICH

CK48M_ICH 48MHz

PCICLK_SL1 33MHz

14.318MHzCK14M_ICH

66MHz

48MHz

66MHz

33MHz

66MHz

Springdale-G

GMCH

AGP SLOT

Intel

ICH5

32.768KHz

PCI1 Slot

M_CHA_SCK[0..2]/#

M_CHB_SCK[0..2]/#

BITCLK

12.288MHz

SUSCLK

32.768KHz

DDR-A0

DDR-B0

AC'97

Codec

To LPC IO

B B

PCICLK_LAN 33MHz

BROADCOM

BCM4401

FWH

ITP

PCICLK_FWH

CPUITPHCLK/#

100/133/167/200 MHz

A A

5

33MHz

25MHz

http://laptop-motherboard-schematic.blogspot.com/

14.318MHzCK14M_IO

SMSC I/O

PCICLK_IO 33MHz

From ICH5

4

SUSCLK 32.768KHz

3

KB_CLK

MSE_CLK

EXT_AUD_IN 14.318MHz

Keyboard

Mouse

ASUSTeK COMPUTER INC

Size Project Name

A3

2

Date: Sheet

Phoenix 2

Title :

Engineer:

1

CLOCK DISTRIBUTION

Jason Lin

252Tuesday, March 18, 2003

of

Rev

X01

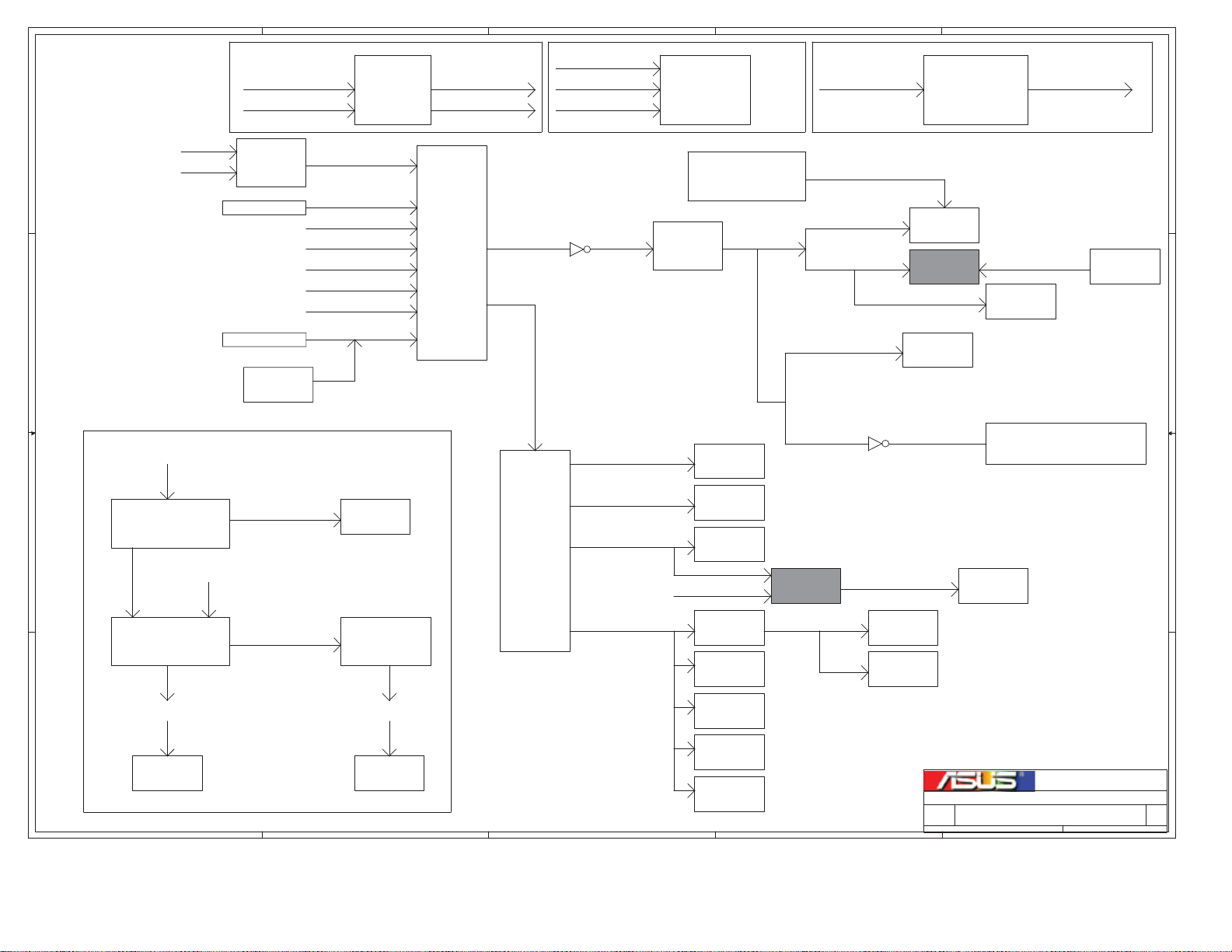

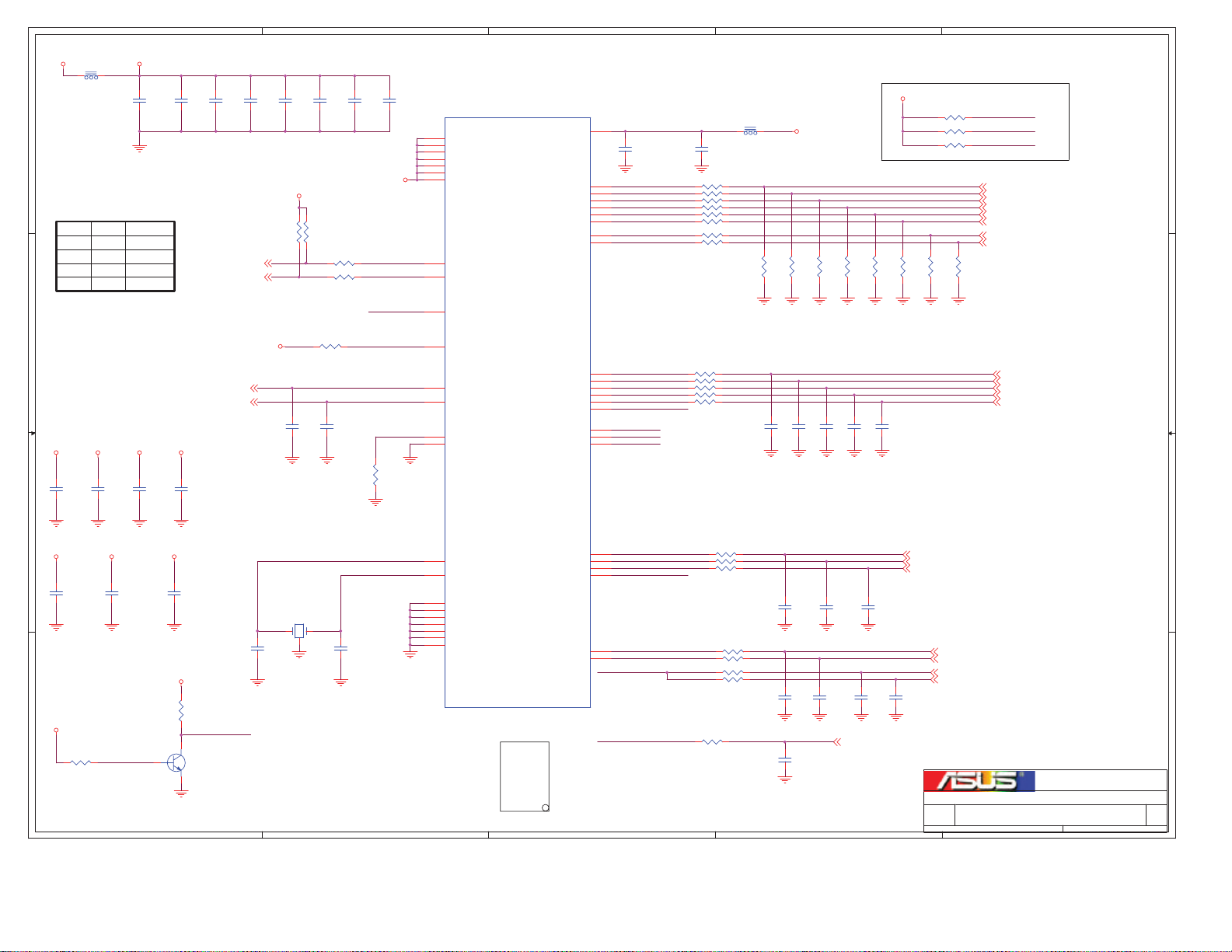

5

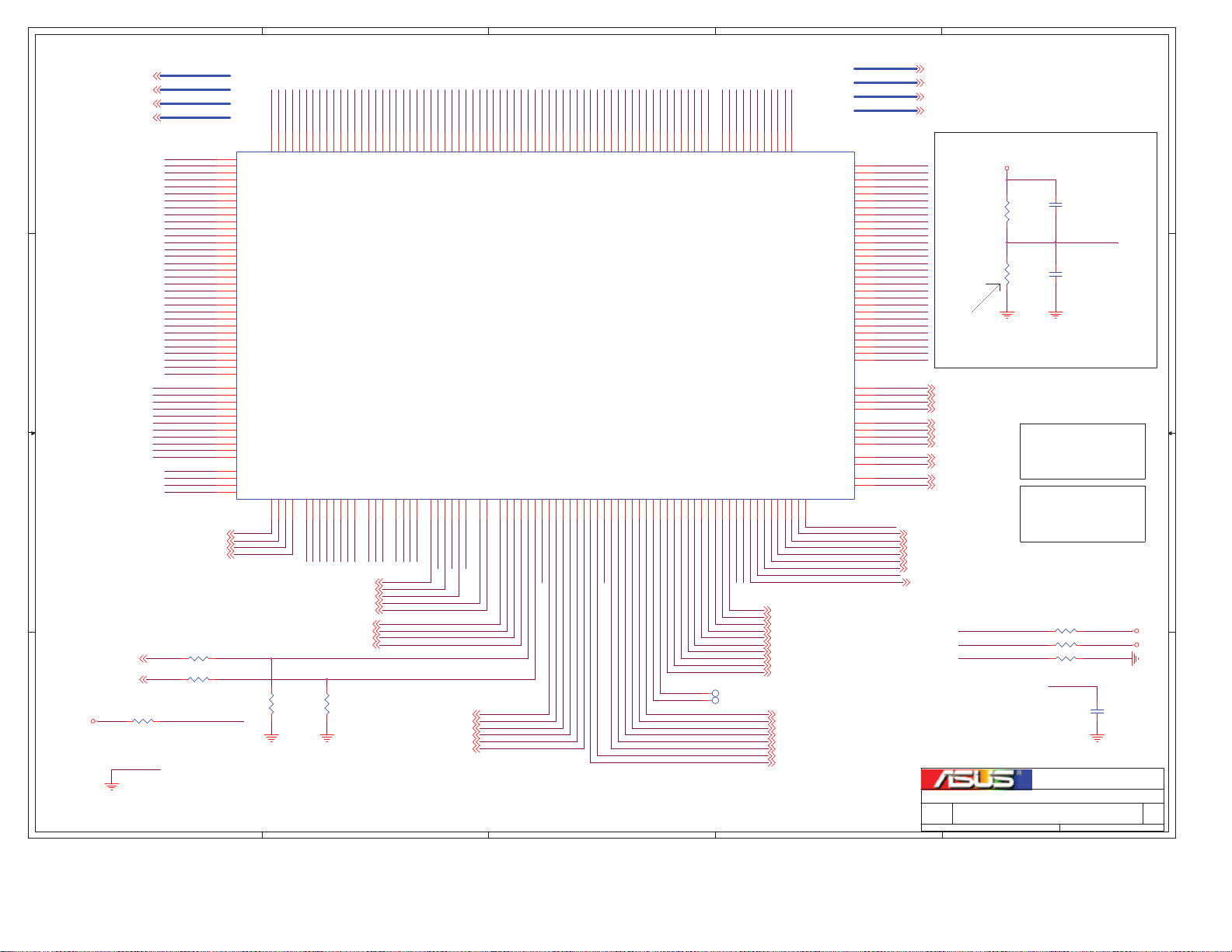

System Reset

D D

RI# Event# (S0/S1)

KB/MS Event (S0/S1/S3)

AGP , PCI1 , BCM4401

C C

3P3V_PWRGOOD CPURST#

PCI_RST_SYS#

LPC IO

PWR BTN#

RST BTN#

PWUREQ#

ICH_PWR_BTN#

RTCRST#

PME#

ICH_RSMRST#

ICH_PWROK

VRM_PWRGD (Option)

SYSTEM_RESET#

4

GMCH

ICH_SYNC#

ICH5

RTC Event#

USB Event#

ICH_SLP_S3#

3

VIDPWRGD

CPURST# CPURST#

H_DBR#

PWR_PS_ON#

CPU ITP

VCCVID

Power CKT

POWER

SUPPLY

PWRGOOD

2

VIDPWRGD

H_DBR#

SYSTEM_PWRGOOD

3P3V_PWRGOOD

Option

ICH_PWROK

GMCH

CPU

ICH_SYNC#

ICH5

1

SYSTEM_RESET#

GMCH

ITP

ICH_PCIRST#

3P3V_PWRGOOD#

+3.3V

VCCVID

B B

Power CKT

VIDPWRGD

EN

VRM 10.0

Power CKT

+12V

VCCVID

VRM_PWRGD

CPU

GMCH_VTT

Power CKT

RESET

BUFFER

IDE_PRST#

IDE_SRST#

PCI_RST_SLOT#

From ICH5

IDE1

IDE2

PCI1

GPIO_LAN_DISABLE

LPC IO

http://laptop-motherboard-schematic.blogspot.com/

Enable

Gate

CPURST#PCI_RST_SYS#

BCMRST#

CPUGMCH

ITP

SMBus Isolation

BCM4401

VCORE

A A

GMCH_VTT

AGP

D-LED

CPU GMCH

5

4

FWH

3

2

ASUSTeK COMPUTER INC

Size Project Name

A3

Date: Sheet

Phoenix 2

Title :

Engineer:

1

RESET MAP

Jason Lin

352Tuesday, March 18, 2003

Rev

X01

of

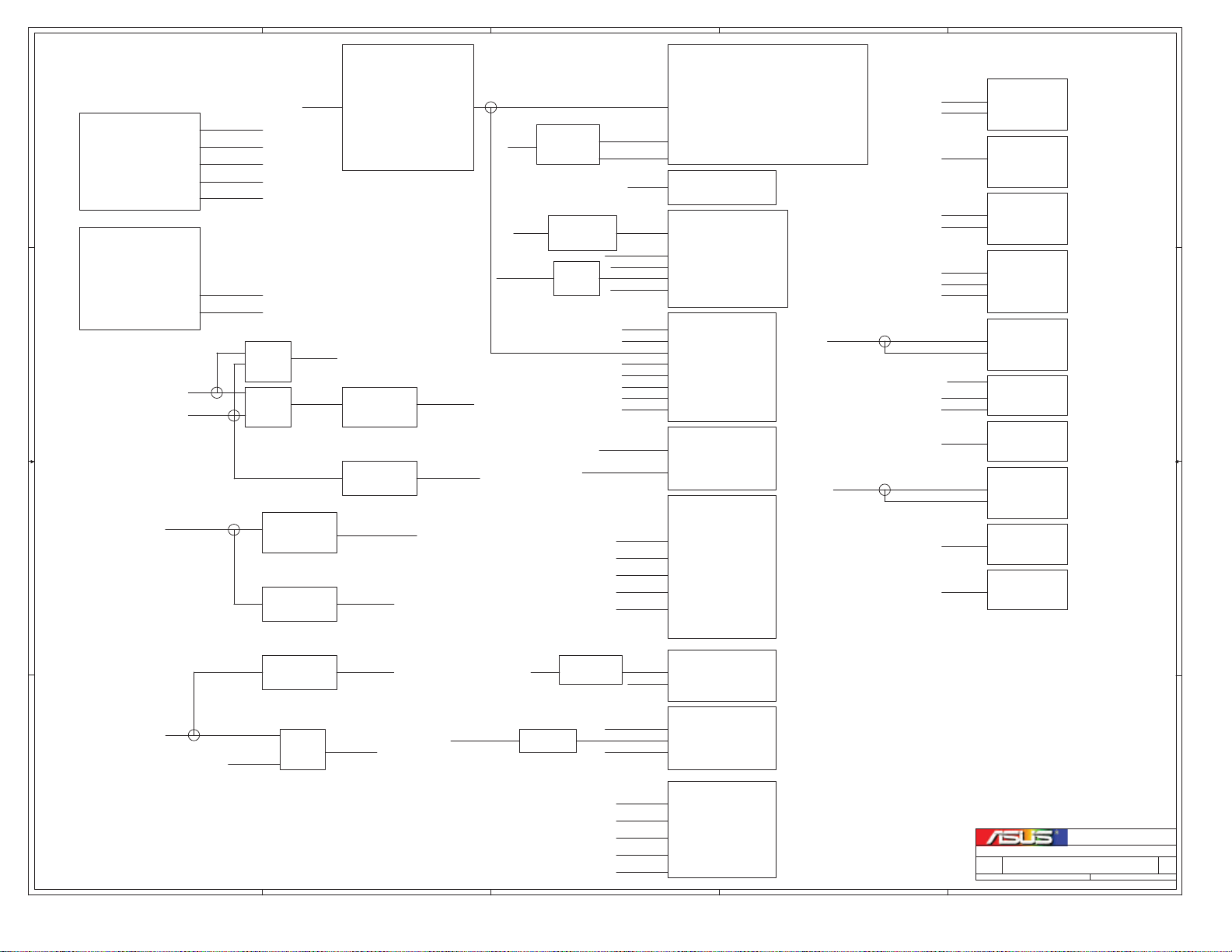

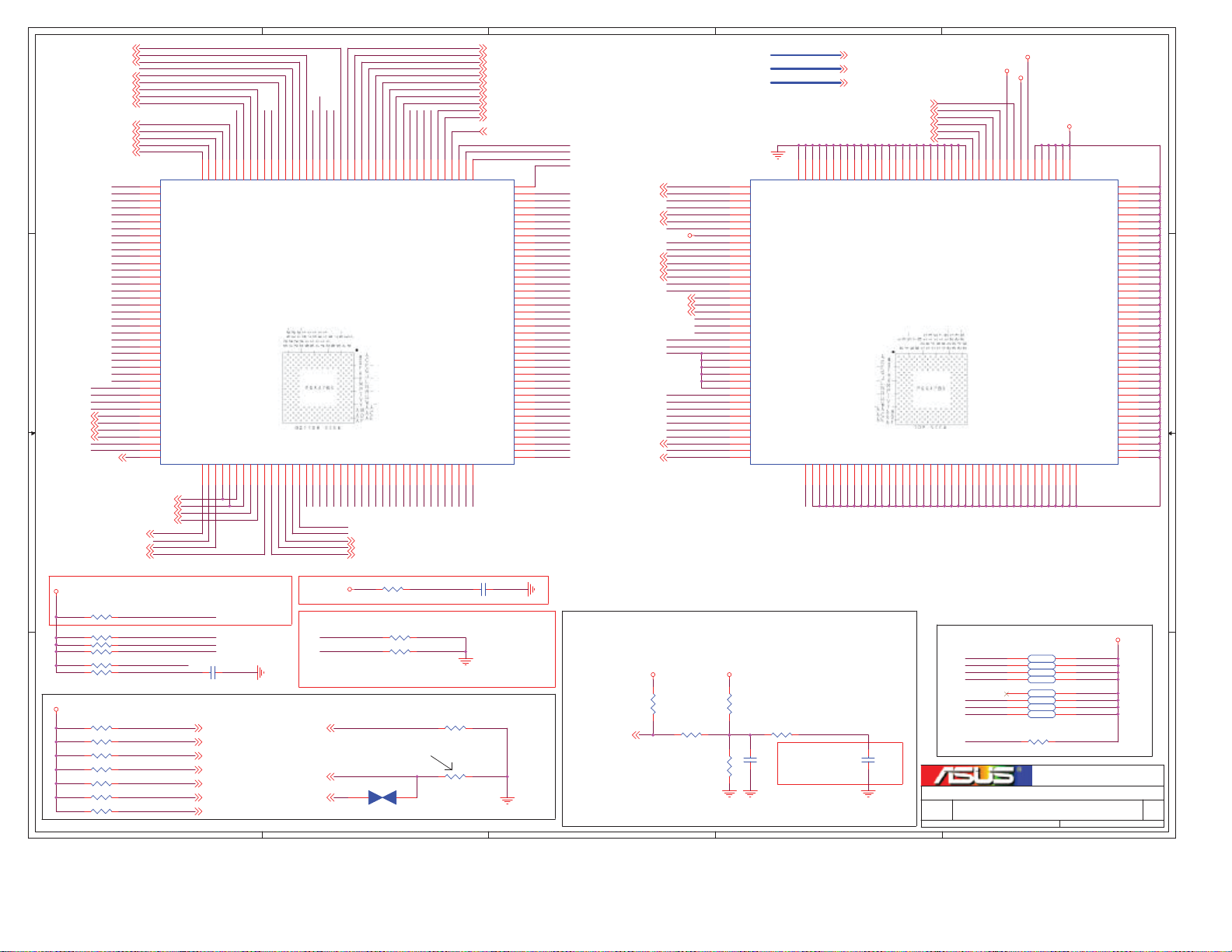

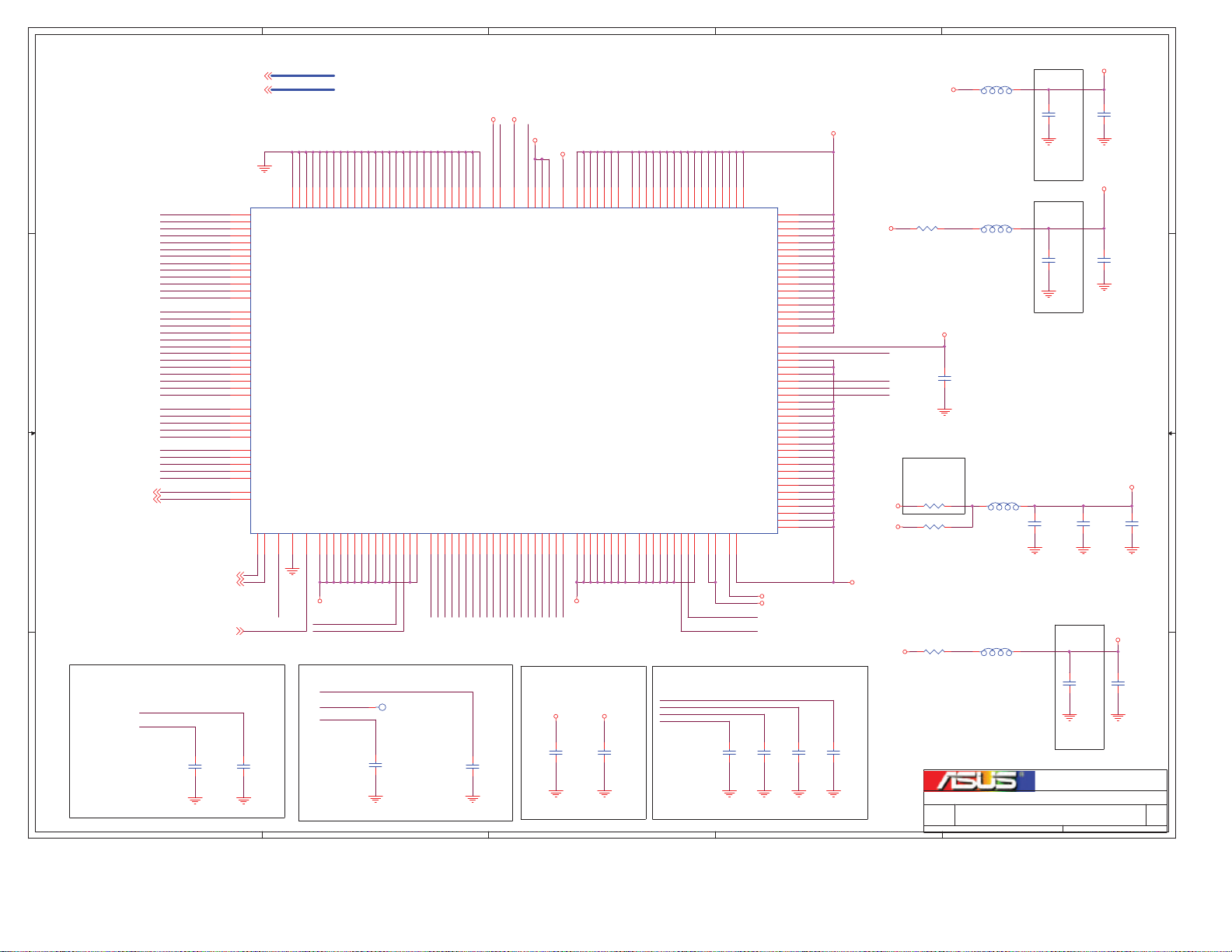

5

4

3

2

1

VRD 10.0 ON BOARD

PRESCOTT FMB1

ICC, sustained=78A ICC,Max=78A

+12V

VRD 9.0 ON BOARD

POWER

D D

SUPPLY

+5V_AUX

11A Max.

+12V

11A Max.

+5V

9A Max.

+3.3V

2A Max.

0.5A Max.

-12V

+5V and +3.3V load sharing will not be greater than 85W

NORTHWOOD FMB2

ICC,peak.=90A

ICC, sustained=70A

82% Efficient

S0,S1

3.0 Volt

BATTERY

CR2032

220 mAh

20mA Max

C C

ICH_VBAT

VBAT

0.25uA 0.75uW

5uA 15uW

MOSFET

+5V_DUAL_USB

CPUCORE

+3.3V

GMCH_VDAC

+3.3V

ON BOARD

LINEAR REG.

ON BOARD

LINEAR REG.

FILTER

+1.2V(VCCVID)

VIDPWRGD

GMCH_VTT

+2.5V_DUAL

+1.5V(VDAC)

ICH_1.5V

ON/OFF

+5V

+5V_AUX

MOSFET

ON/OFF

ON BOARD

SWITCHING REG.

+2.5V_DUAL+5V_DUAL

ICH_VBAT

+3.3V_AUX

+2.5V_DUAL

ON BOARD

LINEAR REG.

+2.5V_DUAL

B B

ON BOARD

LINEAR REG.

ON BOARD

+1.25V(VTT_DDR)

+1.5V

+3.3V_SB

+1.25V(VTT_DDR)

+1.5V

+3.3V_AUX

LINEAR REG.

http://laptop-motherboard-schematic.blogspot.com/

ON BOARD

ICH_1.5V

LINEAR REG.

+3.3V

+3.3V_SB

A A

5

MOSFET

ON/OFF

+3.3V_AUX

4

+3.3V_AUX

+12V

MOSFET

ON BOARD

LINEAR REG.

(+1.8VSB_LAN)

+1.2VSB_LAN

+3VSB_LAN

+2.5VSB_LAN

(+3.3VSB_LAN)

3

+3.3V_AUX

PRESCOTT FMB1

VID,max.=1.35 V , TDP=84W

NORTHWOOD

VCORE

VID,max.=1.55 V , I CC,peak. = 9 0 A , TDP=82W

ICC,Max=70A

S0,S1

FMB2

0.15Amax, 0.18W

+3.3V

+1.5V

+3.3V

+3.3V

VCORE +5V_AUX

+5V

+5V_AUX

+1.5VSB

CLOCK

0.28A 0.9W

S0,S1

Springdale

1.6A 2.32W for Northwood

1.6A 1.96W for Prescott

4.65A 7W

4.9A 12.25W

60mA 90mW

200mA 0.66W

S0,S1,S3,S5

ICH5

990mA 1.485W

480mA 1.584W

2.5mA 3.25mW

5uA 25uW

10uA 50uW

5uA 15uW 1 SERIAL

289mA 953mW

S0,S1,S3,S5

+5V_DUAL

+5V

+12V

+5V

+5V

+12V

+3V

+3.3V_AUX

V_BAT

+5V

-12V

+12V

+5V

DDR

6A 15W

S0,S1,S3

1.8A 2.25W

S0,S1

+5V_DUAL_USB

+5V_AUX

AGP 8X Connector

+3.3V

+12V

+3.3V

+5V

+12V

+3.3V

+5V

1.0A 1.5W

0.75A 2.475W

6A 19.8W

2A 10W

1A 12W

S0,S1

AUDIO

48mA 240mW

20mA 66mW

S0,S1

BROANDCOM NIC

0.2A 0.8W

0.33A 1.0W

S0,S1,S3,S5

+3.3V

+5V

+12V

-12V

PCI/SLOT/RISER

7.6A 25W

5A 25W

0.5A 6W

0.1A 1.2W

Refer to PCI 2.3 spec.

0.375A 1.24W

2

HDD 36G

0.7A 3.5W

0.7A 8.4W

S0

CD ROM

( Slim Type )

0.7A 3.5W

S0

FLOPPY

475mA 2.8W

0.25A 3W

S0

SUPER I/O

50mA 165mW

25mA 83mW

250nA 750nW

S0,S1,S3,S5

PS2 KB/M

0.1A 0.5W

0.04A 0.2Waux

S0,S1,S3

2mA 20mW

100uA 500uW

PARALLEL

+5V

15mA 74mW

S0,S1

USB 8 PORT

+5V

4A 20W

0.32A 1.6W

S0,S1,S3

FWH

67mA 220mW

S0,S1

FAN / ea

0.5A 6W

S0,S1

ASUSTeK COMPUTER INC

Size Project Name

C

Date: Sheet

Engineer:

Phoenix 2

1

Title :

POWER DISTR IB U TI O N

Jason Lin

452Tuesday, March 18, 2003

of

Rev

X01

5

4

3

2

1

RT9181CB

Imax

D D

TBD

eff. 40%

PG

+12V

VCCVID

Idc=50mA

1~5ms delay

=1.2V

VCORE_EN

ADP3168

Iocp

133A

Imax

90A

eff.

82%

VCORE

Idc=Icc,Max*0.85=59.5A for Northwood

Idc=Icc,Max*0.85=66.3 A f o r P r escott

TO CPU

-12V

Silver Box

160W ?

C C

+3.3V

+5V

+5V_AUX

+5V

+5V_AUX

OP+BJT (Linear)

2A Idc=1.6A

Imax

for Northwood

44%

eff.

36% for Presscott

OP+BJT (Linear)

Imax=60mA

eff. 50%

B B

AME1085

Imax=1.5A

eff. 66%

eff. =97%

AP9918H(N-CH)

+

SI2305DS(P-CH)

(1P-CH + 1N-CH)

eff. =98%

AP4502

+5V_DUAL

Idc=9A

RT9202CS

Iocp

Imax

eff.

GMCH_VTT

GMCH_VDAC

Idc=48mA

~

= 25A

18.4A

85%

+5V_DUAL_USB

Idc=4A

TO GMCH

TO GMCH

+3.3V_SB

Idc=1.2A

+2.5V_DUAL

Idc=14A

TO DDR

RT9173ACL5

Iocp

3.0A

Imax 1.8A

OP+MOS(Linear)

Imax=5.7A

eff. =60%

LDO

Imax=0.9A

eff.=45%

VTT_DDR

Idc=1.44A

GMCH_1.5V

Idc=4.56A

To GMCH/AGP Connector

ICH_1.5V

Idc=0.72A

To ICH5

eff. =98%

+3V_AUX

Idc=3A

TO PCI , ICH5 , LAN

http://laptop-motherboard-schematic.blogspot.com/

+3.3V

+3.3V_SB

AP4502

(1N-CH+1P-CH)

Note:

1. Imax is mean to peak current refered to power

distribution on page 4.

2. Idc is mean to the sustain current , and is 80% of Imax

except Vcore is 85%.

A A

5

Power Rail

Switch

ON/OFF

Linear

Control Signal

Switching

4

current

3. Iocp is 1.5~2.0 times of Imax.

3

POWER FLOW

Title :

ASUSTeK COMPUTER INC

Size Project Name

A3

2

Date: Sheet

Phoenix 2

Engineer:

Jason Lin

552Tuesday, March 18, 2003

1

Rev

X01

of

5

4

3

2

1

S5->S0

+12V

S0->S5

+12V

+5V_AUX

+3.3V_SB

D D

+1.5VSB

+1.5V READY

0

1-5ms

0

C C

1.CPUCORE must rise after the voltage across 90% of +1.2V,andthe interval is within 1-5ms

2.VRD_OUTEN rises after the voltage across 90% of its specified value

+5V_DUAL

+3.3V_AUX

+1.5VSB

(BY +5V)

(BY +3.3V)

+2.5V_DUAL

CPUCORE

+1.5V

&

+1.25V

+1.2V

VRD_PWRGOOD

VRD_OUTEN

PS-ON

+5V_DUAL

+3.3V_AUX

(BY +5V)

(BY +3.3V)

+5V_AUX

+3.3V_SB

+2.5V_DUAL

CPUCORE

+1.5VSB

&

0

+1.25V

+1.2V

+1.5V

0

+1.5VSB

0

VRD_PWRGOOD

VRD_OUTEN

PS-OFF

0

0

0

S3->S0

+12V

S0->S3

+12V

+3.3V_AUX

(BY +5V)

(BY +3.3V) (BY +3.3V_SB)

+5V_DUAL

+3.3V_AUX

+5V_DUAL

+2.5V_DUAL

B B

CPUCORE

+1.5VSB

+1.5V&

(BY +5V_AUX)

+2.5V_DUAL

+1.5VSB

+5V_AUX

+3.3V_SB

+2.5V_DUAL

+1.5VSB

0

+5V_DAUL

+3.3V_AUX

(BY +5V)

(BY +3.3V)

+2.5V_DUAL

+1.5VSB

CPUCORE

+1.5V

&

+1.25V

+1.2V

0

+1.25V

+1.2V

1-5ms VRD_PWRGOOD

VRD_OUTEN

0

0

0

PS-ON

0

VRD_PWRGOOD

VRD_OUTEN

PS-OFF

1.CPUCORE must rise after the voltage across 90% of +1.2V,andthe interval is within 1-5ms

2.VRD_OUTEN rises after the voltage across 90% of its specified value

A A

S0:

S3:

S5:

0

Windows Running

Windows Standby

AC Power On Only

5

+12V,+5V_DUAL,+5V_AUX,+3.3V_SB+3.3V,+3.3V_AUX,+2.5V_DUAL,CPUCORE,+1.5V,+1.5VSB,+1.25V,+1.2V existed

+5V_DUAL,+5V_AUX,+3.3V_SB,+3.3V_AUX,+1.5VSB,+2.5V_DUAL existed

+5V_AUX,+3.3V_SB,+1.5VSB existed

4

0

POWER SEQUENCE

Title :

ASUSTeK COMPUTER INC

Size Project Name

A3

3

2

Date: Sheet

Phoenix 2

Engineer:

Jason Lin

652Tuesday, March 18, 2003

1

Rev

X01

of

http://laptop-motherboard-schematic.blogspot.com/

5

4

3

2

1

+3.3V

L51

30OHM/100MHZ

D D

CLOCK TABLE

FS_B FS_A CPU

0

0

1

1

C C

+3.3V

12

EE2

0.1U

B B

+3.3V

12

CB296

0.1U

Y5V Y5V Y5V

NI

GND GND GND

VCORE

A A

R391

220

1 2

CLKVCC3

21

12

GND

100

0

133

1

200

0

167

1

+5V

+3.3V

12

12

EE1

0.1U

GND

GND

+3.3V +3.3V

12

CB277

0.1U

VTT_PWRGD

12

12

CB274

0.1U

12

CB42

0.1U

X7RX7R X7R

GNDGND

CB264

0.1U

R366

4.7K

VTT_PWRGD#

1 2

3

C

Q48

PMBS3904

E

2

GND

CB268

0.1U

SMBCLK_M<16,18,39>

SMBDATA_M<16,18,39>

Afetr check with ICS, For CK409 spec :

Max. External Cap = 2 x CL - Cs - Ci

For X'tal Vendor :

07-009021431 XTAL 14.318MHZ DIP 49US TXC 30PF/30PPM

,MARKING:TXC/14.3x8xF QVL:TXC,

CL= 30pf

For ICS95261BF, Ci = 7pf

For trace capacitance , Cs = 2.98pf

Max. External Cap = 2 x 30 - 2.98 - 7 = 50.02pf

47pf still meet sepc.

CB280

0.1U

X7R X7R X7R X7R X7R X7RX7R

+5V

CB282

0.1U

Y5V

12

CLKVCC3

B

1

5

HBSEL0<8,11>

HBSEL1<8,11>

CLKVCC3

12

GND

CB284

0.1U

12

C194

47P

12

CB275

0.1U

CLKVCC3

R343

R320

1K

1K

1 2

1 2

R317 10K

R336 10K

1 2

R380 8.2K

12

C210

47P

NI

GND GND

X2

14.31818MHZ

12

GND

3

GND

12

CB271

0.1U

12

C208

47P

NI

12

GND

12

12

CB265

CB285

0.1U

4.7U

0805,X5R

CLKVCC3

_CK14M_ICH

12

_EXT_AUD_IN

12

VTT_PWRGD#

PWRD#

SMBCLK_M

SMBDATA_M

R313

475

1%

1 2

GND

OSC_CK14M_XTALIN

OSC_CK14M_XTALOUT

C193

47P

NPONPO

4

U23

3

VDD_REF

10

VDD_PCI1

16

VDD_PCI2

27

VDD3V66

34

VDD_SRC

40

VDD_CPU

24

VDD_48

1

FS_A/REF_1

2

FS_B/REF_0

33

VTT_PWRGD#

20

RST#/PWRDWN#

31

SCLK

32

SDATA

IREF

46

IREF

47

VSS_A

GND

4

XIN

5

XOUT

28

VSS3V66

43

VSS_CPU

37

VSS_SRC

6

VSS_REF

11

VSS_PCI1

23

VSS_48

17

VSS_PCI2

GND

DESIGN NOTE: ICS 952621 / CYPRESS CY28405-2

BOM default is ICS952621

48

VDD_A

CPU_C0

CPU_T0

CPU_ITPC

CPU_ITPT

CPU_C1

CPU_T1

SRC_C

SRC_T

PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

FS_C/PCIF0

FS_D/PCIF1

FS_E/PCIF2

ICS952621

3V66_0

3V66_1

3V66_2/MODE

3V66_3/VCH

USB48

DOT48

2425

48 PIN

IC

1

R318

49.9

1%

1 2

NI

12

C209

10P

GND GND

1 2

CLKVCC3

R344

49.9

1%

12

C211

10P

48

38

39

44

45

41

42

35

36

12

13

14

15

18

19

7

8

9

+3V_CLK

12

CB262

0.1U

X7R

_MCHHCLK#

_MCHHCLK

_CPUITPHCLK#

_CPUITPHCLK

_CPUHCLK#

_CPUHCLK

_ICH_100M#

_ICH_100M

_PCICLK_ICH

_PCICLK_SL1

_PCICLK_LAN

_PCICLK_FWH

_PCICLK_IO

NC_U23_19

FS_C

FS_D

FS_E

L49

600OHM/200mA

0603

12

CB260

4.7U

0805,X5R

GNDGND

R354 33

1 2

R348 33

1 2

R329 33 NI

1 2

R322 33 NI

1 2

R340 33

1 2

R332 33

1 2

R364 33

1 2

R358 33

1 2

R360 33

1 2

R365 33

1 2

R372 33

1 2

R376 33

1 2

R377 33

1 2

+3.3V

21

R359

49.9

1%

1 2

GND GND GND GND GND GND GND GND

12

C203

10P

GND

R351

49.9

1%

1 2

12

C206

10P

GND GND

R324

49.9

1%

1 2

NI

12

C207

10P

http://laptop-motherboard-schematic.blogspot.com/

30

29

26

25

22

21

_CK14M_ICH

_EXT_AUD_IN

3

_CK66M_AGP

_CK66M_MCH

_CK66M_ICH

NC_U23_25

_CK48M_ICH

_CK48M_VGA

R379 33

1 2

R385 33

1 2

R383 33

1 2

R386 33

1 2

R381 33

1 2

R321 33

1 2

R316 33

1 2

R326 33

1 2

12

12

C215

10P

C214

5P

EXT_AUD_IN <40>

2

12

C217

10P

12

C198

10P

C212

10P

GND GND GND

12

12

C218

5P

GND GND GND GND

12

C49

10P

GND

R342 10KNI

R353 10KNI

R352 10KNI

R335

R367

49.9

49.9

1%

1%

1 2

1 2

CK66M_AGP <20>

CK66M_MCH <11>

CK66M_ICH <21>

CK48M_ICH <21>

CK48M_VGA <11>

CK14M_ICH <21>

CK14M_IO <33>

12

C196

10P

ASUSTeK COMPUTER INC

Size Project Name

A3

Date: Sheet

12

12

12

R361

49.9

1%

1 2

FS_C

FS_D

FS_E

MCHHCLK# <11>

MCHHCLK <11>

CPUITPHCLK# <10>

CPUITPHCLK <10>

CPUHCLK# <8>

CPUHCLK <8>

ICH_100M# <21>

ICH_100M <21>

PCICLK_ICH <21>

PCICLK_SL1 <25>

PCICLK_LAN <26>

PCICLK_FWH <30>

PCICLK_IO <33>

Phoenix 2

Title :

Engineer:

1

CLOCK409

Jason Lin

752Tuesday, March 18, 2003

of

Rev

X01

5

FERR#<21>

HIT#<11>

HITM#<11>

IGNNE#<21>

HINIT#<21,30>

INTR<21>

NMI<21>

HLOCK#<12>

PROCHOT#<12>

D D

C C

B B

A A

CPUPWROK<21>

HREQ0#<12>

HREQ1#<12>

HREQ2#<12>

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10 HD#57

HA#11

HA#12

HA#13

HA#14

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#28

HA#29

HA#30

HA#31

NC_XU1_V3

NC_XU1_W2

NC_XU1_Y1

NC_XU1_AB1

A20M#<21>

HADS#<11>

HADSTB0#<11>

HADSTB1#<11>

NC_XU1_AC1

NC_XU1_V5

CPUHCLK<7>

CPUHCLK#<7>

BNR#<11>

BPRI#<11>

VCORE

CAD NOTE: PLACE AT ICH END OF ROUTE

R347 62

1 2

R215 62

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

12

12

R236 121Ohm 1%

R235 200 1%

R183 301 1%

R233 62

VCORE

R212 62

R224 62

R222 62

R217 62

R203 52.3Ohm 1%

R198 150 1%

R210 39.2 1%

IERR#

NC_XU1_V6

NC_XU1_AD26

MCERR#

PWRGOOD

PROCHOT#

BPM#[0]

BPM#[1]

BPM#[2]

AB5

AC4Y6AA5

LINT1

LOCK#

BPM#[3]

BPM#[4]

AB4D2H6

NC_XU1_AC26

AC26W5B2

LINT0

ITP_CLK1

BPM#[5]

BPRI#

GND

J4K5J1

XU1A

K2

A#[03]

K4

A#[04]

L6

A#[05]

K1

A#[06]

L3

A#[07]

M6

A#[08]

L2

A#[09]

M3

A#[10]

M4

A#[11]

N1

A#[12]

M1

A#[13]

N2

A#[14]

N4

A#[15]

N5

A#[16]

T1

A#[17]

R2

A#[18]

P3

A#[19]

P4

A#[20]

R3

A#[21]

T2

A#[22]

U1

A#[23]

P6

A#[24]

U3

A#[25]

T4

A#[26]

V2

A#[27]

R6

A#[28]

W1

A#[29]

T5

A#[30]

U4

A#[31]

V3

A#[32]

W2

A#[33]

Y1

A#[34]

AB1

A#[35]

C6

A20M#

G1

ADS#

L5

ADSTB#[0]

R5

ADSTB#[1]

AC1

AP#[0]

V5

AP#[1]

AF22

BCLK[0]

P4_SOCKET478

BPM0_2#<10>

BPM1_3#<10>

BPM4#<10>

BPM5#<10>

NC_XU1_AA3

FERR#

IERR#

PROCHOT#

HBREQ0#

CPUPWROK TESTHI10

CPURST#

BPM0_2#

BPM1_3#

BPM4#

BPM5#

TDO

TDI

TMS

5

AB23C3V6G4E5D1AD26

REQ#[2]

REQ#[1]

REQ#[0]

BCLK[1]

BINIT#

BNR#

AF23

AA3G2AC6

1 2

C160 22P NI

BPM0_2# <10>

BPM1_3# <10>

BPM4# <10>

BPM5# <10>

TDO <10>

TDI <10>

TMS <10>

CPU_GTLREF

NC_XU1_F6

NC_XU1_AA6

AC3E3F3F6F20

AA6

HIT#

INIT#

IERR#

HITM#

IGNNE#

GTLREF4

ITP_CLK0

BR0#

GTLREF3

BSEL0

BSEL1

COMP[0]

COMP[1]

D#[0]

D#[01]

D#[02]

AD6

AD5

L24P1B21

B22

A23

A25

HD#3

HD#1

HD#2

HD#0

HCOMP1

HCOMP0

VCORE GND

CAD N OTE:PLACE THESE OUTSIDE CPU SOCKET CAVITY

HCOMP0

HCOMP1

TRST#<10>

TCK<10>

FBO<10>

4

NC_XU1_AA21

AA21B6W23

P23

J23

F21

W22

R22

FERR#

GTLREF2

GTLREF1

DSTBP#[3]

DSTBP#[2]

DSTBP#[1]

DSTBP#[0]

DSTBN#[3]

D#[03]

D#[04]

D#[05]

D#[06]

D#[07]

D#[08]

D#[09]

D#[10]

C21

D22

B24

C23

C24

B25

G22

H21

HD#7

HD#6

HD#5

HD#4

HD#8

HD#9

HD#11

HD#10

HBSEL1 <7,11>

HBSEL0 <7,11>

HBREQ0# <11>

1 2

R338 62

R231 61.9 1%

1 2

R234 61.9 1%

1 2

TRST#

BOM change from

27.4 to 24.9

TCK

JP2

FBO

1 2

SHORTPIN

NI

4

NC_XU1_K26

NC_XU1_K25

NC_XU1_L25

NC_XU1_J26

K22

E22H2L25

K26

K25

J26E2H5

DP#[3]

DP#[2]

DP#[1]

DRDY#

DSTBN#[2]

DSTBN#[1]

DSTBN#[0]

D#[11]

D#[12]

D#[13]

D#[14]

D#[15]

D#[16]

D#[17]

C26

D23

J21

D25

H22

E24

G23

HD#18

HD#15

HD#14

HD#17

HD#13

HD#12

HD#16

CPU_THERMTRIP#

R208 680

R204 24.9 1%

AE25

DP#[0]

DBSY#

DEFER#

D#[18]

D#[19]

D#[20]

F23

F24

E25

HD#21

HD#20

HD#19

1 2

1 2

DBR#

D#[21]

HDSTBP3# <11>

HDSTBP2# <11>

HDSTBP1# <11>

HDSTBP0# <11>

HDSTBN3# <11>

HDSTBN2# <11>

HDSTBN1# <11>

HDSTBN0# <11>

HDRDY# <11>

DEFER# <11>

HDBSY# <11>

H_DBR# <31>

V21

P26

G25

DBI#[0]

D#[63]

D#[62]

DBI#[3]

DBI#[2]

DBI#[1]

D#[61]

D#[60]

D#[59]

D#[58]

D#[57]

D#[56]

D#[55]

D#[54]

D#[53]

D#[52]

D#[51]

D#[50]

D#[49]

D#[48]

D#[47]

D#[46]

D#[45]

D#[44]

D#[43]

D#[42]

D#[41]

D#[40]

D#[39]

D#[38]

D#[37]

D#[36]

D#[35]

D#[34]

D#[33]

D#[32]

D#[31]

D#[30]

D#[29]

D#[28]

D#[27]

D#[26]

D#[25]

D#[22]

D#[23]

D#[24]

F26

D26

L21

HD#24

HD#22

HD#23

1 2

C201 22P NI

GND

GND

E21

AA24

AA22

AA25

Y21

Y24

Y23

W25

Y26

W26

V24

V22

U21

V25

U23

U24

U26

T23

T22

T25

T26

R24

R25

P24

R21

N25

N26

M26

N23

M24

P21

N22

M23

H25

K23

J24

L22

M21

H24

G26

HDBI#3

HDBI#2

HDBI#1

HDBI#0

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#56

HD#55

HD#54

HD#53

HD#52HA#15

HD#51

HD#50

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40HA#27

HD#39

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

HD#32

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

HD#25

3

DESIGN NOTE:AF3

TIED TO VCCVID

FOR PRESCOTT

SUPPORT

HREQ3#<12>

HREQ4#<12>

NC_XU1_A22

VIDPWRGD<48,49>

CPU_THERMTRIP#<22>

CAD NOTE: TRCPU/TRCPU# Routing

10/10,use ground guards enclosed

CAD NOTE:

NC_XU1_A7

RCVID5<49>

NC_XU1_AE21

VCCVID

NC_XU1_AF24

NC_XU1_AF25

CPURST#<10,11>

RS0#<12>

RS1#<12>

RS2#<12>

NC_XU1_AB2

NC_XU1_AF26

SLP#<21>

SMI#<22>

STPCLK#<22>

TCK

TDI

TDO

TESTHI0

TESTHI1

TESTHI2

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

NC_XU1_B3

NC_XU1_C4

CPU_THERMTRIP#

HTRDY#<12>

TMS

DATA: SIGNAL(S) ROUTE WITHIN SAME GROUP TO +/-25 MILS AND MUST BE LENGTH MATCHED TO THE STROBE.

ADDRE SS: SIGNAL(S) ROUTE WITHIN SAME GROUP TO +/-25 MILS AND MUST BE LENGTH MATCHED TO THE STROBE.

STROBES: A STROBE AND ITS COMPLEMENT SHOULD BE ROUTED TO +/-10 MILS OF THE SAME LENGTH.

DATA,ADDRESS,STROBE AND CLOCK SHOULD BE ROUTED 7MIL WITH A 13MIL SPACING.

GTL Reference Voltage

GMCH_VTT

12

R185

200

1%

R256

0

GMCH_GTLREF<11>

3

1 2

169Ohm

R255

1%

2

J3

H3

A22

A7

AD2

AD3

AE21

AF3

AF24

AF25

AB25

F1

G5

F4

AB2

AF26

AB26

B5

Y4

D4

C1

D5

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

AD25

B3

C4

A2

F7

J6

P4_SOCKET478

GND

XU1B

REQ#[3]

REQ#[4]

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

RESERVED7

RESERVED8

RESET#

RS#[0]

RS#[1]

RS#[2]

RSP#

SKTOCC#

SLP#

SMI#

STPCLK#

TCK

TDI

TDO

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

THERMDA

THERMDC

THERMTRIP#

TMS

TRDY#

HD#[0..63]

HDBI#[0..3]

HA#[3..31]

AB14

VSS25

AB12

VSS24

TRST#

E6

TRST#

AB10

A10

AA9

VSS23

VSS22

VCC1

VCC2

A12

AA7

VSS21

VCC3

A14

AA4

VSS20

VCC4

A16

AA26

VSS19

VCC5

A18

HD#[0..63] <11>

HDBI#[0..3] <11>

HA#[3..31] <11>

AA23

AA19

AA17

AA15

AA13

AA11

VSS18

VSS17

VSS16

VSS15

VSS14

VSS13

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

A20A8AA10

AA12

AA14

AA16

VCCSENCE<49>

AA1A9A3

VSS12

VCC12

AA18

AA8

RCVID0<49>

RCVID1<49>

RCVID2<49>

RCVID3<49>

RCVID4<49>

VSS11

VSS10

VCC13

VCC14

AB11

A26

VSS9

VCC15

AB13

A24

VSS8

VCC16

AB15

A21

VSS7

VCC17

AB17

A19

AB19

A17

VSS6

VSS5

VCC18

VCC19

AB7

A15

VSS4

VCC20

AB9

A13

VSS3

VCC21

AC10

A11

VSS2

VCC22

AC12

D10

VSS1

VCC23

AC14

AE1

AC16

AE2

VID4

VID3

VCC24

VCC25

AC18

AE3

VID2

VCC26

AC8

VCCVID

AE4

AD11

http://laptop-motherboard-schematic.blogspot.com/

VCORE

12

12

GND

R254

200

1%

1 2

12

CB143

270P

R257

0

CPU_GTLREF

CLOSE TO CPU PIN

#F20 GTLREF

2

12

CB142

1UF

X5RX7R

GNDGND

TESTHI1

TESTHI9

TESTHI8

TESTHI0

TESTHI12

TESTHI2

TESTHI11

ASUSTeK COMPUTER INC

Size Project Name

A3

Date: Sheet

Phoenix 2

AE5

VID1

VID0

VCC27

VCC28

AD13

VCCIOPLL

VCCA

AF4A5AE23

VCCVID

VCCIOPLL

VCCSENSE

VCC29

VCC30

VCC31

AD15

AD17

AD19

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

AD20F9F19

F17

VCCA

VCC85

VCC84

VCC83

VCC32

VCC33

VCC34

VCC35

AD7

AD9

AE10

AE12

56

56

56

56

56

56

56

56

R187

56

Title :

Engineer:

1

VCORE

F15

F13

F11

VCC79

VCC78

VCC77

VCC82

VCC81

VCC80

VCC76

VCC75

VCC74

VCC73

VCC72

VCC71

VCC70

VCC69

VCC68

VCC67

VCC66

VCC65

VCC64

VCC63

VCC62

VCC61

VCC60

VCC59

VCC58

VCC57

VCC56

VCC55

VCC54

VCC53

VCC52

VCC51

VCC50

VCC49

VCC48

VCC47

VCC46

VCC45

VCC44

VCC43

VCC42

VCC41

VCC40

VCC36

VCC37

VCC38

VCC39

AE14

AE16

AE18

AE20

RN16A

RN16B

RN16C

RN16D

RN15A

RN15B

RN15C

RN15D

NWD / PRESCOTT - 1

Jason Lin

852Tuesday, March 18, 2003

1

VCORE

E8

E20

E18

E16

E14

E12

E10

D9

D7

D19

D17

D15

D13

D11

C8

C20

C18

C16

C14

C12

C10

B9

B7

B19

B17

B15

B13

B11

AF9

AF7

AF5

AF21

AF2

AF19

AF17

AF15

AF13

AF11

AE8

AE6

Rev

X01

of

5

VSSA

VSSSENCE<49>

A4

AD22Y5Y25

Y22Y2W6W3W24

W21V4V26

V23V1U5

VSS175

VSS174

VSS74

VSS75

B12

VSS173

VSS76

B14

B16

VSS172

VSS171

VSS77

VSS78

B18

B20

VSS170

VSS169

VSS79

VSS80

B23

U25

B26B4B8

XU1C

AB16

VSS26

AB18

VSS27

AB20

GND

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

P4_SOCKET478

D D

BOOTSELECT<50>

C C

1 2

R192

0

NI

GND

VSSA

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS181

VSS180

VSS179

VSS178

VSS177

VSSSENSE

VSS176

http://laptop-motherboard-schematic.blogspot.com/

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

DESIGN NOTE:AE26 ( OPTIMIZED/COMPAT ) IS GND ON NORTHWOOD BUT WILL BE DETECT ON POESCOTT

U22U2T6T3T24

VSS168

VSS167

VSS166

VSS165

VSS81

VSS82

VSS83

VSS84

C11

VSS164

VSS85

C13

T21R4R26

VSS163

VSS86

C15

C17

4

VSS162

VSS161

VSS87

VSS88

C19C2C22

R23R1P5

VSS160

VSS159

VSS158

VSS89

VSS90

VSS91

C25C5C7C9D12

P25

P22P2N6N3N24

VSS157

VSS156

VSS155

VSS92

VSS93

VSS94

VSS154

VSS153

VSS95

VSS96

D14

VSS152

VSS97

D16

D18

N21M5M25

VSS151

VSS150

VSS98

VSS99

D20

D21

VSS149

VSS148

VSS100

VSS101

D24D3D6

M22M2L4

VSS147

VSS102

VSS146

VSS145

VSS103

VSS104

D8

GND

GND

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

3

CAD NOTE:PLEASE COMPONENTS AS CLOSE AS POSSIBLE TO CPU SOCKET,TRACE

ROUTE TO CAP MUST BE NO SMALLER THAN 12MIL

L26

L23

L1

K6

K3

K24

K21

J5

J25

J22

J2

H4

H26

H23

H1

G6

G3

G24

G21

F8

F5

F25

F22

F2

F18

F16

F14

F12

F10

E9

E7

E4

E26

E23

E19

E17

E15

E13

E11

E1

GND

VCORE

CPU VCORE DECOUPLING

CAD NOTE:PLACE THESE INSIDE THE CPU SOCKET CAVITY - 10UF 1206 X5R x 18

12

12

CB116

10UF/6.3V

X5R X5R X5R X5R X5R X5R X5R X5R X5R

VCORE

12

CB46

10UF/6.3V

X5R X5R X5R

VCORE

12

CB71

CB84

10UF/6.3V

10UF/6.3V

12

12

CB47

CB69

10UF/6.3V

10UF/6.3V

CAD NOTE:PLACE 1206 CAP CLOSE OF CPU SOCKET

SOUTH SIDE - 10UF 1206 X5R x 10

2

VCCA

L45

21

500mOhm/32Mhz

INDUCTOR 10UH/100mA (0805)

12

CB94

10UF/6.3V

12

CB305

10UF/6.3V

X5R X5R X5R X5R

R175 0

1 2

12

CB66

10UF/6.3V

X5R X5R

VSSA

12

12

CB145

10UF/6.3V

12

CB306

10UF/6.3V

CB85

10UF/6.3V

12

CB307

10UF/6.3V

12

CB86

10UF/6.3V

12

CB308

10UF/6.3V

VCCIOPLLVCORE

12

VSSA

12

CB77

10UF/6.3V

CB72

10UF/6.3V

1

L42

500mOhm/32Mhz

INDUCTOR 10UH/100mA (0805)

12

CB96

10UF/6.3V

VCORE

21

12

12

CB107

B B

A A

5

MH1

MH2

MH3

MH4

XU1D

post_nc1

post_nc2

post_nc3

post_nc4

P4_SOCKET478

B1

NC

4

3

10UF/6.3V

VCORE

12

CB111

10UF/6.3V

CAD NOTE:PLACE 1206 CAP CLOSE OF CPU SOCKET

NORTH SIDE - 10UF 1206 X5R x 13

CB108

10UF/6.3V

12

CB87

10UF/6.3V

12

CB93

10UF/6.3V

X5RX5RX5R X5RX5RX5RX5RX5RX5R

12

CB98

10UF/6.3V

12

CB112

10UF/6.3V

12

CB73

10UF/6.3V

2

12

CB110

10UF/6.3V

12

CB88

10UF/6.3V

CHIP

CAP

12

12

12

CB92

10UF/6.3V

12

CB146

10UF/6.3V

VCORE VCORE

ASUSTeK COMPUTER INC

Size Project Name

A3

Date: Sheet

12

CB83

10UF/6.3V

CB74

10UF/6.3V

12

CB120

10UF/6.3V

12

CB95

10UF/6.3V

12

+

CE31

220UF/2V

ESR=9MOHM/IR=3A ESR=9MOHM/IR=3A

+

Engineer:

Phoneix 2

12

CB106

10UF/6.3V

12

CB70

10UF/6.3V

X5RX5RX5RX5RX5RX5RX5RX5RX5R

CE32

220UF/2V

Title :

1

NWD / PRESCOTT - 2

Jason Lin

952Tuesday, March 18, 2003

of

Rev

X01

5

PROCESSOR ITP RIGHT-ANGLE,SURFACE MOUNT

D D

ITP CONNECTOR

4

3

2

1

Place Close to GMCH Pin# E8

VCORE

TDI<8>

TMS<8>

TRST#<8>

TCK<8>

FBO<8>

TDO<8>

CPUITPHCLK#<7>

C C

CPUITPHCLK<7>

CPURST#<8,11>

BPM5#<8>

BPM4#<8>

BPM1_3#<8>

BPM0_2#<8>

SYS_RESET#<22,46>

1 2

R178 150 1% NI

R350 0 NI

1 2

Proto only

MR_R#

Proto only

12

C166

0.1U

Place at ICH5 PIN #U1

B B

Proto only

X7R

NI

GND GND GND

Proto only

NC_P1_4

NC_P1_6

NC_P1_21

NC_P1_23

NC_P1_24

P1

29

SIDE1

1

TDI

2

TMS

3

TRST_

4

NC1

5

TCK

6

NC2

7

TDO

8

BCLK_

9

BCLK

10

GND6

11

FBO

12

CPU_RST_

13

BPM5_

14

GND5

15

BPM4_

16

GND4

17

BPM3_

18

GND3

19

BPM2_

20

GND2

21

BPM1_

22

GND1

23

BPM0_

24

DBA_

25

DBR_

26

VCCP1

27

VCCP2

28

VCCP3

30

SIDE2

FPC_CON_28P

NI

CON.28P,RA,P4,ITP

30

28

1

29

http://laptop-motherboard-schematic.blogspot.com/

A A

ITP Port

Title :

ASUSTeK COMPUTER INC

Size Project Name

A3

5

4

3

2

Date: Sheet

Phoenix 2

Engineer:

Jason Lin

10 52Tuesday, March 18, 2003

1

Rev

X01

of

5

4

3

2

1

HA31#

HA30#

HA29#

HA28#

HA27#

HA26#

HA25#

HA24#

HA23#

HA22#

HA21#

HA20#

HA19#

HA18#

HA17#

HA16#

HA15#

HA14#

HA13#

HA12#

HA11#

HA10#

HA9#

HA8#

HA7#

HA6#

HA5#

HA4#

HA3#

HDSTBP3#

HDSTBP2#

HDSTBP1#

HDSTBP0#

HDSTBN3#

HDSTBN2#

HDSTBN1#

HDSTBN0#

HADSTB1#

HADSTB0#

HCLKN

HCLKP

HI_RCOMP_MCH

HD_SWING

GMCH_GTLREF

2

HI[0..10]

HA#[3..31]

HD#[0..63]

HDBI#[0..3]

G26

J26

G30

F31

E32

K24

H27

E28

F29

G27

J27

C34

F28

C32

D34

F25

J24

B33

E30

B31

J25

C31

C30

K23

B32

E29

L23

D30

D26

D12

G9

L19

B19

E12

F9

K19

C19

D28

B30

C7

B7

HA#31G_AD1

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

HDSTBP3#

HDSTBP2#

HDSTBP1#

HDSTBP0#

HDSTBN3#

HDSTBN2#

HDSTBN1#

HDSTBN0#

HADSTB1#

HADSTB0#

NC_U17_AK7

NC_U17_AH7

NC_U17_AG6

NC_U17_AD11

NC_U17_AF7

NC_U17_AD7

NC_U17_AC10

NC_U17_AF8

NC_U17_AG7

NC_U17_AE9

NC_U17_AH9

5

G_AD[0..31]

G_SBA[0..7]

G_ST[0..2]

G_C/BE#[0..3]

G_AD0

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD2

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD3

G_AD30

G_AD31

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_C/BE#0

G_C/BE#1

G_C/BE#2

G_C/BE#3

G_ADSTB0<20>

G_ADSTB1<20>

G_ADSTB0#<20>

G_ADSTB1#<20>

R193

2KOhm

1%

1 2

1 2

R195

2KOhm

1%

CI_RCOMP

AC11

W10

AA11

AA10

AB11

AG6

AD11

AC10

AG7

HD#57

HD#60

HD#58

HD#59

E10

B10

C9B9D8

HD59#

HD60#

HD61#

GADSTBS0

GADSTBS1

V5

R6P7R3R5U9

G_SBA0

HD#56

D10

C11

HD57#

HD58#

GSBA0#

GSBA1#

G_SBA2

G_SBA1

HD#54

HD#55

C13

B11

HD55#

HD56#

GSBA2#

GSBA3#

G_SBA3

G_SBA4

GPR_GREEN<38>

HADS#<8>

BNR#<8>

BPRI#<8>

HBREQ0#<8>

12

R202

2.49K

1%

GND

HD#53

D14

HD53#

HD54#

GSBA4#

GSBA5#

U10U5T7

G_SBA5

GPR_BLUE<38>

GPR_RED<38>

G_SB_STB#<20>

G_SB_STB<20>

HD#52

HD#51

B12

B15

HD52#

GSBA6#

G_SBA7

G_SBA6

HD#61

HD#63

HD#62

U17A

AE6

AA5

W6

W9

V7

AA2

Y4

Y2

W2

AD5

Y5

V2

W3

U3

T2

T4

T5

R2

P2

P5

AE5

P4

M2

AC9

AB7

AA9

AA6

AK7

AH7

AF7

AD7

AF8

AE9

AH9

Y7

W5

AA3

U2

B8

GAD0

GAD1

HD62#

HD63#

GAD10

GAD11

http://laptop-motherboard-schematic.blogspot.com/

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD2

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD3

GAD30

GAD31

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

CI0

CI1

CI10

CI2

CI3

CI4

CI5

CI6

CI7

CI8

CI9

GCBE0

GCBE1

GCBE2

GCBE3

GADSTBF0

GADSTBF1

AC6V4AC5

12

R194

2.49K

1%

GND

HD#49

HD#50

E14

B14

HD50#

HD51#

GSBA7#

N3N5N2

G_ST0

HD#48

B13

HD49#

GST0

G_ST1

4

HD#47

HD48#

GST1

G_ST2

HD#46

HD46#

HD47#

GST2

HD#45

H10G8E9

HD45#

DINV0#

C17

HDBI#0

HD#44

HD#38

HD#40

J11

HD44#

HD#43

HD#42

E11

K13

HD43#

HD#41

L15

HD41#

HD42#

G10

HD#39

G12

HD40#

K15

HD39#

HD#37

E13

HD37#

HD38#

HD#36

F11

HD#35

F13

HD36#

HD#34

J13

HD35#

HD#33

L16

HD33#

HD34#

HD#31

HD#32

K17

J15

HD32#

HD#30

E17

HD30#

HD31#

HD#29

G14

SPRINGDALE

ADS#

GREEN

GREEN#

BLUE#

H6

G5

G6

F4

GND

GND

MCH_BSEL0

MCH_BSEL1

RED

E4

GND

RED#

GSBSTBS

GSBSTBF

T11

U11

F27

B28

DINV1#

DINV2#

DINV3#

BLUE

L17

L14

C15

H7

HDBI#3

HDBI#2

HDBI#1

CI_SWING = 0.82V

CI_SWING<15>

CK66M_MCH<7>

G_DEVSEL#<20>

G_FRAME#<20>

G_GNT#<20>

G_IRDY#<20>

HD#28

J19

HD29#

BNR#

B26

HD#27

E21

HD27#

HD28#

BPRI#

BREQ0#

B24

HD#26

E15

HD26#

BSEL0

L13

HD#25

HD#24

F21

F15

HD24#

HD25#

BSEL1

CI_RCOMP

L12

AG2

CI_RCOMP

HD#22

HD#23

HD#21

G16

G18

HD22#

HD23#

CI_SWING

GCLKIN

AF2

H4

HD#19

HD#20

F19

J17

L18

HD20#

HD21#

GFRAME

GDEVSEL

U6M7V11

AB4

HD19#

GGNT

HD#17

HD#16

HD#18

G20

F17

E19

HD17#

HD18#

GIRDY

GPAR/ADD_DETECT

AB2

R10

HD#9

HD#15

D18

HD16#

GRBF

AC2

GRCOMP

3

HD#8

HD#11

HD#14

HD#13

HD#12

HD#10

B16

D16

B18

B17

E16

E18

E20

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

GRCOMP/DVOBCRCOMP

GSTOP

GTRDY

GVREF

GVSWING

GWBF

GREQ

W11

AB5

AD2

AC3

R9

N6

AJ6

HD#6

HD#7

HD#5

HD#4

B22

D22

B20

C21

HD5#

HD6#

HD7#

HD8#

CISTRF

CISTRS

CLVREF

CPURST#

AJ5

AF4E8M4M5E27F2H3

CISTRS

CISTRF

D20

HD4#

DBI_HI

B21

HD2#

HD3#

DBI_LO

DBSY#

HD#1

HD#0

B23

E22

HD0#

HD1#

DDCA_CLK

DDCA_DATA

L21

1

1

AJ3

DEFER#

G24G4AP8

HI10

HD#2

HD#3

HI9

HI8

AH2

AJ2

HI9

HI8

HI10

DRDY#

DREFCLK

EXTTS#

NC_U17_AP8

T5 tp30 NI

T4 tp30 NI

HI4

HI5

HI7

HI6

AL4

AL2

AL3

AK5

HI7

HI6

HI5

HDVREF

HDSWING

HDRCOMP

E23

F23

C25

E24

HD_RCOMP

HI3

AG5

HI4

HITM#

K21

HI3

HIT#

HI2

AK2

AH4

CK48M_VGA <7>

HDRDY# <8>

DEFER# <8>

GRP_DDC_DATA_3V <38>

GRP_DDC_CLK_3V <38>

HDBSY# <8>

G_DBI_LO <20>

G_PIPE# <20>

CPURST# <8,10>

CI_VREF <15>

HI1

HI0

AG3

AF5

HI2

HI1

HI0

HISTRS

HISTRF

HI_VREF

HI_SWING

HI_RCOMP

AH5

AE2

AE3

AD4

CI_VREF = 0.34V

GSWING <15>

G_WBF# <20>

AGPREF_MCH <15,20>

G_TRDY# <20>

G_STOP# <20>

G_REQ# <20>

G_RBF# <20>

G_PAR# <20>

G_AD[0..31]<20>

G_SBA[0..7]<20>

G_ST[0..2]<20>

G_C/BE#[0..3]<20>

D D

C C

B B

HBSEL0<7,8>

HBSEL1<7,8>

+1.5V

A A

GND

1 2

R229

52.3Ohm

1%

GND

HI[0..10] <21>

HA#[3..31] <8>

HD#[0..63] <8>

HDBI#[0..3] <8>

GMCH_VTT

12

R189

301

1%

12

R184

100

1%

BOM Change

From 102 to

100

HDSTBP3# <8>

HDSTBP2# <8>

HDSTBP1# <8>

HDSTBP0# <8>

HDSTBN3# <8>

HDSTBN2# <8>

HDSTBN1# <8>

HDSTBN0# <8>

HADSTB1# <8>

HADSTB0# <8>

MCHHCLK# <7>

MCHHCLK <7>

HI_VSWING_MCH <15>

HI_VREF_MCH <15>

HI_STB <21>

HI_STB# <21>

HIT# <8>

HITM# <8>

GMCH_GTLREF <8>

GND

HD_SWING Design 10 mil trace,

7 mil space

GSWING

AGP 3.0 = 0.77V

AGP 2.0 = 1.04V

AGPREF_MCH

AGP 3.0 = 0.35V

AGP 2.0 = 0.75V

HI_RCOMP_MCH

GRCOMP

HD_RCOMP

R223 52.3Ohm 1%

R218 42.2 1%

R226 20Ohm 1%

Title :

ASUSTeK COMPUTER INC

Size Project Name

A3

Date: Sheet

Phoenix 2

Engineer:

12

C146

0.01U

CAP 0.01UF/50V (0603)X7R (103)

HD_SWING

0.25 * GMCH_VTT

12

C147

0.01U

CAP 0.01UF/50V (0603)X7R (103)

GND

1 2

1 2

1 2

GMCH_GTLREF

12

CB113

0.1U

X7R

GND

SPRINGDALE - 1

Jason Lin

11 52Tuesday, March 18, 2003

1

+1.5V

+1.5V

GND

Rev

X01

of

5

GND

R197 137 1%

Close to GMCH route short and

wide

M_CHA_DQS[0..7]<16,17>

D D

C C

B B

M_CHB_DQS[0..7]<18,19>

M_CHA_DM[0..7]<16,17>

M_CHB_DM[0..7]<18,19>

HREQ0#<8>

HREQ1#<8>

HREQ2#<8>

HREQ3#<8>

HREQ4#<8>

M_CHA_BA0<16,17>

M_CHA_BA1<16,17>

M_CHB_BA0<18,19>

M_CHB_BA1<18,19>

M_CHA_CKE0<16,17>

M_CHA_CKE1<16,17>

M_CHB_CKE0<18,19>

M_CHB_CKE1<18,19>

M_CHA_CLK0<16>

M_CHA_CLK1<16>

M_CHA_CLK2<16>

M_CHA_CLK0#<16>

M_CHA_CLK1#<16>

M_CHA_CLK2#<16>

M_CHB_CLK0<18>

M_CHB_CLK1<18>

M_CHB_CLK2<18>

M_CHB_CLK0#<18>

M_CHB_CLK1#<18>

M_CHB_CLK2#<18>

M_CHA_CS#0<16,17>

M_CHA_CS#1<16,17>

M_CHA_DQS[0..7]

M_CHB_DQS[0..7]

M_CHA_DM[0..7]

M_CHB_DM[0..7]

3P3V_PWRGOOD<31>

PCI_RST_SYS#<20,28,30,31,33>

M_CHA_CAS#<16,17>

M_CHB_CAS#<18,19>

GRP_HSYNC_3V_R<38>

NC_U17_AM20

NC_U17_AP20

NC_U17_AG19

NC_U17_AE18

NC_U17_AK33

NC_U17_AM16

NC_U17_P31

NC_U17_AK34

NC_U17_AL16

NC_U17_P32

NC_U17_AJ30

NC_U17_AK15

NC_U17_N31

NC_U17_AH29

NC_U17_AL15

NC_U17_N30

MCH_REFSET

12

PROCHOT#<8>

ICH_SYNC#<31>

HLOCK#<8>

HTRDY#<8>

AE33

AH34

AA25

AL20

AN19

AM20

AP20

AK19

AF19

AG19

AE18

AK32

AP17

AK33

AM16

AK31

AN17

AK34

AL16

AG29

AF17

AJ30

AK15

AG30

AG17

AH29

AL15

AA34

B29

J23

L22

C29

J21

Y25

N33

P31

N34

P32

N27

N31

N26

N30

RS0#<8>

RS1#<8>

RS2#<8>

U17B

3P3V_PWRGOOD

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

SBA_A0

SBA_A1

SBA_B0

SBA_B1

SCKE_A0

SCKE_A1

SCKE_A2

SCKE_A3

SCKE_B0

SCKE_B1

SCKE_B2

SCKE_B3

SCMDCLK_A0

SCMDCLK_A1

SCMDCLK_A2

SCMDCLK_A3

SCMDCLK_A4

SCMDCLK_A5

SCMDCLK_A0#

SCMDCLK_A1#

SCMDCLK_A2#

SCMDCLK_A3#

SCMDCLK_A4#

SCMDCLK_A5#

SCMDCLK_B0

SCMDCLK_B1

SCMDCLK_B2

SCMDCLK_B3

SCMDCLK_B4

SCMDCLK_B5

SCMDCLK_B0#

SCMDCLK_B1#

SCMDCLK_B2#

SCMDCLK_B3#

SCMDCLK_B4#

SCMDCLK_B5#

SCS_A0#

D24G3E25

HSYNC

HTRDY#

AJ8

HLOCK#

ICH_SYNC#

SCS_A1#

SCS_A2#

Y31

Y32

Y34

W31

SCAS_A#

SCAS_B#

SCS_A3#

W34

B27

RS2#

SCS_B0#

SCS_B1#

U26

T29

4

G22

C27

RS0#

RS1#

SCS_B2#

SCS_B3#

V25

W25

MCH_REFSET

L20

AE14D2AR1

AK4

RSTIN#

PWROK

REFSET

PROCHOT#

SDM_A0

SDM_A1

SDM_A2

SDM_A3

AP12

AP16

AM24

AP30

NC_U17_AN35

NC_U17_AG9

NC_U17_AP34

AP34

AG9

AN35

RESERVED1

RESERVED2

RESERVED3

SDM_A4

SDM_A5

SDM_A6

SDM_A7

AF31

W33

M34

H32

M_CHB_DQS7

M_CHB_DQS6

NC_U17_AR1

L27

J30

SDQS_B6

SDQS_B7

RESERVED0

SDM_B0

SDM_B1

SDM_B2

AG11

AG15

AE21

3

M_CHB_DQS5

U30

M_CHB_DQS3

M_CHB_DQS1

M_CHB_DQS4

M_CHB_DQS2

AG13

AG21

AH27

AD29

SDQS_B2

SDQS_B3

SDQS_B4

SDQS_B5

M_CHA_DQS7

M_CHA_DQS6

M_CHB_DQS0

M32

H31

AF15

SDQS_A7

SDQS_B0

SDQS_B1

M_CHA_DQS5

M_CHA_DQS4

M_CHA_DQS3

M_CHA_DQS2

AP23

AM30

AF34

V34

SDQS_A3

SDQS_A4

SDQS_A5

SDQS_A6

M_CHA_DQS1

M_CHA_DQS0

M_CHA_VREF

AN11

AP15

E34

SDQS_A0

SDQS_A1

SDQS_A2

M_CHB_VREF

AP9

SMVREF_A

SMVREF_B

SPRINGDALE

SDM_B3

SDM_B4

SDM_B5

SDM_B6

AJ28

AC31

SDM_B7

U31

M29

J31

SDQ_A0

AP11

AP10

SDQ_A2

SDQ_A1

AN13

AM12

SDQ_A4

SDQ_A3

AL10

AM10

SDQ_A5

SDQ_A6

AP13

AL12

SDQ_A8

SDQ_A7

AM14

AP14

SDQ_A10

SDQ_A9

AP19

AL18

SDQ_A12

SDQ_A11

AL14

AK9

AN9

AL9

AA33

SMXRCOMP

SMYRCOMP

SMXRCOMPVOL

SMXRCOMPVOH

SDQ_A16

SDQ_A15

SDQ_A14

SDQ_A13

AP22

AM18

AP18

AN15

M_CHB_DQ62

M_CHB_DQ63

J29

G32

R34

R33

SDQ_B62

SDQ_B63

SMYRCOMPVOL

SMYRCOMPVOH

SDQ_A21

SDQ_A20

SDQ_A19

SDQ_A18

SDQ_A17

AL22

AP21

AN27

AL24

AM22

M_CHB_DQ57

M_CHB_DQ58

M_CHB_DQ59

M_CHB_DQ60

M_CHB_DQ61

H29

F32

G33

N25

M25

SDQ_B58

SDQ_B59

SDQ_B60

SDQ_B61

SDQ_A25

SDQ_A24

SDQ_A23

SDQ_A22

AP33

AP29

AP28

AP27

AP25

M_CHB_DQ53

M_CHB_DQ54

M_CHB_DQ55

M_CHB_DQ56

R26

P25

L32

K30

SDQ_B54

SDQ_B55

SDQ_B56

SDQ_B57

SDQ_A29

SDQ_A28

SDQ_A27

SDQ_A26

AM31

AN29

AM28

AM33

SMXRCOMP <15>

SMXRCOMPVOH <15>

SMXRCOMPVOL <15>

SMYRCOMP <15>

SMYRCOMPVOH <15>

SMYRCOMPVOL <15>

M_CHB_DQ47

M_CHB_DQ48

M_CHB_DQ49

M_CHB_DQ50

M_CHB_DQ51

M_CHB_DQ52

R27

P29

R30

K28

L30

R31

SDQ_B48

SDQ_B49

SDQ_B50

SDQ_B51

SDQ_B52

SDQ_B53

SDQ_A35

SDQ_A34

SDQ_A33

SDQ_A32

SDQ_A31

SDQ_A30

AH31

AD32

AF32

AG34

AH32

AN34

M_CHB_DQ44

M_CHB_DQ45

M_CHB_DQ43

M_CHB_DQ46

T25

AA31

V29

U25

SDQ_B44

SDQ_B45

SDQ_B46

SDQ_B47

SDQ_A39

SDQ_A38

SDQ_A37

SDQ_A36

AC34

AD34

AE34

AG33

M_CHB_DQ39

M_CHB_DQ40

M_CHB_DQ41

M_CHB_DQ42

AA27

AA30

W30

U27

SDQ_B40

SDQ_B41

SDQ_B42

SDQ_B43

SDQ_A43

SDQ_A42

SDQ_A41

SDQ_A40

AD31

V31

V32

AB31

2

+2.5V_DUAL

M_CHB_DQ36

M_CHB_DQ35

M_CHB_DQ37

M_CHB_DQ38

AE31

AB29

AA26

SDQ_B36

SDQ_B37

SDQ_B38

SDQ_B39

SDQ_A47

SDQ_A46

SDQ_A45

SDQ_A44

U33

U34

AB32

1 2

M_CHB_DQ34

AC30

Y29

SDQ_B33

SDQ_B32

SDQ_B31

SDQ_B30

SDQ_B34

SDQ_B35

SDQ_B29

SDQ_B28

SDQ_B27

SDQ_B26

SDQ_B25

SDQ_B24

SDQ_B23

SDQ_B22

SDQ_B21

SDQ_B20

SDQ_B19

SDQ_B18

SDQ_B17

SDQ_B16

SDQ_B15

SDQ_B14

SDQ_B13

SDQ_B12

SDQ_B11

SDQ_B10

SDQ_B9

SDQ_B8

SDQ_B7

SDQ_B6

SDQ_B5

SDQ_B4

SDQ_B3

SDQ_B2

SDQ_B1

SDQ_B0

SDQ_A63

SDQ_A62

SDQ_A61

SDQ_A60

SDQ_A59

SDQ_A58

SDQ_A57

SDQ_A56

SDQ_A55

SDQ_A54

SDQ_A53

SDQ_A52

SDQ_A51

SDQ_A50

SDQ_A49

SDQ_A48

T32

T34

150

R237

1%

AC27

AE30

AF28

AD25

AJ27

AJ26

AF27

AG27

AH26

AK25

AE22

AJ24

AK21

AL19

AK23

AG23

AE20

AE19

AJ18

AJ16

AJ14

AK13

AL17

AK17

AL13

AE17

AG12

AK11

AF12

AL8

AE16

AL11

AE15

AJ10

F34

G34

J34

K31

F33

E33

H34

J33

L33

L34

P34

T31

K32

K34

GND

M_CHB_DQ33

M_CHB_DQ32

M_CHB_DQ31

M_CHB_DQ30

M_CHB_DQ29

M_CHB_DQ28

M_CHB_DQ27

M_CHB_DQ26

M_CHB_DQ25

M_CHB_DQ24

M_CHB_DQ23

M_CHB_DQ22

M_CHB_DQ21

M_CHB_DQ20

M_CHB_DQ19

M_CHB_DQ18

M_CHB_DQ17

M_CHB_DQ16

M_CHB_DQ15

M_CHB_DQ14

M_CHB_DQ13

M_CHB_DQ12

M_CHB_DQ11

M_CHB_DQ10

M_CHB_DQ9

M_CHB_DQ8

M_CHB_DQ7

M_CHB_DQ6

M_CHB_DQ5

M_CHB_DQ4

M_CHB_DQ3

M_CHB_DQ2

M_CHB_DQ1

M_CHB_DQ0

M_CHA_DQ63

M_CHA_DQ62

M_CHA_DQ61

M_CHA_DQ60

M_CHA_DQ59

M_CHA_DQ58

M_CHA_DQ57

M_CHA_DQ56

M_CHA_DQ55

M_CHA_DQ54

M_CHA_DQ53

M_CHA_DQ52

M_CHA_DQ51

M_CHA_DQ50

12

R238

150

1%

12

C162

2.2U

Y5V

(0805)

GND

12

C164

2.2U

Y5V

(0805)

GND

M_CHB_DQ[0..63]

M_CHA_DQ[0..63]

1

Place close to

MCH

M_CHA_VREF

1.25V (DUAL)

12

C161

0.1U

X7R

GND

M_CHB_VREF

1.25V (DUAL)

12

C163

0.1U

X7R

GND

M_CHB_DQ[0..63] <18,19>

M_CHA_DQ[0..63] <16,17>

M_CHA_DM0

M_CHA_DM1

M_CHA_DM2

M_CHA_DM3

M_CHA_DM4

M_CHA_DM5

M_CHA_DM6

M_CHA_DM7

M_CHB_DM0

M_CHB_DM1

M_CHB_DM2

M_CHB_DM4

M_CHB_DM5

M_CHB_DM6

M_CHB_DM7

NC_U17_W34

NC_U17_W25

NC_U17_Y32

A A

M_CHB_CS#0<18,19>

M_CHB_CS#1<18,19>

5

NC_U17_V25

4

M_CHB_DM3

M_CHA_DQ3

M_CHA_DQ2

M_CHA_DQ1

M_CHA_DQ0

M_CHA_DQ6

M_CHA_DQ5

M_CHA_DQ4

M_CHA_DQ9

M_CHA_DQ8

3

M_CHA_DQ14

M_CHA_DQ15

SPRINGDALE - 2

Title :

ASUSTeK COMPUTER INC

Size Project Name

A3

2

Date: Sheet

Phoneix 2

Engineer:

Jason Lin

12 52Tuesday, March 18, 2003

1

Rev

X01

of

M_CHA_DQ49

M_CHA_DQ48

M_CHA_DQ47

M_CHA_DQ46

M_CHA_DQ45

M_CHA_DQ44

M_CHA_DQ43

M_CHA_DQ42

M_CHA_DQ41

M_CHA_DQ40

M_CHA_DQ39

M_CHA_DQ38

M_CHA_DQ37

M_CHA_DQ36

M_CHA_DQ35

M_CHA_DQ34

M_CHA_DQ33

M_CHA_DQ32

M_CHA_DQ31

M_CHA_DQ30

M_CHA_DQ29

M_CHA_DQ28

M_CHA_DQ27

M_CHA_DQ26

M_CHA_DQ25

M_CHA_DQ24

M_CHA_DQ23

M_CHA_DQ22

M_CHA_DQ21

M_CHA_DQ20

M_CHA_DQ19

M_CHA_DQ18

M_CHA_DQ17

M_CHA_DQ16

M_CHA_DQ13

M_CHA_DQ12

M_CHA_DQ11

M_CHA_DQ10

M_CHA_DQ7

http://laptop-motherboard-schematic.blogspot.com/

5

4

3

2

1

CB80

0.1U

X7R

CB79

0.1U

X7R

12

GND

SPRINGDALE - 3

1

+1.5V_FSB

+1.5V_DPLL

Spec:

62mA

12

CB89

0.1U

X7R

GND

CB90

0.1U

X7R

Jason Lin

13 52Tuesday, March 18, 2003

GND

GND

12

CB65

10uF/10V

Spec:

30mA

12

CB55

10uF/10V

+1.5V_SM

Spec:

30mA

VDAC

GND

Spec: 1A

12

CB56

10uF/10V

GND

of

12

CB54

10uF/10V

Rev

X01

L46

0.82UH

0603,30mA

+1.5V

SMYRCOMPVO

12

CB133

0.22U

Y5V

GND

R141

1 NI

0603

R133

0

R181

0

Place CAP

close to

GMCH

L47

0.1UH

0603,300mA0603

Place CAP

close to

GMCH

INDUCTOR 1UH/1A(1206)

Place CAP

close to GMCH

21

21

L41

0.1UH

0603,300mA

L44

21

1UH

12

GND

12

GND

21

12

CB91

0.01U

Y5V

GND

Title :

ASUSTeK COMPUTER INC

Size Project Name

A3

Date: Sheet

Phoenix 2

Engineer:

AJ34

AL33

AL30

AL26

AL28

AJ33

AJ31

AL25

AF21

AL23

AJ22

AF29

AL21

AJ20

AL34

AL29

AL27

W26

GND

U17C

12

GND

SMAA_A0

SMAA_A1

SMAA_A2

SMAA_A3

SMAA_A4

SMAA_A5

SMAA_A6

SMAA_A7

SMAA_A8

SMAA_A9

SMAA_A10

SMAA_A11

SMAA_A12

SMAA_B0

SMAA_B1

SMAA_B2

SMAA_B3

SMAA_B4

SMAA_B5

SMAA_B6

SMAA_B7

SMAA_B8

SMAA_B9

SMAA_B10

SMAA_B11

SMAA_B12

SMAB_A1

SMAB_A2

SMAB_A3

SMAB_A4

SMAB_A5

SMAB_B1

SMAB_B2

SMAB_B3

SMAB_B4

SMAB_B5

SRAS_A#

SRAS_B#

SWE_A#

SWE_B#

AB34

W27

CB114

0.1U

M_CHA_MAA[0..12]

M_CHB_MAA[0..12]

AA32

AA4

AB10

AB27

AB28

VSS22

VSS23

VSS26

VSS27

TESTIN#

VSSA_DAC

VSYNC

AG10D3E2A6B5

GND

NC_U17_AG10

+1.5V_DPLL+1.5V_FSB

+1.5V_SM

VDAC

VTT_DCAP3

+2.5V_DUAL_DACP2

L6

L7

L9

C2

AB25

AC25

AC26

AL35

B3

A31

B4

A11

AB9

AC1

AC32

AC35

AC4

AH22

AH24

AH3

AH30

AH33

A13

A16

A20

A23

A25

A27

A29

A32A7A9

AA1

AB26

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS24

VSS25

VCCA_DPLL

VCCA_FSB0

VCCA_FSB1

VCCA_DDR2

VCCA_DDR3

VCCA_DAC

VCCA_DDR0

VCCA_DDR1

VCC40

VCC41

SPRINGDALE

http://laptop-motherboard-schematic.blogspot.com/

VTT0

VTT1

VTT2

B6C5C6D5D6D7E6

GMCH_VTT

VTT_DCAP1

VTT_DCAP2

VTT_DCAP3

VTT_DCAP2

VTT_DCAP1

VTT3

VTT4

VTT5

VTT6

VTT10

VTT11

VTT12

VTT13

12

4

VTT8

E7

VTT9

CB102

0.47U

F7

A15

A21A4A5

T1 tp30 NI

VTT14

A3

NC_U17_A3

NC0

NC1

NC2

NC3

A33

A35

AF13

NC_U17_A33

NC_U17_AF13

NC_U17_A35

NC4

NC5

NC6

NC7

AF23

AJ12

AN1

AP2

AR3

NC_U17_AJ12

NC_U17_AP2

NC_U17_AN1

NC_U17_AF23

NC_U17_AR3

12

CB117

0.1U

GND

NC10

NC11

NC12

NC8

NC9

AR35B2B25

AR33

NC_U17_AR35

NC_U17_AR33

NC_U17_B2

NC_U17_B25

NC13

NC14

NC15

B34C1C23

C35

NC_U17_C23

NC_U17_C35

NC_U17_C1

NC_U17_B34

+2.5V_DUAL

NC16

NC17

NC18

NC19

VCC_AGP0

VCC_AGP1

E26

M31

R25

J1

J2

J3J4J5K2K3K4K5

NC_U17_R25

NC_U17_M31

NC_U17_E26

+1.5V

12

CB124

0.01U

X7R

GND GND

VTT7

1

GND

L10

L11

VCC36

VCC37

VCC38

VCC39

VCC_AGP2

VCC_AGP3

VCC_AGP4

VCC_AGP5

+2.5V_DUAL

12

3

VCC34

VCC35

VCC_AGP6

VCC_AGP7

CB123

0.1U

J6M9J7J8J9K6K7K8K9

VCC30

VCC31

VCC32

VCC33

VCC_AGP10

VCC_AGP11

VCC_AGP8

VCC_AGP9

L2L3L4L5Y1

L1

Place CAPS close to GMCH PIN#Place CAPS close to GMCH PIN#

+2.5V_DUAL_DACP5

+2.5V_DUAL_DACP4

+2.5V_DUAL_DACP2

+2.5V_DUAL_DACP1

Y18

Y19

Y20

VCC26

VCC27

VCC28

VCC29

VCC_AGP12

VCC_AGP13

VCC_AGP14

VCC_AGP15

AG1

W19

W20

Y16

Y17

VCC23

VCC24

VCC25

VCC_AGP16

VCC_DAC0

Y11

G1G2AA35

VCORE_DCAP1

VCORE_DCAP2

V18M8V20

W16

VCC20

VCC21

VCC22

VCC_DDR28

VCC_DDR27

VCC_DDR26

VCC_DDR25

VCC_DDR24

VCC_DDR23

VCC_DDR22

VCC_DDR21

VCC_DDR20

VCC_DDR19

VCC_DDR18

VCC_DDR17

VCC_DDR16

VCC_DDR15

VCC_DDR14

VCC_DDR13

VCC_DDR12

VCC_DDR11

VCC_DDR10

VCC_DAC1

VCC_DDR0

AL6

12

CB122

0.47U

Y5V

GND

V16

VCC17

VCC16

VCC15

VCC18

VCC19

VCC14

VCC13

VCC12

VCC11

VCC10

VCC9

VCC8

VCC7

VCC6

VCC5

VCC4

VCC3

VCC2

VCC1

VCC0

VCC_DDR9

VCC_DDR8

VCC_DDR7

VCC_DDR6

VCC_DDR5

VCC_DDR4

VCC_DDR3

VCC_DDR2

VCC_DDR1

GND

U20

U17

U16

T20

T19

T18

T17

T16

R11

P11

P10

N9

N11

N10

M11

M10

R35

E35

AR7

AR5

AR4

AR31

AR21

AR15

AP7

AP6

AP5

AP4

AP3

AN8

AN7

AN6

AN5

AN4

AN2

AM8

AM7

AM6

AM5

AM3

AM2

AM1

AL7

V_SMYRCOMP

+3.3V

12

CB151

0.1U

X7R

GND

12

CB138

0.22U

Y5V

+1.5V

+2.5V_DUAL_DACP1

NC_U17_AR31

+2.5V_DUAL_DACP4

+2.5V_DUAL_DACP5

GMCH_VDAC

12

CB130

0.1U

X7RX7R

GND

2

+1.5V

+1.5V

+2.5V_DUAL

+1.5V

R191

1

1 2

DEBUG ONLY

1 2

1 2

1 2

M_CHA_MAA[0..12]<16,17>

M_CHB_MAA[0..12]<18,19>

D D

M_CHA_MAA0

M_CHA_MAA1

M_CHA_MAA2

M_CHA_MAA3

M_CHA_MAA4

M_CHA_MAA5

M_CHA_MAA6

M_CHA_MAA7

M_CHA_MAA8

M_CHA_MAA9

M_CHA_MAA10

M_CHA_MAA11

M_CHA_MAA12

M_CHB_MAA0

M_CHB_MAA1

M_CHB_MAA2

C C

M_CHA_RAS#<16,17>

M_CHB_RAS#<18,19>

B B

M_CHB_MAA3

M_CHB_MAA4

M_CHB_MAA5

M_CHB_MAA6

M_CHB_MAA7

M_CHB_MAA8

M_CHB_MAA9

M_CHB_MAA10

M_CHB_MAA11

M_CHB_MAA12

NC_U17_AL34

NC_U17_AM34

NC_U17_AP32

NC_U17_AP31

NC_U17_AM26

NC_U17_AE27

NC_U17_AD26

NC_U17_AL29

NC_U17_AL27

NC_U17_AE23

GRP_VSYNC_3V_R<38>

AK29

AN31

AN25

AP26

AP24

AN23

AN21

AG31

AD27

AE24

AK27

AG25

AM34

AP32

AP31

AM26

AE27

AD26

AE23

AC33

M_CHA_WE#<16,17>

M_CHB_WE#<18,19>

Place CAPS close to GMCH PIN#

VCORE_DCAP1

A A

VCORE_DCAP2

5

12

CB105

0.1U

X7R X7R X7RY5V

GND

5

4

3

2

1

U17D

Y9

GND

AB30

AB33

AR25

AR27

AR29

AR32

AD10

AD28

AD30

AD33

AE10

AE11

AE12

AE13

AE25

AE26

AE32

AE35

AF11

AF14

AF16

AF18

AF20

AF22

AF24

AF25

AJ32

AJ35

AK10

AB3

VSS28

VSS29

VSS30

VSS285

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS66

VSS65

VSS67

VSS68

VSS69

VSS70

VSS71

AK12

VSS72

VSS73

AK14

AK16

VSS286

VSS74

VSS75

AK18

VSS76

AK20

AK22

AB6

AB8

AR9

AD3

AD6

AD8

AD9

AE1

AE4

AF3

AJ1

AH6

AJ4

AJ9

D D

C C

B B

Y35Y6Y8

VSS283

VSS284

VSS77

VSS78

AK24

Y30

Y33

VSS282

VSS79

AK26

AK28

Y3

VSS280

VSS281

VSS80

VSS81

AK3

Y27

Y28

VSS279

VSS82

AK8

AL1

Y26

VSS277

VSS278

VSS83

VSS84

AL32

VSS276

VSS85

AM11

AM13

W18

W32W4Y10

VSS274

VSS275

VSS86

VSS87

AM15

AM17

VSS272

VSS273

VSS88

VSS89

AM19

VSS271

VSS90

AM21

AM23

P33P6V8V9W17

VSS269

VSS270

VSS91

VSS92

C10

C12

VSS268

VSS93

C14

VSS266

VSS267

VSS94

VSS95

C16

P27

P28P3P30

VSS265

VSS96

C18

C20

N32

N35N4P26

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

SPRINGDALE

VSS102

VSS101

VSS100

VSS97

VSS98

VSS99

C26

C22

C24

M33M6N1

VSS257

VSS258

VSS104

VSS103

D11D1C8C4C28

M28M3M30

VSS255

VSS256

VSS106

VSS105

D15

D13

M27

VSS253

VSS254

VSS108

VSS107

D17

L35

M26

VSS252

VSS109

D21

D19

L31

VSS250

VSS251

VSS110