Page 1

High-Efficiency Inverter Controller

Figure 1. Typical Floating Secondary Application

FEATURES

• Single-stage power conversion, input voltage

range of 5V to 18V

• Reduces the number of components and board

size by 30% compared with conventional design

• Supports both floating and grounded secondary

designs

• 90% efficiency vs. typical 75% efficiency of

conventional designs

• Internal open-lamp and short-circuit protections

• Wide dimming range

• Supports synchronization among multiple

inverter modules

• Reliable 2-winding transformer design,

eliminates arcing problems

• Constant frequency, symmetrical, sinusoidal

drive

ORDERING INFORMATION

OZ962R - 16 lead TSSOP

OZ962G - 16-pin plastic SOP

TYPICAL APPLICATION CIRCUIT

VDD (+12V)

ENA

GND

CN1

R2

10K

R3

5.1K

F1

1A Fast Fuse

R9

R1

220K

200K

C2

0.1u

C9

.01u

R11

+

-

C3

330p

1M

C1

22u

25V

R5

RT

CT

SST

10K

16

15

14

C5

13

220p

12

11

10

9

0.1u

REF

OVP

NC

SCP

ADJ

FB

CMP

GND

R4

15K

OZ962G

U1

VDD

CLK

ENA

NDR

PDR

1

2

3

4

5

6

7

8

R7

100K

R6

30

C4

OZ962

GENERAL DESCRIPTION

The OZ962 is a unique high-efficiency, CCFL

backlight controller. It generates symmetrical,

near sinusoidal output voltage and current

waveforms for driving a CCFL backlight. The

OZ962 operates in a single, constant frequency,

pulse-width-modulation (PWM) mode. Typical

operating frequency ranges between 30 KHz to

100 KHz, depending on the CCFL and the

transformer’s characteristics.

Operating in a PWM push-pull manner, the

transformer in the OZ962 backlight inverter

requires only one primary winding and one

secondary winding, with the secondary winding

requiring no fold-back treatment.

The OZ962 is available in both 16-pin SOIC and

TSSOP packages. It is specified over the

commercial temperature range: 0 oC to +70 oC.

R10

100

C7

68p

2200T33T

3KV

3.5W

R14

1.0K

C8

0.22u

4

SI4559EY

2

R12

750

3 U2

Q2

Q1

1

R8

0.5

5,6

7,8

C6 2.2u

50V

+-

* *

03/01/00 OZ962-SF -2.7 Page 1

Copyright 1999 by O2Micro All Rights Reserved U.S. Patent #5,619,402

R13

100

Page 2

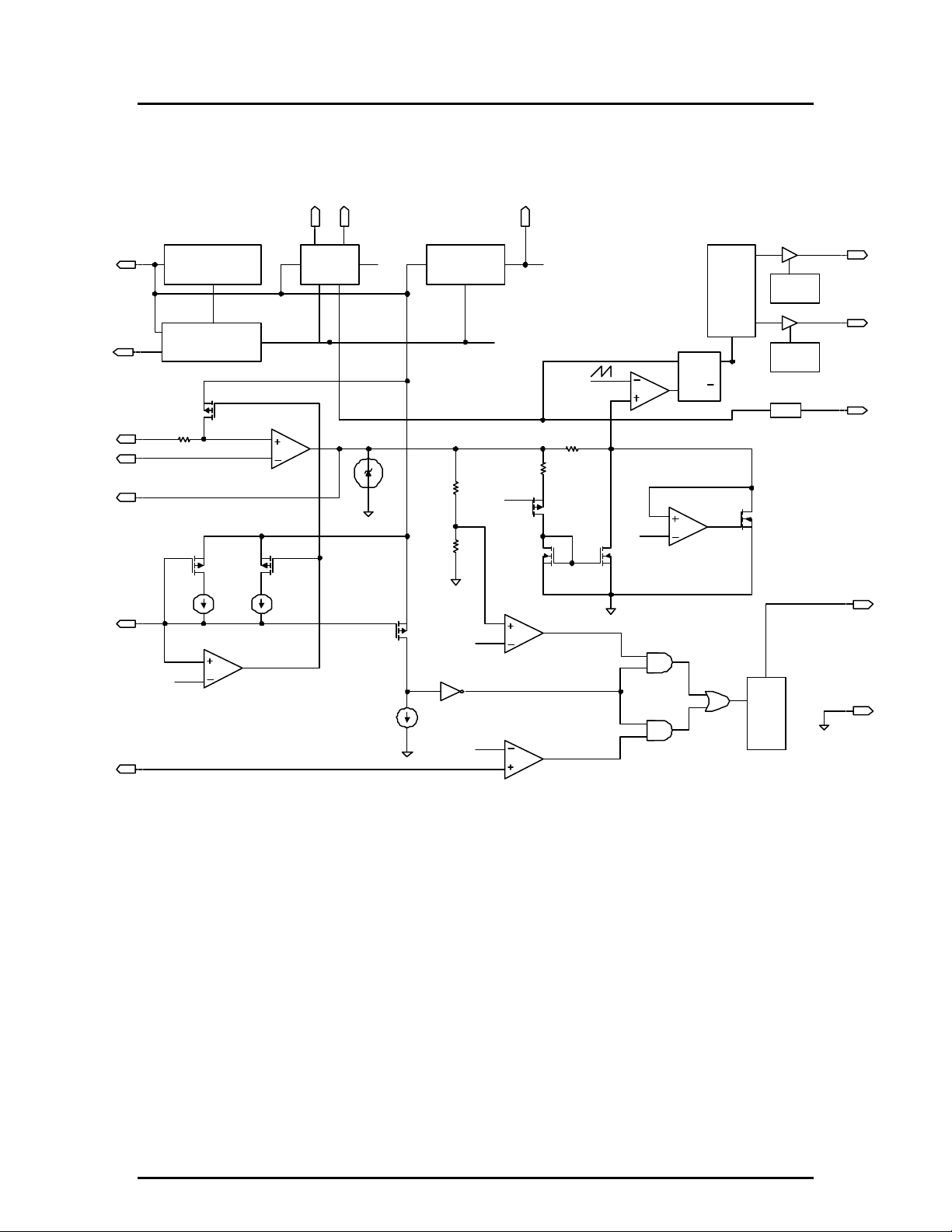

FUNCTIONAL BLOCK DIAGRAM

Note:

UVL – Under Voltage Lockout

OZ962

VDD(16)

REF(1)

ADJ(5)

FB(6)

CMP(7)

SST(9)

Under Voltage

Lockout

Band Gap

Reference

40k

3µA

10µA

Ct(14) Rt(15)

Error

Amp.

OSC

Vcmp

Vdd

SST

RAMP

3V

OVP Voltage

Generator

1k

9k

OVP

OVP(2)

OVP

OVP=Vref-(Vdd - 1)(12.5/150)

D=1.1(OVP)/2.5 - 0.2

Vref (2.5V)

RAMP

30k

SST

60k

OSC

Ve

Ve=Vcmp-2*(Vcmp-SST-Vgs)

OVP

SQRQ

Break

Before

Make

P-Clamp

Dmax

Clamp

N-Clamp

1/2F

NDR(11)

PDR(10)

CLK(13)

ENA(12)

2.0v

SCP(4)

OVP – Over Voltage Protection

SCP – Short-Circuit Protection

2µA

SCP & OVP inhibited during

start-up

ADJ

Figure 2. Functional Block Diagram

OVP

SCP

UVL

shut

down

latch

GND(8)

OZ962-SF -2.7 Page 2

Page 3

OZ962

PIN DESCRIPTION

Names Pin No. I/O Description

REF 1 O Reference voltage output. Nominal voltage is 2.5 V.

OVP 2 I Over-voltage protection setting. Refer to formula for OVP in block diagram

NC 3 - No connection.

SCP 4 I Short-circuit protection input.

ADJ 5 I Reference voltage input for dimming control.

FB 6 I Current sense feedback.

CMP 7 O Compensation for the current sense feedback.

GND 8 GND Ground.

SST 9 I

PDR 10 O Gate drive output for the P-MOSFET.

NDR 11 O Gate drive output for the N-MOSFET.

ENA 12 I Enable input, active high (Vth is about 1.7 V).

CLK 13 O Open-drain clock output.

CT 14 I/O Timing capacitor. CT and RT set the clock frequency.

RT 15 I/O Timing resistor.

VDD 16 PWR Supply voltage input.

ABSOLUTE MAXIMUM RATINGS

VDD 18 V

GND +/- 0.3 V

Logic inputs -0.3 V to VDD+0.3 V

Power dissipation 800 mW at 25 oC

RECOMMENDED OPERATING RANGE

VDD 5V to 18V

Fosc 30 KHz to 100 KHz

Rosc 50 k to 150 k

on page 2 of this document.

Tsst ~ 0.2 Csst (Vdd - 5), where Csst is the soft start capacitor value in µF

and Tsst value is in µs.

Operating temp. 0 oC to 70 oC

Operating junction temp. 150 oC

Storage temp. -55 to 150 oC

OZ962-SF -2.7 Page 3

Page 4

OZ962

FUNCTIONAL SPECIFICATIONS

Parameter Symbol Test Conditions Limits Unit

5 V < VDD < 15 V Min Typ Max

Reference Voltage

Nominal voltage Vref I

Line regulation - 8 - mV/V

Load regulation I

Oscillator

Initial accuracy fosc Ct = 220 pF, Rt = 120 k 48 53 58 KHz

Ramp peak 2.45 2.55 2.65 V

Ramp valley 0.40 0.45 0.50 V

Temp. stability TA = 0 oC to 70 oC - - 200 ppm/ oC

Error Amplifier

Input bias current V

Input offset voltage VFB = 4.0 V - 5 10 mV

Input voltage range 0 - VDD-

Open loop voltage gain 50 60 - dB

Unity gain bandwidth 1 1.5 - MHz

Power supply rejection 50 60 - dB

Under-Voltage Lockout

Positive-going threshold voltage - 3.8 4 V

Negative-going threshold voltage 3.4 3.6 - V

Supply

Supply current - Enable Low

Adj, CT = Open

Supply current - Enable Low

Adj, CT = Open

Supply current - Enable High ION VDD = 5.0 V - 0.6 1.5 mA

Supply current - Enable High ION VDD = 15 V - 0.6 1.5 mA

NDR output

Output high voltage VOH Isink = 10 mA,

VDD >7.8 V 7.0 8.0 9.0 V

Output low voltage VOL Isource = 10 mA - 0.3 0.8 V

Output resistance R

PDR output

Output high voltage VOH Isink = 10 mA VDD-

Output low voltage VOL Isource = 10 mA,

VDD > 7.8 V - VDD-

Output resistance R

Break-Before-Make

Qn off to Qp on delay THL 200 240 280 ns

Qp off to Qn on delay TLH 220 260 300 ns

I

VDD = 5.0 V - 25 120

OFF

I

VDD = 15 V - 25 120

OFF

VDD = 5.0 V - 50 80

OUT

VDD = 5.0 V - 50 80

OUT

= 0.25 mA,

load

VDD = 5 V

= 0.2 mA to 1.0 mA - 1 - mV/mA

load

=2.0 V - 25 500 nA

ADJ=VFB

VDD < 7.8 V

VDD < 7.8 V

2.37 2.50 2.63 V

1.5

VDD-

VDD-

0.3

0.6

0.4 0.5 0.8 V

0.5

VDD-

0.3

6.0

- V

- V

VDD-

4.0

V

µA

µA

Ω

Ω

OZ962-SF -2.7 Page 4

Page 5

PACKAGE INFORMATION

INCHES

MILLIMETERS

DIM

E1E

1

OZ962

A2 A1

A

TSSOP-16

PACKAGE

θ

D

2

R1

b

e

Gauge Plane

R

b

θ

c

c1

θ

3

L

1

L1

b1

A - 0.043 - 1.20

A1 0.002 0.006 0.05 0.15

A2 0.031 0.041 0.80 1.05

D - - 4.90 5.10

E1 0.169 0.177 4.30 4.50

R 0.004 - 0.09 R1 0.004 - 0.09 -

b1 0.007 0.010 0.19 0.25

c1 0.004 0.006 0.09 0.16

L1 0.039REF 1.0REF

θ1 0° 8° 0° 8°

θ2 12°REF 12°REF

θ3 12°REF 12°REF

MIN MAX MIN MAX

L 0.020 0.030 0.45 0.75

E 0.252BSC 6.40BSC

b 0.007 0.012 0.19 0.30

c 0.004 0.008 0.09 0.20

e 0.026BSC 0.65BSC

OZ962-SF -2.7 Page 5

Page 6

A

INCHES

MILLIMETERS

DIM

1

OZ962

A 0.0532 0.0688 1.35 1.75

A1 0.0040 0.0098 0.10 0.25

B 0.013 0.020 0.33 0.51

C 0.0075 0.0098 0.19 0.25

D 0.3859 0.3937 9.80 10.00

H 0.2284 0.2440 5.80 6.20

α

D

HE

SOP-16

PACKAGE

MIN MAX MIN MAX

E 0.1497 0.1574 3.80 4.00

e 0.050 BCS. 1.27 BCS.

L 0.016 0.050 0.40 1.27

0° 8° 0° 8°

αα

C

L

A1eB

OZ962-SF -2.7 Page 6

Loading...

Loading...