A

B

C

D

E

ZZZ

COMPAL CONFIDENTIAL

1 1

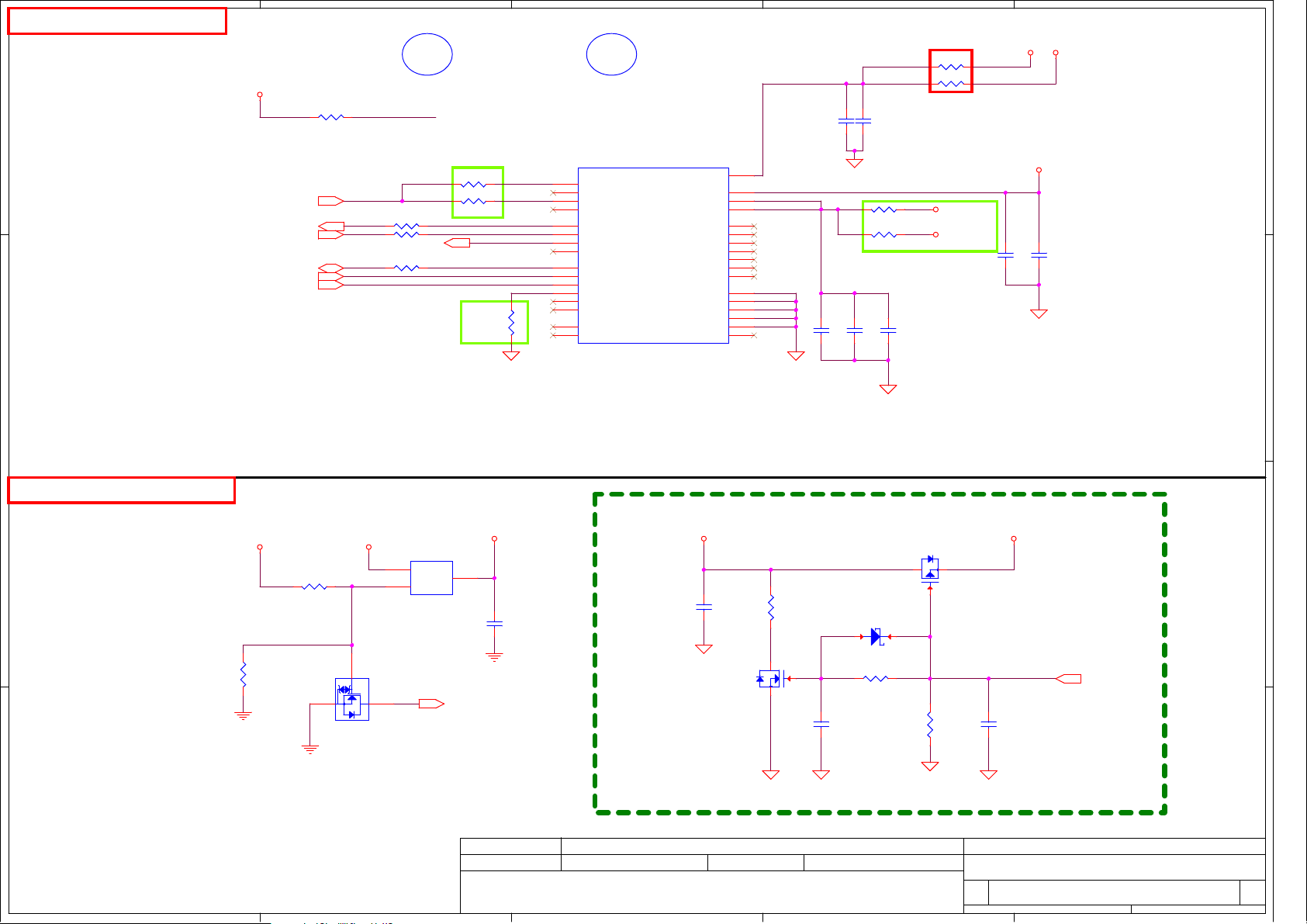

MODEL NAME : Loki-G 15/17

UC1

MB PCB PN : DAA000FC010

PWR/B PCB PN : DA4002L3010

IO/B PCB PN : DA6001XF010

2 2

UC1

PCB R1

DAA000FC010

PCB@

CPU R1

SA0000BPJ1L

i5@

SA0000BPZ1L

i7@

UC1

UC1

CPU R3

SA0000BPJ2L

i5@

SA0000BPZ2L

i7@

Dell/Compal Confidential

Schematic Document

COFFEE LAKE H

3 3

N17P-G0/G1

Loki-G 15/17

2018-03-22

REV : 1.0 (A00)

Layout Dell logo

4 4

Security Classification

Security Classification

COPYRIGHT 2014

ALL RIGHT RESERVED

REV: X00

PWB: 9HTP8

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

For DELL review

A

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2016/01/ 06 2017/01/ 06

2016/01/ 06 2017/01/ 06

2016/01/ 06 2017/01/ 06

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet o f

Date : Sheet o f

D

Date : Sheet o f

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-F611P

LA-F611P

LA-F611P

0.3

0.3

0.3

1 7 8Thursday, March 22 , 2018

1 7 8Thursday, March 22 , 2018

1 7 8Thursday, March 22 , 2018

E

A

B

C

D

E

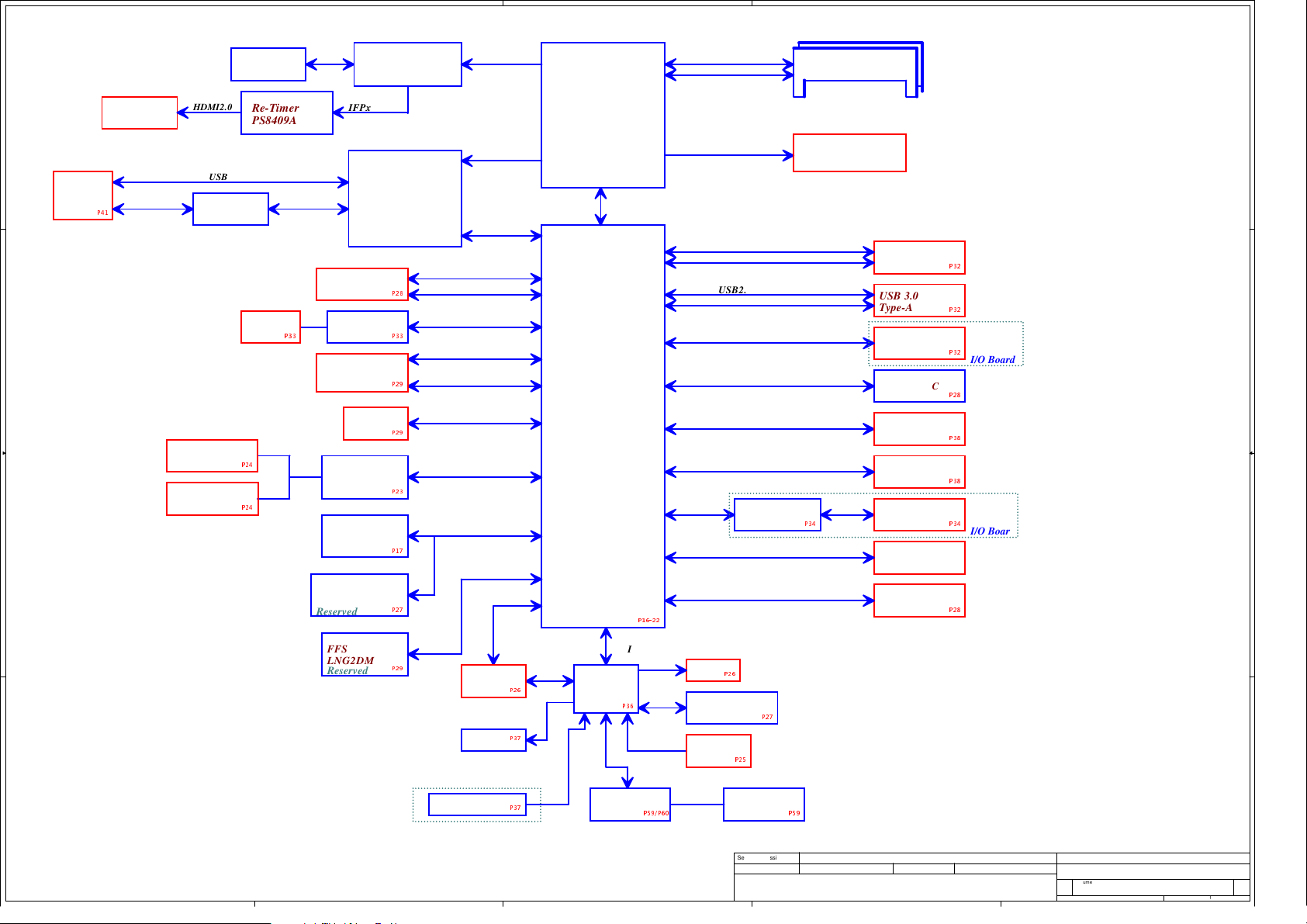

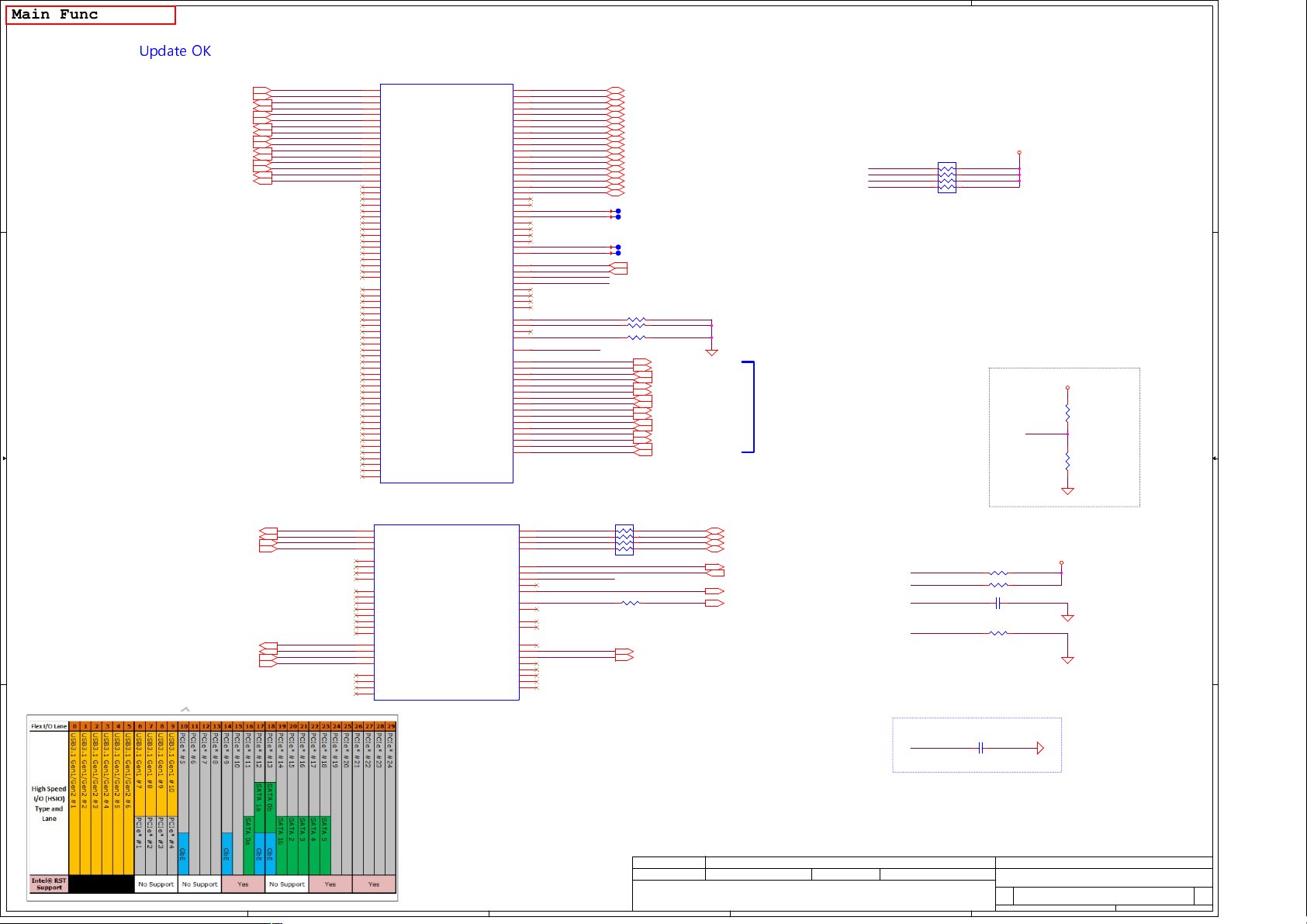

VRAM * 4

GDDR5

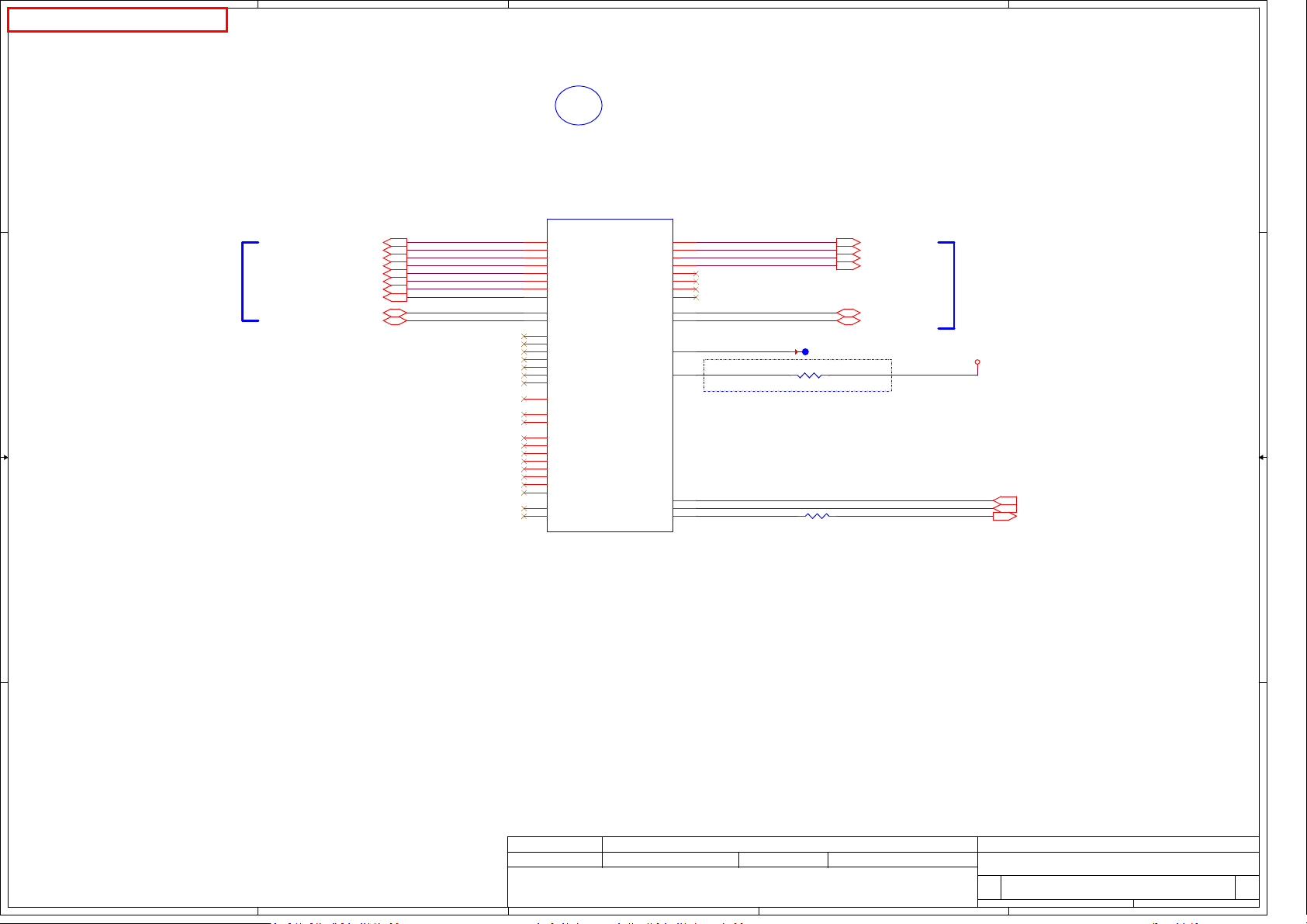

GPU

N17P-G0/G1

GB4-128

PEG 3.0 x8

DDR4 ChannelA

DDR4 ChannelB

Intel

1 1

HDMI 2.0

Conn.

HDMI2.0

Re-Timer

PS8409A

IFPx

DDI1 x4

USB3.1

TypeC

P41

USB2.0/CC

TPS65982DC

I2C/USB2.0

RJ45

2 2

USB3.1 Gen1

Thunderbolt

Alpine Ridge-SP

M.2 Slot A Key-E

(WLAN+BT4.0)

LOM

RTL8111H

M.2 Slot C Key-M

(SATA/PCIe SSD)

PCI-E x4

Port 7-Port 10

PCI-E x1

CNVi

P28

P33P33

P29

Port 15

PCI-E x1

Port 14

PCI-E x4

Port 9-Port 12

SATA1A

CFL-Lake-H

Processor

45W

BGA

DMI x4

100MHz

5GB/s

Intel

CNL-H-PCH

BGA 874 Balls

eDP1.2 x4

USB2.0

USB3.0

USB2.0

USB3.0

USB2.0

USB2.0

HM370

HDD

Conn.

P29

Main SPKR *2

Universal

Audio Jack

3 3

P24

P24

HDA Codec

ALC320 4

SPI Flash

(BIOS 32MB)

TPM

NPCT650

Reserved

P23

P17

P27

SATA0B

HD Audio

SPI

SMBus

I2C

P16 -22

USB2.0

USB2.0

USB2.0 SD3.0

Port 6

Card Reader 2 in 1

RTS51 70 SD / MS

USB2.0

Port 9

DDRIV-DIMM X2

1.2V DDR4 2400 MHz

32GB Max

15.6'' and 17.3"

HD / FHD

Port 1

Port 1

Port 3

Port 3

Port 2

Port 4

Port 5

Port 8

P34 P34

USB 3.0

Type-A

USB 3.0

Type-A

USB 2.0

Type-A

TPS659 82D C

Digital Camera

Conn.

Touch Panel

Conn.

Finger Print

M.2 Slot A Key-E

(WLAN+BT4.0)

P32

P32

P32

P28

P38

P38

P28

Left

Left

Right

I/O Board

I/O Board

FFS

LNG 2D MT R

Reserved

P29

Touch Pad

LED

PS2

P26

P37

SMBus

4 4

Power Button

P37

eSPI

MEC 1416

KBC

Charger &

Battery

PWM

FAN

P26

I2C

P36

P59/ P60 P59

Thermal Sensor

NCT771 8W

KB Conn.

P25

AC Adaptor

P27

Power Button Board

128M*32 x4 =2G

256M*32 x4 =4G

A

For DELL review

B

C

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

2016/01/06 2017/01/06

2016/01/06 2017/01/06

2016/01/06 2017/01/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size

Size

Size

Document Number R ev

Document Number R ev

Document Number R ev

LA-F611P

LA-F611P

LA-F611P

Date : Sheet of

Date : Sheet of

Date : Sheet of

E

2 78Thursday, March 22, 2018

2 78Thursday, March 22, 2018

2 78Thursday, March 22, 2018

0.3

0.3

0.3

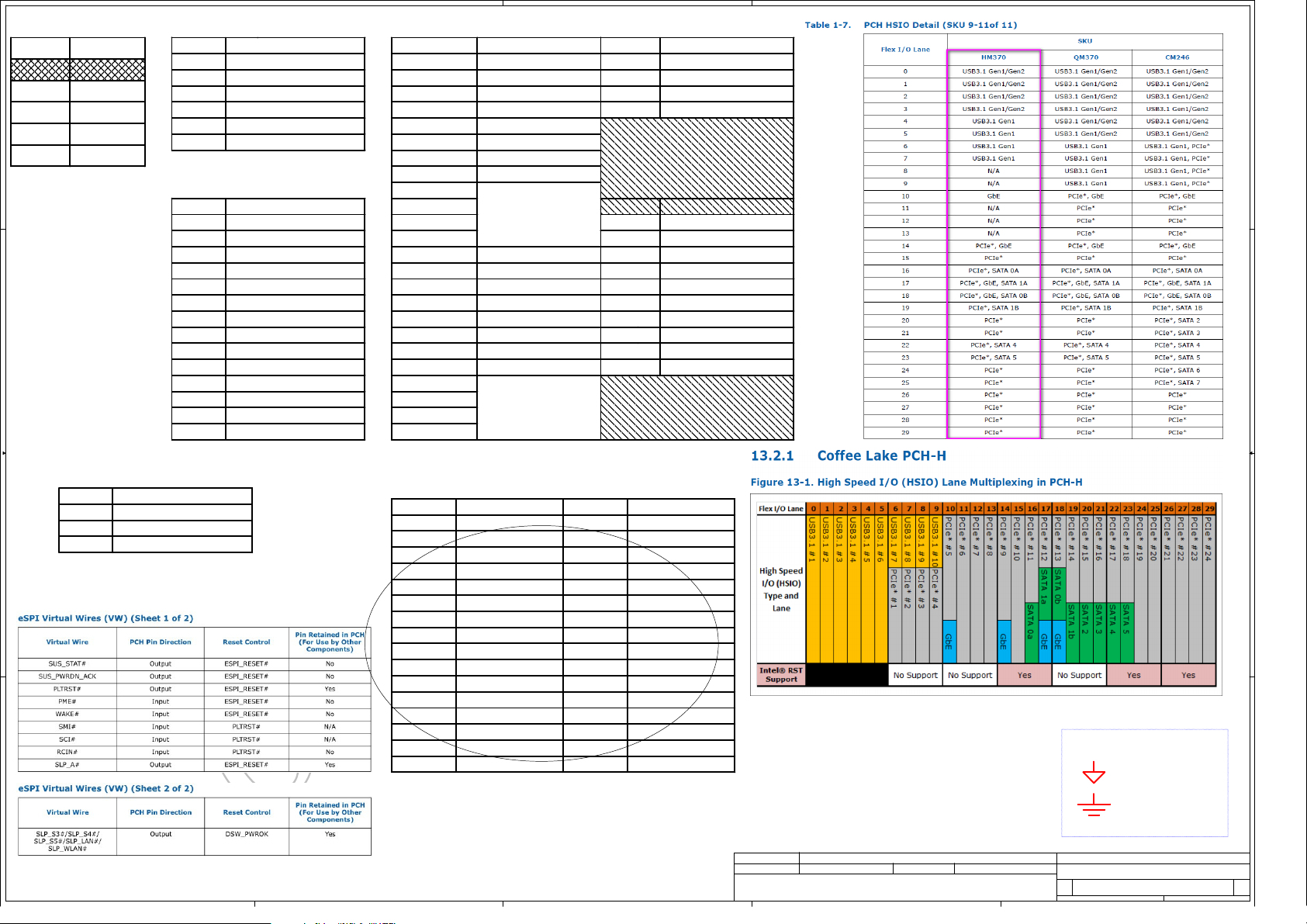

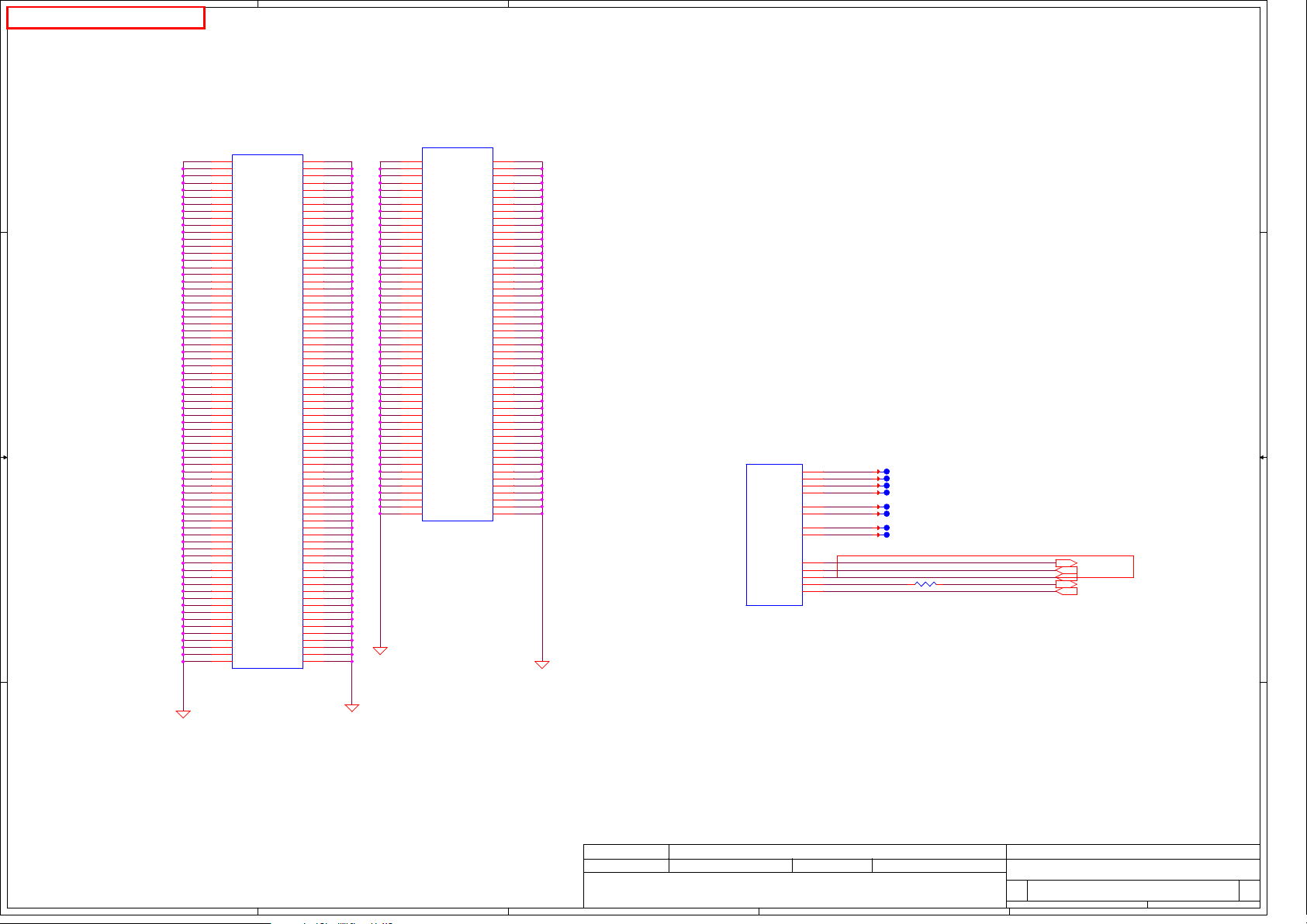

5

Refer Page 26

Board ID

X00

X01

X02

D D

X03

A00

Resistor

10K

17.8K

27K

37.4K

49.9K

HSIO port Alloction

USB3

DESTINATION

1

USB JUSB1 (Left Side)

2

None

3

USB JUSB3 (Left Side)

4

None

5

None

6

None

4

PCI EXPRESS

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8

DESTINATION

None

None

None

None

None

None

None

None

USB3

10

3

7

8

9

DESTINATION

None

None

None

None

2

1

Lane 9

USB2

C C

DESTINATION

1

USB JUSB1 (Left Side)

2

USB JUSB2 (I/O)

3

USB JUSB3 (Left Side)

4

TYPEC PD

CAMERA

5

6

Card Reader (I/O)

7

BT & CNVi BRI

8

Touch Screen

9

Finger Print

10

None

None

11

12

None

None

13

14

None

Lane 10

Lane 11

Lane 12

Lane 13

Lane 14

Lane 15

Lane 16

Lane 17

Lane 18

Lane 19

Lane 20

Lane 21

Lane 22

Lane 23

Lane 24

NGFF - NVMe SSD

None (HDD)

LAN

NGFF - WLAN

None

None

None

None

Alpine Ridge - SP

SATA

DESTINATION

0a

1a

0b

1b

2

3None

4

5 None

6 None

7 None

None (NVMe)

NGFF - SSD

HDD

None (LAM)

None (WLAN)

None

None

DDI

B B

A A

1

2

3

DESTINATION

Alpine Ridge

Alpine Ridge

HDMI2.0 LSPCON PS175

For DELL review

5

CLK_PCIE

4

DESTINATION

0

TBT-AR

1

None

2

None

3

None

4

None

5

None

6

None

7

GPU

None

8

9

NGFF - SSD

10

11

12

13

14

15

None

None

None None

None

LAN

WLAN

CLK_REQ

10

11

12

13

14

15

0

1

2

3

4

5

6

7

8

9

DESTINATION

TBT-AR

None

None

None

None

None

None

GPU

None

NVMe

None

None

None

LAN

WLAN

3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

2017/01/06

2017/01/06

2017/01/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2018/01/06

2018/01/06

2018/01/06

Symbol Note :

: means Digital Ground

: means Analog Ground

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

Document Number R ev

Document Number R ev

Document Number R ev

Thursday, March 22, 2018

Thursday, March 22, 2018

Thursday, March 22, 2018

LA-F611P

LA-F611P

LA-F611P

1

3 78

3 78

3 78

0.3

0.3

0.3

5

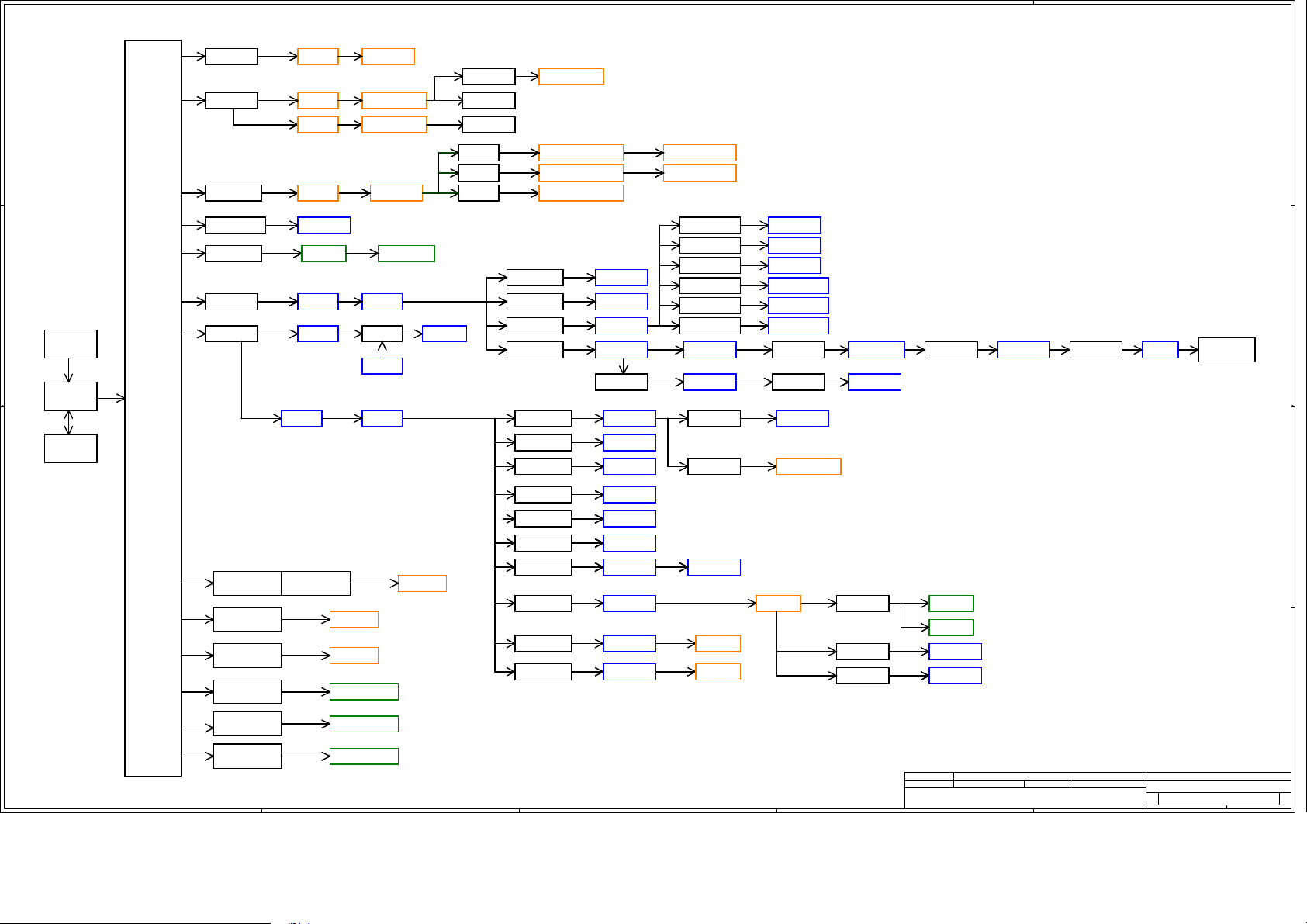

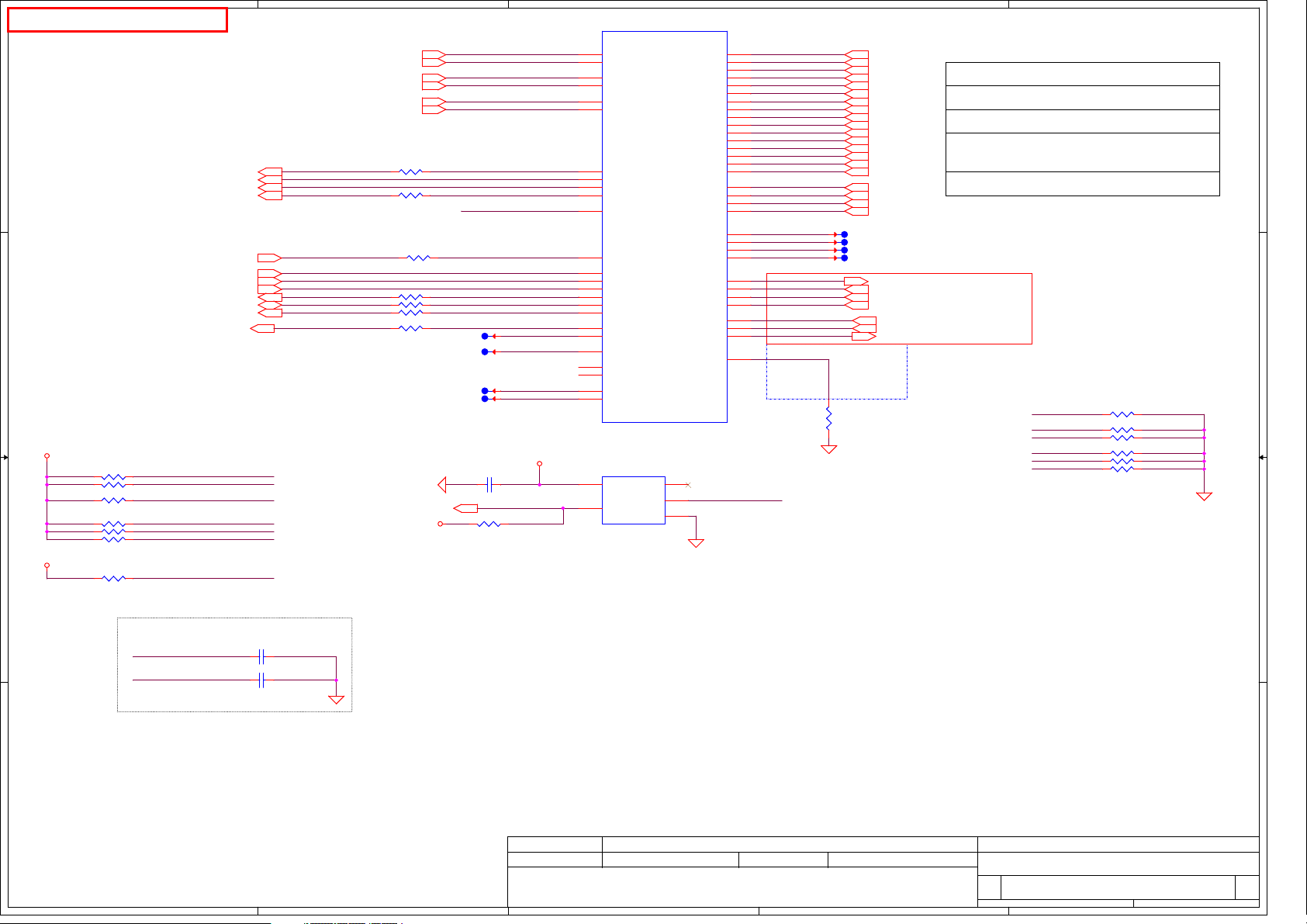

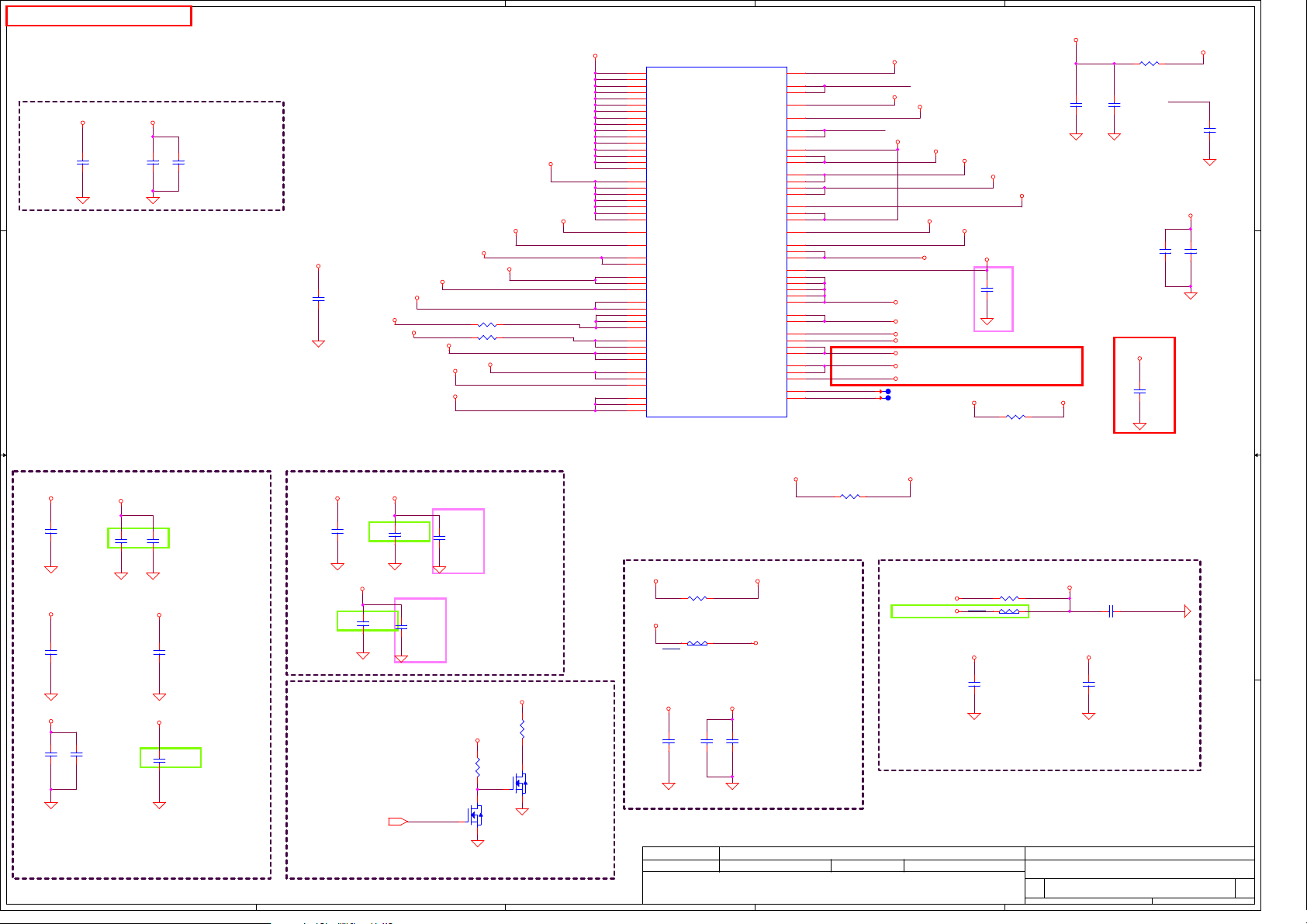

4

3

2

1

PJP901

SY8286RAC

(PU901)

PJPM01

RT8207PGQW

PJPH01

PJPW01

PJP501

PJP301

(PUM01)

TPS51212DSCR

(PUH01)

FUSE 1.5A_24V

(F1)

RT8816AGQW

(PUW01)

SY8180CRAC

(PU501)

SY8288BRAC

(PU301)

D D

CPU PWR

GPU PWR

C C

Peripheral Device PWR

ADAPTER

CHARGER

ISL9538HRTZ-T

(PUB01)

+PWR_S RC

(+19VB)

BATTERY

B B

A A

5

VCCIO_E N

1.2V_VDDQ_ EN

SM_PG_CTRL

EN_5V

EN_3V

NCP302045MNTXG

(PUI01)

NCP302045MN

(PUG01)

NCP302035MNTXG

(PUA01)

NCP302045MNTXG

(PUV01)

NCP302045MNTXG

(PUV02)

NCP302045MNTXG

(PUV03)

+VCCIOP

+1.2VP +1.2V_DDR

+0.6VSP

+1.05VP

+DCBAT_LCD

DGPU_PWRO K

1.35VGPUP

+5VALWP

+3VLP

+3VALWP

NCP302045MNTXG

(PUI02)

DRVON

PWM1_2PH/ICCMAX2

DRVON

PWM1_1PH/ICCMAX1

PJP902

PJPM04

PJPM02

PJPM03

PJPH03

PJPH02FBVDD_ EN

PJPW03

PJPW02

PJP502

PJP503

PJP303

PJP302

DRVON

PWM2_4PH/AD DR

PWM1_4PH/ICCMAX 4

+VCC_GT

+VCC_S A

+GPU_COR E

+GPU_COR E

+GPU_COR E

+VCCIO

EN_VCCSTG_VCCPL L_OC RZ67

+0.6V_DDR_ VTT

+1.05VALW

+1.35VS_VGA

+5VALW

BAS40C

(D1)

+RTC_CELL

+RTC_VCC

+3VALW

+VCC_CORE

4

APE8937GN2

(UZ16)

+1.2V_VCCPLL _OC

JDIMM1/JDIMM2

JDIMM1/JDIMM2

EN_VCCSTG_VCCPL L_OC

TPS22961

(UZ9)

TPS22961

(UZ15)

SIO_SLP _S4#

SIO_SLP _S3#

+VCCSTG_OU T

+VCCST_OU T

RC251 +1.05V_XDP

SY6288D20AAC

(UU1)

SY6288D20AAC

(UU3)

EM5209VF

(UZ1)

SN1610042ZQ ZR

(UT4)

EM5209VF

(UZ1)

0ohm 0603

(RE2)

SY6288C20AAC

(UL2)

0ohm 0402

(RT97)

0ohm 0805

(RT95)

RB551V-30

(DT18)

EM5209VF

(UZ7)

PJP180 1

RT8061AZQW

(PU1801)

PJP250 1 SIO_SLP _S4# PJP250 2

RT9059GSP

(PU2501)

PJP100 1

RT8061AZQW

(PU1001)

USB_EN#

USB_EN#

SIO_SLP _S3#

SIO_SLP _S3#

JPZ2

AUX_ON

PEX_VDD_EN

POK

RT9058-33GX

(PUS04)

RZ48

3.44A

2.8A

+VCCSTG

RZ66

+VCCST

0.24A

0ohm 0603

(R13)

0ohm 0805

(RA1)

0ohm 0603

PLS11, PLS12

3

RH162

PJP180 2

PJP100 2

(RA4)

JP5

AP2330W-7

(UV17)

FUSE 0.5A_13.2V

(F3)

+TBTA_VBUS_1

+3.3V_VBUS_ IN

SY6288C20AAC

(U1)

RT9041E-15GQW

(UP1)

+3VALW_DSW

USB30_VCC A

USB20_VCC B

+5VS

+TBTA_VBUS

+3VS

+3VALW_EC

+LAN_VDD33

+3.3V_TBT_SX

+3VS_TBT

+3VALW_PD

+3V_PCH_ PRIM

+1.8VALWP

+2.5VP +2.5V_MEM

+1.0VS_VGAP +1VS_GFX

3.4A

PLS11, PLS12

PLS11, PLS12

LCD_VCC_TEST_ EN_R

or

EDP_VDD_ EN

+1.8V_PRIM

+TPAN_VDD

+5V_PVD D

+5V_AVD D

+5V_HDD

+VDISPLAY_VCC

+5V_KB_B L

AON7409

(PQS17,PAS18)

RB551V-30

(DT17)

+LCDVD D

+1.2V_RTM_IN

+VBUS_DC_T RIP

+3VALW_PD

AOZ1331

(UG12)

LN2306LT1G

(QA1)

0ohm 0603

(RE66)

1V8_AON_ON

1V8_MAIN_EN

AON7409

(PQS1,PAS15)

+1V8_AON

+1V8_MAIN

+VBUS_DC_ SS

AON7409

(PQS2,PAS16)

+1.8V_AVDD

+1.8VALW_EC

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2016/01/06 2017/01/06

2016/01/06 2017/01/06

2016/01/06 2017/01/06

Deciphered Date

Deciphered Date

Deciphered Date

CHARGER

+SDC_IN

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

ISL9538HRTZ-T

(PUB01)

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Power Rail

Power Rail

Power Rail

Document Number Rev

Document Number Rev

Document Number Rev

LA-F611P

LA-F611P

LA-F611P

1

4 7 8Thursday, March 22, 2 018

4 7 8Thursday, March 22, 2 018

4 7 8Thursday, March 22, 2 018

0.3

0.3

0.3

For DELL review

5

4

3

2

1

D D

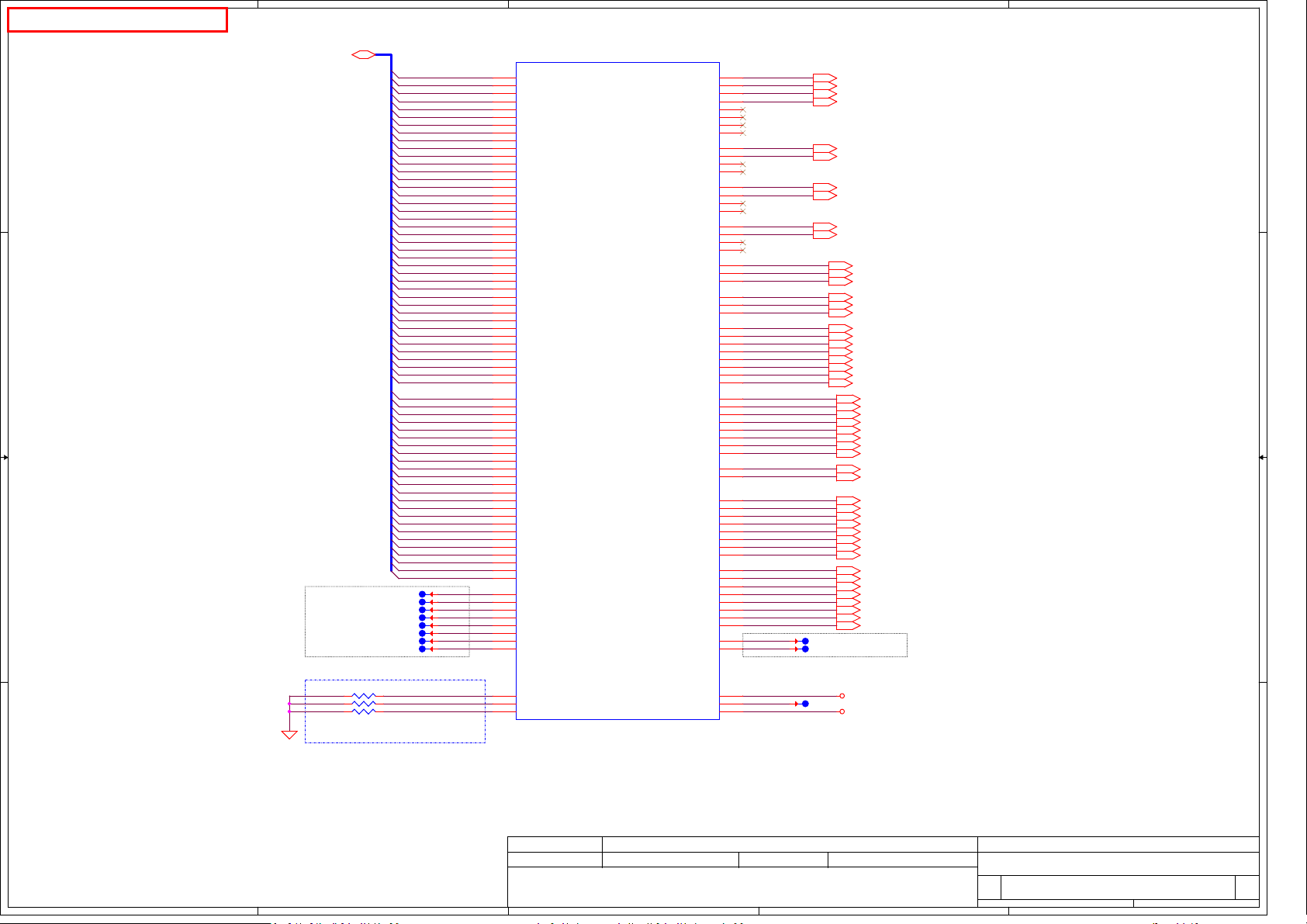

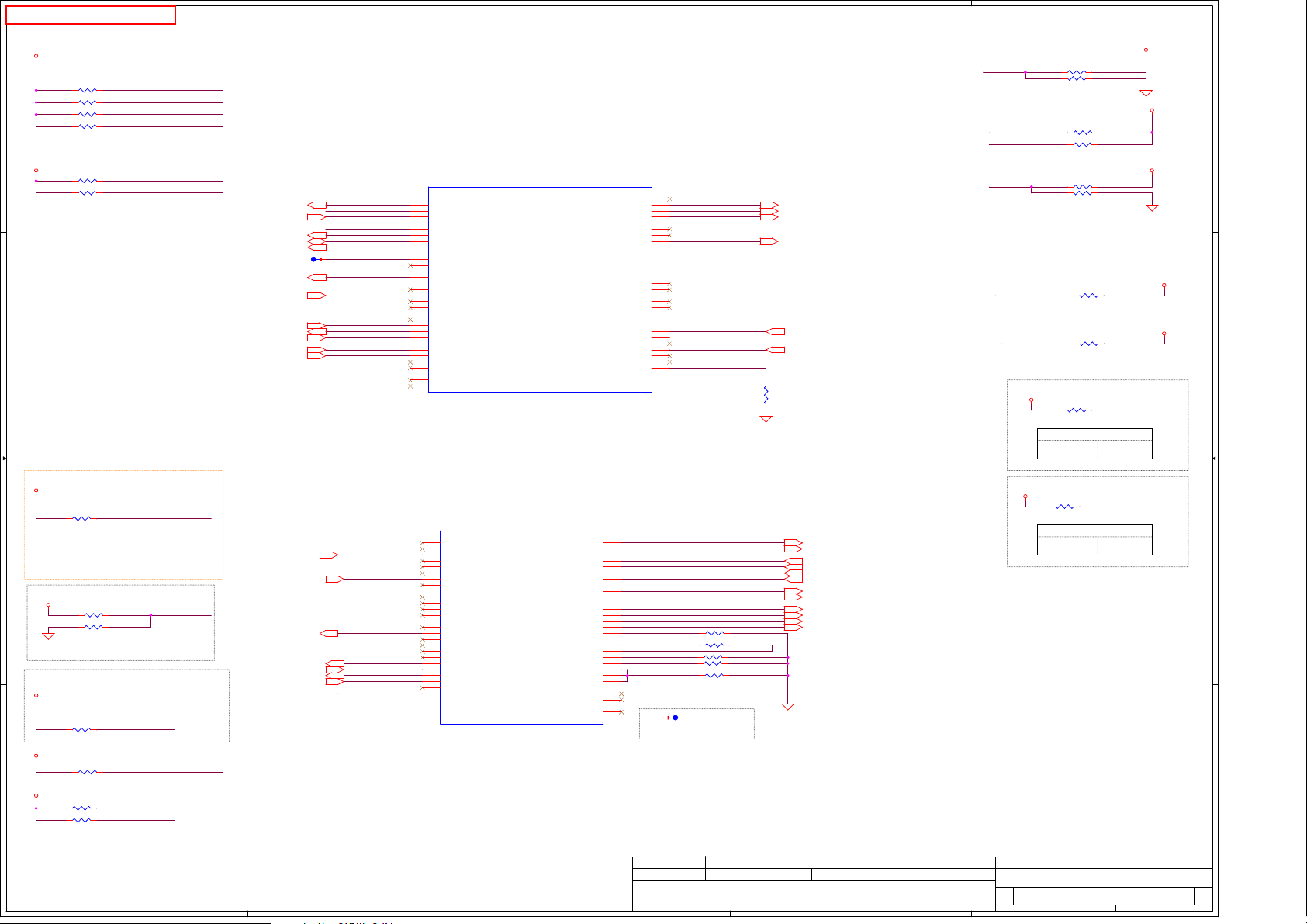

PCH

Host

BE26

BF26

BF25

BE24

Host

C C

Address: 0x88/0x89

B B

BE21

BF21

Slave

BF27

BE27

SMBCLK

SMBDATA

SML0_SMBCLK

SML0_SMBDATA

I2C1_SCL_TCH_PAD

I2C1_SDA_TCH_PAD

GPU_THM_SMBCLK

GPU_THM_SMBDAT

1K

1K

499

499

4.7K

4.7K

+3VALW

+3V S

DMN65D8L

DMN65D8L

+3VALW

+3V S

+3V S

DMN66D0L

DMN66D0L

Host

MEC1416

Host

1K

1K

+3V S

PCH_SMBCLK

PCH_SMBDATA

499@

499

@

2.2K

2.2K

+3V S

+TP_ VD D

I2C_SCL_TP

I2C_SDA_TP

2.2K

@

2.2K

@

1211

9

8

9189

GPU_THM_SMBCLK

GPU_THM_SMBDAT

GPU_THM_SMBCLK

GPU_THM_SMBDAT

Host

+3VA LW_ EC

PBAT_CHG_SMBCLK

PBAT_CHG_SMBDAT

+3V S

DMN66D0L

DMN66D0L

ALL_ GPW RGD

DMN53D0L

DMN53D0L

@

@

4.7K

4.7K

10K

10K

Slave

253

254

Slave

253

254

Slave

1

4

Slave

Slave

8

7

DIMM1

DIMM2

FFS

Touch

Pad

2.2K

2.2K

1.8K

1.8K

+3VA LW_ EC

+3V S

Address: 0xA0/0xA1

Address: 0xA4/0xA5

Address: 0x52/0x53

Address: 0x2C/0x2D

+3V S

THM_SML1_CLK

THM_SML1_DATA

+1V8 _AO N

VGA_SMB_CK2

VGA_SMB_DA2

Slave

7

BATT

6

Slave

22

CHAGER

21

Slave

8

Thermal

7

Sensor

Address: 0x98/0x99

Slave

T4

GPU

T3

Address: 0x9E/0x9F

Address: 0x16/0x17

Address: 0x12/0x13

TYPEC_SMBCLK

TYPEC_SMBDA

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

For DELL review

5

4

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2017/01/06 2018/01/06

2017/01/06 2018/01/06

2017/01/06 2018/01/06

0 Ohm

0 Ohm

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

PD_I2C_SCL_R

PD_I2C_SDA_R

2

Slave

B5

TPS65982D

A5

Address: 0x70/0x71

Compal Electronics, Inc.

Title

Title

Title

SMBus Block Diagram

SMBus Block Diagram

SMBus Block Diagram

Size Document Numb er Re v

Size Document Numb er R ev

Size Document Numb er R ev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

LA-F611P

LA-F611P

LA-F611P

1

5 78Thursday, March 22, 20 18

5 78Thursday, March 22, 20 18

5 78Thursday, March 22, 20 18

0.3

0.3

0.3

A

Main Func = CPU

B

UC1

CFL_H@

C

D

E

1 1

CPU_DP1 _P041

CPU_DP1 _N041

CPU_DP1 _P141

CPU_DP1 _N141

CPU_DP1 _P241

TBT-AR

2 2

3 3

CPU_DP1 _N241

CPU_DP1 _P341

CPU_DP1 _N341

CPU_DP1 _AUXP41

CPU_DP1 _AUXN41

CPU_DP1 _P0

CPU_DP1 _N0

CPU_DP1 _P1

CPU_DP1 _N1

CPU_DP1 _P2

CPU_DP1 _N2

CPU_DP1 _P3

CPU_DP1 _N3

CPU_DP1 _AUXP

CPU_DP1 _AUXN

CFL-H_BGA1 440

SA011703151

UC1D

K36

DDI1_TXP_0

K37

DDI1_TXN_0

J35

DDI1_TXP_1

J34

DDI1_TXN_1

H37

DDI1_TXP_2

H36

DDI1_TXN_2

J37

DDI1_TXP_3

J38

DDI1_TXN_3

D27

DDI1_AUXP

E27

DDI1_AUXN

H34

DDI2_TXP_0

H33

DDI2_TXN_0

F37

DDI2_TXP_1

G38

DDI2_TXN_1

F34

DDI2_TXP_2

F35

DDI2_TXN_2

E37

DDI2_TXP_3

E36

DDI2_TXN_3

F26

DDI2_AUXP

E26

DDI2_AUXN

C34

DDI3_TXP_0

D34

DDI3_TXN_0

B36

DDI3_TXP_1

B34

DDI3_TXN_1

F33

DDI3_TXP_2

E33

DDI3_TXN_2

C33

DDI3_TXP_3

B33

DDI3_TXN_3

A27

DDI3_AUXP

B27

DDI3_AUXN

CFL-H_BG A1440

@

CFL_H_SOC

EDP_TXP_0

EDP_TXN_0

EDP_TXP_1

EDP_TXN_1

EDP_TXP_2

EDP_TXN_2

EDP_TXP_3

EDP_TXN_3

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

DISP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

4 of 13

D29

E29

F28

E28

A29

B29

C28

B28

C26

B26

A33

D37

EDP_TXP 0

EDP_TXN 0

EDP_TXP 1

EDP_TXN 1

EDP_AUX P

EDP_AUX N

EDP_DISP_ UTIL

DP_RCOM P

TC1 TP@

1 2

RC1 24.9_040 2_1%

DP_RCOMP

Trace width=5 mils

Spacing=20 mils

Max length= 600 mils

G27

G25

CPU_DISPA _SDI_C

G29

RC2 20_0402 _5%

12

EDP_TXP 0 29

EDP_TXN 0 29

EDP_TXP 1 29

EDP_TXN 1 29

EDP_AUX P 2 9

EDP_AUX N 29

CPU_DISPA _BCLK

CPU_DISPA _SDO

CPU_DISPA _SDI

eDP

+VCCIO

Check OK

CPU_DISPA _BCLK 18

CPU_DISPA _SDO 18

CPU_DISPA _SDI 18

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

For DELL review

A

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2016/01/ 06 2017/01/ 06

2016/01/ 06 2017/01/ 06

2016/01/ 06 2017/01/ 06

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet o f

Date : Sheet o f

D

Date : Sheet o f

Compal Electronics, Inc.

CFL-H(1/8)DDI/eDP

CFL-H(1/8)DDI/eDP

CFL-H(1/8)DDI/eDP

LA-F611P

LA-F611P

LA-F611P

E

0.3

0.3

0.3

6 7 8Thursday, March 22 , 2018

6 7 8Thursday, March 22 , 2018

6 7 8Thursday, March 22 , 2018

A

Main Func = CPU

B

C

D

E

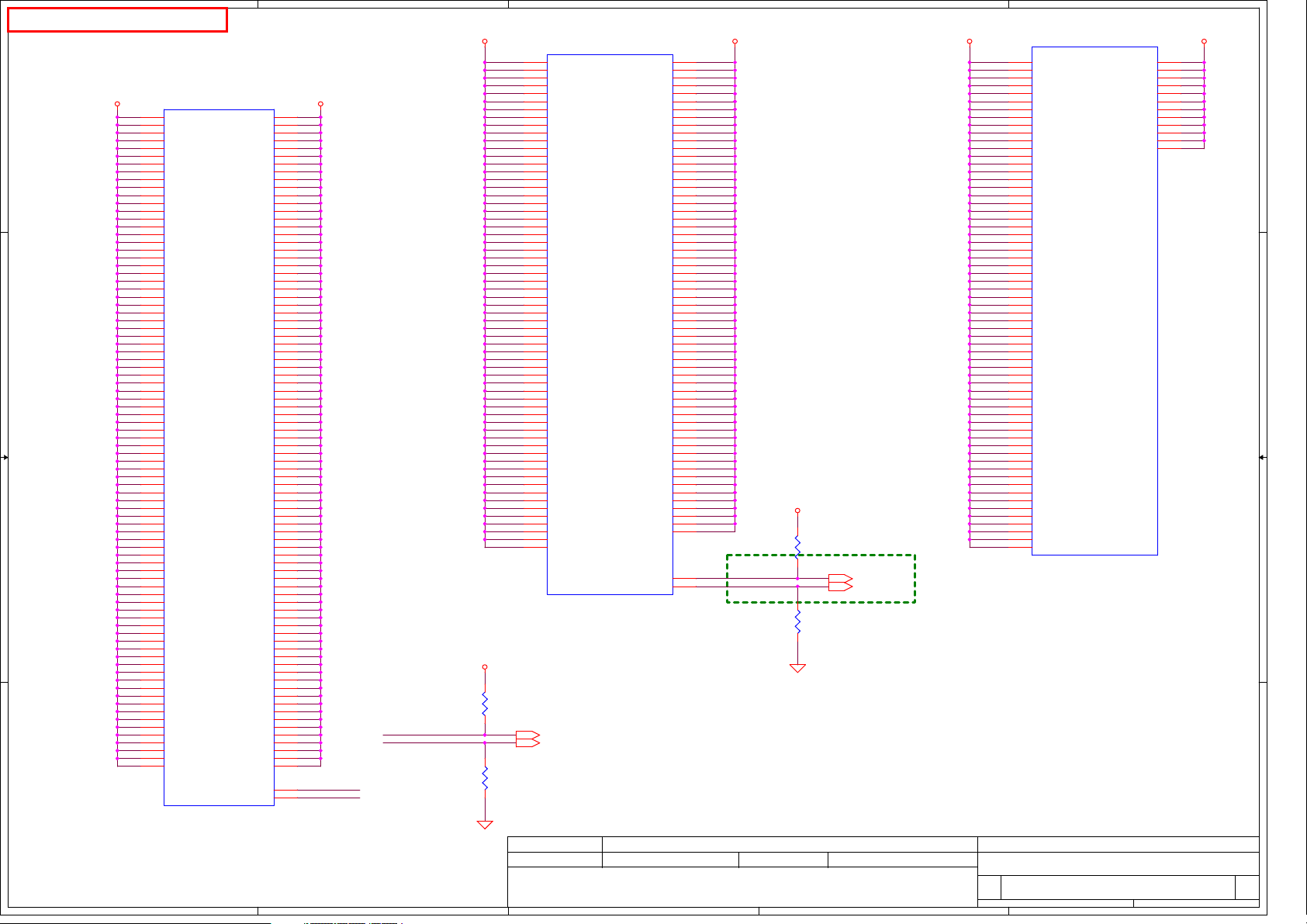

DDR_A_D [0..63]14

1 1

2 2

3 3

For ECC DIMM

DDR_A_D 0

DDR_A_D 1

DDR_A_D 2

DDR_A_D 3

DDR_A_D 4

DDR_A_D 5

DDR_A_D 6

DDR_A_D 7

DDR_A_D 8

DDR_A_D 9

DDR_A_D 10

DDR_A_D 11

DDR_A_D 12

DDR_A_D 13

DDR_A_D 14

DDR_A_D 15

DDR_A_D 16

DDR_A_D 17

DDR_A_D 18

DDR_A_D 19

DDR_A_D 20

DDR_A_D 21

DDR_A_D 22

DDR_A_D 23

DDR_A_D 24

DDR_A_D 25

DDR_A_D 26

DDR_A_D 27

DDR_A_D 28

DDR_A_D 29

DDR_A_D 30

DDR_A_D 31

DDR_A_D 32

DDR_A_D 33

DDR_A_D 34

DDR_A_D 35

DDR_A_D 36

DDR_A_D 37

DDR_A_D 38

DDR_A_D 39

DDR_A_D 40

DDR_A_D 41

DDR_A_D 42

DDR_A_D 43

DDR_A_D 44

DDR_A_D 45

DDR_A_D 46

DDR_A_D 47

DDR_A_D 48

DDR_A_D 49

DDR_A_D 50

DDR_A_D 51

DDR_A_D 52

DDR_A_D 53

DDR_A_D 54

DDR_A_D 55

DDR_A_D 56

DDR_A_D 57

DDR_A_D 58

DDR_A_D 59

DDR_A_D 60

DDR_A_D 61

DDR_A_D 62

DDR_A_D 63

TC4TP@

TC5TP@

TC6TP@

TC7TP@

TC8TP@

TC9TP@

TC10TP @

TC12TP @

UC1A

DDR4(IL)/LP3-DDR4(NIL)

BR6

DDR0_DQ_0/DDR0_DQ_0

BT6

DDR0_DQ_1/DDR0_DQ_1

BP3

DDR0_DQ_2/DDR0_DQ_2

BR3

DDR0_DQ_3/DDR0_DQ_3

BN5

DDR0_DQ_4/DDR0_DQ_4

BP6

DDR0_DQ_5/DDR0_DQ_5

BP2

DDR0_DQ_6/DDR0_DQ_6

BN3

DDR0_DQ_7/DDR0_DQ_7

BL4

DDR0_DQ_8/DDR0_DQ_8

BL5

DDR0_DQ_9/DDR0_DQ_9

BL2

DDR0_DQ_10/DDR0_DQ_10

BM1

DDR0_DQ_11/DDR0_DQ_11

BK4

DDR0_DQ_12/DDR0_DQ_12

BK5

DDR0_DQ_13/DDR0_DQ_13

BK1

DDR0_DQ_14/DDR0_DQ_14

BK2

DDR0_DQ_15/DDR0_DQ_15

BG4

DDR0_DQ_16/DDR0_DQ_32

BG5

DDR0_DQ_17/DDR0_DQ_33

BF4

DDR0_DQ_18/DDR0_DQ_34

BF5

DDR0_DQ_19/DDR0_DQ_35

BG2

DDR0_DQ_20/DDR0_DQ_36

BG1

DDR0_DQ_21/DDR0_DQ_37

BF1

DDR0_DQ_22/DDR0_DQ_38

BF2

DDR0_DQ_23/DDR0_DQ_39

BD2

DDR0_DQ_24/DDR0_DQ_40

BD1

DDR0_DQ_25/DDR0_DQ_41

BC4

DDR0_DQ_26/DDR0_DQ_42

BC5

DDR0_DQ_27/DDR0_DQ_43

BD5

DDR0_DQ_28/DDR0_DQ_44

BD4

DDR0_DQ_29/DDR0_DQ_45

BC1

DDR0_DQ_30/DDR0_DQ_46

BC2

DDR0_DQ_31/DDR0_DQ_47

AB1

DDR0_DQ_32/DDR1_DQ_0

AB2

DDR0_DQ_33/DDR1_DQ_1

AA4

DDR0_DQ_34/DDR1_DQ_2

AA5

DDR0_DQ_35/DDR1_DQ_3

AB5

DDR0_DQ_36/DDR1_DQ_4

AB4

DDR0_DQ_37/DDR1_DQ_5

AA2

DDR0_DQ_38/DDR1_DQ_6

AA1

DDR0_DQ_39/DDR1_DQ_7

V5

DDR0_DQ_40/DDR1_DQ_8

V2

DDR0_DQ_41/DDR1_DQ_9

U1

DDR0_DQ_42/DDR1_DQ_10

U2

DDR0_DQ_43/DDR1_DQ_11

V1

DDR0_DQ_44/DDR1_DQ_12

V4

DDR0_DQ_45/DDR1_DQ_13

U5

DDR0_DQ_46/DDR1_DQ_14

U4

DDR0_DQ_47/DDR1_DQ_15

R2

DDR0_DQ_48/DDR1_DQ_32

P5

DDR0_DQ_49/DDR1_DQ_33

R4

DDR0_DQ_50/DDR1_DQ_34

P4

DDR0_DQ_51/DDR1_DQ_35

R5

DDR0_DQ_52/DDR1_DQ_36

P2

DDR0_DQ_53/DDR1_DQ_37

R1

DDR0_DQ_54/DDR1_DQ_38

P1

DDR0_DQ_55/DDR1_DQ_39

M4

DDR0_DQ_56/DDR1_DQ_40

M1

DDR0_DQ_57/DDR1_DQ_41

L4

DDR0_DQ_58/DDR1_DQ_42

L2

DDR0_DQ_59/DDR1_DQ_43

M5

DDR0_DQ_60/DDR1_DQ_44

M2

DDR0_DQ_61/DDR1_DQ_45

L5

DDR0_DQ_62/DDR1_DQ_46

L1

DDR0_DQ_63/DDR1_DQ_47

LP3/DDR4

BA2

NC/DDR0_ECC_0

BA1

NC/DDR0_ECC_1

AY4

NC/DDR0_ECC_2

AY5

NC/DDR0_ECC_3

BA5

NC/DDR0_ECC_4

BA4

NC/DDR0_ECC_5

AY1

NC/DDR0_ECC_6

AY2

NC/DDR0_ECC_7

CFL-H_BG A1440

CFL_H_SOC

DDRCHANNELA

DDR0_CKP_0/DDR0_CKP_0

DDR0_CKN_0/DDR0_CKN_0

DDR0_CKP_1/DDR0_CKP_1

DDR0_CKN_1/DDR0_CKN_1

NC/DDR0_CKP_2

NC/DDR0_CKN_2

NC/DDR0_CKP_3

NC/DDR0_CKN_3

DDR0_CKE_0/DDR0_CKE_0

DDR0_CKE_1/DDR0_CKE_1

DDR0_CKE_2/DDR0_CKE_2

DDR0_CKE_3/DDR0_CKE_3

DDR0_CS#_0/DDR0_CS#_0

DDR0_CS#_1/DDR0_CS#_1

NC/DDR0_CS#_2

NC/DDR0_CS#_3

DDR0_ODT_0/DDR0_ODT_0

NC/DDR0_ODT_1

NC/DDR0_ODT_2

NC/DDR0_ODT_3

DDR0_CAB_4/DDR0_BA_0

DDR0_CAB_6/DDR0_BA_1

DDR0_CAA_5/DDR0_BG_0

DDR0_CAB_3/DDR0_MA_16

DDR0_CAB_2/DDR0_MA_14

DDR0_CAB_1/DDR0_MA_15

DDR0_CAB_9/DDR0_MA_0

DDR0_CAB_8/DDR0_MA_1

DDR0_CAB_5/DDR0_MA_2

NC/DDR0_MA_3

NC/DDR0_MA_4

DDR0_CAA_0/DDR0_MA_5

DDR0_CAA_2/DDR0_MA_6

DDR0_CAA_4/DDR0_MA_7

DDR0_CAA_3/DDR0_MA_8

DDR0_CAA_1/DDR0_MA_9

DDR0_CAB_7/DDR0_MA_10

DDR0_CAA_7/DDR0_MA_11

DDR0_CAA_6/DDR0_MA_12

DDR0_CAB_0/DDR0_MA_13

DDR0_CAA_9/DDR0_BG_1

DDR0_CAA_8/DDR0_ACT#

NC/DDR0_PAR

NC/DDR0_ALERT#

DDR4(IL)/LP3-DDR4(NIL)

DDR0_DQSN_0/DDR0_DQSN_0

DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSN_2/DDR0_DQSN_4

DDR0_DQSN_3/DDR0_DQSN_5

DDR0_DQSN_4/DDR1_DQSN_0

DDR0_DQSN_5/DDR1_DQSN_1

DDR0_DQSN_6/DDR1_DQSN_4

DDR0_DQSN_7/DDR1_DQSN_5

DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSP_2/DDR0_DQSP_4

DDR0_DQSP_3/DDR0_DQSP_5

DDR0_DQSP_4/DDR1_DQSP_0

DDR0_DQSP_5/DDR1_DQSP_1

DDR0_DQSP_6/DDR1_DQSP_4

DDR0_DQSP_7/DDR1_DQSP_5

DDR0_DQSP_8/DDR0_DQSP_8

1OF13

DDR0_DQSN_8/DDR0_DQSN_8

LP3/DDR4

AG1

AG2

AK2

AK1

AL3

AK3

AL2

AL1

AT1

AT2

AT3

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

AH5

AH1

AU1

AH4

AG4

AD1

AH3

AP4

AN4

AP5

AP2

AP1

AP3

AN1

AN3

AT4

AH2

AN2

AU4

AE3

AU2

AU3

AG3

AU5

BR5

BL3

BG3

BD3

AA3

U3

P3

L3

BP5

BK3

BF3

BC3

AB3

V3

R3

M3

AY3

BA3

DDR_A_C LK0

DDR_A_C LK#0

DDR_A_C LK1

DDR_A_C LK#1

DDR_A_C KE0

DDR_A_C KE1

DDR_A_C S#0

DDR_A_C S#1

DDR_A_O DT0

DDR_A_O DT1

DDR_A_B A0

DDR_A_B A1

DDR_A_B G0

DDR_A_M A16_RAS#

DDR_A_M A14_WE#

DDR_A_M A15_CAS#

DDR_A_M A0

DDR_A_M A1

DDR_A_M A2

DDR_A_M A3

DDR_A_M A4

DDR_A_M A5

DDR_A_M A6

DDR_A_M A7

DDR_A_M A8

DDR_A_M A9

DDR_A_M A10

DDR_A_M A11

DDR_A_M A12

DDR_A_M A13

DDR_A_B G1

DDR_A_A CT#

DDR_A_P AR

DDR_A_A LERT#

DDR_A_D QS#0

DDR_A_D QS#1

DDR_A_D QS#2

DDR_A_D QS#3

DDR_A_D QS#4

DDR_A_D QS#5

DDR_A_D QS#6

DDR_A_D QS#7

DDR_A_D QS0

DDR_A_D QS1

DDR_A_D QS2

DDR_A_D QS3

DDR_A_D QS4

DDR_A_D QS5

DDR_A_D QS6

DDR_A_D QS7

TC11 TP@

TC13 TP@

DDR_A_C LK0 14

DDR_A_C LK#0 14

DDR_A_C LK1 14

DDR_A_C LK#1 14

DDR_A_C KE0 14

DDR_A_C KE1 14

DDR_A_C S#0 14

DDR_A_C S#1 14

DDR_A_O DT0 14

DDR_A_O DT1 14

DDR_A_B A0 1 4

DDR_A_B A1 1 4

DDR_A_B G0 1 4

DDR_A_M A16_RAS# 14

DDR_A_M A14_WE# 14

DDR_A_M A15_CAS# 14

DDR_A_M A0 14

DDR_A_M A1 14

DDR_A_M A2 14

DDR_A_M A3 14

DDR_A_M A4 14

DDR_A_M A5 14

DDR_A_M A6 14

DDR_A_M A7 14

DDR_A_M A8 14

DDR_A_M A9 14

DDR_A_M A10 14

DDR_A_M A11 14

DDR_A_M A12 14

DDR_A_M A13 14

DDR_A_B G1 1 4

DDR_A_A CT# 14

DDR_A_P AR 14

DDR_A_A LERT# 14

DDR_A_D QS#0 14

DDR_A_D QS#1 14

DDR_A_D QS#2 14

DDR_A_D QS#3 14

DDR_A_D QS#4 14

DDR_A_D QS#5 14

DDR_A_D QS#6 14

DDR_A_D QS#7 14

DDR_A_D QS0 14

DDR_A_D QS1 14

DDR_A_D QS2 14

DDR_A_D QS3 14

DDR_A_D QS4 14

DDR_A_D QS5 14

DDR_A_D QS6 14

DDR_A_D QS7 14

For ECC DIMM

4 4

Security Classification

Security Classification

Security Classification

2016/01/ 06 2017/01/ 06

2016/01/ 06 2017/01/ 06

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

For DELL review

A

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2016/01/ 06 2017/01/ 06

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet o f

Date : Sheet o f

D

Date : Sheet o f

Compal Electronics, Inc.

CFL-H(2/8)DIMMA

CFL-H(2/8)DIMMA

CFL-H(2/8)DIMMA

LA-F611P

LA-F611P

LA-F611P

0.3

0.3

0.3

7 7 8Thursday, March 22 , 2018

7 7 8Thursday, March 22 , 2018

7 7 8Thursday, March 22 , 2018

E

A

Main Func = CPU

B

C

D

E

DDR_B_D [0..63]15

DDR_B_D 0

DDR_B_D 1

DDR_B_D 2

DDR_B_D 3

DDR_B_D 4

DDR_B_D 5

TC14TP @

TC15TP @

TC16TP @

TC17TP @

TC18TP @

TC19TP @

TC20TP @

TC22TP @

DDR_B_D 6

DDR_B_D 7

DDR_B_D 8

DDR_B_D 9

DDR_B_D 10

DDR_B_D 11

DDR_B_D 12

DDR_B_D 13

DDR_B_D 14

DDR_B_D 15

DDR_B_D 16

DDR_B_D 17

DDR_B_D 18

DDR_B_D 19

DDR_B_D 20

DDR_B_D 21

DDR_B_D 22

DDR_B_D 23

DDR_B_D 24

DDR_B_D 25

DDR_B_D 26

DDR_B_D 27

DDR_B_D 28

DDR_B_D 29

DDR_B_D 30

DDR_B_D 31

DDR_B_D 32

DDR_B_D 33

DDR_B_D 34

DDR_B_D 35

DDR_B_D 36

DDR_B_D 37

DDR_B_D 38

DDR_B_D 39

DDR_B_D 40

DDR_B_D 41

DDR_B_D 42

DDR_B_D 43

DDR_B_D 44

DDR_B_D 45

DDR_B_D 46

DDR_B_D 47

DDR_B_D 48

DDR_B_D 49

DDR_B_D 50

DDR_B_D 51

DDR_B_D 52

DDR_B_D 53

DDR_B_D 54

DDR_B_D 55

DDR_B_D 56

DDR_B_D 57

DDR_B_D 58

DDR_B_D 59

DDR_B_D 60

DDR_B_D 61

DDR_B_D 62

DDR_B_D 63

1 1

2 2

3 3

For ECC DIMM

UC1B

DDR4(IL)/LP3-DDR4(NIL)

BT11

DDR1_DQ_0/DDR0_DQ_16

BR11

DDR1_DQ_1/DDR0_DQ_17

BT9

DDR1_DQ_2/DDR0_DQ_18

BR8

DDR1_DQ_3/DDR0_DQ_19

BP11

DDR1_DQ_4/DDR0_DQ_20

BN11

DDR1_DQ_5/DDR0_DQ_21

BP8

DDR1_DQ_6/DDR0_DQ_22

BN8

DDR1_DQ_7/DDR0_DQ_23

BL12

DDR1_DQ_8/DDR0_DQ_24

BL11

DDR1_DQ_9/DDR0_DQ_25

BL8

DDR1_DQ_10/DDR0_DQ_26

BJ8

DDR1_DQ_11/DDR0_DQ_27

BJ11

DDR1_DQ_12/DDR0_DQ_28

BJ10

DDR1_DQ_13/DDR0_DQ_29

BL7

DDR1_DQ_14/DDR0_DQ_30

BJ7

DDR1_DQ_15/DDR0_DQ_31

BG11

DDR1_DQ_16/DDR0_DQ_48

BG10

DDR1_DQ_17/DDR0_DQ_49

BG8

DDR1_DQ_18/DDR0_DQ_50

BF8

DDR1_DQ_19/DDR0_DQ_51

BF11

DDR1_DQ_20/DDR0_DQ_52

BF10

DDR1_DQ_21/DDR0_DQ_53

BG7

DDR1_DQ_22/DDR0_DQ_54

BF7

DDR1_DQ_23/DDR0_DQ_55

BB11

DDR1_DQ_24/DDR0_DQ_56

BC11

DDR1_DQ_25/DDR0_DQ_57

BB8

DDR1_DQ_26/DDR0_DQ_58

BC8

DDR1_DQ_27/DDR0_DQ_59

BC10

DDR1_DQ_28/DDR0_DQ_60

BB10

DDR1_DQ_29/DDR0_DQ_61

BC7

DDR1_DQ_30/DDR0_DQ_62

BB7

DDR1_DQ_31/DDR0_DQ_63

AA11

DDR1_DQ_32/DDR1_DQ_16

AA10

DDR1_DQ_33/DDR1_DQ_17

AC11

DDR1_DQ_34/DDR1_DQ_18

AC10

DDR1_DQ_35/DDR1_DQ_19

AA7

DDR1_DQ_36/DDR1_DQ_20

AA8

DDR1_DQ_37/DDR1_DQ_21

AC8

DDR1_DQ_38/DDR1_DQ_22

AC7

DDR1_DQ_39/DDR1_DQ_23

DDR4(IL)/LP3-DDR4(NIL)

W8

DDR1_DQ_40/DDR1_DQ_24

W7

DDR1_DQ_41/DDR1_DQ_25

V10

DDR1_DQ_42/DDR1_DQ_26

V11

DDR1_DQ_43/DDR1_DQ_27

W11

DDR1_DQ_44/DDR1_DQ_28

W10

DDR1_DQ_45/DDR1_DQ_29

V7

DDR1_DQ_46/DDR1_DQ_30

V8

DDR1_DQ_47/DDR1_DQ_31

R11

DDR1_DQ_48/DDR1_DQ_48

P11

DDR1_DQ_49/DDR1_DQ_49

P7

DDR1_DQ_50/DDR1_DQ_50

R8

DDR1_DQ_51/DDR1_DQ_51

R10

DDR1_DQ_52/DDR1_DQ_52

P10

DDR1_DQ_53/DDR1_DQ_53

R7

DDR1_DQ_54/DDR1_DQ_54

P8

DDR1_DQ_55/DDR1_DQ_55

L11

DDR1_DQ_56/DDR1_DQ_56

M11

DDR1_DQ_57/DDR1_DQ_57

L7

DDR1_DQ_58/DDR1_DQ_58

M8

DDR1_DQ_59/DDR1_DQ_59

L10

DDR1_DQ_60/DDR1_DQ_60

M10

DDR1_DQ_61/DDR1_DQ_61

M7

DDR1_DQ_62/DDR1_DQ_62

L8

DDR1_DQ_63/DDR1_DQ_63

LP3/DDR4

AW11

NC/DDR1_ECC_0

AY11

NC/DDR1_ECC_1

AY8

NC/DDR1_ECC_2

AW8

NC/DDR1_ECC_3

AY10

NC/DDR1_ECC_4

AW10

NC/DDR1_ECC_5

AY7

NC/DDR1_ECC_6

AW7

NC/DDR1_ECC_7

CFL_H_SOC

DDRCHANNELB

DDR1_CKP_0/DDR1_CKP_0

DDR1_CKN_0/DDR1_CKN_0

DDR1_CKP_1/DDR1_CKP_1

DDR1_CKN_1/DDR1_CKN_1

NC/DDR1_CKP_2

NC/DDR1_CKN_2

NC/DDR1_CKP_3

NC/DDR1_CKN_3

DDR1_CKE_0/DDR1_CKE_0

DDR1_CKE_1/DDR1_CKE_1

DDR1_CKE_2/DDR1_CKE_2

DDR1_CKE_3/DDR1_CKE_3

DDR1_CS#_0/DDR1_CS#_0

DDR1_CS#_1/DDR1_CS#_1

NC/DDR1_CS#_2

NC/DDR1_CS#_3

DDR1_ODT_0/DDR1_ODT_0

NC/DDR1_ODT_1

NC/DDR1_ODT_2

NC/DDR1_ODT_3

DDR1_CAB_3/DDR1_MA_16

DDR1_CAB_2/DDR1_MA_14

DDR1_CAB_1/DDR1_MA_15

DDR1_CAB_4/DDR1_BA_0

DDR1_CAB_6/DDR1_BA_1

DDR1_CAA_5/DDR1_BG_0

DDR1_CAB_9/DDR1_MA_0

DDR1_CAB_8/DDR1_MA_1

DDR1_CAB_5/DDR1_MA_2

NC/DDR1_MA_3

NC/DDR1_MA_4

DDR1_CAA_0/DDR1_MA_5

DDR1_CAA_2/DDR1_MA_6

DDR1_CAA_4/DDR1_MA_7

DDR1_CAA_3/DDR1_MA_8

DDR1_CAA_1/DDR1_MA_9

DDR1_CAB_7/DDR1_MA_10

DDR1_CAA_7/DDR1_MA_11

DDR1_CAA_6/DDR1_MA_12

DDR1_CAB_0/DDR1_MA_13

DDR1_CAA_9/DDR1_BG_1

DDR1_CAA_8/DDR1_ACT#

NC/DDR1_PAR

NC/DDR1_ALERT#

DDR4(IL)/LP3-DDR4(NIL)

DDR1_DQSN_0/DDR0_DQSN_2

DDR1_DQSN_1/DDR0_DQSN_3

DDR1_DQSN_2/DDR0_DQSN_6

DDR1_DQSN_3/DDR0_DQSN_7

DDR1_DQSN_4/DDR1_DQSN_2

DDR1_DQSN_5/DDR1_DQSN_3

DDR1_DQSN_6/DDR1_DQSN_6

DDR1_DQSN_7/DDR1_DQSN_7

DDR1_DQSP_0/DDR0_DQSP_2

DDR1_DQSP_1/DDR0_DQSP_3

DDR1_DQSP_2/DDR0_DQSP_6

DDR1_DQSP_3/DDR0_DQSP_7

DDR1_DQSP_4/DDR1_DQSP_2

DDR1_DQSP_5/DDR1_DQSP_3

DDR1_DQSP_6/DDR1_DQSP_6

DDR1_DQSP_7/DDR1_DQSP_7

DDR1_DQSP_8/DDR1_DQSP_8

DDR1_DQSN_8/DDR1_DQSN_8

LP3/DDR4

AM9

AN9

AM7

AM8

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

AJ9

AK6

AK5

AL5

AL6

AM6

AN7

AN10

AN8

AR11

AH7

AN11

AR10

AF9

AR7

AT9

AJ7

AR8

BN9

BL9

BG9

BC9

AC9

W9

R9

M9

BP9

BJ9

BF9

BB9

AA9

V9

P9

L9

AW9

AY9

DDR_B_C LK0

DDR_B_C LK#0

DDR_B_C LK1

DDR_B_C LK#1

DDR_B_C KE0

DDR_B_C KE1

DDR_B_C S#0

DDR_B_C S#1

DDR_B_O DT0

DDR_B_O DT1

DDR_B_M A16_RAS#

DDR_B_M A14_WE#

DDR_B_M A15_CAS#

DDR_B_B A0

DDR_B_B A1

DDR_B_B G0

DDR_B_M A0

DDR_B_M A1

DDR_B_M A2

DDR_B_M A3

DDR_B_M A4

DDR_B_M A5

DDR_B_M A6

DDR_B_M A7

DDR_B_M A8

DDR_B_M A9

DDR_B_M A10

DDR_B_M A11

DDR_B_M A12

DDR_B_M A13

DDR_B_B G1

DDR_B_A CT#

DDR_B_P AR

DDR_B_A LERT#

DDR_B_D QS#0

DDR_B_D QS#1

DDR_B_D QS#2

DDR_B_D QS#3

DDR_B_D QS#4

DDR_B_D QS#5

DDR_B_D QS#6

DDR_B_D QS#7

DDR_B_D QS0

DDR_B_D QS1

DDR_B_D QS2

DDR_B_D QS3

DDR_B_D QS4

DDR_B_D QS5

DDR_B_D QS6

DDR_B_D QS7

TC21 TP@

TC23 TP@

DDR_B_C LK0 15

DDR_B_C LK#0 15

DDR_B_C LK1 15

DDR_B_C LK#1 15

DDR_B_C KE0 15

DDR_B_C KE1 15

DDR_B_C S#0 15

DDR_B_C S#1 15

DDR_B_O DT0 15

DDR_B_O DT1 15

DDR_B_M A16_RAS# 15

DDR_B_M A14_WE# 15

DDR_B_M A15_CAS# 15

DDR_B_B A0 1 5

DDR_B_B A1 1 5

DDR_B_B G0 1 5

DDR_B_M A0 15

DDR_B_M A1 15

DDR_B_M A2 15

DDR_B_M A3 15

DDR_B_M A4 15

DDR_B_M A5 15

DDR_B_M A6 15

DDR_B_M A7 15

DDR_B_M A8 15

DDR_B_M A9 15

DDR_B_M A10 15

DDR_B_M A11 15

DDR_B_M A12 15

DDR_B_M A13 15

DDR_B_B G1 1 5

DDR_B_A CT# 15

DDR_B_P AR 15

DDR_B_A LERT# 15

DDR_B_D QS#0 15

DDR_B_D QS#1 15

DDR_B_D QS#2 15

DDR_B_D QS#3 15

DDR_B_D QS#4 15

DDR_B_D QS#5 15

DDR_B_D QS#6 15

DDR_B_D QS#7 15

DDR_B_D QS0 15

DDR_B_D QS1 15

DDR_B_D QS2 15

DDR_B_D QS3 15

DDR_B_D QS4 15

DDR_B_D QS5 15

DDR_B_D QS6 15

DDR_B_D QS7 15

For ECC DIMM

1 2

RC3 1 21_0402_1%

1 2

RC4 75_0402 _1%

1 2

RC5 100_040 2_1%

Trace Width/Space: 15 mil/ 25 mil

Max Trace Length: 500 mil

4 4

For DELL review

A

B

SM_RCOM P0

SM_RCOM P1

SM_RCOM P2

G1

DDR_RCOMP_0

H1

DDR_RCOMP_1

J2

DDR_RCOMP_2

CFL-H_BG A1440

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2OF13

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

2016/01/ 06 2017/01/ 06

2016/01/ 06 2017/01/ 06

2016/01/ 06 2017/01/ 06

C

+V_DDR_ REFA_R

BN13

BP13

+V_DDR_ REFB_R

BR13

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

TC111TP@

+V_DDR_ REFA_R

+V_DDR_ REFB_R

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

Compal Electronics, Inc.

CFL-H(3/8)DIMMB

CFL-H(3/8)DIMMB

CFL-H(3/8)DIMMB

LA-F611P

LA-F611P

LA-F611P

8 7 8Thursday, March 22 , 2018

8 7 8Thursday, March 22 , 2018

8 7 8Thursday, March 22 , 2018

E

0.3

0.3

0.3

A

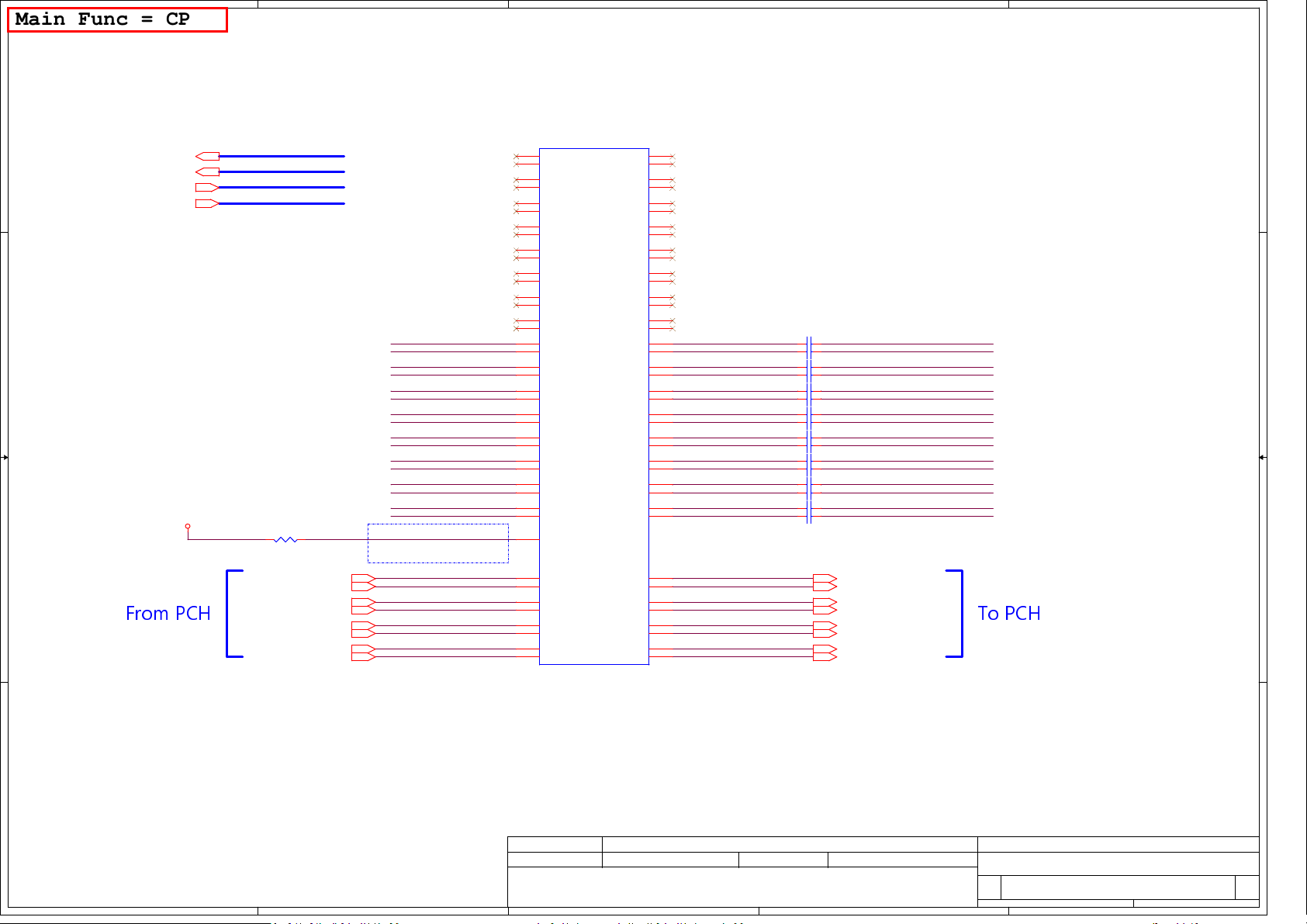

Main Func = CPU

B

C

D

E

1 1

PEG_CTX _C_GRX_P[0..7]48

PEG_CTX _C_GRX_N[0..7]48

PEG_CRX _GTX_P[0..7]48

PEG_CRX _GTX_N[0..7]48

2 2

+VCCIO

3 3

From PCH To PCH

PEG_CTX _C_GRX_P[0..7]

PEG_CTX _C_GRX_N[0..7]

PEG_CRX _GTX_P[0..7]

PEG_CRX _GTX_N[0..7]

1 2

RC9 24.9_040 2_1%

DMI_CRX_P TX_P019

DMI_CRX_P TX_N019

DMI_CRX_P TX_P119

DMI_CRX_P TX_N119

DMI_CRX_P TX_P219

DMI_CRX_P TX_N219

DMI_CRX_P TX_P319

DMI_CRX_P TX_N319

PEG_CRX _GTX_P7

PEG_CRX _GTX_N7

PEG_CRX _GTX_P6

PEG_CRX _GTX_N6

PEG_CRX _GTX_P5

PEG_CRX _GTX_N5

PEG_CRX _GTX_P4

PEG_CRX _GTX_N4

PEG_CRX _GTX_P3

PEG_CRX _GTX_N3

PEG_CRX _GTX_P2

PEG_CRX _GTX_N2

PEG_CRX _GTX_P1

PEG_CRX _GTX_N1

PEG_CRX _GTX_P0

PEG_CRX _GTX_N0

PEG_RCO MP

Trace Width/Space: 15 mil/ 15 mil

Max Trace Length: 600 mil

DMI_CRX_P TX_P0

DMI_CRX_P TX_N0

DMI_CRX_P TX_P1

DMI_CRX_P TX_N1

DMI_CRX_P TX_P2

DMI_CRX_P TX_N2

DMI_CRX_P TX_P3

DMI_CRX_P TX_N3

E25

D25

E24

F24

E23

D23

E22

F22

E21

D21

E20

F20

E19

D19

E18

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

D11

E11

F10

E10

G2

D8

E8

E6

F6

D5

E5

J8

J9

PEG_RCOMP

CFL_H_SOC

UC1C

PEG_RXP_0

PEG_RXN_0

PEG_RXP_1

PEG_RXN_1

PEG_RXP_2

PEG_RXN_2

PEG_RXP_3

PEG_RXN_3

PEG_RXP_4

PEG_RXN_4

PEG_RXP_5

PEG_RXN_5

PEG_RXP_6

PEG_RXN_6

PEG_RXP_7

PEG_RXN_7

PEG_RXP_8

PEG_RXN_8

PEG_RXP_9

PEG_RXN_9

PEG_RXP_10

PEG_RXN_10

PEG_RXP_11

PEG_RXN_11

PEG_RXP_12

PEG_RXN_12

PEG_RXP_13

PEG_RXN_13

PEG_RXP_14

PEG_RXN_14

PEG_RXP_15

PEG_RXN_15

PEG_RCOMP

DMI_RXP_0

DMI_RXN_0

DMI_RXP_1

DMI_RXN_1

DMI_RXP_2

DMI_RXN_2

DMI_RXP_3

DMI_RXN_3

CFL-H_BG A1440

@

PEG_TXP_10

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

3OF13

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

B25

A25

B24

C24

B23

A23

B22

C22

B21

A21

B20

C20

B19

A19

B18

C18

PEG_CTX _GRX_P7

A17

PEG_CTX _GRX_N7

B17

PEG_CTX _GRX_P6

C16

PEG_CTX _GRX_N6 PEG_CTX _C_GRX_N6

B16

PEG_CTX _GRX_P5

A15

PEG_CTX _GRX_N5 PEG_CTX _C_GRX_N5

B15

PEG_CTX _GRX_P4 PEG_C TX_C_GRX_P4

C14

PEG_CTX _GRX_N4

B14

PEG_CTX _GRX_P3

A13

PEG_CTX _GRX_N3

B13

PEG_CTX _GRX_P2

C12

PEG_CTX _GRX_N2 PEG_CTX _C_GRX_N2

B12

PEG_CTX _GRX_P1

A11

PEG_CTX _GRX_N1

B11

PEG_CTX _GRX_P0

C10

PEG_CTX _GRX_N0 PEG_CTX _C_GRX_N0

B10

B8

A8

C6

B6

B5

A5

D4

B4

DMI_CTX_P RX_P0

DMI_CTX_P RX_N0

DMI_CTX_P RX_P1

DMI_CTX_P RX_N1

DMI_CTX_P RX_P2

DMI_CTX_P RX_N2

DMI_CTX_P RX_P3

DMI_CTX_P RX_N3

1 2

CC15 0.22U_02 01_6.3V6M

1 2

CC16 0.22U_02 01_6.3V6M

1 2

CC13 0.22U_02 01_6.3V6M

1 2

CC14 0.22U_02 01_6.3V6M

1 2

CC11 0.22U_02 01_6.3V6M

1 2

CC12 0.22U_02 01_6.3V6M

1 2

CC9 0.22U_0201 _6.3V6M

1 2

CC10 0.22U_02 01_6.3V6M

1 2

CC7 0.22U_0201 _6.3V6M

1 2

CC8 0.22U_0201 _6.3V6M

1 2

CC5 0.22U_0201 _6.3V6M

1 2

CC6 0.22U_0201 _6.3V6M

1 2

CC3 0.22U_0201 _6.3V6M

1 2

CC4 0.22U_0201 _6.3V6M

1 2

CC1 0.22U_0201 _6.3V6M

1 2

CC2 0.22U_0201 _6.3V6M

DMI_CTX_P RX_P0 19

DMI_CTX_P RX_N0 19

DMI_CTX_P RX_P1 19

DMI_CTX_P RX_N1 19

DMI_CTX_P RX_P2 19

DMI_CTX_P RX_N2 19

DMI_CTX_P RX_P3 19

DMI_CTX_P RX_N3 19

PEG_CTX _C_GRX_P7

PEG_CTX _C_GRX_N7

PEG_CTX _C_GRX_P6

PEG_CTX _C_GRX_P5

PEG_CTX _C_GRX_N4

PEG_CTX _C_GRX_P3

PEG_CTX _C_GRX_N3

PEG_CTX _C_GRX_P2

PEG_CTX _C_GRX_P1

PEG_CTX _C_GRX_N1

PEG_CTX _C_GRX_P0

Trace width=15 mils

Spacing=15 mils

Max length= 600 mils

4 4

Security Classification

Security Classification

Security Classification

2016/01/ 06 2017/01/ 06

2016/01/ 06 2017/01/ 06

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

For DELL review

A

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2016/01/ 06 2017/01/ 06

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet o f

Date : Sheet o f

D

Date : Sheet o f

Compal Electronics, Inc.

CFL-H(4/8)PEG

CFL-H(4/8)PEG

CFL-H(4/8)PEG

LA-F611P

LA-F611P

LA-F611P

0.3

0.3

0.3

9 7 8Thursday, March 22 , 2018

9 7 8Thursday, March 22 , 2018

9 7 8Thursday, March 22 , 2018

E

A

Main Func = CPU

1 1

VR_SVID_A LERT#67

VR_SVID_C LK67

VR_SVID_D ATA67

H_PROCH OT#26,59,61,6 7

H_VCCST _PWRGD18

H_CPUPW RGD18

H_PLTRS T_CPU#16

H_PM_SYNC _R16

H_PM_DO WN16

PECI_EC16,26

H_THERM TRIP#16

PROC_DE TECT#16

2 2

+VCCST

H_VCCST _PWRGD

H_THERM TRIP#

XDP_PRE Q#

CATERR#

VR_SVID_D ATA

VR_SVID_A LERT#

1 2

1 2

1 2

1 2

12

12

RC20 1K_0 402_5%

RC46 1K_0 402_5%

RC259 51_0402 _5%@

RC263 49.9_040 2_1%@

RC260 100_040 2_1%

RC261 56.2_040 2_1%

+VCCSTG

3 3

1 2

RC262 1K_0402 _5%

H_PROCH OT#

VR_SVID_A LERT# VR_SVID_A LERT#_R

VR_SVID_D ATA

H_PROCH OT#

PROC_DE TECT#

B

PCH_CPU _BCLK_P17

PCH_CPU _BCLK_N17

PCH_CPU _PCIBCLK_P17

PCH_CPU _PCIBCLK_N17

CPU_24M HZ_P17

CPU_24M HZ_N17

1 2

RC267 220_040 2_5%

1 2

RC268 499_040 2_1%

1 2

RC269 60.4_0 402_1%

1 2

RC22 20_0402 _5%

1 2

RC44 0_0201_ 5%

1 2

RC45 0_0201_ 5%

1 2

RC277 0_040 2_5%@

< VDDQ_VTT_EN >

SM_PG_C TRL63

+3VS

C

CFL_H_SOC

UC1E

PCH_CPU _BCLK_P

PCH_CPU _BCLK_N

PCH_CPU _PCIBCLK_P

PCH_CPU _PCIBCLK_N

CPU_24M HZ_P

CPU_24M HZ_N

DDR_VTT _PG_CTRL

< OUT >

VCCST_P WRGD_CPUH_VCCST _PWRGD

H_CPUPW RGD

H_PLTRS T_CPU#

H_PM_SYNC _R

H_PM_DO WN_RH_PM_DO WN

PECI_EC_RPECI_EC

H_THERM TRIP#_CH_THERM TRIP#

TC97TP@

TC96TP@

TC94TP@

TC95TP@

PROC_SE LECT#

CATERR#

H_PROCH OT#_R

D35

C36

D31

BH31

BH32

BH29

BR30

BT13

BT31

BP35

BM34

BP31

BT34

BR33

BN1

BM30

AT13

AW13

AU13

AY13

B31

A32

E31

H13

J31

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

VCCST_PWRGD

PROCPWRGD

RESET#

PM_SYNC

PM_DOWN

PECI

THERMTRIP#

SKTOCC#

PROC_SELECT#

CATERR#

ZVM#

MSM#

RSVD1

RSVD2

CFL-H_BG A1440

@

5 OF13

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_17

CFG_16

CFG_19

CFG_18

BPM#_0

BPM#_1

BPM#_2

BPM#_3

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

+1.2V_DDR

12

CH197 0.1U_ 0402_10V7K

1 2

RC270 330 K_0402_5%

SA00007WE00 (S IC 74AUP1G07SE-7 SOT353 5P LOW PW BUFF) _DIODES

SA00005U600 (S IC 74AUP1G07GW TSSOP 5P BUFFER) _NXP

UC10

5

4

74AUP1G 07GW_TSSO P5

MAIN@

VCC

Y

NC

GND

1

2

A

3

BN25

BN27

BN26

BN28

BR20

BM20

BT20

BP20

BR23

BR22

BT23

BT22

BM19

BR19

BP19

BT19

BN23

BP23

BP22

BN22

BR27

BT27

BM31

BT30

BT28

BL32

BP28

BR28

BP30

BL30

BP27

BT25

< IN >

DDR_VTT _PG_CTRL

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG17

CFG16

CFG19

CFG18

XDP_BPM #0

XDP_BPM #1

XDP_BPM #2

XDP_BPM #3

CPU_XDP _TDO

CPU_XDP _TDI

CPU_XDP _TMS

CPU_XDP _TCK0

CPU_XDP _TRST#

XDP_PRE Q#

XDP_PRD Y#

CFG_RCO MP

Trace Width/Space: 4 mil/ 12 mil

Max Trace Length: 600 mil

TC98 TP@

TC99 TP@

TC101TP@

TC100TP@

12

RC19

49.9_040 2_1%

D

CFG0 38

CFG1 38

CFG2 38

CFG3 38

CFG4 38

CFG5 38

CFG6 38

CFG7 38

CFG8 38

CFG9 38

CFG10 38

CFG11 38

CFG12 38

CFG13 38

CFG14 38

CFG15 38

CFG17 38

CFG16 38

CFG19 38

CFG18 38

CPU_XDP _TDO 18,38

CPU_XDP_TDI 18,38

CPU_XDP_TMS 18,38

CPU_XDP_TCK0 18,38

CPU_XDP_TRST# 22,3 8

XDP_PREQ# 22,38

XDP_PRD Y# 22,38

The CFG signals have a default value of '1' if not terminated on the board.

E

CFG[0]: Stall reset sequence after PCU PLL lock until de-asserted

*1 = (Default) Normal Operation;

0 = Stall.

CFG[2]: PCI Express* Static x16 Lane Numbering Reversal.

1 = Normal operation

*0 = Lane numbers reversed.

CFG[4]: eDP enable:

1 = Disabled.

*0 = Enabled.

CFG[6:5]: PCI Express* Bifurcation:

00 = 1 x8, 2 x4 PCI Express*

01 = reserved

*10 = 2 x8 PCI Express*

11 = 1 x16 PCI Express*

CFG[7]: PEG Training:

*1 = (default) PEG Train immediately following RESET# de assertion.

0 = PEG Wait for BIOS for training.

To be confirm

CFG0

CFG2

CFG4

CFG5

CFG6

CFG7

1 2

RC255 1K_0402 _5%@

1 2

RC258 1K_0402 _5%

1 2

RC257 1K_0402 _5%

1 2

RC256 1K_0402 _5%

1 2

RC253 1K_0402 _5%@

1 2

RC254 1K_0402 _5%@

Reserve for ESD

H_VCCST _PWRGD

H_PROCH OT#_R

4 4

For DELL review

A

CH210

CH211

1 2

100P_04 02_50V8J@ESD@

1 2

100P_04 02_50V8J

Security Classification

Security Classification

Security Classification

2016/01/ 06 2017/01/ 06

2016/01/ 06 2017/01/ 06

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

2016/01/ 06 2017/01/ 06

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet o f

Date : Sheet o f

D

Date : Sheet o f

Compal Electronics, Inc.

CFL-H(5/8)CFG

CFL-H(5/8)CFG

CFL-H(5/8)CFG

LA-F611P

LA-F611P

LA-F611P

0.3

0.3

0.3

10 78T hursday, March 22, 2018

10 78T hursday, March 22, 2018

10 78T hursday, March 22, 2018

E

A

Main Func = CPU

+VCCGT +VCCGT

AT14

1 1

2 2

3 3

4 4

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AU14

AU29

AU30

AU31

AU32

AU35

AU36

AU37

AU38

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BC36

BC37

BC38

BD13

BD14

BD29

BD30

BD31

BD32

BD33

BD34

BP37

BP38

BR15

BR16

BR17

CFL_H_SOC

UC1K

VCCGT1

VCCGT2

VCCGT3

VCCGT4

VCCGT5

VCCGT6

VCCGT7

VCCGT8

VCCGT9

VCCGT10

VCCGT11

VCCGT12

VCCGT13

VCCGT14

VCCGT15

VCCGT16

VCCGT17

VCCGT18

VCCGT19

VCCGT20

VCCGT21

VCCGT22

VCCGT23

VCCGT24

VCCGT25

VCCGT26

VCCGT27

VCCGT28

VCCGT29

VCCGT30

VCCGT31

VCCGT32

VCCGT33

VCCGT34

VCCGT35

VCCGT36

VCCGT37

VCCGT38

VCCGT39

VCCGT40

VCCGT41

VCCGT42

VCCGT43

VCCGT44

VCCGT45

VCCGT46

VCCGT47

VCCGT48

VCCGT49

VCCGT50

VCCGT51

VCCGT52

VCCGT53

VCCGT54

VCCGT55

VCCGT56

VCCGT57

VCCGT58

VCCGT59

VCCGT60

VCCGT61

VCCGT62

VCCGT63

VCCGT64

VCCGT65

VCCGT66

VCCGT67

VCCGT68

VCCGT69

VCCGT70

VCCGT71

VCCGT72

VCCGT73

VCCGT74

VCCGT75

VCCGT76

VCCGT77

VCCGT78

VCCGT79

VCCGT159

VCCGT160

VCCGT161

VCCGT162

VCCGT163

11OF13

CFL-H_BG A1440

VCCGT80

VCCGT81

VCCGT82

VCCGT83

VCCGT84

VCCGT85

VCCGT86

VCCGT87

VCCGT88

VCCGT89

VCCGT90

VCCGT91

VCCGT92

VCCGT93

VCCGT94

VCCGT95

VCCGT96

VCCGT97

VCCGT98

VCCGT99

VCCGT100

VCCGT101

VCCGT102

VCCGT103

VCCGT104

VCCGT105

VCCGT106

VCCGT107

VCCGT108

VCCGT109

VCCGT110

VCCGT111

VCCGT112

VCCGT113

VCCGT114

VCCGT115

VCCGT116

VCCGT117

VCCGT118

VCCGT119

VCCGT120

VCCGT121

VCCGT122

VCCGT123

VCCGT124

VCCGT125

VCCGT126

VCCGT127

VCCGT128

VCCGT129

VCCGT130

VCCGT131

VCCGT132

VCCGT133

VCCGT134

VCCGT135

VCCGT136

VCCGT137

VCCGT138

VCCGT139

VCCGT140

VCCGT141

VCCGT142

VCCGT143

VCCGT144

VCCGT145

VCCGT146

VCCGT147

VCCGT148

VCCGT149

VCCGT150

VCCGT151

VCCGT152

VCCGT153

VCCGT154

VCCGT155

VCCGT156

VCCGT157

VCCGT158

VCCGT164

VCCGT165

VCCGT166

VCCGT167

VCCGT168

VSSGT_SENSE

VCCGT_SENSE

BD35

BD36

BE31

BE32

BE33

BE34

BE35

BE36

BE37

BE38

BF13

BF14

BF29

BF30

BF31

BF32

BF35

BF36

BF37

BF38

BG29

BG30

BG31

BG32

BG33

BG34

BG35

BG36

BH33

BH34

BH35

BH36

BH37

BH38

BJ16

BJ17

BJ19

BJ20

BJ21

BJ23

BJ24

BJ26

BJ27

BJ37

BJ38

BK16

BK17

BK19

BK20

BK21

BK23

BK24

BK26

BK27

BL15

BL16

BL17

BL23

BL24

BL25

BL26

BL27

BL28

BL36

BL37

BM15

BM16

BM17

BM36

BM37

BN15

BN16

BN17

BN36

BN37

BN38

BP15

BP16

BP17

BR37

BT15

BT16

BT17

BT37

AH37

AH38

VSSGT_S ENSE

VCCGT_S ENSE

For DELL review

A

B

B

C

+VCC_CORE +VCC_CORE +VCC_CORE +VCC_CORE

UC1I

AA13

AA31

AA32

AA33

AA34

AA35

AA36

AA37

AA38

AB29

AB30

AB31

AB32

AB35

AB36

AB37

AB38

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF29

AF30

AF31

AF32

AF33

AF34

AF35

AF36

AF37

AF38

AG14

AG31

AG32

AG33

AG34

AG35

AG36

CFL-H_BG A1440

+VCCGT

RC12

100_040 2_1%

VCCGT_S ENSE

VSSGT_S ENSE

1 2

12

RC13

100_040 2_1%

VCCGT_S ENSE 6 7

1. VccGT_S ENSE / VssGT_SENSE Trace L ength Mat ch < 25 mils

2. Ma intain 25-mil s eparation distance away from any other dynamic signals.

3. RC1, RC2 shoul d be placed w ithin 2 inch es (50.8 mm) of CPU

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

CFL_H_SOC

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

9OF13

VSSGT_S ENSE 67

AH13

VCC64

AH14

VCC65

AH29

VCC66

AH30

VCC67

AH31

VCC68

AH32

VCC69

AJ14

VCC70

AJ29

VCC71

AJ30

VCC72

AJ31

VCC73

AJ32

VCC74

AJ33

VCC75

AJ34

VCC76

AJ35

VCC77

AJ36

VCC78

AK31

VCC79

AK32

VCC80

AK33

VCC81

AK34

VCC82

AK35

VCC83

AK36

VCC84

AK37

VCC85

AK38

VCC86

AL13

VCC87

AL29

VCC88

AL30

VCC89

AL31

VCC90

AL32

VCC91

AL35

VCC92

AL36

VCC93

AL37

VCC94

AL38

VCC95

AM13

VCC96

AM14

VCC97

AM29

VCC98

AM30

VCC99

AM31

VCC100

AM32

VCC101

AM33

VCC102

AM34

VCC103

AM35

VCC104

AM36

VCC105

AN13

VCC106

AN14

VCC107

AN31

VCC108

AN32

VCC109

AN33

VCC110

AN34

VCC111

AN35

VCC112

AN36

VCC113

AN37

VCC114

AN38

VCC115

AP13

VCC116

AP30

VCC117

AP31

VCC118

AP32

VCC119

AP35

VCC120

AP36

VCC121

AP37

VCC122

AP38

VCC123

K13

VCC124

VCC_SENSE

VSS_SENSE

AG37

AG38

Compal Secret Data

Compal Secret Data

2016/01/ 06 2017/01/ 06

2016/01/ 06 2017/01/ 06

2016/01/ 06 2017/01/ 06

C

Compal Secret Data

VCC_SEN SE

VSS_SEN SE

Deciphered Date

Deciphered Date

Deciphered Date

+VCC_CORE

RC10

100_040 2_1%

1 2

12

RC11

100_040 2_1%

1. Vcc_S ENSE/ Vss _SENSE Tr ace Lengt h Match < 25 mils

2. Ma intain 25-mil s eparation distance away from any other dynamic signals.

3. RC1, RC2 shoul d be placed w ithin 2 inch es (50.8 mm) of CPU

D

VCC_SEN SE 6 7

VSS_SEN SE 67

LA-F611PR01_0531C.DSN

VCCSENSE change to VCC_SENSE

VSSSENSE change to VSS_SENSE

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet o f

Date : Sheet o f

D

Date : Sheet o f

E

UC1J

K14

L13

L14

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13