Dell lnspiron 15 5552 boardview

A

1 1

B

C

D

E

Compal Confidential

2 2

Schematic Document

Intel Braswell M

UMA

2015-6-09 Rev: 1.0

3 3

ZZZ

PCB@

PCB 1EE LA-C571P REV1 M/B 2

DA6001DX010

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/11/10 2015/11/25

2014/11/10 2015/11/25

2014/11/10 2015/11/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Title

Title

Title

P01-Cover Page

P01-Cover Page

P01-Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-C571P

LA-C571P

LA-C571P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

1 44Tuesday, June 16, 2015

1 44Tuesday, June 16, 2015

1 44Tuesday, June 16, 2015

1.0

1.0

1.0

5

4

3

2

1

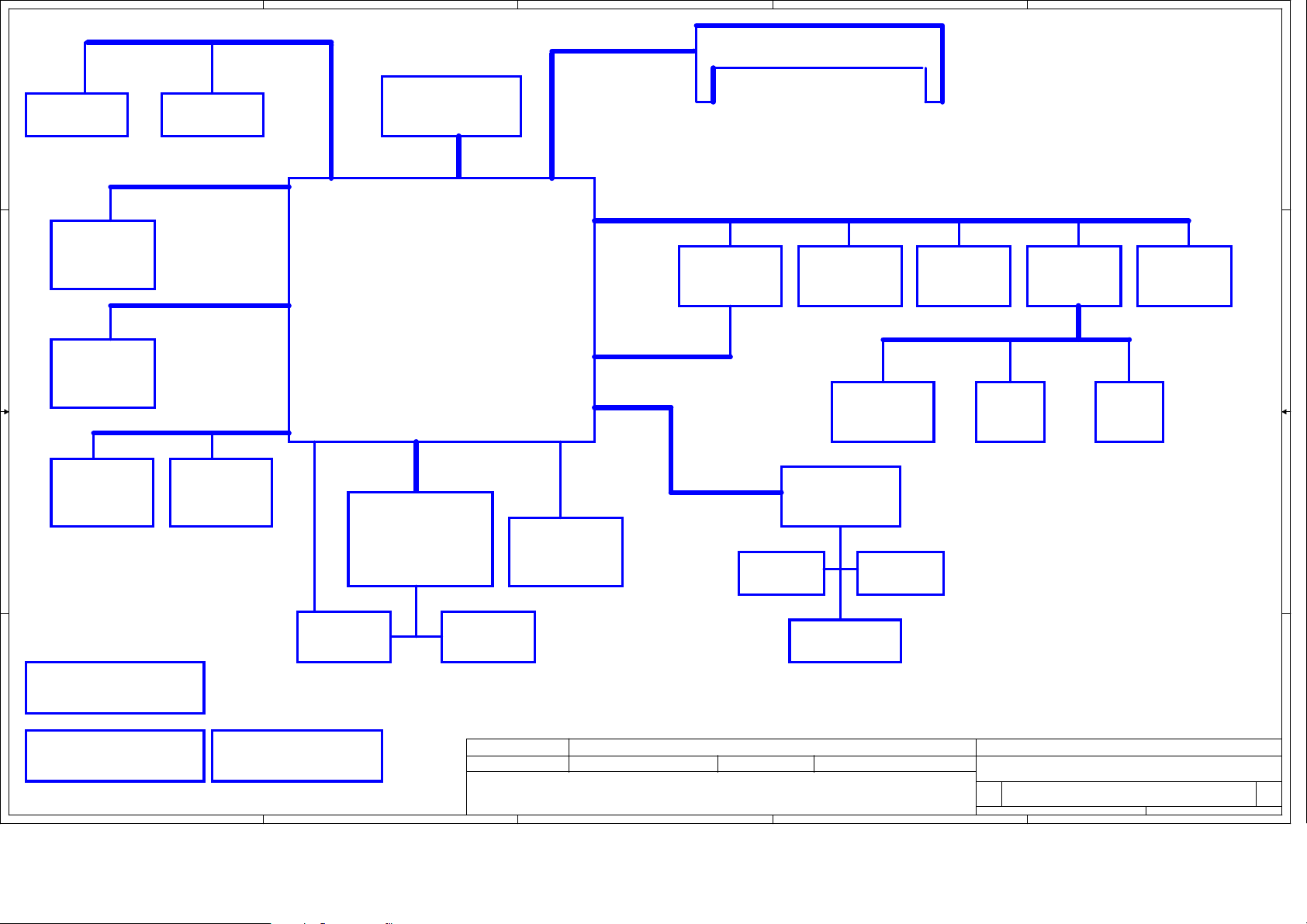

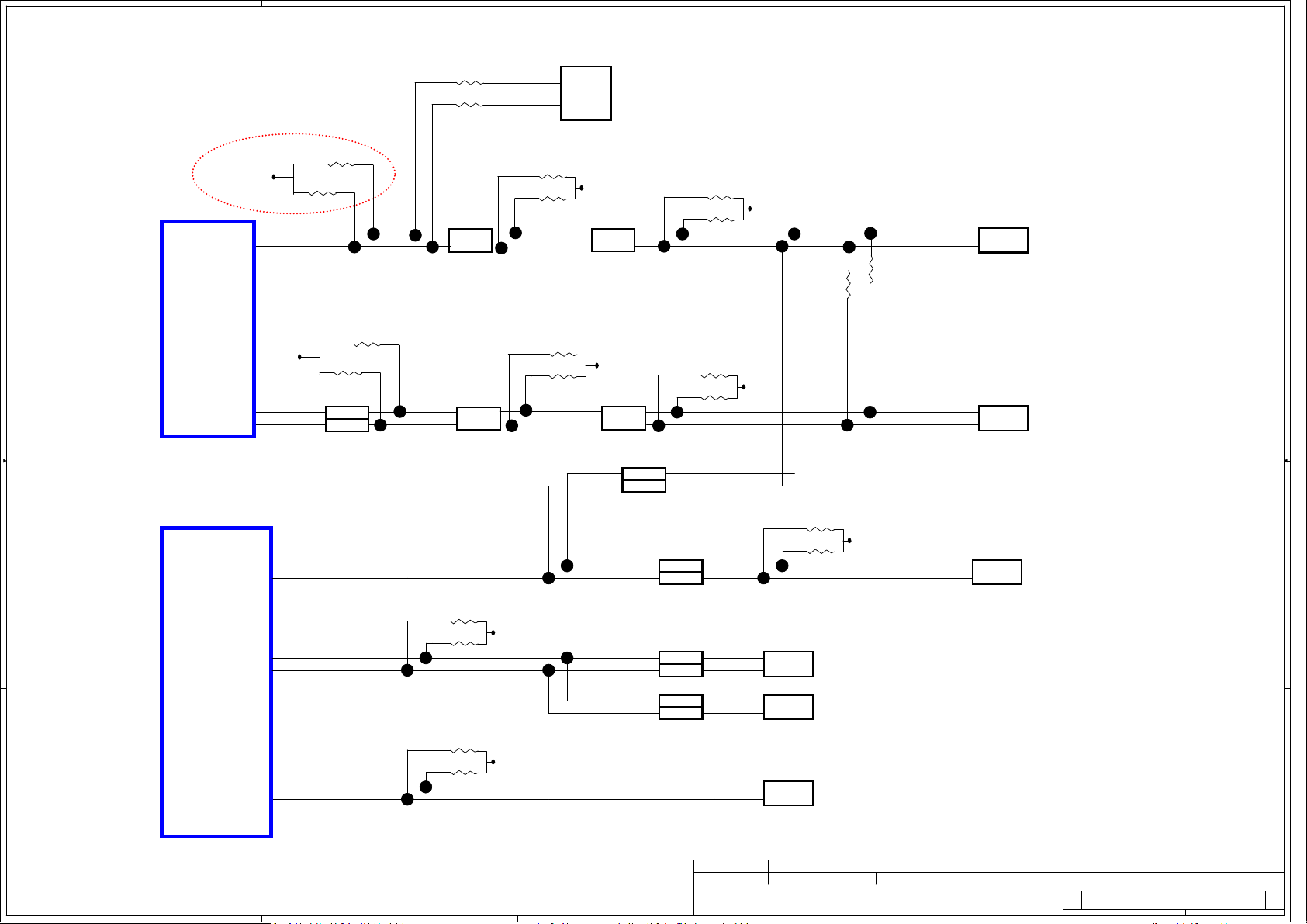

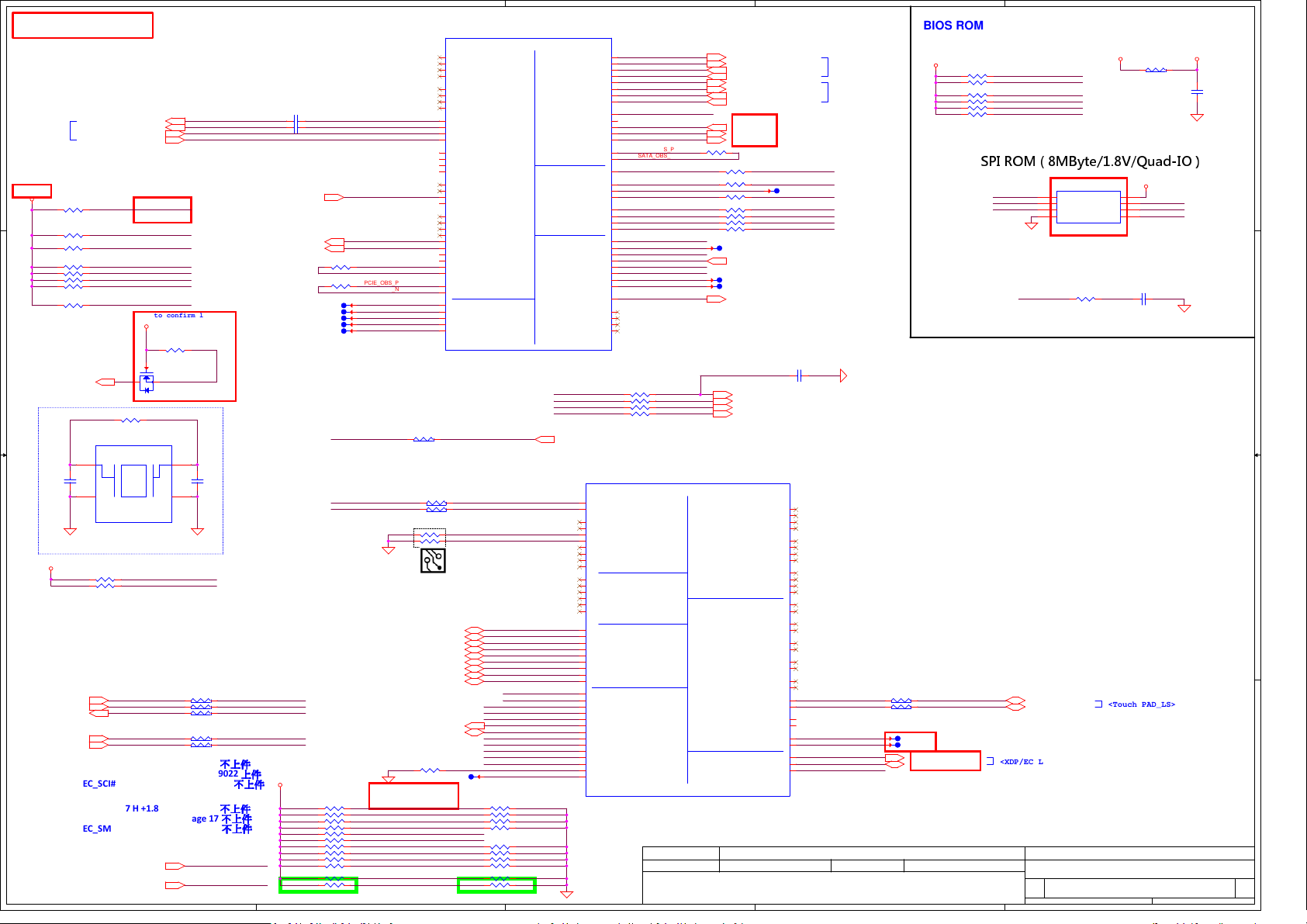

port 0port 1

P.19

Memory BUS

204pin DDR3L-SO-DIMM X1

XDP-60Pin

D D

eDP Conn.

HDMI Conn.

P.21P.20

PCIE x1

DDI x2

port 1

NGFF

WLAN/BT4.0

P.28

C C

eMMC

THGBMBG8D4KBAIR

port 1

P.22

port 1

SATA ODD

Conn.

B B

P.27

SATA HDD

Conn.

SDMMC

SATA III x2

port 0

SM BUS

P.27

Debug

Conn.

P.16

SOC

Intel Braswell-M

Quad Core (4C/4T)

TDP: 6W

FCBGA 1170-Pin

14nm

0.593mm Ball Pitch

LPC BUS

EC

ENE KB9022

P.32

Single Channel

1.35V DDR3L 1066/1333/1600

USB2.0 x5

USB3.0

HD Audio

page 08~16

SPI

SPI ROM

1.8V (8MB)

P.11

port 0

USB 3.0

Conn

USB 2.0

P.25 P.25

Conn

Debug Port

Card Reader

RTS5170

Port4

HDA Codec

ALC3234

Speaker

P.23

P.23

Int. MIC

HD Camera

Conn.

P.24

P.23

port 3port 2port 1

USB HUB

P.20

FE1.1s(STT)

P.26

Touch BT 4.0

Port4

P.28P.20Port1 Port2

USB2.0

Conn.

P.25

Combo Jack

P.25

P.29

Int.KBDTouch Pad

P.29

RTC CKT.

A A

DC/DC Interface CKT.

P.12

Security Classification

Security Classification

LED/Power On/Off

P.29P.30

5

4

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/11/10 2015/11/25

2014/11/10 2015/11/25

2014/11/10 2015/11/25

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

P02-Block diagram

P02-Block diagram

P02-Block diagram

LA-C571P

LA-C571P

LA-C571P

1.0

1.0

1.0

2 44Tuesday, June 16, 2015

2 44Tuesday, June 16, 2015

2 44Tuesday, June 16, 2015

1

A

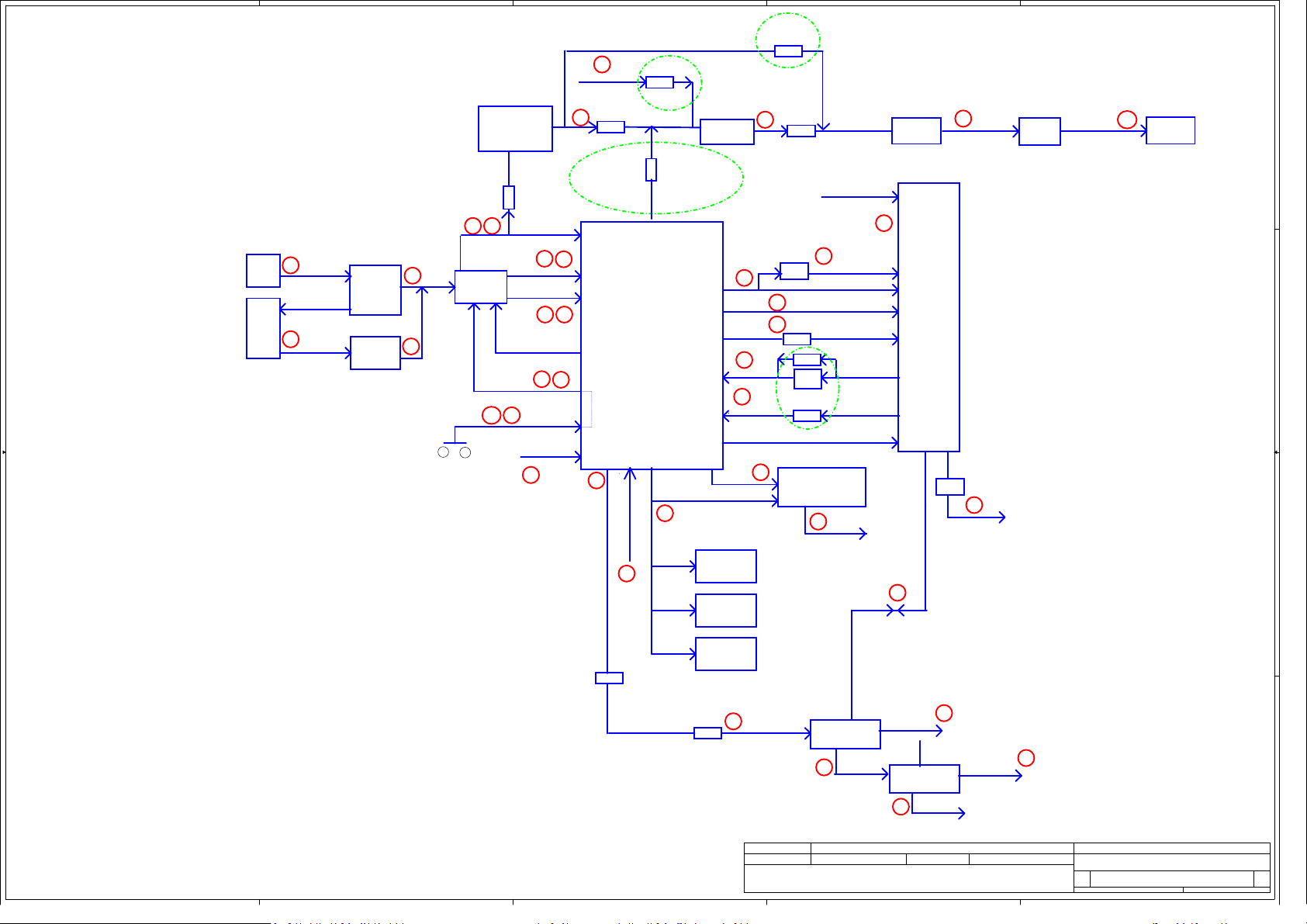

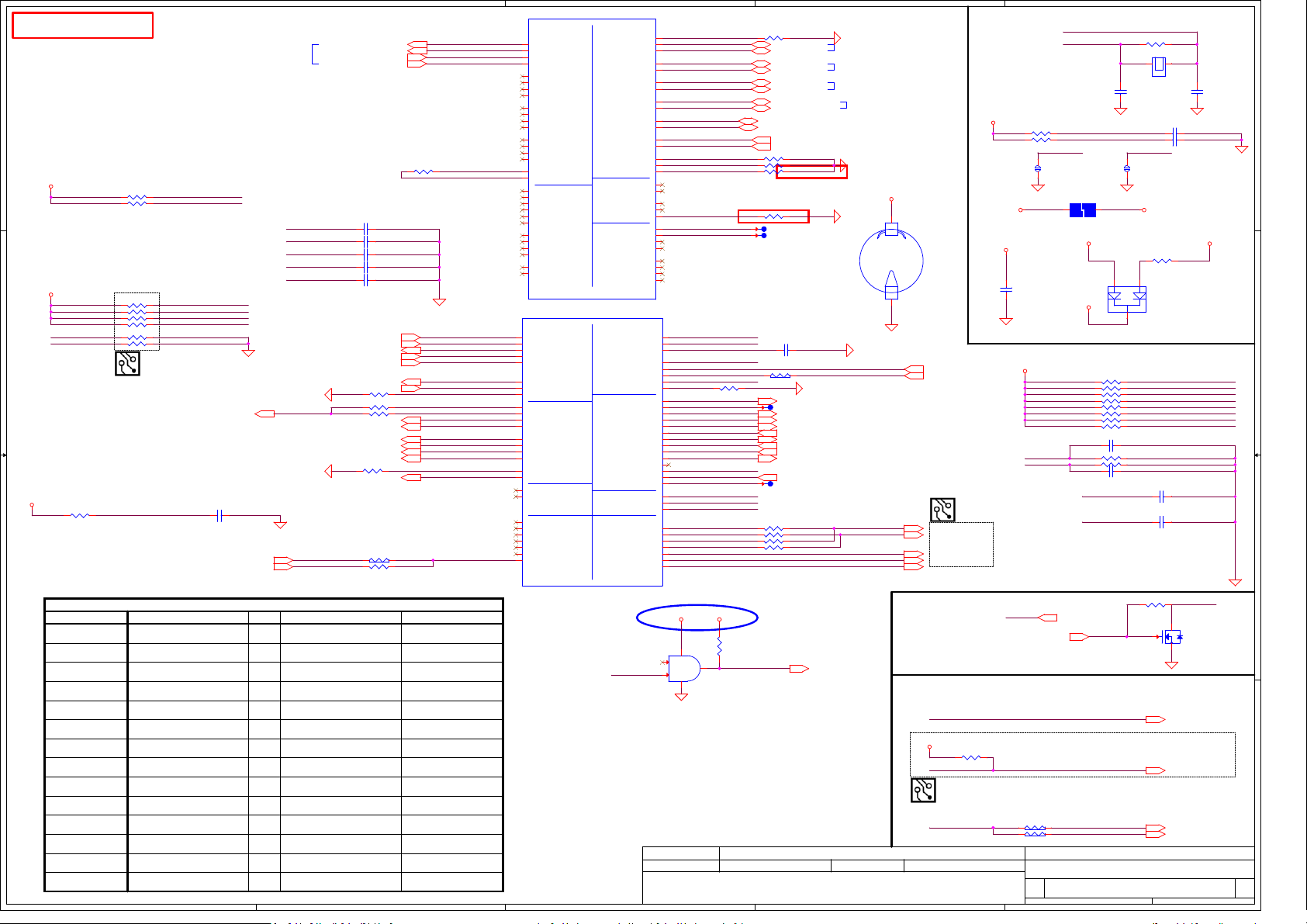

RT8171BGQW

VGG_PWRGD

(PU600)

VR12_1_VR_ON

RT8171BGQW

(PU800)

SYX196DQNC

SPOK

(PU500) (PJP500)

1 1

ADAPTER

CHARGER

1500mA

B+_3/5V

B+

SYSON

SUSP#

(FX2)

+INV_PWR_SRC

TPS51225CRUKR

(PU100)

RT8207PGQW

(PU200)

BATTERY

EC_ON

2 2

EC_ON

3 3

4 4

A

TPS51225CRUKR

(PU100)

TPS51225CRUKR

(PU100)

6400mA

11000mA

12mA

1000mA

4500mA

6620mA

6560 mA

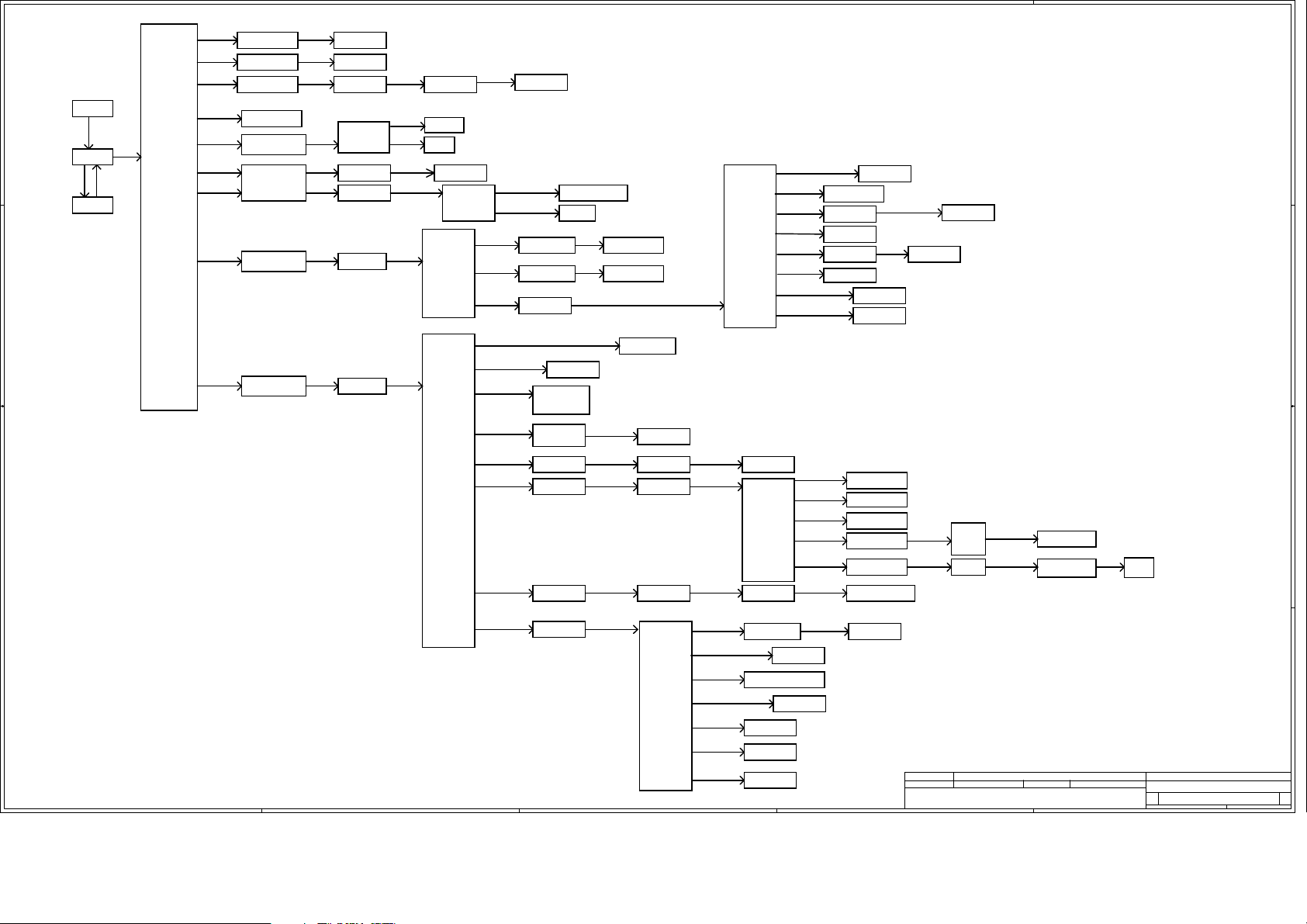

+VCC_CORE

+VGG_CORE

+1.05VALWP

+0.675VSP

+1.35VP

+5VALWP

+3VALWP

+3VLP

B

5700mA5700mA

8uA

(JP12)

12mA

1000mA

(PJP202)

4500mA

(PJP201)

6620mA

(PJP100)

6560 mA

(PJP101)

B

+1.05VALW

+CHTRTC

UE1

+0.675VS

+5VALW

+3VALW

3500mA

(JPC4)

+1.35V

USB_EN#

USB_EN#

SUSP#

5VS_EN

(RE2 0603 Short Pad)

+1.8VALW_PW RGD

3V_SOC_EN

VR12.1_VR_ON

+1.24VALW_PW RGD

(PJP400)

+1.15VALW_PW RGD

SUSP#

3VS_EN

2500mA

(JPC3)

2000mA

(PJP302)

C

+1.05V_VNN

+1.35V_DDR_VDDQ

(JPC6)

JDIMM1

SY6288D20AAC

(UI5)

SY6288D20AAC

(UI4)

EM5209VF

(U38)

1500mA

1500mA

4315mA

20 mA

(RE6)

+5V_USB_PWR1

+5V_USB_PWR2

(JP37)

+3VALW_EC

+3VS_TPIN

UC23

USB SW

FSUSB42MUX

EM5209VF

U37

SY8032ABC

(PU300) (PJP301)

SY8032ABC

(PU400) (PJP401)

SY8032ABC

(PU301) (PJP303)

EM5209VF

(U38)

200mA

(JP39)

800mA

5364mA

(JP36)

+3V_SOC

+1.15VALWP

+1.8VALWP

+1.24VALWP

+3VS

C

MODEL NAME:

PCB NAME:

REVISION:

DATE:

+5VS

700mA

700mA1680mA

+1.15VALW

+1.8VALW

700mA700mA

ENVDD_R

(RX27 0603 Short PAD)

(RM7 1206)

+1.24VALW

SY6288C20AAC

(UX4)

150mA

+3VS_WLAN_NGFF

(RR9 , 0603 Short Pad)

thermal sensor

1500mA

+5V_3V_HDD

@(JP14)

200mA

+5VS_TOUCH

@(RX29)

(RX28 , 0603 ,Short Pad)

(FX1 , 1206)

(RV54 0805 Short Pad )

(RV59 0603 Short Pad)

+3VS_CAM

+3VS_CARD

(U2407)

Power Rail Block Diagram

LA-C571PR02 2015/03/27

0.2

2015/04/13

200mA

1000mA

1500mA

(JP7)

1500mA

(JP13)

EN_DFAN1

20 mA

CAPS_LED

(RE60)

550mA

(RC190)

500mA

(RC191)

35mA

(RC87)

SUSP#

1.8VS_ON

SUSP#

(PJP404)

(JPC5)

1500mA

+VDISPLAY_VCC

+5VS_ODD_R1

+5V_3V_HDD

NCT3942S

(UE3)

KB_CAPS_PWR

1000mA

+5V_PVDD

1000mA

+5V_AUDIO

+3V_+1.8V_SDIO

+1.8V_XDP_AB

+1.8V_SPI

EM5209VF

(U37)

G971ADJF11U

(PU402)

+1.24V_USB_VDDQ

+LCDVDD

+5VS_TOUCH

D

(RS12 , Short Pad)

1000 mA

+5VS_ODD

+FAN_POWER

550mA

(JP38)

750mA

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

(RC192)

+1.8VS

750mA

+1.5VSP

(PJP405)

2014/11/10 2015/11/25

2014/11/10 2015/11/25

2014/11/10 2015/11/25

+1.8VS_XDP_CD

+1.5VS

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

E

UA1 ,

Audio

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

P03-DB block diagram

P03-DB block diagram

P03-DB block diagram

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

LA-C571P

LA-C571P

LA-C571P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

3 44Tuesday, June 1 6, 2015

3 44Tuesday, June 1 6, 2015

3 44Tuesday, June 1 6, 2015

1.0

1.0

1.0

A

B

C

D

E

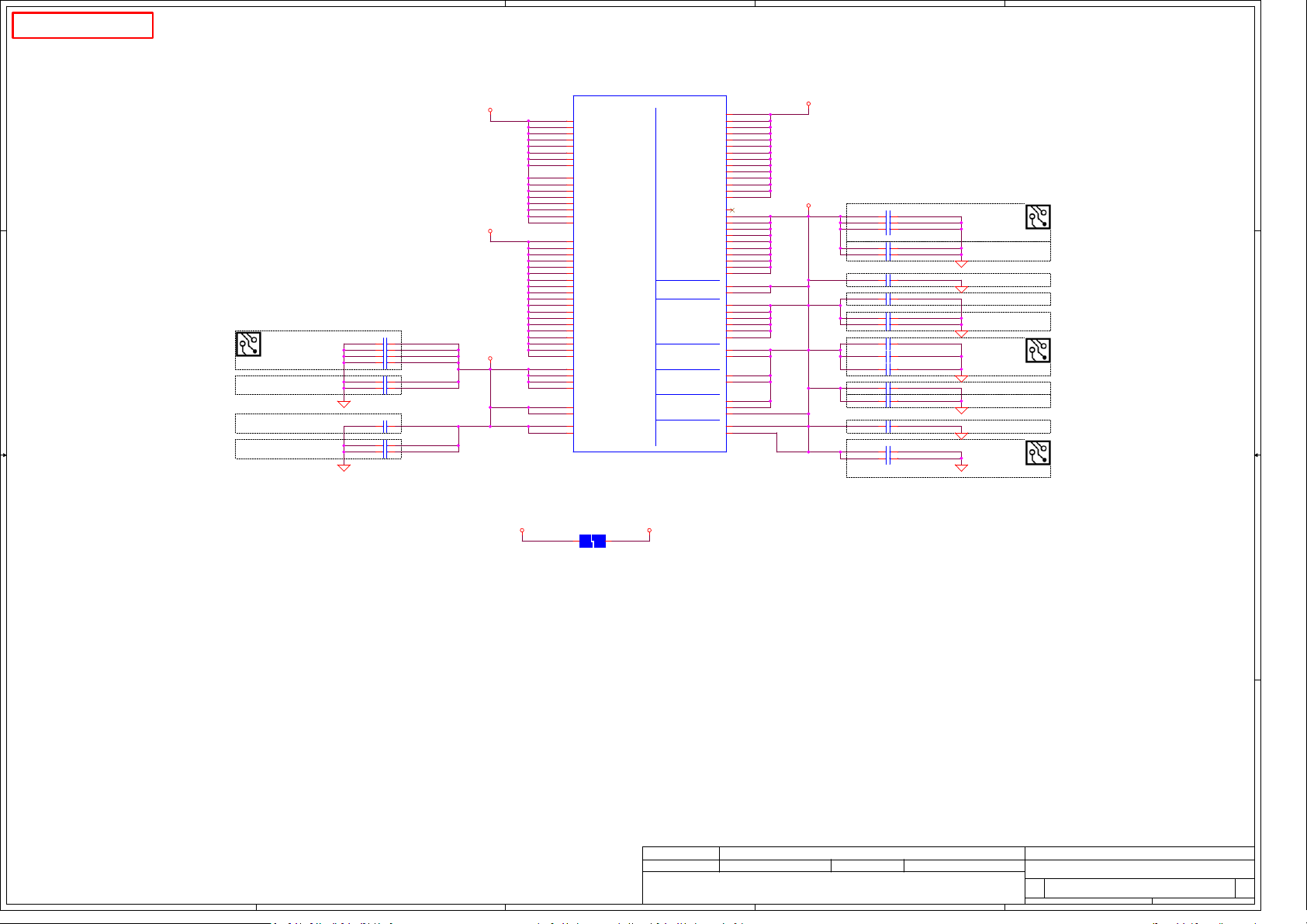

Voltage Rails

S0 S3 S4/S5Power Plane Description

VIN

BATT+ 12V Battery power supply

B+

1 1

+RTCVCC RTC Battery Power

+1.05VALW

+1.24VALW +1.24v Always power rail

+1.8VALW

+3VALW +3.3v Always power rail

+5VALW

+VCC_CORE Core voltage for SOC

+VGG_CORE GFX voltage for SOC

+0.675VS +0.675V power rail for DDR3L Terminator

+1.15VALW

2 2

+1.35VS ON

+1.5VS

+1.8VS

+3VS

+5VS

19V Adapter power supply

AC or battery power rail for power circuit. (19V/12V)

+1.05v Always power rail

+1.8v Always power rail

+5.0v Always power rail

+1.35V power rail for DDR3L+1.35V

+1.35v system power rail

+1.5v system power rail

+1.8v system power rail

+3.3v system power rail

+5.0v system power rail

ON

ON ON

ON ONON

ON ONON

ON ON ON

ON ONON

ON ON ON

ONONON

ONON ON

ONONON+3V_SOC +3V_SOC Always power rail

ON ONON

ON ON

ON

ON

ON OFF OFF

ON OFF OFF+1.15VALW system power rail

ON OFFOFF

ON OFF OFF

ON OFFOFF

OFF

OFF OFF

OFF OFF

OFF OFF

OFFON OFF

Board ID / SKU ID Table for AD channel

BOARD ID Table

Board ID

0

1

2

3

PCB Revision

0.1

0.2

0.3

1.0

BOM Option Table

Item BOM Structure

Unpop @

CONN@Connector

XDP (Debug Port)

XDP@

EMI@EMC requirement

NEMI@EMC requirement unpop

LPC18@LPC18

LPC33@LPC33

RF@Rvs. RF requirement

ESD@ESD requirement

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

ESD requirement unpop NESD@

NXDP@XDP (Debug Port) unpop

For JUMP JP@

3 3

For PCB

For CPU

SATA re-Driver

PCB@

SOC@

601@

SOC1@

Test Point TP@

SATA re-Driver unpop N601@

43 level BOM table

4319Y031L01 MB AC571 AAL14 BSW U PEN HDMI

4319Y031L02

4 4

A

MB AC571 AAL14 BSW U CEL HDMI

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

Compal Secret Data

Compal Secret Data

2014/02/26 2015/02/25

2014/02/26 2015/02/25

2014/02/26 2015/02/25

C

Compal Secret Data

EMI@/ESD@/XDP@/LPC33@/PCB@/ODD@/SOC@/601@/N601@/PARADE@

EMI@/ESD@/XDP@/LPC33@/PCB@/ODD@/SOC1@/601@/N601@/PARADE@

Deciphered Date

Deciphered Date

Deciphered Date

BOM Structure43 Level Description

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

P04-Notes List

P04-Notes List

P04-Notes List

LA-C571P

LA-C571P

LA-C571P

1.0

1.0

1.0

4 44Tuesday, June 16, 2015

4 44Tuesday, June 16, 2015

4 44Tuesday, June 16, 2015

E

5

4

3

2

1

MODEL NAME:

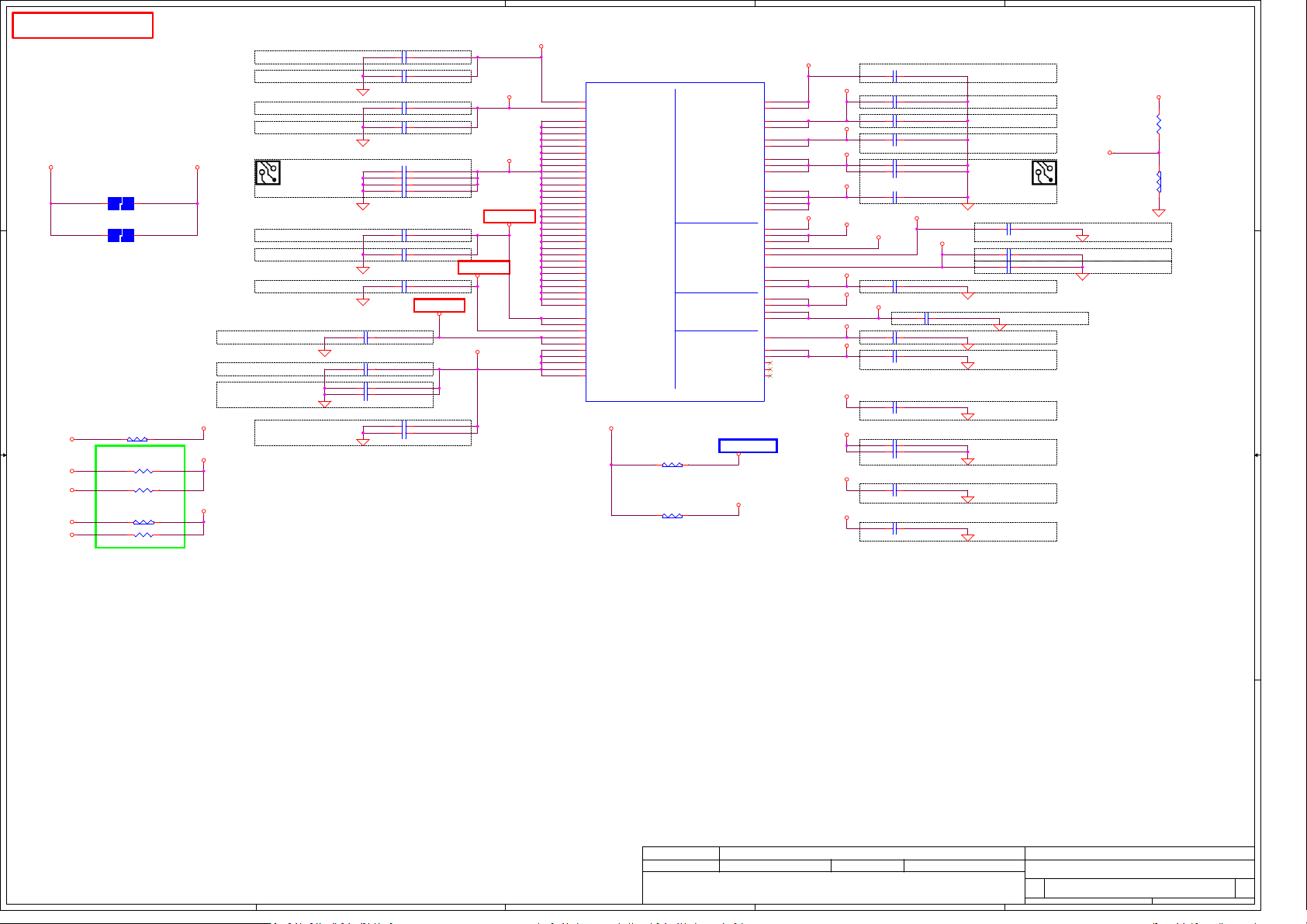

SOC_SMB_CLK

HW3 follow Intel SCL

D D

0p92 P.43 use 1k Ohm

RP68

2.2K

2.2K

RP68

SOC_SMB_CLK

SOC_SMB_DATA

SOC

+1.8VALW

AM6

AM7

BSW

RC174

1K,@

RC175

RC158

0 ohm

0 ohm

RC159

1K,@

I2C_5_SDA_R

C C

B B

A A

KBC

KB9022QD

+1.8VALW

AB2

I2C_5_SCL

I2C_5_SDA

AC3

79

80

77

78

87

88

EC_SMB_CK2_EC

EC_SMB_DA2_EC

EC_SMB_CK1

EC_SMB_DA1

TP_CLK

TP_DATA

RC209

RC208

SOC_SMB_DATA

+1.8VALW

I2C_5_SCL_R

RP36

RP36

RE10

RE9

0 , XDP@

0 , XDP@

Q2516

Dual

N-MOS

DMN63D8

+1.8VALW

Q2514

Dual

N-MOS

2.2K

2.2K

4.7K

4.7K

SMB_XDP_SCL

SMB_XDP_SDA

R1184

R1183

SOC_SMB_CLK_L

SOC_SMB_DATA_L

R1181

R1182

I2C_5_SDA_R_L

+3VALW_EC

+3VS_TP

53

51

1K

1K

10K

10K

I2C_5_SCL_R_L

+3VALW

+3VS

Q2517

Dual

N-MOS

DMN63D8

+3VALW

+3VS

Q2515

N-MOS

JXDP1

CONN@

Dual

RE15@

Reserve

Reserve

RE16@

PR717

PR719

PR8

PR9

RP36

RP36

10K

10K

RE22

0 ohm

0 ohm

RE23

0 ohm

0 ohm

100 ohm

100 ohm

2.2K

2.2K

EC_SMB_CK2

EC_SMB_DA2

RE17

RE19

I2C5_SCL_TP_R

I2C5_SDA_TP_R

CLK_SMB

DAT_SMB

+3VS

+3VS_TP

10

9

6

5

8

7

R2451

PBATT1

JTP

2.2K

2.2K

R2449

0 ,@

RE32

POWERPU700

Charger

BATT

CONN

PCB NAME:

REVISION:

DATE:

EC_SMB_CK2

EC_SMB_DA2

0 ,@

RE33

I2C5_SCL_TP_R

I2C5_SDA_TP_R

+3VS

THERMAL_SMB_CK2

THERMAL_SMB_DA2

SMBUS Address [?]

SMBUS Address [?]

2015/04/13

202

DIMMA

200

10

U2407

9

SMbus Block Diagram

LA-C571 PR02 2015/03/27

0.2

SMBUS Address [?]

I2C Address [?]

TP

Thermal

SMBUS Address [?]

Sensor

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/11/10 2015/11/25

2014/11/10 2015/11/25

2014/11/10 2015/11/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

P05-SMBus block diagram

P05-SMBus block diagram

P05-SMBus block diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

LA-C571P

LA-C571P

LA-C571P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

5 44Tuesday, June 16, 2015

5 44Tuesday, June 16, 2015

5 44Tuesday, June 16, 2015

1.0

1.0

1.0

5

D D

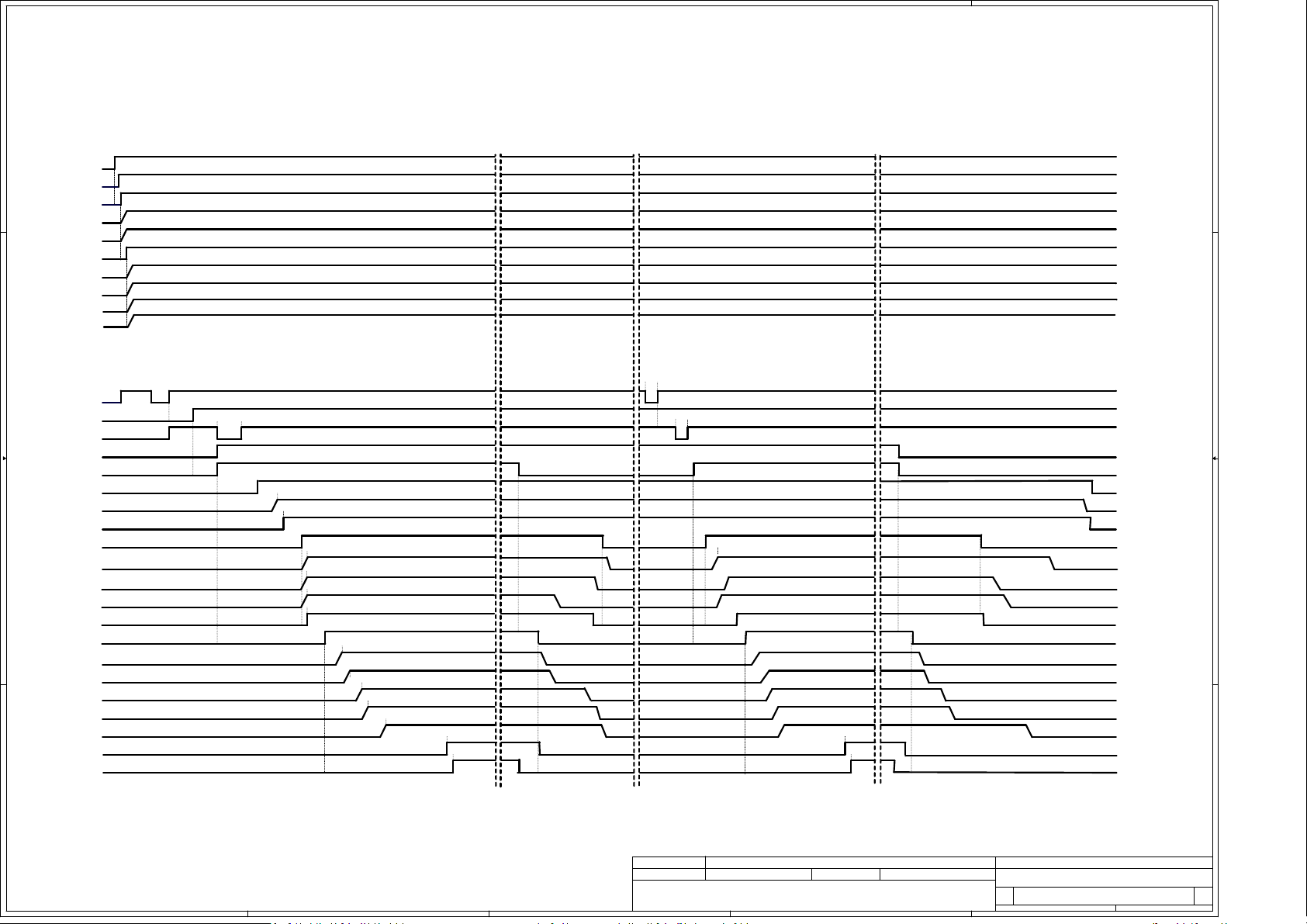

S5->S0 S0->S3 S3->S0

ACIN

2.785ms

+3VLP

EC_ON

+3VALW

+5VALW

SPOK

+1.24VALW

+1.8VALW

+3V_SOC

C C

VNN

2.948ms

455.9us

499.1us

4.732ms

229.8us

3.259ms

4.368ms

8.809ms

4

3

2

1

S0->S5

ACIN

+3VLP

EC_ON

+3VALW

+5VALW

SPOK

VNN

+1.24VALW

+1.8VALW

+3V_SOC

ON/OFF

EC_RSMRST#

PBTN_OUT#

EC_SLP_S4#

EC_SLP_S3#

SYSON

+1.35V

DDR_PWROK

VR_ON

+1.15VALW

B B

+VCC_CORE

+VGG_CORE

VGATE

SUSP#

+1.5VS

+1.8VS

+3VS

+5VS

+0.675VS

SOC_VCCA_PWROK

PMC_PLTRST#

A A

98ms

80.81ms

102.5ms

102.5ms

60ms

140ms

140.5ms

146.2ms

280.8ms

282.2ms

716.6us

2.917ms

1.388ms

3.12ms

1.702ms

2.509ms

3.715ms

3.94ms

7.981ms

120.9ms

135.1ms

24.9ms

1.574ms

14.2ms

1.97us

30.85ms

43.7ms

37.52ms

198.5us

194.1us

5.737us

19.34ms

19.94ms

28.1ms

211.8ms

134.4ms

3.119ms

717us

155.5ms

2.933ms

1.403ms

1.699ms

2.553ms

3.718ms

3.966ms

7.966ms

121ms

135.8ms

48.71ms

28.6ms

197.8us

198.9us

4.839us

31.38ms

1.615ms

14.14ms

18.96ms

19.58ms

27.9ms

2.939us

23.68ms

ON/OFF

EC_RSMRST#

PBTN_OUT#

EC_SLP_S4#

EC_SLP_S3#

211ms

SYSON

212.1ms

+1.35V

206.8ms

DDR_PWROK

VR_ON

+1.15VALW

+SOC_VCC

+SOC_VGG

VGATE

SUSP#

+1.5VS

+1.8VS

+3VS

+5VS

+0.675VS

SOC_VCCA_PWROK

PMC_PLTRST#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

5

4

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

2014/11/10 2015/11/25

2014/11/10 2015/11/25

2014/11/10 2015/11/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

P06-Power Sequence

P06-Power Sequence

P06-Power Sequence

LA-C571P

LA-C571P

LA-C571P

6 44Tuesday, June 16, 2015

6 44Tuesday, June 16, 2015

1

6 44Tuesday, June 16, 2015

1.0

1.0

1.0

5

MODEL NAME:

PCB NAME:

REVISION:

DATE:

D D

C C

B B

2015/04/13

Power Sequence Block Diagram

LA-C571PR02 2015/03/27

0.2

AC

MODE

DC

MODE

A1

VIN

B1

BATT+

PU700

ISL88731

CHRTZ-T

PQ706

PMOS

4

3

2

1

V0.2 Modify

1.05VALW_PWRGD

15c

(VR12.1_VR_ON)

SYX198DQNC

(PU500)

+1.05VALW

(+1.05V_VNN)

1

PR500

B7A6

SPOK

A2

B2

1

PU100

B+

TPS51225

CRUKR

VCOUT0_PH

A11

B4

ON/OFFBTN#

PLT_RST#

18

2

1.05VALW_PWRGD

SPOK

A5

B6

+3VALW

+5VALW

+3VLP,VLBATT+

B3

A3

A4

B5

EC_ON

A7

PR300

18

104

112

114

13

15c

@

+1.15VALWP_ON

121

97

RE64

V0.2 Modify

@

RE63

25

UE1

EC9022QD

116

1

1.15VALWP_EC

V0.3 Modify

95

SY8032ABC

(PU300)

+1.15VALW

32

100

PBTN_OUT# PMU_RSTBTN#

122

SIO_SLP_S3#

6

SIO_SLP_S4#

123

2

SYSON

SUSP#

16

VGATE

VR_ON_EC

EM5209VF

SUSP#

SUSP#

(U38)

+5VS, +3VS

EM5209VF

(U37)

+1.8VS

15g

RE62

+1.15VALW_PWRGD

A8

5

Level

UC7

17

PCH_PWROK

12

13

15b

14

V0.2 Modify

15

8

7

@

PR308

DDR_PWROK

SOC_DRAM_PWROK

17a

SOC_VCCA_PWROK

EC_RSMRST#

R27

R35, @

Level

QC7

R34

EC_KBRST#

RT8207PGQW

(PU200)

10

15a

DDR_PWROK

SOC_DRAM_PWROK

+1.24VALWP_ON

PMU_SLP_S3#

PMU_SLP_S4#

15a

SY8032ABC

(PU301)

1

+1.24VALW

AV28

AV26

G16

F18

M16

B14

C12

V40

AD42

AD41

AD40

15d

SOC

USOC1

SVID Bus

F14

UC5

A9

+1.24VALW_PWRGD

PMU_PLTRST#

18

PLT_RST#

SY8032ABC

(PU400)

+1.8VALW

+1.8VALW_PG

3V_SOC_EN

A10

EM5209VF

(U37)

+3V_SOC

G971ADJF11U

SUSP#

(PU402)

+1.5VS

RE12

VR_ON

A A

5

4

3

R464

15c

(VR12.1_VR_ON)

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

13,14,15

SVID Bus

VGG_PWRGD

+VGG_CORE

26

RT8171BGQW

26

(PU800)

17

15e

2014/11/10 2015/11/25

2014/11/10 2015/11/25

2014/11/10 2015/11/25

15d

SVID Bus

13,14,15

RT8171BGQW

(PU600)

17

15g

VGATE

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

+VCC_CORE

15f

Compal El ectronics, Inc.

Compal El ectronics, Inc.

Compal El ectronics, Inc.

Title

Title

Title

P07-Power Sequence Block Diagram

P07-Power Sequence Block Diagram

P07-Power Sequence Block Diagram

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Custom

Custom

Custom

LA-C571P

LA-C571P

LA-C571P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

7 44Tuesday, June 16, 2015

7 44Tuesday, June 16, 2015

7 44Tuesday, June 16, 2015

1.0

1.0

1.0

5

Main Func = CPU

D D

UC1

SOC@

S IC A31 FH80665017 15906 QJ4S C0 1.6G

Part Number = SA00008U 62L

C C

UC1

SOC1@

S IC A31 FH80665017 15914 QJ4V C0 1.6G

Part Number = SA00008U 52L

4

1 2

3

@

DDR_M0_MA[0..15 ]<19>

DDR_M0_BS2<19>

DDR_M0_BS1<19>

DDR_M0_BS0<19>

DDR_M0_CAS#<19>

DDR_M0_RAS#<19>

DDR_M0_W E#< 19>

DDR_M0_CS #1< 19>

DDR_M0_CS #0< 19>

DDR_M0_CL K1< 19>

DDR_M0_CL K#1<19>

DDR_M0_CK E1<19>

DDR_M0_CL K0<19>

DDR_M0_CL K#0<19>

DDR_M0_CK E0<19>

DDR_M0_ODT 0<19>

DDR_M0_ODT 1<19>

+0.675V_M0_VREFC A

+0.675V_M0_VREFD Q

DDR_M0_DR AMRST#<19>

DDR_M0_DM [4..7]<19>

DDR_M0_DM [0..3]<19>

DDR_M0_DQS [0..7]<19>

DDR_M0_DQS #[0..7]<19>

DDR_M0_RC OMP

RC1182_0402_ 1%

DDR_M0_MA15

DDR_M0_MA14

DDR_M0_MA13

DDR_M0_MA12

DDR_M0_MA11

DDR_M0_MA10

DDR_M0_MA9

DDR_M0_MA8

DDR_M0_MA7

DDR_M0_MA6

DDR_M0_MA5

DDR_M0_MA4

DDR_M0_MA3

DDR_M0_MA2

DDR_M0_MA1

DDR_M0_MA0

DDR_M0_BS2

DDR_M0_BS1

DDR_M0_BS0

DDR_M0_CAS#

DDR_M0_RAS#

DDR_M0_W E#

DDR_M0_CS #1

DDR_M0_CS #0

DDR_M0_CL K1

DDR_M0_CL K#1

DDR_M0_CK E1

DDR_M0_CL K0

DDR_M0_CL K#0

DDR_M0_CK E0

DDR_M0_ODT 0

DDR_M0_ODT 1

DDR_M0_DR AMRST#

SOC_DRAM_PW ROK

DDR_M0_RC OMP

DDR_M0_DM 7

DDR_M0_DM 6

DDR_M0_DM 5

DDR_M0_DM 4

DDR_M0_DM 3

DDR_M0_DM 2

DDR_M0_DM 1

DDR_M0_DM 0

DDR_M0_DQS 7

DDR_M0_DQS #7

DDR_M0_DQS 6

DDR_M0_DQS #6

DDR_M0_DQS 5

DDR_M0_DQS #5

DDR_M0_DQS 4

DDR_M0_DQS #4

DDR_M0_DQS 3

DDR_M0_DQS #3

DDR_M0_DQS 2

DDR_M0_DQS #2

DDR_M0_DQS 1

DDR_M0_DQS #1

DDR_M0_DQS 0

DDR_M0_DQS #0

UC1A

BD49

DDR3_M0_MA_15

BD47

DDR3_M0_MA_14

BF44

DDR3_M0_MA_13

BF48

DDR3_M0_MA_12

BB49

DDR3_M0_MA_11

BJ45

DDR3_M0_MA_10

BE52

DDR3_M0_MA_9

BD44

DDR3_M0_MA_8

BE46

DDR3_M0_MA_7

BB46

DDR3_M0_MA_6

BH48

DDR3_M0_MA_5

BD42

DDR3_M0_MA_4

BH47

DDR3_M0_MA_3

BJ48

DDR3_M0_MA_2

BC42

DDR3_M0_MA_1

BB47

DDR3_M0_MA_0

BF52

DDR3_M0_BS_2

AY40

DDR3_M0_BS_1

BH46

DDR3_M0_BS_0

BG45

DDR3_M0_CASB

BA40

DDR3_M0_RASB

BH44

DDR3_M0_WEB

AU38

DDR3_M0_CSB_1

AY38

DDR3_M0_CSB_0

BD38

DDR3_M0_CK_1

BF38

DDR3_M0_CKB_1

AY42

DDR3_M0_CKE_1

BD40

DDR3_M0_CK_0

BF40

DDR3_M0_CKB_0

BB44

DDR3_M0_CKE_0

AT30

RSVD1

AU30

RSVD2

AV36

DDR3_M0_ODT_0

BA38

DDR3_M0_ODT_1

AT28

DDR3_M0_OCAVREF

AU28

DDR3_M0_ODQVREF

BA42

DDR3_M0_DRAMRSTB

AV28

DDR3_DRAM_PWROK

BA28

DDR3_M0_RCOMPPD

BH30

DDR3_M0_DM_7

BD32

DDR3_M0_DM_6

AY36

DDR3_M0_DM_5

BG41

DDR3_M0_DM_4

BA53

DDR3_M0_DM_3

AP44

DDR3_M0_DM_2

AT48

DDR3_M0_DM_1

AP52

DDR3_M0_DM_0

BH32

DDR3_M0_DQS_7

BG31

DDR3_M0_DQSB_7

BC30

DDR3_M0_DQS_6

BC32

DDR3_M0_DQSB_6

AT32

DDR3_M0_DQS_5

AT34

DDR3_M0_DQSB_5

BH40

DDR3_M0_DQS_4

BG39

DDR3_M0_DQSB_4

AY52

DDR3_M0_DQS_3

BA51

DDR3_M0_DQSB_3

AT42

DDR3_M0_DQS_2

AT41

DDR3_M0_DQSB_2

AV47

DDR3_M0_DQS_1

AV48

DDR3_M0_DQSB_1

AM52

DDR3_M0_DQS_0

AM51

DDR3_M0_DQSB_0

BSW-MCP-ED S_FCBGA1170

CHV_MCP_EDS

DDR0

1 OF 13

DDR3_M0_DQ_63

DDR3_M0_DQ_62

DDR3_M0_DQ_61

DDR3_M0_DQ_60

DDR3_M0_DQ_59

DDR3_M0_DQ_58

DDR3_M0_DQ_57

DDR3_M0_DQ_56

DDR3_M0_DQ_55

DDR3_M0_DQ_54

DDR3_M0_DQ_53

DDR3_M0_DQ_52

DDR3_M0_DQ_51

DDR3_M0_DQ_50

DDR3_M0_DQ_49

DDR3_M0_DQ_48

DDR3_M0_DQ_47

DDR3_M0_DQ_46

DDR3_M0_DQ_45

DDR3_M0_DQ_44

DDR3_M0_DQ_43

DDR3_M0_DQ_42

DDR3_M0_DQ_41

DDR3_M0_DQ_40

DDR3_M0_DQ_39

DDR3_M0_DQ_38

DDR3_M0_DQ_37

DDR3_M0_DQ_36

DDR3_M0_DQ_35

DDR3_M0_DQ_34

DDR3_M0_DQ_33

DDR3_M0_DQ_32

DDR3_M0_DQ_31

DDR3_M0_DQ_30

DDR3_M0_DQ_29

DDR3_M0_DQ_28

DDR3_M0_DQ_27

DDR3_M0_DQ_26

DDR3_M0_DQ_25

DDR3_M0_DQ_24

DDR3_M0_DQ_23

DDR3_M0_DQ_22

DDR3_M0_DQ_21

DDR3_M0_DQ_20

DDR3_M0_DQ_19

DDR3_M0_DQ_18

DDR3_M0_DQ_17

DDR3_M0_DQ_16

DDR3_M0_DQ_15

DDR3_M0_DQ_14

DDR3_M0_DQ_13

DDR3_M0_DQ_12

DDR3_M0_DQ_11

DDR3_M0_DQ_10

DDR3_M0_DQ_9

DDR3_M0_DQ_8

DDR3_M0_DQ_7

DDR3_M0_DQ_6

DDR3_M0_DQ_5

DDR3_M0_DQ_4

DDR3_M0_DQ_3

DDR3_M0_DQ_2

DDR3_M0_DQ_1

DDR3_M0_DQ_0

BG33

BH28

BJ29

BG28

BG32

BH34

BG29

BJ33

BD28

BF30

BA34

BD34

BD30

BA32

BC34

BF34

AV32

AV34

BD36

BF36

AU32

AU34

BA36

BC36

BH38

BH36

BJ41

BH42

BJ37

BG37

BG43

BG42

BB51

AW53

BC52

AW51

AV51

BC53

AV52

BD52

AV42

AP41

AV41

AT44

AP40

AT38

AP42

AT40

AV45

AY50

AT50

AP47

AV50

AY48

AT47

AP48

AP51

AR53

AK52

AL53

AR51

AT52

AL51

AK51

DDR_M0_D6 0

DDR_M0_D5 8

DDR_M0_D6 2

DDR_M0_D5 9

DDR_M0_D5 7

DDR_M0_D6 1

DDR_M0_D6 3

DDR_M0_D5 6

DDR_M0_D5 5

DDR_M0_D5 4

DDR_M0_D5 3

DDR_M0_D5 2

DDR_M0_D5 1

DDR_M0_D5 0

DDR_M0_D4 9

DDR_M0_D4 8

DDR_M0_D4 7

DDR_M0_D4 6

DDR_M0_D4 5

DDR_M0_D4 4

DDR_M0_D4 3

DDR_M0_D4 2

DDR_M0_D4 1

DDR_M0_D4 0

DDR_M0_D3 9

DDR_M0_D3 8

DDR_M0_D3 7

DDR_M0_D3 6

DDR_M0_D3 5

DDR_M0_D3 4

DDR_M0_D3 3

DDR_M0_D3 2

DDR_M0_D3 1

DDR_M0_D2 5

DDR_M0_D3 0

DDR_M0_D2 4

DDR_M0_D2 8

DDR_M0_D2 6

DDR_M0_D2 9

DDR_M0_D2 7

DDR_M0_D1 8

DDR_M0_D1 6

DDR_M0_D2 3

DDR_M0_D2 2

DDR_M0_D2 1

DDR_M0_D1 9

DDR_M0_D1 7

DDR_M0_D2 0

DDR_M0_D1 5

DDR_M0_D1 4

DDR_M0_D1 3

DDR_M0_D1 2

DDR_M0_D1 1

DDR_M0_D1 0

DDR_M0_D9

DDR_M0_D8

DDR_M0_D7

DDR_M0_D6

DDR_M0_D5

DDR_M0_D4

DDR_M0_D3

DDR_M0_D2

DDR_M0_D1

DDR_M0_D0

2

DDR_M0_D[3 2..63] <19>

DDR_M0_D[0 ..31] <19>

1

B B

Place close to SOC pins

+1.35V

@

RC5

10K_0402_1 %

Pull high 10K on page 36

1 2

SOC_DRAM_PW ROK

1 2

RC180 0 _0402_5%

SHORT@

Power Name and Connection Check OK

DDR_PWR OK

DDR_PWROK(BTM) From Power controller

DDR_PWR OK <36>

+1.35V_DDR_VDD Q + 0.675V_M0_VREFCA

RC2 4.7K_ 0402_1%

RC6 4.7K_ 0402_1%

RC8 4.7K_ 0402_1%

RC10 4.7K_0402_1 %

8 mils minimum for maximum of 300 mils in breakout area

+0.675V_M0_VREFC A_R

1 2

1 2

1 2

1 2

SD0344701 80

+0.675V_M0_VREFD Q_R

1 2

SHORT@

RC3 0 _0402_5%

1 2

SHORT@

RC9 0 _0402_5%

1

CC1

.1U_0402_1 6V7K

2

+0.675V_M0_VREFD Q+1.35V_DDR_VDD Q

1

CC3

.1U_0402_1 6V7K

2

Place close to SOC pins Place close to SOC pins

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/11/10 2015/11/25

2014/11/10 2015/11/25

2014/11/10 2015/11/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Docu ment Number Rev

Size Docu ment Number Rev

Size Docu ment Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

P08-BSW(1/8) DDR3L-CH0

P08-BSW(1/8) DDR3L-CH0

P08-BSW(1/8) DDR3L-CH0

LA-C571P

LA-C571P

LA-C571P

1

8 44Tuesday, June 16, 2015

8 44Tuesday, June 16, 2015

8 44Tuesday, June 16, 2015

1.0

1.0

1.0

5

Main Func = CPU

D D

C C

B B

4

1 2

RC11182_0402_ 1% @

Place close to SOC pins

SOC_VCCA_PWR OK<12>

1 2

C1159 22P_0402_5 0V8J

SOC_VCCA_PWR OK

ESD@

SOC_VCCA_PWR OK

DDR_M1_RC OMP

3

BD5

BD7

BF10

BF6

BB5

BJ9

BE2

BD10

BE8

BB8

BH6

BD12

BH7

BJ6

BC12

BB7

BF2

AY14

BH8

BG9

BA14

BH10

AU16

AY16

BD16

BF16

AY12

BD14

BF14

BB10

AT24

AU24

AV18

BA16

AT26

AU26

BA12

AV26

BA26

BH24

BD22

AY18

BG13

BA1

AP10

AT6

AP2

BH22

BG23

BC24

BC22

AT22

AT20

BH14

BG15

AY2

BA3

AT12

AT13

AV7

AV6

AM2

AM3

@

UC1B

DDR3_M1_MA_15

DDR3_M1_MA_14

DDR3_M1_MA_13

DDR3_M1_MA_12

DDR3_M1_MA_11

DDR3_M1_MA_10

DDR3_M1_MA_9

DDR3_M1_MA_8

DDR3_M1_MA_7

DDR3_M1_MA_6

DDR3_M1_MA_5

DDR3_M1_MA_4

DDR3_M1_MA_3

DDR3_M1_MA_2

DDR3_M1_MA_1

DDR3_M1_MA_0

DDR3_M1_BS_2

DDR3_M1_BS_1

DDR3_M1_BS_0

DDR3_M1_CASB

DDR3_M1_RASB

DDR3_M1_WEB

DDR3_M1_CSB_1

DDR3_M1_CSB_0

DDR3_M1_CK_1

DDR3_M1_CKB_1

DDR3_M1_CKE_1

DDR3_M1_CK_0

DDR3_M1_CKB_0

DDR3_M1_CKE_0

RSVD1

RSVD2

DDR3_M1_ODT_0

DDR3_M1_ODT_1

DDR3_M1_OCAVREF

DDR3_M1_ODQVREF

DDR3_M1_DRAMRSTB

DDR3_VCCA_PWROK

DDR3_M1_RCOMPPD

DDR3_M1_DM_7

DDR3_M1_DM_6

DDR3_M1_DM_5

DDR3_M1_DM_4

DDR3_M1_DM_3

DDR3_M1_DM_2

DDR3_M1_DM_1

DDR3_M1_DM_0

DDR3_M1_DQS_7

DDR3_M1_DQSB_7

DDR3_M1_DQS_6

DDR3_M1_DQSB_6

DDR3_M1_DQS_5

DDR3_M1_DQSB_5

DDR3_M1_DQS_4

DDR3_M1_DQSB_4

DDR3_M1_DQS_3

DDR3_M1_DQSB_3

DDR3_M1_DQS_2

DDR3_M1_DQSB_2

DDR3_M1_DQS_1

DDR3_M1_DQSB_1

DDR3_M1_DQS_0

DDR3_M1_DQSB_0

BSW-MCP-ED S_FCBGA1170

CHV_MCP_EDS

DDR1

2 OF 13

DDR3_M1_DQ_63

DDR3_M1_DQ_62

DDR3_M1_DQ_61

DDR3_M1_DQ_60

DDR3_M1_DQ_59

DDR3_M1_DQ_58

DDR3_M1_DQ_57

DDR3_M1_DQ_56

DDR3_M1_DQ_55

DDR3_M1_DQ_54

DDR3_M1_DQ_53

DDR3_M1_DQ_52

DDR3_M1_DQ_51

DDR3_M1_DQ_50

DDR3_M1_DQ_49

DDR3_M1_DQ_48

DDR3_M1_DQ_47

DDR3_M1_DQ_46

DDR3_M1_DQ_45

DDR3_M1_DQ_44

DDR3_M1_DQ_43

DDR3_M1_DQ_42

DDR3_M1_DQ_41

DDR3_M1_DQ_40

DDR3_M1_DQ_39

DDR3_M1_DQ_38

DDR3_M1_DQ_37

DDR3_M1_DQ_36

DDR3_M1_DQ_35

DDR3_M1_DQ_34

DDR3_M1_DQ_33

DDR3_M1_DQ_32

DDR3_M1_DQ_31

DDR3_M1_DQ_30

DDR3_M1_DQ_29

DDR3_M1_DQ_28

DDR3_M1_DQ_27

DDR3_M1_DQ_26

DDR3_M1_DQ_25

DDR3_M1_DQ_24

DDR3_M1_DQ_23

DDR3_M1_DQ_22

DDR3_M1_DQ_21

DDR3_M1_DQ_20

DDR3_M1_DQ_19

DDR3_M1_DQ_18

DDR3_M1_DQ_17

DDR3_M1_DQ_16

DDR3_M1_DQ_15

DDR3_M1_DQ_14

DDR3_M1_DQ_13

DDR3_M1_DQ_12

DDR3_M1_DQ_11

DDR3_M1_DQ_10

DDR3_M1_DQ_9

DDR3_M1_DQ_8

DDR3_M1_DQ_7

DDR3_M1_DQ_6

DDR3_M1_DQ_5

DDR3_M1_DQ_4

DDR3_M1_DQ_3

DDR3_M1_DQ_2

DDR3_M1_DQ_1

DDR3_M1_DQ_0

BG21

BH26

BJ25

BG26

BG22

BH20

BG25

BJ21

BD26

BF24

BA20

BD20

BD24

BA22

BC20

BF20

AV22

AV20

BD18

BF18

AU22

AU20

BA18

BC18

BH16

BH18

BJ13

BH12

BJ17

BG17

BG11

BG12

BB3

AW1

BC2

AW3

AV3

BC1

AV2

BD2

AV12

AP13

AV13

AT10

AP14

AT16

AP12

AT14

AV9

AY4

AT4

AP7

AV4

AY6

AT7

AP6

AP3

AR1

AK2

AL1

AR3

AT2

AL3

AK3

2

1

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/11/10 2015/11/25

2014/11/10 2015/11/25

2014/11/10 2015/11/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Docu ment Number Rev

Size Docu ment Number Rev

Size Docu ment Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

P09-BSW(2/8) DDR3L-CH1

P09-BSW(2/8) DDR3L-CH1

P09-BSW(2/8) DDR3L-CH1

LA-C571P

LA-C571P

LA-C571P

1

9 44Tuesday, June 16, 2015

9 44Tuesday, June 16, 2015

9 44Tuesday, June 16, 2015

1.0

1.0

1.0

5

4

3

2

1

Main Func = CPU

@

UC1C

HDMI_TX2+<21>

SOC_DP0_HPD #<21>

SOC_DP0_CT RL_CLK<21>

SOC_DP0_CT RL_DATA<21>

EDP_CPU_LANE _P0<20 >

EDP_CPU_LANE _N0<20>

EDP_CPU_LANE _P1<20 >

EDP_CPU_LANE _N1<20>

EDP_CPU_AUX<20>

EDP_CPU_AUX#<20>

EDP_CPU_HP D<20>

SOC_DDI1_ENBKL<18>

SOC_DDI1_PW M<18>

SOC_DDI1_ENVDD<18 >

1 2

SHORT@

1 2

SHORT@

HDMI_TX2-<21>

HDMI_TX1+<21>

HDMI_TX1-<21>

HDMI_TX0+<21>

HDMI_TX0-<21>

HDMI_CLK+<21>

HDMI_CLK-<21>

T78 @TP

T79 @TP

T65 @TP

T66 @TP

T67 @TP

1 2

RC20

402_0402_ 1%

T68 @TP

T69 @TP

T70 @TP

T71 @TP

1 2

RC22

402_0402_ 1%

D D

<HDMI>

<eDP>

C C

<WIN7 Kernel DBG>

B B

UART_0_CT XD_DRXD_OP<25>

UART_0_CRXD_ DTXD_OP<25>

UART_0_CT XD_DRXD_OP

UART_0_CRXD_ DTXD_OP

RC391 0_0402_5%

RC392 0_0402_5%

HDMI_TX2+

HDMI_TX2-

HDMI_TX1+

HDMI_TX1-

HDMI_TX0+

HDMI_TX0-

HDMI_CLK+

HDMI_CLK-

SOC_DP0_AUXP

SOC_DP0_AUXN

SOC_DP0_HPD #

SOC_DP0_CT RL_CLK

SOC_DP0_CT RL_DATA

SOC_DDI0_ENBKL

SOC_DDI0_PW M

SOC_DDI0_ENVDD

DDI0_PLLOBS_P

DDI0_PLLOBS_N

EDP_CPU_LANE _P0

EDP_CPU_LANE _N0

EDP_CPU_LANE _P1

EDP_CPU_LANE _N1

EDP_TXP2

EDP_TXN2

EDP_TXP3

EDP_TXN3

EDP_CPU_AUX

EDP_CPU_AUX#

EDP_CPU_HP D

SOC_DDI1_ENBKL

SOC_DDI1_PW M

SOC_DDI1_ENVDD

DDI1_PLLOBS_P

DDI1_PLLOBS_N

SOC_DP2_CT RL_CLK

SOC_DP2_CT RL_DATA

D50

DDI0_TXP_0

C51

DDI0_TXN_0

H49

DDI0_TXP_1

H50

DDI0_TXN_1

F53

DDI0_TXP_2

F52

DDI0_TXN_2

G53

DDI0_TXP_3

G52

DDI0_TXN_3

H47

DDI0_AUXP

H46

DDI0_AUXN

W51

HV_DDI0_HPD

Y51

HV_DDI0_DDC_SCL

Y52

HV_DDI0_DDC_SDA

V52

PANEL0_BKLTEN

V51

PANEL0_BKLTCTL

W53

PANEL0_VDDEN

F38

DDI0_PLLOBS_P

G38

DDI0_PLLOBS_N

J51

DDI1_TXP_0

H51

DDI1_TXN_0

K51

DDI1_TXP_1

K52

DDI1_TXN_1

L53

DDI1_TXP_2

L51

DDI1_TXN_2

M52

DDI1_TXP_3

M51

DDI1_TXN_3

M42

DDI1_AUXP

K42

DDI1_AUXN

R51

HV_DDI1_HPD

P51

PANEL1_BKLTEN

P52

PANEL1_BKLTCTL

R53

PANEL1_VDDEN

F47

DDI1_PLLOBS_P

F49

DDI1_PLLOBS_N

F40

DDI2_TXP_0

G40

DDI2_TXN_0

J40

DDI2_TXP_1

K40

DDI2_TXN_1

F42

DDI2_TXP_2

G42

DDI2_TXN_2

D44

DDI2_TXP_3

F44

DDI2_TXN_3

D48

DDI2_AUXP

C49

DDI2_AUXN

U51

HV_DDI2_HPD

T51

HV_DDI2_DDC_SCL

T52

HV_DDI2_DDC_SDA

B53

RSVD6

A52

RSVD3

E52

RSVD9

D52

RSVD8

B50

RSVD5

B49

RSVD4

E53

RSVD10

C53

RSVD7

A51

RSVD2

A49

RSVD1

G44

RSVD11

BSW-MCP-ED S_FCBGA1170

CHV_MCP_EDS

M44

RSVD15

K44

RSVD12

K48

RSVD14

K47

RSVD13

RSVD17

RSVD16

MCSI_COMP

SDMMC1_D0

SDMMC1_D1

SDMMC1_D2

MMC1_D5

MMC1_D6

MMC1_D7

MMC1_RCLK

SDMMC2_D0

SDMMC2_D1

SDMMC2_D2

SDMMC3_D0

SDMMC3_D1

SDMMC3_D2

SDMMC3_D3

T44

T45

Y47

Y48

V45

V47

V50

V48

T41

T42

P50

P48

P47

P45

M48

M47

T50

T48

P44

MCSI_COMP

AB41

GP_CAMSB00

AB45

GP_CAMSB01

AB44

GP_CAMSB02

AC53

GP_CAMSB03

AB51

GP_CAMSB04

AB52

GP_CAMSB05

AA51

GP_CAMSB06

AB40

GP_CAMSB07

Y44

GP_CAMSB08

Y42

Y41

V40

GP_CAMSB11

M7

EMMC_1_CLK

P6

EMMC_1_CMD

M6

EMMC_1_D0

M4

EMMC_1_D1

P9

EMMC_1_D2

P7

EMMC_1_D3

T6

EMMC_1_D4

T7

EMMC_1_D5

T10

EMMC_1_D6

T12

EMMC_1_D7

T13

EMMC_1_RCL K

P13

EMMC_1_RCO MP

K10

K9

M12

M10

K7

K6

SOC_LID_OUT#

F2

D2

K3

J1

J3

H3

G2

K2

L3

P12

SDIO_3_RCOMP

1 2

RC21 15 0_0402_1%

GP_CAMSB00 <16>

GP_CAMSB01 <16>

GP_CAMSB02 <16>

GP_CAMSB03 <16>

GP_CAMSB04 <16>

GP_CAMSB05 <16>

GP_CAMSB06 <16>

GP_CAMSB07 <16>

GP_CAMSB08 <11,16>

GP_CAMSB11 <11>

EMMC_1_CLK <22>

EMMC_1_CMD <22>

EMMC_1_D0 <22>

EMMC_1_D1 <22>

EMMC_1_D2 <22>

EMMC_1_D3 <22>

EMMC_1_D4 <22>

EMMC_1_D5 <22>

EMMC_1_D6 <22>

EMMC_1_D7 <22>

EMMC_1_RCL K <22>

1 2

RC23 10 0_0402_1%

SOC_LID_OUT# <18>

12

@

RC33

80.6_0402_1 %

Should be 80_0402_1%

<eMMC>

MCSI_1_CLKP

MCSI_1_CLKN

DDI0

DDI1

SDMMC1

DDI2

SDMMC2

NC's

SDMMC3

3 OF 13

MCSI_1_DP_0

MCSI_1_DN_0

MCSI_1_DP_1

MCSI_1_DN_1

MCSI_1_DP_2

MCSI_1_DN_2

MCSI and Camera interface

MCSI_1_DP_3

MCSI_1_DN_3

MCSI_2_CLKP

MCSI_2_CLKN

MCSI_2_DP_0

MCSI_2_DN_0

MCSI_2_DP_1

MCSI_2_DN_1

GP_CAMERASB00

GP_CAMERASB01

GP_CAMERASB02

GP_CAMERASB03

GP_CAMERASB04

GP_CAMERASB05

GP_CAMERASB06

GP_CAMERASB07

GP_CAMERASB08

GP_CAMERASB09

GP_CAMERASB10

GP_CAMERASB11

SDMMC1_CLK

SDMMC1_CMD

SDMMC1_D3_CD_B

MMC1_D4_SD_WE

SDMMC1_RCOMP

SDMMC2_CLK

SDMMC2_CMD

SDMMC2_D3_CD_B

SDMMC3_CLK

SDMMC3_CMD

SDMMC3_CD_B

SDMMC3_1P8_EN

SDMMC3_PWR_EN_B

SDMMC3_RCOMP

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/11/10 2015/11/25

2014/11/10 2015/11/25

2014/11/10 2015/11/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Docu ment Number Rev

Size Docu ment Number Rev

Size Docu ment Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

P10-BSW(3/8) DDI,MCSI,SDMMC

P10-BSW(3/8) DDI,MCSI,SDMMC

P10-BSW(3/8) DDI,MCSI,SDMMC

LA-C571P

LA-C571P

LA-C571P

1

10 44Tu esday, June 16, 2015

10 44Tu esday, June 16, 2015

10 44Tu esday, June 16, 2015

1.0

1.0

1.0

5

Main Func = CPU

D D

<WLAN>

+1.8VALW

RC231 10K_0402_5 %

RC383 10K_0402_5 %

RC242 10K_0402_5 %

RC189 10K_0402_5 %@

RC326 10K_0402_5 %@

RC174 1K_0402_5%@

RC175 1K_0402_5%@

RC104 1K_0402_5%@

C C

Pull High 10k at LED Page

SOC_SATALED#<28,32>

+1.8VALW

B B

WL_OFF#<28,32>

SOC_TP_INT#<29>

BT_ON#<28>

SOC_SCI#<17>

SOC_SMI#<17>

A A

PCIE_PTX_C_DRX_P2<28>

PCIE_PTX_C_DRX_N 2<28>

PCIE_CRX_DTX_P2<28>

PCIE_CRX_DTX_N2<28>

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

SOC_XTAL19_IN SOC_XTAL19_OUT

1

CC7 12P_0402_50V8J

2

1

2

Change P/N to SJ10000N700

19.2MHz_12pF

1 2

RC56 4.7K_0402_5 %

1 2

RC58 4.7K_0402_5 %

GPIO_SUS6 H +1.8VALW Page 11

SOC_SCI# PH +1.8VS Page 17 for 9022

EC_SCI# PH +3.3VS Page 32 for 9012

GPIO_SUS7 H +1.8VALW Page 11

SOC_SMI# PH +1.8VALW Page 17

EC_SMI# PH +3VALW_EC Page 32

WLAN_CLKR EQ#

SOC_TS_EN

SATA_DEVSLP

SATA_LED#

EMMC_1_RST #

I2C_5_SCL_R

I2C_5_SDA_R

SOC_SMB_ALERT #

Need to confirm leakage

+1.8VS

123

D

1 2

RC37 200K_0402_1%

YC1

1

GND

SJ10000N70 0

19.2MHZ_12PF_ 7V19200001

WL_OFF#

SOC_TP_INT# SEC_GPIO_SUS10

BT_ON# SEC_GPIO_SUS9

SOC_SCI#

SOC_SMI#

GP_CAMSB08<10 ,16>

GP_CAMSB11<10>

5

PCIE_PTX_C_DRX_P2

PCIE_PTX_C_DRX_N 2

RC26

10K_0402_5 %

1 2

G

SATA_LED#

S

QC3

MESS138W -G_SOT323-3

3

4

DDI0_ENABLE

DDI1_ENABLE

1 2

1 2

1 2

1 2

1 2

CC8 12P_0402_50V8J

2

1

SHORT@

SHORT@

SHORT@

SHORT@

SHORT@

GP_CAMSB08

GP_CAMSB11

3

GND

RC380 0_0402_5%

RC334 0_0402_5%

RC338 0_0402_5%

RC227 0_0402_5%

RC228 0_0402_5%

不不不不不不不不不不不不

不不不不不不不不不不不不

不不不不不不不不不不不不

不不不不不不不不不不不不

不不不不不不不不不不不不

1 2

C1 .1U_0402_1 6V7K

1 2

C2 .1U_0402_1 6V7K

WLAN_CLKR EQ#<28>

CLK_PCIE_WL AN< 28>

CLK_PCIE_WL AN#<28>

GPIO_SUS3

GPIO_SUS6

GPIO_SUS7

不不不不不不不不

+1.8VALW

Place close to SOC pins

1 2

@

RC35 0_0402_5%

1 2

RC36 402_0402_1%

T120@TP

T142@TP

T122@TP

T123@TP

T124@TP

1 2

RC60 10K_0402_5 %

1 2

RC62 10K_0402_5 %@

1 2

RC64 100K_0402_ 5%

1 2

RC66 10K_0402_5 %

1 2

RC68 10K_0402_5 %@

1 2

RC80 10K_0402_5 %@

1 2

RC118 10K_0402_5 %@

1 2

RC74 10K_0402_5 %@

1 2

RC76 10K_0402_5 %@

1 2

RC386 4.7K_0402_5 %

LPC33@

1 2

RC78 10K_0402_5 %@

1 2

RC82 10K_0402_5 %@

PCIE_CTX_DRX_P2

PCIE_CTX_DRX_N2

PCIE_CRX_DTX_P2

PCIE_CRX_DTX_N2

WLAN_CLKR EQ#

CLK_PCIE_WL AN

CLK_PCIE_WL AN#

CLK_PCIE_P4

CLK_PCIE_N4

PCIE_OBS_P

PCIE_OBS_N

SOC_SPI_CLK

SOC_SPI_CS#0

SOC_SPI_CS#1

SOC_SPI_SI

SOC_SPI_SO

SOC_XTAL19_IN

SOC_XTAL19_OUT

BIOS/EFI Top Swap

4

@

UC1D

C24

PCIE_TXP0

B24

PCIE_TXN0

G20

PCIE_RXP0

J20

PCIE_RXN0

A25

PCIE_TXP1

C25

PCIE_TXN1

D20

PCIE_RXP1

F20

PCIE_RXN1

B26

PCIE_TXP2

C26

PCIE_TXN2

D22

PCIE_RXP2

F22

PCIE_RXN2

A27

PCIE_TXP3

C27

PCIE_TXN3

G24

PCIE_RXP3

J24

PCIE_RXN3

AM10

PCIE_CLKREQ0B

AM12

PCIE_CLKREQ1B

AK14

PCIE_CLKREQ2B

AM14

PCIE_CLKREQ3B

A21

CLK_DIFF_P_0

C21

CLK_DIFF_N_0

C19

CLK_DIFF_P_1

B20

CLK_DIFF_N_1

C18

CLK_DIFF_P_2

B18

CLK_DIFF_N_2

C17

CLK_DIFF_P_3

A17

CLK_DIFF_N_3

C16

RSVD20

B16

RSVD19

D26

PCIE_OBSP

F26

PCIE_OBSN

V14

SPI1_CLK

Y13

SPI1_CS0_B

Y12

SPI1_CS1_B

V13

SPI1_MISO

V12

SPI1_MOSI

BSW-MCP-ED S_FCBGA1170

1 2

RC382 0_0402_5%

SHORT@

1 2

RC38 0_0402_5%

SHORT@

1 2

RC39 0_0402_5%

SHORT@

1 2

RC40 2.49K_0402_ 1%

1 2

RC41 49.9_0402_1 %

Place close to SOC pins

XDP_GPIO_DFX0<16>

XDP_GPIO_DFX1<16>

XDP_GPIO_DFX2<16>

XDP_GPIO_DFX3<16>

XDP_GPIO_DFX4<16>

XDP_GPIO_DFX5<16>

XDP_GPIO_DFX6<16>

XDP_GPIO_DFX7<16>

XDP_GPIO_DFX8<16>

GPIO_SUS5<12>

GPIO_SUS6<16>

1 2

RC42 100_0402_ 1%

4

GPIO_SUS2

GPIO_SUS3

GPIO_SUS4

GPIO_SUS5

GPIO_SUS6

GPIO_SUS7

SEC_GPIO_SUS8

SEC_GPIO_SUS9

SEC_GPIO_SUS10

SEC_GPIO_SUS11

GP_CAMSB08

GP_CAMSB11

T133@TP

CHV_MCP_EDS

PCIe

SPI

4 OF 13

SOC_KBRST#GP_CAMSB11

SOC_XTAL19_IN_R

SOC_XTAL19_OUT _R

ICLKICOMP

ICLKRCOMP

XDP_GPIO_DFX0

XDP_GPIO_DFX1

XDP_GPIO_DFX2

XDP_GPIO_DFX3

XDP_GPIO_DFX4

XDP_GPIO_DFX5

XDP_GPIO_DFX6

XDP_GPIO_DFX7

XDP_GPIO_DFX8

DDI0_ENABLE

DDI1_ENABLE

GPIO_SUS2

GPIO_SUS3

GPIO_SUS4

GPIO_SUS5

GPIO_SUS6

GPIO_SUS7

SEC_GPIO_SUS9

SEC_GPIO_SUS8

SEC_GPIO_SUS10

SEC_GPIO_SUS11

SOC_COLD_RE SET#

1 2

RC61 10K_0402_5 %@

1 2

RC63 10K_0402_5 %@

1 2

RC65 10K_0402_5 %@

1 2

RC67 4.7K_0402_5 %@

1 2

RC105 4.7K_0402_5 %

1 2

RC75 10K_0402_5 %@

1 2

RC77 10K_0402_5 %@

1 2

RC395 10K_0402_5 %

LPC18@

1 2

RC79 100K_0402_ 5%

1 2

RC83 100K_0402_ 5%@

SATA_TXP0

SATA_TXN0

SATA_RXP0

SATA_RXN0

SATA_TXP1

SATA_TXN1

SATA_RXP1

SATA_RXN1

SATA_LEDN

SATA_GP0

SATA

SATA_GP1

SATA_GP2

SATA_GP3

SATA_OBSP

SATA_OBSN

FST_SPI_CLK

FST_SPI_CS0_B

FST_SPI_CS1_B

FST_SPI_CS2_B

FST_SPI_D0

FAST SPI

FST_SPI_D1

FST_SPI_D2

FST_SPI_D3

MF_HDA_RSTB

MF_HDA_SDI1

MF_HDA_CLK

MF_HDA_SDI0

MF_HDA_SYNC

MF_HDA_SDO

MF_HDA_DOCKENB

MF_HDA_DOCKRSTB

AUDIO

GP_SSP_2_CLK

GP_SSP_2_FS

GP_SSP_2_TXD

GP_SSP_2_RXD

HDA_BIT_CLK_C

HDA_SYNC_C

HDA_SDOUT_C

HDA_RST#_C

SOC_KBRST# <32>

P24

M22

J26

N26

P20

N20

P26

K26

M26

AH45

A9

C9

B8

B7

B5

B4

AM40

AM41

AM44

AM45

AM47

AK48

AM48

AK41

AK42

AD51

AD52

AH50

AH48

AH51

AH52

AG51

AG53

AF52

AF51

AE51

AC51

AH40

Y3

3

C31

SATA_PTX_DRX_P0_C

B30

SATA_PTX_DRX_N0_ C

N28

SATA_PRX_DTX_P0_C

M28

SATA_PRX_DTX_N0_ C

C29

SATA_PTX_DRX_P1_C

A29

SATA_PTX_DRX_N1_ C

J28

SATA_PRX_DTX_P1_C

K28

SATA_PRX_DTX_N1_ C

AH3

SATA_LED#

AH2

AG3

SOC_TS_INT#

AG1

SATA_DEVSLP

AF3

EMMC_1_RST #

N30

SATA_OBS_P

M30

SATA_OBS_N

W3

SOC_FST_SPI_CLK

V4

SOC_FST_SPI_CS# 0

V6

SOC_TS_EN

V7

SOC_FST_SPI_CS# 2

V2

SOC_FST_SPI_D0

V3

SOC_FST_SPI_D1

U1

SOC_FST_SPI_D2

U3

SOC_FST_SPI_D3

AF13

HDA_RST#_C

AD6

HDA_SDIN1

AD9

HDA_BIT_CLK_C

AD7

HDA_SDIN0

AF12

HDA_SYNC_C

AF14

HDA_SDOUT_C

AB9

HDA_DOCKEN#

AB7

HDA_DOCKRST #

H4

SOC_SPKR

SPKR

AK9

AK10

AK12

AK13

1 2

RA6 75_0402_5 %EMI@

1 2

RA5 75_0402_5 %EMI@

1 2

RA7 75_0402_5 %EMI@

1 2

RA10 75_0402 _5%EMI@

@

UC1E

OSCIN

OSCOUT

RSVD13

RSVD17

ICLKICOMP

ICLKRCOMP

RSVD18

RSVD14

RSVD16

RSVD1

MF_PLT_CLK0

MF_PLT_CLK1

MF_PLT_CLK2

MF_PLT_CLK3

MF_PLT_CLK4

MF_PLT_CLK5

GPIO_DFX0

GPIO_DFX1

GPIO_DFX2

GPIO_DFX3

GPIO_DFX4

GPIO_DFX5

GPIO_DFX6

GPIO_DFX7

GPIO_DFX8

GPIO_SUS0

GPIO_SUS1

GPIO_SUS2

GPIO_SUS3

GPIO_SUS4

GPIO_SUS5

GPIO_SUS6

GPIO_SUS7

SEC_GPIO_SUS9

SEC_GPIO_SUS8

SEC_GPIO_SUS10

SEC_GPIO_SUS11

GPIO0_RCOMP

GPIO_ALERT

BSW-MCP-ED S_FCBGA1170

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

iCLK

PLTFM CLK's

GPIO_DFX

GPIO_SUS

Issued Date

Issued Date

Issued Date

CHV_MCP_EDS

1 2

RC34

402_0402_ 1%

RC93 10_0402_5 %EMI@

RC89 33_0402_5 %EMI@

RC97 33_0402_5 %@

RC94 10_0402_5 %EMI@

RC90 10_0402_5 %EMI@

RC91 10_0402_5 %EMI@

RC92 10_0402_5 %EMI@

HDA_BITCLK_AUDIO

RESERVED

SMBUS

5 OF 13

2

SATA_PTX_DRX_P0_C <27>

SATA_PTX_DRX_N0_ C <27>

SATA_PRX_DTX_P0_C <27>

SATA_PRX_DTX_N0_ C <27>

SATA_PTX_DRX_P1_C <27>

SATA_PTX_DRX_N1_ C <27>

SATA_PRX_DTX_P1_C <27>

SATA_PRX_DTX_N1_ C <27>

SOC_TS_INT# <20>

SATA_DEVSLP < 27>

EMMC_1_RST # <22>

1 2

1 2

1 2

1 2

1 2

1 2

1 2

T102@TP

HDA_SDIN0 <23>

T132@TP

T121@TP

SOC_SPKR <23>

For EMI

CC74

22P_0402_5 0V8J

HDA_BITCLK_AUDIO <23>

HDA_SYNC_AUDIO < 23>

HDA_SDOUT_AUD IO <23>

HDA_RST_AUDIO# <23>

RSVD3

RSVD2

RSVD9

RSVD8

RSVD5

RSVD7

RSVD4

RSVD6

RSVD11

RSVD10

RSVD12

RSVD15

I2C0_SCL

I2C0_SDA

I2C1_SCL

I2C1_SDA

I2C2_SCL

I2C

I2C2_SDA

I2C3_SCL

I2C3_SDA

I2C4_SCL

I2C4_SDA

I2C5_SCL

I2C5_SDA

I2C6_SCL

I2C6_SDA

RSVD21

RSVD22

MF_SMB_CLK

MF_SMB_DATA

MF_SMB_ALERTB

2014/11/10 2015/11/25

2014/11/10 2015/11/25

2014/11/10 2015/11/25

SPI_CLK

SPI_CS#0

T104@TP

SPI_CS#2

SPI_MOSI

SPI_MISO

SPI_WP#

SPI_HOLD#

1 2

EMI@

C11

B10

F12

F10

D12

E8

C7

D6

J12

F7

J14

L13

AK6

AH7

AF6

AH6

AF9

AF7

AE4

AD2

AC1

AD3

AB2

I2C_5_SCL

AC3

I2C_5_SDA

AA1

AB3

AA3

I2C_NFC_SCL

Y2

I2C_NFC_SDA

AM6

SOC_SMB_CLK

AM7

SOC_SMB_DATA

AM9

SOC_SMB_ALERT #GPIO0_RCOMP

Compal Secret Data

Compal Secret Data

Compal Secret Data

<HDD>

<ODD>

RC158 0_0402_5%

RC159 0_0402_5%

Deciphered Date

Deciphered Date

Deciphered Date

1 2

1 2

2

BIOS ROM

+1.8V_SPI

SHORT@

SHORT@

T143@TP

T144@TP

SOC_SMB_CLK <16,17>

SOC_SMB_DATA <16,17>

+1.8VALW +1.8V_SPI

1 2

RC86 3.3K_0402_5 %

1 2

RC88 3.3K_0402_5 %@

1 2

RC98 20K_0402_5 %@

1 2

RC99 20K_0402_5 %@

1 2

RC100 20K_0402_5 %

1 2

RC101 20K_0402_5 %

SPI_CS#0

SPI_CS#2

SPI_MOSI

SPI_MISO

SPI_WP#

SPI_HOLD#

SPI ROM ( 8MByte/1.8V/Quad-IO )

UC2

SPI_CS#0

SPI_MISO

SPI_WP#

I2C_5_SCL_R

I2C_5_SDA_R

<XDP/EC LS/Thermal Sensor LS>

1

CS#

DO(IO1)

WP#(IO2)

GND

HOLD#(IO3)

DI(IO0)

VCC

CLK

2

3

4

W25Q64D WSSIG_SO8

SA00006ZV00

Modification @ 2014/07/21

Reserve for EMI(Near SPI ROM)

1 2

SPI_CLK

I2C_5_SCL_R <29>

I2C_5_SDA_R <29>

Title

Title

Title

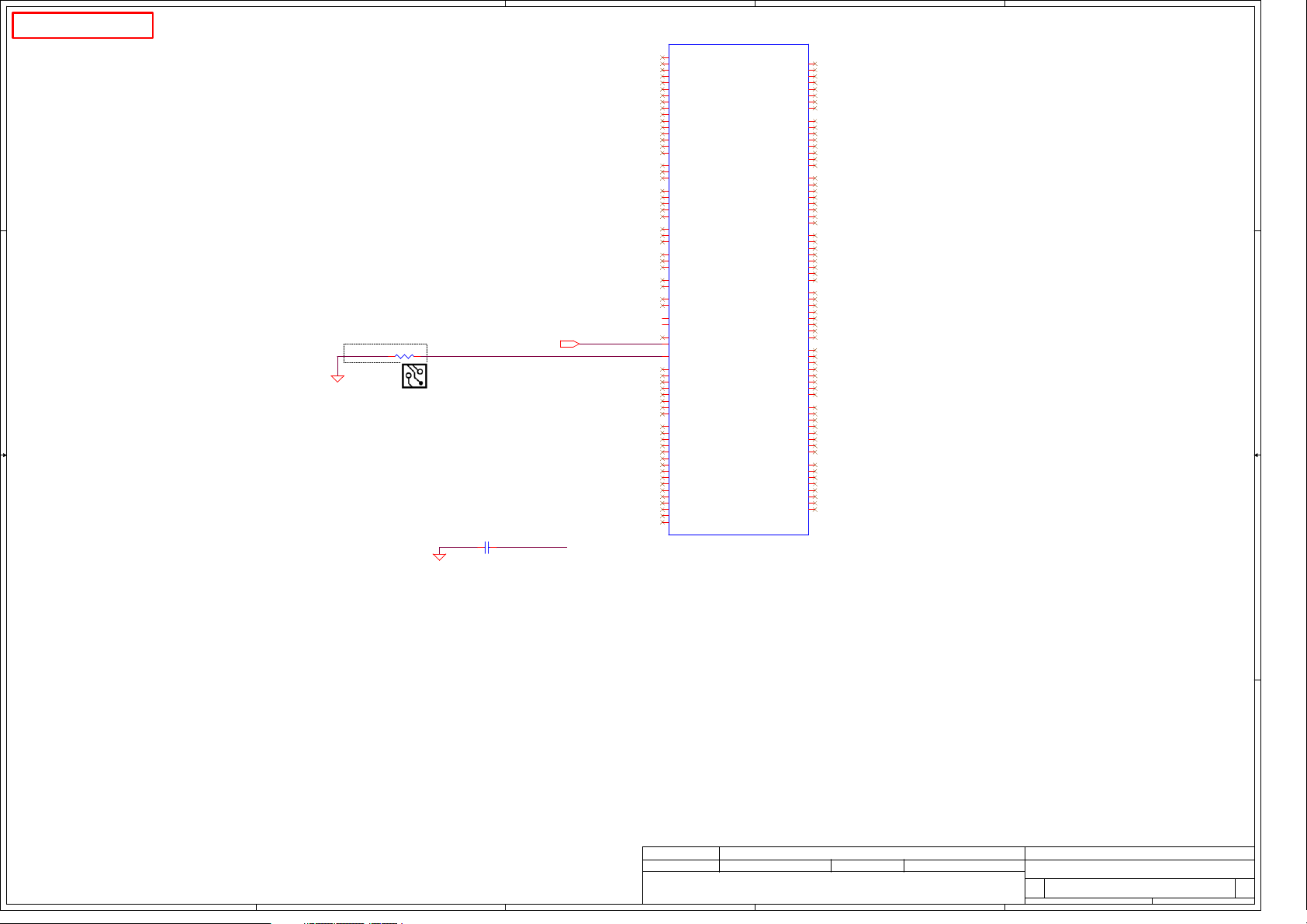

P11-BSW(4/8) PCIE,SATA,I2C,CLK

P11-BSW(4/8) PCIE,SATA,I2C,CLK

P11-BSW(4/8) PCIE,SATA,I2C,CLK

Size Docu ment Number Rev

Size Docu ment Number Rev

Size Docu ment Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

R1002

NEMI@

33_0402_5 %

<Touch PAD_LS>

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

LA-C571P

LA-C571P

LA-C571P

1

1 2

SHORT@

RC87 0_0402_5%

+1.8V_SPI

8

7

SPI_HOLD#

6

SPI_CLK

5

SPI_MOSI

12

C1014

NEMI@

10P_0402_5 0V8J

1

11 44Tu esday, June 16, 2015

11 44Tu esday, June 16, 2015

11 44Tu esday, June 16, 2015

1

CC76

.1U_0402_1 6V7K

2

1.0

1.0

1.0

5

Main Func = CPU

D D

+1.8VALW

+1.8V_XDP_AB

XDP_H_TCK

C C

B B

XDP_H_TRST #

+1.8VALW

1 2

RC147 2 0K_0402_5%

Pin Name

GPIO_SUS0

GPIO_SUS1

GPIO_SUS2

GPIO_SUS3

GPIO_SUS4

GPIO_SUS5

GPIO_SUS6

GPIO_SUS7

A A

SEC_GPIO_SUS8

SEC_GPIO_SUS9

SEC_GPIO_SUS10

GP_CAMERASB08

GP_CAMERASB09

GP_CAMERASB11

1 2

RC24 10 K_0402_5%

1 2

RC25 10 K_0402_5%

1 2

RC107 5 1_0402_5%XDP@

1 2

RC109 5 1_0402_5%XDP@

1 2

RC110 5 1_0402_5%XDP@

1 2

RC111 5 1_0402_5%XDP@

1 2

RC112 5 1_0402_5%XDP@

1 2

RC108 5 1_0402_5%XDP@

Place close to SOC pins

H_PROCHOT# _R

Purpose

DDI0 Detect

DDI1 Detect

A16 swap overdrive

DSI Display Detect

Boot BIOS Strap BBS

Flash Descriptor Security

Override

DFX Boot Halt Strap,

VISA Early POSM Debug Enable

DFX Sus Debug Strap

ICLK, USB2, DDI SFR

Supply Select

ICLK, USB2, DDI SFR Bypass

POSM Select

ICLK Xtal OSC Bypass

CCU SUS RO Bypass

RTC OSC Bypass

5

USB_OC0#

USB_OC1#

XDP_H_TDI

XDP_H_TDO

XDP_H_TMS

XDP_H_PREQ_BU F#

LPC_CLK_EC<32>

1 2

CC95 .1U _0402_16V7K

ESD@

H_PROCHOT#<32,34>

FAN_ALERT#<3 1>

Hardware Strap

PU/PD

PD

PD

PU

PD

PU

PU

PU

PU

PD

PU

PD

PD

PD

PD

XDP_H_TCK

XDP_H_TDO

XDP_H_TRST #

XDP_H_TDI

XDP_H_TMS

LPC_CLK_EC

H_PROCHOT#

FAN_ALERT#

Description Default State

1: DDI0 detected

0: DDI0 not detected

1: DDI1 detected

0: DDI1 not detected

1: Normal operation

0: Change Boot Loader address

1: DSI detected

0: DSI not detected

1: Boot from SPI

0: Boot from LPC

1: Security enabled

0: Security disabled

1: Normal operation

0: Halt boot enable

1: Normal operation

0: Sus Debug enabled

1: 1.35V supply

0: 1.25V supply

1: Bypass with 1.05V

0: No bypass

1: PMC

0: Fuse controller

1: Bypass

0: No bypass

1: Bypass

0: No bypass

1: Bypass

0: No bypass

4

PCH_USB3_T X0_P<25>

PCH_USB3_T X0_N<25>

PCH_USB3_R X0_P<25>

PCH_USB3_R X0_N<25>

1 2

RC43

402_0402_ 1%

1 2

CC102 .1U_0402_1 6V7KN ESD@

1 2

C1162 2 2P_0402_50V8JNESD@

1 2

C1163 2 2P_0402_50V8JNESD@

1 2

C1164 2 2P_0402_50V8JNESD@

1 2

C1165 2 2P_0402_50V8JNESD@

XDP_H_TCK<16>

XDP_H_TDI<16>

XDP_H_TDO<16>

XDP_H_TMS<16>

XDP_H_TRST #<16>

XDP_H_PRDY#<16>

XDP_H_PREQ_BU F#<16>

1 2

RC47 10K_0402_5%@

1 2

RC239 0_0402_5%

1 2

RC240 0_0402_5%@

LPC_CLKRU N#<32 >

LPC_FRAME#<32 >

LPC_AD0<32>

LPC_AD1<32>

LPC_AD2<32>

LPC_AD3<32>

1 2

RC48 100_0402_ 1%

LPC_SOC_SER IRQ<17>

1 2

RC236 0_0402_5%

SHORT@

1 2

RC237 0_0402_5%

@

Don't care,

if GPIO_SUS6 is pulled hgh

4

XDP_H_TCK

XDP_H_TDI

XDP_H_TDO

XDP_H_TMS

XDP_H_TRST #

XDP_H_PRDY#

XDP_H_PREQ_BU F#

EDM_SOC

LPC_CLKOUT 0

LPC_CLKOUT 1

LPC_CLKRU N#

LPC_FRAME#

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_HVT_RC OMP

LPC_SOC_SER IRQ

H_PROCHOT# _R

High

High

High

Low

High

High

High

High

Low

Low

Low

Low

Low

PCH_USB3_T X0_P

PCH_USB3_T X0_N

PCH_USB3_R X0_P

PCH_USB3_R X0_N

USB3_OBS_P

USB3_OBS_N

@

UC1F

B32

USB3_TXP0

C32

USB3_TXN0

F28

USB3_RXP0

D28

USB3_RXN0

A33

USB3_TXP1

C33

USB3_TXN1

F30

USB3_RXP1

D30

USB3_RXN1

C34

USB3_TXP2

B34

USB3_TXN2

G32

USB3_RXP2

J32

USB3_RXN2

C35

USB3_TXP3

A35

USB3_TXN3

G34

USB3_RXP3

J34

USB3_RXN3

D34

USB3_OBSP

F34

USB3_OBSN

C37

RSVD4

A37

RSVD1

F36

RSVD7

D36

RSVD6

M34

RSVD11

M32

RSVD10

C38

RSVD5

B38

RSVD2

G36

RSVD8

J36

RSVD9

N34

RSVD12

P34

RSVD13

BSW-MCP-ED S_FCBGA1170

@

UC1G

AF42

TCK

AD47

TDI

AF40

TDO

AD48

TMS

AB48

TRST_B

AD45

CX_PRDY_B

AF41

CX_PREQ_B

M13

RSVD5

P2

MF_LPC_CLKOUT0

R3

MF_LPC_CLKOUT1

T3

LPC_CLKRUNB

P3

LPC_FRAMEB

M3

MF_LPC_AD0

M2