5

D D

4

3

2

1

WASP 13 CS

C C

Whiskey Lake-U

2019-01

REV : A00

B B

<Core Design>

<Core Design>

<Core Design>

istron Corporation

istron Corporation

istron Corporation

W

W

A A

DY : None Installed

T

tle

Title

Title

UMA: UMA only installed

OPS: DIS only installed

5

4

3

i

ov

ov

ov

C

C

W

W

W

C

A

A

A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

4

4

4

Thursday, March 07, 2019

Thursday, March 07, 2019

Thursday, March 07, 2019

Date: Sheet

Date: Sheet

Date: Sheet

2

W

2

2

2

1

1

1

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

er Page

er Page

er Page

SP 13" WHL-U

SP 13" WHL-U

SP 13" WHL-U

1 1

1 1

1 1

0

0

0

0

0

0

A

A

o

o

o

f

f

f

1

A

06

06

06

5

WWW.AliSaler.Com

4

3

2

1

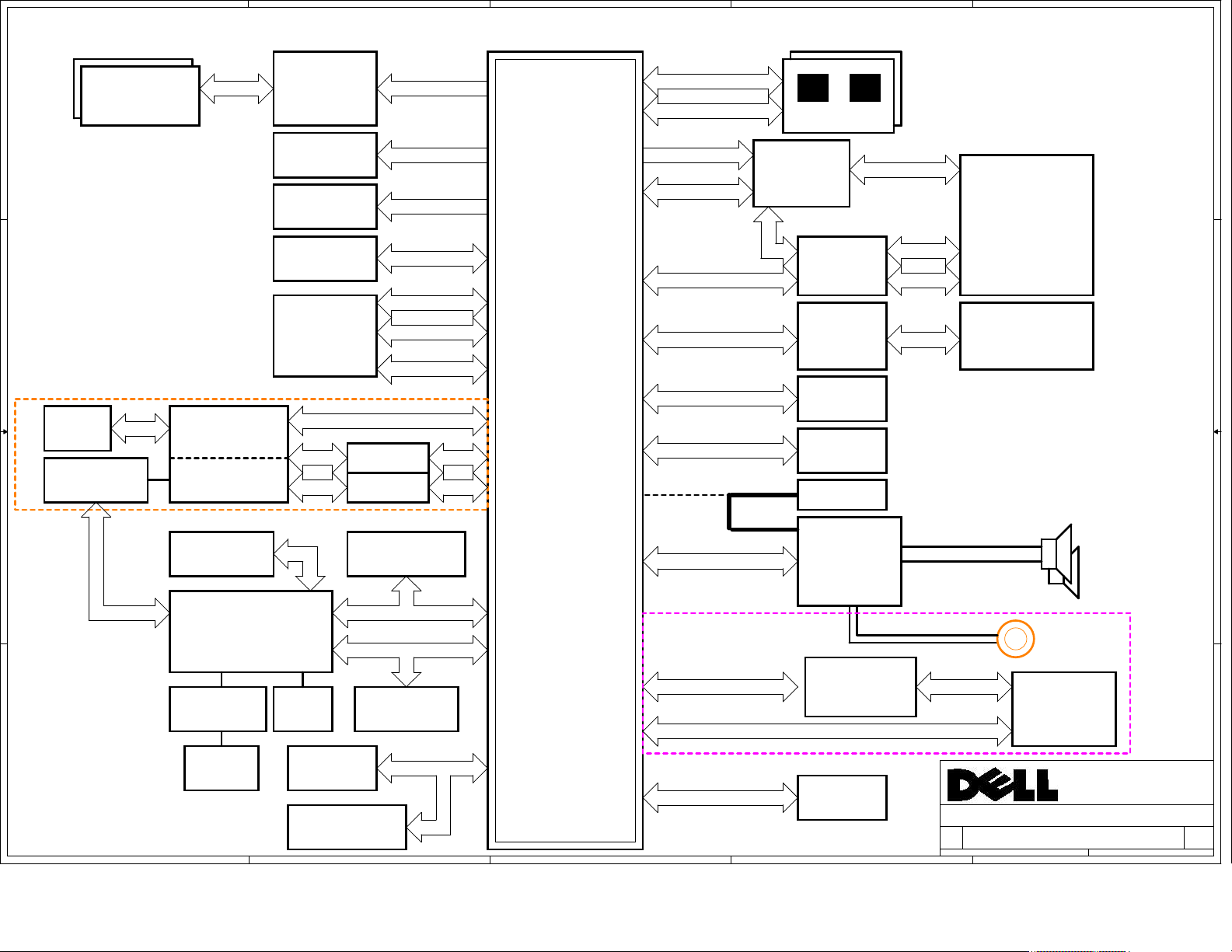

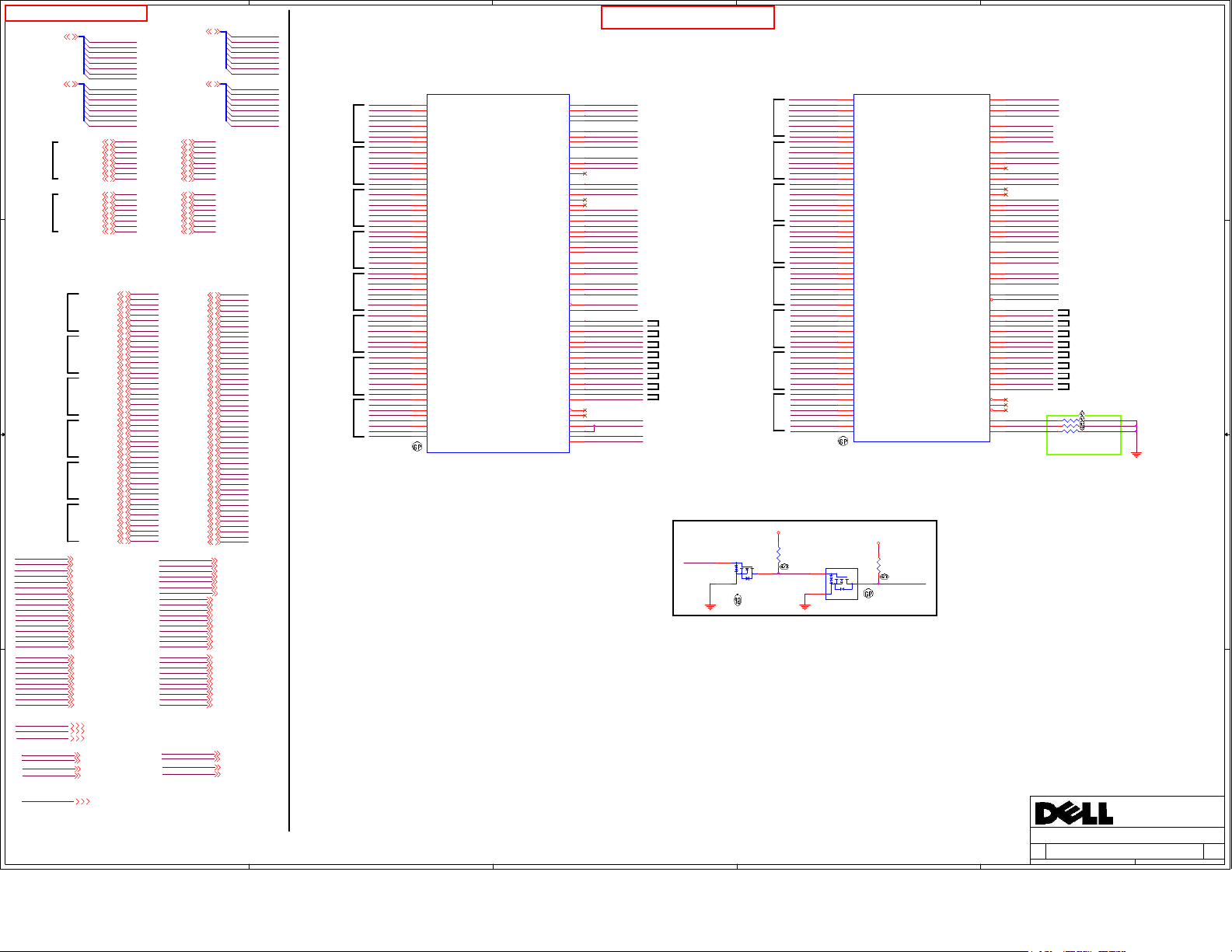

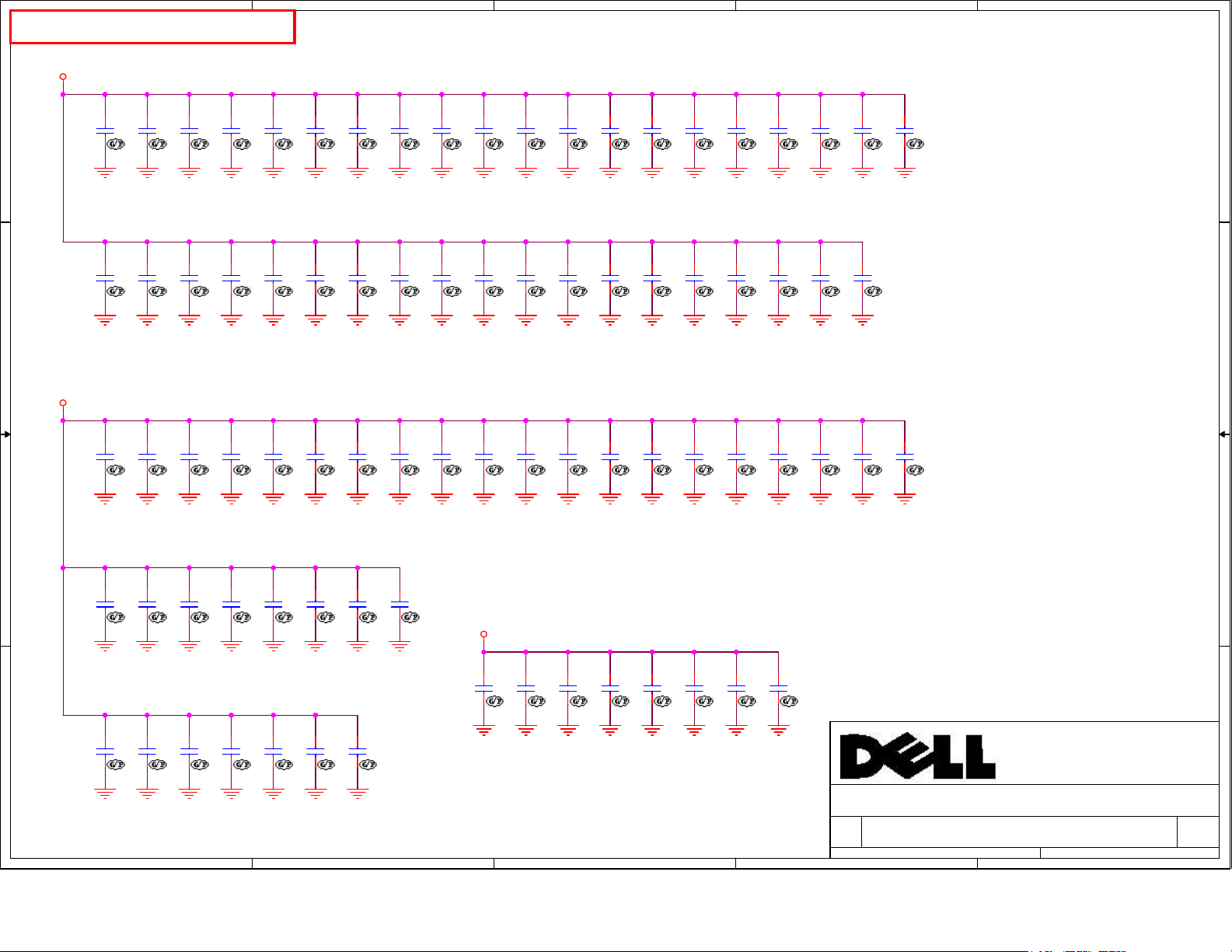

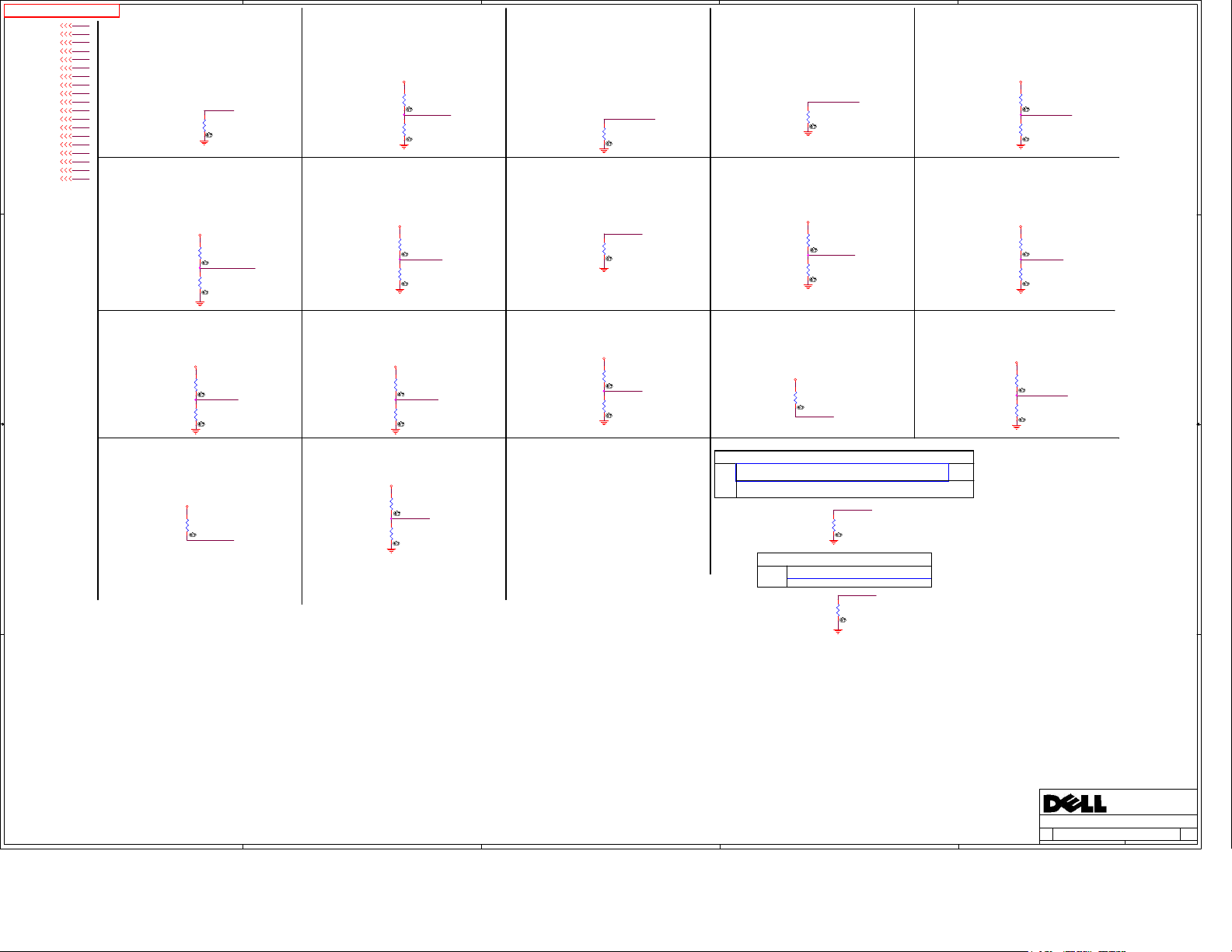

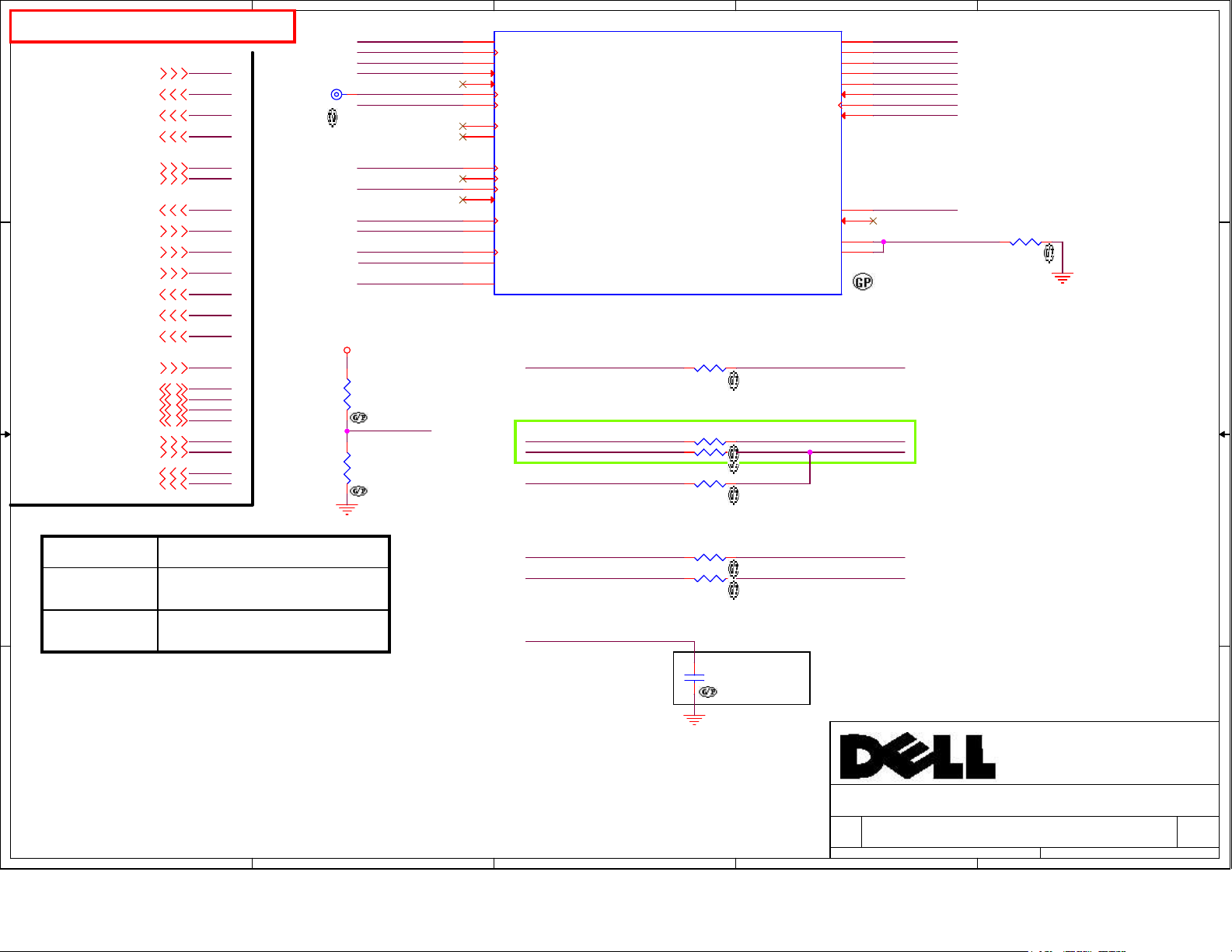

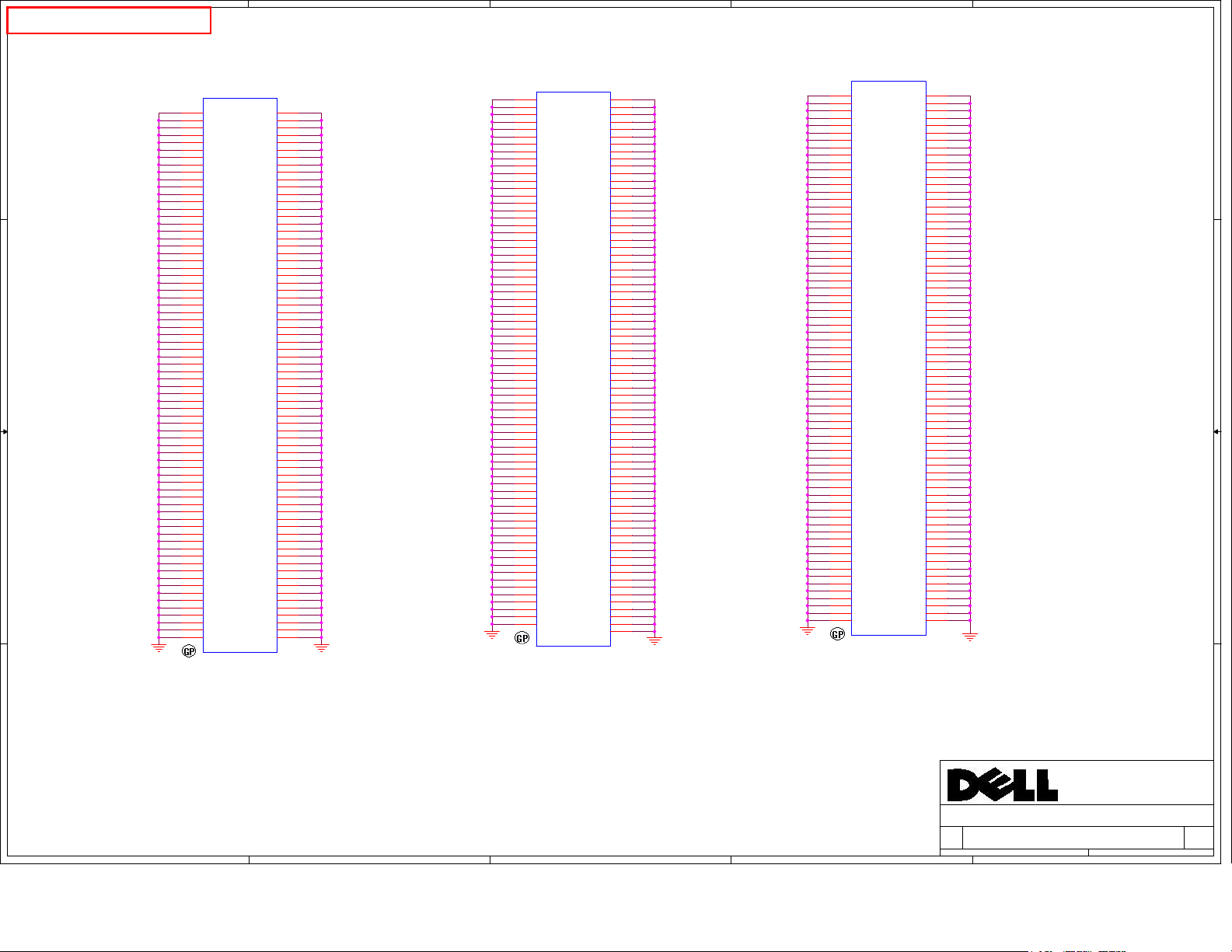

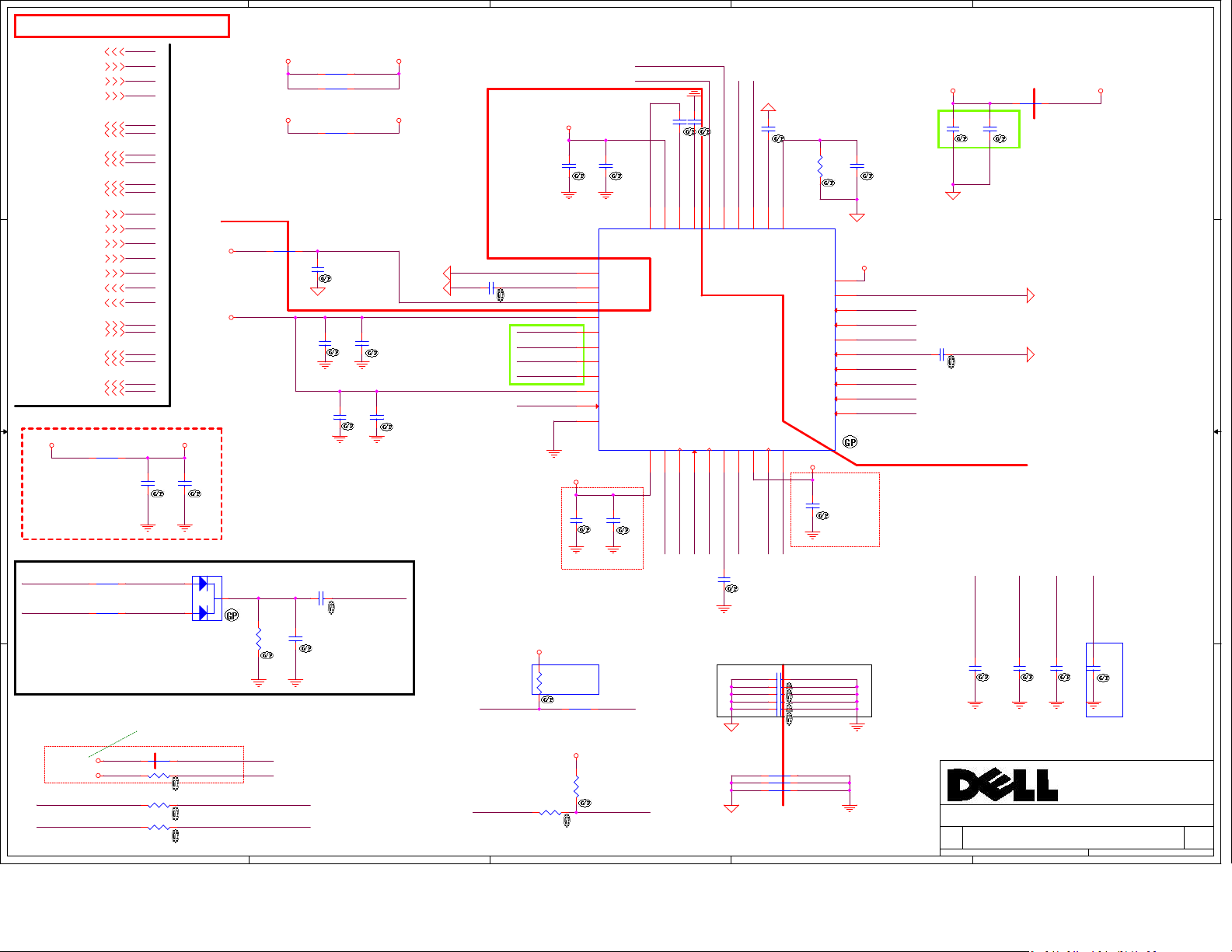

WASP 13" CPU 15W + GPU 18W Block Diagram

Project code :

N5 -> 4PD0GW010001

M(GDDR5) *2

RA

V

2GB

D D

C C

DDR5

G

WWAN BD

eSIM

IO expander

IT8010FN

B B

I2C

A A

NGFF WWAN

WWAN/LTE

2nd storage

Thermal

NUVOTON

NCT7718W

KBC

MICROCHIP

EC

M

Fan Control

PWM

FAN

5

GPU

NVIDIA

N17S-G2 18W

HDMI 1.4

CONN.

13.3"

(FHD)

M.2 SSD

NGFF

WLAN

(CNVi)

2

4

65

Redriver

PI3EQX12902AZLEX

Redriver

PI3EQX12902AZLEX

PCIe x 1

PCIe x 1

SMBus

26 68

1418

Int.

26

KB

Flash ROM

26

16MB

Quad Read

TPM

NPCT750JAB

PCIE x 4

7

6-8081-82

DDI1

5

7

eDP

5

5

SATA/PCIEx4

6

3

PCIe x 1

USB2.0

6

1

CNVi

USB2.0

eSPI debug port

eSPI BUS

I2C

ouc

h PAD

T

Image sensor

SPI

25

91

4

L

ANE 5~8

LANE 10

L

ANE 10

LANE 9

PCIe x 1

PCIe x 1

6

5

nt

el CPU

I

Whiskey Lake-U

15W

WHL PCH-LP

10 USB 2.0/1.1 ports

U

SB 3.0 ports

6

igh

Definition Audio

H

3 SATA ports

PC

IE ports

6

LPC I/F

CPI

5.0

A

Channel A

Channel B

DP 1.2

USB3.1 Gen1

USB2.0

LANE 4

LPDDR3

Memory Down

SS MUX

TI

TUSB546A

I2C

TPS65982DD

1

2,13

DP1.2/USB 3.1 Gen1

7

1

USB 2.0

CC1 & CC2

CardReader

SDIO

USB2.0

I2C

Reserve path

LANE 5

I2C

SD 3.0

Realtak

RTS5100

Finger Print

e fall

re

F

Gsensor

ST

LNG2DMTR

D-MIC

3

3

92

7

0

5

5

HDA

HDA

L

L

ANE 1

ANE 6

USB2.0

USB2.0

3

CODEC

Realtek

ALC3204

USB 3.1 Gen1

Re-driver

PS8719

Camera

(HD)

5

5

2

2

7

MIC_IN/GND

HP_R/L

USB3.1 Gen1USB3.1 Gen1

<

<

<

re Design>

re Design>

re Design>

Co

Co

Co

T

le

Title

Title

it

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

3

3

3

Date: Sheet

Date: Sheet

Date: Sheet

V5 -> 4PD0GX010001

L -> 4PD0H6010001

PCB P/N : 18769-1

Revision: A00

USB3.1 Gen1

TypeC

Port1

7372

MicroSD Card Slot

3

3

2CH SPEAKER

(2CH 2W/4ohm)

IOBD

ni

versal Jack

U

USB3.1 Gen1

Port2

is

is

is

tron Corporation

tron Corporation

tron Corporation

W

W

W

2

2

2

, 88, Sec.1, H sin Tai Wu Rd., Hsichih,

, 88, Sec.1, H sin Tai Wu Rd., Hsichih,

, 88, Sec.1, H sin Tai Wu Rd., Hsichih,

1F

1F

1F

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

loc

loc

loc

k Diagram

k Diagram

k Diagram

B

B

B

P 13" WHL-U

P 13" WHL-U

P 13" WHL-U

AS

AS

AS

W

W

W

1

2

6Thursday, March 07, 2019

6Thursday, March 07, 2019

6Thursday, March 07, 2019

f

10

f

10

f

10

00

00

00

A

A

A

o

2

o

2

o

5

4

3

2

1

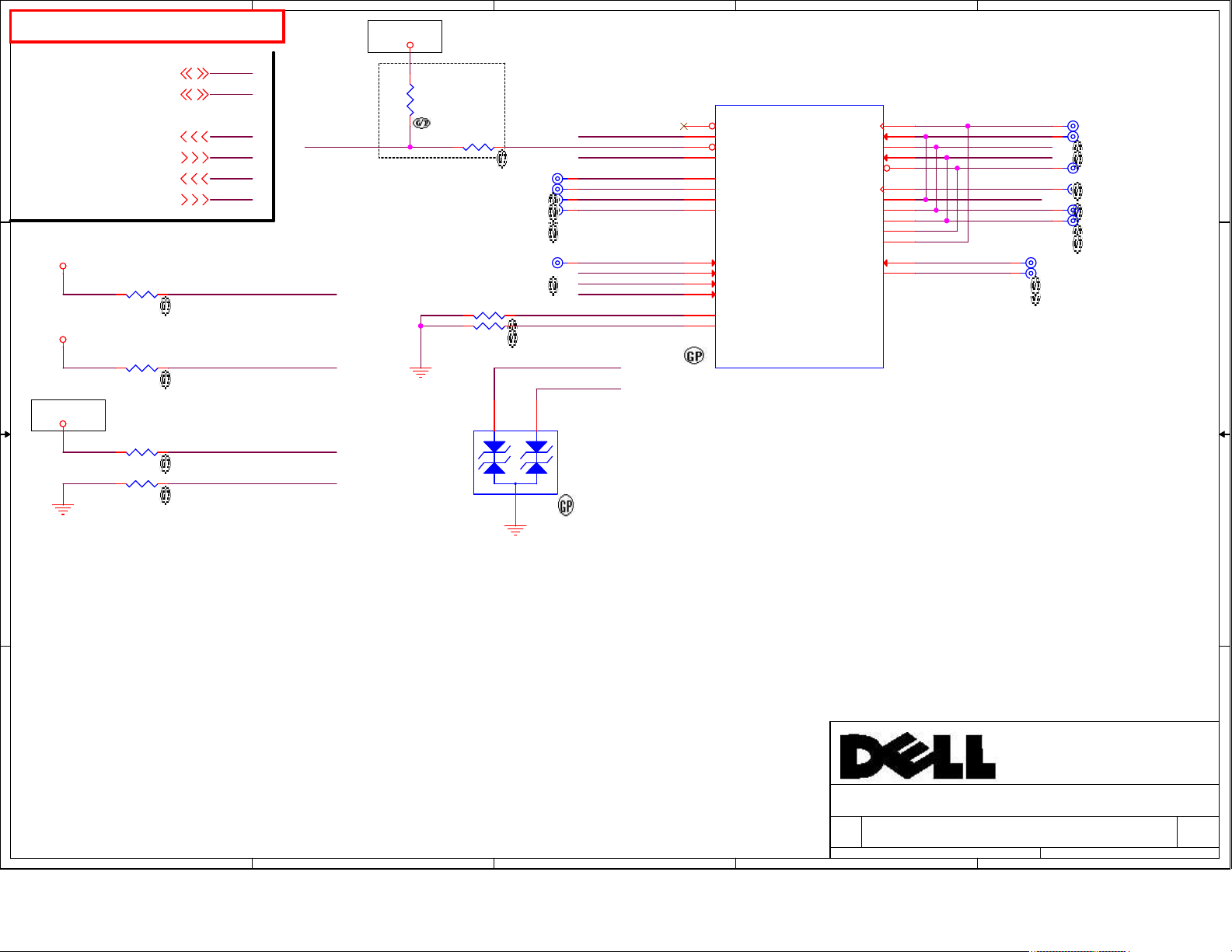

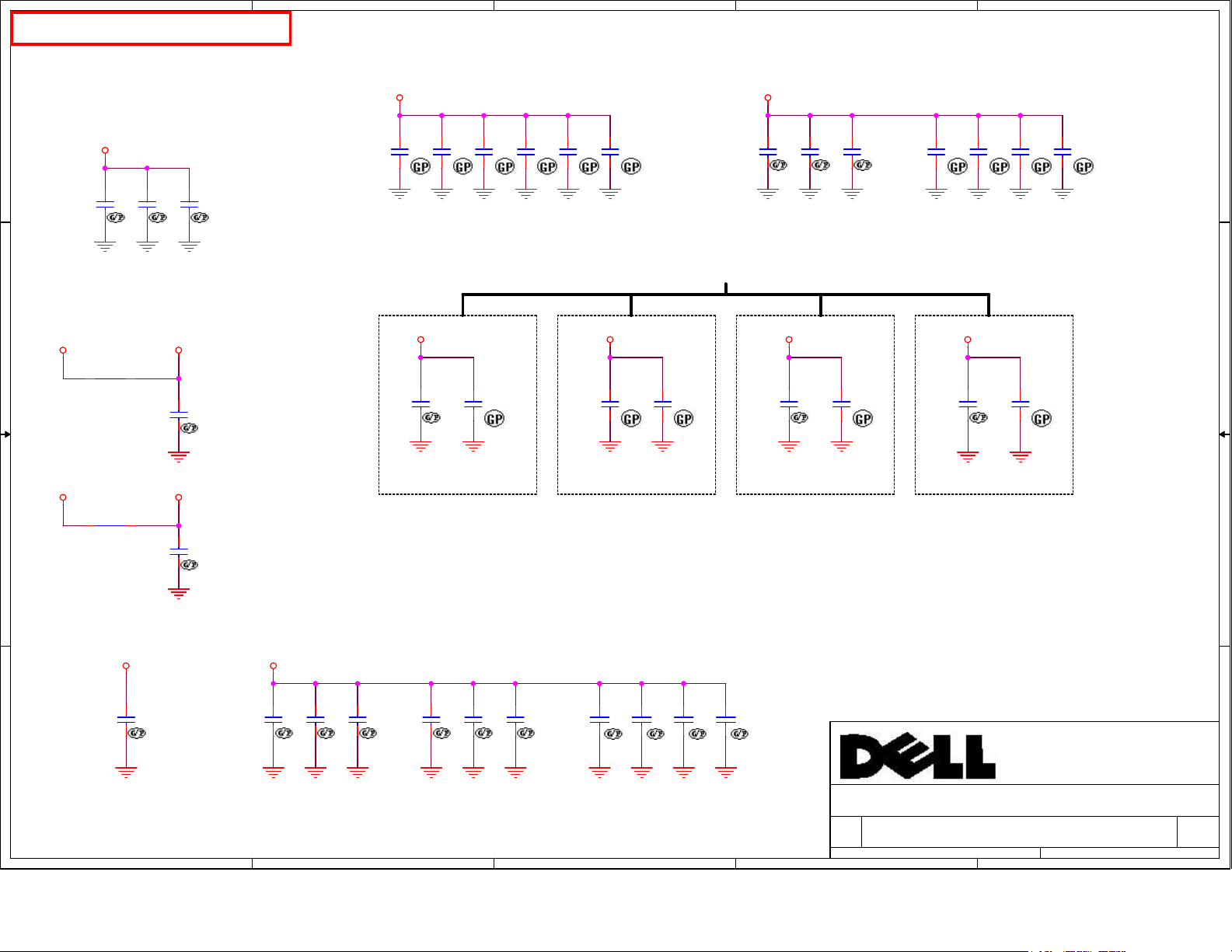

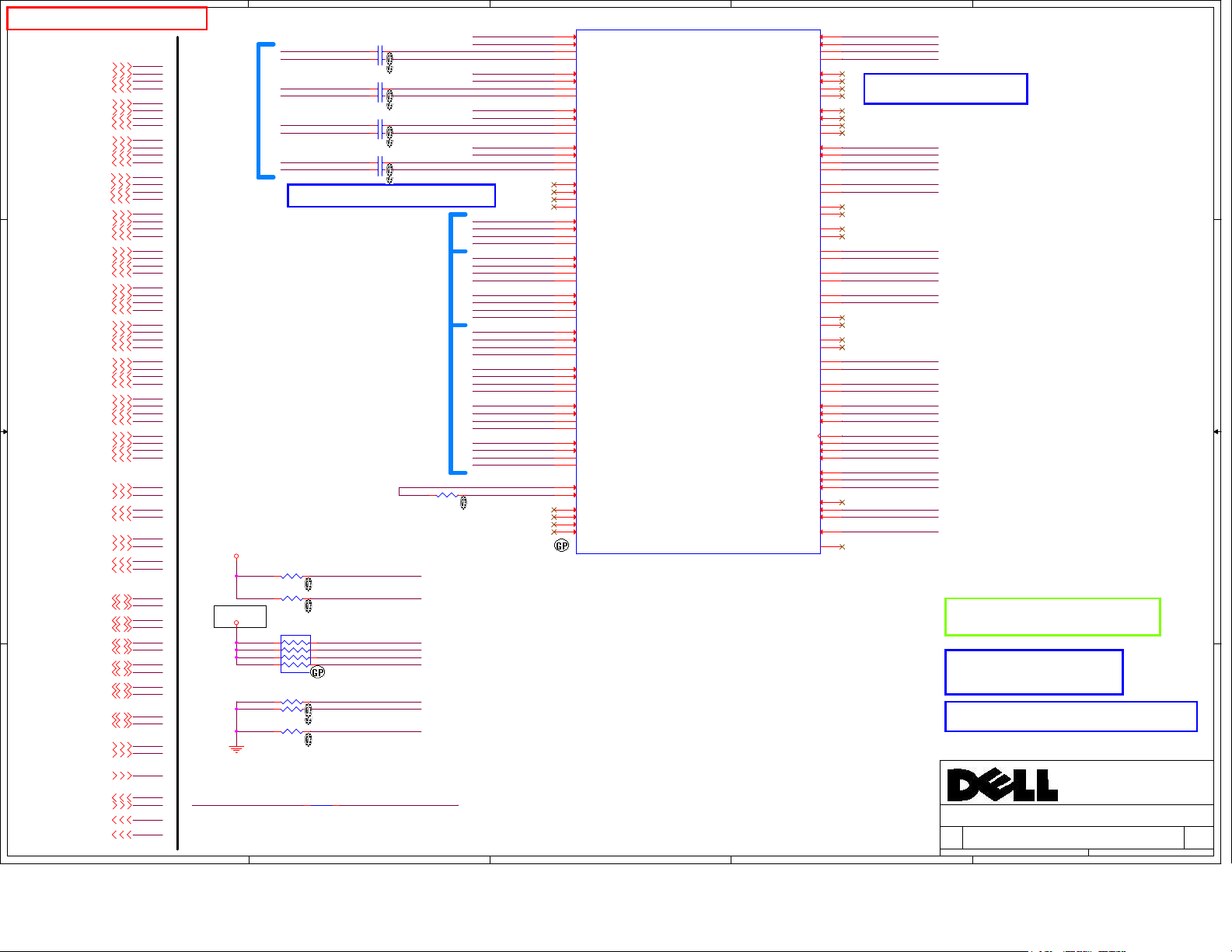

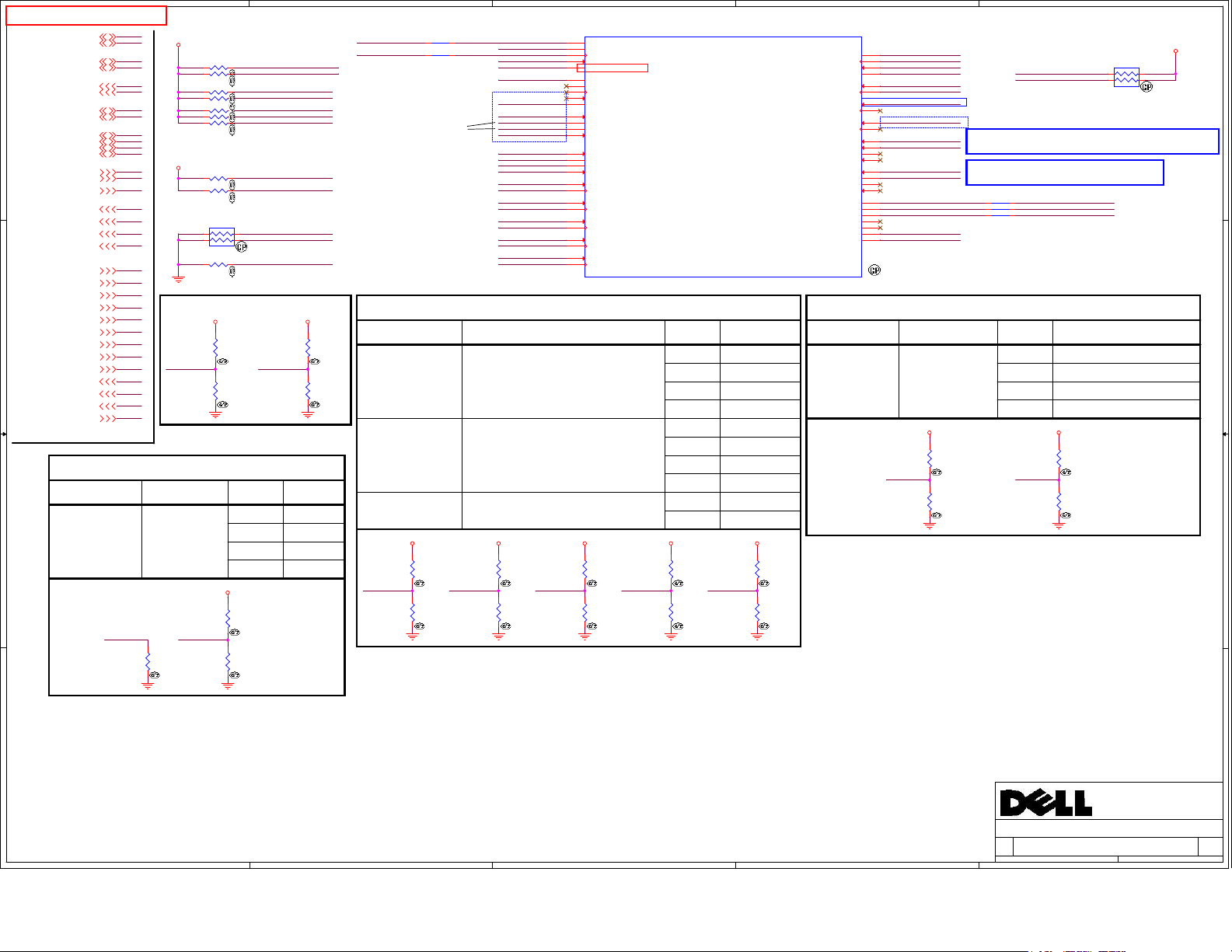

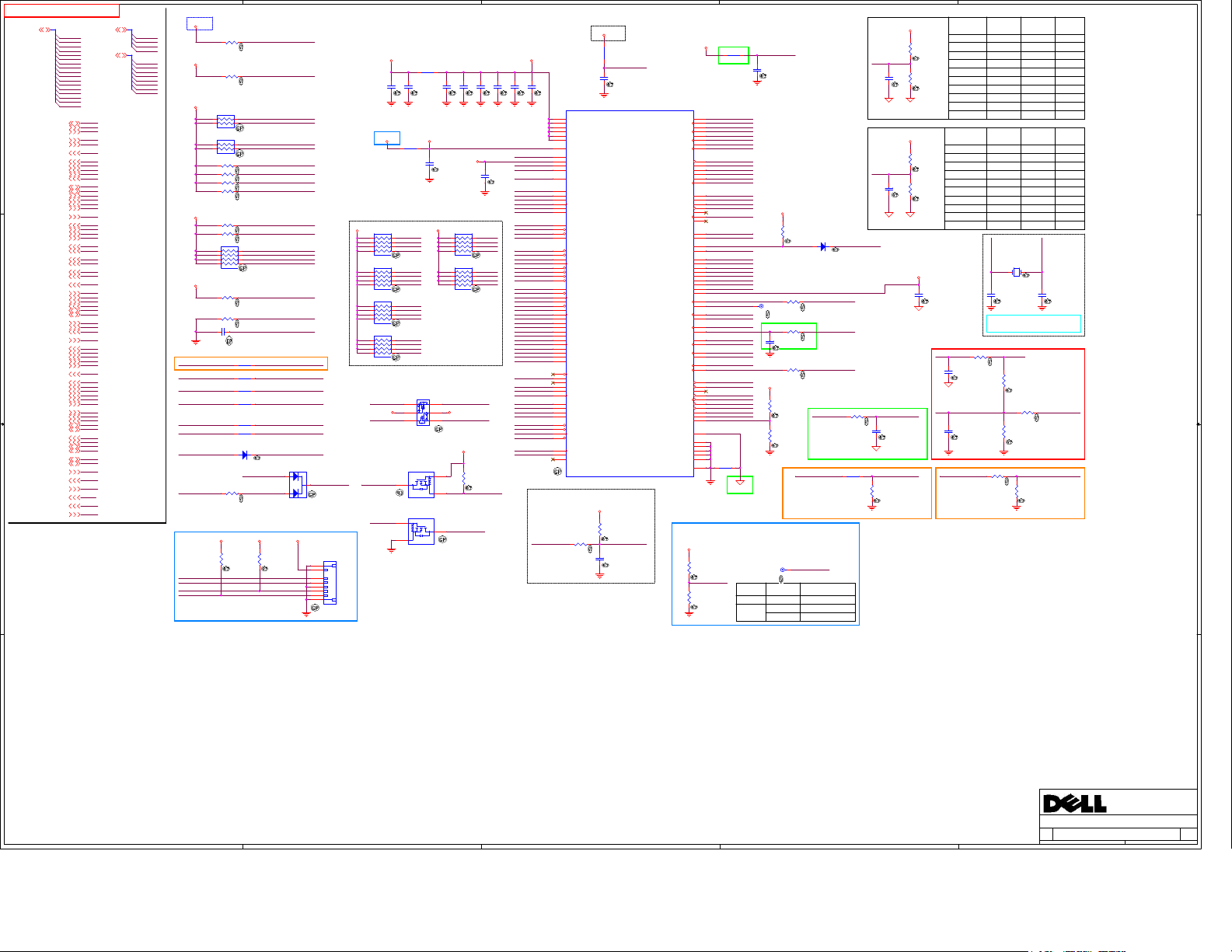

Main Func = CPU

P

E

CI_CPU24

P

OCHOT#_CPU24,44,46

R

D D

T

O

UCH_PANEL_INTR#55

T

_WAKE_KBC#24,65

P

T

UCH_PANEL_PD#55

O

H

CPUPWRGD17

_

3

D

3V_S5_PCH

T

_WAKE_KBC#

1 2

R

03 100KR2J-1-GP

3

DY

1

_VCCST_CPU

V

C C

1 2

R

08 1KR2J-1-GP

3

1

V

_VCCSTG

P

T

H

ERMTRIP#_CPU

1V_VCCSTG = 1.05V

X

P_TDO_CPU

1 2

R

3

10 51R2J-2-GP

1 2

R

17 51R2J-2-GP

3

D

X

D

P_TCLK

P

OCHOT#_CPU

R

1

_VCCSTG

V

Rb

1V_VCCSTG = 1.05V

12

R

01

3

1KR2J-1-GP

Ra

1 2

R

3

02 499R2F-2-GP

1 2

R

3

04 49D9R2F-GP

1 2

R

05 49D9R2F-GP

3

1

DY

[PECI] and [PROCHOT#]

Impedance control: 50 ohm

P

E

CI_CPU

P

OCHOT#_CPU_R

R

T

H

ERMTRIP#_CPU

B

M_N0

P

T

P

T

P

T

P

T

P

T

1

307

1

308

1

302

1

303

1

304

P

T

H

ERMTRIP#_CPU

H

CPUPWRGD

_

2

E

301

D

AZ5125-02S-R7G-GP

B

P

M_N1

B

P

M_CPU_N2

B

P

M_CPU_N3

G

P

P_E3/CPU_GP0

T

O

UCH_PANEL_INTR#

T

P

_WAKE_KBC#

T

UCH_PANEL_PD#

O

C

U_POPIRCOMP

P

P

H_POPIRCOMP

C

75.05125.07D

3

C

P

AA4

A

C

AR1

E

P

Y4

R

P

BJ1

H

T

U1

P

B

U2

P

B

U3

P

B

U4

P

B

CE9

P

G

CN3

P

G

CB34

P

G

CC35

P

G

BP27

R

P

BW25

C

P

WHISKEY-LAKE-GP

ZZ.00CPU.271

U1D

TERR#

CI

OCHOT#

RMTRIP#

M#0

M#1

M#2

M#3

P_E3/CPU_GP0

P_E7/CPU_GP1

P_B3/CPU_GP2

P_B4/CPU_GP3

OC_POPIRCOMP

H_OPIRCOMP

4

R

P

R

P

R

P

R

P

R

OC_TRST#

P

P

P

P

P

H_TRST#

C

P

C

H_JTAGX

P

R

OC_PREQ#

P

OC_PRDY#

R

P

OF 20

OC_TCK

OC_TDI

OC_TDO

OC_TMS

H_TCK

C

C

H_TDI

H_TDO

C

H_TMS

C

T6

U6

Y5

T5

AB6

W6

U5

W5

P5

Y6

P6

W2

W1

X

D

X

D

P_PREQ#

P_PRDY#

X

P_TCLK

D

X

D

P_TDI

X

P_TDO_CPU

D

X

D

P_TMS

X

D

P_TRST#

P

C

H_TCK

1

T

309

P

1

T

310

P

1

T

P

313

1

T

314

P

1

T

P

1

1

T

305

P

1

T

P

306

316

T

P

317

B B

<Core Design>

<Core Design>

<Core Design>

istron Corporation

istron Corporation

istron Corporation

W

W

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

4

4

4

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

2

P

P

P

U (THML/JTAG)

U (THML/JTAG)

U (THML/JTAG)

C

C

C

A

A

A

SP 13" WHL-U

SP 13" WHL-U

SP 13" WHL-U

W

W

W

W

2

2

2

1

1

1

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

o

o

o

f

f

3 1

3 1

3 1

f

1

A

A

A

0

0

0

0

0

0

06Thursday, March 07, 2019

06Thursday, March 07, 2019

06Thursday, March 07, 2019

5

WWW.AliSaler.Com

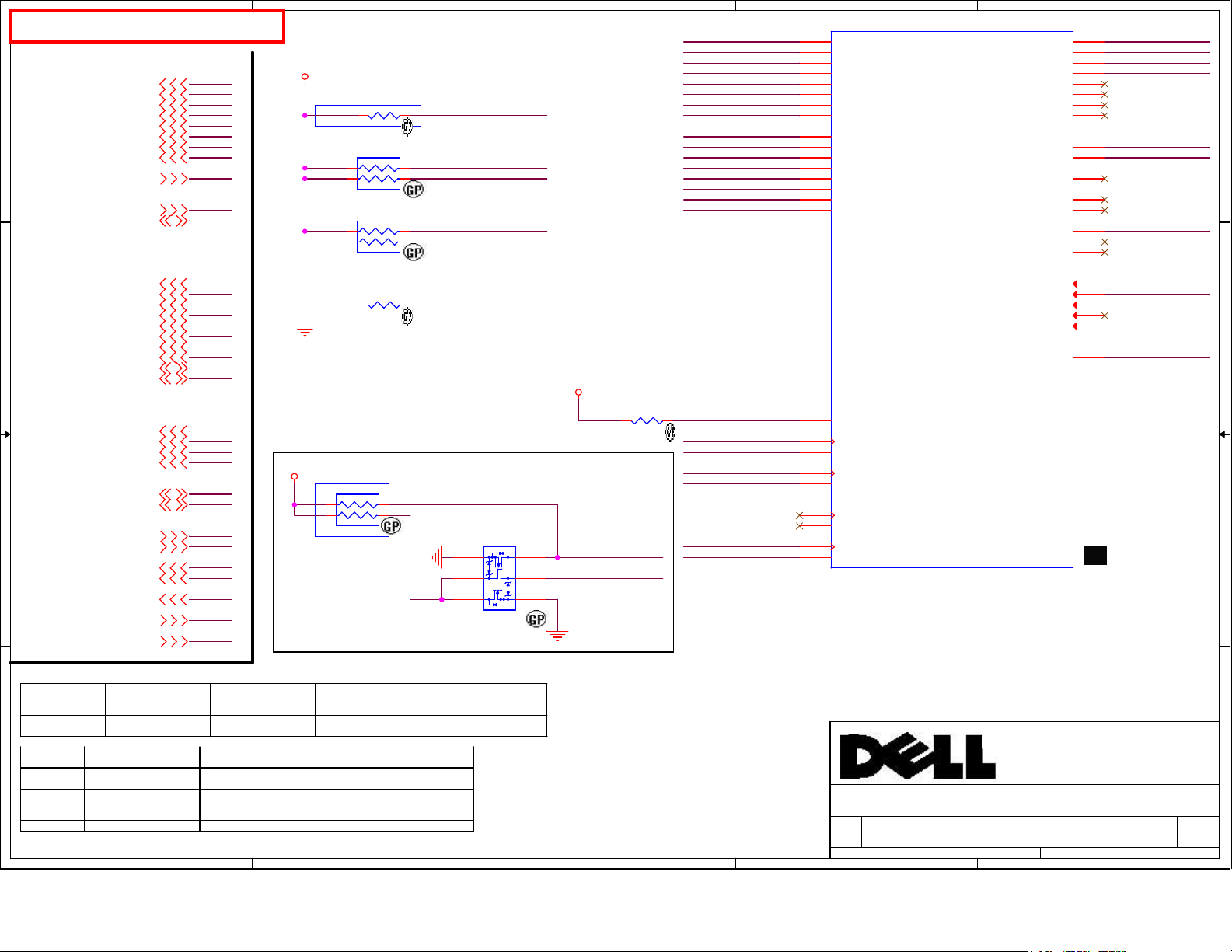

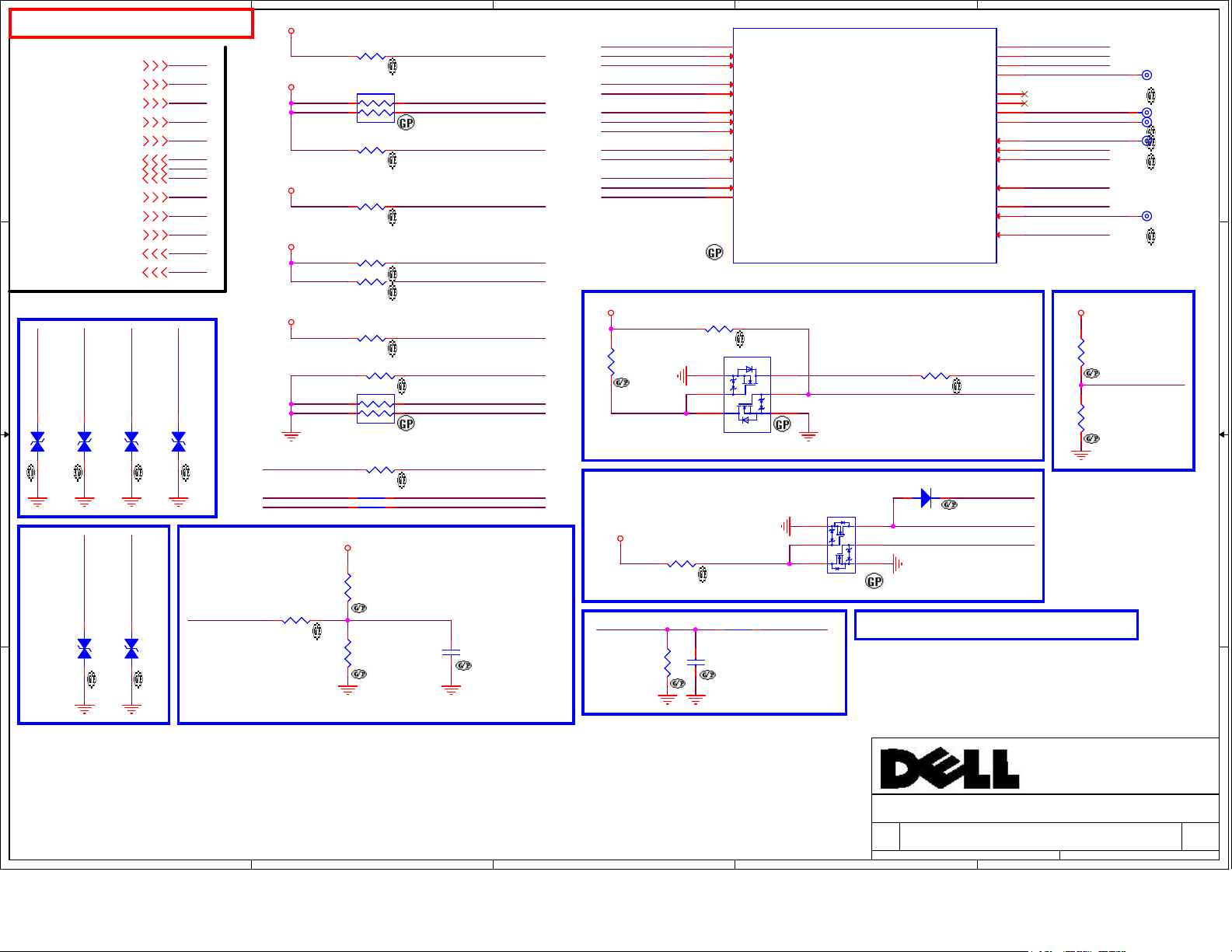

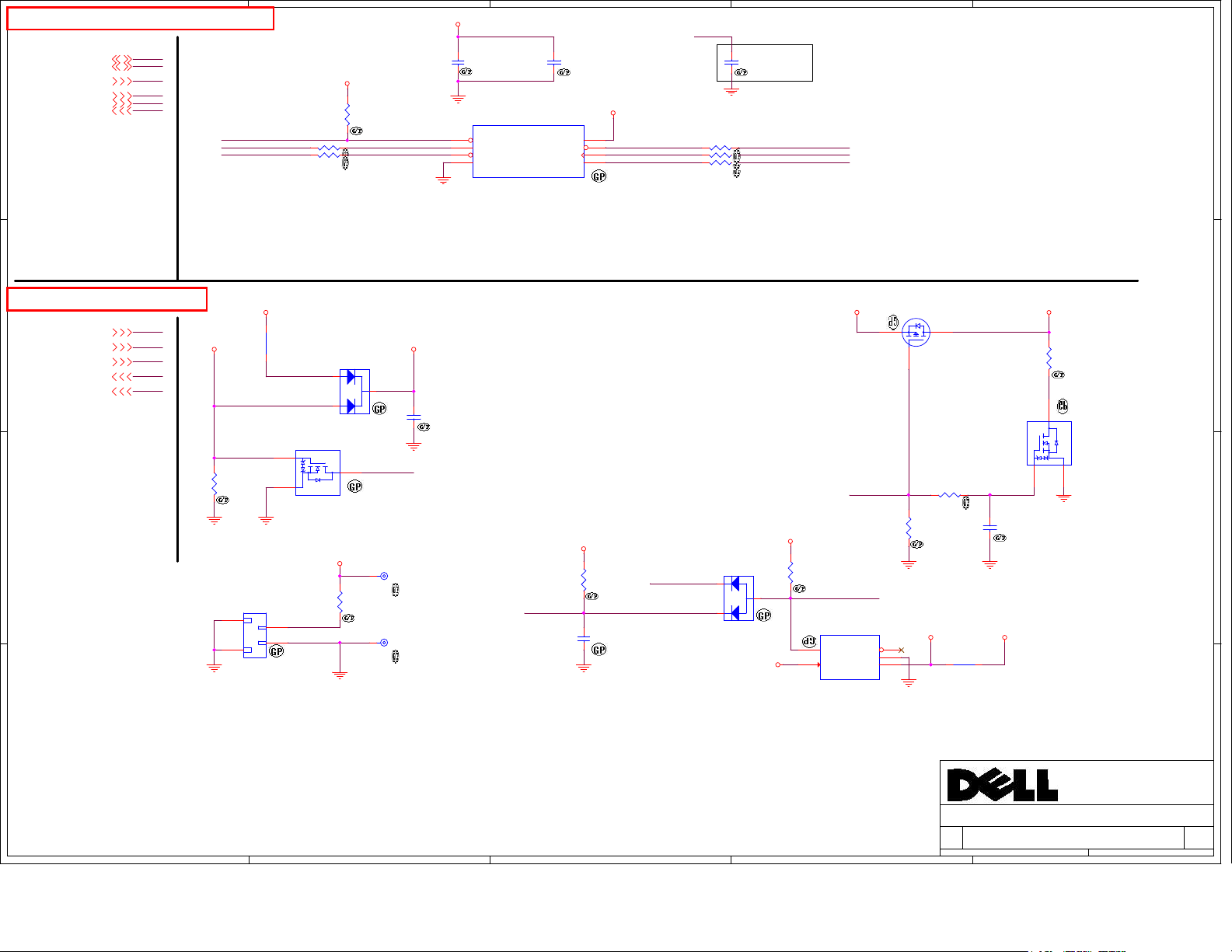

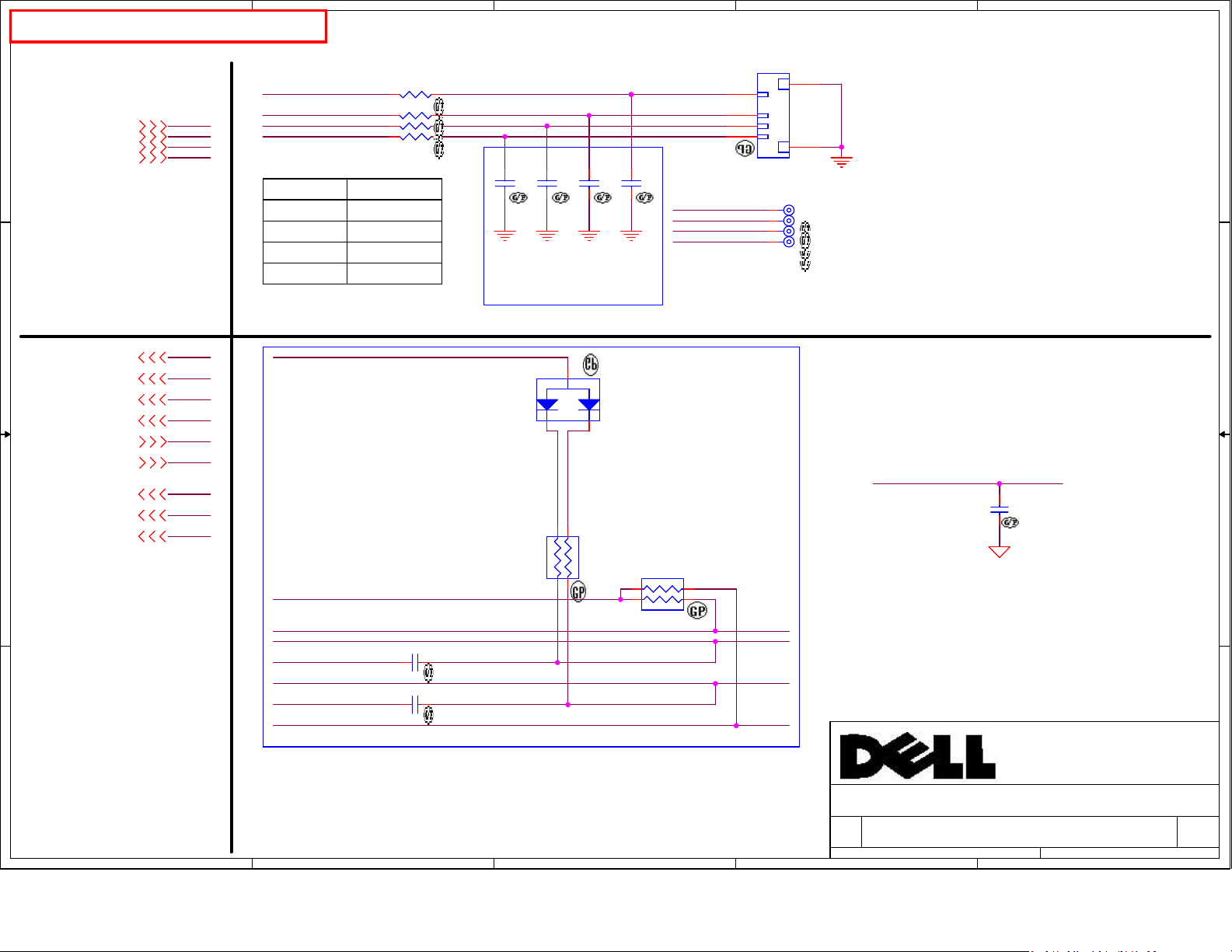

Main Func = CPU

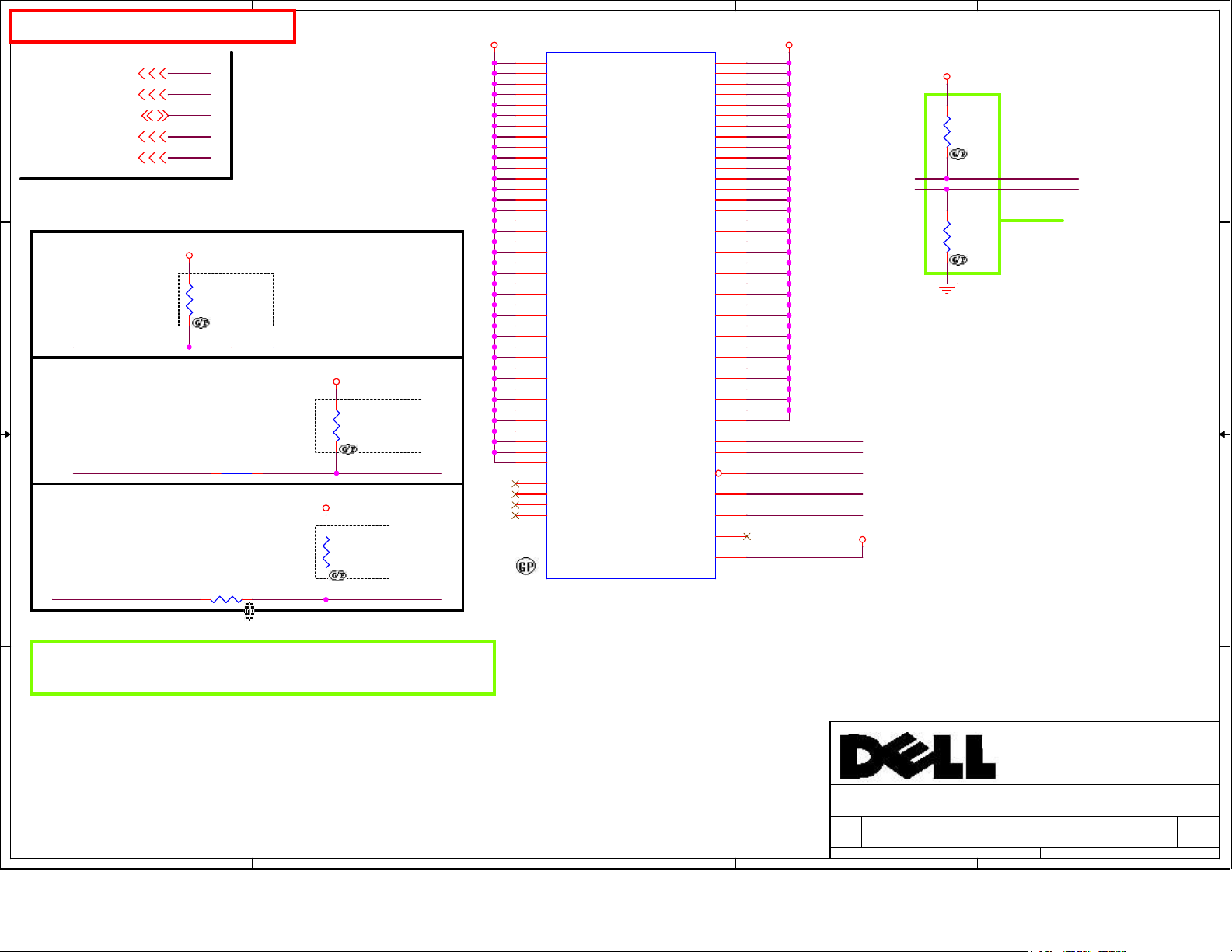

DP to HDMI1.4

H

I_DDI_TX_N057

DM

H

I_DDI_TX_P057

DM

H

I_DDI_TX_N157

DM

H

I_DDI_TX_P157

D D

DM

H

M

I_DDI_TX_N257

D

H

DM

I_DDI_TX_P257

H

M

I_DDI_TX_N357

D

H

I_DDI_TX_P357

DM

H

I_HPD_CPU57

DM

C

PU

_DP1_CTRL_CLK57

C

_DP1_CTRL_DATA57

PU

DP for Type-C Mux

D

_DDI_TX_N071

P2

D

P2

_DDI_TX_P071

D

P2

_DDI_TX_N171

D

_DDI_TX_P171

P2

D

_DDI_TX_N271

C C

P2

D

P2

_DDI_TX_P271

D

P2

_DDI_TX_N371

D

P2

_DDI_TX_P371

D

P2

_AUX_CPU_P71

D

P2

_AUX_CPU_N71

3

V_S0

D3

2

0180904 Stuff

R

10KR2J-L-GP

R

100KR2J-1-GP

4

1 2

40

2

R

01

N4

1

2 3

SRN2K2J-1-GP

R

N4

03

1

2 3

SRN2K2J-1-GP

1 2

40

3

4

4

S

IO

_EXT_SMI#

C

PU

_DP1_CTRL_DATA

C

_DP1_CTRL_CLK

PU

C

PU

_DP2_CTRL_DATA

C

PU

_DP2_CTRL_CLK

D

_HPD_CPU_R

P1

3

DP to HDMI

H

H

H

H

H

H

H

H

D

D

D

D

D

D

D

D

DM

I_DDI_TX_N0

I_DDI_TX_P0

DM

DM

I_DDI_TX_N1

DM

I_DDI_TX_P1

DM

I_DDI_TX_N2

I_DDI_TX_P2

DM

DM

I_DDI_TX_N3

DM

I_DDI_TX_P3

P2

_DDI_TX_N0

_DDI_TX_P0

P2

P2

_DDI_TX_N1

P2

_DDI_TX_P1

_DDI_TX_N2

P2

P2

_DDI_TX_P2

P2

_DDI_TX_N3

P2

_DDI_TX_P3

AL5

AL6

AJ5

AJ6

AF6

AF5

AE5

AE6

AC4

AC3

AC1

AC2

AE4

AE3

AE1

AE2

DP for Type-C Mux

1

VCCIO

V_

2

E

E

D

D

D

D

D

D

D

DP

E

E

DP

E

1

O

DP

_TXN0

E

DP

_TXP0

E

_TXN1

DP

E

_TXP1

DP

E

_TXN2

DP

E

DP

_TXP2

E

_TXN3

DP

E

_TXP3

DP

E

_AUX_N

DP

_AUX_P

DP

P_UTILS

IS

DI

1_AUX_N

1_AUX_P

DI

2_AUX_N

DI

2_AUX_P

DI

DI

3_AUX_N

DI

3_AUX_P

_BKLTEN

_VDDEN

DP

_BKLTCTL

F 20

C

1A

PU

DI

1_TXN0

D

DI

1_TXP0

D

1_TXN1

DI

D

1_TXP1

DI

D

1_TXN2

DI

D

DI

1_TXP2

D

1_TXN3

DI

D

1_TXP3

DI

D

DI

2_TXN0

D

2_TXP0

DI

D

2_TXN1

DI

D

DI

2_TXP1

D

2_TXN2

DI

D

2_TXP2

DI

D

DI

2_TXN3

D

2_TXP3

DI

D

PP

_E13/DDPB_HPD0/DISP_MISC0

G

PP

_E14/DDPC_HPD1/DISP_MISC1

G

_E15/DPPD_HPD2/DISP_MISC2

PP

G

PP

_E16/DPPE_HPD3/DISP_MISC3

G

PP

_E17/EDP_HPD/DISP_MISC4

G

AG4

AG3

AG2

AG1

AJ4

AJ3

AJ2

AJ1

AH4

AH3

AM7

AC7

AC6

AD4

AD3

AG7

AG6

CN6

CM6

CP7

CP6

CM7

CK11

CG11

CH11

1

e

DP

_TX_CPU_N0

e

_TX_CPU_P0

DP

e

DP

_TX_CPU_N1

e

DP

_TX_CPU_P1

e

_AUX_CPU_N

DP

e

DP

_AUX_CPU_P

D

_AUX_CPU_N

P2

D

P2

_AUX_CPU_P

H

DM

I_HPD_CPU

D

_HPD_CPU_R

P1

S

_EXT_SMI#

IO

e

_HPD_CPU

DP

L

KLT_EN

_B

E

_VDD_EN

DP

L

_B

KLT_CTRL

eDP

e

_TX_CPU_N055

DP

e

_TX_CPU_P055

DP

e

_TX_CPU_N155

DP

e

_TX_CPU_P155

DP

e

_AUX_CPU_N55

DP

e

DP

_AUX_CPU_P55

e

DP

B B

_HPD_CPU55

D

P1

_HPD_CPU71,72

L

KLT_EN24

_B

L

KLT_CTRL55

_B

E

DP

_VDD_EN55

G

PP

_H17_STRAP15

G

_THM_DIS#24

C6

3

D3

V_S5_PCH

R

05

N4

1

2 3

SRN10KJ-5-GP

S

A 0816

4

C

PU

_DP_HPD_P

Q

40

1

N

ote:ZZ.27002.F7C01

1

2

3 4

2N7002KDW-1-G P

6

5

D

D

75.27002.F7C

R

40

1

24D9R2F-L-GP

_HPD_CPU_R

P1

_HPD_CPU

P1

1 2

e

DP

_RCOMP_CPU

C

PU

_DP1_CTRL_CLK

C

_DP1_CTRL_DATA

PU

C

PU

_DP2_CTRL_CLK

C

PU

_DP2_CTRL_DATA

G

C6

_THM_DIS#

G

_H17_STRAP

PP

AM6

IS

D

CC8

PP

G

CC9

PP

G

CH4

PP

G

CH3

PP

G

CP4

PP

G

CN4

PP

G

CR26

PP

G

CP26

PP

G

WHISKEY-LAKE-GP

ZZ.00CPU.271

P_RCOMP

_E18/DPPB_CTRLCLK/CNV_BT_HOST_WAKE#

_E19/DPPB_CTRLDATA

_E20/DPPC_CTRLCLK

_E21/DPPC_CTRLDATA

_E22/DPPD_CTRLCLK

_E23/DPPD_CTRLDATA

_H16/DDPF_CTRLCLK

_H17/DDPF_CTRLDATA

(#543016) eDP_RCOMP Guideline

Signal Trace

Width

eDP_RCOMP 20 mils 25 mils 24.9 �[

(#543016) DDI Disabling and Termination Guidelines

A A

Port Strap Enable Port Disable Port

Port 1

Port 2

DDPB_CTRLDATA

DDPC_CTRLDATA

5

Isolation

Spacing

Resistor

Value

��1%

PU to 3.3 V with 2.2-k

��5% resistor

PU to 3.3 V with 2.2-k

��5% resistor

Length

<Core Design>

<Core Design>

Max = 100 mils

NC

NC

4

3

<Core Design>

istron Corporation

istron Corporation

istron Corporation

W

W

W

2

2

2

1F

1F

1F

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

4

4

4

Date: Sheet

Date: Sheet

Date: Sheet

2

PU

PU

PU

(DDI/EDP)

(DDI/EDP)

(DDI/EDP)

C

C

C

AS

AS

AS

W

W

W

P 13" WHL-U

P 13" WHL-U

P 13" WHL-U

4 1

4 1

4 1

1

o

o

o

f

f

f

A

A

A

00

00

00

0

0

0

6Thursday, March 07, 2019

6Thursday, March 07, 2019

6Thursday, March 07, 2019

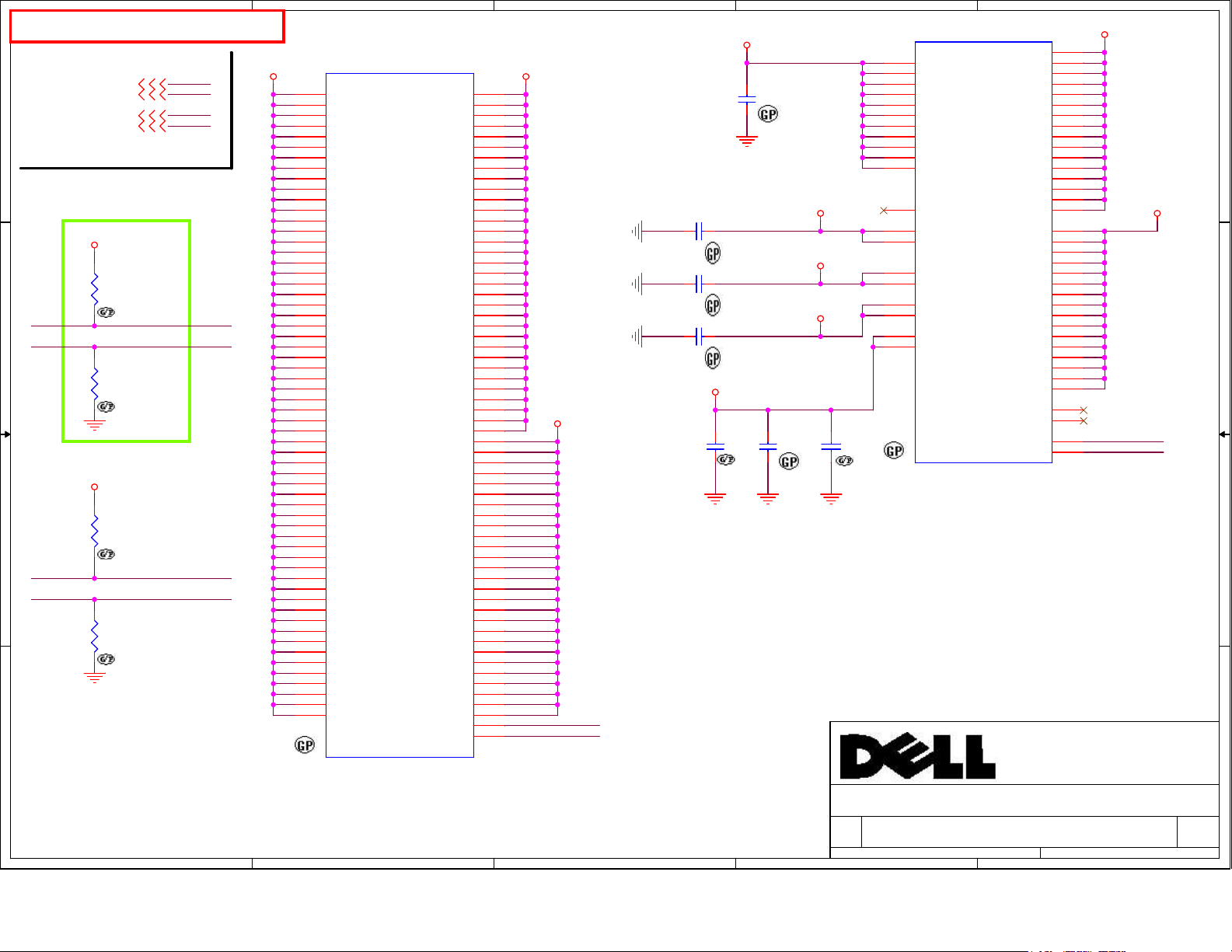

_

A_DQS_DN0

M

_

A_DQS_DN1

M

_

A_DQS_DN2

M

A_DQS_DN3

_

M

_

A_DQS_DN4

M

_

A_DQS_DN5

M

A_DQS_DN6

_

M

_

A_DQS_DN7

M

_

A_DQS_DP0

M

_

A_DQS_DP1

M

_

A_DQS_DP2

M

_

A_DQS_DP3

M

A_DQS_DP4

_

M

A_DQS_DP5

_

M

_

A_DQS_DP6

M

_

A_DQS_DP7

M

5

_

B_DQS_DN[7:0]13

M

B_DQS_DP[7:0]13

_

M

_

B_DQ013

M

_

B_DQ113

M

_B_DQ213

M

_

B_DQ313

M

B_DQ413

_

M

_

B_DQ513

M

B_DQ613

_

M

B_DQ713

_

M

_

B_DQ813

M

B_DQ913

_

M

_

B_DQ1013

M

B_DQ1113

_

M

_

B_DQ1213

M

_

B_DQ1313

M

_

B_DQ1413

M

_

B_DQ1513

M

B_DQS_DN0

_

M

_

B_DQS_DN1

M

_

B_DQS_DN2

M

_

B_DQS_DN3

M

B_DQS_DN4

_

M

_

B_DQS_DN5

M

_

B_DQS_DN6

M

B_DQS_DN7

_

M

_

B_DQS_DP0

M

_

B_DQS_DP1

M

_

B_DQS_DP2

M

_

B_DQS_DP3

M

B_DQS_DP4

_

M

B_DQS_DP5

_

M

_

B_DQS_DP6

M

_

B_DQS_DP7

M

M_A_DQ[0:7]

M_A_DQ[8:15]

M_A_DQ[32:39]

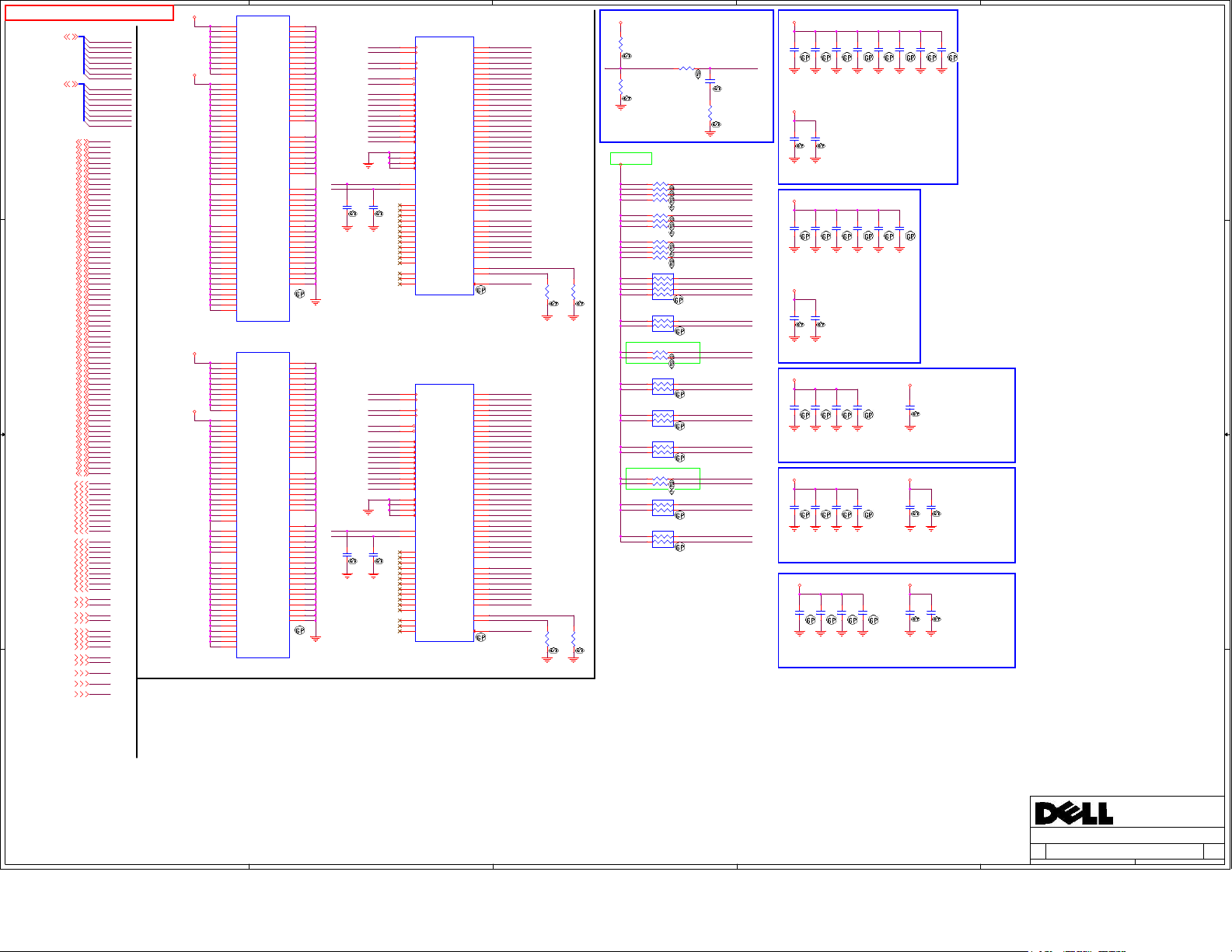

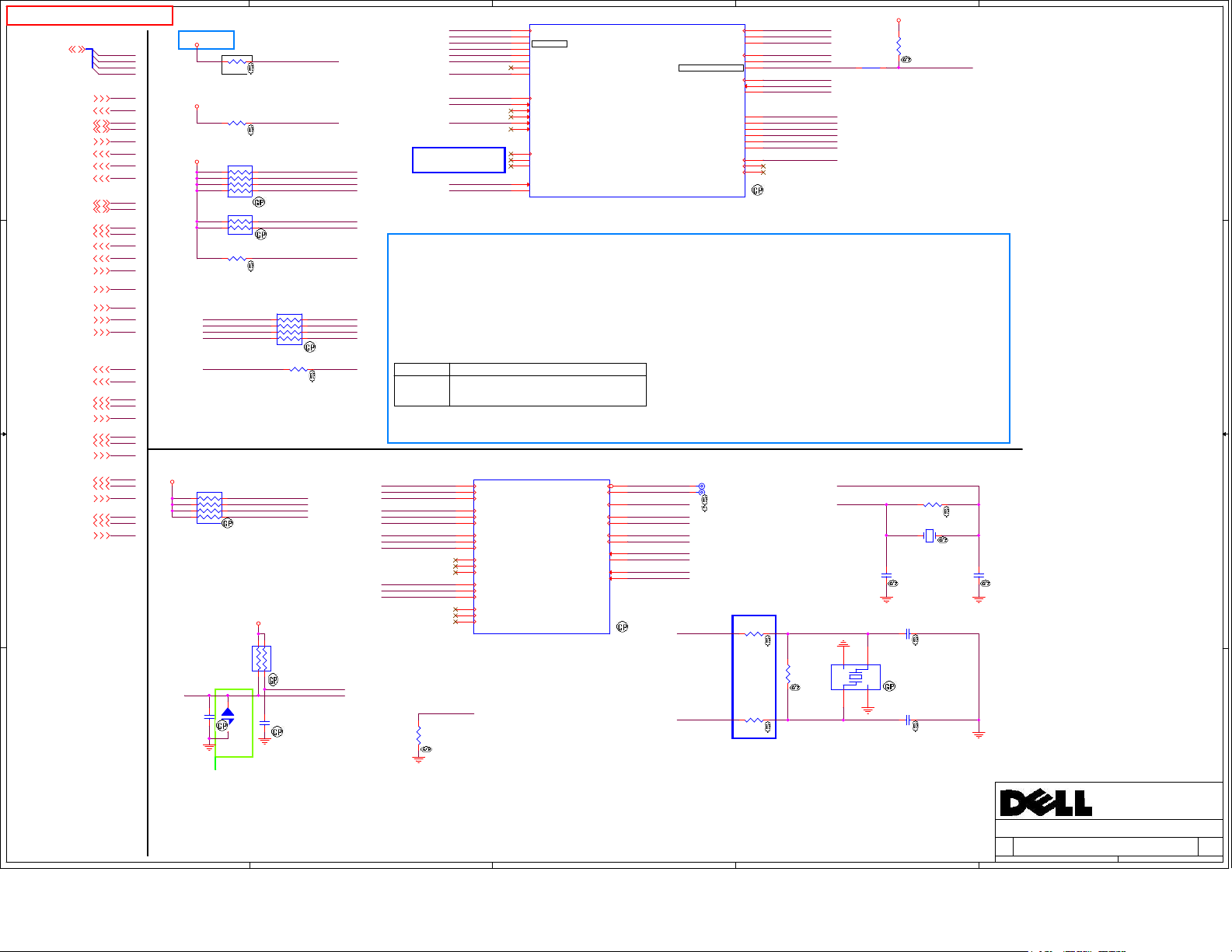

Main Func = CPU

A_DQS_DN[7:0]12

_

M

A_DQS_DP[7:0]12

_

M

D D

_

A_DQ012

M

_

A_DQ112

M

_A_DQ212

M

_

A_DQ312

M

A_DQ412

DQ[0:7]

DQ[8:15]

_

M

_

A_DQ512

M

A_DQ612

_

M

A_DQ712

_

M

_

A_DQ812

M

A_DQ912

_

M

_

A_DQ1012

M

A_DQ1112

_

M

_

A_DQ1212

M

_

A_DQ1312

M

_

A_DQ1412

M

_

A_DQ1512

M

M_A_DQ[40:47]

_

A_DQ1612

M

A_DQ1712

_

M

_

A_DQ1812

M

_A_DQ1912

_

A_CLK#0 12

M

A_CLK0 12

_

M

A_CLK#1 12

_

M

_

A_CLK1 12

M

_

A_CKE0 12

M

_

A_CS#0 12

M

A_ODT0 12

_

M

_

M

_

M

_

M

_

M

_A_A4 12

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

A_A0 12

A_A1 12

A_A2 12

A_A3 12

A_A5 12

A_A6 12

A_A7 12

A_A8 12

A_A9 12

A_B0 12

A_B1 12

A_B2 12

A_B3 12

A_B4 12

A_B5 12

A_B6 12

A_B7 12

A_B8 12

A_B9 12

A_CKE1 12

A_CS#1 12

M

_

A_DQ2012

M

_

A_DQ2112

M

A_DQ2212

_

M

A_DQ2312

_

M

A_DQ2412

_

M

_

A_DQ2512

M

A_DQ2612

_

M

_

A_DQ2712

M

A_DQ2812

_

M

A_DQ2912

_

M

_

A_DQ3012

M

_

A_DQ3112

M

A_DQ3212

_

M

A_DQ3312

_

M

_

A_DQ3412

M

A_DQ3512

_

M

_

A_DQ3612

M

A_DQ3712

_

M

_

A_DQ3812

M

A_DQ3912

_

M

A_DQ4012

_

M

_A_DQ4112

M

A_DQ4212

_

M

A_DQ4312

_

M

A_DQ4412

_

M

_

A_DQ4512

M

_

A_DQ4612

M

_

A_DQ4712

M

A_DQ4812

_

M

A_DQ4912

_

M

A_DQ5012

_

M

_

A_DQ5112

M

A_DQ5212

_

M

A_DQ5312

_

M

_

A_DQ5412

M

A_DQ5512

_

M

_

A_DQ5612

M

A_DQ5712

_

M

_

A_DQ5812

M

_

A_DQ5912

M

A_DQ6012

_

M

_

A_DQ6112

M

_

A_DQ6212

M

A_DQ6312

_

M

_

SM_VREF_CNTA 1 2

V

_

SM_VREF_CNTB 1 3

V

R_CA_VREF 12

D

D

A_CKE2 12

A_CKE3 12

T

T_CNTL 51

V

5

M_A_DQ[16:23]

C C

M_A_DQ[24:31]

M_A_DQ[32:39]

M_A_DQ[40:47]

M_A_DQ[48:55]

M_A_DQ[56:63]

B B

A A

_

B_DQ1613

M

B_DQ1713

_

M

_

B_DQ1813

M

_B_DQ1913

M

_

B_DQ2013

M

_

B_DQ2113

M

B_DQ2213

_

M

B_DQ2313

_

M

B_DQ2413

_

M

_

B_DQ2513

M

B_DQ2613

_

M

_

B_DQ2713

M

B_DQ2813

_

M

B_DQ2913

_

M

_

B_DQ3013

M

_

B_DQ3113

M

B_DQ3213

_

M

B_DQ3313

_

M

_

B_DQ3413

M

B_DQ3513

_

M

_

B_DQ3613

M

B_DQ3713

_

M

_

B_DQ3813

M

B_DQ3913

_

M

B_DQ4013

_

M

_B_DQ4113

M

B_DQ4213

_

M

B_DQ4313

_

M

B_DQ4413

_

M

_

B_DQ4513

M

_

B_DQ4613

M

_

B_DQ4713

M

B_DQ4813

_

M

B_DQ4913

_

M

B_DQ5013

_

M

_

B_DQ5113

M

B_DQ5213

_

M

B_DQ5313

_

M

_

B_DQ5413

M

B_DQ5513

_

M

_

B_DQ5613

M

B_DQ5713

_

M

_

B_DQ5813

M

_

B_DQ5913

M

B_DQ6013

_

M

_

B_DQ6113

M

_

B_DQ6213

M

B_DQ6313

_

M

_

B_CLK#0 13

M

_

B_CLK0 13

M

B_CLK#1 13

_

M

B_CLK1 13

_

M

_B_CKE0 13

M

B_CS#0 13

_

M

B_ODT0 13

_

M

B_A0 13

_

M

B_A1 13

_

M

B_A2 13

_

M

_

B_A3 13

M

_B_A4 13

M

_

B_A5 13

M

_

B_A6 13

M

B_A7 13

_

M

_

B_A8 13

M

B_A9 13

_

M

_

B_B0 13

M

_

B_B1 13

M

_

B_B2 13

M

_

B_B3 13

M

B_B4 13

_

M

B_B5 13

_

M

_

B_B6 13

M

B_B7 13

_

M

_

B_B8 13

M

B_B9 13

_

M

B_CKE1 13

_

M

_

B_CS#1 13

M

_

B_CKE2 13

M

B_CKE3 13

_

M

M_B_DQ[0:7]

M_B_DQ[8:15]

M_B_DQ[32:39]

M_B_DQ[40:47]

4

3

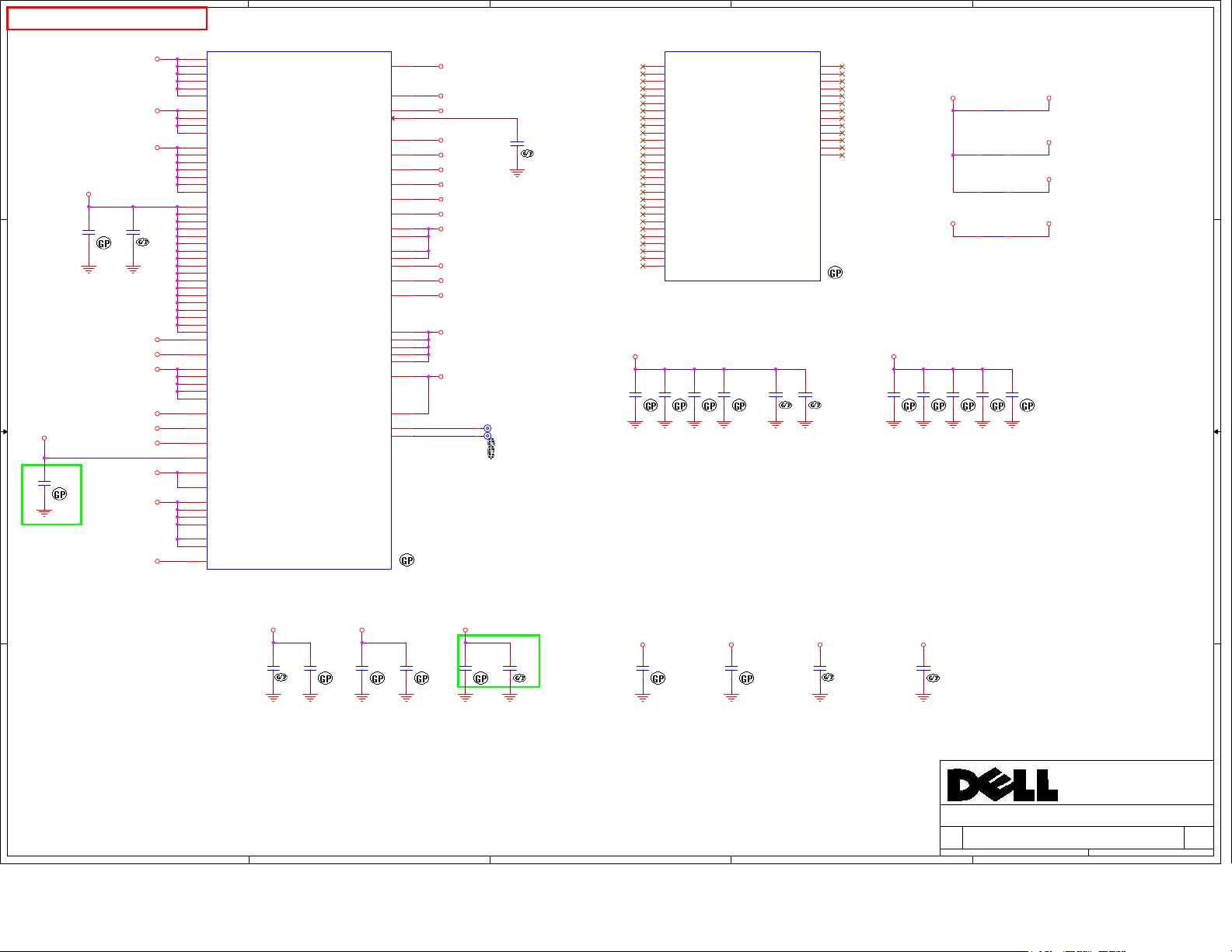

DDR4 ball type: Non-Interleaved Type

P

A_DQ0

A_DQ1

A_DQ2

A_DQ3

A_DQ4

A_DQ5

A_DQ6

A_DQ7

A_DQ8

A_DQ9

A_DQ10

A_DQ11

A_DQ12

A_DQ13

A_DQ14

A_DQ15

A_DQ32

A_DQ33

A_DQ34

A_DQ35

A_DQ36

A_DQ37

A_DQ38

A_DQ39

A_DQ40

A_DQ41

A_DQ42

A_DQ43

A_DQ44

A_DQ45

A_DQ46

A_DQ47

B_DQ32

B_DQ33

B_DQ34

B_DQ35

B_DQ36

B_DQ37

B_DQ38

B_DQ39

B_DQ40

B_DQ41

B_DQ42

B_DQ43

B_DQ44

B_DQ45

B_DQ47

AW35

AW34

AW36

AW37

A26

D26

D28

C28

B26

C26

B28

A28

B30

D30

B33

D32

A30

C30

B32

C32

H37

H34

K34

K35

H36

H35

K36

K37

N36

N34

R37

R34

N37

N35

R36

R35

AN35

AN34

AR35

AR34

AN37

AN36

AR36

AR37

AU35

AU34

AU37

AU36

BA35

BA34

BC35

BC34

BA37

BA36

BC36

BC37

BE35

BE34

BG35

BG34

BE37

BE36

BG36

BG37

WHISKEY-LAKE-GP

C

D

R0_DQ0/DDR0_DQ0

D

R0_DQ1/DDR0_DQ1

D

D

DR0_DQ2/DDR0_DQ2

D

D

R0_DQ3/DDR0_DQ3

D

R0_DQ4/DDR0_DQ4

D

D

DR0_DQ5/DDR0_DQ5

D

D

R0_DQ6/DDR0_DQ6

D

R0_DQ7/DDR0_DQ7

D

D

D

R0_DQ8/DDR0_DQ8

D

D

R0_DQ9/DDR0_DQ9

D

D

R0_DQ10/DDR0_DQ10

D

D

R0_DQ11/DDR0_DQ11

D

R0_DQ12/DDR0_DQ12

D

D

D

R0_DQ13/DDR0_DQ13

D

R0_DQ14/DDR0_DQ14

D

D

D

R0_DQ15/DDR0_DQ15

D

R0_DQ16/DDR0_DQ32

D

D

R0_DQ17/DDR0_DQ33

D

D

R0_DQ18/DDR0_DQ34

D

D

R0_DQ19/DDR0_DQ35

D

D

D

R0_DQ20/DDR0_DQ36

D

R0_DQ21/DDR0_DQ37

D

D

D

R0_DQ22/DDR0_DQ38

D

R0_DQ23/DDR0_DQ39

D

D

R0_DQ24/DDR0_DQ40

D

D

D

R0_DQ25/DDR0_DQ41

D

D

R0_DQ26/DDR0_DQ42

D

R0_DQ27/DDR0_DQ43

D

D

D

R0_DQ28/DDR0_DQ44

D

D

R0_DQ29/DDR0_DQ45

D

R0_DQ30/DDR0_DQ46

D

D

D

R0_DQ31/DDR0_DQ47

D

R0_DQ32/DDR1_DQ0

D

D

D

R0_DQ33/DDR1_DQ1

D

D

R0_DQ34/DDR1_DQ2

D

R0_DQ35/DDR1_DQ3

D

D

D

R0_DQ36/DDR1_DQ4

D

D

R0_DQ37/DDR1_DQ5

D

R0_DQ38/DDR1_DQ6

D

D

R0_DQ39/DDR1_DQ7

D

D

D

R0_DQ40/DDR1_DQ8

D

R0_DQ41/DDR1_DQ9

D

D

D

R0_DQ42/DDR1_DQ10

D

R0_DQ43/DDR1_DQ11

D

D

R0_DQ44/DDR1_DQ12

D

D

R0_DQ45/DDR1_DQ13

D

D

D

R0_DQ46/DDR1_DQ14

D

R0_DQ47/DDR1_DQ15

D

D

D

R0_DQ48/DDR1_DQ32

D

D

R0_DQ49/DDR1_DQ33

D

R0_DQ50/DDR1_DQ34

D

D

D

R0_DQ51/DDR1_DQ35

D

R0_DQ52/DDR1_DQ36

D

D

D

R0_DQ53/DDR1_DQ37

D

DR0_DQ54/DDR1_DQ38

D

D

R0_DQ55/DDR1_DQ39

D

D

R0_DQ56/DDR1_DQ40

D

D

R0_DQ57/DDR1_DQ41

D

R0_DQ58/DDR1_DQ42

D

D

D

R0_DQ59/DDR1_DQ43

D

D

R0_DQ60/DDR1_DQ44

D

R0_DQ61/DDR1_DQ45

D

D

D

R0_DQ62/DDR1_DQ46

D

R0_DQ63/DDR1_DQ47

D

D

ZZ.00CPU.271

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

B_DQ0

M

B_DQ1

_

M

B_DQ2

_

M

_

B_DQ3

M

B_DQ4

_

M

_B_DQ5

M

B_DQ6

_

M

B_DQ7

_

M

_

B_DQ8

M

_

B_DQ9

M

B_DQ10

_

M

_

B_DQ11

M

_B_DQ12

M

B_DQ13

_

M

_

B_DQ14

M

B_DQ15

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_B_DQ46

M

_

M

DQ Bit Swapping is allowed within the same byte, a nd Byte Swapping is allowed within the same channel.

Clock (CLK and CLK#) and Strobe ( DQS and DQS#) dif ferential signal swapping within a pair is not allow ed. Also differen tial

clock pair to c lock pair swapping within a channel is not allowed.

4

U1B

2 OF 20

D

R0_CKN0/DDR0_CKN0

D

R0_CKP0/DDR0_CKP0

D

D

DR0_CKN1/DDR0_CKN1

D

D

R0_CKP1/DDR0_CKP1

D

DR0_CKE0/DDR0_CKE0

D

D

R0_CKE1/DDR0_CKE1

D

R0_CKE2/NC

D

D

D

R0_CKE3/NC

D

D

R0_CS#0/DDR0_CS#0

D

D

R0_CS#1/DDR0_CS#1

D

R0_ODT0/DDR0_ODT0

D

D

C

/DDR0_ODT1

N

D

R0_CAB9/DDR0_MA0

D

R0_CAB8/DDR0_MA1

D

D

R0_CAB5/DDR0_MA2

D

D

/DDR0_MA3

C

N

/DDR0_MA4

C

N

D

R0_CAA0/DDR0_MA5

D

R0_CAA2/DDR0_MA6

D

D

D

R0_CAA4/DDR0_MA7

D

R0_CAA3/DDR0_MA8

D

D

R0_CAA1/DDR0_MA9

D

D

D

R0_CAB7/DDR0_MA10

D

D

R0_CAA7/DDR0_MA11

D

R0_CAA6/DDR0_MA12

D

D

D

R0_CAB0/DDR0_MA13

D

R0_CAB2/DDR0_MA14

D

D

D

R0_CAB1/DDR0_MA15

D

R0_CAB3/DDR0_MA16

D

D

D

R0_CAB4/DDR0_BA0

D

R0_CAB6/DDR0_BA1

D

D

D

R0_CAA5/DDR0_BG0

D

R0_CAA8/DDR0_ACT#

D

D

R0_CAA9/DDR0_BG1

D

D

R0_DQSN0/DDR0_DQSN0

D

D

D

R0_DQSP0/DDR0_DQSP0

D

R0_DQSN1/DDR0_DQSN1

D

D

R0_DQSP1/DDR0_DQSP1

D

D

R0_DQSN2/DDR0_DQSN4

D

D

D

R0_DQSP2/DDR0_DQSP4

D

R0_DQSN3/DDR0_DQSN5

D

D

D

R0_DQSP3/DDR0_DQSP5

D

D

R0_DQSN4/DDR1_DQSN0

D

R0_DQSP4/DDR1_DQSP0

D

D

D

R0_DQSN5/DDR1_DQSN1

D

R0_DQSP5/DDR1_DQSP1

D

D

D

R0_DQSN6/DDR1_DQSN4

D

DR0_DQSP6/DDR1_DQSP4

D

D

R0_DQSN7/DDR1_DQSN5

D

D

R0_DQSP7/DDR1_DQSP5

D

/DDR0_ALERT#

C

N

C

/DDR0_PAR

N

D

R_VREF_CA

D

R0_VREF_DQ0

D

D

D

R0_VREF_DQ1

D

R1_VREF_DQ

D

D

R_VTT_CTL

D

D

_

A_CLK#0

V32

M

A_CLK0

_

V31

M

A_CLK#1

_

T32

M

_

A_CLK1

T31

M

A_CKE0

_

U36

M

_

A_CKE1

U37

M

A_CKE2

_

U34

M

_

A_CKE3

U35

M

_

A_CS#0

AE32

M

A_CS#1

_

AF32

M

A_ODT0

_

AE31

M

AF31

_

A_B9

AC37

M

A_B8

_

AC36

M

_

A_B5

AC34

M

AC35

AA35

_

A_A0

AB35

M

_

A_A2

AA37

M

A_A4

_

AA36

M

_

A_A3

AB34

M

_

A_A1

W36

M

A_B7

_

Y31

M

_

A_A7

W34

M

A_A6

_

AA34

M

_

A_B0

AC32

M

A_B2

_

AC31

M

_

A_B1

AB32

M

_

A_B3

Y32

M

A_B4

_

W32

M

_

A_B6

AB31

M

A_A5

_

V34

M

A_A8

_

V35

M

A_A9

_

W35

M

_

A_DQS_DN0

C27

M

A_DQS_DP0

_

D27

M

_

A_DQS_DN1

D31

M

_A_DQS_DP1

C31

M

A_DQS_DN4

_

J35

M

_

A_DQS_DP4

J34

M

A_DQS_DN5

_

P34

M

_

A_DQS_DP5

P35

M

_

B_DQS_DN0

AP35

M

_

B_DQS_DP0

AP34

M

_

B_DQS_DN1

AV34

M

_

B_DQS_DP1

AV35

M

B_DQS_DN4

_

BB35

M

B_DQS_DP4

_

BB34

M

_

B_DQS_DN5

BF34

M

B_DQS_DP5

_

BF35

M

W37

W31

R_CA_VREF

D

F36

D

_

SM_VREF_CNTA

D35

V

D37

_

SM_VREF_CNTB

E36

V

M

_PGCNTL

C35

S

3

M_A_DQS0

M_A_DQS1

M_A_DQS4

M_A_DQS5

M_B_DQS0

M_B_DQS1

M_B_DQS4

M_B_DQS5

M

S

_PGCNTL

M_A_DQ[16:23]

M_A_DQ[24:31]

M_A_DQ[48:55]

M_A_DQ[56:63]

M_B_DQ[16:23]

M_B_DQ[24:31]

M_B_DQ[48:55]

M_B_DQ[56:63]

5

01

G

Q

S

PJA138KA-GP

084.00138.0A31

_

A_DQ16

M

_

A_DQ17

M

A_DQ18

_

M

A_DQ19

_

M

_

A_DQ20

M

_

A_DQ21

M

A_DQ22

_

M

_

A_DQ23

M

A_DQ24

_

M

_

A_DQ25

M

A_DQ26

_

M

_

A_DQ27

M

A_DQ28

_

M

A_DQ29

_

M

A_DQ30

_

M

A_DQ31

_

M

_

A_DQ48

M

A_DQ49

_

M

_

A_DQ50

M

_

A_DQ51

M

A_DQ52

_

M

_

A_DQ53

M

_

A_DQ54

M

A_DQ55

_

M

_

A_DQ56

M

_

A_DQ57

M

A_DQ58

_

M

_

A_DQ59

M

A_DQ60

_

M

_

A_DQ61

M

A_DQ62

_

M

A_DQ63

_

M

_

B_DQ16

M

_

B_DQ17

M

B_DQ18

_

M

B_DQ19

_

M

_

B_DQ20

M

B_DQ21

_

M

_B_DQ22

M

B_DQ23

_

M

B_DQ24

_

M

_

B_DQ25

M

_

B_DQ26

M

B_DQ27

_

M

_

B_DQ28

M

_B_DQ29

M

B_DQ30

_

M

_

B_DQ31

M

B_DQ48

_

M

_

B_DQ49

M

_

B_DQ50

M

_

B_DQ51

M

_

B_DQ52

M

_

B_DQ53

M

B_DQ54

_

M

B_DQ55

_

M

_

B_DQ56

M

B_DQ57

_

M

_

B_DQ58

M

B_DQ59

_

M

B_DQ60

_

M

B_DQ61

_

M

_

B_DQ62

M

_B_DQ63

M

J22

H25

G22

H22

F25

J25

G25

F22

D22

C22

C24

D24

A22

B22

A24

B24

G31

G32

H29

H28

G28

G29

H31

H32

L31

L32

N29

N28

L28

L29

N31

N32

AJ29

AJ30

AM32

AM31

AM30

AM29

AJ31

AJ32

AR31

AR32

AV30

AV29

AR30

AR29

AV32

AV31

BA32

BA31

BD31

BD32

BA30

BA29

BD29

BD30

BG31

BG32

BK32

BK31

BG29

BG30

BK30

BK29

C

WHISKEY-LAKE-GP

ZZ.00CPU.271

2

P

U1C

R1_DQ0/DDR0_DQ16

D

D

D

R1_DQ1/DDR0_DQ17

D

R1_DQ2/DDR0_DQ18

D

D

DR1_DQ3/DDR0_DQ19

D

D

R1_DQ4/DDR0_DQ20

D

R1_DQ5/DDR0_DQ21

D

D

DR1_DQ6/DDR0_DQ22

D

D

R1_DQ7/DDR0_DQ23

D

R1_DQ8/DDR0_DQ24

D

D

D

R1_DQ9/DDR0_DQ25

D

D

R1_DQ10/DDR0_DQ26

D

D

R1_DQ11/DDR0_DQ27

D

D

R1_DQ12/DDR0_DQ28

D

R1_DQ13/DDR0_DQ29

D

D

D

R1_DQ14/DDR0_DQ30

D

R1_DQ15/DDR0_DQ31

D

D

D

R1_DQ16/DDR0_DQ48

D

R1_DQ17/DDR0_DQ49

D

D

R1_DQ18/DDR0_DQ50

D

D

R1_DQ19/DDR0_DQ51

D

D

R1_DQ20/DDR0_DQ52

D

D

D

R1_DQ21/DDR0_DQ53

D

R1_DQ22/DDR0_DQ54

D

D

D

R1_DQ23/DDR0_DQ55

D

R1_DQ24/DDR0_DQ56

D

D

R1_DQ25/DDR0_DQ57

D

D

D

R1_DQ26/DDR0_DQ58

D

D

R1_DQ27/DDR0_DQ59

D

R1_DQ28/DDR0_DQ60

D

D

D

R1_DQ29/DDR0_DQ61

D

D

R1_DQ30/DDR0_DQ62

D

R1_DQ31/DDR0_DQ63

D

D

D

R1_DQ32/DDR1_DQ16

D

R1_DQ33/DDR1_DQ17

D

D

D

R1_DQ34/DDR1_DQ18

D

D

R1_DQ35/DDR1_DQ19

D

R1_DQ36/DDR1_DQ20

D

D

D

R1_DQ37/DDR1_DQ21

D

D

R1_DQ38/DDR1_DQ22

D

R1_DQ39/DDR1_DQ23

D

D

R1_DQ40/DDR1_DQ24

D

D

D

R1_DQ41/DDR1_DQ25

D

R1_DQ42/DDR1_DQ26

D

D

D

R1_DQ43/DDR1_DQ27

D

R1_DQ44/DDR1_DQ28

D

D

R1_DQ45/DDR1_DQ29

D

D

R1_DQ46/DDR1_DQ30

D

D

D

R1_DQ47/DDR1_DQ31

D

R1_DQ48/DDR1_DQ48

D

D

D

R1_DQ49/DDR1_DQ49

D

D

R1_DQ50/DDR1_DQ50

D

R1_DQ51/DDR1_DQ51

D

D

D

R1_DQ52/DDR1_DQ52

D

R1_DQ53/DDR1_DQ53

D

D

D

R1_DQ54/DDR1_DQ54

D

DR1_DQ55/DDR1_DQ55

D

D

R1_DQ56/DDR1_DQ56

D

D

R1_DQ57/DDR1_DQ57

D

D

R1_DQ58/DDR1_DQ58

D

R1_DQ59/DDR1_DQ59

D

D

D

R1_DQ60/DDR1_DQ60

D

D

R1_DQ61/DDR1_DQ61

D

R1_DQ62/DDR1_DQ62

D

D

D

R1_DQ63/DDR1_DQ63

D

3 OF 20

R1_CKN0/DDR1_CKN0

D

D

D

R1_CKP0/DDR1_CKP0

D

R1_CKN1/DDR1_CKN1

D

D

DR1_CKP1/DDR1_CKP1

D

R1_CKE0/DDR1_CKE0

D

D

DR1_CKE1/DDR1_CKE1

D

D

R1_CKE2/NC

D

R1_CKE3/NC

D

D

D

R1_CS#0/DDR1_CS#0

D

D

R1_CS#1/DDR1_CS#1

D

D

R1_ODT0/DDR1_ODT0

D

/DDR1_ODT1

C

N

D

R1_CAB9/DDR1_MA0

D

R1_CAB8/DDR1_MA1

D

D

D

R1_CAB5/DDR1_MA2

D

/DDR1_MA3

C

N

/DDR1_MA4

C

N

R1_CAA0/DDR1_MA5

D

D

R1_CAA2/DDR1_MA6

D

D

D

R1_CAA4/DDR1_MA7

D

R1_CAA3/DDR1_MA8

D

D

D

R1_CAA1/DDR1_MA9

D

R1_CAB7/DDR1_MA10

D

D

R1_CAA7/DDR1_MA11

D

D

D

R1_CAA6/DDR1_MA12

D

D

R1_CAB0/DDR1_MA13

D

D

R1_CAB2/DDR1_MA14

D

D

R1_CAB1/DDR1_MA15

D

R1_CAB3/DDR1_MA16

D

D

R1_CAB4/DDR1_BA0

D

D

D

R1_CAB6/DDR1_BA1

D

D

R1_CAA5/DDR1_BG0

D

D

R1_CAA9/DDR1_BG1

D

D

R1_CAA8/DDR1_ACT#

D

R1_DQSN0/DDR0_DQSN2

D

D

D

R1_DQSP0/DDR0_DQSP2

D

R1_DQSN1/DDR0_DQSN3

D

D

D

R1_DQSP1/DDR0_DQSP3

D

R1_DQSN2/DDR0_DQSN6

D

D

R1_DQSP2/DDR0_DQSP6

D

D

R1_DQSN3/DDR0_DQSN7

D

D

D

R1_DQSP3/DDR0_DQSP7

D

R1_DQSN4/DDR1_DQSN2

D

D

D

R1_DQSP4/DDR1_DQSP2

D

D

R1_DQSN5/DDR1_DQSN3

D

R1_DQSP5/DDR1_DQSP3

D

D

D

R1_DQSN6/DDR1_DQSN6

D

R1_DQSP6/DDR1_DQSP6

D

D

D

R1_DQSN7/DDR1_DQSN7

D

DR1_DQSP7/DDR1_DQSP7

D

C

/DDR1_ALERT#

N

C

/DDR1_PAR

N

AM_RESET#

R

D

D

R_RCOMP0

D

R_RCOMP1

D

D

D

R_RCOMP2

D

_

B_CLK#0

AF28

M

_

B_CLK0

AF29

M

B_CLK#1

_

AE28

M

B_CLK1

_

AE29

M

_

B_CKE0

T28

M

B_CKE1

_

T29

M

_

B_CKE2

V28

M

B_CKE3

_

V29

M

B_CS#0

_

AL37

M

_

B_CS#1

AL35

M

B_ODT0

_

AL36

M

AL34

B_B9

_

AG36

M

B_B8

_

AG35

M

_

B_B5

AF34

M

AG37

AE35

_

B_A0

AF35

M

B_A2

_

AE37

M

_

B_A4

AC29

M

_

B_A3

AE36

M

B_A1

_

AB29

M

_

B_B7

AG34

M

_

B_A7

AC28

M

B_A6

_

AB28

M

_

B_B0

AK35

M

_

B_B2

AJ35

M

B_B1

_

AK34

M

B_B3

_

AJ34

M

_

B_B4

AJ37

M

B_B6

_

AJ36

M

B_A5

_

W29

M

B_A9

_

Y28

M

_B_A8

W28

M

A_DQS_DN2

_

H24

M

_

A_DQS_DP2

G24

M

_

A_DQS_DN3

C23

M

A_DQS_DP3

_

D23

M

_

A_DQS_DN6

G30

M

_A_DQS_DP6

H30

M

A_DQS_DN7

_

L30

M

_

A_DQS_DP7

N30

M

B_DQS_DN2

_

AL31

M

_

B_DQS_DP2

AL30

M

_

B_DQS_DN3

AU31

M

_

B_DQS_DP3

AU30

M

_

B_DQS_DN6

BC31

M

_

B_DQS_DP6

BC30

M

B_DQS_DN7

_

BH31

M

B_DQS_DP7

_

BH30

M

Y29

AE34

BU31

_RCOMP_0

M

BN28

S

M

_RCOMP_1

BN27

S

M_RCOMP_2

BN29

S

Layout Note:

M_A_DQS2

M_A_DQS3

M_A_DQS6

M_A_DQS7

M_B_DQS2

M_B_DQS3

M_B_DQS6

M_B_DQS7

01 200R2F-L-GP

5

R

1 2

5

02 80D6R2F-L-GP

1 2

R

5

03 162R2F-GP

1 2

R

1

#543016

Design Guidelin e:

SM_RCOMP keep r outing length less than 500 mils.

D

3V_S5

3

12

06

5

R

10KR2J-L-GP

5

02_G

Q

D

G

S

2N7002K-2-GP

02

5

Q

Notice:ZZ.2N702 .J3101

84.2N702.J31

3V_S0

D

3

12

5

07

R

10KR2J-L-GP

T_CNTL

T

V

D

<Core Design>

<Core Design>

<Core Design>

W

W

W

stron Corporation

stron Corporation

stron Corporation

i

i

i

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

1

1

1

2

2

2

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

i

tle

Title

Title

T

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

2

2

2

A

A

A

Date: Sheet

Date: Sheet

2

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

C

C

C

P

P

P

U_(DDR)

U_(DDR)

U_(DDR)

SP 13" WHL-U

SP 13" WHL-U

SP 13" WHL-U

A

A

A

W

W

W

1

5 1

5 1

5 1

f

f

f

o

o

o

0

0

0

0

0

0

A

A

A

06Thursday, March 07, 2019

06Thursday, March 07, 2019

06Thursday, March 07, 2019

5

WWW.AliSaler.Com

Main Func = CPU

C

FG

C

315

FG

C

415

D D

C C

B B

FG

1 2

R

60

1 49D9R2F-GP

T

P6

3

C

4

FG

C

FG

I

TP

1

18

_RCOMP

_PMODE

4

M4

M3

AB5

W4

CG2

CG1

BV24

BV25

BK36

BK35

W3

AM4

AM3

3

SV

R

SV

R

D_TP#CN36

SV

R

SV

R

SV

R

SV

R

SV

R

SV

R

SV

R

SV

R

SV

R

D_TP#CR35

SV

R

1

OF 20

7

D_TP#F37

D_TP#F34

_TRIG

ST

I

D_TP#BJ36

D_TP#BJ34

BK34

P#

T

BR18

P#

T

D_TP#BT9

D_TP#BT8

D_TP#BP8

D_TP#BP9

SV

D#CR4

R

SV

D#CP3

R

SV

D#CR3

R

D_TP#AT3

D_TP#AU3

D#AN1

SV

R

SV

D#AN2

R

D#AN4

SV

R

SV

D#AN3

R

ST

_TP0

I

ST

_TP1

I

_TRIG0

ST

I

ST

_TRIG1

I

P#

BP34

T

SS

V

P#

BP35

T

F37

F34

CP36

CN36

BJ36

BJ34

BK34

BR18

BT9

BT8

BP8

BP9

CR4

CP3

CR3

AT3

AU3

AN1

AN2

AN4

AN3

AL2

AL1

AL4

AL3

BP34

P36

B

BP35

CR35

I

ST

_TRIG

1

T

P6

20

TPAD14-OP-GP

C

1Q

PU

T4

R4

T3

R3

J4

J3

R2

N2

R1

N1

J2

L2

J1

L1

L3

N3

L4

N4

H4

H3

WHL QS/CFL/WHL_ES1_CNL U

FG

0

C

1

FG

C

2

FG

C

FG

3

C

4

FG

C

5

FG

C

FG

6

C

FG

7

C

8

FG

C

9

FG

C

FG

10

C

11

FG

C

12

FG

C

FG

13

C

14

FG

C

15

FG

C

FG

16

C

FG

18

C

FG

17

C

19

FG

C

_RCOMP

FG

C

TP

_PMODE

I

SV

D#CG2

R

D#CG1

SV

R

D#H4

SV

R

SV

D#H3

R

SV

D#BV24

R

D#BV25

SV

R

SV

D#BK36

R

D#BK35

SV

R

SV

D#W3

R

D#AM4

SV

R

D_TP#AM3

SV

R

2

1

<Core Design>

<Core Design>

E1

KT

OCC#

S

A A

WHISKEY-LAKE-GP

S

KT

OCC#

1

T

P6

19

ZZ.00CPU.271

5

4

3

<Core Design>

istron Corporation

istron Corporation

istron Corporation

W

W

W

2

2

2

1F

1F

1F

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

4

4

4

Date: Sheet

Date: Sheet

Date: Sheet

2

PU

PU

PU

(CFG/IST)

(CFG/IST)

(CFG/IST)

C

C

C

AS

AS

AS

P 13" WHL-U

P 13" WHL-U

P 13" WHL-U

W

W

W

o

o

o

f

f

6 1

6 1

6 1

f

1

A

A

A

00

00

00

0

0

0

6Thursday, March 07, 2019

6Thursday, March 07, 2019

6Thursday, March 07, 2019

5

4

3

2

1

Main Func = CPU

V

C

CCORE_SENSE46

V

SCORE_SENSE46

S

S

ID_DATA_CPU46

V

D D

S

V

ID_CLK_CPU46

S

ID_ALERT#_CPU46

V

1

_VCCST_CPU

V

#

544669

CLOSE TO CPU

12

R

26

7

SVID DATA

C C

S

ID_DATA_CPU_R

V

SVID CLOCK

S

V

ID_CLK_CPU_R

B B

SVID ALERT

S

ID_ALERT#_CPU_R

V

100R2F-L1-GP-U

1 2

R

09 0R0402-PAD

7

1 2

R

32 0R0402-PAD

7

1 2

R

7

28 220R2J-L2-GP

1

V

_VCCST_CPU

DY

1

V

_VCCST_CPU

12

S

ID_DATA_CPU

V

#544669

CLOSE TO VR

12

R

7

23

54D9R2F-L1-GP

S

V

ID_CLK_CPU

#

544669

CLOSE TO CPU

R

7

27

56R2J-4-GP

S

ID_ALERT#_CPU

V

1

_CPU_CORE

V

C

P

AN9

V

AN10

V

AN24

V

AN26

V

AN27

V

AP2

V

AP9

V

AP24

V

AP26

V

AR5

V

AR6

V

AR7

V

AR8

V

AR10

V

AR25

V

AR27

V

AT9

V

AT24

V

AT26

V

AU5

V

AU6

V

AU7

V

AU8

V

AU9

V

AU24

V

AU25

V

AU26

V

AU27

V

AV2

V

AV5

V

AV7

V

AV10

V

AV27

V

AW5

V

AW6

V

AW7

V

AW8

V

AW9

V

AW10

V

BB9

R

BC24

R

AY9

R

BB24

R

WHISKEY-LAKE-GP

ZZ.00CPU.271

U1L

CCORE

C

CCORE

C

CCORE

C

C

CCORE

CCORE

C

CCORE

C

C

CCORE

C

CCORE

CCORE

C

CCORE

C

C

CCORE

CCORE

C

CCORE

C

C

CCORE

CCORE

C

CCORE

C

CCORE

C

C

CCORE

C

CCORE

C

CCORE

CCORE

C

C

CCORE

C

CCORE

CCORE

C

C

CCORE

C

CCORE

C

CCORE

C

CCORE

CCORE

C

C

CCORE

C

CCORE

CCORE

C

C

CCORE

CCORE

C

C

CCORE

CCORE

C

C

CCORE

CCORE

C

CCORE

C

VD#BB9

S

S

VD#BC24

S

VD#AY9

VD#BB24

S

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

C

C_SENSE

V

S_SENSE

S

V

I

DALERT#

V

V

R

1

2

OF 20

CCORE

C

CCORE

C

CCORE

C

C

CCORE

CCORE

C

CCORE

C

C

CCORE

C

CCORE

CCORE

C

CCORE

C

C

CCORE

CCORE

C

CCORE

C

C

CCORE

CCORE

C

CCORE

C

CCORE

C

C

CCORE

C

CCORE

C

CCORE

CCORE

C

C

CCORE

C

CCORE

CCORE

C

C

CCORE

C

CCORE

C

CCORE

C

CCORE

CCORE

C

C

CCORE

C

CCORE

CCORE

C

C

CCORE

CCORE

C

C

CCORE

I

DSCK

V

DSOUT

I

VD#Y3

S

CSTG

C

V

AW24

AW25

AW26

AW27

AY24

AY26

BA5

BA7

BA8

BA25

BA27

BB2

BB26

BC5

BC6

BC7

BC9

BC10

BC26

BC27

BD5

BD8

BD10

BD25

BD27

BE9

BE24

BE25

BE26

BE27

BF2

BF9

BF24

BF26

BG27

AN6

AN5

AA3

AA1

AA2

Y3

BG3

1

_CPU_CORE

V

V

C

CCORE_SENSE

V

SCORE_SENSE

S

S

V

ID_ALERT#_CPU_R

S

V

ID_CLK_CPU_R

S

V

ID_DATA_CPU_R

1

V

_VCCSTG

1

_CPU_CORE

V

12

R

7

100R2F-L1-GP-U

12

R

7

100R2F-L1-GP-U

19

V

CCORE_SENSE

C

V

S

SCORE_SENSE

20

Layout Note:

1

. Place close to CPU

2. VCC_SENSE/ VSS_SENSE

impedance=50 ohm

3. Length match<25mil

SVID_543016:

L

ayout Note:

The total Length of Data and Clock (from CPU to each

inch).

Route the Alert signal between the Clock and the Data signals.

A A

5

VR) must be equal (��0.1

4

<Core Design>

<Core Design>

<Core Design>

istron Corporation

istron Corporation

istron Corporation

W

W

W

2

2

2

1

1

1

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

U (VCORE/VID)

U (VCORE/VID)

U (VCORE/VID)

P

P

P

C

C

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

4

4

4

Thursday, March 07, 2019

Thursday, March 07, 2019

Thursday, March 07, 2019

Date: Sheet

Date: Sheet

3

Date: Sheet

2

C

A

A

A

SP 13" WHL-U

SP 13" WHL-U

SP 13" WHL-U

W

W

W

o

o

o

f

f

7 1

7 1

7 1

f

1

A

A

A

0

0

0

0

0

0

06

06

06

5

WWW.AliSaler.Com

Main Func = CPU

1

VCCGT

V_

V

GT_SENSE46

SS

V

GT_SENSE46

CC

V

SA_SENSE46

D D

C C

B B

A A

SS

V

C

C

1

V_

1

V_

SA_SENSE46

VCCGT

12

R

80

100R2F-L1-GP-U

12

R

80

100R2F-L1-GP-U

VCCSA

12

R

81

100R2F-L1-GP-U

12

R

80

100R2F-L1-GP-U

7

V

GT_SENSE

CC

V

GT_SENSE

SS

8

0

V

SA_SENSE

CC

V

SA_SENSE

SS

9

5

C

A5

A6

A8

A11

A12

A14

A15

A17

A18

A20

B3

B4

B6

B8

B11

B14

B17

B20

C2

C3

C6

C7

C8

C11

C12

C14

C15

C17

C18

C20

D4

D7

D11

D12

D14

D15

D17

D18

D20

E4

F5

F6

F7

F8

F11

F14

F17

F20

G11

G12

G14

G15

G17

G18

G20

H5

H6

H7

H8

H11

WHISKEY-LAKE-GP

ZZ.00CPU.271

4

1M

PU

WHL QS/CFL/WHL_ES1_CNL U

CC

GT

V

GT

CC

V

GT

CC

V

CC

GT

V

CC

GT

V

GT

CC

V

GT

CC

V

CC

GT

V

GT

CC

V

GT

CC

V

CC

GT

V

GT

CC

V

GT

CC

V

GT

CC

V

CC

GT

V

CC

GT

V

CC

GT

V

GT

CC

V

CC

GT

V

CC

GT

V

GT

CC

V

CC

GT

V

CC

GT

V

CC

GT

V

CC

GT

V

GT

CC

V

CC

GT

V

CC

GT

V

GT

CC

V

CC

GT

V

GT

CC

V

CC

GT

V

GT

CC

V

CC

GT

V

GT

CC

V

GT

CC

V

CC

GT

V

GT

CC

V

CC

GT

V

CC

GT

V

GT

CC

V

GT

CC

V

GT

CC

V

CC

GT

V

GT

CC

V

CC

GT

V

GT

CC

V

CC

GT

V

CC

GT

V

GT

CC

V

CC

GT

V

GT

CC

V

GT

CC

V

CC

GT

V

GT

CC

V

GT

CC

V

GT

CC

V

CC

GT

V

CC

GT

V

GT

CC

V

CC

GT_SENSE

V

SS

GT_SENSE

V

4

3

1

V_S3

D2

1

VCCGT

H12

H14

H15

H17

H18

H20

J7

J8

J11

J14

J17

J20

K2

K11

L7

L8

L10

M9

N7

N8

N9

N10

P2

P8

R9

T8

T9

T10

U8

U10

V9

W8

W9

AA9

AB2

AB8

AB9

AB10

AC8

AD9

AE8

AE9

AE10

AF2

AF8

AF10

AG8

AG9

AH9

AJ8

AJ10

AK2

AK9

AL8

AL9

AL10

AM8

V2

Y8

Y10

E3

D2

V_

V

CC

V

SS

1

V_

CPU_CORE

GT_SENSE

GT_SENSE

12

C

4

80

DY

SC1U10V2KX-1DLGP

1

V_

VCCST_CPU

1 2

C

1 SC1U10V2KX-1DLGP

80

1

V_

1 2

C

2 SC1U10V2KX-1DLGP

80

1

D2

V_VCCSFR_OC

1 2

C

80

3 SC1U10V2KX-1DLGP

1

V_

VCCST_CPU

C

12

80

7

3

0.12 A

SC22U6D3V3MX-1-DL-GP

SC1U10V2KX-1DLGP

C

12

80

6

1

OF 20

3

CC

GT

V

GT

CC

V

GT

CC

V

CC

GT

V

CC

GT

V

GT

CC

V

GT

CC

V

CC

GT

V

GT

CC

V

GT

CC

V

CC

GT

V

GT

CC

V

GT

CC

V

GT

CC

V

CC

GT

V

CC

GT

V

CC

GT

V

GT

CC

V

CC

GT

V

CC

GT

V

GT

CC

V

CC

GT

V

CC

GT

V

CC

GT

V

CC

GT

V

GT

CC

V

CC

GT

V

CC

GT

V

GT

CC

V

CC

GT

V

GT

CC

V

CC

GT

V

GT

CC

V

CC

CORE

V

CORE

CC

V

CORE

CC

V

CC

CORE

V

CORE

CC

V

CC

CORE

V

CC

CORE

V

CORE

CC

V

CORE

CC

V

CORE

CC

V

CC

CORE

V

CORE

CC

V

CC

CORE

V

CORE

CC

V

CC

CORE

V

CC

CORE

V

CORE

CC

V

CC

CORE

V

CORE

CC

V

CORE

CC

V

CC

CORE

V

CORE

CC

V

CORE

CC

V

CORE

CC

V

CC

CORE

V

CC

CORE

V

CORE

CC

V

0.04 A

VCCSTG

12

2

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

CC

V

SS

V

SS

V

CC

V

1

OF 20

4

CC

IO_OUT

IO_OUT

CC

IO_OUT

CC

IO_OUT

CC

CC

IO_OUT

IO_OUT

CC

IO_OUT

CC

CC

IO_OUT

CC

IO_OUT

IO_OUT

CC

IO_OUT

CC

CC

IO_OUT

IO_OUT

CC

IO_OUT

CC

CC

IO_OUT

IO_OUT

CC

SA

CC

V

CC

SA

V

CC

SA

V

CC

SA

V

SA

CC

V

CC

SA

V

CC

SA

V

SA

CC

V

CC

SA

V

CC

SA

V

CC

SA

V

CC

SA

V

SA

CC

V

CC

SA

V

CC

SA

V

SA

CC

V

IO_SENSE

IO_SENSE

SA_SENSE

SA_SENSE

C

1N

PU

AD36

AH32

AH36

AM36

AN32

AW32

AY36

BE32

BH36

R32

Y36

BC28

BP11

BP2

BG1

BG2

BL27

BM26

BR11

BT11

SCD1U16V2KX-3DLGP

C

80

5

Q

DD

V

Q

DD

V

Q

DD

V

DD

Q

V

Q

DD

V

Q

DD

V

DD

Q

V

DD

Q

V

Q

DD

V

Q

DD

V

DD

Q

V

D#BC28

SV

R

ST

CC

V

CC

ST

V

STG

CC

V

CC

STG

V

PLL_OC

CC

V

CC

PLL_OC

V

CC

PLL

V

CC

PLL

V

WHISKEY-LAKE-GP

AK24

AK26

AL24

AL25

AL26

AL27

AM25

AM27

BH24

BH25

BH26

BH27

BJ24

BJ26

BP16

BP18

BG8

BG10

BH9

BJ8

BJ9

BJ10

BK8

BK25

BK27

BL8

BL9

BL10

BL24

BL26

BM24

BN25

BP28

BP29

BE7

BG7

1

1

V_

VCCIO

+

VCCIO(ICCMAX.=2.73A

1

V_

V

SS

SA_SENSE

V

SA_SENSE

CC

ZZ.00CPU.271

<Core Design>

<Core Design>

<Core Design>

istron Corporation

istron Corporation

istron Corporation

W

W

W

2

2

2

1F

1F

1F

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

(VCCGT/VCCIO/VDDQ/VCCSA)

(VCCGT/VCCIO/VDDQ/VCCSA)

(VCCGT/VCCIO/VDDQ/VCCSA)

PU

PU

PU

C

C

C

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

4

4

4

Date: Sheet

Date: Sheet

Date: Sheet

2

AS

AS

AS

P 13" WHL-U

P 13" WHL-U

P 13" WHL-U

W

W

W

o

o

o

f

f

8 1

8 1

8 1

f

1

VCCSA

A

A

A

00

00

00

0

0

0

6Thursday, March 07, 2019

6Thursday, March 07, 2019

6Thursday, March 07, 2019

5

D D

C C

4

3

2

1

(Blanking)

B B

<Core Design>

<Core Design>

<Core Design>

istron Corporation

istron Corporation

istron Corporation

W

W

A A

T

tle

Title

Title

i

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

4

4

4

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

R

R

R

eserved)

eserved)

eserved)

(

(

(

2

W

2

2

2

1

1

1

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

A

A

A

SP 13" WHL-U

SP 13" WHL-U

SP 13" WHL-U

W

W

W

o

o

o

f

f

9 1

9 1

9 1

f

1

A

A

A

0

0

0

0

0

0

06Thursday, March 07, 2019

06Thursday, March 07, 2019

06Thursday, March 07, 2019

5

WWW.AliSaler.Com

Main Func = CPU

1

CPU_CORE

V_

4

1V_CPU_CORE

3

22U 0603 x 39 (7DY)

2

1

P

P

P

C1

002

VCCGT

12

U42

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

022

C1

12

DY

DY

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

D D

C C

1

V_

P

C1

C1

003

023

12

U42

P

12

004

U42

024

C1

U42

12

P

C1

12

P

C1

C1

005

12

P

C1

12

006

12

U42

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

026

025

C1

12

DY

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

VCCGT

P

P

037

C1

12

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

B B

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

038

C1

12

039

C1

12

P

P

C1

12

041

040

C1

12

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

P

12

P

12

C1

C1

C1

007

027

12

P

12

U42

008

028

C1

DY

22U 0603 x 35 (9 DY)

P

P

C1

12

042

043

C1

12

P

P

C1

009

12

P

029

C1

12

P

044

C1

12

P

C1

C1

010

030

045

011

12

P

031

C1

12

P

046

C1

12

12

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

C1

12

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

C1

12

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

P

C1

012

12

U42

P

032

C1

12

DY

P

047

C1

12

P

C1

C1

013

12

12

P

P

034

C1

12

P

12

C1

12

DY

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

048

C1

C1

12

014

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

036

DY

049

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

P

12

P

12

P

12

C1

C1

C1

C1

015

079

050

DY

016

12

U42

P

080

C1

12

P

051

C1

12

P

P

12

P

12

P

12

C1

C1

017

12

U42

P

081

C1

C1

12

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

052

C1

C1

12

P

P

018

12

U42

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

082

12

U42

P

053

12

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

C1

C1

C1

C1

019

083

054

12

U42

P

12

P

12

020

084

C1

055

C1

P

C1

021

12

P

056

C1

12

P

P

057

C1

12

DY

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

C1

065

12

A A

DY

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

5

P

058

066

059

C1

12

P

C1

067

12

DY

C1

12

P

C1

12

P

P

060

C1

C1

12

12

P

P

C1

C1

068

12

12

DY

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

061

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

069

DY

P

062

070

DY

DY

063

C1

12

P

C1

001

12

4

C1

12

P

C1

12

DY

P

064

C1

12

1

V_

VCCSA

VCCSA

P

P

C1

071

12

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

P

C1

072

12

12

22U 0603 x 8 (3DY)

P

P

C1

C1

073

DY

074

12

3

P

C1

C1

075

12

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

076

12

DY

P

P

12

C1

C1

077

DY

078

12

<Core Design>

<Core Design>

<Core Design>

istron Corporation

istron Corporation

istron Corporation

W

W

W

2

2

2

1F

1F

1F

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,

, 88, Sec.1, Hsin Tai Wu Rd., Hsichi h,