Page 1

5

D D

4

3

2

1

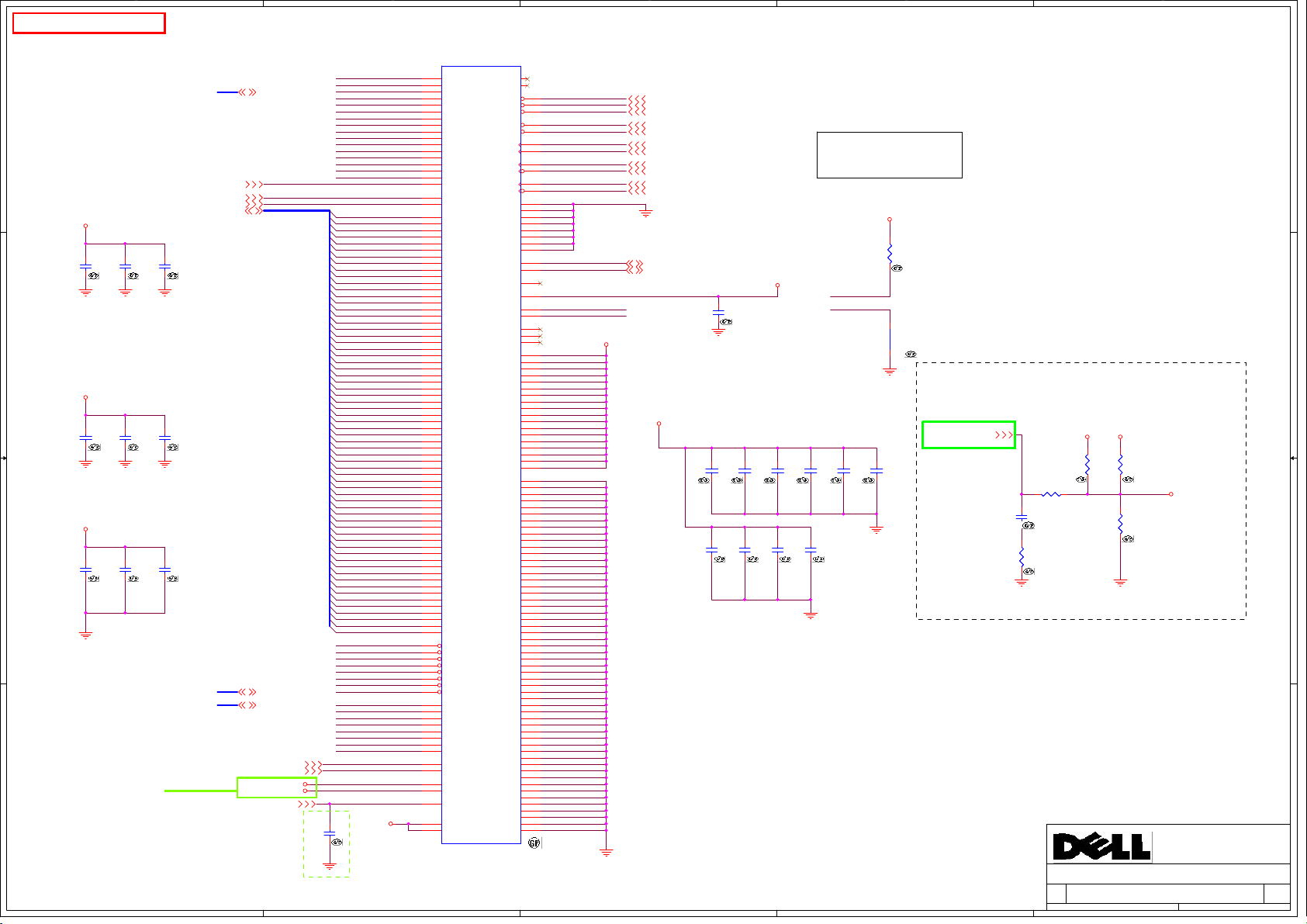

Hadley15" Schematics Document

Haswell ULT

C C

2013-06-28

REV : A00

B B

DY : None Installed

UMA: UMA only installed

OPS: Optimus solution installed.

eDP: Support eDP Panel installed.

LVDS: Support LVDS Panel installed.

A A

5

4

3

2

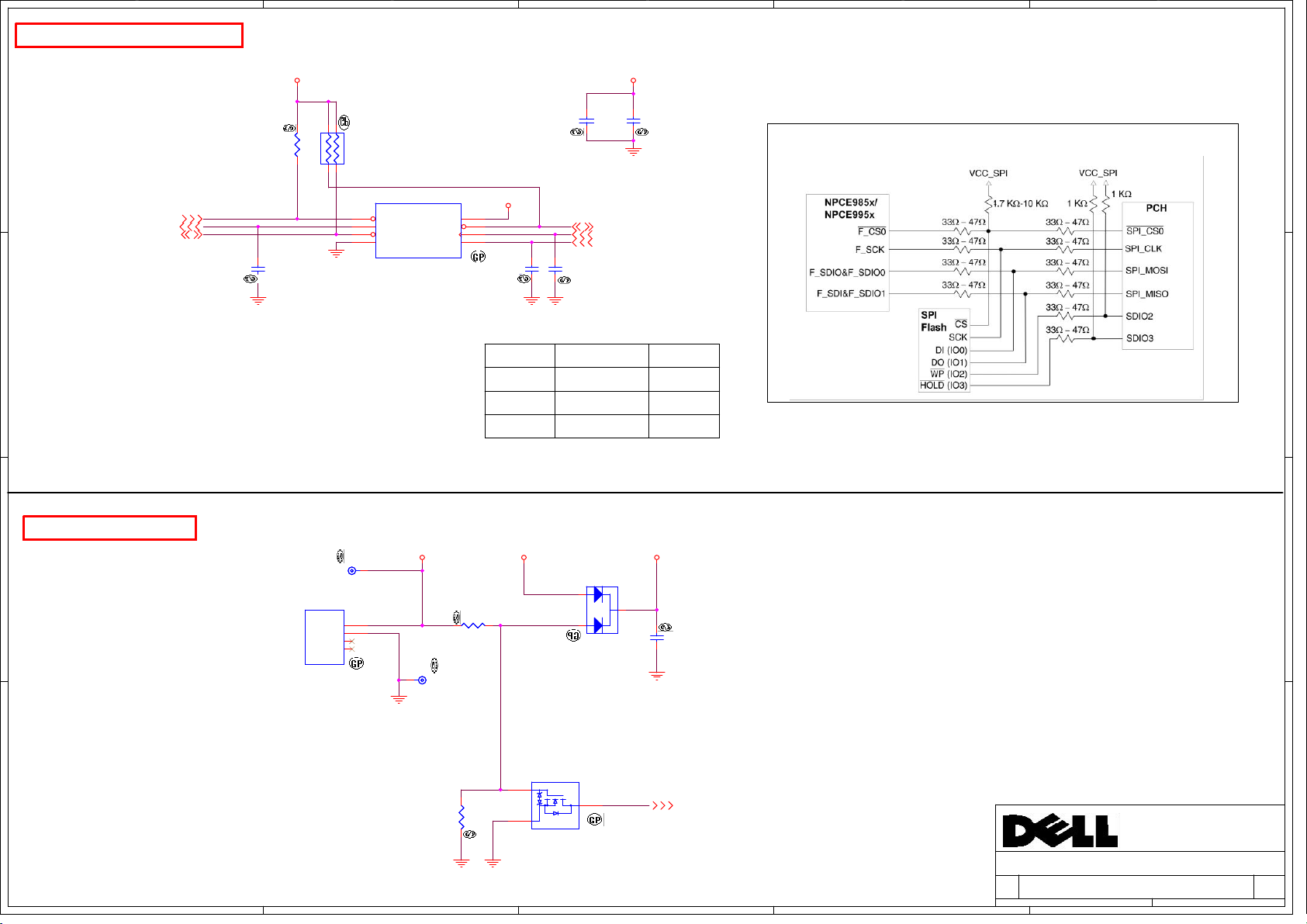

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

Title

Title

Title

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan , R.O.C.

Cover Page

Cover Page

Cover Page

Hadley 15"

Hadley 15"

Hadley 15"

1

1 101Friday, June 28, 2 013

of

1 101Friday, June 28, 2 013

of

1 101Friday, June 28, 2 013

X02

X02

X02

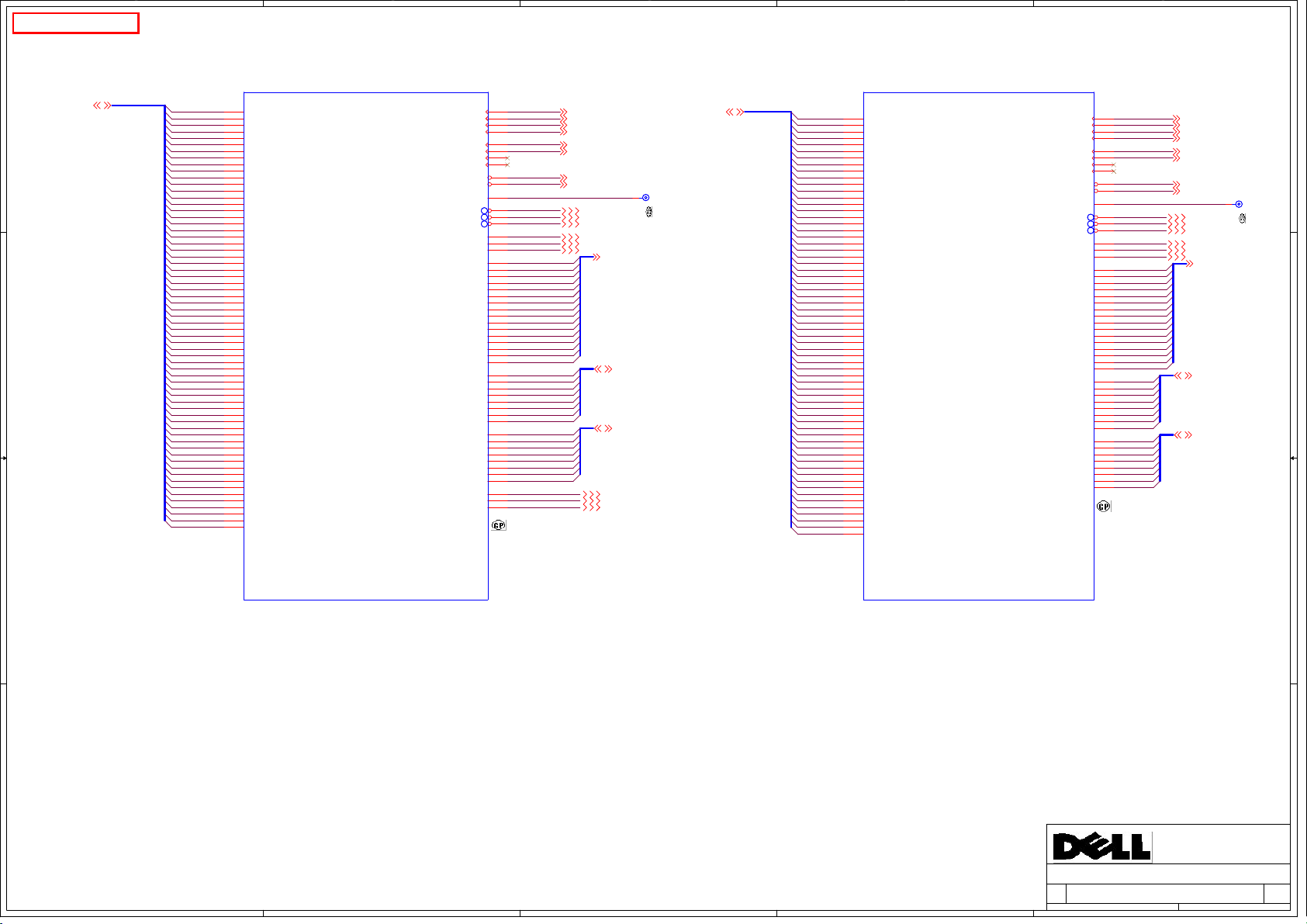

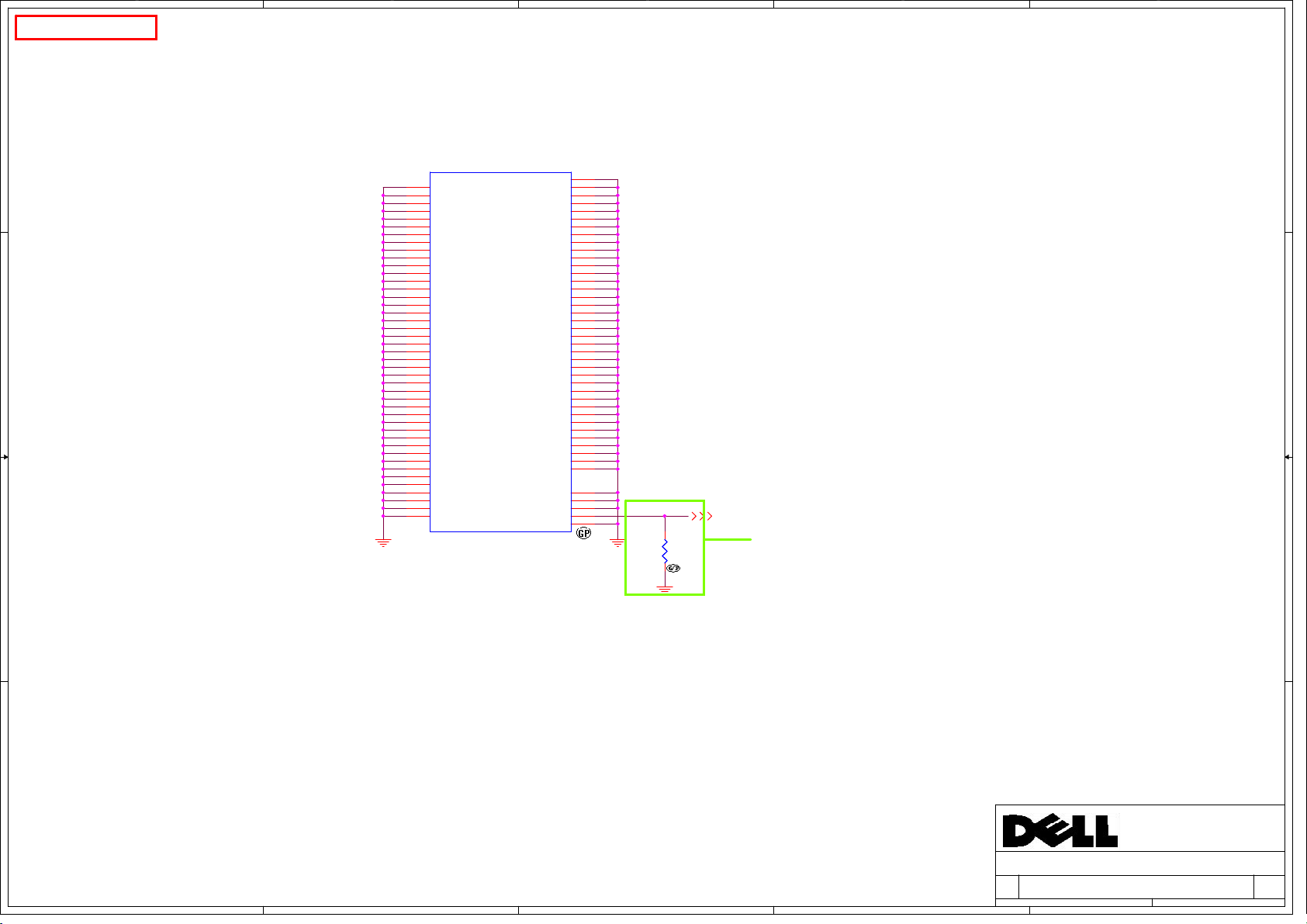

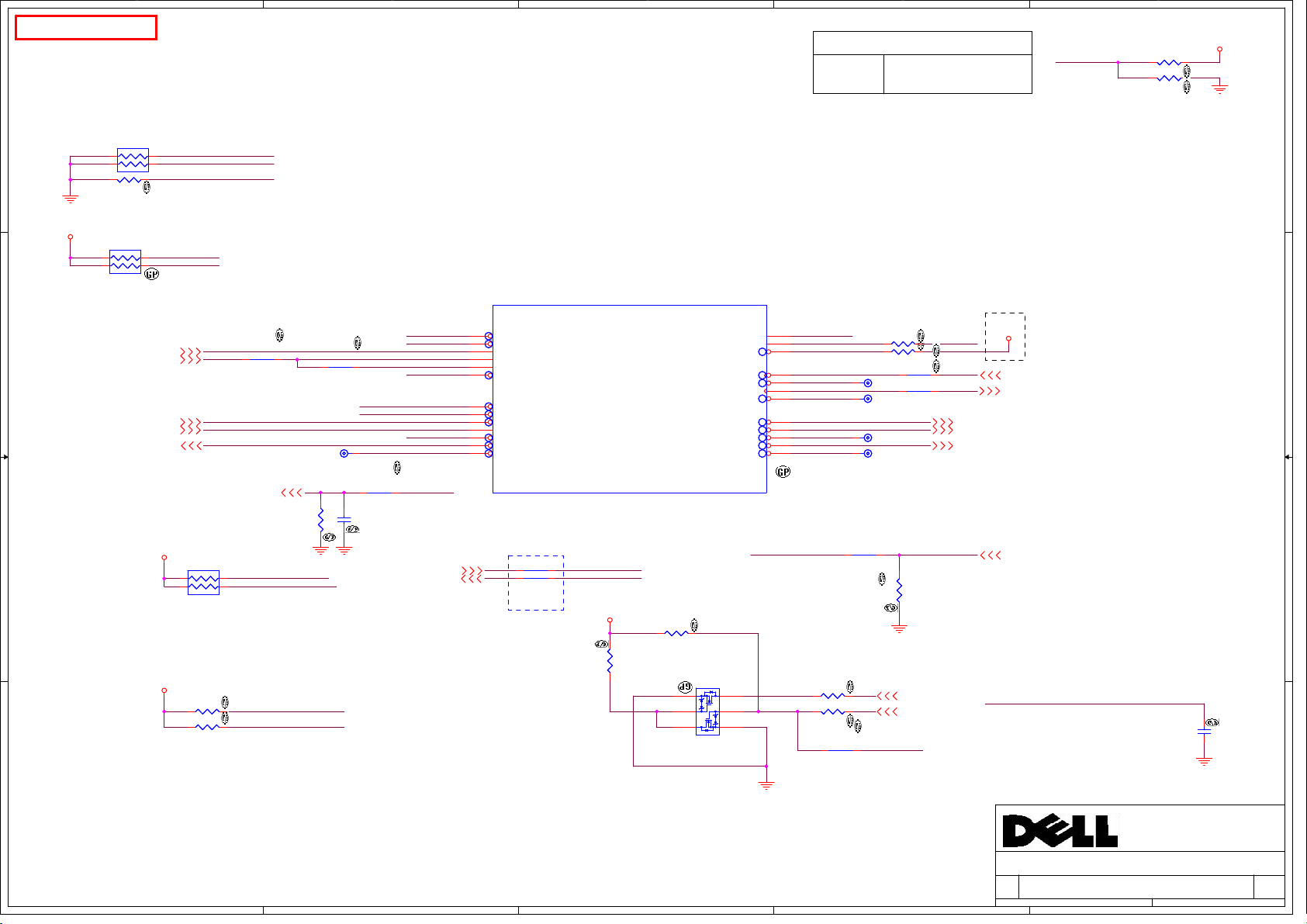

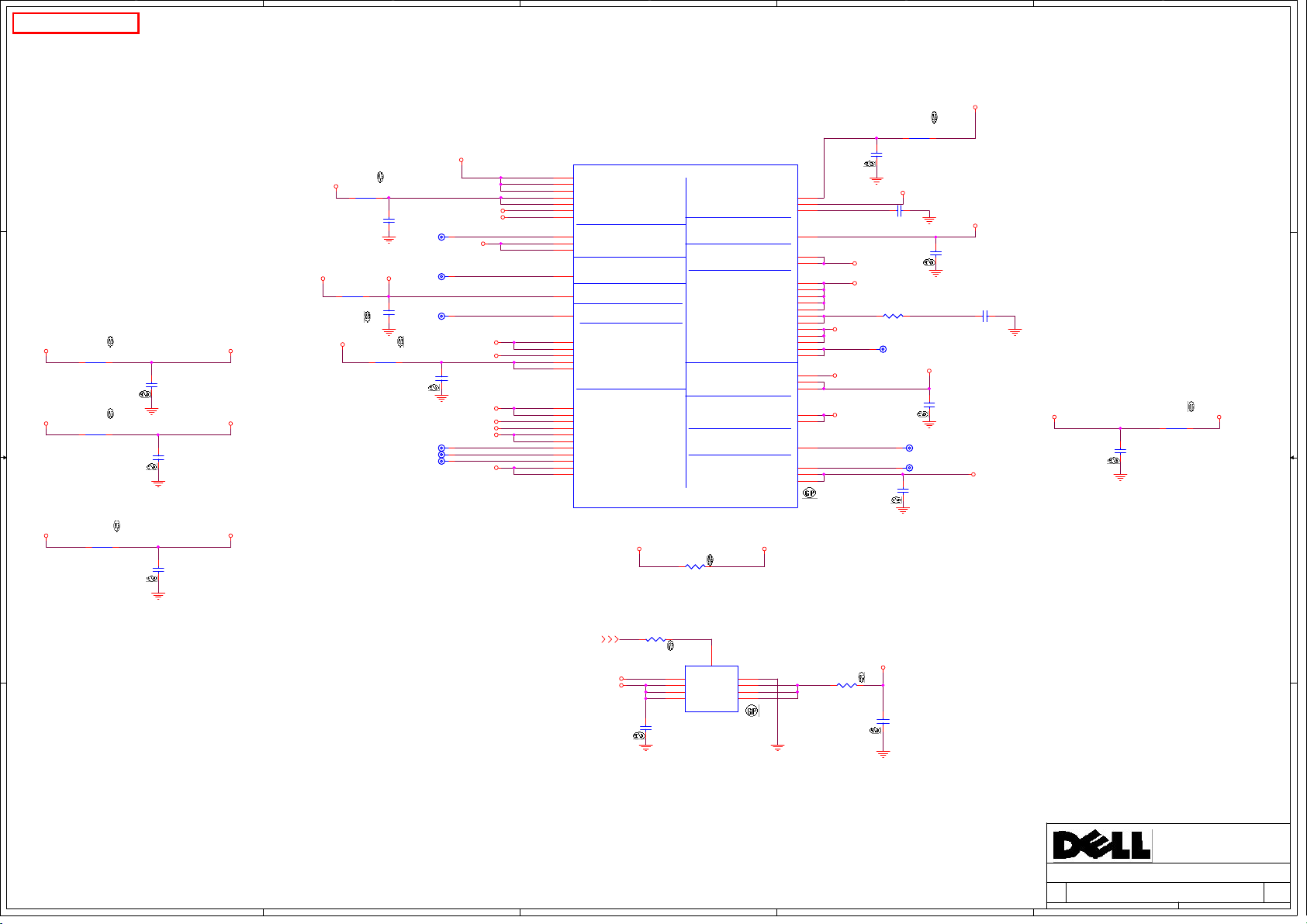

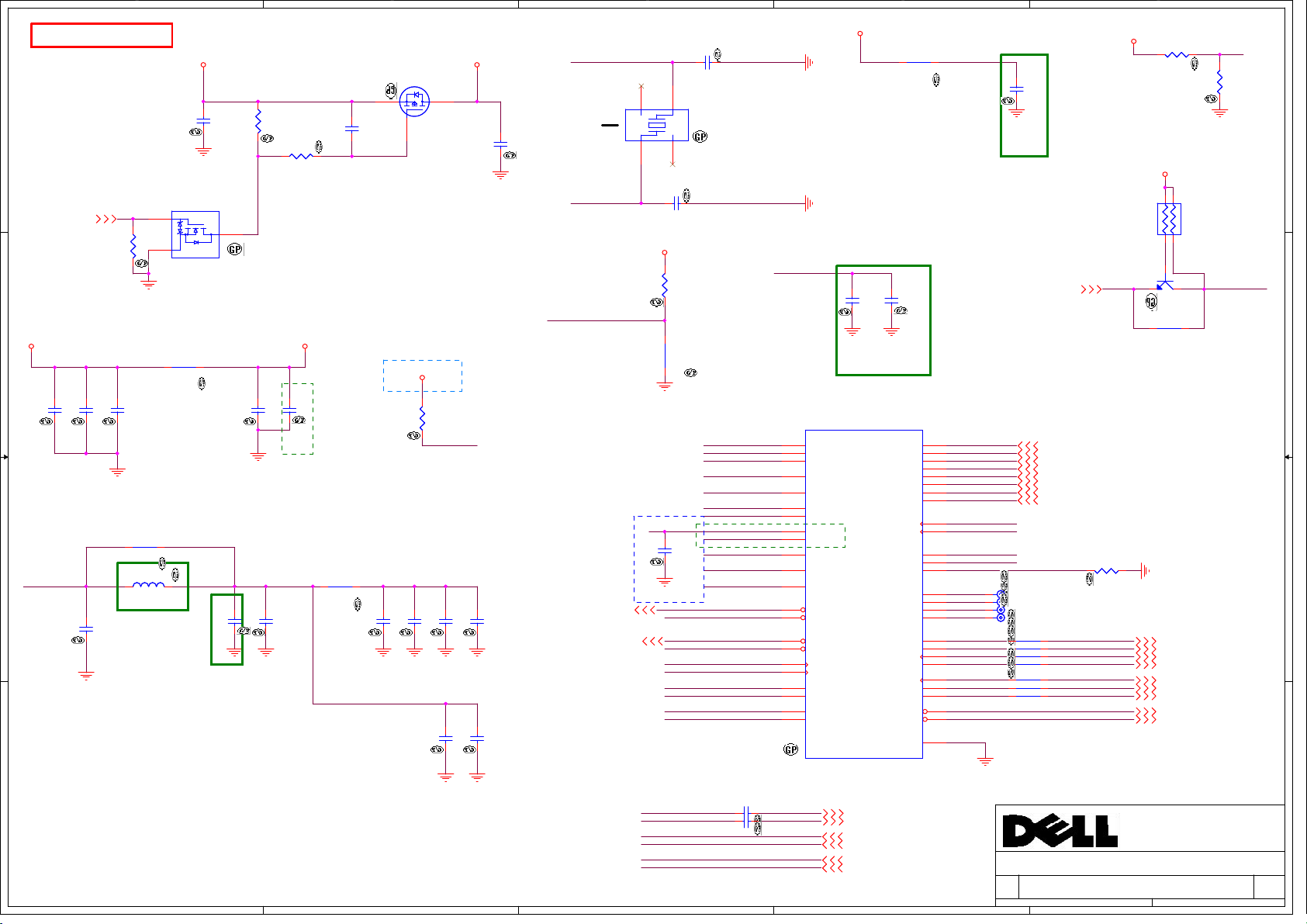

Page 2

5

4

3

2

1

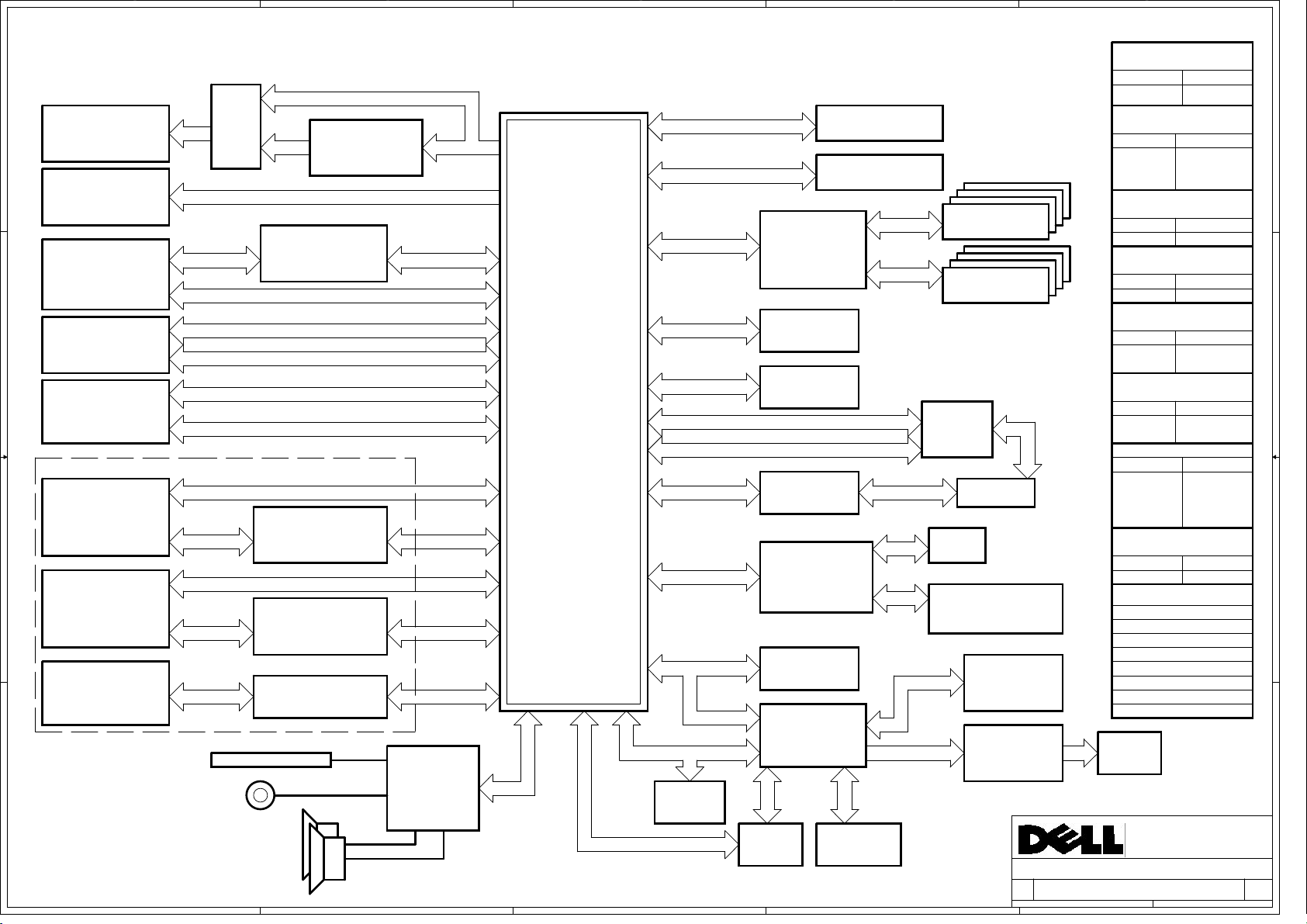

Project code : 91.47L01.001

Hadly15 Block Diagram

PCB P/N : 12311-1

Revision : A00

eDP/

D D

15.6" LCD

FHD(1920 x 1080)

52

LVDS

Option

circuit

52, 53

HDMI CONN

54

USB 2.0

USB 3.0 / Power share

34

C C

USB 3.0 CONN

34

Mini-Card

802.11a/b/g/n

BT

58

Daughter board

USB 3.0 CONN

USB 3.0

B B

USB 3.0 CONN

USB 3.0

mSATA

SATA3

Internal Digital M IC

A A

Universal jack

29

2CH SPEAKER

5

eDP

eDP to LVDS

LVDS

Converter

Realtek

RTD2136R

USB PowerShare

PERICOM

PI5USB1457AZAE

PCI-E

USB 2.0

USB3.0 Redriver

TI

SN65LVPE502RGER

USB3.0 Redriver

TI

SN65LVPE502RGER

SATA repeater

TI

SN75LVCP601

52

29

53

35

Audio Codec

Realtek

ALC3223

4

TMDS

USB 2.0

USB 3.0

USB 2.0

USB 3.0

USB 2.0

USB 3.0

USB 2.0

USB 3.0

SATA3

eDP

DDR3L

1600MHz

DDR3L

1600MHz

Slot A

Slot B

12

13

Intel CPU

Haswell ULT

DDR3L Channel A

DDR3L Channel B

15W/25W

VRAM(GDDR5)

128M x 16 x4(1GB)

VRAM(GDDR5)

128M x 16 x 4(1GB)

FFS

ST

DE351DL

RJ45

67

HDD

31

INT2

56

MMI Card Connector

(SD/SDHC/SDXC/

SD-UHS/MS/MS-Pro)

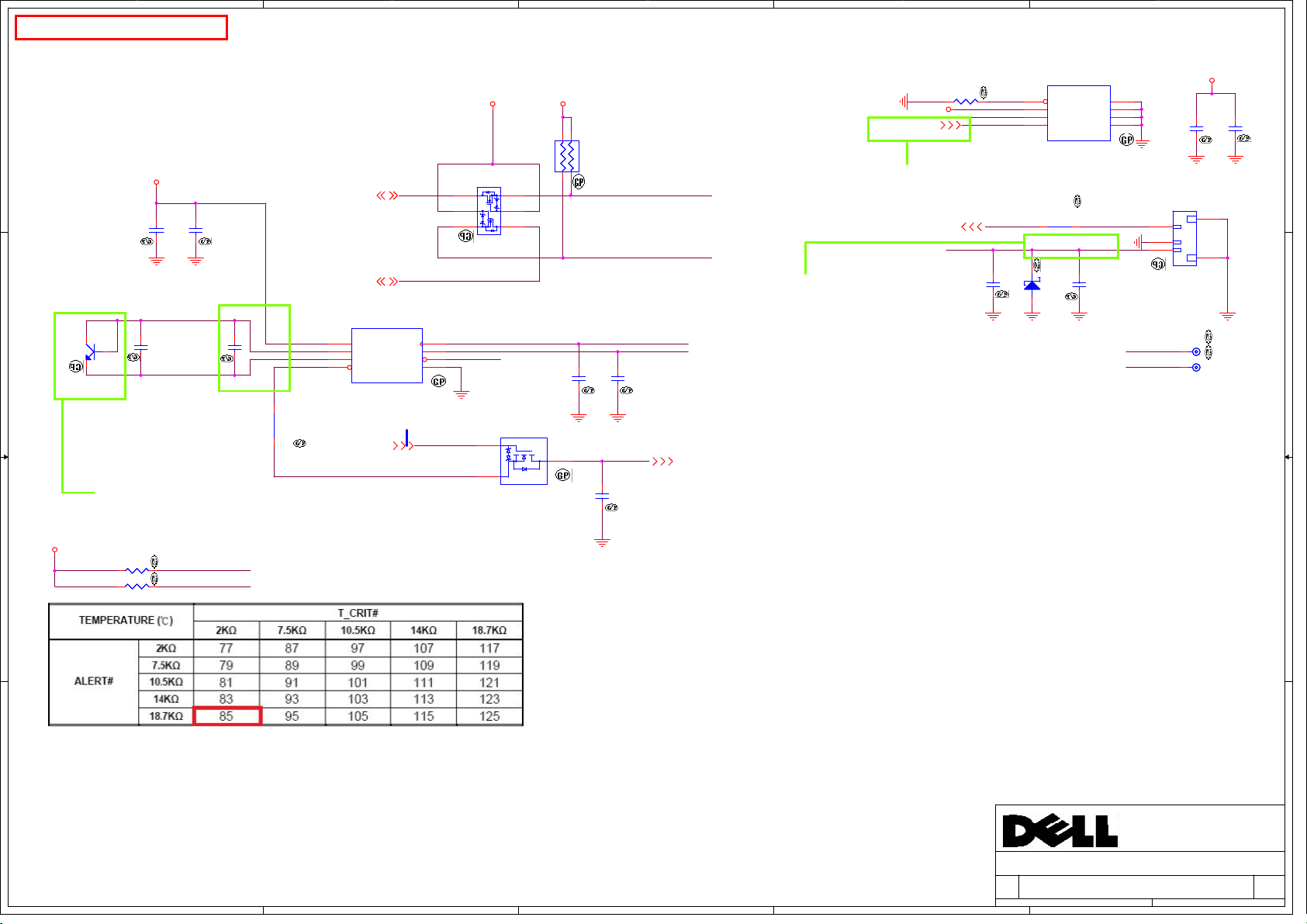

Thermal

Nuvoton

NCT7718W

33

26

Lynx Point-LP

8 USB 2.0/1.1 ports

2-4 USB 3.0 ports

High Definition Audio

4 SATA ports

8-12 PCIE ports

LPC I/F

ACPI 4.0a

PCI-E x4

USB 2.0

USB 2.0

SMBUS

INT1

SATA3

PCI-E

LPC

GPU

25W

N14P-GT

73~77

Touch Screen

52

2M 720P

Camera

52

SATA repeater

TI

SN75LVCP601

LAN+Card reader

(10/100/1000M)

Realtek

RTL8411B

LPC debug port

65

GDDR5 Ch A

GDDR5 Ch B

SATA3

30

SMBus

KBC

Nuvoton

SPI

HDA

27

SMBus

Flash ROM

3

8MB

25

NPCE985PA0DX

PS2

Touch

Pad

62

24

Backlight

Int. KB

62

2

DC Fan Contrroller

ANPEC

APL5606AKI

26

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

DC Fan

Module

Block Diagram

Block Diagram

Block Diagram

Hadley 15"

Hadley 15"

Hadley 15"

CHARGER

BQ24717

AD+

BT+ DCBATOUT

OUTPUTSINPUTS

SYSTEM DC/DC

TPS51225

INPUTS OUTPUTS

DCBATOUT

INPUTS OUTPUTS

DCBATOUT

5V_AUX_S5

3D3V_AUX_S5

5V_CHARGER

3D3V_PWR

CPU DC/DC

TPS51622

VCC_CORE

46~47

SYSTEM DC/DC

TPS51363

OUTPUTSINPUTS

DCBATOUT

1D05V_S0

SYSTEM DC/DC

TPS51216

INPUTS

DCBATOUT

OUTPUTS

1D35V_S3

0D675V_S0

SYSTEM DC/DC

NCP81172

INPUTS

DCBATOUT

5V_S5

3D3V_S5

3D3V_S0

1D05V_S0

1D35V_S3 1D35V_VGA_S0

OUTPUTS

VGA_CORE

Switches

OUTPUTSINPUTS

5V_S0

3D3V_S0

3D3V_VGA_S0

1D05V_VGA_S0

36, 83

LDO

TLV70215DBVR

3D3V_S5

OUTPUTSINPUTS

PCB LAYER

L1 : TOP

L2 : GND

L3 : Signal

L4 : Signal

L5 : VCC

L6 : Signal

L7 : GND

L8 : Bottom

26

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

2 101Friday, June 28, 2013

2 101Friday, June 28, 2013

2 101Friday, June 28, 2013

1

44

45

48

49

82

51

X02

X02

X02

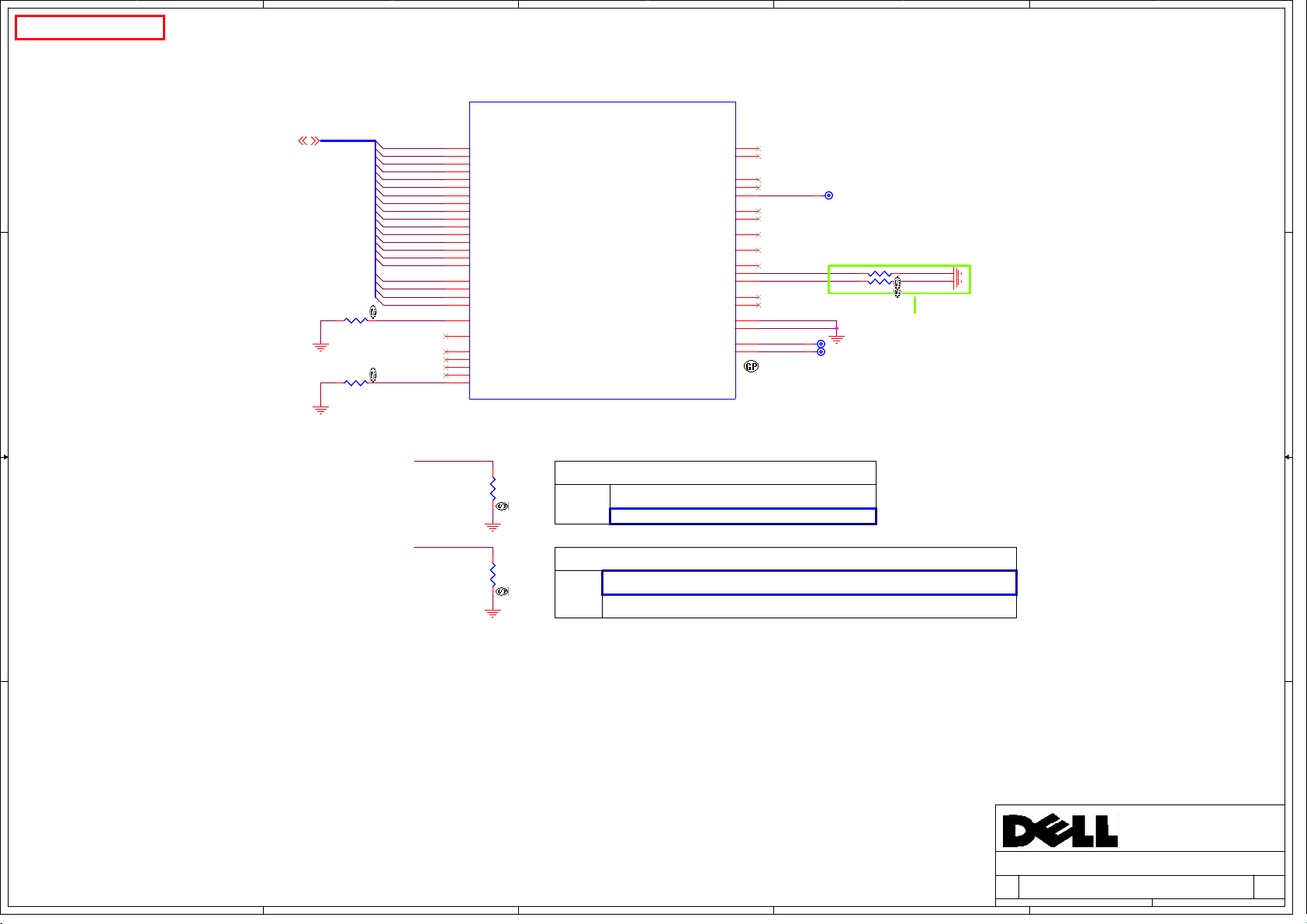

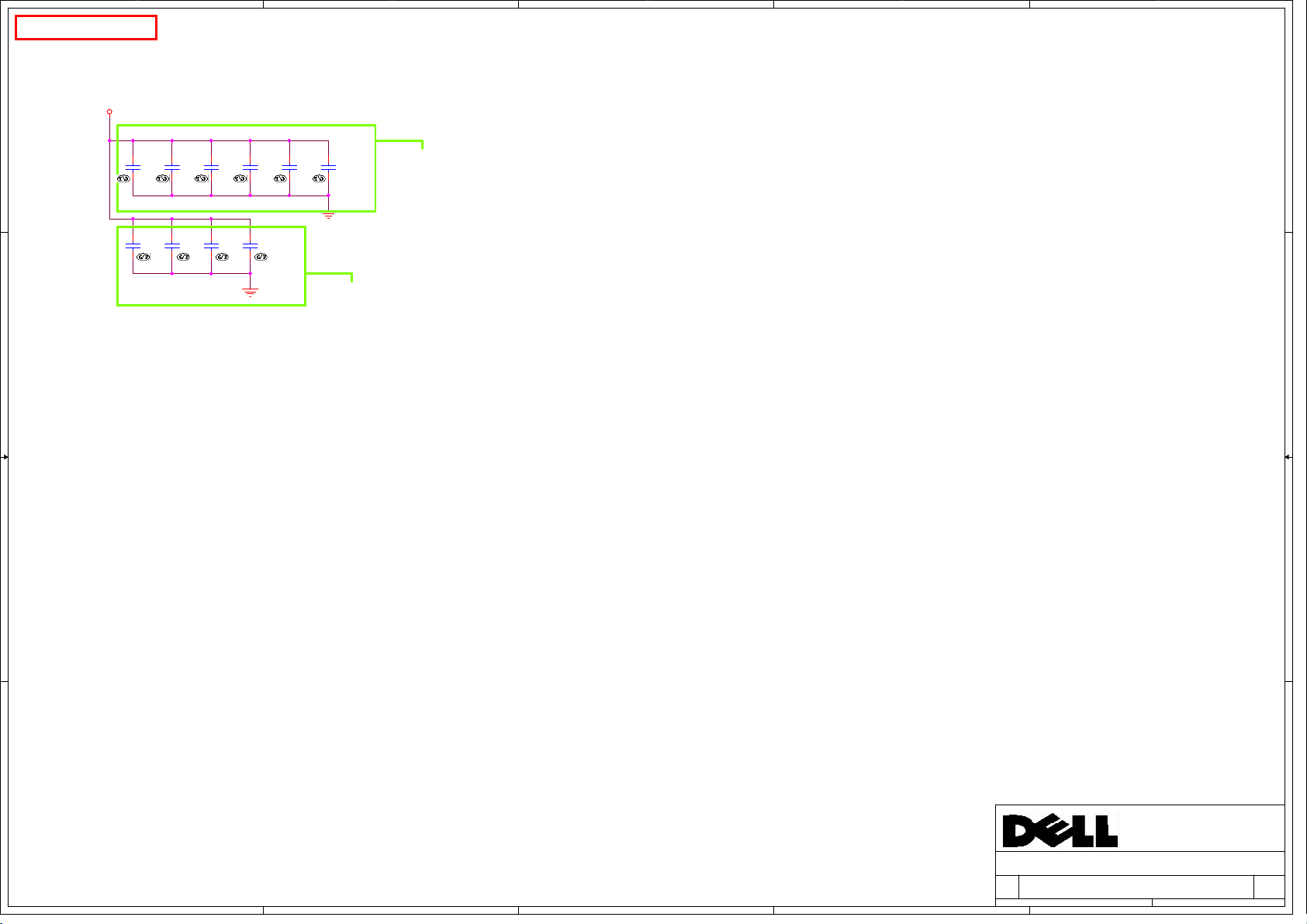

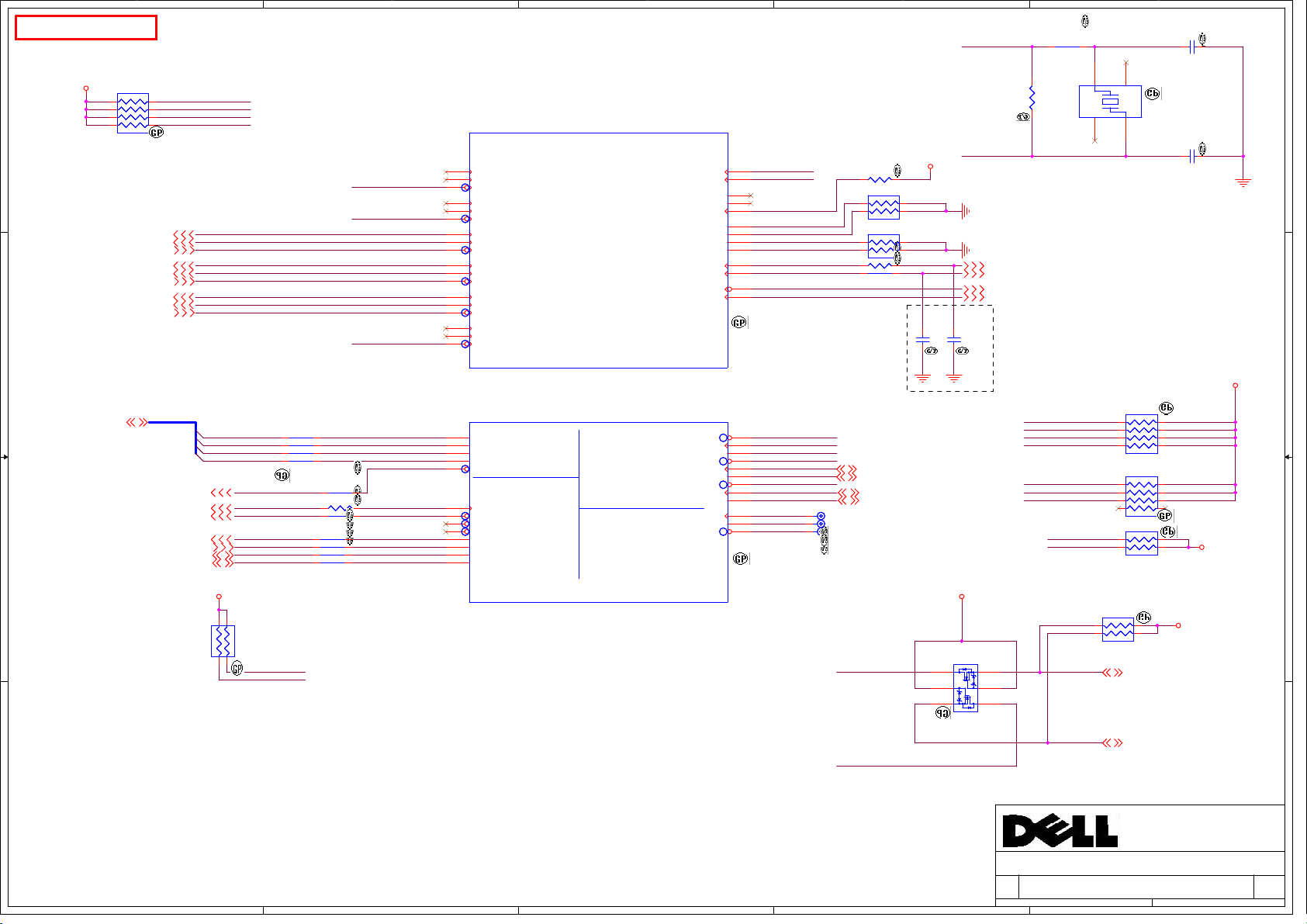

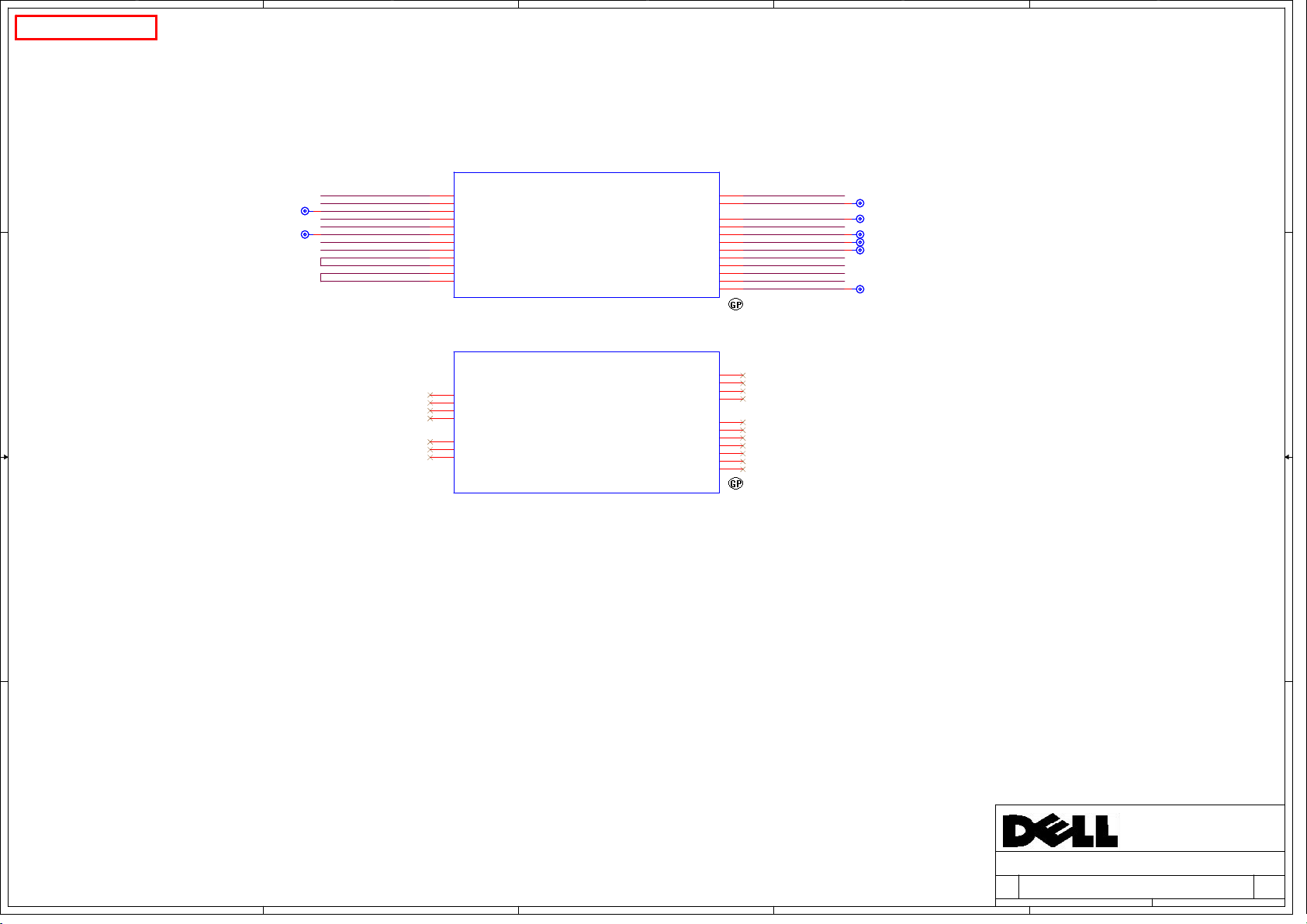

Page 3

5

D D

C C

4

3

2

1

(Blanking)

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

Title

Title

Title

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

Date: Sheet

(Reserved)

(Reserved)

(Reserved)

Hadley 15"

Hadley 15"

Hadley 15"

Taipei Hsien 221, Taiwan , R.O.C.

3 101Friday, June 28, 2 013

of

3 101Friday, June 28, 2 013

of

3 101Friday, June 28, 2 013

1

X02

X02

X02

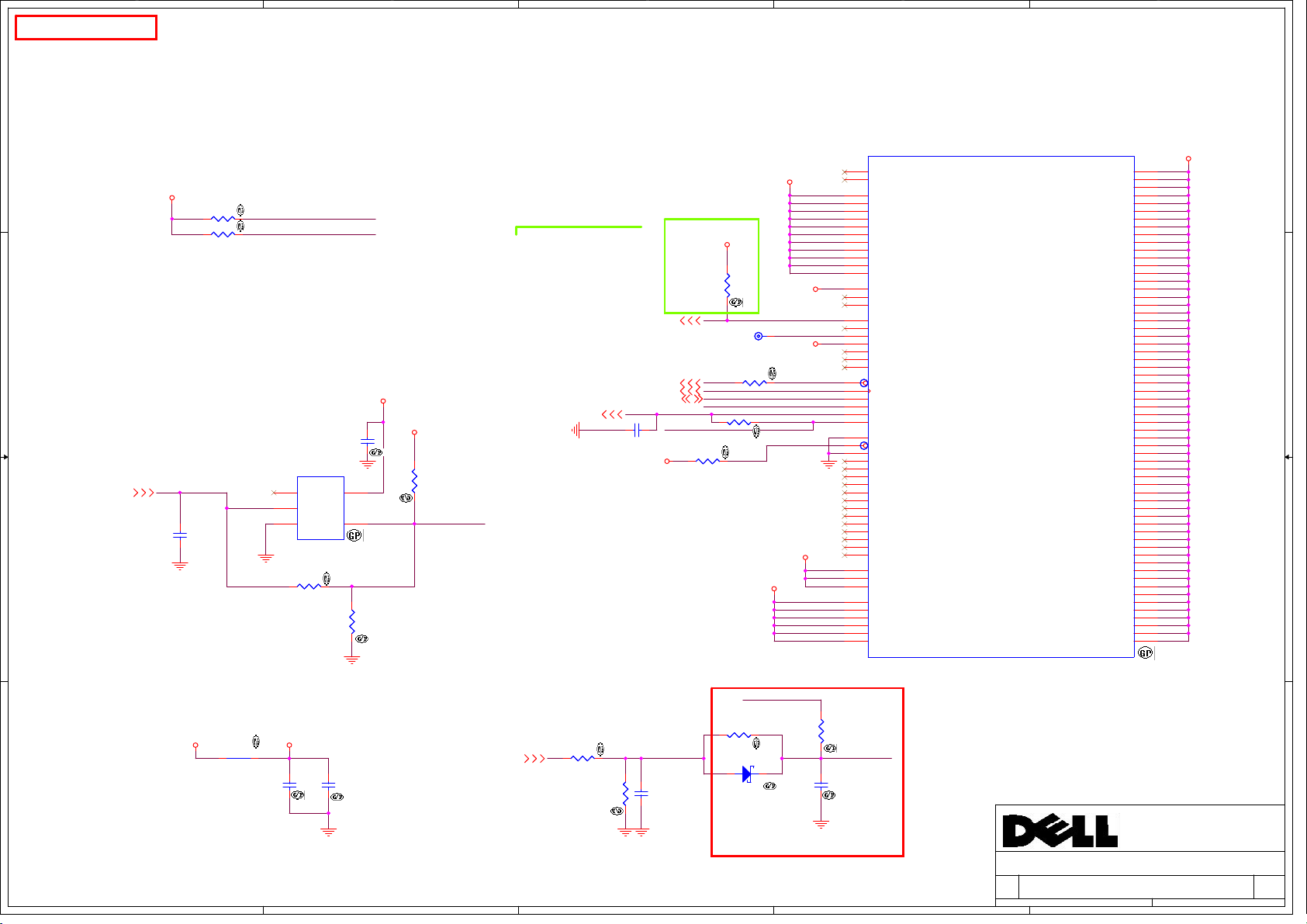

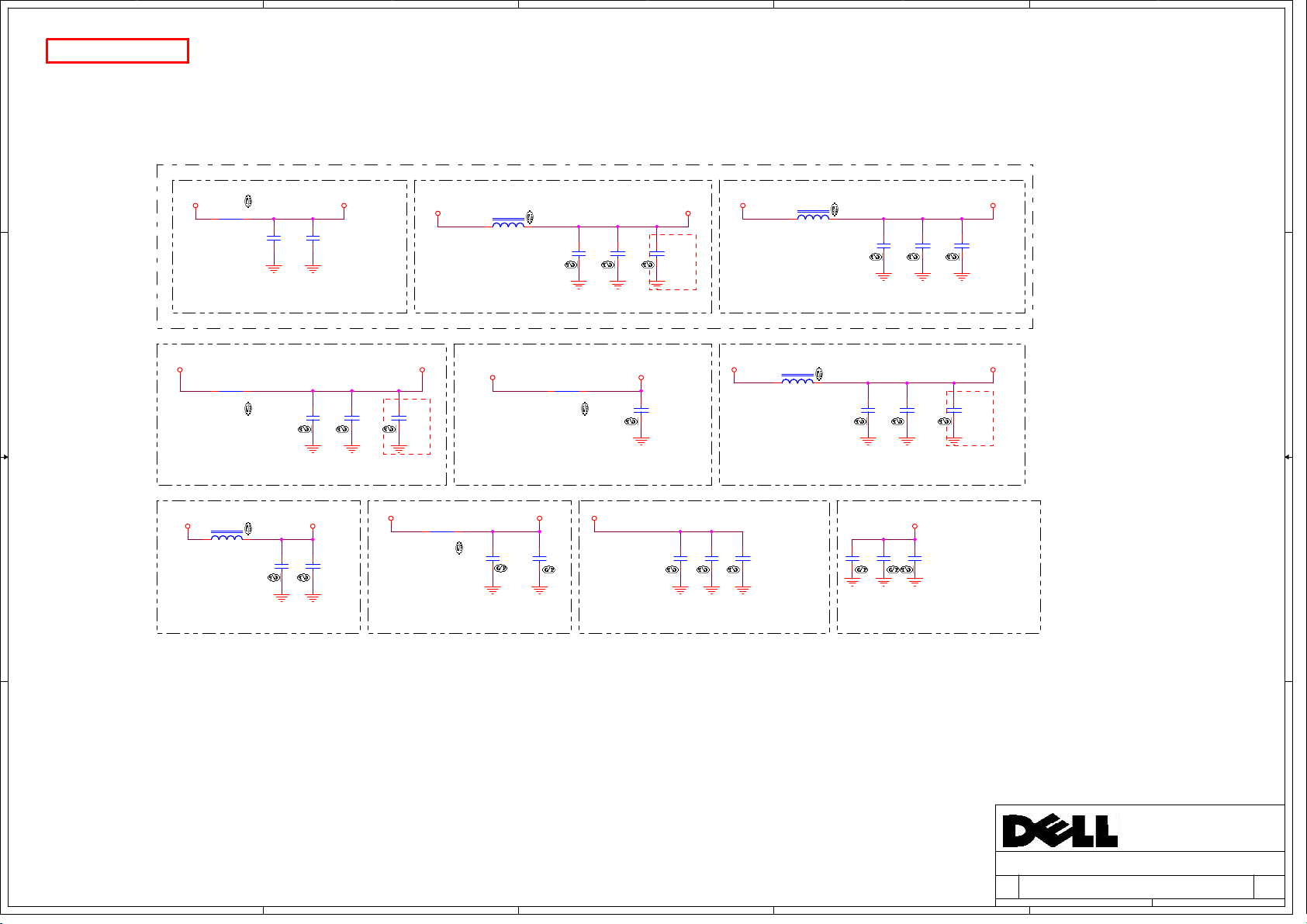

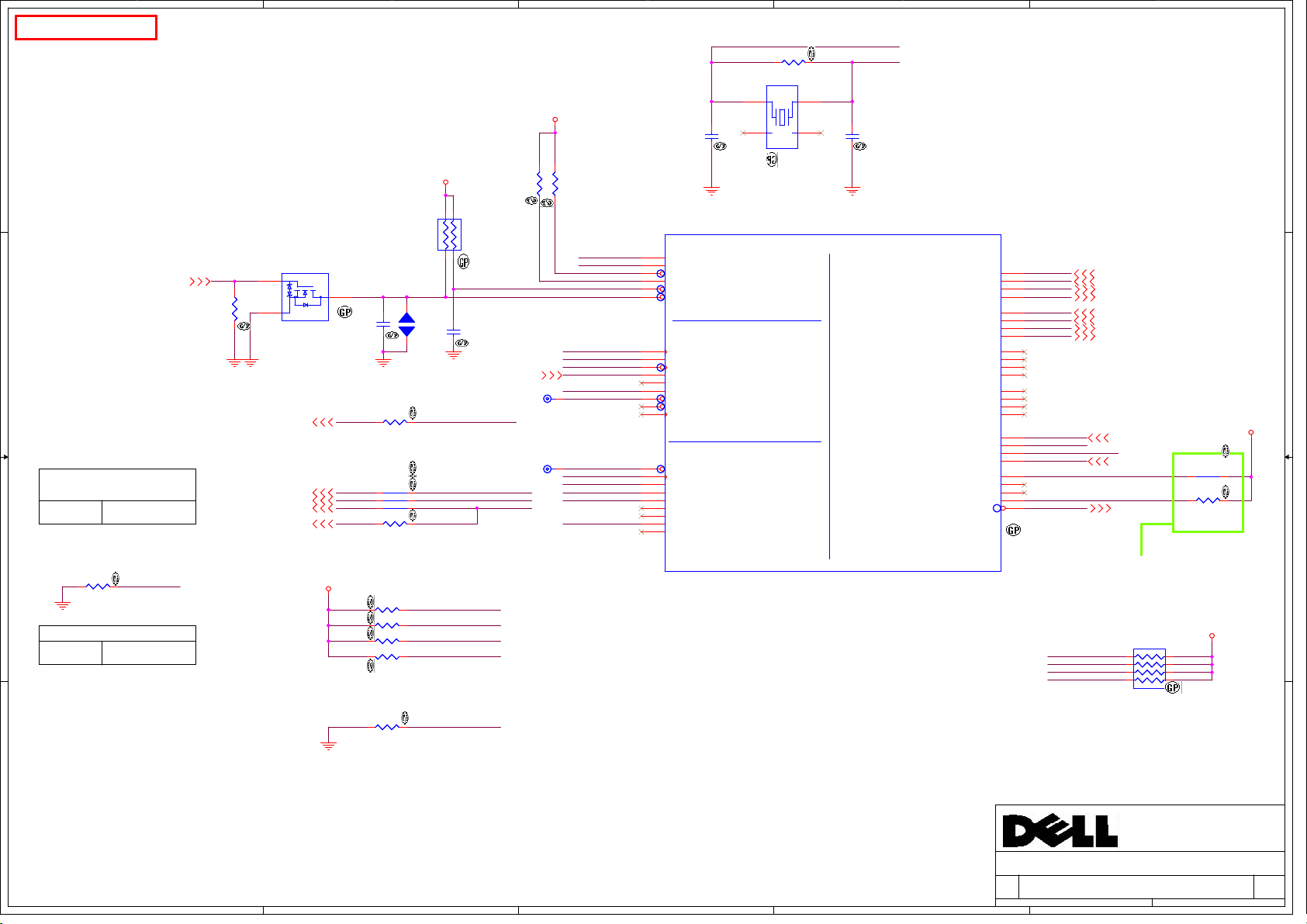

Page 4

5

4

3

2

1

SSID = CPU

D D

1D05S_ VCCST

12

R401

R401

62R2J-G P

62R2J-G P

H_PROC HOT#[24,42,44 ,46]

C C

R407 200R2F -L-GPR407 200R2F -L-GP

1 2

R408 120R2F -GPR40 8 120R2F -GP

1 2

R409 100R2F -L1-GP-UR409 100R2F -L1-GP-U

1 2

Layout Note:

Design Gui deline:

SM_RCOMP k eep routi ng length less tha n 500 mil s.

Layout Note:

Impedance control:5 0 ohm

SM_RCO MP_0

SM_RCO MP_1

SM_RCO MP_2

TP401TP401

TP402TP402

H_PECI[24]

1 2

TP403TP403

DDR_PG _CTRL[12]

R403

R403

56R2J-4 -GP

56R2J-4 -GP

SKTOCC #

1

H_CATE RR#

1

H_PROC HOT#_R

H_CPUP WRGD

1

R405

R405

12

10KR2J -3-GP

10KR2J -3-GP

SM_RCO MP_0

SM_RCO MP_1

SM_RCO MP_2

SM_DRA MRST#

DDR_PG _CTRL

B B

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

CPU1B

CPU1B

PROC_DETECT#

CATERR#

PECI

PROCHOT#

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST#

SM_PG_CNTL1

HASW ELL-6-GP

HASW ELL-6-GP

SM_DRA MRST#

MISC

MISC

THERMAL

THERMAL

PWR

PWR

DDR3L

DDR3L

HSW_ULT_DDR3L

HSW_ULT_DDR3L

1D35V_ S3

12

R410

R410

470R2J -2-GP

470R2J -2-GP

R404

R404

1 2

0R0402 -PAD-2-GP

0R0402 -PAD-2-GP

JTAG

JTAG

2 OF 19

2 OF 19

XDP_PR DY#

J62

PRDY#

PREQ#

PROC_TCK

PROC_TMS

PROC_TRST#

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

Layout Note:

Place close to DIMM

XDP_PR EQ#

K62

XDP_TC LK

E60

XDP_TM S

E61

XDP_TR ST#

E59

XDP_TD I

F63

XDP_TD O

F62

XDP_BP M0

J60

XDP_BP M1

H60

XDP_BP M2

H61

XDP_BP M3

H62

XDP_BP M4

K59

XDP_BP M5

H63

XDP_BP M6

K60

XDP_BP M7

J61

DDR3_D RAMRST# [12,13]

XDP_PR DY# [96]

XDP_PR EQ# [96]

XDP_BP M[7:0]

XDP_BP M[7:0] [96 ]

XDP_TD O

XDP_TD I

XDP_TM S

R402 51R2J-2 -GP

R402 51R2J-2 -GP

XDP_TR ST#

XDP_TC LK

R406 51R2J-2 -GPR406 51R2J-2 -GP

RN401

RN401

1

2

3

XDP

XDP

4 5

SRN51J -1-GP

SRN51J -1-GP

XDP

XDP

1 2

1 2

1D05S_ VCCST

8

7

6

X01 change to short pad

<Core Design>

<Core Design>

A A

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

Title

Title

Title

CPU (THERMAL/CLOCK)

CPU (THERMAL/CLOCK)

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

Date: Sheet of

Date: Sheet

Date: Sheet

CPU (THERMAL/CLOCK)

A3

A3

A3

Taipei Hsien 221, Taiwan , R.O.C.

Hadley 15"

Hadley 15"

Hadley 15"

4 101Friday, June 28, 2 013

of

4 101Friday, June 28, 2 013

of

4 101Friday, June 28, 2 013

X02

X02

X02

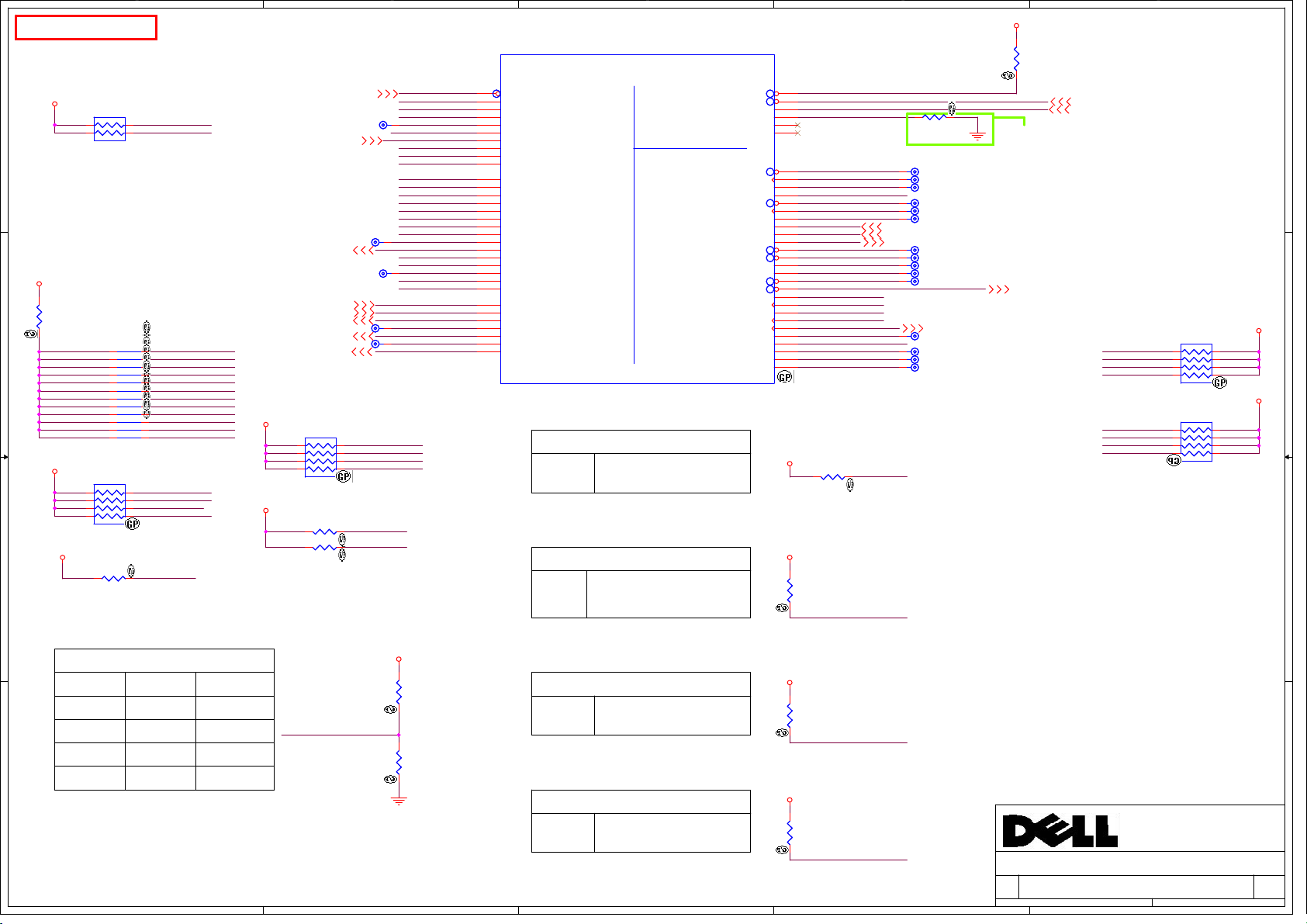

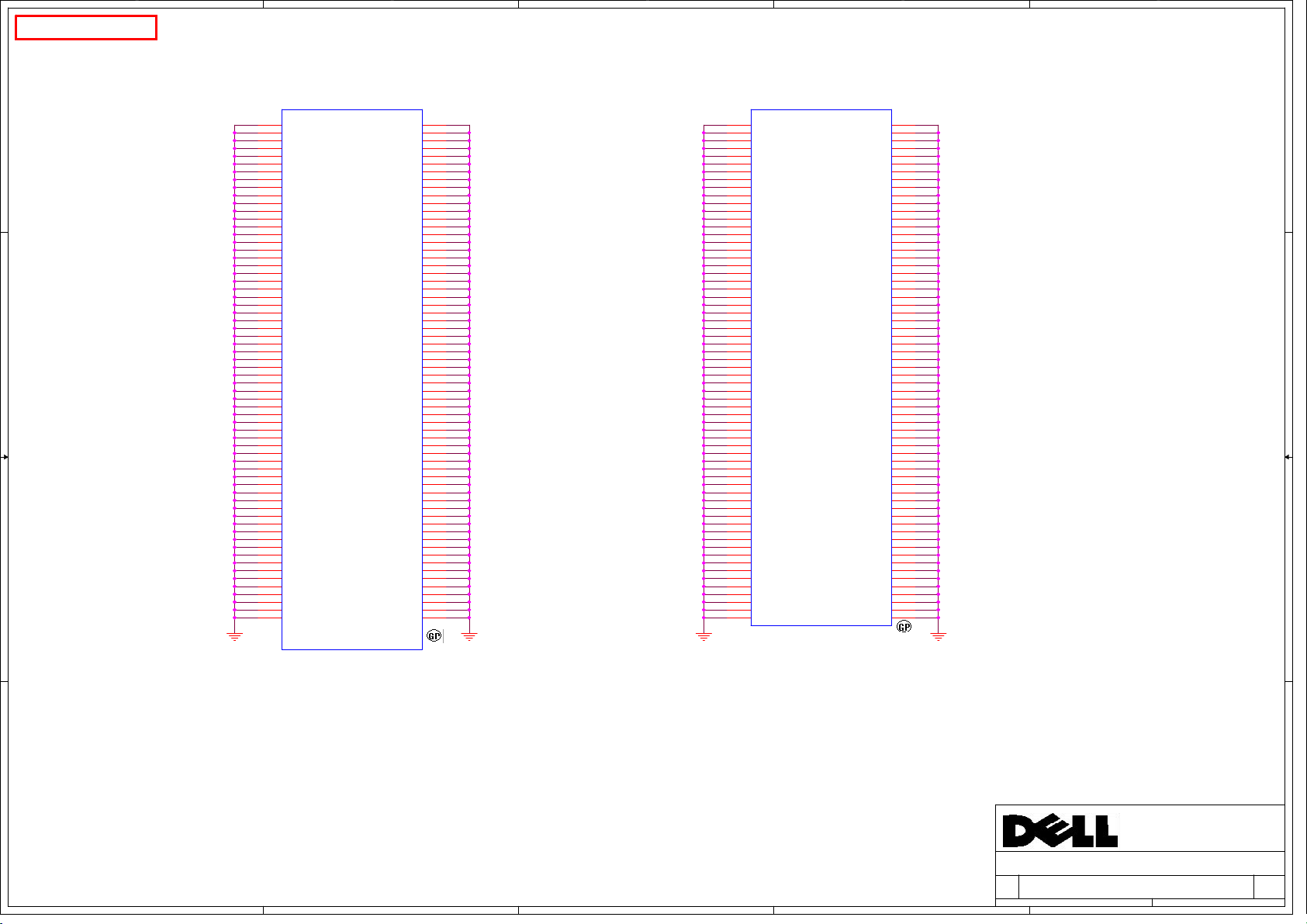

Page 5

5

4

3

2

1

SSID = CPU

HSW_ULT_DDR3L

CPU1C

M_A_DQ[63:0][12]

D D

C C

M_A_DQ[63:0]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56 M_A_DQS7

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

CPU1C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

HSW_ULT_DDR3L

DDR CHANNEL A

DDR CHANNEL A

3 OF 19

3 OF 19

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS#

SA_WE#

SA_CAS#

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

+V_SM_VREF_CNT

M_A_DIMA_CLK_DDR#0 [12]

M_A_DIMA_CLK_DDR0 [12]

M_A_DIMA_CLK_DDR#1 [12]

M_A_DIMA_CLK_DDR1 [12]

M_A_DIMA_CKE0 [12]

M_A_DIMA_CKE1 [12]

M_A_DIMA_CS#0 [12]

M_A_DIMA_CS#1 [12]

TP_M_A_DIMA_ODT0

M_A_RAS# [12]

M_A_WE# [12]

M_A_CAS# [12]

M_A_BS0 [12]

M_A_BS1 [12]

M_A_BS2 [12]

M_A_A[15:0] [12]

M_A_DQS#[7:0] [12]

M_A_DQS[7:0] [12]

+V_SM_VREF_CNT [37]

DDR_WR_VREF01 [12]

DDR_WR_VREF02 [13]

CPU1D

CPU1D

M_B_DQ[63:0][13]

TP501TP501

1

M_B_DQ[63:0]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HSW_ULT_DDR3L

HSW_ULT_DDR3L

DDR CHANNEL B

DDR CHANNEL B

4 OF 19

4 OF 19

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS#

SB_WE#

SB_CAS#

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

TP_M_B_DIMB_ODT0

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DIMB_CLK_DDR#0 [13]

M_B_DIMB_CLK_DDR0 [13]

M_B_DIMB_CLK_DDR#1 [13]

M_B_DIMB_CLK_DDR1 [13]

M_B_DIMB_CKE0 [13]

M_B_DIMB_CKE1 [13]

M_B_DIMB_CS#0 [13]

M_B_DIMB_CS#1 [13]

M_B_RAS# [13]

M_B_WE# [13]

M_B_CAS# [13]

M_B_BS0 [13]

M_B_BS1 [13]

M_B_BS2 [13]

M_B_A[15:0] [13]

M_B_DQS#[7:0] [13]

M_B_DQS[7:0] [13]

TP503TP503

1

B B

HASWELL-6-GP

HASWELL-6-GP

HASWELL-6-GP

A A

5

4

3

HASWELL-6-GP

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

CPU (DDR)

CPU (DDR)

CPU (DDR)

Hadley 15"

Hadley 15"

Hadley 15"

1

X02

X02

5 101Friday, June 28, 2013

5 101Friday, June 28, 2013

5 101Friday, June 28, 2013

X02

Page 6

5

4

3

2

1

SSID = CPU

HSW_ULT_DDR3L

CPU1S

CPU1S

D D

CFG[19:0 ][96]

C C

CFG[19:0 ]

1 2

R601

R601

49D9R2 F-GP

49D9R2 F-GP

1 2

R603

R603

8K2R2F -1-GP

8K2R2F -1-GP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RC OMP

TD_IREF

AC60

AC62

AC63

AA63

AA60

Y62

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

AA62

U63

AA61

U62

V63

H18

B12

A5

E1

D1

J20

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD#A5

RSVD#E1

RSVD#D1

RSVD#J20

RSVD#H18

TD_IREF

HSW_ULT_DDR3L

RESERVED

RESERVED

19 OF 19

19 OF 19

RSVD_TP#AV63

RSVD_TP#AU63

RSVD_TP#C63

RSVD_TP#C62

RSVD#B43

RSVD_TP#A51

RSVD_TP#B51

RSVD_TP#L60

RSVD#N60

RSVD#W23

RSVD#Y22

PROC_OPI_RCOMP

RSVD#AV62

RSVD#D58

VSS

VSS

RSVD#P20

RSVD#R20

AV63

AU63

C63

C62

EDP_SP ARE

B43

A51

B51

L60

N60

W23

PROC_O PI_COMP3

Y22

PROC_O PI_COMP

AY15

AV62

D58

P22

N21

HVM_CL K#

P20

HVM_CL K

R20

1

TP605TP605

R606 49D9R2 F-GP

R606 49D9R2 F-GP

1 2

DY

DY

R602 49D9R2 F-GPR602 49D9R2 F-GP

1 2

1

TP619TP619

1

TP620TP620

Layout Note:

1.Referenced "continuous " VSS plane only.

2.Avoid routing next to clock pins or noisy

signals.

3.Trace width: 12~15mil

4.Isolation Spacing: 12m il

5.Max length: 500mil

CFG3

DY

DY

12

R604

R604

1KR2J-1 -GP

1KR2J-1 -GP

PHYSICAL_D EBUG_ENAB LED (DFX PRIVACY)

0 : ENABL ED

CFG[3]

SET DFX EN ABLED BIT IN DEBU G INTERFA CE MSR

1 : DISABL ED

CFG4

B B

A A

5

4

12

R605

R605

1KR2J-1 -GP

1KR2J-1 -GP

DISPLAY PO RT PRESEN CE STRAP

0 : ENABL ED

AN EXTERNA L DISPLAY PORT DEV ICE IS CO NNECTED T O THE EMBE DDED DISP LAY PORT

CFG[4]

1 : DISABL ED

NO PHYSICA L DISPLAY PORT ATT ACHED TO EMBEDDED DISPLAY PO RT

3

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

Title

Title

Title

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

2

Date: Sheet

Taipei Hsien 221, Taiwan , R.O.C.

CPU (RESERVED)

CPU (RESERVED)

CPU (RESERVED)

Hadley 15"

Hadley 15"

Hadley 15"

6 101Friday, June 28, 2 013

6 101Friday, June 28, 2 013

6 101Friday, June 28, 2 013

1

X02

X02

of

of

X02

Page 7

5

4

3

2

1

SSID = CPU

D D

HSW_ULT_DDR3L

CPU1L

CPU1L

L59

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

AC58

AB23

AD23

AA23

AE59

AD60

AD59

AA59

AE60

AC59

AG58

AC22

AE22

AE23

AB57

AD57

AG57

F59

N58

E63

A59

E20

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

U59

V59

C24

C28

C32

J58

RSVD#L59

RSVD#J58

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD#N58

RSVD#AC58

VCC_SENSE

RSVD#AB23

VCCIO_OUT

VCCIOA_OUT

RSVD#AD23

RSVD#AA23

RSVD#AE59

VIDALERT#

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG#

VSS

RSVD_TP#P60

RSVD_TP#P61

RSVD_TP#N59

RSVD_TP#N61

RSVD#T59

RSVD#AD60

RSVD#AD59

RSVD#AA59

RSVD#AE60

RSVD#AC59

RSVD#AG58

RSVD#U59

RSVD#V59

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

HASW ELL-6-GP

HASW ELL-6-GP

1D35V_ S3

1D05S_ VCCST

R703 75R2F-2 -GPR703 75R2F-2 -GP

1 2

R704 130R2F -1-GPR704 130R2F -1-GP

1 2

C C

1D05V_ VTT_PWR GD[36,48]

EC701

EC701

SCD1U25V2KX-GP

SCD1U25V2KX-GP

12

DY

DY

B B

VR_SVID_ ALERT#

H_CPU_ SVIDDAT

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

U701

U701

1

NC#1

2

A

DY

DY

GND3Y

74LVC1 G07GW-GP

74LVC1 G07GW-GP

73.01G07.0HG

73.01G07.0HG

1 2

R707

R707

100KR2 F-L1-GP

100KR2 F-L1-GP

VCC

C702

C702

5

4

12

3D3V_S 5

12

DY

DY

R709

R709

51KR2J -1-GP

51KR2J -1-GP

1D05S_ VCCST

12

R706

R706

10KR2J -3-GP

10KR2J -3-GP

DY

DY

H_VCCS T_PWRGD

Layout Note:

1. Place close to CPU

2. VCC_SENSE/ VSS_SENSE

impedance=50 ohm

3. Lwngth match<25mil

VR_SVID_ ALERT#[46]

H_CPU_ SVIDCLK[46]

H_VR_E NABLE[46]

H_CPU_ SVIDDAT[46]

C705

C705

SCD1U2 5V2KX-GP

SCD1U2 5V2KX-GP

1D05S_ VCCST

100R2F -L1-GP-U

100R2F -L1-GP-U

VCC_SE NSE[46]

IMVP_PW RGD_R

1 2

DY

DY

R705 150R2J -L1-GP-UR705 150R2J -L1-GP-U

1 2

VCC_CO RE

R702

R702

1 2

12

TP701TP701

R701

R701

43R2J-G P

43R2J-G P

1 2

DY

DY

VCC_CO RE

TP_VCC IO_OUT

1

+VCCIOA_ OUT

H_CPU_ SVIDALRT#

H_CPU_ SVIDCLK

H_CPU_ SVIDDAT

H_VCCS T_PWRGD

10KR2J -3-GP

10KR2J -3-GP

R710

R710

PWR _DEBUG

1D05S_ VCCST

VCC_CO RE

HSW_ULT_DDR3L

HSW ULT POWER

HSW ULT POWER

12 OF 19

12 OF 19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

A00 0619

H_VR_E NABLE

PR714

PR714

1D05S_ VCCST1D05V_ S0

1 2

R711

R711

0R0805 -PAD-2-GP-U

0R0805 -PAD-2-GP-U

A A

5

DY

DY

12

12

C701

C701

C703

C703

DY

DY

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

4

IMVP_PW RGD[24,46]

1 2

R713

R713

100KR2 F-L1-GP

100KR2 F-L1-GP

47KR2F -GP

47KR2F -GP

IMVP_PW RGD_L IMVP_PW RGD_R

C704

C704

SCD1U25V2KX-GP

SCD1U25V2KX-GP

12

12

R712

R712

DY

DY

3

1 2

0R2J-2-G P

0R2J-2-G P

PD701

PD701

DY

DY

BAT54L PS-7-GP

BAT54L PS-7-GP

KA

12

PR715

PR715

DY

DY

10KR2F -2-GP

10KR2F -2-GP

12

PC706

PC706

DY

DY

SCD047 U10V2KX-2GP

SCD047 U10V2KX-2GP

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

CPU (VCC_CORE)

CPU (VCC_CORE)

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

2

Date: Sheet

CPU (VCC_CORE)

Hadley 15"

Hadley 15"

Hadley 15"

VCC_CO RE

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

7 101Friday, June 28, 2 013

of

7 101Friday, June 28, 2 013

of

7 101Friday, June 28, 2 013

1

X02

X02

X02

Page 8

5

4

3

2

1

SSID = CPU

D D

HSW_ULT_DDR3L

X01 remove

CPU1A

CPU1A

HSW_ULT_DDR3L

1 OF 19

1 OF 19

HDMI_DAT A2#[54]

HDMI_DAT A2[54]

HDMI

HDMI_DAT A1#[54]

HDMI_DAT A1[54]

HDMI_DAT A0#[54]

HDMI_DAT A0[54]

HDMI_CLK #[54]

HDMI_CLK[54]

C C

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

HASW ELL-6-GP

HASW ELL-6-GP

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

EDPDDI

EDPDDI

EDP_RCOMP

EDP_DISP_UTIL

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

EDP_TX 0_DN [53]

EDP_TX 0_DP [5 3]

EDP_TX 1_DN [53]

EDP_TX 1_DP [5 3]

EDP_AU X_DN [5 3]

EDP_AU X_DP [53]

EDP_CO MP

EDP_BR IGHTNESS

R801

R801

24D9R2 F-L-GP

24D9R2 F-L-GP

1

TP801TP801

+VCCIOA_ OUT

Design Gui deline:

12

EDP_COMP k eep routi ng length max 100 mils.

Trace Widt h:20 mils .

B B

<Core Design>

<Core Design>

A A

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

Title

Title

Title

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan , R.O.C.

CPU (DDI/EDP)

CPU (DDI/EDP)

CPU (DDI/EDP)

Hadley 15"

Hadley 15"

Hadley 15"

8 101Friday, June 28, 2 013

8 101Friday, June 28, 2 013

8 101Friday, June 28, 2 013

of

of

X02

X02

X02

Page 9

5

4

3

2

1

SSID = CPU

D D

HSW_ULT_DDR3L

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

HSW_ULT_DDR3L

CPU1P

CPU1P

D33

D34

D35

D37

D38

D39

D41

D42

D43

D45

D46

D47

D49

D5

D50

D51

D53

D54

D55

D57

C C

B B

D59

D62

D8

E11

E17

F20

F26

F30

F34

F38

F42

F46

F50

F54

F58

F61

G18

G22

G3

G5

G6

G8

H13

HASW ELL-6-GP

HASW ELL-6-GP

16 OF 19

16 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_SENSE

VSS

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

VSS_SE NSE

VSS_SE NSE [46]

12

R901

R901

100R2F-L1-GP-U

100R2F-L1-GP-U

Layout Note:

1. Place close to CPU

2. VCC_SENSE/ VSS_SENSE

impedance=50 ohm

3. Lwngth match<25mil

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

Title

Title

Title

CPU (VSS)

CPU (VSS)

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

Date: Sheet

CPU (VSS)

Taipei Hsien 221, Taiwan , R.O.C.

Hadley 15"

Hadley 15"

Hadley 15"

9 101Friday, June 28, 2 013

of

9 101Friday, June 28, 2 013

of

9 101Friday, June 28, 2 013

1

X02

X02

X02

Page 10

5

4

3

2

1

SSID = CPU

1D35V_ S3

D D

C1005

SC10U6D3V3MX-GP

C1005

C1004

C1004

C1003

SC10U6D3V3MX-GP

C1003

C1002

C1002

C1001

SC10U6D3V3MX-GP

C1001

SC10U6D3V3MX-GP

12

12

12

12

C1017

C1017

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

C C

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C1018

C1018

DY

DY

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

12

12

12

12

C1019

C1019

DY

DY

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C1020

C1020

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

C1006

SC10U6D3V3MX-GPDYC1006

SC10U6D3V3MX-GP

12

DY

Layout Note:

Direct tie to CPU VccIn/ Vss balls

Layout Note:

As close to CPU as possi ble

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

Title

Title

Title

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan , R.O.C.

CPU(Power CAP1)

CPU(Power CAP1)

CPU(Power CAP1)

Hadley 15"

Hadley 15"

Hadley 15"

10 10 1Friday, June 28, 2 013

10 10 1Friday, June 28, 2 013

10 10 1Friday, June 28, 2 013

1

of

of

of

X02

X02

X02

Page 11

5

4

3

2

1

SSID = CPU

D D

MAX: 1.92A

1.838A 41mA 42mA

1D05V_ HSIO +V1.05D X_MODPHY_PCH

1 2

R1101

R1101

0R0805 -PAD-2-GP-U

0R0805 -PAD-2-GP-U

12

C1101

SC1U6D3V2KX-GP

C1101

C1102

C1102

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

L1101 IND -2D2UH-196-GP

L1101 IND -2D2UH-196-GP

1 2

68.2R21D.10R

68.2R21D.10R

C1103

C1103

12

+V1.05S _AUSB3PLL

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C1104

SC10U6D3V3MX-GP

C1104

SC10U6D3V3MX-GP

12

+V1.05S _AUSB3PLL1D05V_ HSIO

C1123

SC10U6D3V3MX-GPDYC1123

SC10U6D3V3MX-GP

12

DY

1D05V_ HSIO +V1.05S _ASATA3PLL

L1102 IND -2D2UH-196-GP

L1102 IND -2D2UH-196-GP

1 2

68.2R21D.10R

68.2R21D.10R

C1105

SC1U6D3V2KX-GP

C1105

SC1U6D3V2KX-GP

12

+V1.05S _ASATA3PLL

C1106

SC10U6D3V3MX-GP

C1106

SC10U6D3V3MX-GP

12

C1107

12

SC10U6D3V3MX-GPDYC1107

SC10U6D3V3MX-GP

DY

CAP need close to pin K9 L10

C C

1 2

R1102

R1102

0R0603 -PAD-2-GP-U

0R0603 -PAD-2-GP-U

+V1.05S _APLLOPI

C1109

SC1U6D3V2KX-GP

C1109

SC1U6D3V2KX-GP

12

12

C1110

SC10U6D3V3MX-GP

C1110

SC10U6D3V3MX-GP

CAP need close to pin AA21 CAP need close to pin AC9 CAP need close to pin J18

CAP need close to pin B18 CAP need close to pin B11

+V1.05S _APLLOPI1D05V_ S0

C1124

SC10U6D3V3MX-GPDYC1124

SC10U6D3V3MX-GP

12

3D3V_S 5_PCH +V3.3A_ PSUS

1 2

R1103

R1103

0R0603 -PAD-2-GP-U

0R0603 -PAD-2-GP-U

1205 Add

C1108

SC10U6D3V3MX-GP

C1108

SC10U6D3V3MX-GP

12

1D05V_ S0 +V1.05S _AXCK_DCB

L1103 IND -2D2UH-196-GP

L1103 IND -2D2UH-196-GP

1 2

68.2R21D.10R

68.2R21D.10R

DY

1205 Add

200mA62mA57mA

+V1.05S _AXCK_DCB

C1112

SC10U6D3V3MX-GPDYC1112

SC10U6D3V3MX-GP

C1125

SC10U6D3V3MX-GPDYC1125

DY

SC10U6D3V3MX-GP

12

C1111

SC1U6D3V2KX-GP

C1111

SC1U6D3V2KX-GP

12

12

DY

1205 Add

31mA 658mA 1.632A 1mA

IND-2D2UH -196-GP

IND-2D2UH -196-GP

L1104

L1104

1 2

68.2R21D.10R

68.2R21D.10R

B B

+V1.05S _AXCK_LCPL L1D05V_ S0

C1113

SC1U6D3V2KX-GP

C1113

SC1U6D3V2KX-GP

C1114

12

12

DY

CAP need close to pin A20 CAP need close to pin AE9 CAP need close to pin AE8 J11

1D05V_ S0 +1.05M_ ASW 1D05V _S0

1 2

R1104

R1104

0R0603 -PAD-2-GP-U

SC10U6D3V3MX-GPDYC1114

SC10U6D3V3MX-GP

0R0603 -PAD-2-GP-U

C1115

SC22U6D3V5MX-2GPDYC1115

SC22U6D3V5MX-2GP

12

DY

RTC_AU X_S5

C1117

SC1U6D3V2KX-GP

C1117

C1116

SC1U6D3V2KX-GP

C1116

SC1U6D3V2KX-GP

12

SC1U6D3V2KX-GP

C1118

SC1U6D3V2KX-GP

C1118

SC1U6D3V2KX-GP

12

C1119

SC10U6D3V3MX-GP

C1119

SC10U6D3V3MX-GP

12

12

C1120

SCD1U10V2KX-5GPDYC1120

SCD1U10V2KX-5GP

12

C1122

SC1U6D3V2KX-GP

C1122

SC1U6D3V2KX-GP

C1121

SCD1U10V2KX-5GP

C1121

SCD1U10V2KX-5GP

12

12

DY

CAP need close to pin AG10

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

Title

Title

Title

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan , R.O.C.

CPU(Power CAP2)

CPU(Power CAP2)

CPU(Power CAP2)

Hadley 15"

Hadley 15"

Hadley 15"

11 10 1Friday, June 28, 2 013

11 10 1Friday, June 28, 2 013

11 10 1Friday, June 28, 2 013

1

of

of

X02

X02

X02

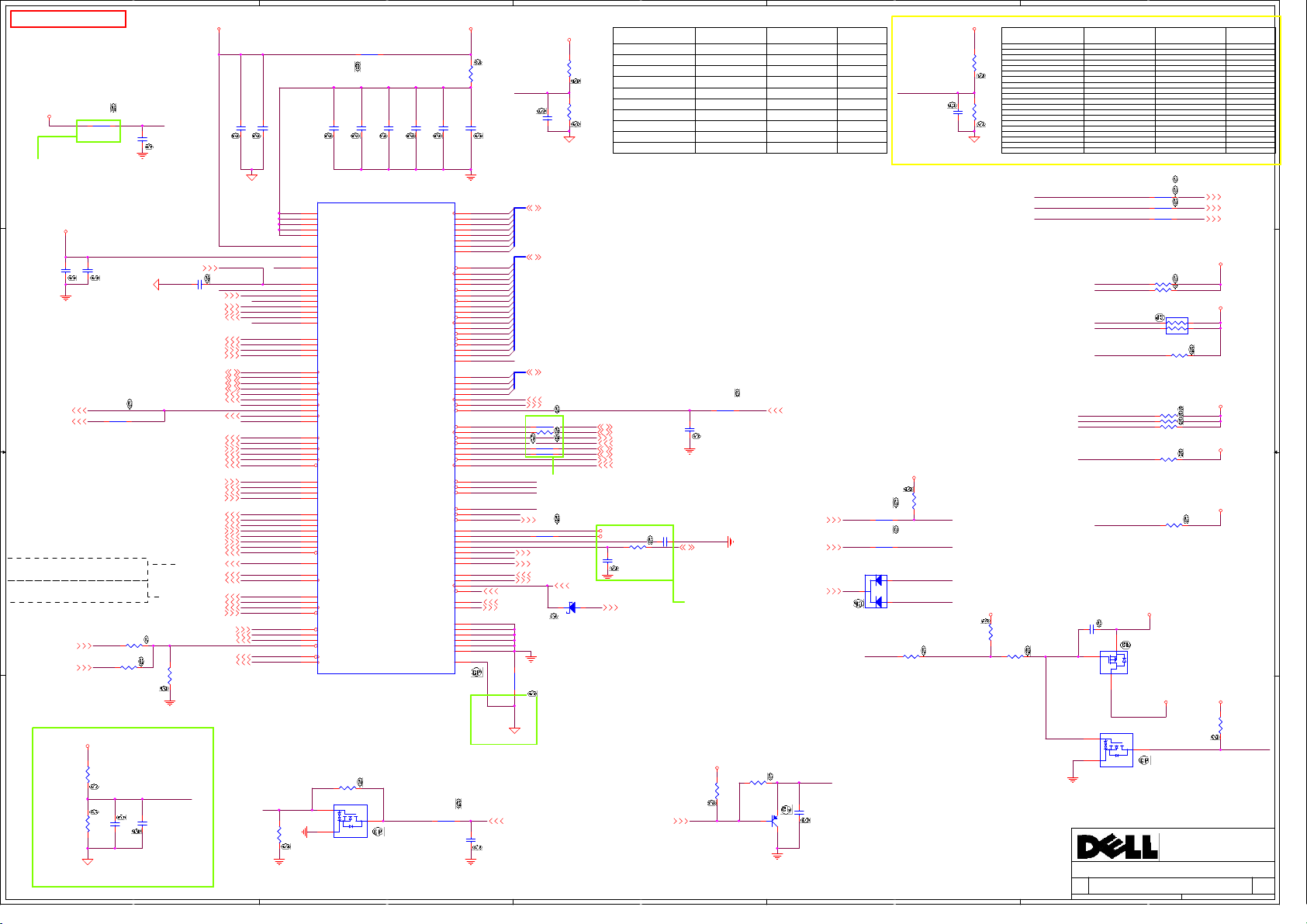

Page 12

5

4

3

2

1

SSID = MEMORY

DM1

DM1

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12

119

A13

80

A14

78

A15

79

A16/BA2

109

BA0

108

BA1

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

10

DQS0#

27

DQS1#

45

DQS2#

62

DQS3#

135

DQS4#

152

DQS5#

169

DQS6#

186

DQS7#

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

116

ODT0

120

ODT1

126

VREF_CA

1

VREF_DQ

30

RESET#

203

VTT1

204

VTT2

SKT_DDR 204P SMD

SKT_DDR 204P SMD

DDR3-204P-122-GP-U1

DDR3-204P-122-GP-U1

62.10017.Z51

62.10017.Z51

4

RAS#

WE#

CAS#

CS0#

CS1#

CKE0

CKE1

CK0#

CK1#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

EVENT#

VDDSPD

NC#1

NC#2

NC#/TEST

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

NP1

NP1

NP2

NP2

110

113

115

114

121

73

74

101

CK0

103

102

CK1

104

11

28

46

63

136

153

170

187

200

SDA

202

SCL

198

199

SA0_DIMA

197

SA0

SA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SA1_DIMA

201

77

122

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

1D35V_S3

M_A_RAS# [5]

M_A_WE# [5]

M_A_CAS# [5]

M_A_DIMA_CS#0 [5]

M_A_DIMA_CS#1 [5]

M_A_DIMA_CKE0 [5]

M_A_DIMA_CKE1 [5]

M_A_DIMA_CLK_DDR0 [5]

M_A_DIMA_CLK_DDR#0 [5]

M_A_DIMA_CLK_DDR1 [5]

M_A_DIMA_CLK_DDR#1 [5]

PCH_SMBDATA [13,18,58,62,67]

PCH_SMBCLK [13,18,58,62,67]

C1203

C1203

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

1D35V_S3

Layout Note:

Place these Caps near SO-DIMMA.

X01 change to short pad

DDR_PG_CTRL[4]

1 2

Q1201 Need check Vth=1V

3D3V_S0

12

DY

DY

12

0R0402-PAD-2-GP

0R0402-PAD-2-GP

R1205

R1205

3

0R0402-PAD-2-GP

0R0402-PAD-2-GP

C1207

12

DY

12

C1211

C1211

C1210

C1210

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

DDR_PG_CTRL_R

SA0_DIMA

SA1_DIMA

SC10U6D3V3MX-GPDYC1207

SC10U6D3V3MX-GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

R1202

R1202

C1208

C1208

12

12

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

C1212

C1212

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

1D35V_S3

Q1201

Q1201

DMN5L06K-7-GP

DMN5L06K-7-GP

84.05067.031

84.05067.031

C1209

SC10U6D3V3MX-GP

C1209

SC10U6D3V3MX-GP

C1213

C1213

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

G

12

R1201

R1201

0R0402-PAD-2-GP

0R0402-PAD-2-GP

12

C1220

C1220

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

DS

12

5V_S5

C1221

C1221

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

12

DY

DY

Note:

SA0 DIM0 = 0, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA0

SO-DIMMA TS Address is 0x30

Layout Note:

Place Close SO-DIMMA.

DDR_WR_VREF01[5]

12

C1222

C1222

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

1D35V_S3

D

R1208

R1208

220KR2J-L2-GP

220KR2J-L2-GP

DDR_VTT_PG_CTRL

R1204

R1204

2MR2-GP

2MR2-GP

G

2

12

+V_VREF_PATH1

12

Q1202

Q1202

2N7002K-2-GP

2N7002K-2-GP

84.2N702.J31

84.2N702.J31

2ND = 84.2N702.031

2ND = 84.2N702.031

S

M_A_B_DIMM_ODT

DDR_VTT_PG_CTRL [49]

1D35V_S30D675V_VTTREF

12

12

R1215

R1215

0R2J-2-GP

0R2J-2-GP

DY

DY

2R2F-GP

2R2F-GP

R1210

R1210

1 2

C1219

C1219

SCD022U16V2JX-GP

SCD022U16V2JX-GP

R1212

R1212

24D9R2F-L-GP

24D9R2F-L-GP

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

R1211

R1211

1K8R2F-GP

1K8R2F-GP

12

R1213

R1213

1K8R2F-GP

1K8R2F-GP

R1206 66D5R2F-GPR1206 66D5R2F-GP

1 2

R1207 66D5R2F-GPR1207 66D5R2F-GP

1 2

R1203 66D5R2F-GPR1203 66D5R2F-GP

1 2

R1209 66D5R2F-GPR1209 66D5R2F-GP

1 2

DDR3L-SODIMM1

DDR3L-SODIMM1

DDR3L-SODIMM1

Hadley 15"

Hadley 15"

Friday, June 28, 2013

Friday, June 28, 2013

Friday, June 28, 2013

Hadley 15"

M_VREF_DQ_DIMMA

M_A_DIMA_ODT0

M_A_DIMA_ODT1

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

1

M_B_DIMB_ODT0 [13]

M_B_DIMB_ODT1 [13]

12 101

12 101

12 101

X02

X02

X02

C1217

SCD1U10V2KX-5GPDYC1217

SCD1U10V2KX-5GP

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQ13

M_A_DQ8

M_A_DQ14

M_A_DQ10

M_A_DQ9

M_A_DQ12

M_A_DQ15

M_A_DQ11

M_A_DQ29

M_A_DQ28

M_A_DQ30

M_A_DQ31

M_A_DQ25

M_A_DQ24

M_A_DQ27

M_A_DQ26

M_A_DQ44

M_A_DQ41

M_A_DQ43

M_A_DQ47

M_A_DQ45

M_A_DQ40

M_A_DQ42

M_A_DQ46

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ7

M_A_DQ21

M_A_DQ20

M_A_DQ17

M_A_DQ16

M_A_DQ18

M_A_DQ19

M_A_DQ22

M_A_DQ23

M_A_DQ36

M_A_DQ33

M_A_DQ34

M_A_DQ38

M_A_DQ37

M_A_DQ32

M_A_DQ35

M_A_DQ39

M_A_DQ62

M_A_DQ58

M_A_DQ60

M_A_DQ61

M_A_DQ63

M_A_DQ59

M_A_DQ56

M_A_DQ57

M_A_DQS#1

M_A_DQS#3

M_A_DQS#5

M_A_DQS#6

M_A_DQS#0

M_A_DQS#2

M_A_DQS#4

M_A_DQS#7

M_A_DQS1

M_A_DQS3

M_A_DQS5

M_A_DQS6

M_A_DQS0

M_A_DQS2

M_A_DQS4

M_A_DQS7

M_A_DIMA_ODT0

M_A_DIMA_ODT1

0D675V_S0

12

M_A_A[15:0][5]

D D

M_A_BS2[5]

M_A_BS0[5]

M_A_BS1[5]

M_A_DQ[63:0][5]

12

DY

DY

C1202

C1202

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

Layout Note:

Place these caps

close to VREF_DQ

12

DY

DY

C1206

C1206

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

C1216

C1216

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

M_A_DQS#[7:0][5]

M_A_DQS[7:0][5]

DDR3_DRAMRST#[4,13]

Layout Note:

Place these caps

close to VREF_CA

Layout Note:

Place these caps

close to VTT1 and

VTT2.

M_VREF_CA_DIMMA

M_VREF_DQ_DIMMA

M_VREF_CA_DIMMA

12

12

DY

DY

C1201

C1201

C1218

C1218

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

C C

M_VREF_DQ_DIMMA

12

C1204

C1204

0D675V_S0

12

C1214

C1214

B B

A A

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

Layout Note:

All VREF traces should

have width=20mil;

spacing=20 mil

SCD1U10V2KX-5GP

12

C1205

C1205

DY

DY

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

12

C1215

C1215

DY

DY

DY

DY

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

DY

close to dimm

5

Page 13

5

4

3

2

1

SSID = MEMORY

DM2

M_B_A0

M_B_A1

M_B_A[15:0] [5]

D D

M_B_BS2[5]

M_B_BS0[5]

M_B_BS1[5]

12

DY

DY

12

DY

DY

12

C1318

C1318

M_B_DQ[63:0][5]

Layout Note:

Place these caps

close to VREF_CA

C1302

C1302

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

Layout Note:

Place these caps

close to VREF_DQ

C1306

C1306

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

Layout Note:

Place these caps

close to VTT1 and

VTT2.

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

M_B_DQS#[7:0] [5]

M_B_DQS[7:0] [5]

M_B_DIMB_ODT0[12]

M_B_DIMB_ODT1[12]

M_VREF_CA_DIMMB

M_VREF_DQ_DIMMB

DDR3_DRAMRST#[4,12]

M_VREF_CA_DIMMB

12

12

DY

DY

C1301

C1301

EC1302

EC1302

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

C C

M_VREF_DQ_DIMMB

12

12

C1305

C1305

DY

DY

C1304

C1304

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

0D675V_S0

12

B B

A A

12

DY

DY

C1317

C1317

C1316

C1316

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

Layout Note:

All VREF traces should

have width=20mil;

spacing=20 mil

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQ8

M_B_DQ14

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ9

M_B_DQ13

M_B_DQ15

M_B_DQ28

M_B_DQ29

M_B_DQ26

M_B_DQ27

M_B_DQ25

M_B_DQ24

M_B_DQ30

M_B_DQ31

M_B_DQ40

M_B_DQ41

M_B_DQ46

M_B_DQ42

M_B_DQ45

M_B_DQ44

M_B_DQ47

M_B_DQ43

M_B_DQ56

M_B_DQ57

M_B_DQ59

M_B_DQ58

M_B_DQ61

M_B_DQ60

M_B_DQ63

M_B_DQ62

M_B_DQ4

M_B_DQ1

M_B_DQ3

M_B_DQ7

M_B_DQ5

M_B_DQ0

M_B_DQ2

M_B_DQ6

M_B_DQ21

M_B_DQ20

M_B_DQ22

M_B_DQ23

M_B_DQ16

M_B_DQ17

M_B_DQ19

M_B_DQ18

M_B_DQ36

M_B_DQ33

M_B_DQ35

M_B_DQ39

M_B_DQ37

M_B_DQ32

M_B_DQ34

M_B_DQ38

M_B_DQ52

M_B_DQ49

M_B_DQ48

M_B_DQ53

M_B_DQ51

M_B_DQ55

M_B_DQ54

M_B_DQ50

M_B_DQS#1

M_B_DQS#3

M_B_DQS#5

M_B_DQS#7

M_B_DQS#0

M_B_DQS#2

M_B_DQS#4

M_B_DQS#6

M_B_DQS1

M_B_DQS3

M_B_DQS5

M_B_DQS7

M_B_DQS0

M_B_DQS2

M_B_DQS4

M_B_DQS6

C1319

SCD1U10V2KX-5GPDYC1319

SCD1U10V2KX-5GP

0D675V_S0

12

DY

close to dimm

5

4

DM2

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12

119

A13

80

A14

78

A15

79

A16/BA2

109

BA0

108

BA1

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

10

DQS0#

27

DQS1#

45

DQS2#

62

DQS3#

135

DQS4#

152

DQS5#

169

DQS6#

186

DQS7#

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

116

ODT0

120

ODT1

126

VREF_CA

1

VREF_DQ

30

RESET#

203

VTT1

204

VTT2

SKT_DDR 204P SMD

SKT_DDR 204P SMD

DDR3-204P-122-GP-U1

DDR3-204P-122-GP-U1

62.10017.Z51

62.10017.Z51

RAS#

WE#

CAS#

CS0#

CS1#

CKE0

CKE1

CK0#

CK1#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

EVENT#

VDDSPD

NC#1

NC#2

NC#/TEST

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

NP1

NP1

NP2

NP2

110

113

115

114

121

73

74

101

CK0

103

102

CK1

104

11

28

46

63

136

153

170

187

200

SDA

202

SCL

198

199

197

SA0

SA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SA1_DIMB

201

77

122

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

1D35V_S3

M_B_RAS# [5]

M_B_WE# [5]

M_B_CAS# [5]

M_B_DIMB_CS#0 [5]

M_B_DIMB_CS#1 [5]

M_B_DIMB_CKE0 [5]

M_B_DIMB_CKE1 [5]

M_B_DIMB_CLK_DDR0 [5]

M_B_DIMB_CLK_DDR#0 [5]

M_B_DIMB_CLK_DDR1 [5]

M_B_DIMB_CLK_DDR#1 [5]

PCH_SMBDATA [12,18,58,62,67]

PCH_SMBCLK [12,18,58,62,67]

DY

DY

C1303

C1303

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

1D35V_S3

12

DY

12

Layout Note:

Place these Caps near SO-DIMMA.

3

3D3V_S0

12

C1312

SC10U6D3V3MX-GPDYC1312

SC10U6D3V3MX-GP

C1311

SC10U6D3V3MX-GPDYC1311

SC10U6D3V3MX-GP

12

DY

12

C1314

C1314

C1313

C1313

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

Note:

SO-DIMMB SPD Address is 0xA4

SO-DIMMB TS Address is 0x34

3D3V_S0

12

R1301

R1301

10KR2J-3-GP

10KR2J-3-GP

SA1_DIMB

SA0_DIMBSA0_DIMB

12

R1302

R1302

0R0402-PAD-2-GP

0R0402-PAD-2-GP

Layout Note:

Place Close SO-DIMMA.

DDR_WR_VREF02[5]

C1307

SC10U6D3V3MX-GP

C1307

SC10U6D3V3MX-GP

C1308

SC10U6D3V3MX-GP

C1308

C1310

SC10U6D3V3MX-GPDYC1310

SC10U6D3V3MX-GP

12

12

DY

DY

12

12

C1315

C1315

DY

DY

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SC10U6D3V3MX-GP

C1309

SC10U6D3V3MX-GPDYC1309

SC10U6D3V3MX-GP

EC1301

EC1301

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

12

2

0D675V_VTTREF

R1308

R1308

0R2J-2-GP

0R2J-2-GP

2R2F-GP

2R2F-GP

R1304

R1304

1 2

12

C1320

C1320

SCD022U16V2JX-GP

SCD022U16V2JX-GP

+V_VREF_PATH2

12

R1307

R1307

24D9R2F-L-GP

24D9R2F-L-GP

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

1D35V_S3

12

DY

DY

Friday, June 28, 2013

Friday, June 28, 2013

Friday, June 28, 2013

12

R1306

R1306

1K8R2F-GP

1K8R2F-GP

12

R1303

R1303

1K8R2F-GP

1K8R2F-GP

DDR3L-SODIMM2

DDR3L-SODIMM2

DDR3L-SODIMM2

Hadley 15"

Hadley 15"

Hadley 15"

M_VREF_DQ_DIMMB

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

13 101

13 101

13 101

1

X02

X02

X02

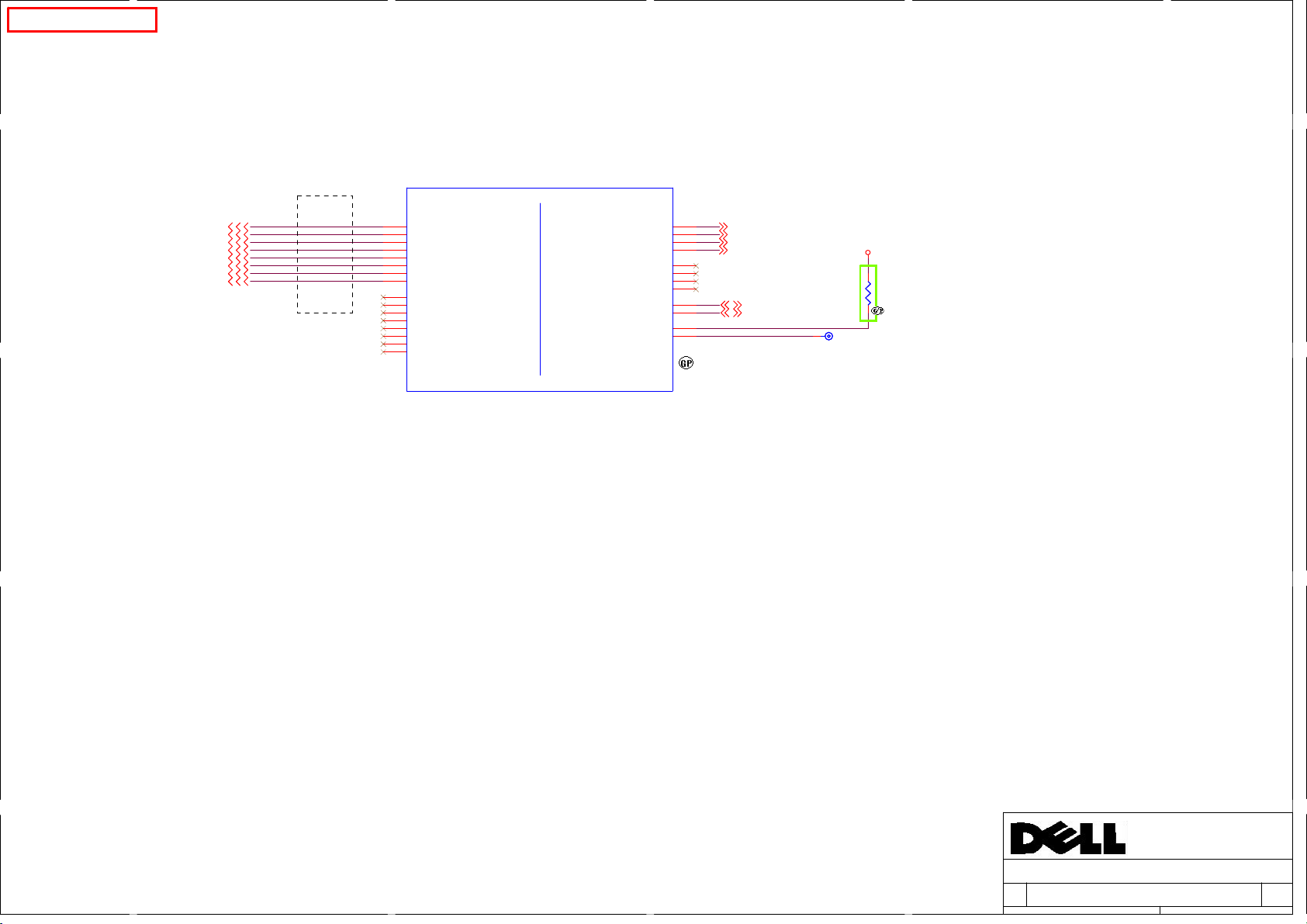

Page 14

5

D D

C C

4

3

2

1

(Blanking)

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

Title

Title

Title

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan , R.O.C.

M1&M3

M1&M3

M1&M3

Hadley 15"

Hadley 15"

Hadley 15"

14 10 1Friday, June 28, 2 013

of

14 10 1Friday, June 28, 2 013

of

14 10 1Friday, June 28, 2 013

1

X02

X02

X02

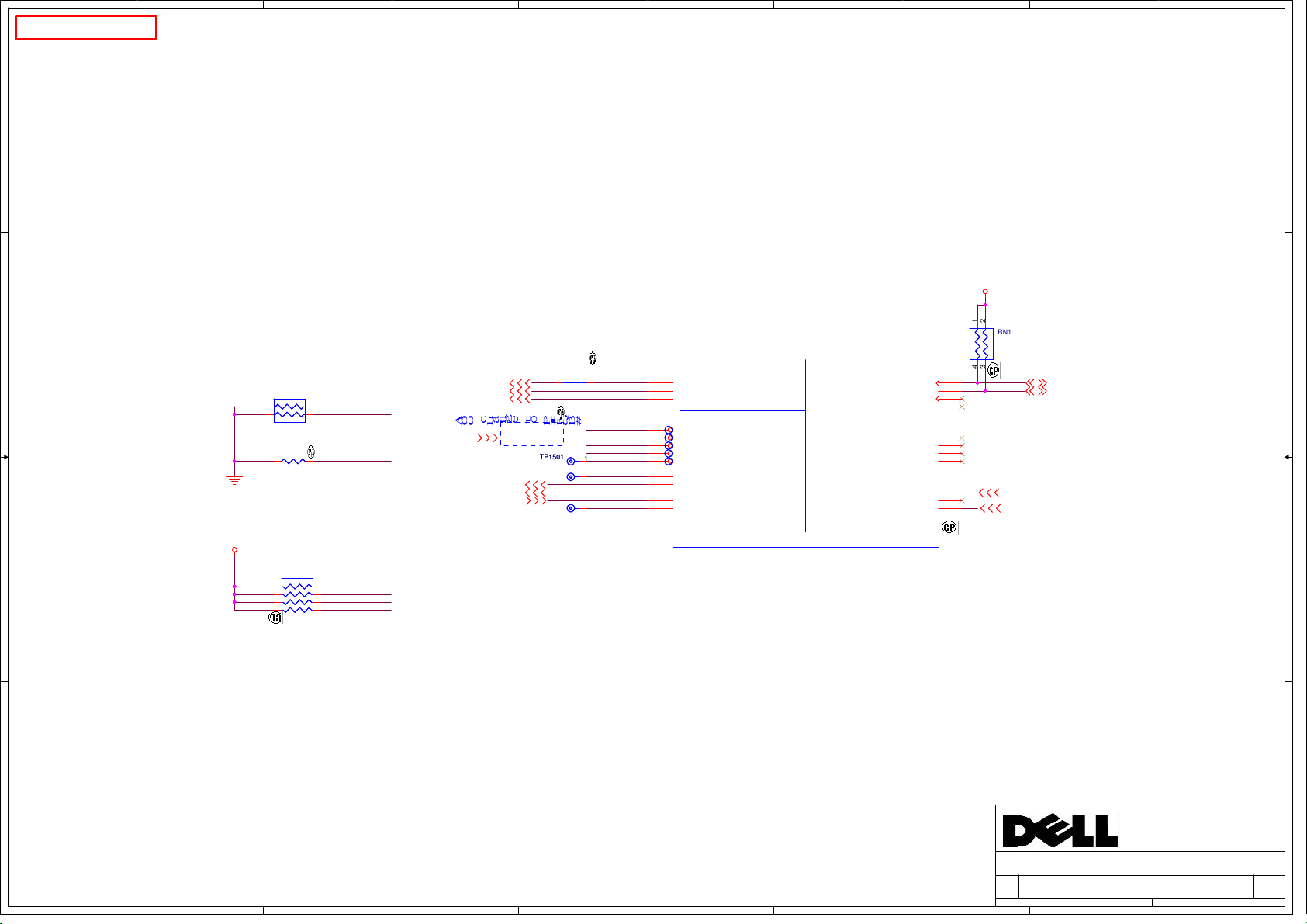

Page 15

5

4

3

2

1

SSID = CPU

D D

3D3V_S 0

1

23

RN1501

HSW_ULT_DDR3L

eDP SIDEBAND

eDP SIDEBAND

PCIE

PCIE

HSW_ULT_DDR3L

DISPLAY

DISPLAY

CPU1I

AD4

CPU1I

B8

A9

C6

U6

P4

N4

N2

U7

L1

L3

R5

L4

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA#/GPIO77

PIRQB#/GPIO78

PIRQC#/GPIO79

PIRQD#/GPIO80

PME#

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

C C

0R0402 -PAD-2-GP

0R0402 -PAD-2-GP

L_BKLT _CTRL_R

R1501

R1501

RN1504

RN1504

1

2 3

OPS

OPS

SRN10K J-5-GP

SRN10K J-5-GP

100KR2 J-1-GP

100KR2 J-1-GP

R1509

R1509

1 2

DGPU_P WR_EN

4

DGPU_H OLD_RST#

DGPU_P WROK

L_BKLT _CTRL[53 ]

L_BKLT _EN[24]

EDP_VD D_EN[52]

B11!dibohf!up!QJSRC$

HDD_FA LL_INT[67]

DGPU_P WR_EN[82,83]

DGPU_H OLD_RST#[73]

DGPU_P WROK[24,82,83 ]

1 2

0R0402 -PAD-2-GP

0R0402 -PAD-2-GP

R1503

R1503

1 2

TP1501TP1501

TP1503TP1503

TP1502TP1502

PIRQA#

PIRQB#

PIRQC#

PIRQD#

PCI_PME#

1

MCP_GP IO55

1

DGPU_P WR_EN

DGPU_H OLD_RST#

DGPU_P WROK

PCH_SD _CD#

1

9 OF 19

9 OF 19

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

RN1501

SRN2K2 J-1-GP

SRN2K2 J-1-GP

4

HDMI_PCH _DET [54]

EDP_HP D [52 ,53]

PCH_HD MI_CLK [54]

PCH_HD MI_DATA [54]

3D3V_S 0

B B

A A

5

RN1505

RN1505

8

7

6

SRN10K J-6-GP

SRN10K J-6-GP

PIRQD#

1

PIRQC#

2

PIRQB#

3

PIRQA#

45

4

3

HASW ELL-6-GP

HASW ELL-6-GP

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, S ec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsien 221, Taiwan , R.O.C.

Taipei Hsien 221, Taiwan , R.O.C.

Title

Title

Title

CPU ( EDP SIDEBAND/GPIO/DDI )

CPU ( EDP SIDEBAND/GPIO/DDI )

CPU ( EDP SIDEBAND/GPIO/DDI )

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

2

Date: Sheet

Taipei Hsien 221, Taiwan , R.O.C.

Hadley 15"

Hadley 15"

Hadley 15"

X02

X02

15 10 1Friday, June 28, 2 013

of

15 10 1Friday, June 28, 2 013

of

15 10 1Friday, June 28, 2 013

1

X02

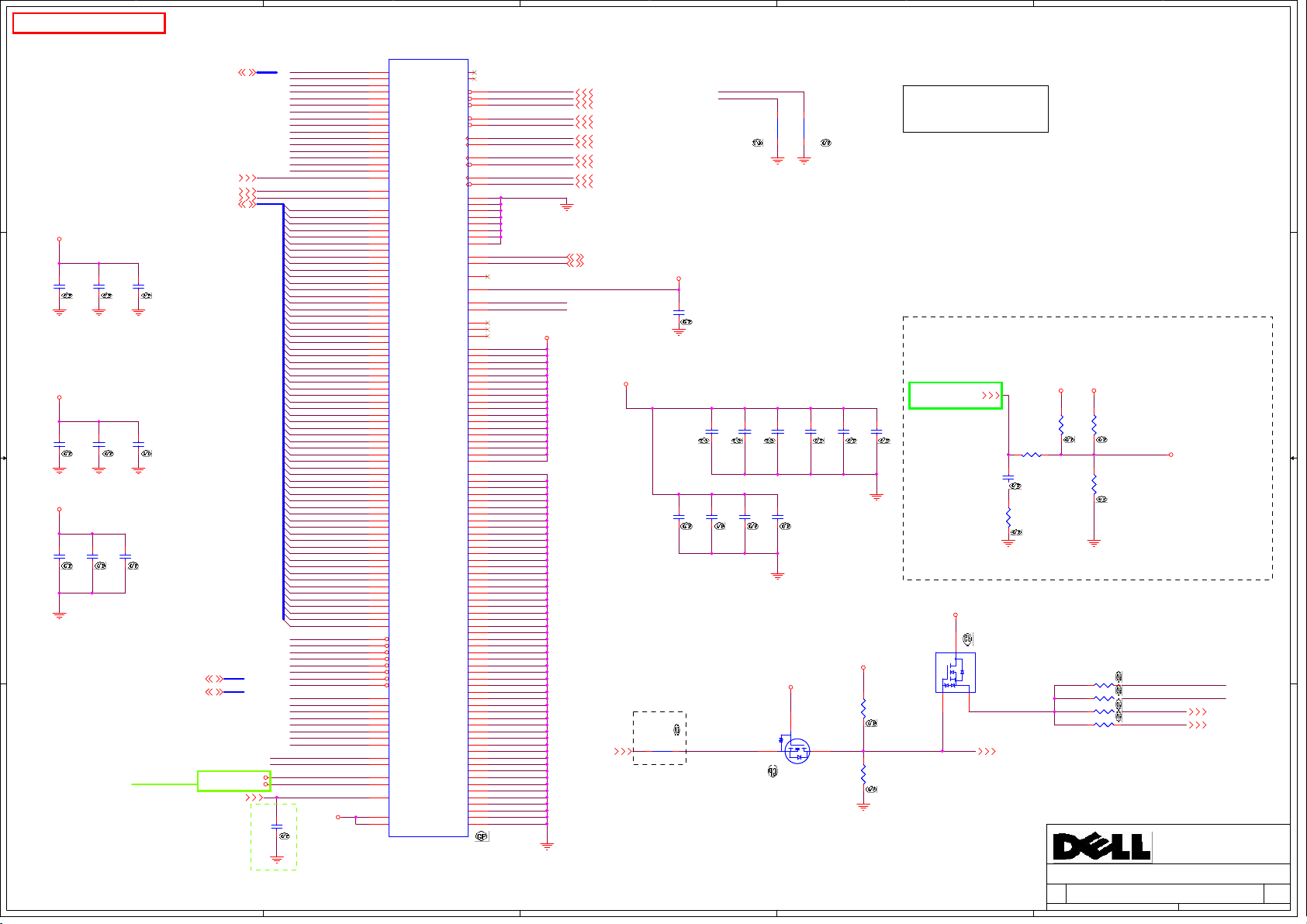

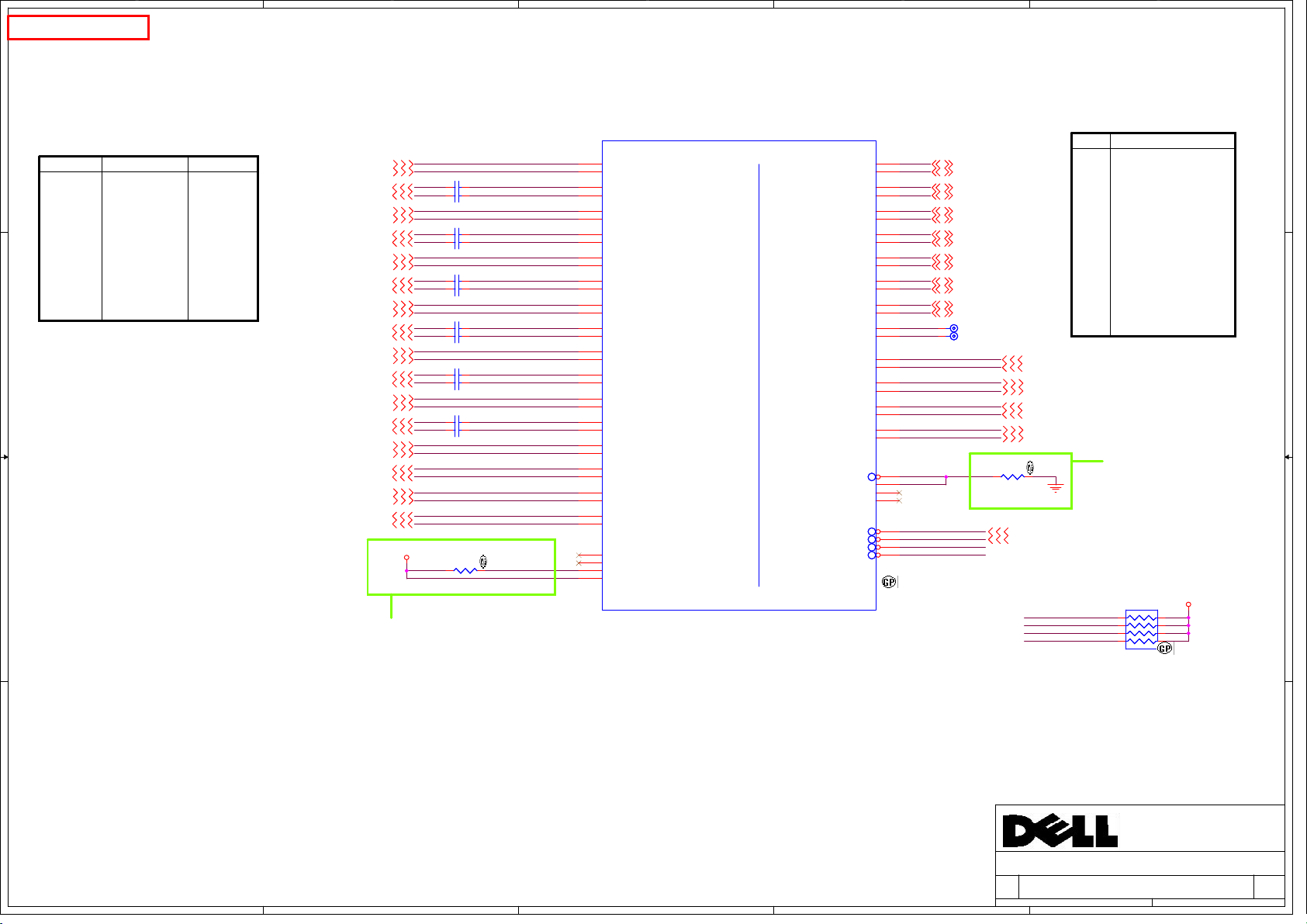

Page 16

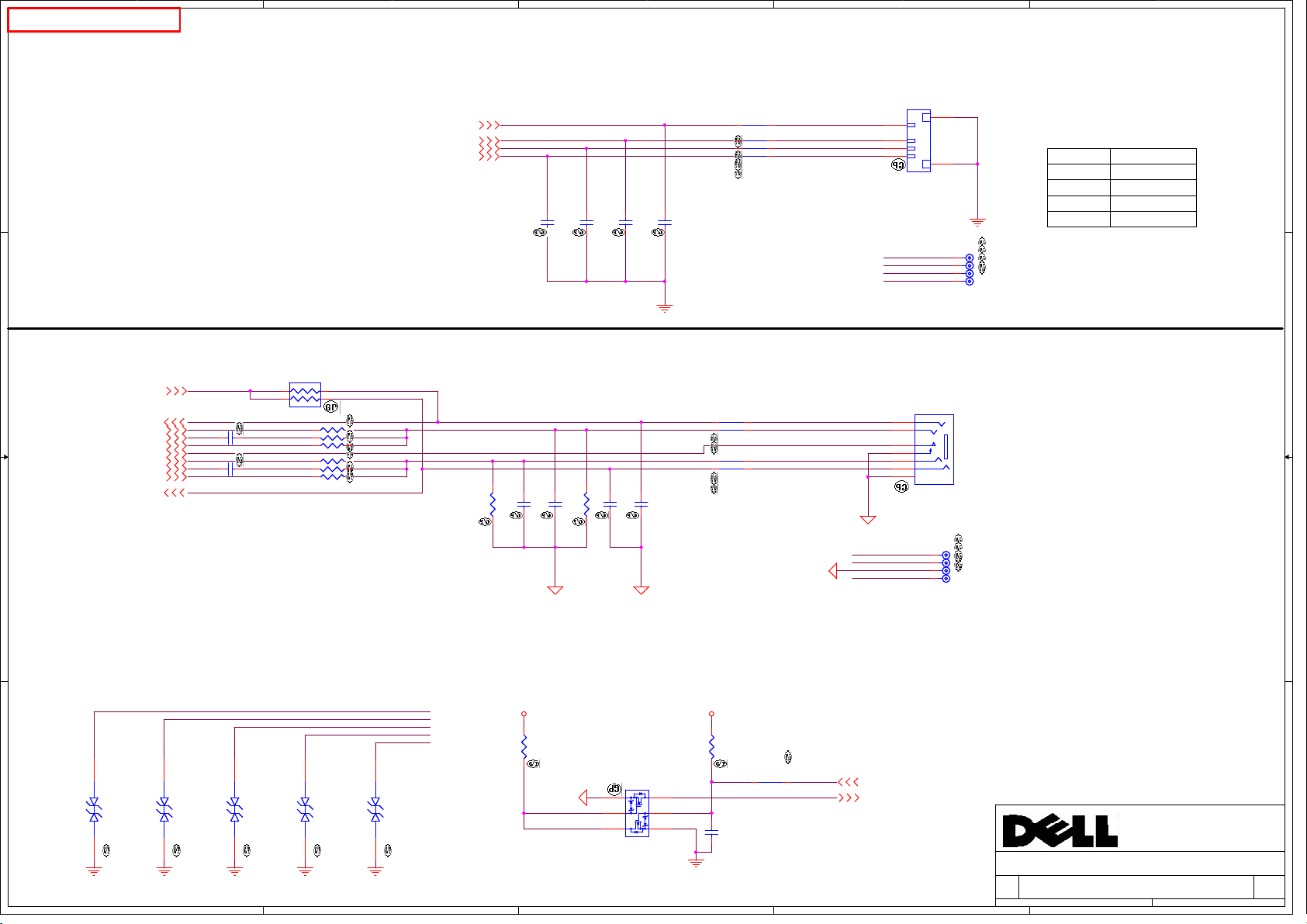

SSID = CPU

5

4

3

2

1

D D

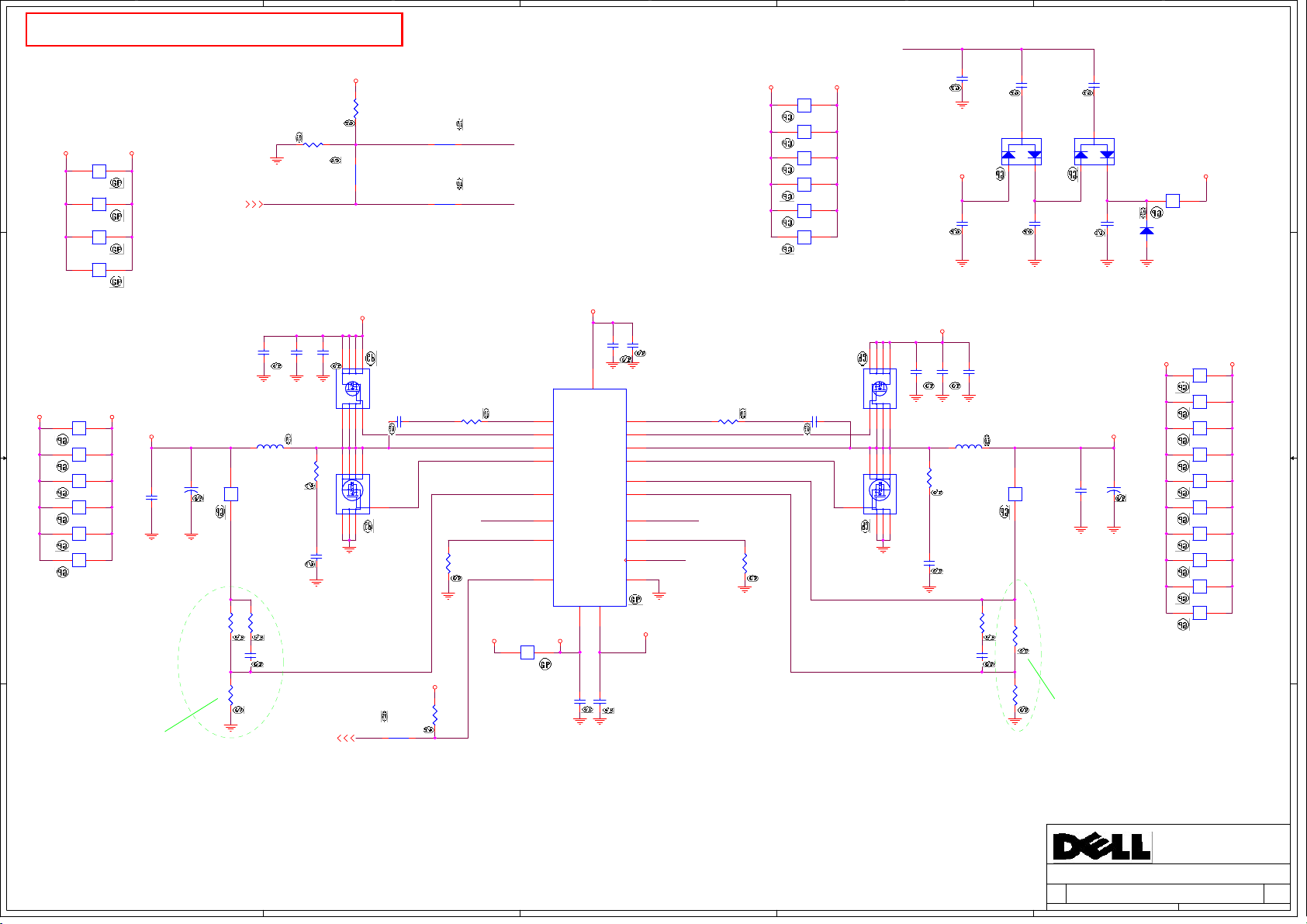

PCIE Table

Port

1

2

3

4

5(4lane)

6(4lane)

C C

B B

Device

N/A

N/A

WLAN

LAN+

Card reader

GPU

N/A

Share BUS

USB3.0_3

USB3.0_4

SATA0~3

CPU_RX N_C_dGPU_T XN0[73]

CPU_RX P_C_dGPU_T XP0[73]

dGPU_R XN_C_CPU_T XN0[73]

dGPU_R XP_C_CPU_T XP0[7 3]

CPU_RX N_C_dGPU_T XN1[73]

CPU_RX P_C_dGPU_T XP1[73 ]

dGPU_R XN_C_CPU_T XN1[73]

dGPU_R XP_C_CPU_T XP1[7 3]

CPU_RX N_C_dGPU_T XN2[73]

CPU_RX P_C_dGPU_T XP2[73 ]

dGPU_R XN_C_CPU_T XN2[73]

dGPU_R XP_C_CPU_T XP2[7 3]

CPU_RX N_C_dGPU_T XN3[73]

CPU_RX P_C_dGPU_T XP3[73 ]

dGPU_R XN_C_CPU_T XN3[73]

dGPU_R XP_C_CPU_T XP3[7 3]

PCIE_PRX _WLANTX _N3[58]

PCIE_PRX _WLANTX _P3[58]

PCIE_PTX _WLANRX _N3_C[58]

PCIE_PTX _WLANRX _P3_C[58]

PCIE_PRX _LANTX_N4[30]

PCIE_PRX _LANTX_P4[30]

PCIE_PTX _LANRX_N4_ C[30]

PCIE_PTX _LANRX_P4_ C[30]

USB3_P RX_DTX_N2[63]

USB3_P RX_DTX_P2[63]

USB3_P TX_DRX_N2[63]

USB3_P TX_DRX_P2[63]

USB3_P RX_DTX_N3[63]

USB3_P RX_DTX_P3[63]

USB3_P TX_DRX_N3[63]

USB3_P TX_DRX_P3[63]

+V1.05S _AUSB3PLL

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

C1606

C1606

1 2

OPS

OPS

1 2

OPS

OPS

C1605

C1605

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

C1608

C1608

1 2

OPS

OPS

1 2

OPS

OPS

C1607

C1607

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

C1610

C1610

1 2

OPS

OPS

1 2

OPS

OPS

C1609

C1609

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

C1612

C1612

1 2

OPS

OPS

1 2

OPS

OPS

C1611

C1611

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

C1601

C1601

1 2

1 2

C1602

C1602

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

C1603

C1603

1 2

1 2

C1604

C1604

SCD1U1 0V2KX-5GP

SCD1U1 0V2KX-5GP

R1601

R1601

3KR2F-G P

3KR2F-G P

1 2

Layout Note:

1. PCIE_RC OMP/ PCIE _IREF tra ce width= 12~15mil

2. Isolati on Spacin g: 12mil

3. Total t race leng th<500mil

dGPU_R XN_CPU_TXN 0

dGPU_R XP_CPU_TXP 0

dGPU_R XN_CPU_TXN 1

dGPU_R XP_CPU_TXP 1

dGPU_R XN_CPU_TXN 2

dGPU_R XP_CPU_TXP 2

dGPU_R XN_CPU_TXN 3

dGPU_R XP_CPU_TXP 3

PCIE_PTX _WLANRX _N3

PCIE_PTX _WLANRX _P3

PCIE_PTX _LANRX_N4

PCIE_PTX _LANRX_P4

PCIE_RCO MP

E10

C23

C22

B23

A23

H10

G10

B21

C21

B22

A21

G11

C29

B30

G13

B29

A29

G17

C30

C31

G15

B31

A31

E15

E13

A27

B27

CPU1K

CPU1K

F10

F8

E8

E6

F6

F11

F13

F17

F15

PERN5_L0

PERP5_L0

PETN5_L0

PETP5_L0

PERN5_L1

PERP5_L1

PETN5_L1

PETP5_L1

PERN5_L2

PERP5_L2

PETN5_L2

PETP5_L2

PERN5_L3

PERP5_L3

PETN5_L3

PETP5_L3

PERN3

PERP3

WLAN

PETN3

PETP3

PERN4

PERP4

LAN+Card reader

PETN4

PETP4

PERN1/USB3RN3

PERP1/USB3RP3

PETN1/USB3TN3

PETP1/USB3TP3

PERN2/USB3RN4

PERP2/USB3RP4

PETN2/USB3TN4

PETP2/USB3TP4

RSVD#E15

RSVD#E13

PCIE_RCOMP

PCIE_IREF

HASW ELL-6-GP

HASW ELL-6-GP

HSW_ULT_DDR3L

HSW_ULT_DDR3L

PCIE USB

PCIE USB

11 OF 19

11 OF 19

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS#

USBRBIAS

RSVD#AN10

RSVD#AM10

OC0/GPIO40#

OC1/GPIO41#

OC2/GPIO42#

OC3/GPIO43#

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USB_PN 7

USB_PP 7

USB_CO MP

USB_OC #0_1

USB_OC #2_3

USB_OC #4_5

USB_OC #6_7

1

1

USB_PN 0 [34]

USB_PP 0 [3 4]

USB_PN 1 [35]

USB_PP 1 [3 5]

USB_PN 2 [63]

USB_PP 2 [6 3]

USB_PN 3 [63]

USB_PP 3 [6 3]

USB_PN 4 [52]

USB_PP 4 [5 2]

USB_PN 5 [58]

USB_PP 5 [5 8]

USB_PN 6 [52]

USB_PP 6 [5 2]

TP1602TP1602

TP1601TP1601

1 2

R1602

R1602

22D6R2 F-L1-GP

22D6R2 F-L1-GP

USB_OC #0_1 [3 5]

USB_OC #2_3 [3 5]

USB 2.0 Table

Pair

0

1

2

3

4

5

6

7

USB3_P RX_CTX_N0 [34 ]

USB3_P RX_CTX_P0 [34]

USB3_P TX_CRX_N0 [34 ]