5

4

3

2

1

D

D

KR CS MLK 13" Schematics

Whiskey Lake-U

C

2018-07-19

REV : A00

C

B

A

DY : None Installed

UMA: UMA only installed

5

4

B

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Thursday, July 19, 2018

Thursday, July 19, 2018

Thursday, July 19, 2018

Date: Sheet

Date: Sheet

Date: Sheet

3

2

Cover Page

KR CS MLK 13"

KR CS MLK 13"

KR CS MLK 13"

1 106

of

1 106

of

1 106

of

1

A00

A00

A00

A

5

Project code: 4PD0EZ010001???

4

3

2

1

D

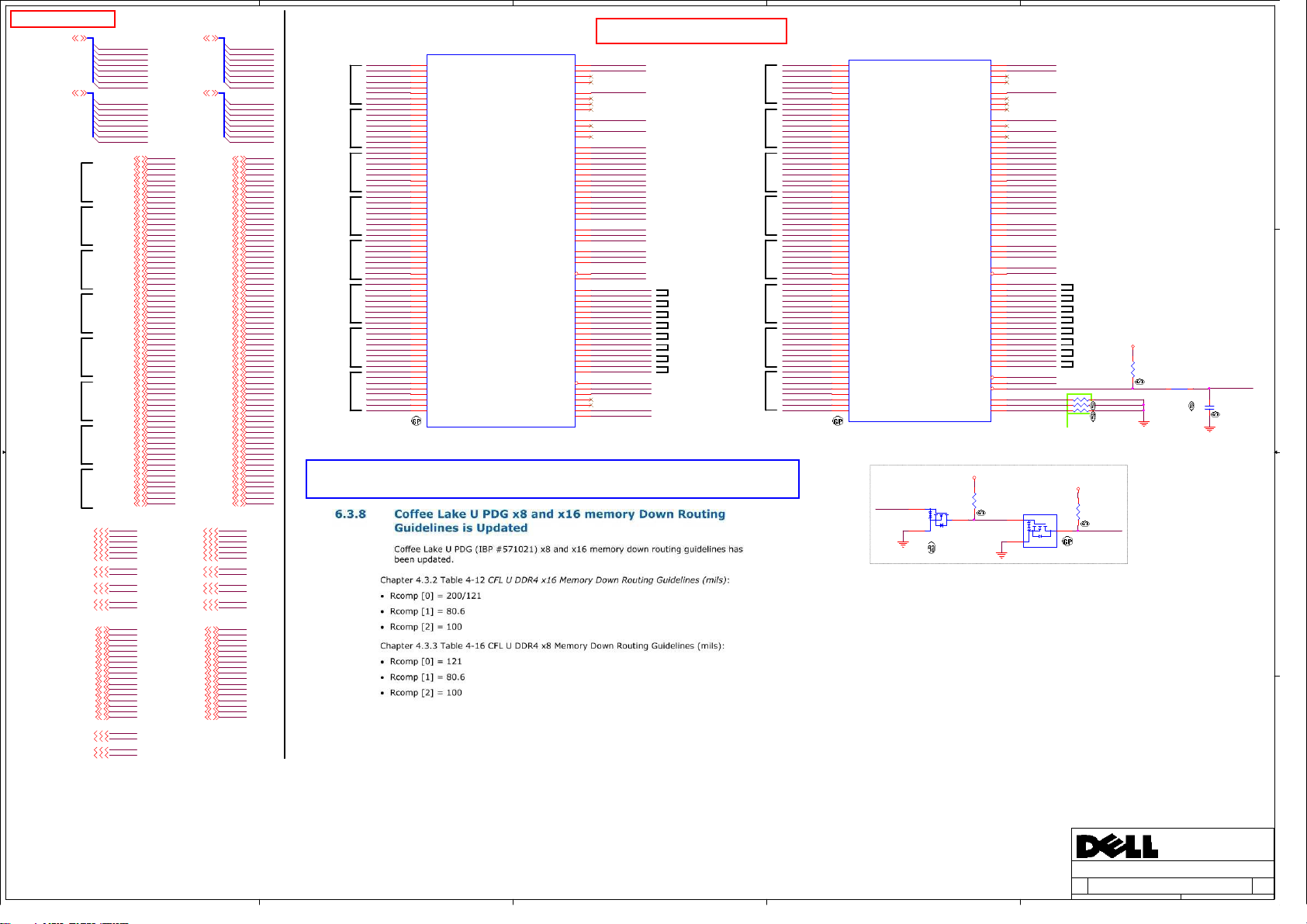

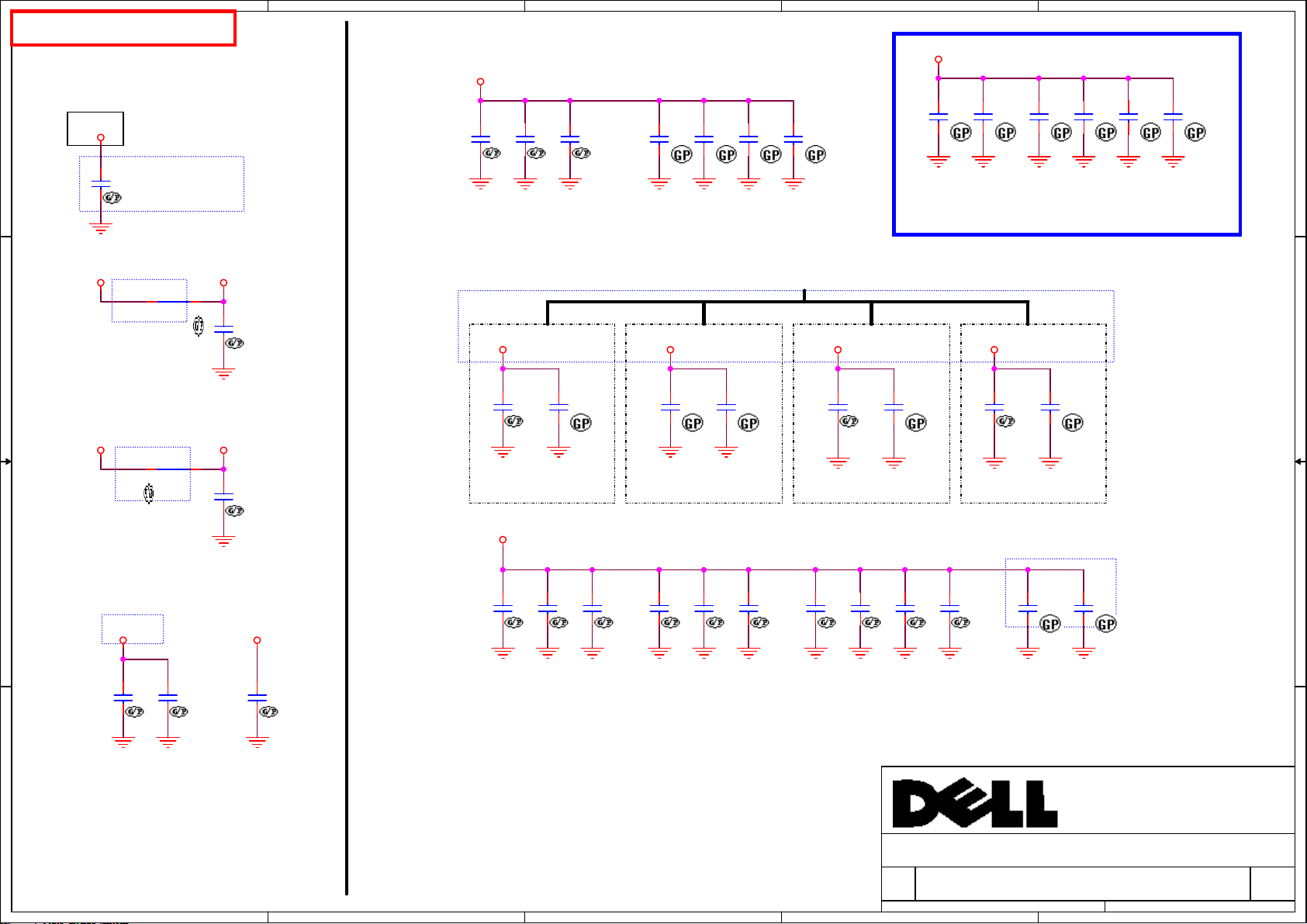

DDR4 X16 Memory Down

HDMI CONN.

C

B

12

HDMI2.0

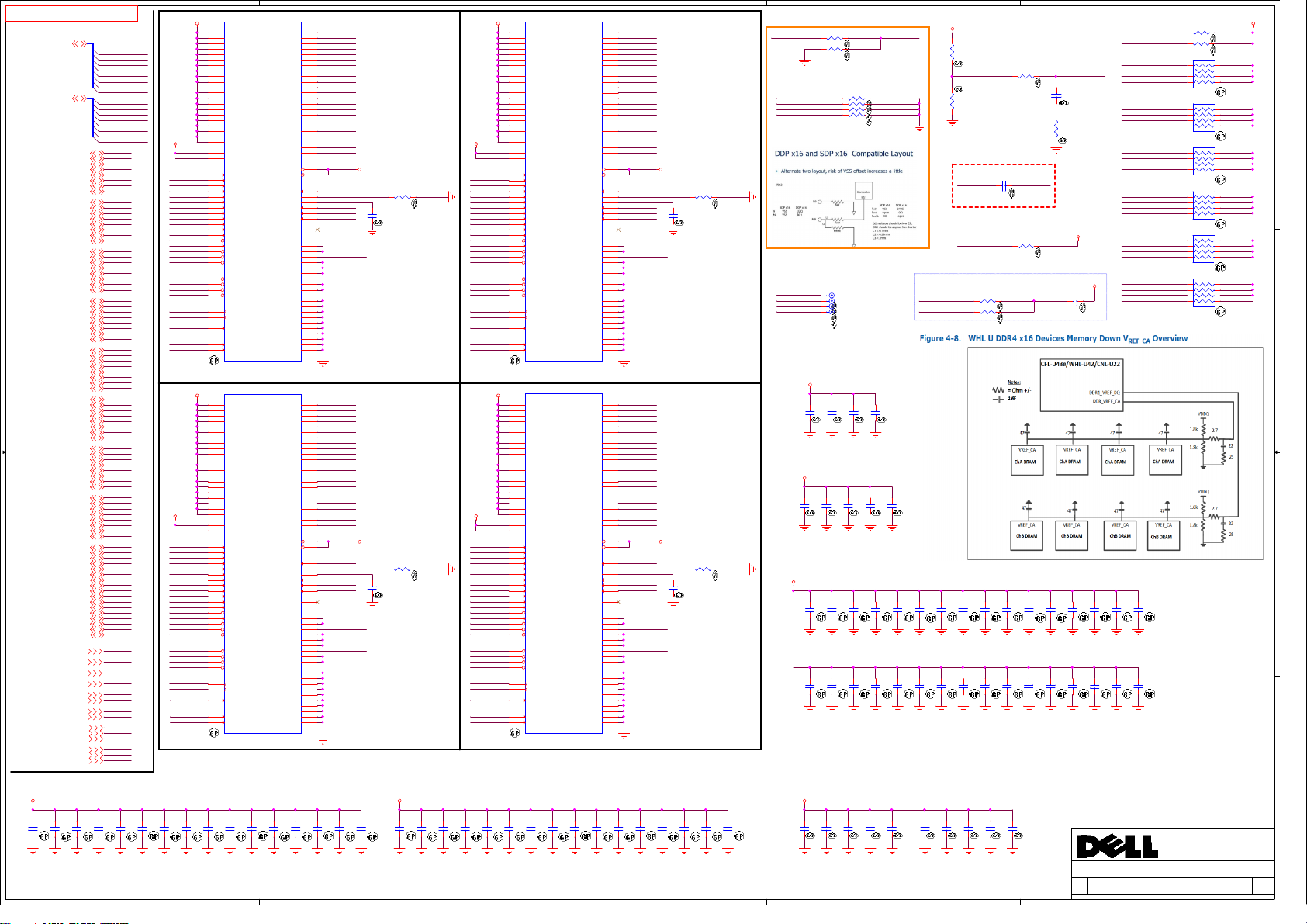

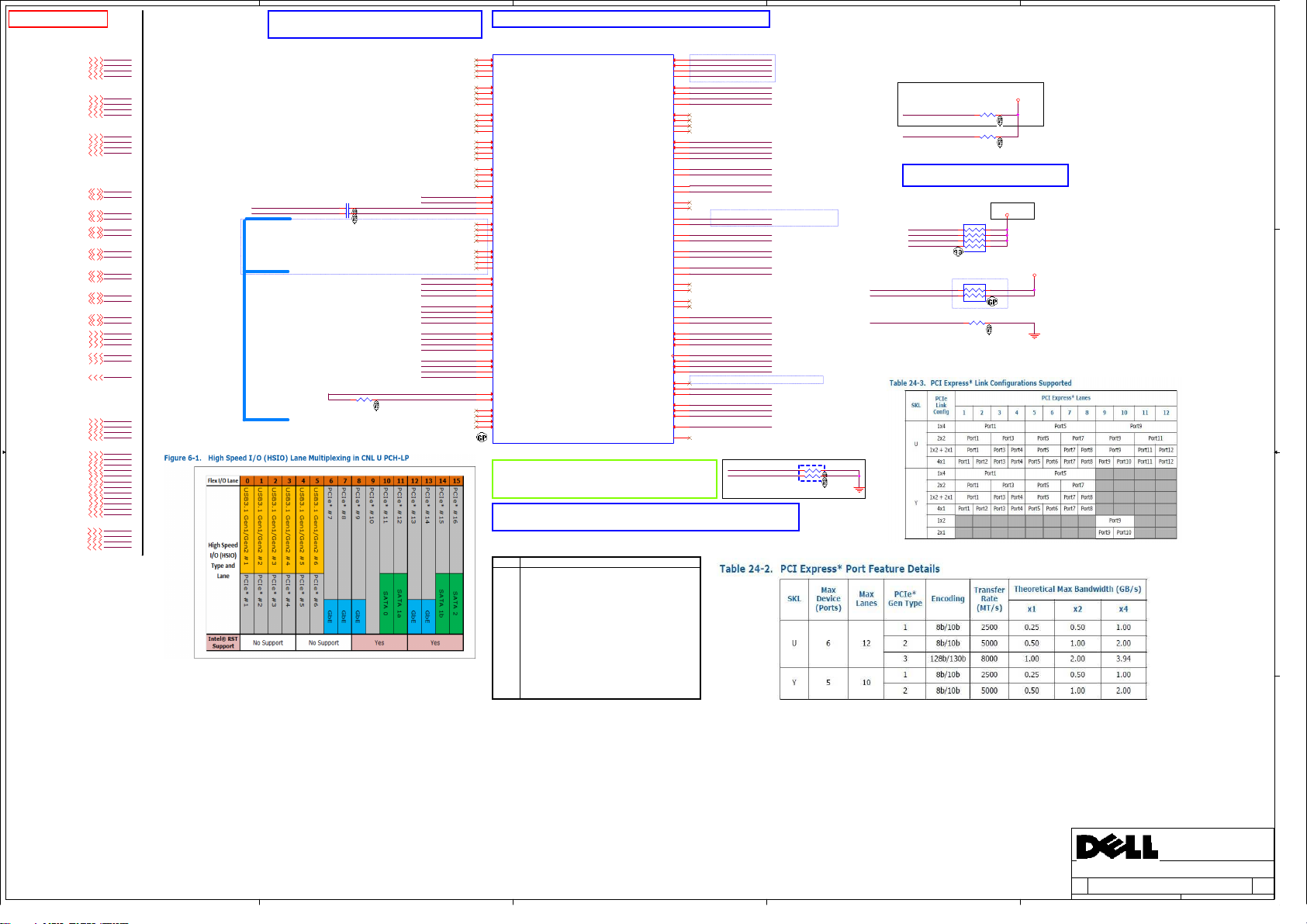

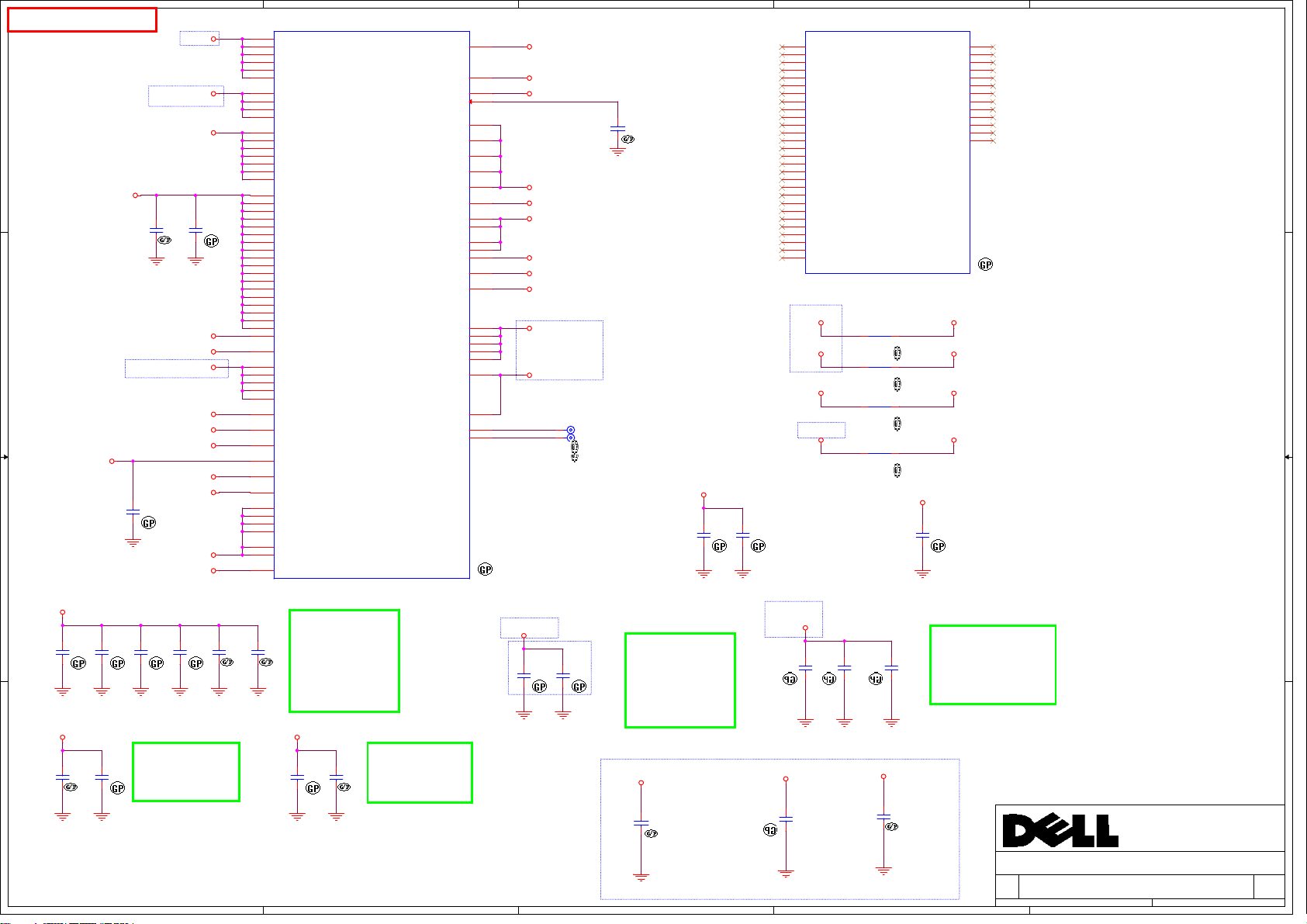

WHL-U 13" CPU 15W Block Diagram

1Rx16

1Rx16 Channel B

USB2.0 LANE5

Intel CPU

Whiskey Lake U

15W (UMA)

WHL PCH-LP

10 USB 2.0/1.1 ports

6 USB 3.0 ports

High Definition Audio

3 SATA ports

6 PCIE ports

LPC I/F

ACPI 5.0

DP

USB3.0

USB3.0 LANE4

USB2.0

USB2.0 LANE4

PCIE

USB2.0

USB2.0

USB2.0 LANE7

USB3.0

USB3.0 LANE1

USB2.0

USB2.0 LANE1

HDA

MUX and Redriver

TUSB546

I2C1

DDR4 X16 Memory Down

13.3" FHD

Touch panel

LPSCON

PS175HDM

M.2 SSD

Finger Printer

LID SENSOR

ALPS

HGDEDM013A

USB 3.0 CONN.

Type-A

eSPI debug port

Channel A

13

eDP

55

I2C

DDI1

57

63

92

PCIE/SATA

USB2.0

I2C

70

USB3.0

USB3.0 LANE2

USB2.0 LANE2

USB2.0

eSPI

35

68

PCB P/N: 17945

Revision: SA

DP/USB 3.0

71

PD

TI

TPS65982DC

NGFF

WLAN

CardReader

SD 3.0

Realtak

RTS5176E

USB 3.0

re-driver

Parade PS8713B

HDA

CODEC

Realtek

ALC3254

CC1/CC2

SMBUS

USB 2.0

USB3.0

MIC_IN/AGND

HP_R/L

27

USB3.0 Type-C

Port1

IO Board

Micro SD Card

Slot

USB3.0 CONN.

Type-A

Universal Jack

2CH SPEAKER

(2CH 2W/4ohm)

D

7372

LPS

C

B

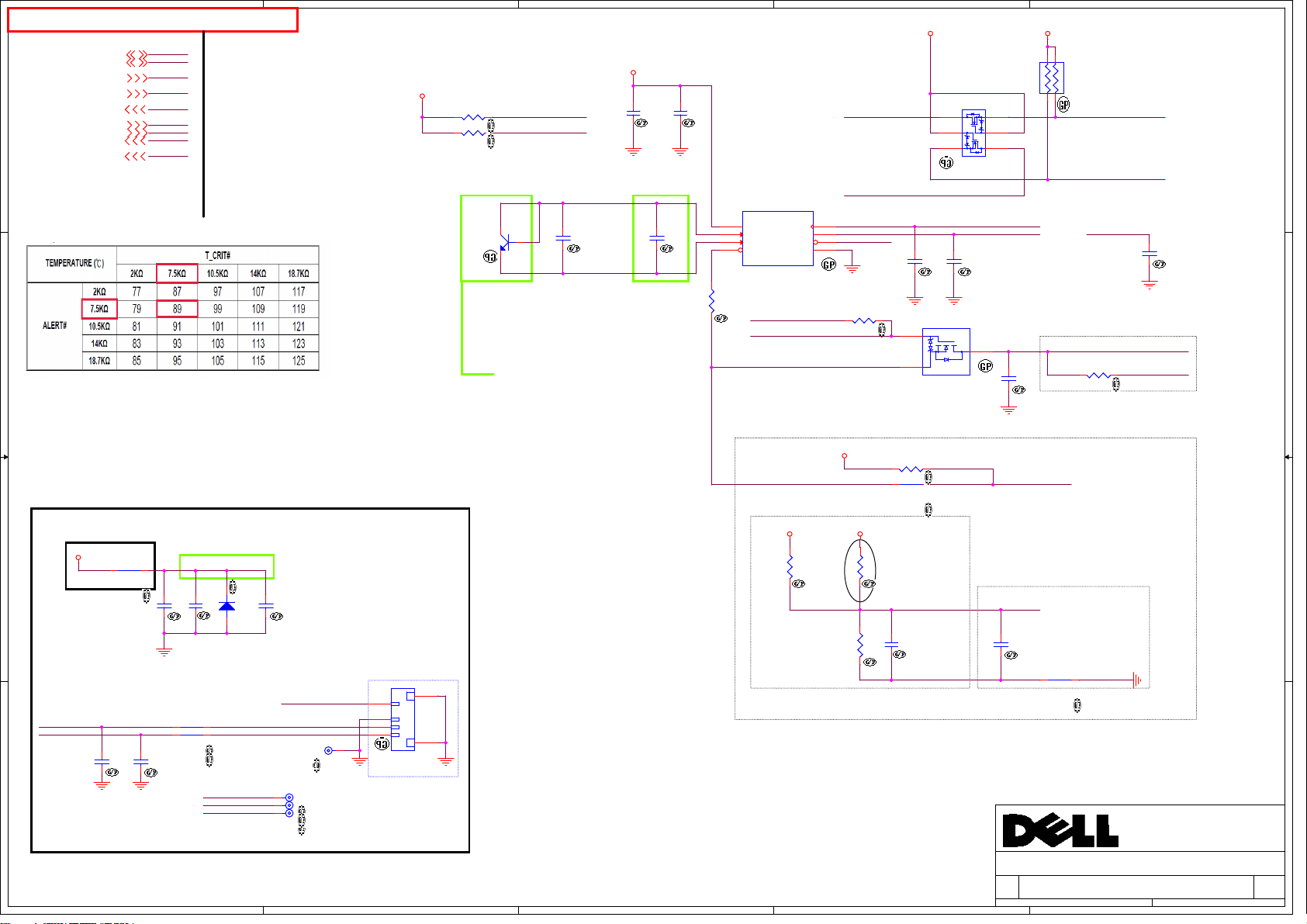

Thermal

NUVOTON

NCT7718W

A

Fan Control

PWM

26

26

SMBUS

FAN DETECT

KBC

KB SCAN

INTERFACE

Int.

FAN

5

KB

MICROCHIP

MEC1416

Touch PAD

Image sensor

PS2

4

USB2.0 x 1

USB2.0 LANE6

24

SPI

I2C

Flash ROM

16MB

Quad Read

3

25

TPM

NUVOTON NPCT750

91

Camera (HD)

D-MIC

2

55

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Block Diagram

Block Diagram

Block Diagram

KR CS MLK 13"

KR CS MLK 13"

KR CS MLK 13"

1

of

2 106Thursday, July 19, 2018

of

2 106Thursday, July 19, 2018

of

2 106Thursday, July 19, 2018

A00

A00

A00

A

5

4

3

2

1

SSID = CPU

PECI_CPU[24]

PROCHOT#_CPU[24,44,46]

D

C

TP_WAKE_KBC#[24,65]

H_CPUPWRGD[17]

TOUCH_PANEL_INTR#[55]

TOUCH_PANEL_PD#[55]

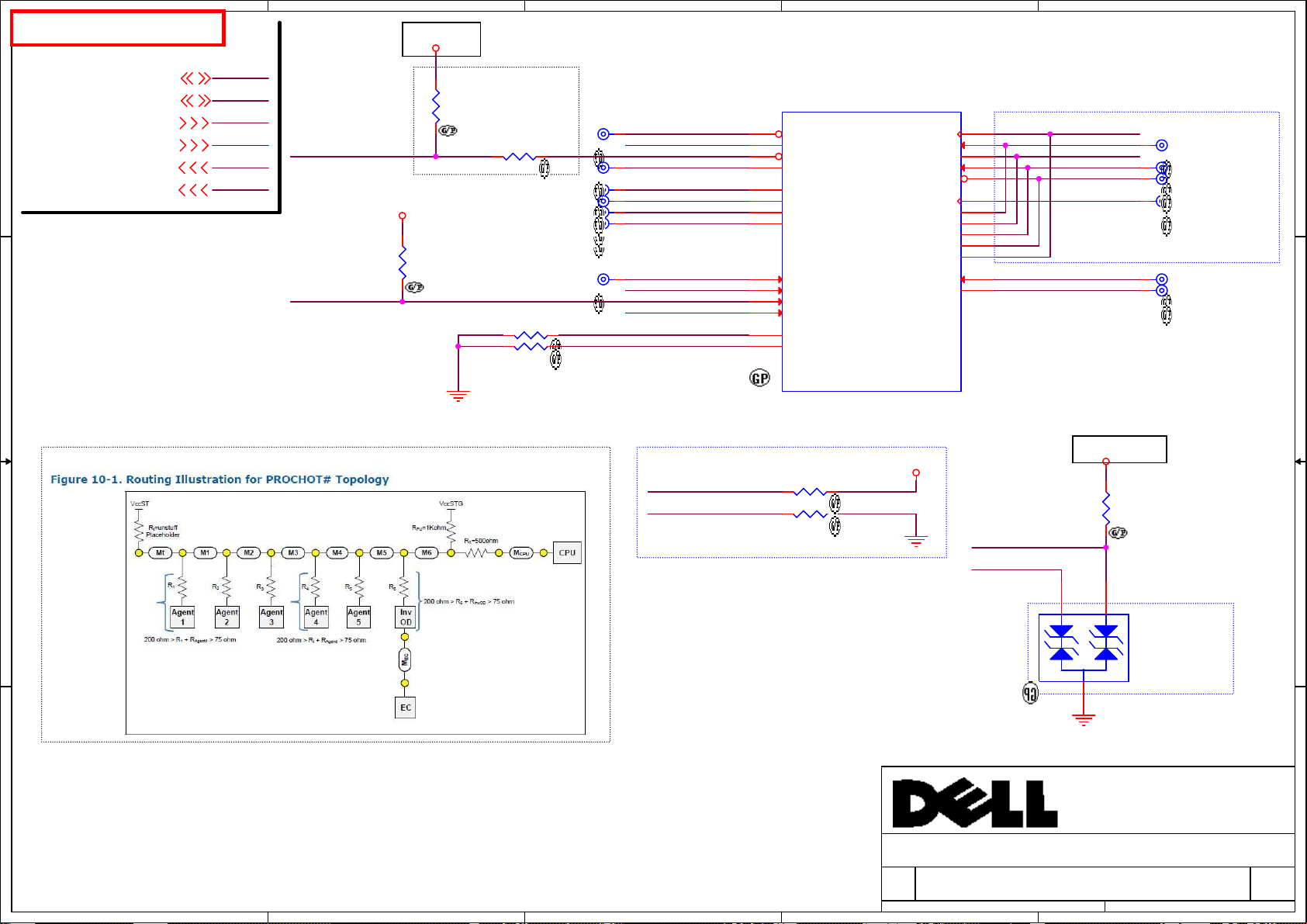

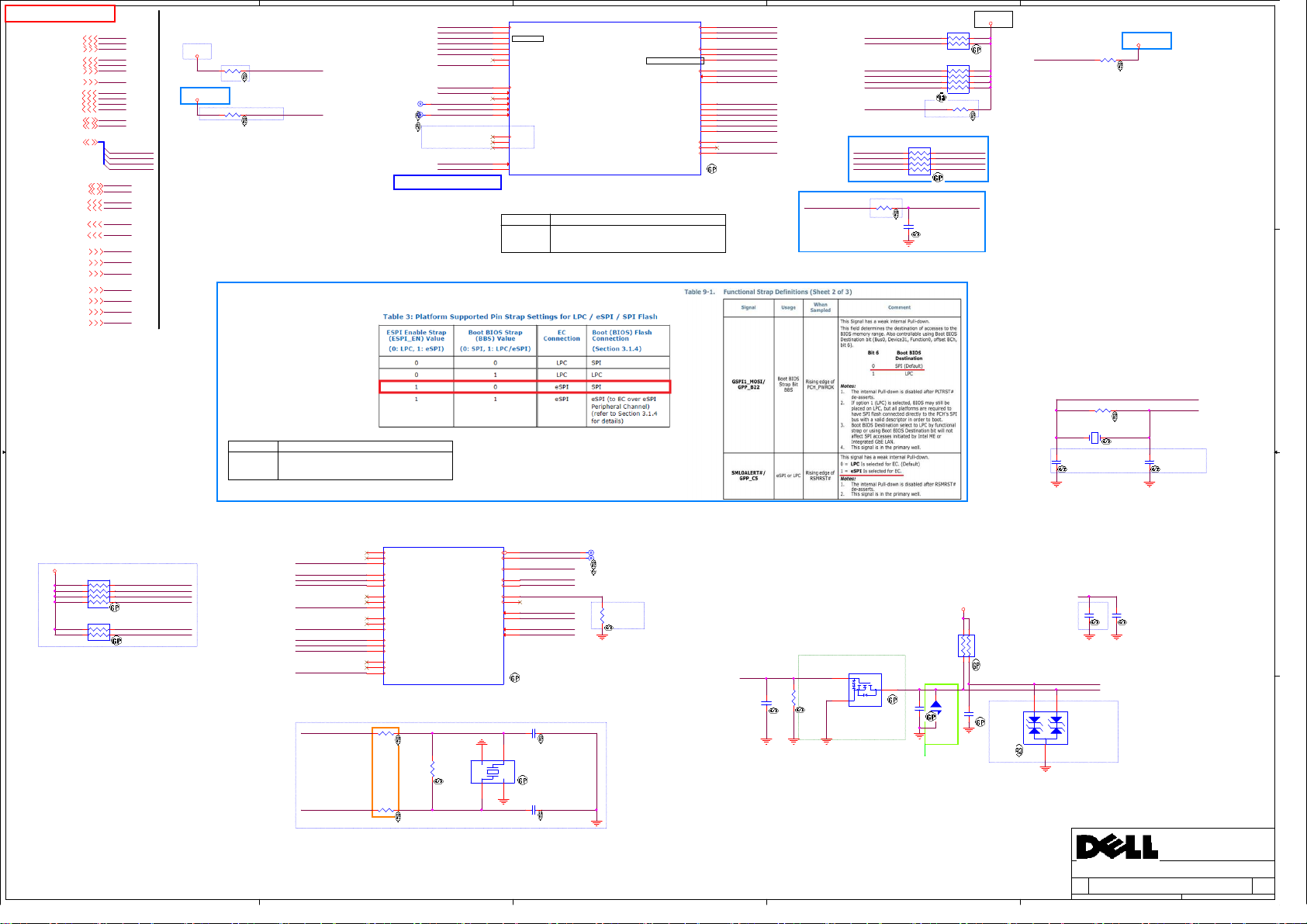

(#543016) PROCHOT# Routing Guidelines

1V_VCCSTG

Rb

PROCHOT#_CPU

[PECI] and [PROCHOT#]

Impedance control: 50 ohm

3D3V_S5_PCH

1

R303

Do Not Stuff

DY

TP_WAKE_KBC#

2

1

R301

1KR2J-1-GP

2

R302 499R2F-2-GP

Ra

1

R304 49D9R2F-GP

R305 49D9R2F-GP

2

TP309Do Not Stuff

TP302Do Not Stuff

TP303Do Not Stuff

TP304Do Not Stuff

TP307Do Not Stuff

TP308Do Not Stuff

1

1

2

2

TP301

Do Not Stuff

1

1

1

1

1

1

1

CATERR#_CPU

PECI_CPU

PROCHOT#_CPU_R

THERMTRIP#_CPU

BPM_CPU_N0

BPM_CPU_N1

BPM_CPU_N2

BPM_CPU_N3

GPP_E3/CPU_GP0

TOUCH_PANEL_INTR#

TOUCH_PANEL_PD#

CPU_POPIRCOMP

PCH_POPIRCOMP

20180412 Follow RO

XDP_TDO_CPU

XDP_TCLK

CPU1D

AA4

CATERR#

AR1

PECI

Y4

PROCHOT#

BJ1

THRMTRIP#

U1

BPM#0

U2

BPM#1

U3

BPM#2

U4

BPM#3

CE9

GPP_E3/CPU_GP0

CN3

GPP_E7/CPU_GP1

CB34

GPP_B3/CPU_GP2

CC35

GPP_B4/CPU_GP3

BP27

PROC_POPIRCOMP

BW25

PCH_OPIRCOMP

WHISKEY-LAKE-GP

1

R310 51R2J-2-GP

1

R317 51R2J-2-GP

2

2

PROC_PREQ#

PROC_PRDY#

1V_VCCSTG

4 OF 20

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_TRST#

PCH_JTAGX

20180412 Follow RO13

T6

U6

Y5

T5

AB6

W6

U5

W5

P5

Y6

P6

XDP_PREQ#

W2

XDP_PRDY#

W1

XDP_TCLK

XDP_TDI

XDP_TDO_CPU

XDP_TMS

XDP_TRST#

PCH_JTAG_TCK

1V_VCCST_CPU

#544669 CRB Rev0.52

1

R308

1KR2J-1-GP

1

TP311 Do Not Stuff

1

TP313 Do Not Stuff

1

TP314 Do Not Stuff

1

TP315 Do Not Stuff

1

TP305 Do Not Stuff

1

TP306 Do Not Stuff

D

C

B

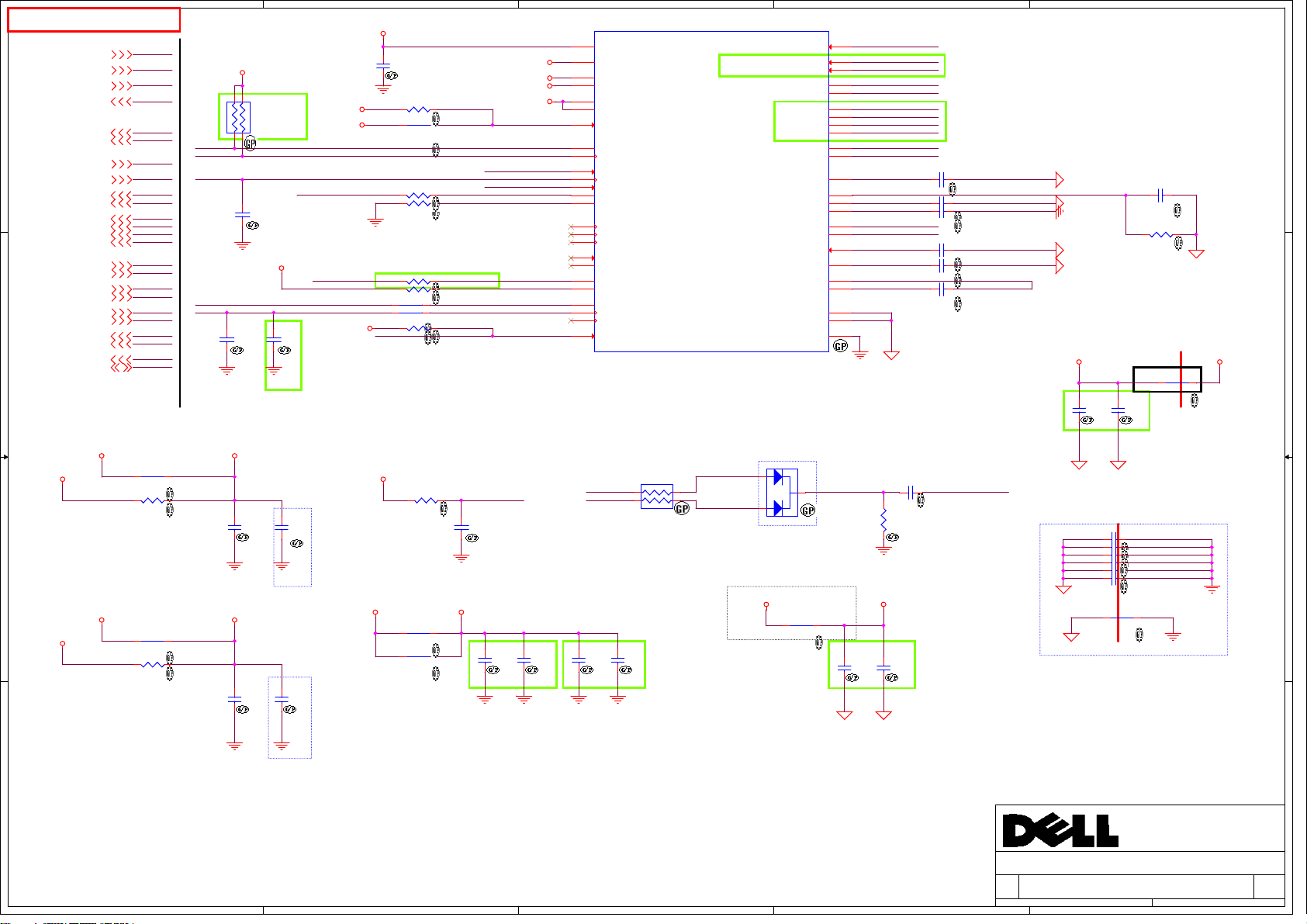

M1,2,3,4,5: <3 inches

M6: 1-11 inches

MCPU: 0.3-1.5 inches

Mt <0.3 mils

A

Main route(M1+M2+M3+M4+M5+M6+MCPU): 1-12 inches

5

THERMTRIP#_CPU

H_CPUPWRGD

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

4

3

Date: Sheet

(Reserved)

(Reserved)

(Reserved)

2

KR CS MLK 13"

KR CS MLK 13"

KR CS MLK 13"

2

RO13_20171001

1

2

ED301

DY

3

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Do Not Stuff

Do Not Stuff

3 106Thursday, July 19, 2018

of

3 106Thursday, July 19, 2018

of

3 106Thursday, July 19, 2018

of

1

A00

A00

A00

B

A

5

4

3

2

1

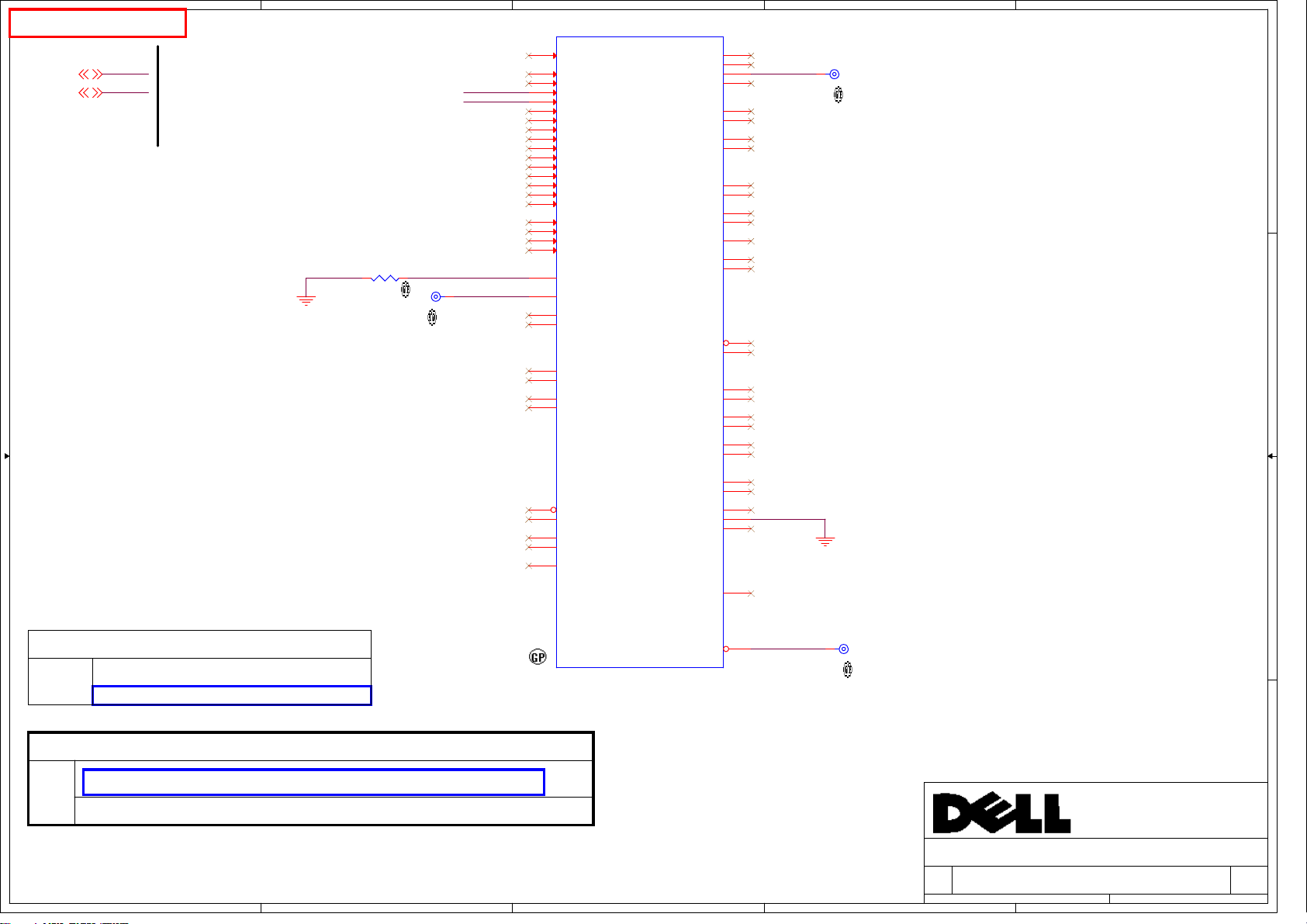

SSID = CPU

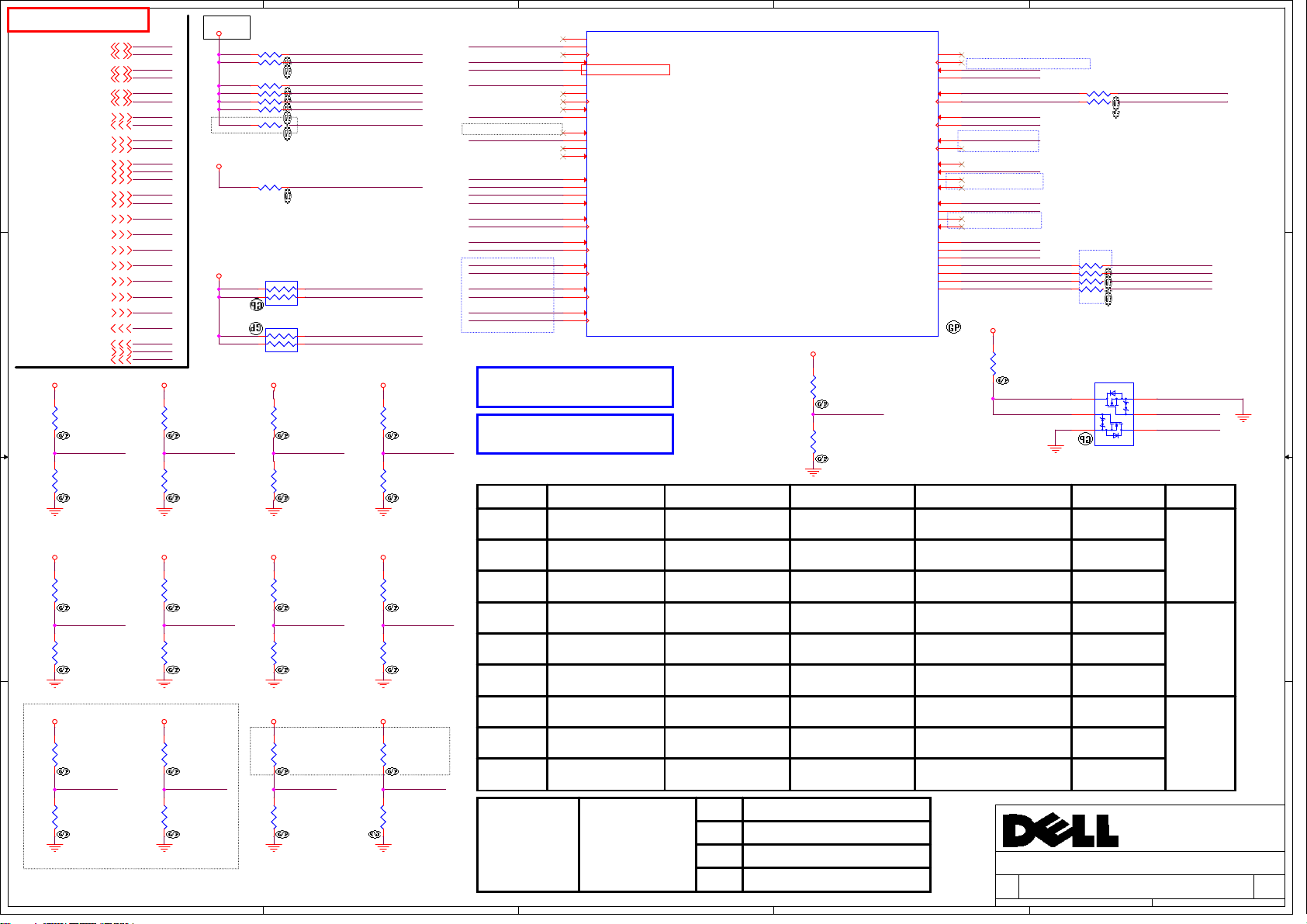

DP to HDMI2.0

HDMI_DDI_TX_N0[57]

HDMI_DDI_TX_P0[57]

HDMI_DDI_TX_N1[57]

HDMI_DDI_TX_P1[57]

D

HDMI_DDI_TX_N2[57]

HDMI_DDI_TX_P2[57]

HDMI_DDI_TX_N3[57]

HDMI_DDI_TX_P3[57]

DP1_AUX_CPU_N[57]

DP1_AUX_CPU_P[57]

HDMI_HPD_CPU[57]

DP for Type-C Mux

DP2_DDI_TX_N0[71]

DP2_DDI_TX_P0[71]

DP2_DDI_TX_N1[71]

DP2_DDI_TX_P1[71]

DP2_DDI_TX_N2[71]

C

DP2_DDI_TX_P2[71]

DP2_DDI_TX_N3[71]

DP2_DDI_TX_P3[71]

DP2_AUX_CPU_N[71]

DP2_AUX_CPU_P[71]

eDP_TX_CPU_N0[55]

eDP_TX_CPU_P0[55]

eDP_TX_CPU_N1[55]

eDP_TX_CPU_P1[55]

eDP_TX_CPU_N2[55]

eDP_TX_CPU_P2[55]

eDP_TX_CPU_N3[55]

eDP_TX_CPU_P3[55]

eDP_AUX_CPU_N[55]

eDP_AUX_CPU_P[55]

B

eDP_HPD_CPU[55]

DP1_HPD_CPU[71,72]

L_BKLT_EN[24]

L_BKLT_CTRL[55]

EDP_VDD_EN[55]

GPP_H17_STRAP[15]

3D3V_S0

RN401

1

2

SRN2K2J-1-GP

RN403

1

2

SRN2K2J-1-GP

1

R402

10KR2J-3-GP

Add RTC Gen 9 reset circuit_20170814

leakage issue

3D3V_S5_PCH

1

R406

10KR2J-3-GP

RTC_RST

2

CPU_DP_HPD_P

PCH side Device side

DP1_HPD_CPU_R

CPU_DP1_CTRL_DATA

4

CPU_DP1_CTRL_CLK

3

CPU_DP2_CTRL_CLK

4

CPU_DP2_CTRL_DATA

3

SIO_EXT_SMI#

2

Q401

1

2

RTC_RST

3

2N7002KDW-1-GP

75.27002.F7C

20170814

RTC Gen 9 reset circuit

NON_RTC_RST

1

R404

Do Not Stuff

1

R403

100KR2J-1-GP

2

3D3V_S5_PCH

Note:ZZ.27002.F7C01

6

5

4

2

1

R405

10KR2J-3-GP

RTC_RST

2

DP1_HPD_CPU_R

DP1_HPD_CPU

DP1_HPD_CPU

DP to HDMI2.0

DP for Type-C Mux

1V_VCCIO

(#543016) DDI Disabling and Termination Guidelines

Port Strap Enable Port Disable Port

Port 1

Port 2

DDPB_CTRLDATA

DDPC_CTRLDATA

PU to 3.3 V with 2.2-k

±5% resistor

PU to 3.3 V with 2.2-k

±5% resistor

NC

NC

HDMI_DDI_TX_N0

HDMI_DDI_TX_P0

HDMI_DDI_TX_N1

HDMI_DDI_TX_P1

HDMI_DDI_TX_N2

HDMI_DDI_TX_P2

HDMI_DDI_TX_N3

HDMI_DDI_TX_P3

DP2_DDI_TX_N0

DP2_DDI_TX_P0

DP2_DDI_TX_N1

DP2_DDI_TX_P1

DP2_DDI_TX_N2

DP2_DDI_TX_P2

DP2_DDI_TX_N3

DP2_DDI_TX_P3

CHECK WHL design guide: DISP_RCOMP

Design Guideline:

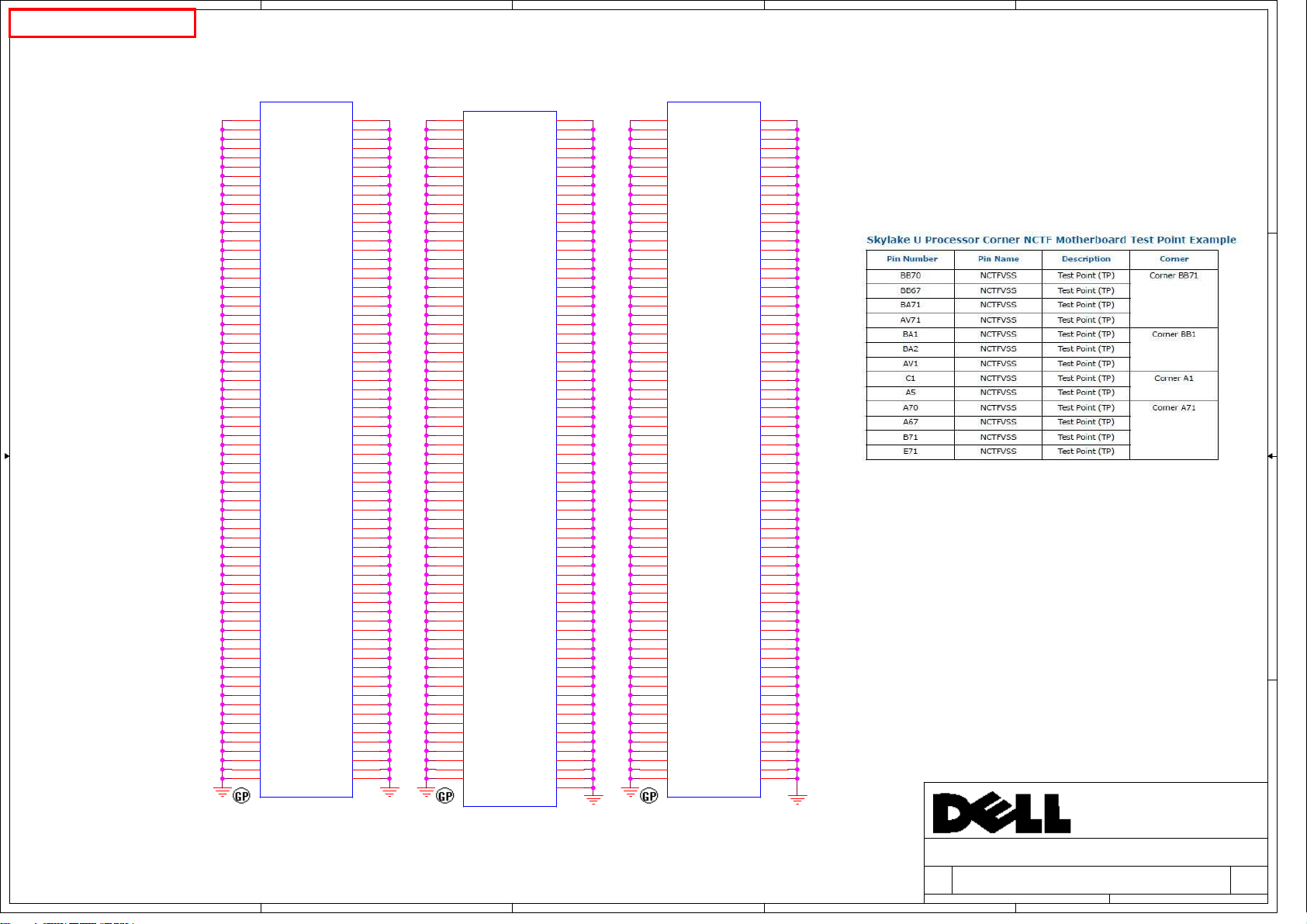

Skylake processor signal eDP_RCOMP

should be connected to the VCCIO

rail via a single 24.9 ±1% Ω resistor.

eDP_RCOMP_CPU

2

1

R401

24D9R2F-L-GP

TP402

Do Not Stuff

1

CPU_DP1_CTRL_CLK

CPU_DP1_CTRL_DATA

CPU_DP2_CTRL_CLK

CPU_DP2_CTRL_DATA

GPP_E23_STRAP

GPP_H17_STRAP

AL5

DDI1_TXN0

AL6

DDI1_TXP0

AJ5

DDI1_TXN1

AJ6

DDI1_TXP1

AF6

DDI1_TXN2

AF5

DDI1_TXP2

AE5

DDI1_TXN3

AE6

DDI1_TXP3

AC4

DDI2_TXN0

AC3

DDI2_TXP0

AC1

DDI2_TXN1

AC2

DDI2_TXP1

AE4

DDI2_TXN2

AE3

DDI2_TXP2

AE1

DDI2_TXN3

AE2

DDI2_TXP3

AM6

DISP_RCOMP

CC8

GPP_E18/DPPB_CTRLCLK/CNV_BT_HOST_WAKE#

CC9

GPP_E19/DPPB_CTRLDATA

CH4

GPP_E20/DPPC_CTRLCLK

CH3

GPP_E21/DPPC_CTRLDATA

CP4

GPP_E22/DPPD_CTRLCLK

CN4

GPP_E23/DPPD_CTRLDATA

CR26

GPP_H16/DDPF_CTRLCLK

CP26

GPP_H17/DDPF_CTRLDATA

WHISKEY-LAKE-GP

(#543016) eDP_RCOMP Guideline

Signal Trace

Width

eDP_RCOMP 20 mils 25 mils 24.9 Ω ±1%

Isolation

Spacing

1 OF 20CPU1A

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUX_N

EDP_AUX_P

DISP_UTILS

DDI1_AUX_N

DDI1_AUX_P

DDI2_AUX_N

DDI2_AUX_P

DDI3_AUX_N

DDI3_AUX_P

GPP_E13/DDPB_HPD0/DISP_MISC0

GPP_E14/DDPC_HPD1/DISP_MISC1

GPP_E15/DPPD_HPD2/DISP_MISC2

GPP_E16/DPPE_HPD3/DISP_MISC3

GPP_E17/EDP_HPD/DISP_MISC4

EDP_BKLTEN

EDP_VDDEN

EDP_BKLTCTL

Resistor

Value

Length

Max = 100 mils

AG4

AG3

AG2

AG1

AJ4

AJ3

AJ2

AJ1

AH4

AH3

AM7

AC7

AC6

AD4

AD3

AG7

AG6

CN6

CM6

CP7

CP6

CM7

CK11

CG11

CH11

eDP_TX_CPU_N0

eDP_TX_CPU_P0

eDP_TX_CPU_N1

eDP_TX_CPU_P1

eDP_TX_CPU_N2

eDP_TX_CPU_P2

eDP_TX_CPU_N3

eDP_TX_CPU_P3

eDP_AUX_CPU_N

eDP_AUX_CPU_P

DP1_AUX_CPU_N

DP1_AUX_CPU_P

DP2_AUX_CPU_N

DP2_AUX_CPU_P

HDMI_HPD_CPU

DP1_HPD_CPU_R

SIO_EXT_SMI#

eDP_HPD_CPU

L_BKLT_EN

EDP_VDD_EN

L_BKLT_CTRL

20180208

Follow RO NC

for HDMI2.0

for Type-C Mux

D

C

B

<Core Design>

<Core Design>

<Core Design>

A00

A00

A00

A

A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

5

4

3

2

CPU_(JTAG/CPU SIDE BAND)

CPU_(JTAG/CPU SIDE BAND)

CPU_(JTAG/CPU SIDE BAND)

Custom

Custom

Custom

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

KR CS MLK 13"

KR CS MLK 13"

KR CS MLK 13"

4 106Thursday, July 19, 2018

4 106Thursday, July 19, 2018

4 106Thursday, July 19, 2018

1

of

of

of

SSID = CPU

M_A_DQS_DN[7: 0][12]

M_A_DQS_DP[7:0][12]

D

M_A_DQ[0:7]

M_A_DQ[8:15]

M_A_DQ[16:23]

M_A_DQ[24:31]

C

M_A_DQ[32:39]

M_A_DQ[40:47]

M_A_DQ[48:55]

M_A_DQ[56:63]

M_B_CLK#0[13]

M_B_CLK0[13]

M_B_CKE0[13]

M_B_CS#0[13]

M_B_ODT0[13]

B

M_B_ACT_N[13]

M_B_BG0[13]

M_B_BG1[13]

M_B_BA0[13]

M_B_BA1[13]

M_B_ALERT_N[13]

M_B_PARITY[13]

V_SM_VREF_CN TA[12]

V_SM_VREF_CN TB[13]

VTT_CNTL[51]

SM_DRAMRST #[12,13]

1D2V_S3

1

R505

470R2F-GP

2

1

R504

Do Not Stuff

D

C

SM_DRAMRST #

2

1

1

C501

DY

Do Not Stuff

2

B

2

CPU1C

DDR1_DQ0/DDR0_DQ16

DDR1_DQ1/DDR0_DQ17

DDR1_DQ2/DDR0_DQ18

DDR1_DQ3/DDR0_DQ19

DDR1_DQ4/DDR0_DQ20

DDR1_DQ5/DDR0_DQ21

DDR1_DQ6/DDR0_DQ22

DDR1_DQ7/DDR0_DQ23

DDR1_DQ8/DDR0_DQ24

DDR1_DQ9/DDR0_DQ25

DDR1_DQ10/DDR0_DQ26

DDR1_DQ11/DDR0_DQ27

DDR1_DQ12/DDR0_DQ28

DDR1_DQ13/DDR0_DQ29

DDR1_DQ14/DDR0_DQ30

DDR1_DQ15/DDR0_DQ31

DDR1_DQ16/DDR0_DQ48

DDR1_DQ17/DDR0_DQ49

DDR1_DQ18/DDR0_DQ50

DDR1_DQ19/DDR0_DQ51

DDR1_DQ20/DDR0_DQ52

DDR1_DQ21/DDR0_DQ53

DDR1_DQ22/DDR0_DQ54

DDR1_DQ23/DDR0_DQ55

DDR1_DQ24/DDR0_DQ56

DDR1_DQ25/DDR0_DQ57

DDR1_DQ26/DDR0_DQ58

DDR1_DQ27/DDR0_DQ59

DDR1_DQ28/DDR0_DQ60

DDR1_DQ29/DDR0_DQ61

DDR1_DQ30/DDR0_DQ62

DDR1_DQ31/DDR0_DQ63

DDR1_DQ32/DDR1_DQ16

DDR1_DQ33/DDR1_DQ17

DDR1_DQ34/DDR1_DQ18

DDR1_DQ35/DDR1_DQ19

DDR1_DQ36/DDR1_DQ20

DDR1_DQ37/DDR1_DQ21

DDR1_DQ38/DDR1_DQ22

DDR1_DQ39/DDR1_DQ23

DDR1_DQ40/DDR1_DQ24

DDR1_DQ41/DDR1_DQ25

DDR1_DQ42/DDR1_DQ26

DDR1_DQ43/DDR1_DQ27

DDR1_DQ44/DDR1_DQ28

DDR1_DQ45/DDR1_DQ29

DDR1_DQ46/DDR1_DQ30

DDR1_DQ47/DDR1_DQ31

DDR1_DQ48/DDR1_DQ48

DDR1_DQ49/DDR1_DQ49

DDR1_DQ50/DDR1_DQ50

DDR1_DQ51/DDR1_DQ51

DDR1_DQ52/DDR1_DQ52

DDR1_DQ53/DDR1_DQ53

DDR1_DQ54/DDR1_DQ54

DDR1_DQ55/DDR1_DQ55

DDR1_DQ56/DDR1_DQ56

DDR1_DQ57/DDR1_DQ57

DDR1_DQ58/DDR1_DQ58

DDR1_DQ59/DDR1_DQ59

DDR1_DQ60/DDR1_DQ60

DDR1_DQ61/DDR1_DQ61

DDR1_DQ62/DDR1_DQ62

DDR1_DQ63/DDR1_DQ63

WHISKEY-LAKE- GP

20180409 Follow RO13

SM_PGCNTL

3 OF 20

DDR1_CKN0/DDR1_CKN0

DDR1_CKP0/DDR1_CKP0

DDR1_CKN1/DDR1_CKN1

DDR1_CKP1/DDR1_CKP1

DDR1_CKE0/DDR1_CKE0

DDR1_CKE1/DDR1_CKE1

DDR1_CKE2/NC

DDR1_CKE3/NC

DDR1_CS#0/DDR1_CS#0

DDR1_CS#1/DDR1_CS#1

DDR1_ODT0/DDR1_ODT0

NC/DDR1_ODT1

DDR1_CAB9/DDR1_MA0

DDR1_CAB8/DDR1_MA1

DDR1_CAB5/DDR1_MA2

NC/DDR1_MA3

NC/DDR1_MA4

DDR1_CAA0/DDR1_MA5

DDR1_CAA2/DDR1_MA6

DDR1_CAA4/DDR1_MA7

DDR1_CAA3/DDR1_MA8

DDR1_CAA1/DDR1_MA9

DDR1_CAB7/DDR1_MA10

DDR1_CAA7/DDR1_MA11

DDR1_CAA6/DDR1_MA12

DDR1_CAB0/DDR1_MA13

DDR1_CAB2/DDR1_MA14

DDR1_CAB1/DDR1_MA15

DDR1_CAB3/DDR1_MA16

DDR1_CAB4/DDR1_BA0

DDR1_CAB6/DDR1_BA1

DDR1_CAA5/DDR1_BG0

DDR1_CAA9/DDR1_BG1

DDR1_CAA8/DDR1_ACT#

DDR1_DQSN0/DDR0_DQSN2

DDR1_DQSP0/DDR0_DQSP2

DDR1_DQSN1/DDR0_DQSN3

DDR1_DQSP1/DDR0_DQSP3

DDR1_DQSN2/DDR0_DQSN6

DDR1_DQSP2/DDR0_DQSP6

DDR1_DQSN3/DDR0_DQSN7

DDR1_DQSP3/DDR0_DQSP7

DDR1_DQSN4/DDR1_DQSN2

DDR1_DQSP4/DDR1_DQSP2

DDR1_DQSN5/DDR1_DQSN3

DDR1_DQSP5/DDR1_DQSP3

DDR1_DQSN6/DDR1_DQSN6

DDR1_DQSP6/DDR1_DQSP6

DDR1_DQSN7/DDR1_DQSN7

DDR1_DQSP7/DDR1_DQSP7

NC/DDR1_ALERT#

NC/DDR1_PAR

DRAM_RESET#

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

3D3V_S5

Q501

G

PJA138KA-GP

D

S

084.00138.0A31

M_B_CLK#0

AF28

M_B_CLK0

AF29

AE28

AE29

M_B_CKE0

T28

T29

V28

V29

M_B_CS#0

AL37

AL35

M_B_ODT0

AL36

AL34

M_B_A0

AG36

M_B_A1

AG35

M_B_A2

AF34

M_B_A3

AG37

M_B_A4

AE35

M_B_A5

AF35

M_B_A6

AE37

M_B_A7

AC29

M_B_A8

AE36

M_B_A9

AB29

M_B_A10

AG34

M_B_A11

AC28

M_B_A12

AB28

M_B_A13

AK35

M_B_A14

AJ35

M_B_A15

AK34

M_B_A16

AJ34

M_B_BA0

AJ37

M_B_BA1

AJ36

M_B_BG0

W29

M_B_BG1

Y28

M_B_ACT_N

W28

M_A_DQS_DN2

H24

M_A_DQS_DP2

G24

M_A_DQS_DN3

C23

M_A_DQS_DP3

D23

M_A_DQS_DN6

G30

M_A_DQS_DP6

H30

M_A_DQS_DN7

L30

M_A_DQS_DP7

N30

M_B_DQS_DN2

AL31

M_B_DQS_DP2

AL30

M_B_DQS_DN3

AU31

M_B_DQS_DP3

AU30

M_B_DQS_DN6

BC31

M_B_DQS_DP6

BC30

M_B_DQS_DN7

BH31

M_B_DQS_DP7

BH30

M_B_ALERT_N

Y29

M_B_PARITY

AE34

SM_DRAMRST #_CPU

BU31

SM_RCOMP_0

BN28

SM_RCOMP_1

BN27

SM_RCOMP_2

BN29

R501 (RO13)(20170911)(DEL: R507)

DDP: 121 ohm (64.12105.6DL)

SDP: 200 ohm (64.20005.6DL)

1

R506

10KR2F-2-DL- GP

Q502_G

Q502

G

S

Notice:ZZ.2N70 2.J3101

2N7002K-2-GP

84.2N702.J31

2

M_A_DQS2

M_A_DQS3

M_A_DQS6

M_A_DQS7

M_B_DQS2

M_B_DQS3

M_B_DQS6

M_B_DQS7

2

1

R501 121R2F-GP

DDP/SDP

2

1

R502 80D6R2F-L-G P

2

1

R503 100R2F-L1-GP- U

Layout Note:

#543016

Design Guideline:

SM_RCOMP keep routing length less than 500 mils.

3D3V_S0

1

R507

10KR2F-2-DL- GP

2

VTT_CNTL

D

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

4

CPU1B

A26

DDR0_DQ0/DDR0_DQ0

D26

DDR0_DQ1/DDR0_DQ1

D28

DDR0_DQ2/DDR0_DQ2

C28

DDR0_DQ3/DDR0_DQ3

B26

DDR0_DQ4/DDR0_DQ4

C26

DDR0_DQ5/DDR0_DQ5

B28

DDR0_DQ6/DDR0_DQ6

A28

DDR0_DQ7/DDR0_DQ7

B30

DDR0_DQ8/DDR0_DQ8

D30

DDR0_DQ9/DDR0_DQ9

B33

DDR0_DQ10/DDR0_DQ10

D32

DDR0_DQ11/DDR0_DQ11

A30

DDR0_DQ12/DDR0_DQ12

C30

DDR0_DQ13/DDR0_DQ13

B32

DDR0_DQ14/DDR0_DQ14

C32

DDR0_DQ15/DDR0_DQ15

H37

DDR0_DQ16/DDR0_DQ32

H34

DDR0_DQ17/DDR0_DQ33

K34

DDR0_DQ18/DDR0_DQ34

K35

DDR0_DQ19/DDR0_DQ35

H36

DDR0_DQ20/DDR0_DQ36

H35

DDR0_DQ21/DDR0_DQ37

K36

DDR0_DQ22/DDR0_DQ38

K37

DDR0_DQ23/DDR0_DQ39

N36

DDR0_DQ24/DDR0_DQ40

N34

DDR0_DQ25/DDR0_DQ41

R37

DDR0_DQ26/DDR0_DQ42

R34

DDR0_DQ27/DDR0_DQ43

N37

DDR0_DQ28/DDR0_DQ44

N35

DDR0_DQ29/DDR0_DQ45

R36

DDR0_DQ30/DDR0_DQ46

R35

DDR0_DQ31/DDR0_DQ47

AN35

DDR0_DQ32/DDR1_DQ0

AN34

DDR0_DQ33/DDR1_DQ1

AR35

DDR0_DQ34/DDR1_DQ2

AR34

DDR0_DQ35/DDR1_DQ3

AN37

DDR0_DQ36/DDR1_DQ4

AN36

DDR0_DQ37/DDR1_DQ5

AR36

DDR0_DQ38/DDR1_DQ6

AR37

DDR0_DQ39/DDR1_DQ7

AU35

DDR0_DQ40/DDR1_DQ8

AU34

DDR0_DQ41/DDR1_DQ9

AW35

DDR0_DQ42/DDR1_DQ10

AW34

DDR0_DQ43/DDR1_DQ11

AU37

DDR0_DQ44/DDR1_DQ12

AU36

DDR0_DQ45/DDR1_DQ13

AW36

DDR0_DQ46/DDR1_DQ14

AW37

DDR0_DQ47/DDR1_DQ15

BA35

DDR0_DQ48/DDR1_DQ32

BA34

DDR0_DQ49/DDR1_DQ33

BC35

DDR0_DQ50/DDR1_DQ34

BC34

DDR0_DQ51/DDR1_DQ35

BA37

DDR0_DQ52/DDR1_DQ36

BA36

DDR0_DQ53/DDR1_DQ37

BC36

DDR0_DQ54/DDR1_DQ38

BC37

DDR0_DQ55/DDR1_DQ39

BE35

DDR0_DQ56/DDR1_DQ40

BE34

DDR0_DQ57/DDR1_DQ41

BG35

DDR0_DQ58/DDR1_DQ42

BG34

DDR0_DQ59/DDR1_DQ43

BE37

DDR0_DQ60/DDR1_DQ44

BE36

DDR0_DQ61/DDR1_DQ45

BG36

DDR0_DQ62/DDR1_DQ46

BG37

DDR0_DQ63/DDR1_DQ47

WHISKEY-LAKE- GP

DDR4 ball type: Non-Interleaved Type

2 OF 20

DDR0_CKE2/NC

DDR0_CKE3/NC

NC/DDR0_ODT1

NC/DDR0_MA3

NC/DDR0_MA4

NC/DDR0_PAR

DDR_VREF_CA

DDR_VTT_CTL

V32

V31

T32

T31

U36

U37

U34

U35

AE32

AF32

AE31

AF31

AC37

AC36

AC34

AC35

AA35

AB35

AA37

AA36

AB34

W36

Y31

W34

AA34

AC32

AC31

AB32

Y32

W32

AB31

V34

V35

W35

C27

D27

D31

C31

J35

J34

P34

P35

AP35

AP34

AV34

AV35

BB35

BB34

BF34

BF35

W37

W31

F36

D35

D37

E36

C35

DDR0_CKN0/DDR0_CKN0

DDR0_CKP0/DDR0_CKP0

DDR0_CKN1/DDR0_CKN1

DDR0_CKP1/DDR0_CKP1

DDR0_CKE0/DDR0_CKE0

DDR0_CKE1/DDR0_CKE1

DDR0_CS#0/DDR0_CS#0

DDR0_CS#1/DDR0_CS#1

DDR0_ODT0/DDR0_ODT0

DDR0_CAB9/DDR0_MA0

DDR0_CAB8/DDR0_MA1

DDR0_CAB5/DDR0_MA2

DDR0_CAA0/DDR0_MA5

DDR0_CAA2/DDR0_MA6

DDR0_CAA4/DDR0_MA7

DDR0_CAA3/DDR0_MA8

DDR0_CAA1/DDR0_MA9

DDR0_CAB7/DDR0_MA10

DDR0_CAA7/DDR0_MA11

DDR0_CAA6/DDR0_MA12

DDR0_CAB0/DDR0_MA13

DDR0_CAB2/DDR0_MA14

DDR0_CAB1/DDR0_MA15

DDR0_CAB3/DDR0_MA16

DDR0_CAB4/DDR0_BA0

DDR0_CAB6/DDR0_BA1

DDR0_CAA5/DDR0_BG0

DDR0_CAA8/DDR0_ACT#

DDR0_CAA9/DDR0_BG1

DDR0_DQSN0/DDR0_DQSN0

DDR0_DQSP0/DDR0_DQSP0

DDR0_DQSN1/DDR0_DQSN1

DDR0_DQSP1/DDR0_DQSP1

DDR0_DQSN2/DDR0_DQSN4

DDR0_DQSP2/DDR0_DQSP4

DDR0_DQSN3/DDR0_DQSN5

DDR0_DQSP3/DDR0_DQSP5

DDR0_DQSN4/DDR1_DQSN0

DDR0_DQSP4/DDR1_DQSP0

DDR0_DQSN5/DDR1_DQSN1

DDR0_DQSP5/DDR1_DQSP1

DDR0_DQSN6/DDR1_DQSN4

DDR0_DQSP6/DDR1_DQSP4

DDR0_DQSN7/DDR1_DQSN5

DDR0_DQSP7/DDR1_DQSP5

NC/DDR0_ALERT#

DDR0_VREF_DQ0

DDR0_VREF_DQ1

DDR1_VREF_DQ

5

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

M_A_DQ0[12]

M_A_DQ1[12]

M_A_DQ2[12]

M_A_DQ3[12]

M_A_DQ4[12]

M_A_DQ5[12]

M_A_DQ6[12]

M_A_DQ7[12]

M_A_DQ8[12]

M_A_DQ9[12]

M_A_DQ10[12]

M_A_DQ11[12]

M_A_DQ12[12]

M_A_DQ13[12]

M_A_DQ14[12]

M_A_DQ15[12]

M_A_DQ16[12]

M_A_DQ17[12]

M_A_DQ18[12]

M_A_DQ19[12]

M_A_DQ20[12]

M_A_DQ21[12]

M_A_DQ22[12]

M_A_DQ23[12]

M_A_DQ24[12]

M_A_DQ25[12]

M_A_DQ26[12]

M_A_DQ27[12]

M_A_DQ28[12]

M_A_DQ29[12]

M_A_DQ30[12]

M_A_DQ31[12]

M_A_DQ32[12]

M_A_DQ33[12]

M_A_DQ34[12]

M_A_DQ35[12]

M_A_DQ36[12]

M_A_DQ37[12]

M_A_DQ38[12]

M_A_DQ39[12]

M_A_DQ40[12]

M_A_DQ41[12]

M_A_DQ42[12]

M_A_DQ43[12]

M_A_DQ44[12]

M_A_DQ45[12]

M_A_DQ46[12]

M_A_DQ47[12]

M_A_DQ48[12]

M_A_DQ49[12]

M_A_DQ50[12]

M_A_DQ51[12]

M_A_DQ52[12]

M_A_DQ53[12]

M_A_DQ54[12]

M_A_DQ55[12]

M_A_DQ56[12]

M_A_DQ57[12]

M_A_DQ58[12]

M_A_DQ59[12]

M_A_DQ60[12]

M_A_DQ61[12]

M_A_DQ62[12]

M_A_DQ63[12]

M_B_A0[13]

M_B_A1[13]

M_B_A2[13]

M_B_A3[13]

M_B_A4[13]

M_B_A5[13]

M_B_A6[13]

M_B_A7[13]

M_B_A8[13]

M_B_A9[13]

M_B_A10[13]

M_B_A11[13]

M_B_A12[13]

M_B_A13[13]

M_B_A14[13]

M_B_A15[13]

M_B_A16[13]

M_B_DQS_DN[7: 0][13]

M_B_DQS_DP[7:0][13]

M_A_CLK#0[12]

M_A_CLK0[12]

M_A_CKE0[12]

M_A_CS#0[12]

M_A_ODT0[12]

M_A_ACT_N[12]

M_A_BG0[12]

M_A_BG1[12]

M_A_BA0[12]

M_A_BA1[12]

M_A_ALERT_N[12]

M_A_PARITY[12]

M_A_A0[12]

M_A_A1[12]

M_A_A2[12]

M_A_A3[12]

M_A_A4[12]

M_A_A5[12]

M_A_A6[12]

M_A_A7[12]

M_A_A8[12]

M_A_A9[12]

M_A_A10[12]

M_A_A11[12]

M_A_A12[12]

M_A_A13[12]

M_A_A14[12]

M_A_A15[12]

M_A_A16[12]

M_B_DQS_DN0

M_B_DQS_DN1

M_B_DQS_DN2

M_B_DQS_DN3

M_B_DQS_DN4

M_B_DQS_DN5

M_B_DQS_DN6

M_B_DQS_DN7

M_B_DQS_DP0

M_B_DQS_DP1

M_B_DQS_DP2

M_B_DQS_DP3

M_B_DQS_DP4

M_B_DQS_DP5

M_B_DQS_DP6

M_B_DQS_DP7

M_B_DQ0[13]

M_B_DQ1[13]

M_B_DQ2[13]

M_B_DQ3[13]

M_B_DQ4[13]

M_B_DQ5[13]

M_B_DQ6[13]

M_B_DQ7[13]

M_B_DQ8[13]

M_B_DQ9[13]

M_B_DQ10[13]

M_B_DQ11[13]

M_B_DQ12[13]

M_B_DQ13[13]

M_B_DQ14[13]

M_B_DQ15[13]

M_B_DQ16[13]

M_B_DQ17[13]

M_B_DQ18[13]

M_B_DQ19[13]

M_B_DQ20[13]

M_B_DQ21[13]

M_B_DQ22[13]

M_B_DQ23[13]

M_B_DQ24[13]

M_B_DQ25[13]

M_B_DQ26[13]

M_B_DQ27[13]

M_B_DQ28[13]

M_B_DQ29[13]

M_B_DQ30[13]

M_B_DQ31[13]

M_B_DQ32[13]

M_B_DQ33[13]

M_B_DQ34[13]

M_B_DQ35[13]

M_B_DQ36[13]

M_B_DQ37[13]

M_B_DQ38[13]

M_B_DQ39[13]

M_B_DQ40[13]

M_B_DQ41[13]

M_B_DQ42[13]

M_B_DQ43[13]

M_B_DQ44[13]

M_B_DQ45[13]

M_B_DQ46[13]

M_B_DQ47[13]

M_B_DQ48[13]

M_B_DQ49[13]

M_B_DQ50[13]

M_B_DQ51[13]

M_B_DQ52[13]

M_B_DQ53[13]

M_B_DQ54[13]

M_B_DQ55[13]

M_B_DQ56[13]

M_B_DQ57[13]

M_B_DQ58[13]

M_B_DQ59[13]

M_B_DQ60[13]

M_B_DQ61[13]

M_B_DQ62[13]

M_B_DQ63[13]

M_A_DQ[0:7]

M_A_DQ[8:15]

M_A_DQ[32:39]

M_A_DQ[40:47]

M_B_DQ[0:7]

M_B_DQ[8:15]

M_B_DQ[32:39]

M_B_DQ[40:47]

DQ Bit Swapping is allowed within the same byte, and Byte Swapping is allowed within the same channel.

Clock (CLK and CLK#) and Strobe (DQS and DQS#) differential signal swapping within a pair is not allowed. Also differential

clock pair to clock pair swapping within a channel is not allowed.

M_A_CLK#0

M_A_CLK0

M_A_CKE0

M_A_CS#0

M_A_ODT0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_A16

M_A_BA0

M_A_BA1

M_A_BG0

M_A_ACT_N

M_A_BG1

M_A_DQS_DN0

M_A_DQS_DP0

M_A_DQS_DN1

M_A_DQS_DP1

M_A_DQS_DN4

M_A_DQS_DP4

M_A_DQS_DN5

M_A_DQS_DP5

M_B_DQS_DN0

M_B_DQS_DP0

M_B_DQS_DN1

M_B_DQS_DP1

M_B_DQS_DN4

M_B_DQS_DP4

M_B_DQS_DN5

M_B_DQS_DP5

M_A_ALERT_N

M_A_PARITY

V_SM_VREF_CN TA

V_SM_VREF_CN TB

SM_PGCNTL

3

M_A_DQS0

M_A_DQS1

M_A_DQS4

M_A_DQS5

M_B_DQS0

M_B_DQS1

M_B_DQS4

M_B_DQS5

M_A_DQ[16:23]

M_A_DQ[24:31]

M_A_DQ[48:55]

M_A_DQ[56:63]

M_B_DQ[16:23]

M_B_DQ[24:31]

M_B_DQ[48:55]

M_B_DQ[56:63]

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AJ29

AJ30

AM32

AM31

AM30

AM29

AJ31

AJ32

AR31

AR32

AV30

AV29

AR30

AR29

AV32

AV31

BA32

BA31

BD31

BD32

BA30

BA29

BD29

BD30

BG31

BG32

BK32

BK31

BG29

BG30

BK30

BK29

J22

H25

G22

H22

F25

J25

G25

F22

D22

C22

C24

D24

A22

B22

A24

B24

G31

G32

H29

H28

G28

G29

H31

H32

L31

L32

N29

N28

L28

L29

N31

N32

A00

A00

A00

A

A

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

Taipei Hsie n 221, Taiwan, R.O.C .

Taipei Hsie n 221, Taiwan, R.O.C .

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Taipei Hsie n 221, Taiwan, R.O.C .

CPU_(DDR)

CPU_(DDR)

CPU_(DDR)

KR CS MLK 13"

KR CS MLK 13"

KR CS MLK 13"

1

5 106Thursday, July 19, 2018

of

5 106Thursday, July 19, 2018

of

5 106Thursday, July 19, 2018

of

5

SSID = CPU

CFG3[15]

CFG4[15]

D

C

B

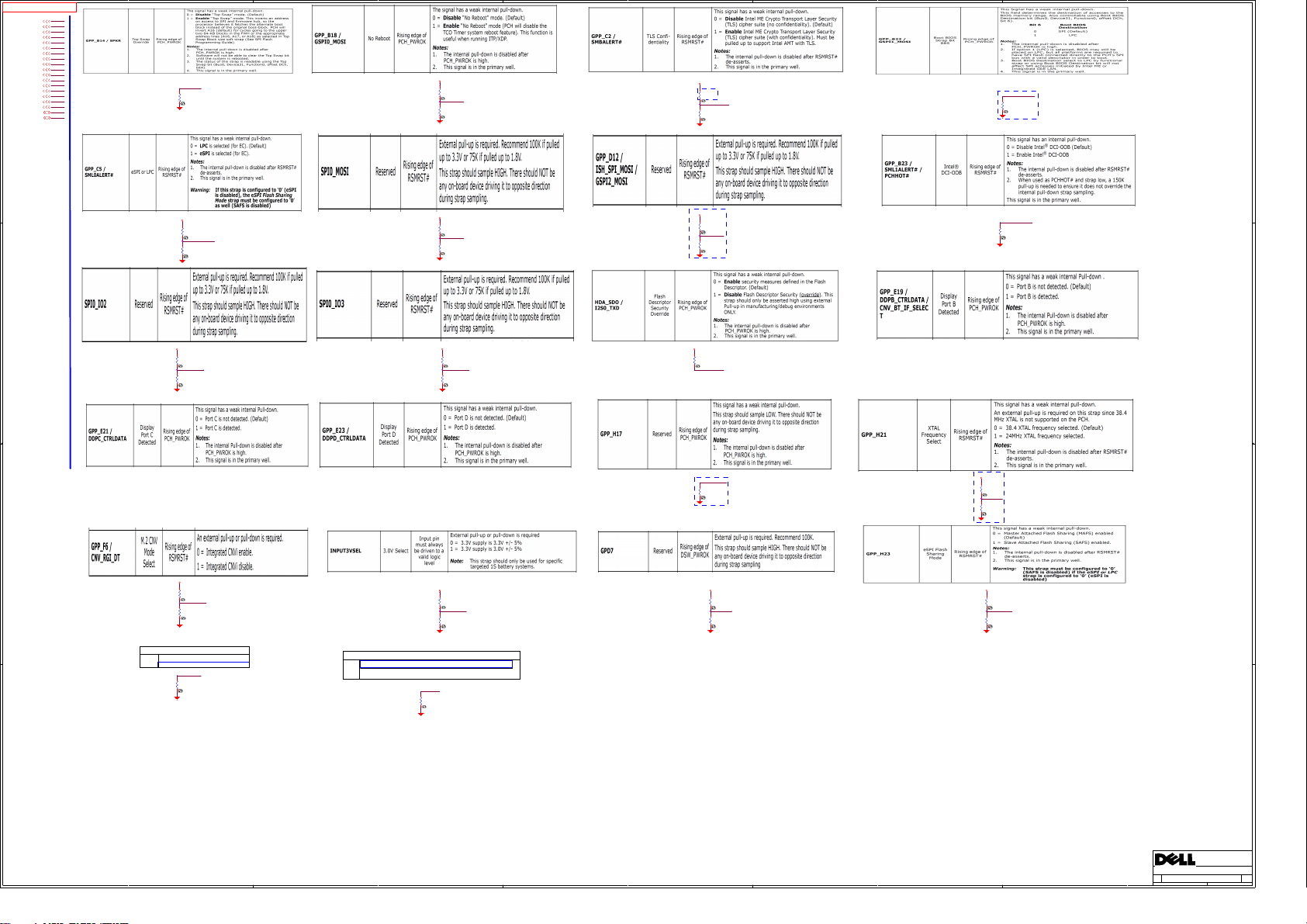

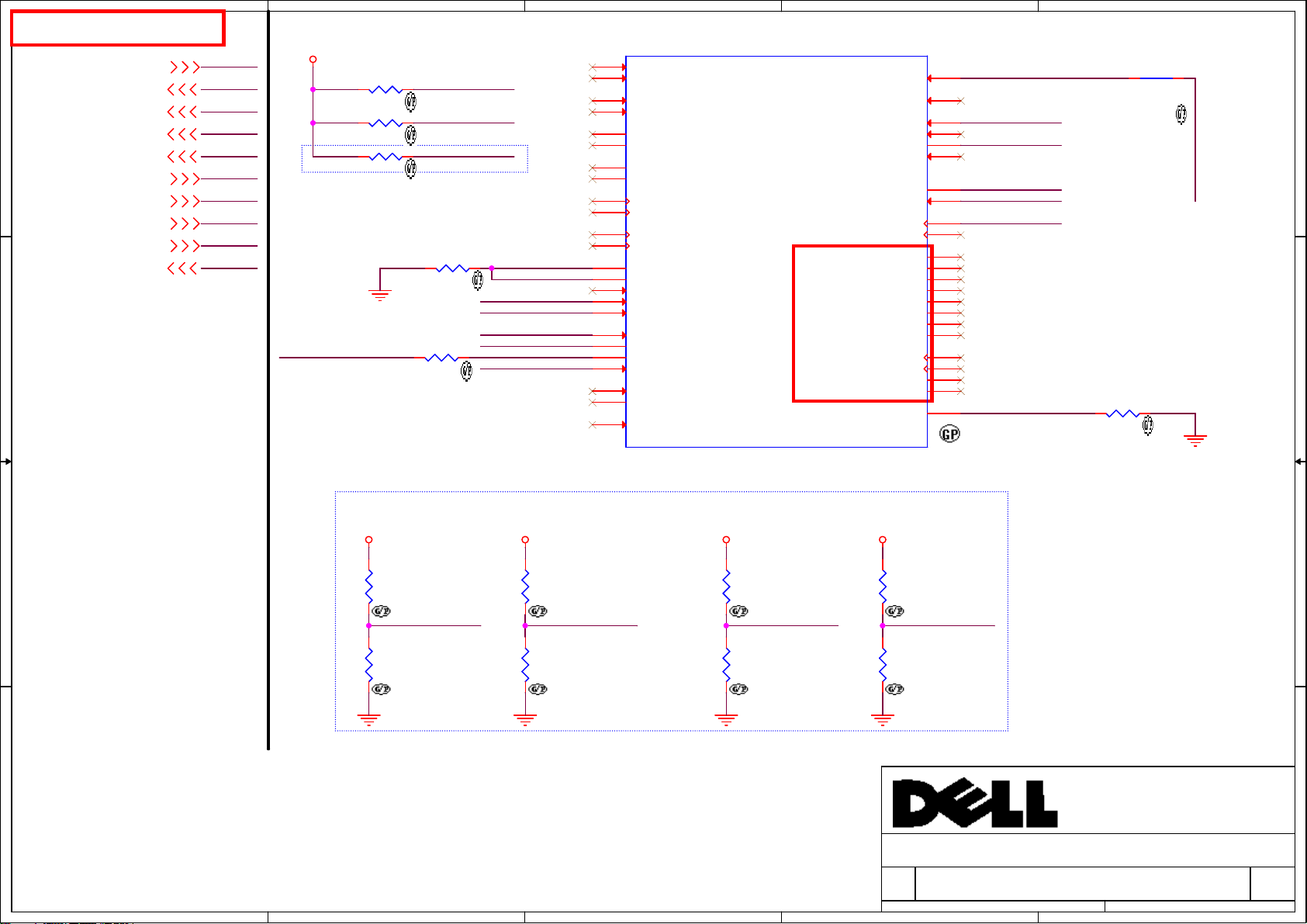

PCH strap pin:

CFG3 CFG4

[BDW Only]PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

CFG[3]

(#543016)

SKL(#543016):

Processor strap CFG[4] should be pulled low to enable embedded DisplayPort*

DISPLAY PORT PRESENCE STRAP

CFG[4]

A

0 : ENABLED

SET DFX ENABLED BIT IN DEBUG INTERFACE MSR

1 : DISABLED

0 : ENABLED

An external Display Port device is connected to the Embedded Display Port.

1 : DISABLED (Default)

No Physical Display Port attached to Embedded DisplayPort*. No connect for disable.

5

4

2

1

R601 49D9R2F-GP

TP618Do Not Stuff

4

1

CFG3

CFG4

CFG_RCOMP

ITP_PMODE

T4

CFG0

R4

CFG1

T3

CFG2

R3

CFG3

J4

CFG4

M4

CFG5

J3

CFG6

M3

CFG7

R2

CFG8

N2

CFG9

R1

CFG10

N1

CFG11

J2

CFG12

L2

CFG13

J1

CFG14

L1

CFG15

L3

CFG16

N3

CFG18

L4

CFG17

N4

CFG19

AB5

CFG_RCOMP

W4

ITP_PMODE

CG2

RSVD#CG2

CG1

RSVD#CG1

H4

RSVD#H4

H3

RSVD#H3

BV24

RSVD#BV24

BV25

RSVD#BV25

BK36

RSVD#BK36

BK35

RSVD#BK35

W3

RSVD#W3

AM4

RSVD#AM4

AM3

RSVD_TP#AM3

WHISKEY-LAKE-GP

3

WHL QS/CFL/WHL_ES1_CNL U

RSVD_TP#F37

RSVD_TP#F34

RSVD_TP#CN36

RSVD_TP#BJ36

RSVD_TP#BJ34

RSVD_TP#BT9

RSVD_TP#BT8

RSVD_TP#BP8

RSVD_TP#BP9

RSVD#CR4

RSVD#CP3

RSVD#CR3

RSVD_TP#AT3

RSVD_TP#AU3

RSVD#AN1

RSVD#AN2

RSVD#AN4

RSVD#AN3

RSVD_TP#CR35

3

17 OF 20CPU1Q

IST_TRIG

TP#BK34

TP#BR18

IST_TP0

IST_TP1

IST_TRIG0

IST_TRIG1

TP#BP34

VSS

TP#BP35

SKTOCC#

F37

F34

CP36

CN36

BJ36

BJ34

BK34

BR18

BT9

BT8

BP8

BP9

CR4

CP3

CR3

AT3

AU3

AN1

AN2

AN4

AN3

AL2

AL1

AL4

AL3

BP34

BP36

BP35

CR35

E1

IST_TRIG

SKTOCC#

1

TP620 Do Not Stuff

1

TP619 Do Not Stuff

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU_(RESERVED)

CPU_(RESERVED)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

2

CPU_(RESERVED)

KR CS MLK 13"

KR CS MLK 13"

KR CS MLK 13"

1

6 106Thursday, July 19, 2018

6 106Thursday, July 19, 2018

6 106Thursday, July 19, 2018

1

D

C

B

A

A00

A00

of

of

of

A00

5

SSID = CPU

VCCCORE_SENSE[46]

D

C

B

VSSCORE_SENSE[46]

SVID_CLK_CPU[46]

SVID_ALERT#_CPU[46]

SVID_DATA_CPU[46]

1V_CPU_CORE

1

R719

100R2F-L1-GP-U

2

1

R720

100R2F-L1-GP-U

2

Layout Note:

1. Place close to CPU

2. VCC_SENSE/ VSS_SENSE

impedance=50 ohm

3. Length match<25mil

VCCCORE_SENSE

VSSCORE_SENSE

1V_CPU_CORE

AW10

AN9

AN10

AN24

AN26

AN27

AP2

AP9

AP24

AP26

AR5

AR6

AR7

AR8

AR10

AR25

AR27

AT9

AT24

AT26

AU5

AU6

AU7

AU8

AU9

AU24

AU25

AU26

AU27

AV2

AV5

AV7

AV10

AV27

AW5

AW6

AW7

AW8

AW9

BB9

BC24

AY9

BB24

4

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

RSVD#BB9

RSVD#BC24

RSVD#AY9

RSVD#BB24

12 OF 20CPU1L

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

RSVD#Y3

VCCSTG

1V_CPU_CORE

AW24

AW25

AW26

AW27

AY24

AY26

BA5

BA7

BA8

BA25

BA27

BB2

BB26

BC5

BC6

BC7

BC9

BC10

BC26

BC27

BD5

BD8

BD10

BD25

BD27

BE9

BE24

BE25

BE26

BE27

BF2

BF9

BF24

BF26

BG27

VCCCORE_SENSE

AN6

VSSCORE_SENSE

AN5

SVID_ALERT#_CPU_R

AA3

SVID_CLK_CPU_R

AA1

SVID_DATA_CPU_R

AA2

Y3

BG3

3

1V_VCCSTG

2

1

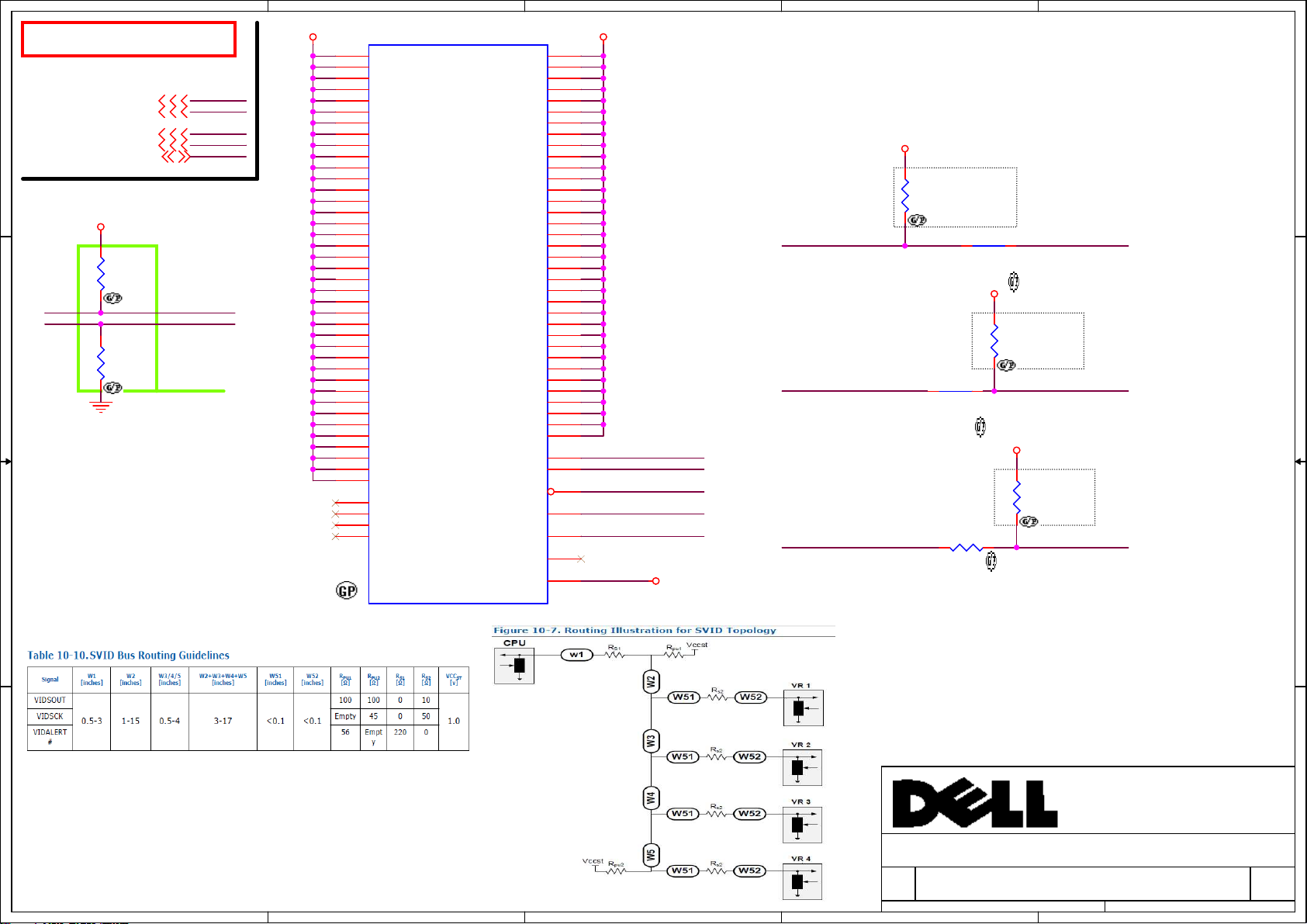

SVID_543016:

Layout Note:

The total Length of Data and Clock (from CPU to each VR) must be equal (±0.1 inch).

Route the Alert signal between the Clock and the Data signals.

1V_VCCST_CPU

SVID DATA

SVID_DATA_CPU_R

SVID CLOCK

SVID_CLK_CPU_R

SVID ALERT

SVID_ALERT#_CPU_R

1

R726

100R2F-L1-GP-U

2

R709

Do Not Stuff

1

R732

Do Not Stuff

R728

220R2F-GP

1

1V_VCCST_CPU

1

#544669

CLOSE TO CPU

SVID_DATA_CPU

2

1

R723

Do Not Stuff

DY

2

1

2

2

SVID_CLK_CPU

R727

56R2F-1-GP

SVID_ALERT#_CPU

2

1V_VCCST_CPU

#544669

CLOSE TO VR

20180208

R727, R728 change to 1%

#544669

CLOSE TO CPU

D

C

B

WHISKEY-LAKE-GP

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A

Title

Title

Title

CPU(VCC_CORE)

CPU(VCC_CORE)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Thursday, July 19, 2018

Thursday, July 19, 2018

Thursday, July 19, 2018

Date: Sheet

Date: Sheet

Date: Sheet

5

4

3

2

CPU(VCC_CORE)

KR CS MLK 13"

KR CS MLK 13"

KR CS MLK 13"

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

7 106

of

7 106

of

7 106

of

1

A00

A00

A00

A

5

SSID = CPU

VCCGT_SENSE[46]

VSSGT_SENSE[46]

VSSSA_SENSE[46]

VCCSA_SENSE[46]

D

1V_VCCGT

1

R807

100R2F-L1-GP-U

2

VCCGT_SENSE

VSSGT_SENSE

1

R808

100R2F-L1-GP-U

C

B

A

2

VCCSA_SENSE

VSSSA_SENSE

1V_VCCSA

5

1

R810

100R2F-L1-GP-U

2

1

R809

100R2F-L1-GP-U

2

1V_VCCGT

WHL QS/CFL/WHL_ES1_CNL U

A5

VCCGT

A6

VCCGT

A8

VCCGT

A11

VCCGT

A12

VCCGT

A14

VCCGT

A15

VCCGT

A17

VCCGT

A18

VCCGT

A20

VCCGT

B3

VCCGT

B4

VCCGT

B6

VCCGT

B8

VCCGT

B11

VCCGT

B14

VCCGT

B17

VCCGT

B20

VCCGT

C2

VCCGT

C3

VCCGT

C6

VCCGT

C7

VCCGT

C8

VCCGT

C11

VCCGT

C12

VCCGT

C14

VCCGT

C15

VCCGT

C17

VCCGT

C18

VCCGT

C20

VCCGT

D4

VCCGT

D7

VCCGT

D11

VCCGT

D12

VCCGT

D14

VCCGT

D15

VCCGT

D17

VCCGT

D18

VCCGT

D20

VCCGT

E4

VCCGT

F5

VCCGT

F6

VCCGT

F7

VCCGT

F8

VCCGT

F11

VCCGT

F14

VCCGT

F17

VCCGT

F20

VCCGT

G11

VCCGT

G12

VCCGT

G14

VCCGT

G15

VCCGT

G17

VCCGT

G18

VCCGT

G20

VCCGT

H5

VCCGT

H6

VCCGT

H7

VCCGT

H8

VCCGT

H11

VCCGT

WHISKEY-LAKE-GP

4

4

13 OF 20CPU1M

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCGT_SENSE

VSSGT_SENSE

1V_VCCGT

H12

H14

H15

H17

H18

H20

J7

J8

J11

J14

J17

J20

K2

K11

L7

L8

L10

M9

N7

N8

N9

N10

P2

P8

R9

T8

T9

T10

U8

U10

V9

W8

W9

AA9

AB2

AB8

AB9

AB10

AC8

AD9

AE8

AE9

AE10

AF2

AF8

AF10

AG8

AG9

AH9

AJ8

AJ10

AK2

AK9

AL8

AL9

AL10

AM8

V2

Y8

Y10

E3

D2

1V_GT_CORE

VCCGT_SENSE

VSSGT_SENSE

3

1D2V_S3

1

C804

DY

Do Not Stuff

2

1V_VCCST_CPU

2

1

C801 SC1U10V2KX-1DLGP

1V_VCCSTG

2

1

C802 SC1U10V2KX-1DLGP

1D2V_VCCSFR_OC

2

1

C803 SC1U10V2KX-1DLGP

1V_VCCST_CPU

0.12 A

1

C805

SCD1U25V2KX-1-DL-GP

2

1V_CPU_CORE

3

2

AD36

VDDQ

AH32

VDDQ

AH36

VDDQ

AM36

VDDQ

AN32

VDDQ

AW32

VDDQ

AY36

VDDQ

BE32

VDDQ

BH36

VDDQ

R32

VDDQ

Y36

VDDQ

BC28

0.04 A

1

C806

2

SC1U10V2KX-1DLGP

RSVD#BC28

BP11

VCCST

BP2

VCCST

BG1

VCCSTG

BG2

VCCSTG

BL27

VCCPLL_OC

BM26

VCCPLL_OC

BR11

VCCPLL

BT11

VCCPLL

WHISKEY-LAKE-GP

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

RO13_CFLU_20171225

1V_GT_CORE

RO13_CFLU_20171227(ES2 used)

ES2

ES2

2

2

2

1

R811 D0002R5J-2-GP

1

R813 D0002R5J-2-GP

1

R814 D0002R5J-2-GP

ES2

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

Date: Sheet

2

14 OF 20CPU1N

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCIO_OUT

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

RO13_CFLU_20171227(ES0/ES1 used)

R812 Do Not Stuff

R815 Do Not Stuff

1V_VCCIO

AK24

AK26

AL24

AL25

AL26

AL27

AM25

AM27

BH24

BH25

BH26

BH27

BJ24

BJ26

BP16

BP18

BG8

BG10

BH9

BJ8

BJ9

BJ10

BK8

BK25

BK27

BL8

BL9

BL10

BL24

BL26

BM24

BN25

BP28

BP29

VSSSA_SENSE

BE7

VCCSA_SENSE

BG7

1

ES0/ES1

1

+VCCIO(ICCMAX.=2.73A

1V_VCCSA

2

2

ES0/ES1

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU_(DISPLAY)

CPU_(DISPLAY)

CPU_(DISPLAY)

KR CS MLK 13"

KR CS MLK 13"

KR CS MLK 13"

1

D

C

B

1V_VCCGT

A

A00

A00

A00

8 106Thursday, July 19, 2018

of

8 106Thursday, July 19, 2018

of

8 106Thursday, July 19, 2018

of

1

5

4

3

2

1

D

C

D

C

(Blanking)

A00

A00

A00

B

A

B

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

(Reserved)

(Reserved)

(Reserved)

2

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

KR CS MLK 13"

KR CS MLK 13"

KR CS MLK 13"

9 106Thursday, July 19, 2018

9 106Thursday, July 19, 2018

9 106Thursday, July 19, 2018

1

of

of

of

SSID = CPU

1V_CPU_CORE

PC1002

1

1

2

D

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1014

1

1

2

2

5

1V_CPU_CORE

PC1004

PC1003

1

2

PC1015

PC1016

1

2

PC1006

PC1005

1

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1017

1

2

1

1

2

2

PC1018

1

1

2

2

22U 0603 x 39 (7DY)

PC1007

PC1019

PC1009

PC1008

1

1

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1020

1

2

1

2

2

PC1021

1

1

2

2

PC1011

PC1010

1

1

2

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1022

PC1023

1

1

2

2

4

PC1013

PC1012

1

2

PC1024

PC1025

1

2

3

2

1

D

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1027

PC1026

1

1

2

2

C

B

1V_VCCGT

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1037

1

1

DY

2

2

Do Not Stuff

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1052

1

1

2

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1063

1

1

DY

2

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1028

PC1029

1

1

2

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

1V_VCCGT

PC1039

PC1038

1

1

DY

2

2

Do Not Stuff

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1053

PC1054

1

1

2

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1064

PC1065

1

1

DY

2

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1031

PC1032

PC1030

1

1

2

DY

2

1

2

Do Not Stuff

Do Not Stuff

Do Not Stuff

DY

PC1034

1

2

DY

PC1036

1

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1080

PC1079

1

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

Do Not Stuff

1

1

DY

2

2

PC1081

1

DY

2

Do Not Stuff

Do Not Stuff

Do Not Stuff

PC1082

DY

1

1

DY

2

2

C

PC1084

PC1083

22U 0603 x 35 (9 DY)

PC1049

PC1045

PC1040

PC1055

PC1066

PC1042

PC1041

1

1

2

2

PC1057

PC1056

1

1

2

1

2

DY

2

PC1067

PC1068

1

DY

2

PC1044

PC1043

1

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

Do Not Stuff

PC1058

1

2

Do Not Stuff

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1069

1

2

1

1

DY

2

2

PC1059

1

1

2

2

PC1070

1

1

2

2

PC1046

1

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1061

PC1060

1

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1001

PC1048

PC1047

1

1

2

2

PC1062

1

2

PC1050

1

1

1

DY

DY

2

2

2

SC22U6D3V3MX-1-DL-GP

Do Not Stuff

Do Not Stuff

PC1051

B

A

SC22U6D3V3MX-1-DL-GP

Do Not Stuff

Do Not Stuff

1V_VCCSA

PC1071

1

1

2

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

VCCSA

PC1073

PC1072

1

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

22U 0603 x 8 (2DY)

PC1075

PC1074

1

1

2

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

Do Not Stuff

Do Not Stuff

5

Do Not Stuff

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

PC1077

PC1076

1

DY

2

PC1078

1

1

DY

2

2

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU_(Power CAP1)

CPU_(Power CAP1)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

CPU_(Power CAP1)

KR CS MLK 13"

KR CS MLK 13"

KR CS MLK 13"

10 106Thursday, July 19, 2018

10 106Thursday, July 19, 2018

10 106Thursday, July 19, 2018

1

of

of

of

A00

A00

A00

A

5

SSID = CPU

PCH Power

D

1D0V_S5

1

C1112

SC22U6D3V3MX-1-DL-GP

2

RO13_20171110

KR EC list

4

3

CPU Power

1V_VCCIO

VCCIO

C1133

1

1

2

2

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

Do Not Stuff

C1134

1

DY

2

+VCCIO(ICCMAX.=2.73A)

C1135

C1108

1

DY

2

Do Not Stuff

SC1U10V2KX-1DLGP

SC1U10V2KX-1DLGP

SC1U10V2KX-1DLGP

C1109

1

1

2

2

C1111

C1110

1

2

2

SSID

1V_VCCGT

C1102

1

DY

2

Do Not Stuff

Do Not Stuff

Do Not Stuff

UNSLICED GT

DY

C1103

1

2

DY

C1104

1

2

1U 0402 x 6

C1105

1

DY

2

SC1U10V2KX-1DLGP

Do Not Stuff

SC1U10V2KX-1DLGP

1

C1107

C1106

1

1

2

2

D

3D3V_S5_PCH

1

R1103

Do Not Stuff

RO13_20171020

C

1D8V_S5

2

R1104

Do Not Stuff

RO13_20171020

B

1D0V_S5

C1128

1

2

3D3V_VCCPRIM

2

1D8V_VCCPRIM

1

C1129

1

2

C1113

1

DY

2

C1122

1

DY

2

3D3V_VCCPRIM

DY

+VCCMPHYGTAON_1P0(ICCMAX.=2.12A)

Do Not Stuff

1D0V_S5

C1115

Do Not Stuff

1

DY

2

Do Not Stuff

1D2V_S3

C1130

1

DY

2

C1123

Do Not Stuff

1

2

SC22U6D3V3MX-1-DL-GP

Do Not Stuff

Do Not Stuff

C1114

SC1U10V2KX-1DLGP

1

2

C1131

1

1

DY

2

2

1D0V_S5

C1132

1

2

SC10U6D3V3MX-DL-GP

SC10U6D3V3MX-DL-GP

SC10U6D3V3MX-DL-GP

C1116

SC1U10V2KX-1DLGP

C1117

1

2

C1136

1

2

SC1U10V2KX-1DLGP

1

2

C1138

C1137

1

2

1D0V_S5

C1118

SC22U6D3V3MX-1-DL-GP

1

2

C1139

1

2

SCD1U25V2KX-1-DL-GP

SCD1U25V2KX-1-DL-GP

SCD1U25V2KX-1-DL-GP

SCD1U25V2KX-1-DL-GP

1

2

C1140

1

2

C1119

C1141

1

2

RO13_20171030

+VCCMPHYGTAON_1P0_LS_SIP change to 1D0V_S5.

1D0V_S5

C1121

C1120

SC1U10V2KX-1DLGP

C1142

1

2

1

DY

2

RO13_20170717

DY

Do Not Stuff

1

2

Do Not Stuff

Do Not Stuff

SC1U10V2KX-1DLGP

1

2

DY

FC1103

1

2

FC1102

C

B

<Core Design>

<Core Design>

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

A

5

4

3

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU_(Power CAP2)

CPU_(Power CAP2)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

Date: Sheet

2

CPU_(Power CAP2)

KR CS MLK 13"

KR CS MLK 13"

KR CS MLK 13"

11 106Thursday, July 19, 2018

11 106Thursday, July 19, 2018

11 106Thursday, July 19, 2018

1

of

of

of

A00

A00

A00

A

SSID = MEMORY

M_A_DQS_DN[7: 0][5]

M_A_DQS_DP[7:0][5]

D

M_A_DQ0[5]

M_A_DQ1[5]

M_A_DQ2[5]

M_A_DQ3[5]

M_A_DQ4[5]

M_A_DQ5[5]

M_A_DQ6[5]

M_A_DQ7[5]

M_A_DQ8[5]

M_A_DQ9[5]

M_A_DQ10[5]

M_A_DQ11[5]

M_A_DQ12[5]

M_A_DQ13[5]

M_A_DQ14[5]

M_A_DQ15[5]

M_A_DQ16[5]

M_A_DQ17[5]

M_A_DQ18[5]

M_A_DQ19[5]

M_A_DQ20[5]

M_A_DQ21[5]

M_A_DQ22[5]

M_A_DQ23[5]

M_A_DQ24[5]

M_A_DQ25[5]

M_A_DQ26[5]

M_A_DQ27[5]

M_A_DQ28[5]

M_A_DQ29[5]

M_A_DQ30[5]

C

B

M_A_DQ31[5]

M_A_DQ32[5]

M_A_DQ33[5]

M_A_DQ34[5]

M_A_DQ35[5]

M_A_DQ36[5]

M_A_DQ37[5]

M_A_DQ38[5]

M_A_DQ39[5]

M_A_DQ40[5]

M_A_DQ41[5]

M_A_DQ42[5]

M_A_DQ43[5]

M_A_DQ44[5]

M_A_DQ45[5]

M_A_DQ46[5]

M_A_DQ47[5]

M_A_DQ48[5]

M_A_DQ49[5]

M_A_DQ50[5]

M_A_DQ51[5]

M_A_DQ52[5]

M_A_DQ53[5]

M_A_DQ54[5]

M_A_DQ55[5]

M_A_DQ56[5]

M_A_DQ57[5]

M_A_DQ58[5]

M_A_DQ59[5]

M_A_DQ60[5]

M_A_DQ61[5]

M_A_DQ62[5]

M_A_DQ63[5]

M_A_A0[5]

M_A_A1[5]

M_A_A2[5]

M_A_A3[5]

M_A_A4[5]

M_A_A5[5]

M_A_A6[5]

M_A_A7[5]

M_A_A8[5]

M_A_A9[5]

M_A_A10[5]

M_A_A11[5]

M_A_A12[5]

M_A_A13[5]

M_A_A14[5]

M_A_A15[5]

M_A_A16[5]

V_SM_VREF_CN TA[5]

M_A_ODT0[5]

M_A_BG0[5]

M_A_PARITY[5]

M_A_CLK0[5]

M_A_CLK#0[5]

M_A_CKE0[5]

M_A_CS#0[5]

SM_DRAMRST #[5 ,13]

M_A_ACT_N[5]

M_A_ALERT_N[5]

M_A_BA0[5]

M_A_BA1[5]

M_A_BG1[5]

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

2

M_A_BG1_M9_R

2

2

2

DDP/SDP

2

DDP/SDP

2

DDP/SDP

2

DDP/SDP

CLK

C1290

C1291

1

1

DY

2

2

C1278

C1276

C1277

1

1

1

DY

2

2

2

VDDQ/VDD 1uF x32

C1206

C1208

C1207

1

1

1

2

1

2

C1223

1

2

2

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

C1224

1

1

2

2

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

DY

2

C1222

1

DY

2

1D2V_S3

1

R1222

1K8R2F-GP

2

M_VREF_CA_D IMMA

2

R1223

1K8R2F-GP

1

close to CPU

M_A_CLK0

R1225 33R2F-3-GP

M_A_CLK#0

R1226 33R2F-3-GP

C1210

C1209

1

2

C1225

C1226

1

2

M_A_CLK0

2016/11/25 DY

ALERT

M_A_ALERT_N

1

1

C1211

1

2

C1227

1

DY

2

C1285

Do Not Stuff

1

DY

2

2

C1212

1

1

DY

2

2

SC1U10V2KX-1D LGP

Do Not Stuff

Do Not Stuff

SC1U10V2KX-1D LGP

C1228

1

2

Do Not Stuff

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

R1202

1

2D7R2F-1-G P

M_A_CLK#0

2

R1208

1

49D9R2F-GP

C1213

C1229

1

2

2

???

2

M_A_CLK

C1214

1

DY

2

C1230

1

2

V_SM_VREF_CN TA

1

C1202

SCD022U16V2KX -3DLGP

2

+V_VREF_PATH 1

1

R1203

24D9R2F-L-G P

2

1D2V_S3

1D2V_S3

C1247

2

1

SCD01U50V2KX- 1DLGP

C1216

C1215

1

1

2

2

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

C1231

C1232

1

1

DY

2

2

Do Not Stuff

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

1

2

1

2

M_A_DQ42

G2

M_A_DQ41

F7

M_A_DQ46

H3

M_A_DQ44

H7

M_A_DQ43

H2

M_A_DQ40

H8

M_A_DQ47

J3

M_A_DQ45

J7

M_A_DQ37

A3

M_A_DQ36

B8

M_A_DQ34

C3

M_A_DQ38

C7

M_A_DQ32

C2

M_A_DQ33

C8

M_A_DQ39

D3

M_A_DQ35

D7

M_A_DQS_DP4

B7

M_A_DQS_DN4

A7

M_A_DQS_DP5

G3

M_A_DQS_DN5

F3

E2

E7

M_A_ODT0

K3

A_ZQ_RAM2

F9

M_VREF_CA_D IMMA

M1

M_A_BG0

M2

TEST_MODE_4

N9

M_A_PARITY

T3

T7

B2

E1

E9

G8

K1

K9

M9

N1

T1

A2

A8

C9

D2

D8

E3

E8

F1

H1

H9

M_A_DQ11

G2

M_A_DQ13

F7

M_A_DQ15

H3

M_A_DQ12

H7

M_A_DQ10

H2

M_A_DQ8

H8

M_A_DQ14

J3

M_A_DQ9

J7

M_A_DQ4

A3

M_A_DQ5

B8

M_A_DQ6

C3

M_A_DQ3

C7

M_A_DQ0

C2

M_A_DQ1

C8

M_A_DQ7

D3

M_A_DQ2

D7

M_A_DQS_DP0

B7

M_A_DQS_DN0

A7

M_A_DQS_DP1

G3

M_A_DQS_DN1

F3

E2

E7

M_A_ODT0

K3

A_ZQ_RAM4

F9

M_VREF_CA_D IMMA

M1

M_A_BG0

M2

TEST_MODE_1

N9

M_A_PARITY

T3

T7

B2

E1

E9

G8

K1

K9

M9

N1

T1

A2

A8

C9

D2

D8

E3

E8

F1

H1

H9

3

M_A_BG1_E9_4

M_A_BG1_M9_R

M_A_BG1_E9_1

M_A_BG1_M9_R

1D2V_S3

1

R1234 240R2D-GP

1

C1286

SCD047U25V2KX -4-GP

2

1D2V_S3

1

R1201 240R2D-GP

1

C1201

SCD047U25V2KX -4-GP

2

SDP & DDP SETTING

M_A_BG1

1

R1220 0R2J-L-GP

DDP

1

R1221 Do Not Stuff

SDP

R1212~R1215 (RO13)(20170911)(DEL: R1216~R1219)

DDP: 240 ohm (64.24005.6DL)

SDP: 0 ohm (63.R0034.L0L)

M_A_BG1_E9_1

M_A_BG1_E9_2

M_A_BG1_E9_3

M_A_BG1_E9_4

2

TEST_MODE_1

TEST_MODE_2

TEST_MODE_3

TEST_MODE_4

2

1D2V_S3

1

R1212 240R2F-1-GP

1

R1213 240R2F-1-GP

1

R1214 240R2F-1-GP

1

R1215 240R2F-1-GP

1

TP1201 Do Not Stuff

1

TP1202 Do Not Stuff

1

TP1203 Do Not Stuff

1

TP1204 Do Not Stuff

0D6V_VREF_S0

VTT 10uF x4

C1289

C1288

1

1

DY

2

2

SC10U6D3V3MX- DL-GP

Do Not Stuff

SC10U6D3V3MX- DL-GP

Do Not Stuff

2D5V_S3

VPP 10uF x5

C1275

C1279

1

1

DY

2

2

SC10U6D3V3MX- DL-GP

Do Not Stuff

SC10U6D3V3MX- DL-GP

SC10U6D3V3MX- DL-GP

Do Not Stuff

C1204

C1205

1

1

2

2

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

Do Not Stuff

SC1U10V2KX-1D LGP

C1221

C1220

1

1

2

2

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

SC1U10V2KX-1D LGP

Do Not Stuff

5

1D2V_S3

2D5V_S3

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_A16

M_A_CS#0

SM_DRAMRST #

M_A_ACT_N

M_A_ALERT_N

M_A_CLK0

M_A_CLK#0

M_A_CKE0

M_A_BA0

M_A_BA1

2D5V_S3

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_A16

M_A_CS#0

SM_DRAMRST #

M_A_ACT_N

M_A_ALERT_N

M_A_CLK0

M_A_CLK#0

M_A_CKE0

M_A_BA0

M_A_BA1

RAM1

B3

B9

D1

G7

J1

J9

L1

L9

R1

T9

A1

A9

C1

D9

F2

F8

G1

G9

J2

J8

B1

R9

P3

P7

R3

N7

N3

P8

P2

R8

R2

R7

M3

T2

M7

T8

L2

M8

L8

L7

P1

L3

P9

K7

K8

K2

N2

N8

MT40A256M16GE-083E- B-COLAY1-GP

ZZ.00PAD.0Q2

1D2V_S3

RAM3

B3

B9

D1

G7

J1

J9

L1

L9

R1

T9

A1

A9

C1

D9

F2

F8

G1

G9

J2

J8

B1

R9

P3

P7

R3

N7

N3

P8

P2

R8

R2

R7

M3

T2

M7

T8

L2

M8

L8

L7

P1

L3

P9

K7

K8

K2

N2

N8

MT40A256M16GE-083E- B-COLAY1-GP

ZZ.00PAD.0Q2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VPP

VPP

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

WE#/A14

CAS#/A15

RAS#/A16

CS#

RESET#

ACT#

ALERT#

CK_T

CK_C

CKE

BA0

BA1

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VPP

VPP

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

WE#/A14

CAS#/A15

RAS#/A16

CS#

RESET#

ACT#

ALERT#

CK_T

CK_C

CKE

BA0

BA1

NF#E2/UDM#/UDBI#

NF#E7/LDM#/LDBI#

NF#E2/UDM#/UDBI#

NF#E7/LDM#/LDBI#

UDQS_T

UDQS_C

LDQS_T

LDQS_C

VREFCA

NC#T7

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

UDQS_T

UDQS_C

LDQS_T

LDQS_C

VREFCA

NC#T7

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

ODT

BG0

TEN

PAR

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

ODT

BG0

TEN

PAR

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

ZQ

ZQ

M_A_DQ59

G2

M_A_DQ61

F7

M_A_DQ62

H3

M_A_DQ56

H7

M_A_DQ58

H2

M_A_DQ57

H8

M_A_DQ63

J3

M_A_DQ60

J7

M_A_DQ53

A3

M_A_DQ50

B8

M_A_DQ48

C3

M_A_DQ54

C7

M_A_DQ52

C2

M_A_DQ51

C8

M_A_DQ49

D3

M_A_DQ55

D7

M_A_DQS_DP6

B7

M_A_DQS_DN6

A7

M_A_DQS_DP7

G3

M_A_DQS_DN7

F3

E2

E7

M_A_ODT0

K3

A_ZQ_RAM1

F9

M_VREF_CA_D IMMA

M1

M_A_BG0

M2

TEST_MODE_2

N9

M_A_PARITY

T3

T7

B2

E1

E9

G8

K1

K9

M9

N1

T1

A2

A8

C9

D2

D8

E3

E8

F1

H1

H9

M_A_DQ17

G2

M_A_DQ19

F7

M_A_DQ22

H3

M_A_DQ23

H7

M_A_DQ21

H2

M_A_DQ18

H8

M_A_DQ20

J3

M_A_DQ16

J7

M_A_DQ25

A3

M_A_DQ29

B8

M_A_DQ27

C3

M_A_DQ31

C7

M_A_DQ28

C2

M_A_DQ24

C8

M_A_DQ26

D3

M_A_DQ30

D7

M_A_DQS_DP3

B7

M_A_DQS_DN3

A7

M_A_DQS_DP2

G3

M_A_DQS_DN2

F3

E2

E7

M_A_ODT0

K3

A_ZQ_RAM3

F9

M_VREF_CA_D IMMA

M1

M_A_BG0

M2

TEST_MODE_3

N9

M_A_PARITY

T3

T7

B2

E1

E9

G8

K1

K9

M9

N1

T1

A2

A8

C9

D2

D8

E3

E8

F1

H1

H9

M_A_BG1_E9_3

M_A_BG1_M9_R

M_A_BG1_E9_2

M_A_BG1_M9_R

4

1D2V_S3

2

1

R1205 240R2D-GP

1

C1236

SCD047U25V2KX -4-GP

2

1D2V_S3

2

1

R1204 240R2D-GP

1

C1203

SCD047U25V2KX -4-GP

2

2D5V_S3

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_A16

M_A_CS#0

SM_DRAMRST #

M_A_ACT_N

M_A_ALERT_N

M_A_CLK0

M_A_CLK#0

M_A_CKE0

M_A_BA0

M_A_BA1

2D5V_S3

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_A16

M_A_CS#0

SM_DRAMRST #

M_A_ACT_N

M_A_ALERT_N

M_A_CLK0

M_A_CLK#0

M_A_CKE0

M_A_BA0

M_A_BA1

1D2V_S3

RAM2

B3

B9

D1

G7

J1

J9

L1

L9

R1

T9

A1

A9

C1

D9

F2

F8

G1

G9

J2

J8

B1

R9

P3

P7

R3

N7

N3

P8

P2

R8

R2

R7

M3

T2

M7

T8

L2

M8

L8

L7

P1

L3

P9

K7

K8

K2

N2

N8

MT40A256M16GE-083E- B-COLAY1-GP

ZZ.00PAD.0Q2

1D2V_S3

RAM4

B3

B9

D1

G7

J1

J9

L1

L9

R1

T9

A1

A9

C1

D9

F2

F8

G1

G9

J2

J8

B1

R9

P3

P7

R3

N7

N3

P8

P2

R8

R2

R7

M3

T2

M7

T8

L2

M8

L8

L7

P1

L3

P9

K7

K8

K2

N2

N8

MT40A256M16GE-083E- B-COLAY1-GP

ZZ.00PAD.0Q2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VPP

VPP

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

WE#/A14

CAS#/A15

RAS#/A16

CS#

RESET#

ACT#

ALERT#

CK_T

CK_C

CKE

BA0

BA1

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VPP

VPP

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

WE#/A14

CAS#/A15

RAS#/A16

CS#

RESET#

ACT#

ALERT#

CK_T

CK_C

CKE

BA0

BA1

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

UDQS_T

UDQS_C

LDQS_T

LDQS_C

NF#E2/UDM#/UDBI#

NF#E7/LDM#/LDBI#

VREFCA

NC#T7

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15