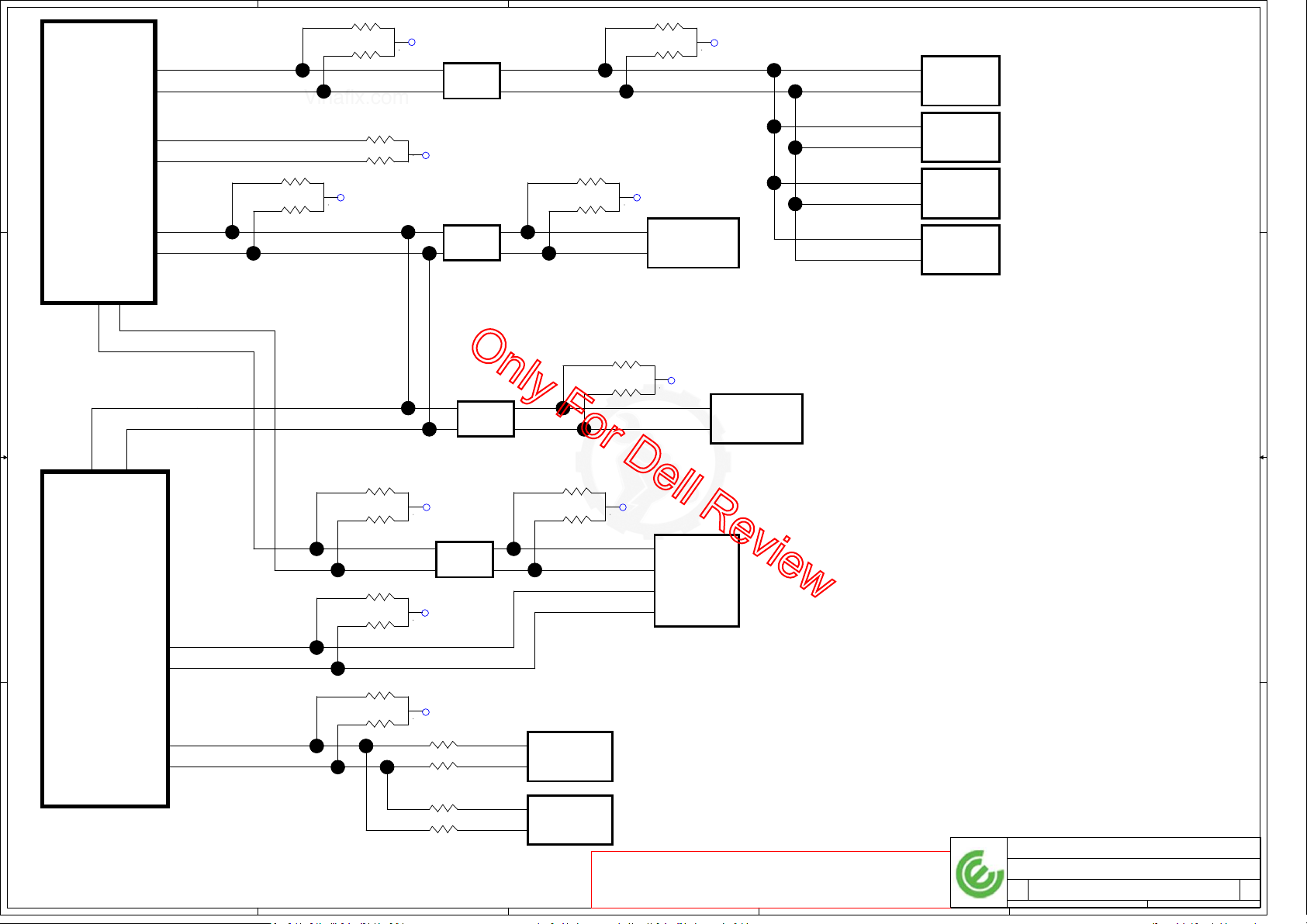

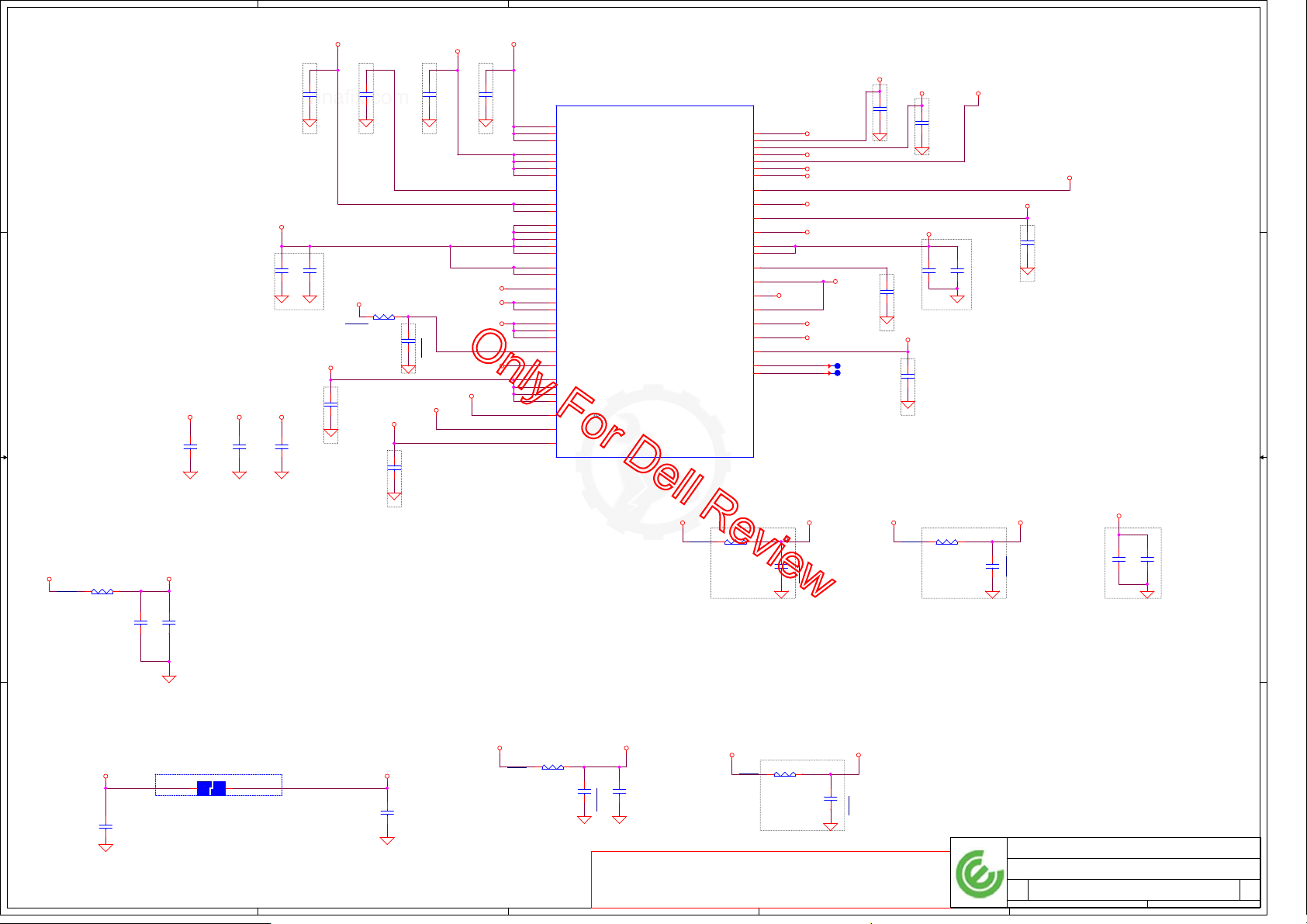

Dell INSPIRON 14-7472 Schematic

Vinafix.com

A

ZZZ

PCB@

B 252 LA-F251P REV0 M/B 1

DA8001BW010

UC1

UC1

1 1

KBL_U42_I7_QS18@

KBL_U42_I5_QS16@

B

UC1

KBL_U42_I7_18G@

C

UC1

KBL_U42_I5_16G@

D

E

S IC A31 FJ8067703281816 QNBF Y0 1.8G

SA0000AWC0L

UC1

KBL_U42_I7_QS19@

S IC A31 FJ8067703281718 QNBE Y0 1.9G

SA0000AWR0L

2 2

S IC A31 FJ8067703282221 QNEG Y0 1.6G

SA0000AWB1L

UC1

KBL_U42_I5_QS17@

S IC A31 FJ8067703282016 QNEE Y0 1.7G

SA0000AWS0L

S IC FJ8067703281816 SR3LC Y0 1.8G A31!

SA0000AWC2L

S IC FJ8067703282221 SR3LB Y0 1.6G A31!

SA0000AWB3L

Compal Confidential

DDH40 / DDH50 MB Schematic Document

LA-F251P

3 3

Rev: 1.0

2017.07.24

4 4

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITH OUT THE EXPRESS WRITTEN AUTHOR IZATION OF DELL . IN ADDITION,

NEITHER THIS SHEET NOR TH E INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

A

B

PARTY WITHOUT DELL'S EXPRESS WRIT TEN CONSENT.

C

D

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-F251P

LA-F251P

Tuesday, August 08, 2017

Tuesday, August 08, 2017

Tuesday, August 08, 2017

LA-F251P

1.0

1.0

1

1

1

E

1.0

55

55

55

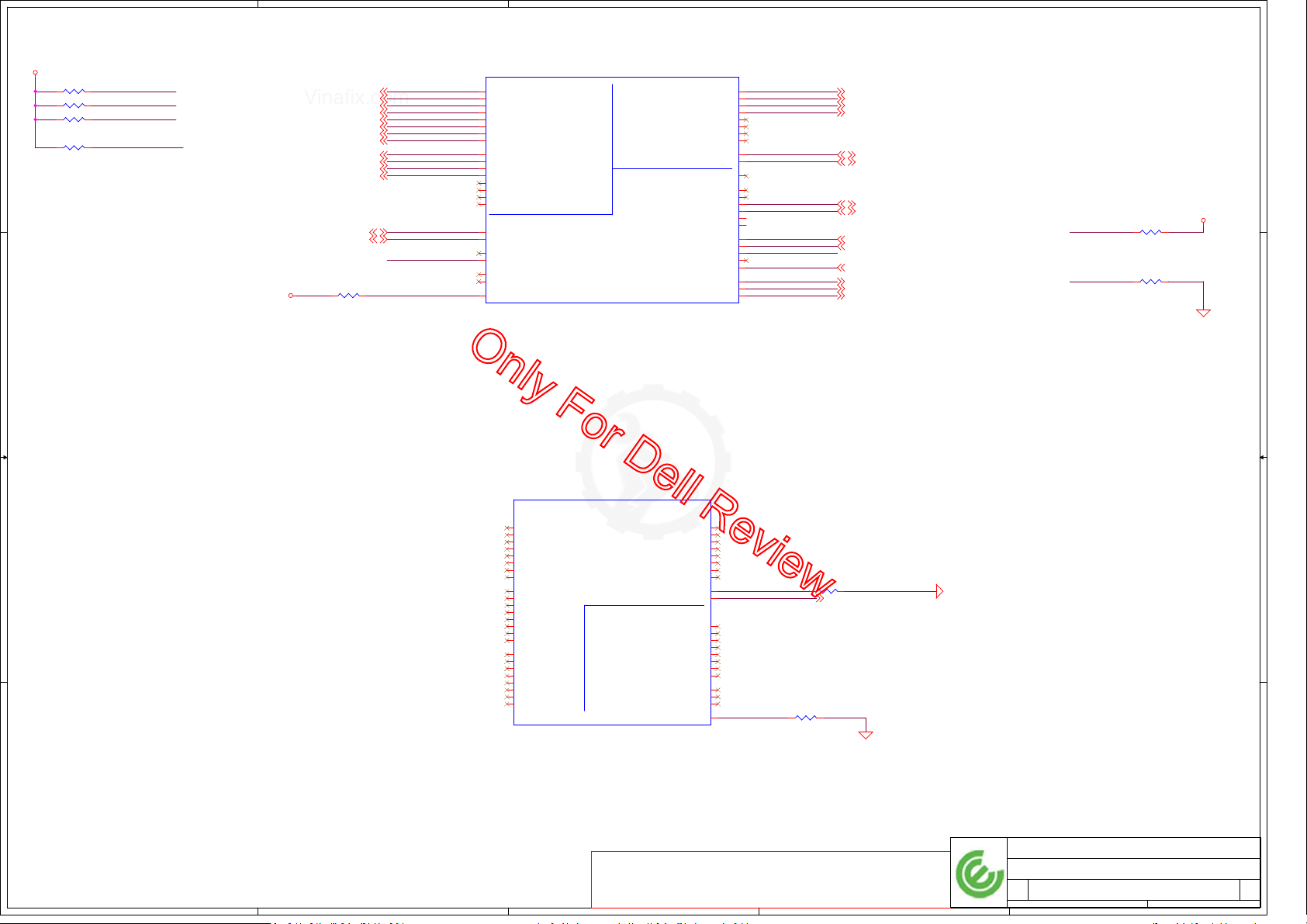

Vinafix.com

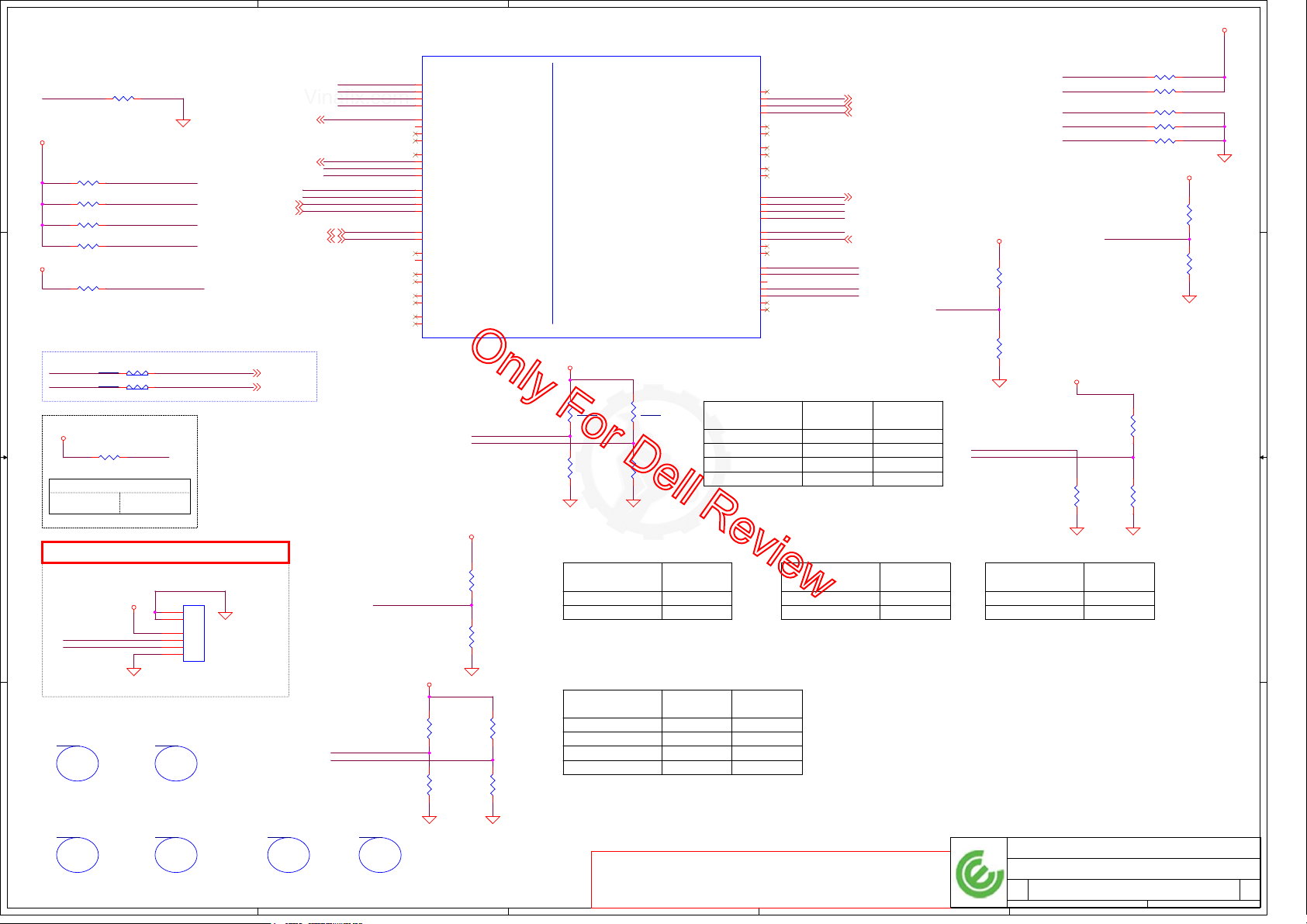

A

B

C

D

E

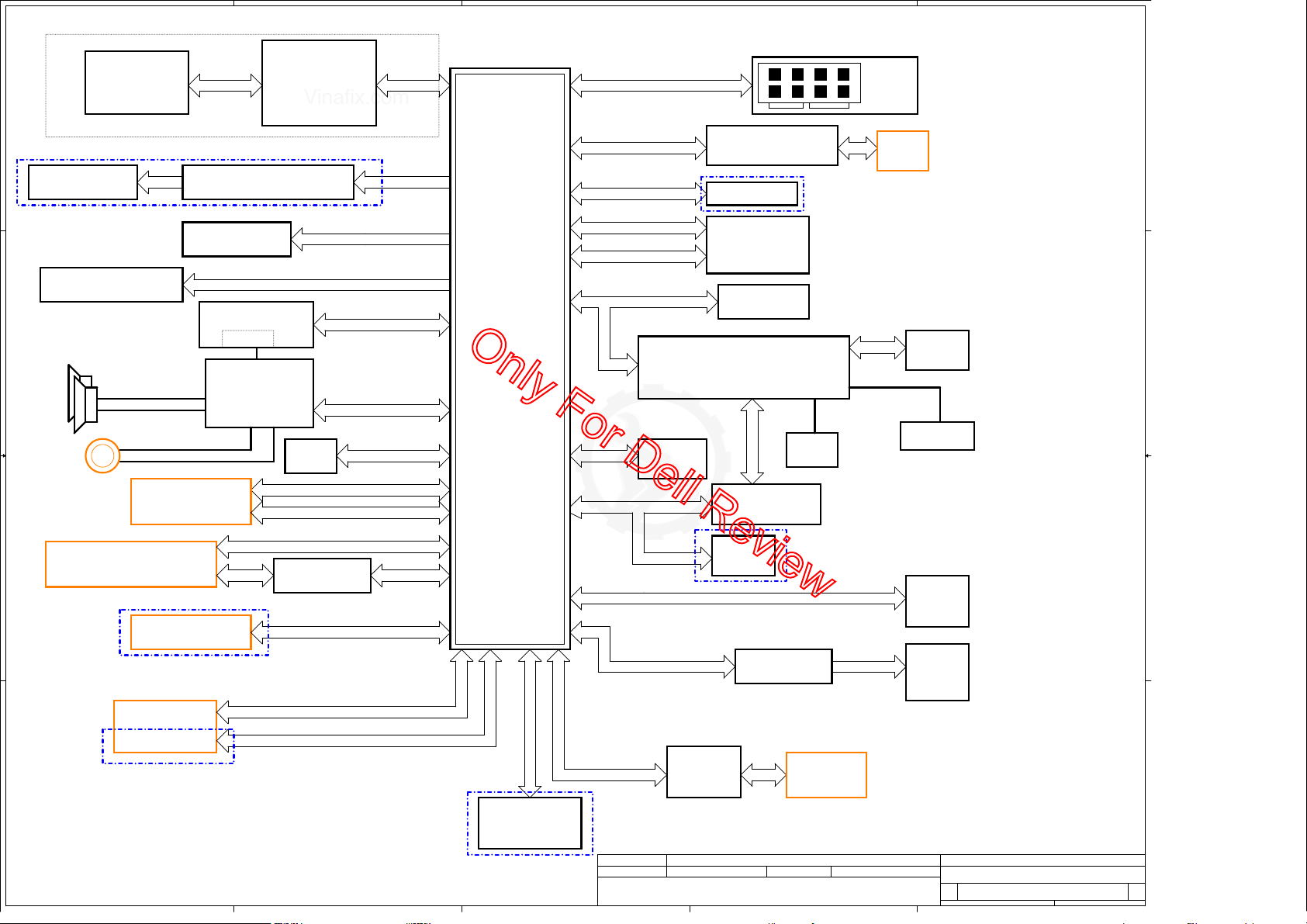

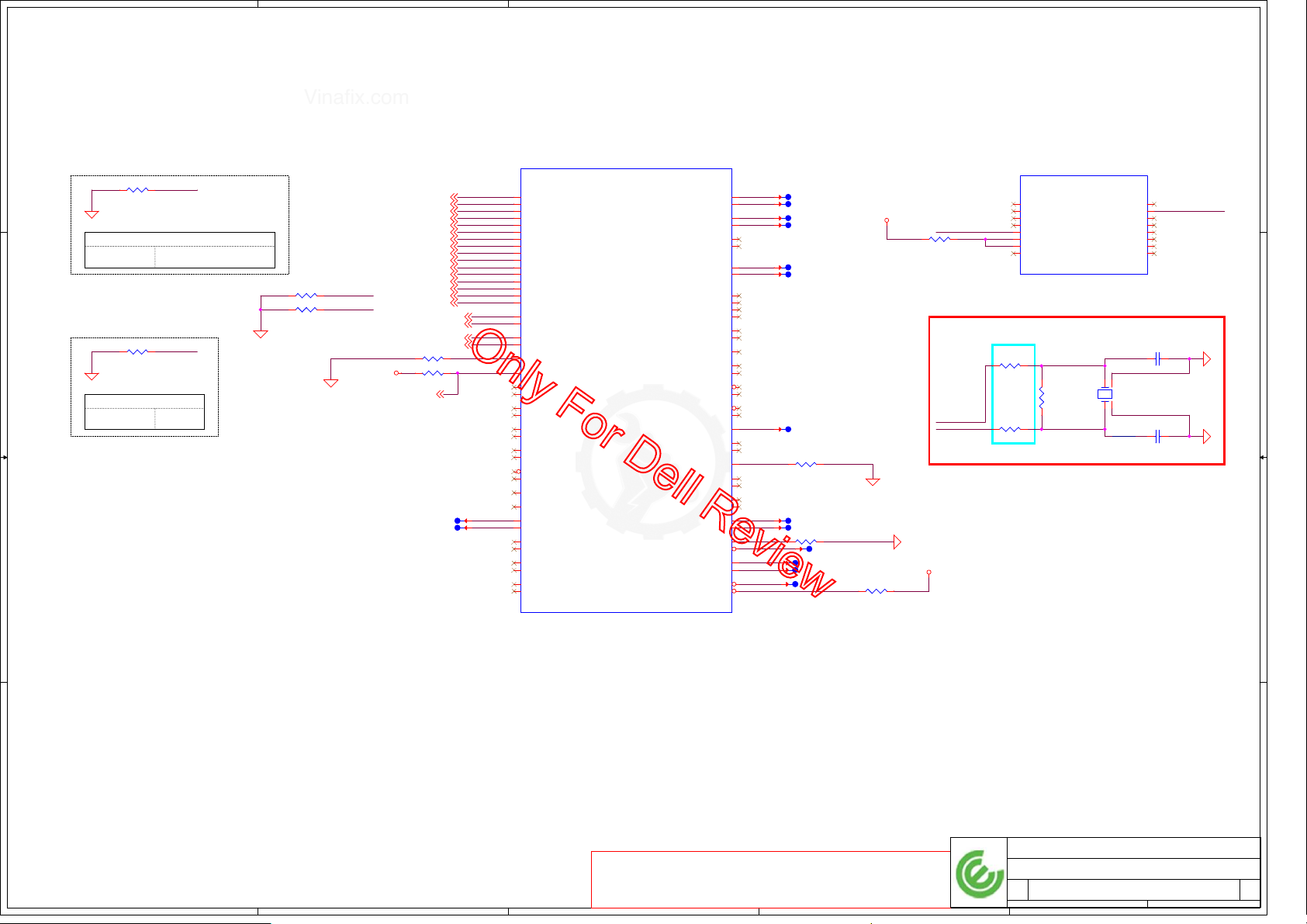

VRAM(GDDR5) * 4

1 1

DIS on board

Dali Only

VGA Conn.

14.0" / 15.6"

(FHD)

2 2

VGA

2CH SPEAKER

(2CH 2W/4ohm)

Universal Jack

Port 1 (USB3.0)

DP to VGA Translator

HDMI V1.4a

HD Camera

D-MIC

HDA

CODEC

Realtek

ALC3246-CG

MIC_IN /GND

HP_R/ L

Left side

RTD216 6

Nvida

N17S-G1

(14"/15")

Touch

Screen

(18W)

USB2.0 x 1

GPU

(Gen3)

PCIe x 4

DDI 2

DDI 1

eDP

HDA

USB2.0 x 1

USB3.0 x 1

USB2.0 x 1

Cox ial

Wir e

Wir e

Wir e

Intel CPU

Kabylake - U

/ Kabylake - R

42mm X 24mm

BGA13 56

15W

PCH-LP

10 USB 2.0/1.1 po rts

6 USB 3 .0 ports

High Definition Audio

3 SATA p orts

6 PCIE ports

LPC I/F

eSPI

I2C x12

DDR4 1866/2133MHz Channel A

PCIe x 1

USB2.0 x 1

Wir e

PCIe x 1

USB2.0 x 1

Finger Printer

NGFF WLAN

802.11b/g/n

802.11ac

BT 4.0 1x1

eSP I

MEC1416

SPI

Flash ROM

W25Q12 8FVSIQ

(16MB)

I2C

LAN 10/100/1000

RealTek RTL8111H

eSPI debug port

EC

SMSC

PS2

Precision Touchpad

Dali Only

Int.

KB

DDR4

4GB/8G B

SODIMM A

RJ45

Conn.

SMB US

Thermal

NCT77 18W

PWM FAN

Left side

3 3

Port 0 (USB3.0)

USB2.0

USB PowerShare

TI TPS2544RTER

Dali 15.6" Only

Right side

Port 0 (USB2.0)

Right side

Port 2 (USB3.0)

Port 2 (USB2.0)

USB2.0 x 1

USB3.0 x 1

USB2.0 x 1

Astro Only

4 4

A

Wir e

Cox ial

Wir e

B

USB3.0 x 1

USB2.0 x 1

Dali Only

TPM2.0

China TPM2.0

Nuvoton NPCT650VB2Y X

Nuvoton Z32 H330TC

SPI

G-Sensor

LNG2DMTR

Dali Only

PCIe x 4

SATA(Gen3) x1

CardReader

USB2.0 x 1

Wir e

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

SD 3.0

Realte k

RTS5170

SATA re-driver

PS8527

SD Card Slot

Compal Secret Data

Compal Secret Data

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

SSD

NGFF

M2.Slot

2.5"

HDD

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U_2+2 Block Diagrams

SKL-U_2+2 Block Diagrams

SKL-U_2+2 Block Diagrams

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

LA-F251P

LA-F251P

LA-F251P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

0.3

0.3

2 55Tuesday, August 08, 2017

2 55Tuesday, August 08, 2017

2 55Tuesday, August 08, 2017

0.3

Vinafix.com

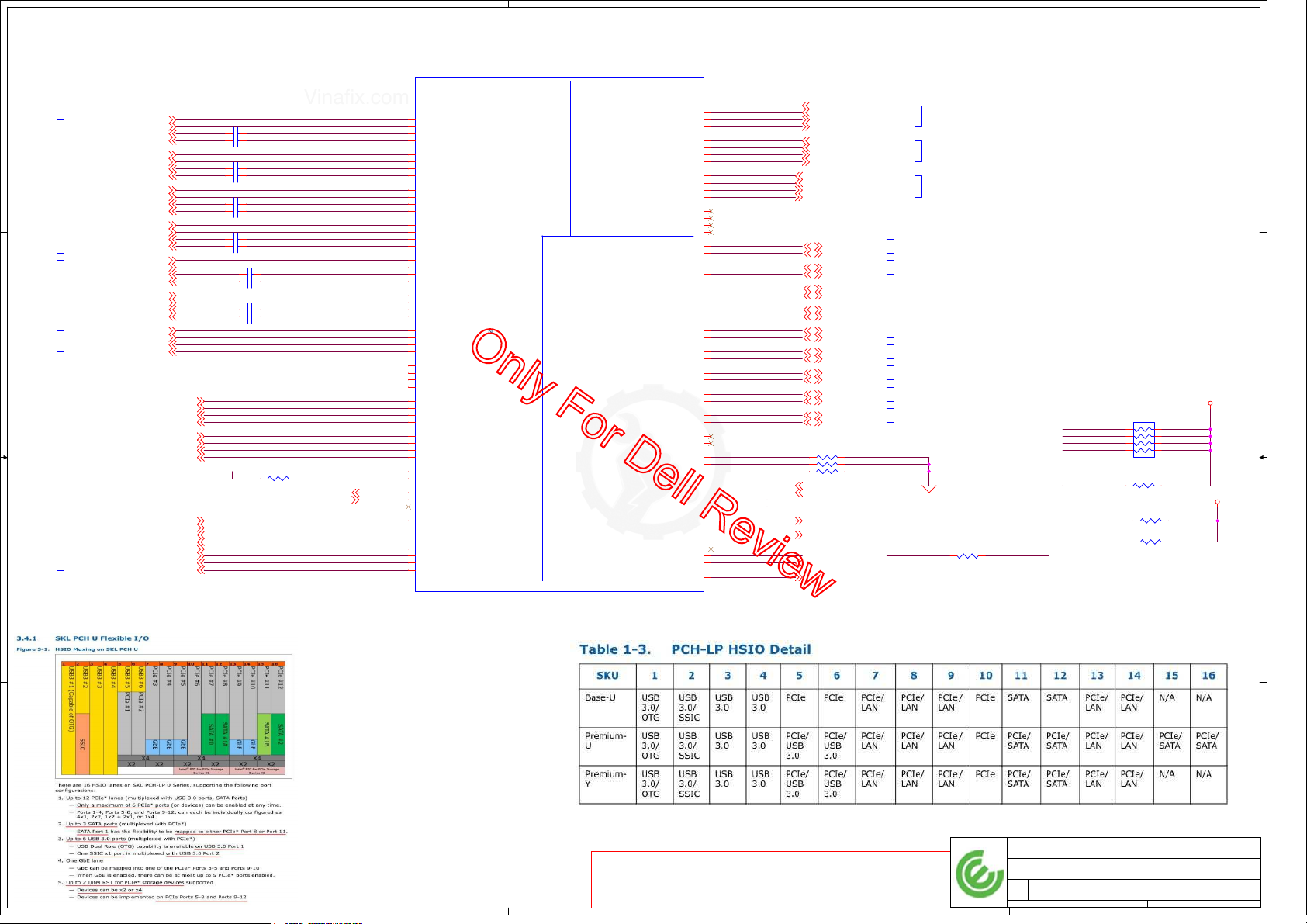

5

4

3

2

1

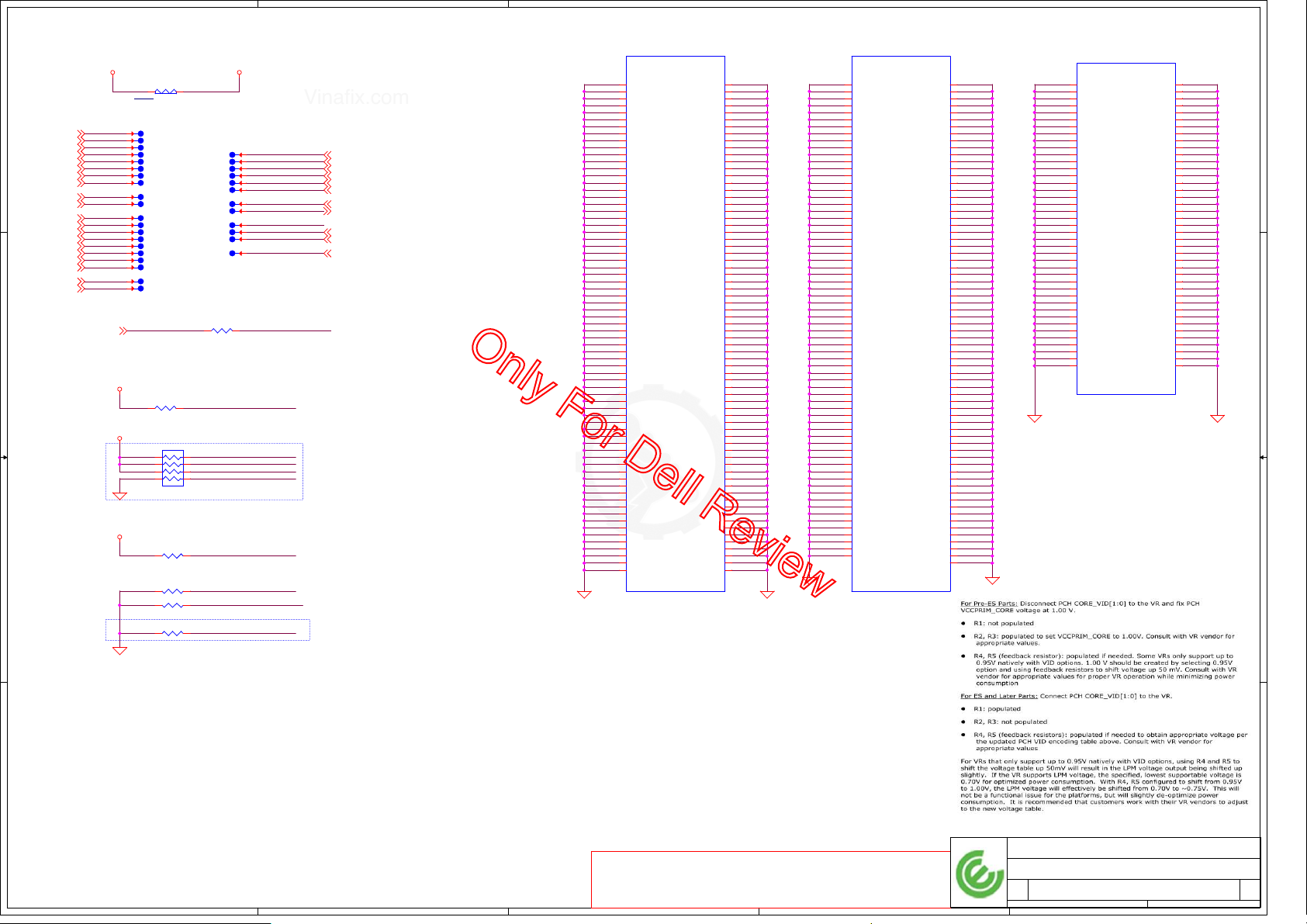

POWER STATES

Signal

State

S0 (Full ON) / M0

S3 (Suspend to RAM) / M3 LOW

D D

S4 (Suspend to DISK) / M3

S5 (SOFT OFF) / M3

G3 OFF OFF OFF OFF OFF OFF OFF

SLP

S3#

HIGH

LOW

LOW LOW

SLP

SLP

S4#

HIGH HIGH

HIGH HIGH ON

LOW

LOW

S5#

HIGH

ALWAY S

PLANE

ON

ON

ON

PM TABLE

+RTC_CELL

+RTC_VCC

power

plane

C C

State

+3VLP

+19VB

+1.0V_PRIM

+1.0V_MPHYPLL

+5VALW

+3VALW

+3.3V_ALW_DSW

+1.8V_PRIM

RUN

SUS

PLAN E

PLANE

ON

ON ON

ON

OFF

OFF

OFF

OFF OFF

OFF

+1.0V_VCCST

+1.2V_DDR

+2.5V_MEM

+3VALW_PCH

+1.0VS_VCC IO

+1.0V_VCCSTG

+VCC_G T

+VCC_SA

+VCC_CORE

+GPU_CORE

+5VS

+3VS

+0.6V_DDR_ VTT

CLOCKS

OFF

OFF

*+

()&()&

#$%$&&'

-.'/&.'&

,

0()10()1

,

"

"

"

"

"!

!

*

,

S0

S3

S4&S5 / AC

S4&S5 / DC

B B

ON

ON

ON

ON

ON

ON ON

ON

OFF

ON

OFF

OFF

ON

OFF

OFF

OFF

Board ID & Model ID table

&2

#33)4'05%21 #33#605 %21

A A

5

73(/& (),+)&3

7081

7081

7081

.301

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

Compal Electronics, Inc.

Port assignment

Port assignment

Port assignment

Document Number Re v

Document Number Re v

Document Number Re v

LA-F251P

LA-F251P

LA-F251P

1

3 55Tuesday, August 08, 2017

3 55Tuesday, August 08, 2017

3 55Tuesday, August 08, 2017

0.3

0.3

0.3

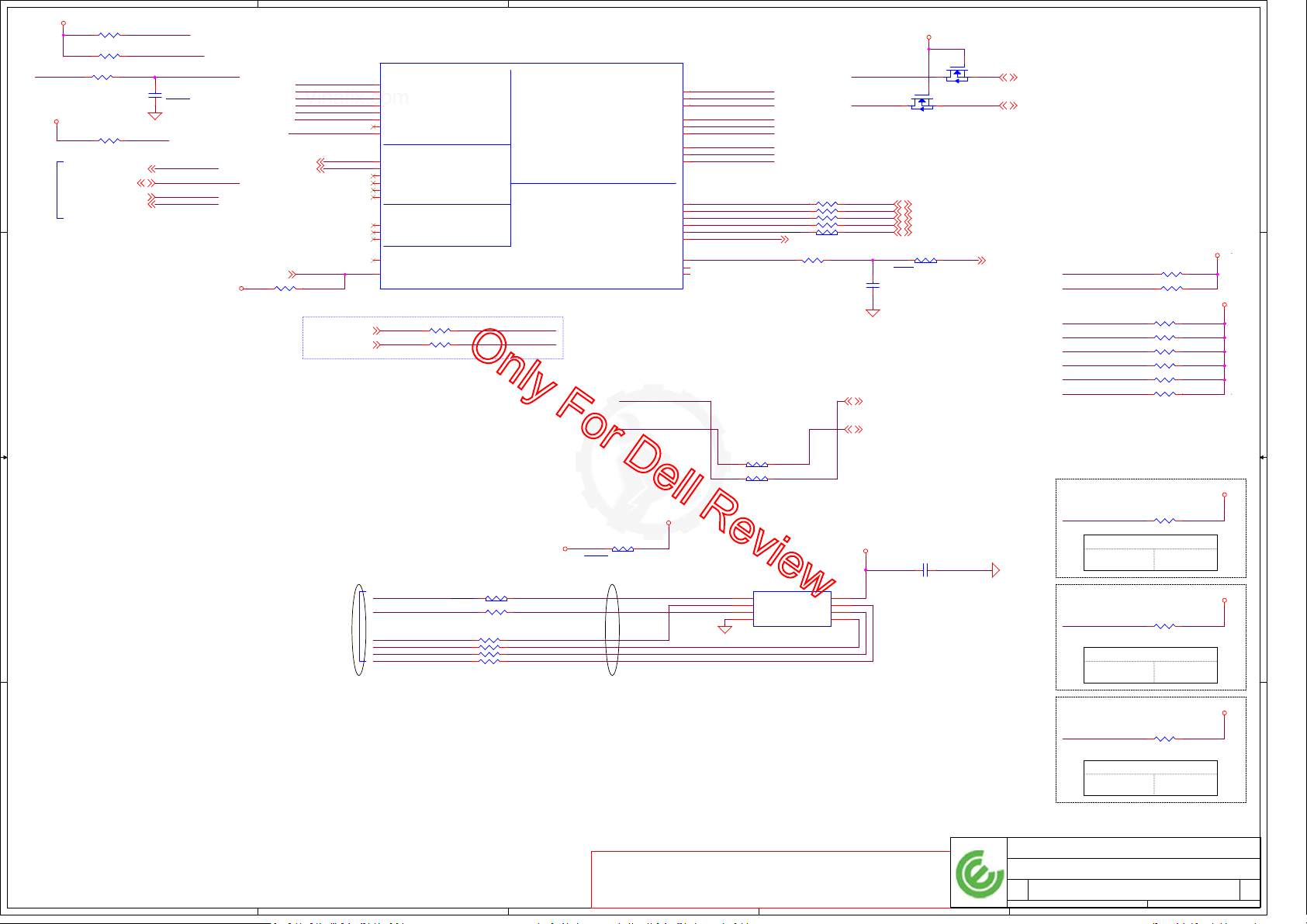

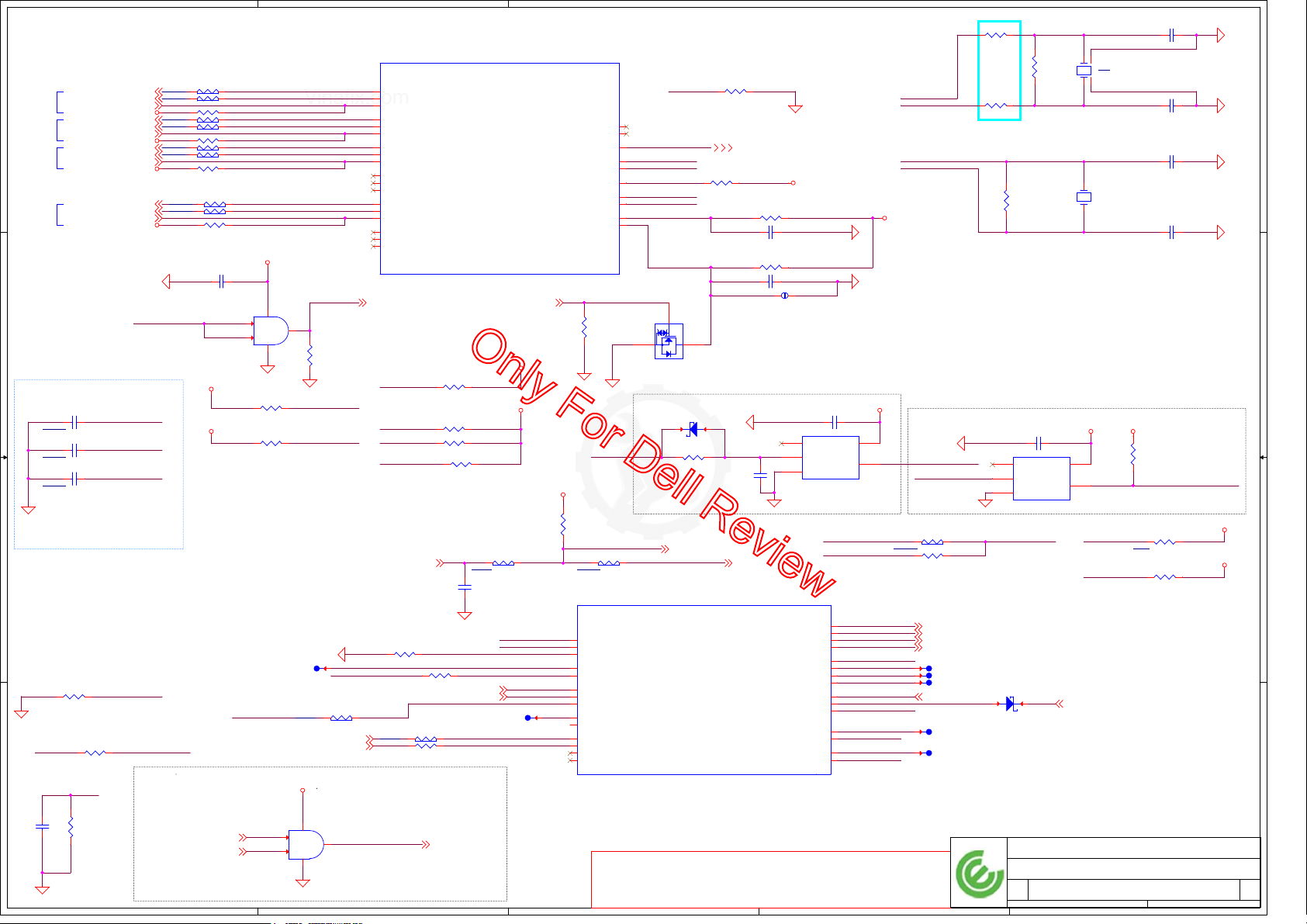

Vinafix.com

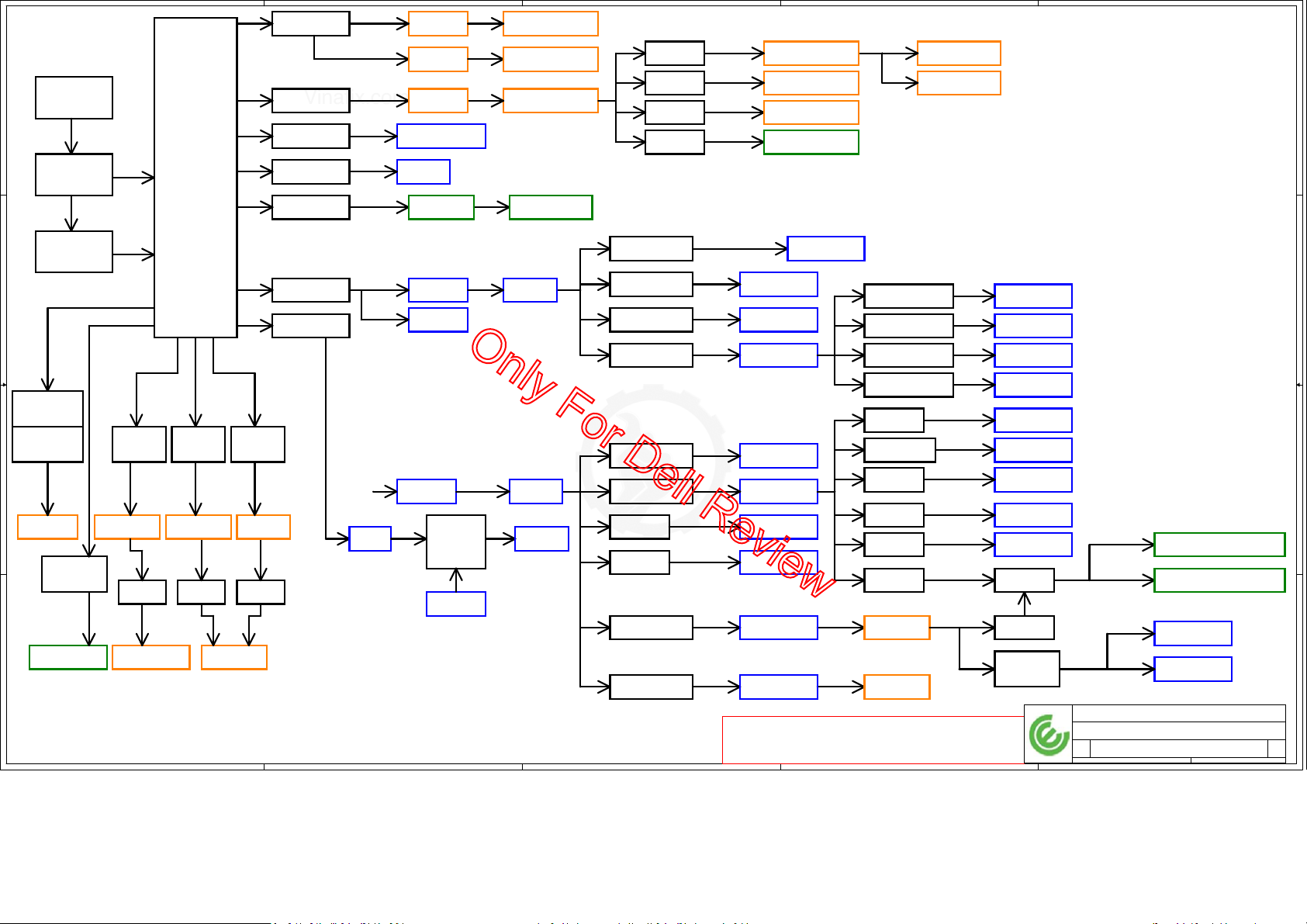

5

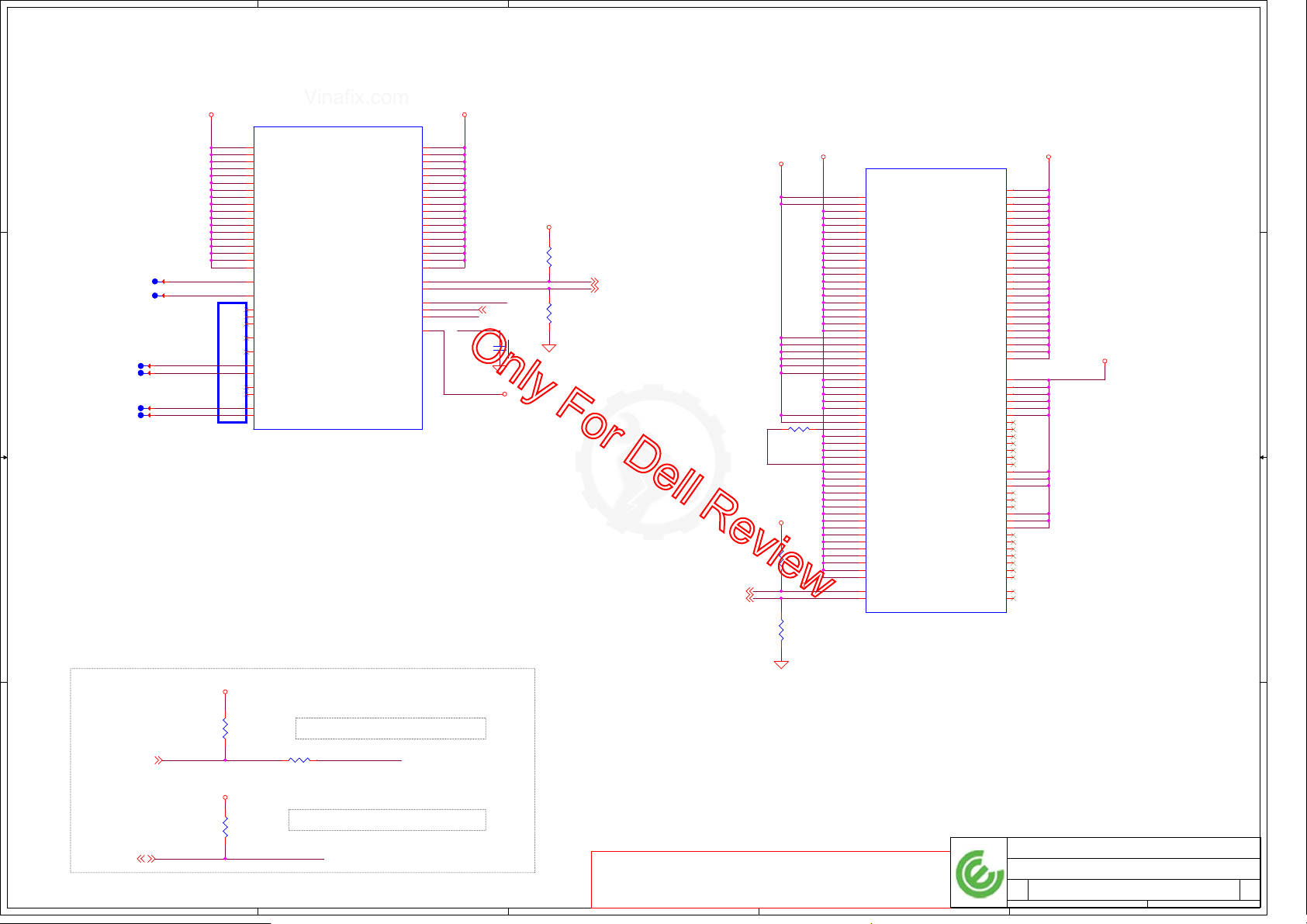

CPU PWR

GPU PWR

Peripheral Device PWR

D D

ADAPTER

CHARGER

ISL88739HRZ-T

(PU703)

+PWR_SRC

(+19VB)

PJP206

PJP301

PJP1401

RT8207PGQ W

(PU200)

SY8286RAC

(PU300)

0ohm 0805

(R5214)

0ohm 0402

(R6528)

SY8286RAC

(PU1400)

0.6V_DDR_ VTT_ON

SIO_SLP_S4#

01

POK

1.35V_PW R_EN

4

PJP200

+1.2VP +1.2V_DDR

+0.6VSP

+1VALW P

PJP203

PJP302

+DCBATOUT_LC D

+IR_LED+

+1.35VGPUP

PJP1402

+0.6V_DDR_VTT

+1.0V_PRIM

+1.35VS_VRAM

3

TPS22961

(UZ19)

JUMP

(JP17)

TPS22967

(UZ21)

TPS22961

(UV13)

SIO_SLP_S3#

SIO_SLP_S0#

SIO_SLP_S4#

N16S@

DGPU_P WROK

1.0VS_DG PU_EN

N17S@

+1.0V_VCCSTG_C

+1.0V_MPHYPLL

+1.0V_VCCST

+1.0VS_DGPU

Volume

JP15

2

+1.0VS_VCCIO

+1.0V_VCCST G

1

USB_POWER SHARE_V BUS_EN

USB_EN#

USB_EN#

SIO_SLP_S3#

TP_EN#

SIO_SLP_S3#

01

+USB30_ VCCB

+USB30_ VCCC

JP21

+5VS

+TP_VDD

JP13

+3VS

+3VALW_P CH

+3V_SPI

01

+1.8VALWP

SIO_SLP_S4# PJP802

+2.5VP +2.5V_MEM

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

+USB30_ VCCA

PJP502POK

0ohm 0603

(R5232)

(R5601)

AP2330W- 7

(U5604)

FUSE 0.5A_13.2V

(F6201)

RT9724GB

(U5201)

SY6288C2 0AAC

(UL3)

0ohm 0805

(R5809)

0ohm 0603

(R5229)

JUMP

(JP1)

N16S@

0ohm 0603

(RV163)

+1.8V_PRIM

2

LCDVDD _EN

+TPAN_VD D

+5V_HDD

+5VS_HDMI

+5V_KB_ BL

+LCDVDD

+3.3V_LAN

+3.3V_WLAN

+3.3V_CAM

+3VS_S SD

EM5209VF

(UV2)

N17S@

0ohm 0805

(RV162)

LN2306LT1G

(Q6205)

DGPU_MA IN_EN

DGPU_P WR_EN

+3VS_1.8VS_DGPU_MAIN

+3VS_1.8VS_DG PU_AON

+CPV DD

+1.8V _AVDD

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

Power rails

Power rails

Power rails

LA-F251P

LA-F251P

LA-F251P

1

4 55Tuesday, August 08, 2017

4 55Tuesday, August 08, 2017

4 55Tuesday, August 08, 2017

0.3

0.3

0.3

PJP501

PJP801

TPS2544RTER

(UUS5)

AP22802B W5

(U3504)

AP22802B W5

(U3505)

EM5209VF

(UZ2)

NTK3139PT1G

(Q6203)

EM5209VF

(UZ2)

0ohm 0603

(RZ1705)

0ohm 0402

(RC1124)

RT8061AZQW

(PU500)

RT9059GSP

(PU800)

3

BATTERY

EN_3V

ENLDO_3V5 V

EN_5V

+3VLP

+5VALW P

PJP103

+5VALW

VL 0ohm 0805

+3VALW P

PJP102

BAS4 0C

(D2501)

+3VALW

+RTC_CELL

+RTC_VCC

4

PJP106 ENLDO_3V5 V

PJP105

DRVO N

+VCC_GT

0ohm 0805

(PRC02)

010101

SY8286CRAC

(PU102)

SY8286BRAC

(PU100)

C C

NCP8125 3

(PUA01)

AON7934

(PQA01)

B B

DRVO N DRVO N

+VCC_ SA

RT8816AGQ W

(PU1101)

VGA_CORE _EN

+GPU_CORE

A A

NCP30203 5

(PUI01)

+VCC_CO RE

0ohm 0805

(PRC01)

01

+VCC_CO RE

NCP30203 5

(PUI02)

0ohm 0805

(PRC03)

+VCC_COR E_42 +VCC_GT_4 2

5

DRVO N

NCP30203 5

(PUG01)

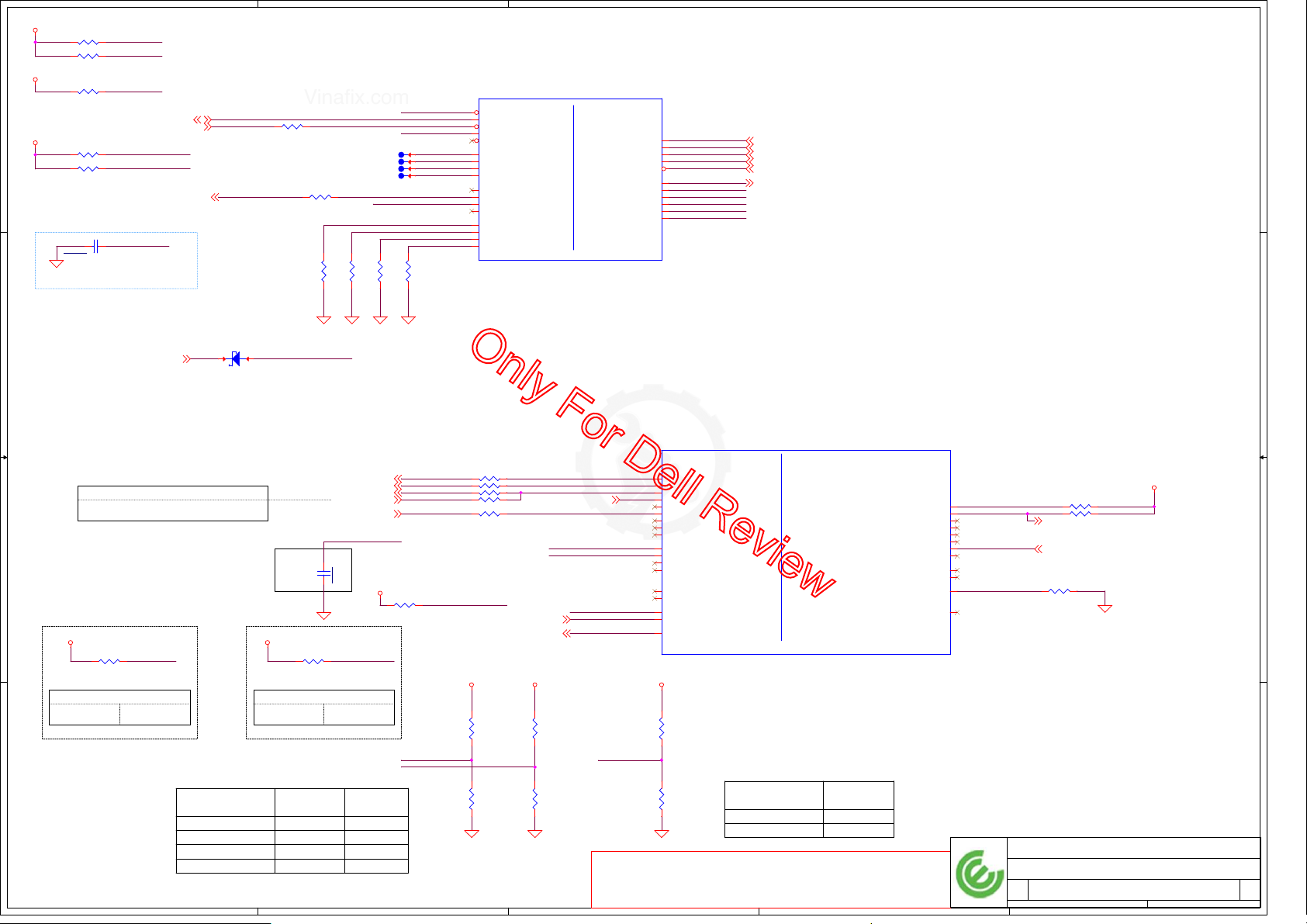

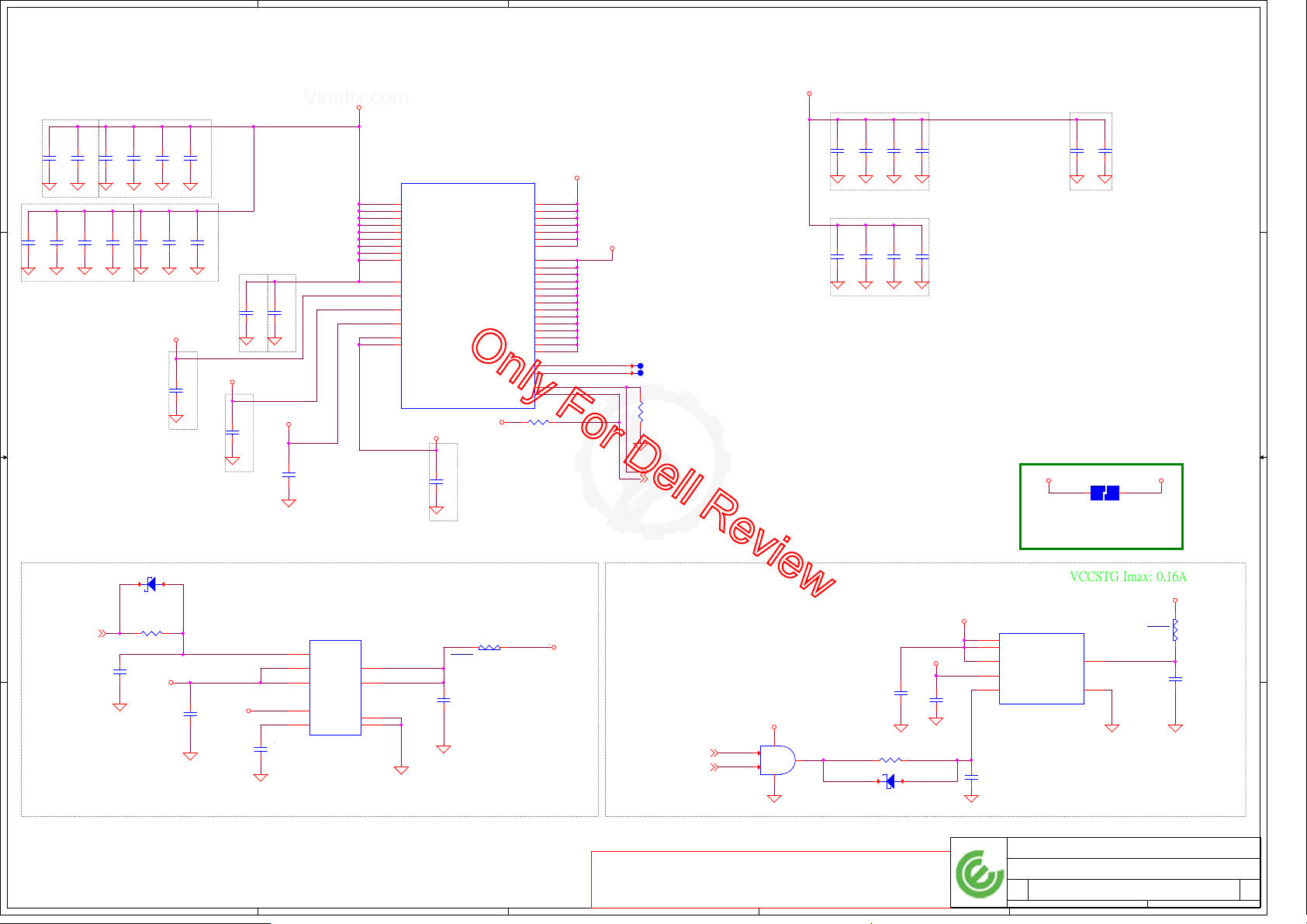

Vinafix.com

5

KBL-U

R7

+!5

+

D D

+!! 5

+!

+!! 5

+!

R8

R9

W2

W3

V3

+!5

+

+!:+!5

+!:+

9%2

9%2

+!! 5

+!

4

9%2

9%2

9%2

9%2

+3VALW_PCH

+3VALW_PCH

;

+

+3VALW_PCH

;7

=5

*:+!5

*:+

3

9 %2

9 %2

>

9 %2

>

9 %2

:!

:

+3VS_+1.8VS_DGPU_AON

D9

+!5

)"

D8

+

'%&2(3

SMBus Address: 0x41 / 0x41

+3VS

*:+!5

*:+

*:+!5

*:+

*:+!5

*:+

*:+!5

*:+

2

253

!

++

254

SMBus Address: 000

253

!

++

254

SMBus Address: 010

30

!

7"

29

1

!

--

4

!"+

SMBus Address: 0x64/0x65 & 0x68/0x69

1

U6 U7

::

C C

12 11

SMB0 2_C LK

SMB0 2_D AT A

KBC

MEC 1416

B B

GPIO 11 4

GPIO 11 5

SMB0 1_C LK

SMB0 1_D AT A

A A

5

:!:

78

79

9

8

!5::

::

:*":+!5

:*":+

+!! 5

+!

9 %2

9 %2

:!:

::

9 %2

9 %2

9 %2

9 %2

4

;

+

+3VS

;

+

TP_VDD

+3VALW_EC

%2

%2

%2

%2

!5:+

:+

4

!

5

3

4

!

9 %2

3

2

8

7

+3VS

8

!

%&2(3

7

SMBus Address: $2C

SMBus Address: 1001100xb (x is R/W bit)

9 %2

9 %2

:!::;

:::;

!5::

::

9 %2

*+:+!:!5

*+:+!:

TP_VDD

SMBus Address: 0x01

%(/&

!* <

SMBus Address: 0001001 (R/W#)

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

SMbus Block diagram

SMbus Block diagram

SMbus Block diagram

LA-F251P

LA-F251P

LA-F251P

5 55Tuesday, August 08, 2017

5 55Tuesday, August 08, 2017

5 55Tuesday, August 08, 2017

1

0.3

0.3

0.3

Vinafix.com

5

4

3

2

1

+3VS

SDVO_SCLK

RC175 2.2K_0201_5%

RC178 2.2K_0201_5%

D D

RE439

RC1122 2.2K_0201_5%

C C

B B

12

SDVO_SDATA

12

WLAN_RADIO_DIS#

12

10K_0402_5%

DDPC_SDATA

12

+1.0VS_VCCIO

CPU_DP1_N2[26]

CPU_DP1_P2[26]

CPU_DP1_N1[26]

CPU_DP1_P1[26]

CPU_DP1_N0[26]

CPU_DP1_P0[26]

CPU_DP1_N3[26]

CPU_DP1_P3[26]

SOC_DP2_N0[33]

SOC_DP2_P0[33]

SOC_DP2_N1[33]

SOC_DP2_P1[33]

SDVO_SCLK[26]

SDVO_SDATA[26]

1 2

RC2 24.9_0402_1%

COMPENSATION PU FOR eDP

CAD Note:Trace width=20 mils ,Spacing=25mil,

Max length=100 mils.

SDVO_SCLK

SDVO_SDATA

DDPC_SDATA

EDP_COMP

UC1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKL-U_BGA1356

SKL-U Ballout Rev0.71 & INTEL symbol Rev1.0

UC1I

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKL-U_BGA1356

SKL-U

DDI

DISPLAY SIDEBANDS

SKL_U LT

1 OF 20

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

EDP

EDP_DISP_UTIL

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

9 OF 20

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

EDP_VDDEN

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

SOC_DP2_AUXN

E48

SOC_DP2_AUXP

F48

G46

F46

L9

L7

SIO_EXT_SMI#

L6

N9

L10

BKLT_EN_EC

R12

R11

U13

CSI2_COMP

WLAN_RADIO_DIS#

EMMC_RCOMP

RC4 200_0402_1%

1 2

RC3

1 2

EDP_TX0_DN [25]

EDP_TX0_DP [25]

EDP_TX1_DN [25]

EDP_TX1_DP [25]

EDP_AUX_DN [25]

EDP_AUX_DP [25]

SOC_DP2_AUXN [33]

SOC_DP2_AUXP [33]

HDMI_HPD [26]

CRT_HPD [33]

EDP_HPD [25]

BKLT_EN_EC [22]

L_BKLT_CTRL [25]

EDP_VDD_EN [25]

100_0402_1%

WLAN_RADIO_DIS# [29]

SIO_EXT_SMI#

BKLT_EN_EC

10K_0402_5%

12

RC239

12

RC390100K_0402_5%

+3VALW_PCH

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (1/14)

CPU (1/14)

CPU (1/14)

LA-F251P

LA-F251P

LA-F251P

6 55Tuesday, August 08, 2017

6 55Tuesday, August 08, 2017

6 55Tuesday, August 08, 2017

1

0.3

0.3

0.3

Vinafix.com

5

DDR4, Ballout for B2B(Interleave)

4

3

2

1

UC1B

DDR_A_D[0..15][18]

D D

DDR_A_D[16..31][18]

DDR_A_D[32..47][18]

C C

DDR_A_D[48..63][18]

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

SKL-U

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

DDR0_ODT[1]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

2 OF 20

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CKE2

DDR_A_CKE3

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_MA5

DDR_A_MA9

DDR_A_MA6

DDR_A_MA8

DDR_A_MA7

DDR_A_BG0

DDR_A_MA12

DDR_A_MA11

DDR_A_ACT#

DDR_A_BG1

DDR_A_MA13

DDR_A_CAS#

DDR_A_WE#

DDR_A_RAS#

DDR_A_BS0

DDR_A_MA2

DDR_A_BS1

DDR_A_MA10

DDR_A_MA1

DDR_A_MA0

DDR_A_MA3

DDR_A_MA4

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

DDR_A_ALERT#

DDR_A_PAR

DDR_VTT_CNTL

DDR_A_CLK#0 [18]

DDR_A_CLK0 [18]

DDR_A_CLK#1 [18]

DDR_A_CLK1 [18]

DDR_A_CKE0 [18]

DDR_A_CKE1 [18]

DDR_A_CS#0 [18]

DDR_A_CS#1 [18]

DDR_A_ODT0 [18]

DDR_A_ODT1 [18]

DDR_A_MA5 [18]

DDR_A_MA9 [18]

DDR_A_MA6 [18]

DDR_A_MA8 [18]

DDR_A_MA7 [18]

DDR_A_BG0 [18]

DDR_A_MA12 [18]

DDR_A_MA11 [18]

DDR_A_ACT# [18]

DDR_A_BG1 [18]

DDR_A_MA13 [18]

DDR_A_CAS# [18]

DDR_A_WE# [18]

DDR_A_RAS# [18]

DDR_A_BS0 [18]

DDR_A_MA2 [18]

DDR_A_BS1 [18]

DDR_A_MA10 [18]

DDR_A_MA1 [18]

DDR_A_MA0 [18]

DDR_A_MA3 [18]

DDR_A_MA4 [18]

DDR_A_DQS#0 [18]

DDR_A_DQS0 [18]

DDR_A_DQS#1 [18]

DDR_A_DQS1 [18]

DDR_A_DQS#2 [18]

DDR_A_DQS2 [18]

DDR_A_DQS#3 [18]

DDR_A_DQS3 [18]

DDR_A_DQS#4 [18]

DDR_A_DQS4 [18]

DDR_A_DQS#5 [18]

DDR_A_DQS5 [18]

DDR_A_DQS#6 [18]

DDR_A_DQS6 [18]

DDR_A_DQS#7 [18]

DDR_A_DQS7 [18]

DDR_A_ALERT# [18]

DDR_A_PAR [18]

+V_DDR_REFA_R

PAD~D

PAD~D

@

T3

@

T4

DDR0_PAR,DDR0_ALERT# for

DDR4

UC1C

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

SKL-U

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

3 OF 20

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

H_DRAMRST#

AT13

SM_RCOMP0

AR18

SM_RCOMP1

AT18

SM_RCOMP2

AU18

DDR1_PAR,DDR1_ALERT# for DDR4

H_DRAMRST#

0.1U_0402_16V7K~D

RC1126

1

ESD@

2

H_DRAMRST# [7,18]

H_DRAMRST# [7,18]

Buffer with Op en Drai n Output For VTT power control

+1.2V_DDR

0.1U_0402_16V7K

DDR_VTT_CNTL

A A

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSOP5

12

UC14

CC57

Y

+3VS

12

5

4

RC123

100K_0402_5%

0.6V_DDR_VTT_ON [39]

DDR4 COMPENSATION SIGNALS

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

CAD Note:

Trace width=12~15 mil, Spacing=20 mils

Max trace length= 500 mil

1 2

RC5 121_0402_1%

1 2

RC6 80.6_0402_1%

1 2

RC7 100_0402_1%

place cap near DRAM_RES ET# PIN

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (2/14)

CPU (2/14)

CPU (2/14)

LA-F251P

LA-F251P

LA-F251P

7 55Tuesday, August 08, 2017

7 55Tuesday, August 08, 2017

7 55Tuesday, August 08, 2017

1

0.3

0.3

0.3

Vinafix.com

1 2

1 2

EMI@

1 2

PCH_SPI_CS2#[32]

PCH_SPI_D1[32]

PCH_SPI_D0[32]

5

PCH_SPI_D2

PCH_SPI_CS#0

1 2

FFS_INT1

PCH_SPI_CLK_PCH

RF@

CC1823

12P_0201_50V8J

PCH_SPI_CS2#

PCH_SPI_CLK_PCH

PCH_SPI_D1

PCH_SPI_D0

+1.8V_PRIM

SPI_MOSI= SPI_IO0

SPI_MISO= SPI_IO1

PCH EDS R0.7 p.235~236

PCH_SPI_CLK

PCH_SPI_D1

PCH_SPI_D0

PCH_SPI_D2

PCH_SPI_D3

PCH_SPI_CS#0

PCH_SPI_CS2#

TPM_PIRQ#[32]

FFS_INT1[27]

ESPI_ALERT#[22]

1 2

RC21 10K_0402_5%

XDP_SPI_IO2[14]

RC355/354 place to within 1100 mil of SPIO_MOSI/SPI0_IO2 pin for XDP

+3V_SPI

RC30 1K_0402_5%

CRB & Module design RC53 un-mount

RC53 4.7K_0402_5%

PCH_SPI_CLK

1 2

RC59 33_0201_5%

RC59 & CC1823 close to CPU

To SPI TPM

+3VS

RC1123 10K_0402_5%

PCH_SPI_CLK_PCH[32]

D D

C C

4

UC1E

AV2

AW3

AV3

AW2

AU4

AU3

AU2

AU1

AW13

AY11

XDP_SPI_SI[14]

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

C LINK

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL-U_BGA1356

1 2

RC355 1K_0402_1%

CMC@

1 2

RC354 1K_0402_1%

CMC@

SKL-U

SMBUS, SMLINK

GPP_B23/SML1ALERT#/PCHHOT#

LPC

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

PCH_SPI_D0

PCH_SPI_D2

3

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

5 OF 20

SML1CLK

SML1DATA

R7

SMBCLK

R8

SMBDATA

PCH_SMB_ALERT#

R10

SML0_SMBCLK

R9

SML0_SMBDATA

W2

GPP_C5

W1

W3

SML1CLK

V3

SML1DATA

GPP_B23

AM7

ESPI_IO0_R

AY13

ESPI_IO1_R

BA13

ESPI_IO2_R

BB13

ESPI_IO3_R

AY12

ESPI_CS#_R

BA12

ESPI_RESET#

BA11

ESPI_CLK_R ESPI_CLK_EC

AW9

AY9

AW11

1 2

RE449 15_0402_1%

1 2

RE450 15_0402_1%

1 2

RE451 15_0402_1%

1 2

RE452 15_0402_1%

1 2

RE453 0_0402_5%@

ESPI_RESET# [22]

1 2

EMI@

RC22

22_0402_5%

2

+3VS

SMBCLK

3 4

SMBDATA

ESPI_IO0 [22]

ESPI_IO1 [22]

ESPI_IO2 [22]

ESPI_IO3 [22]

ESPI_CS# [22]

1 2

@

RE454 0_0402_5%

CC1803

12P_0402_50V8J

RF@

2

1

GPU_THM_SMBCLK [22,34,51]

GPU_THM_SMBDAT [22,34,51]

QC2A

2

DMN66D0LDW-7_SOT363-6

1

6

5

QC2B

DMN66D0LDW-7_SOT363-6

SML1 -> EC,DGPU,THM

ESPI_CLK [22]

PCH_SMBCLK [18,27,33]

PCH_SMBDATA [18,27,33]

PCH_SMBDATA

PCH_SMBCLK

SMBCLK

SMBDATA

SML1CLK

SML1DATA

SML0_SMBCLK

SML0_SMBDATA

1

SMB -> DDR,CRT,FFS

12

RN192.2K_0402_5%

12

RN202.2K_0402_5%

+3VALW_PCH

1 2

RC12 1K_0402_5%

1 2

RC14 1K_0402_5%

1 2

RC15 1K_0402_5%

1 2

RC17 1K_0402_5%

1 2

RC19 1K_0402_5%

1 2

RC20 1K_0402_5%

+3VS

1 2

@

RC397 0_0402_5%

1 2

@

RC399 0_0402_5%

+3V_SPI

VCC

CLK

+3V_SPI

1 2

CC9

8

7

IO3

6

5

IO0

0.1U_0402_16V7K

1 2

+3VALW

B B

L1 Routing

To SPI ROM

Single SPI ROM_CS0# 16M SPI ROM (Confirmed by BIOS RD)

PCH_SPI_CS#0

PCH_SPI_D1

PCH_SPI_D0

PCH_SPI_CLK_PCH

PCH_SPI_D3

1 2

RC1125 0_0402_5%@

1 2

RC1120 33_0402_5%

1 2

RC1119 33_0402_5%

1 2

RC58 33_0402_5%

1 2

RC6666 33_0402_5%

1 2

RC60 33_0402_5%

@

RC1124 0_0402_5%

L2 Routing

PCH_SPI_D0_R

PCH_SPI_CLK_R

PCH_SPI_D3_R

PCH_SPI_CS#0_R

PCH_SPI_D1_R

PCH_SPI_D2_RPCH_SPI_D2

UC2

1

/CS

2

IO1

3

IO2

4

GND

W25Q128FVSIQ_SO8

Layout need meet L1 = L2

'

PCH_SMB_ALERT#

1 2

RC23 8.2K_0402_5%

! -!?

*"*

! 0-!1

'

GPP_C5

1 2

RC25 10K_0402_5%

.'&@($&

*"*

! 0-!1

+).@A7(3#& 9@ +

,, =(B'

GPP_B23

1 2

RC365 150K_0402_5%

@

!

!

!

CMC@

+3VALW_PCH

+3VALW_PCH

+3VALW_PCH

8!!?

*"*

A A

! 0-!1

!

!

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (3/14)

CPU (3/14)

CPU (3/14)

LA-F251P

LA-F251P

LA-F251P

8 55Tuesday, August 08, 2017

8 55Tuesday, August 08, 2017

8 55Tuesday, August 08, 2017

1

0.3

0.3

0.3

Vinafix.com

5

4

3

2

1

+3VALW_PCH

@

RC1106

10K_0402_5%

@

RC1107

10K_0402_5%

SKL-U

+1.8V_PRIM

12

RC370

10K_0402_5%

12

@

RC371

10K_0402_5%

PROJECT ID

Dali

Astro

VRAM ID

(PCBA VRAM Size C onfig.)

UMA

2G

4G

AMD

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D15/ISH_UART0_RTS#

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

12

RC372

10K_0402_5%

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_A12/BM_BUSY#/ISH_GP6

6 OF 20

PHASE ID

EVT

12

@

RC373

10K_0402_5%

PROJECT_ID

(GPP_A 21)

DVT1

DVT2

Pilot

0

1

VRAM_ID2

(GPP_D14)

0 0

0

1

1 1

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

VRAM_ID1

(GPP_B17)

1

0

DGPU_HOLD_RST#

IR_CAM_DET#

RTC_DET#

DGPU_PWR_EN

VRAM_ID2

IO_CBL_DET#

VGA_CBL_DET#

BOARD_ID1

PHASE_ID2

PHASE_ID1

PROJECT_IDKB_DET#

FFS_DET

PHASE_ID1

(GPP_A 19)

BOARD ID

KBL-U

KBL_RU

DGPU_HOLD_RST# [48]

IR_CAM_DET# [25]

RTC_DET# [20]

DGPU_PWR_EN [51,53]

FFS_INT2 [27]

PHASE_ID2

(GPP_A 18)

0 0

0

1

1 1

BOARD_ID1

(GPP_C 12)

RTC_DET#

SIO_EXT_WAKE#

DGPU_HOLD_RST#

IO_CBL_DET#

VGA_CBL_DET#

+1.8V_PRIM

12

FFS@

RC6673

10K_0402_5%

FFS_DET

12

NOFFS@

RC6674

10K_0402_5%

+3VS

1

BOARD_ID2

BOARD_ID1

1 2

RC384 10K_0402_5%

1 2

RC387 10K_0201_5%

1 2

RC383 10K_0402_5%

1 2

RC6670 10K_0402_5%

1 2

RC6671 10K_0402_5%

DGPU_PWR_EN

12

U42@

RC1129

10K_0402_5%

+3VS

12

1 2

RC359

10K_0402_5%

RC1140

150K_0402_5%

@

0

12

RC375

10K_0402_5%

BOARD ID

0

12

BOARD_ID2

(GPP_C 11)

0

U22@

RC1128

10K_0402_5%

1

UC1F

SOC_GPIOB15

SOC_GPIOB16

LCD_CBL_DET#

D D

+3VS

RC293 10K_0402_5%

RC292 10K_0402_5%

RC62 49.9K_0201_1%

RC63 49.9K_0201_1%

+3VALW_PCH

RC288 10K_0402_5%

C C

SOC_GPIOB15

SOC_GPIOB16

+3VALW_PCH

1 2

RC6669 10K_0402_5%

1 2

1 2

12

12

12

TO DGPU

RC204 0_0402_5%@

RC195 0_0402_5%@

1 2

RC186 4.7K_0402_5%@

IR_CAM_DET#

BLUETOOTH_EN

UART_2_CRXD_DTXD

UART_2_CTXD_DRXD

1 2

1 2

NRB_BIT

GPU_EVENT#

GC6_FB_EN3V3

DBC_EN[25]

BLUETOOTH_EN[29]

SIO_EXT_WAKE#[22]

KB_DET#[34]

I2C_SDA_TP[34]

I2C_SCL_TP[34]

GPU_EVENT# [51]

GC6_FB_EN3V3 [48,52]

VRAM_ID1

NRB_BIT

DBC_EN

BLUETOOTH_EN

LCD_CBL_DET#

BOARD_ID2

UART_2_CRXD_DTXD

UART_2_CTXD_DRXD

AN8

AP7

AP8

AR7

AM5

AN7

AP5

AN5

AB1

AB2

AB3

AD1

AD2

AD3

AD4

AH9

AH10

AH11

AH12

AF11

AF12

W4

U7

U6

U8

U9

LPSS ISH

GPP_B15/GSPI0_CS#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/UART0_RXD

GPP_C9/UART0_TXD

GPP_C10/UART0_RTS#

GPP_C11/UART0_CTS#

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_F6/I2C3_SDA

GPP_F7/I2C3_SCL

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

SKL-U_BGA1356

PHASE_ID2

PHASE_ID1

4G@

!

+5VALW

CVILU_CI1804M1VRA-NH

RC1106

10K_0402_5%

SD028100280

6

5

4

3

2

1

JWDB1

GND

GND

4

3

2

1

@

4G@

VRAM_ID1

VRAM_ID2

PROJECT_ID

+3VS

12

@

RC1104

10K_0402_5%

12

@

RC1105

10K_0402_5%

+1.8V_PRIM

12

ASTRO@

RC376

10K_0402_5%

12

DALI@

RC377

10K_0402_5%

12

12

*"*

! 0-!1

&(9

Win7 Debug solution

B B

A A

Option 2 : For Open Chassis Platforms

UART_2_CTXD_DRXD

UART_2_CRXD_DTXD

RC1105

10K_0402_5%

SD028100280

RC1104

2G@

10K_0402_5%

SD028100280

5

RC1107

2G@

10K_0402_5%

SD028100280

RC1105

UMA@

10K_0402_5%

SD028100280

RC1107

UMA@

10K_0402_5%

SD028100280

4

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (4/14)

CPU (4/14)

CPU (4/14)

LA-F251P

LA-F251P

LA-F251P

9 55Tuesday, August 08, 2017

9 55Tuesday, August 08, 2017

9 55Tuesday, August 08, 2017

1

0.3

0.3

0.3

Vinafix.com

5

4

3

2

1

UC1H

PCIE/US B3/SATA

D D

GPU

LAN

WLAN

HDD

C C

SSD

B B

PCIE_CRX_GTX_N1[48]

PCIE_CRX_GTX_P1[48]

PCIE_CTX_C_GRX_N1[48]

PCIE_CTX_C_GRX_P1[48]

PCIE_CRX_GTX_N2[48]

PCIE_CRX_GTX_P2[48]

PCIE_CTX_C_GRX_N2[48]

PCIE_CTX_C_GRX_P2[48]

PCIE_CRX_GTX_N3[48]

PCIE_CRX_GTX_P3[48]

PCIE_CTX_C_GRX_N3[48]

PCIE_CTX_C_GRX_P3[48]

PCIE_CRX_GTX_N4[48]

PCIE_CRX_GTX_P4[48]

PCIE_CTX_C_GRX_N4[48]

PCIE_CTX_C_GRX_P4[48]

PCIE_PRX_LANTX_N5[30]

PCIE_PRX_LANTX_P5[30]

PCIE_PTX_C_LANRX_N5[30]

PCIE_PTX_C_LANRX_P5[30]

PCIE_PRX_WLANTX_N6[29]

PCIE_PRX_WLANTX_P6[29]

PCIE_PTX_C_WLANRX_N6[29]

PCIE_PTX_C_WLANRX_P6[29]

SATA3_PRX_HDDTX_N0[27]

SATA3_PRX_HDDTX_P0[27]

SATA3_PTX_HDDRX_N0[27]

SATA3_PTX_HDDRX_P0[27]

PCIE_PRX_SSDTX_N9[28]

PCIE_PRX_SSDTX_P9[28]

PCIE_PTX_SSDRX_N9[28]

PCIE_PTX_SSDRX_P9[28]

PCIE_PRX_SSDTX_N10[28]

PCIE_PRX_SSDTX_P10[28]

PCIE_PTX_SSDRX_N10[28]

PCIE_PTX_SSDRX_P10[28]

PCIE_PRX_SSDTX_N11[28]

PCIE_PRX_SSDTX_P11[28]

PCIE_PTX_SSDRX_N11[28]

PCIE_PTX_SSDRX_P11[28]

PCIE_PRX_SSDTX_N12[28]

PCIE_PRX_SSDTX_P12[28]

PCIE_PTX_SSDRX_N12[28]

PCIE_PTX_SSDRX_P12[28]

CC1813 0.22U_0402_16V7K

CC1812 0.22U_0402_16V7K

CC1814 0.22U_0402_16V7K

CC1811 0.22U_0402_16V7K

1 2

CC17 0.22U_0402_16V7KDIS@

1 2

DIS@

1 2

CC18 0.22U_0402_16V7K

DIS@

1 2

CC19 0.22U_0402_16V7K

DIS@

1 2

CC20 0.22U_0402_16V7K

DIS@

1 2

DIS@

1 2

DIS@

1 2

DIS@

1 2

CC135 0.1U_0402_10V7K

1 2

CC136 0.1U_0402_10V7K

1 2

CC1815 0.1U_0402_10V7K

1 2

CC1816 0.1U_0402_10V7K

PCIE_PRX_SSDTX_N9

PCIE_PRX_SSDTX_P9

PCIE_PTX_SSDRX_N9

PCIE_PTX_SSDRX_P9

PCIE_PRX_SSDTX_N10

PCIE_PRX_SSDTX_P10

PCIE_PTX_SSDRX_N10

PCIE_PTX_SSDRX_P10

1 2

RC45 100_0402_1%

PCIE_PRX_SSDTX_N11

PCIE_PRX_SSDTX_P11

PCIE_PTX_SSDRX_N11

PCIE_PTX_SSDRX_P11

PCIE_PRX_SSDTX_N12

PCIE_PRX_SSDTX_P12

PCIE_PTX_SSDRX_N12

PCIE_PTX_SSDRX_P12

PCIE_CRX_GTX_N1

PCIE_CRX_GTX_P1

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_P1

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P2

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_P2

PCIE_CRX_GTX_N3

PCIE_CRX_GTX_P3

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_P3

PCIE_CRX_GTX_N4

PCIE_CRX_GTX_P4

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_P4

PCIE_PRX_LANTX_N5

PCIE_PRX_LANTX_P5

PCIE_PTX_LANRX_N5

PCIE_PTX_LANRX_P5

PCIE_PRX_WLANTX_N6

PCIE_PRX_WLANTX_P6

PCIE_PTX_WLANRX_N6

PCIE_PTX_WLANRX_P6

SATA3_PTX_HDDRX_N0

SATA3_PTX_HDDRX_P0

PCIE_RCOMPN

PCIE_RCOMPP

XDP_PRDY#[14]

XDP_PREQ#[14]

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKL-U_BGA1356

SKL-U

SSIC / USB3

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB2

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

8 OF 20

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

USBCOMP

USB2_ID

AG3

USB2_VBUSSENSE

AG4

USB_OC#0

A9

USB_OC#1

C9

USB_OC#2

D9

USB_OC#3

B9

J1

SIO_EXT_SCI#

J2

J3

H2

GPP_E1 GPP_E1 SSD_PEDET

H3

SSD_PEDET

G4

SATA_LED#

H1

USB3_CRX_DTX_N1 [23]

USB3_CRX_DTX_P1 [23]

USB3_CTX_DRX_N1 [23]

USB3_CTX_DRX_P1 [23]

USB3_CRX_DTX_N2 [23]

USB3_CRX_DTX_P2 [23]

USB3_CTX_DRX_N2 [23]

USB3_CTX_DRX_P2 [23]

USB3_CRX_DTX_N3 [33]

USB3_CRX_DTX_P3 [33]

USB3_CTX_DRX_N3 [33]

USB3_CTX_DRX_P3 [33]

USB_PN1 [24]

USB_PP1 [24]

USB_PN2 [23]

USB_PP2 [23]

USB_PN3 [33]

USB_PP3 [33]

USB_PN4 [33]

USB_PP4 [33]

USB_PN5 [25]

USB_PP5 [25]

USB_PN6 [33]

USB_PP6 [33]

USB_PN7 [29]

USB_PP7 [29]

USB_PN8 [25]

USB_PP8 [25]

USB_PN9 [33]

USB_PP9 [33]

1 2

RC44 113_0402_1%

1 2

RC366 1K_0402_5%

1 2

RC393 1K_0201_5%

USB_OC#0 [24]

USB_OC#1 [24]

HDD_DEVSLP [27]

SSD_DEVSLP [28]

SSD_PEDET [28]

SATA_LED# [25]

USB3 Port 0

USB3 Port 1

USB3 Port 2

USB3 Port 0

USB3 Port 1

USB3 Port 2

USB2 Port 0

HD CAM

Card Reader

BT

Touch Screen

Finger Printer

1 2

0_0402_5%

RC6536

@

USB_OC#3

USB_OC#0

USB_OC#1

USB_OC#2

SSD_PEDET

SIO_EXT_SCI#

SATA_LED#

+3VALW_PCH

RPC3

4 5

3

6

2

7

1

8

10K_8P4R_5%

RC2222

1 2

10K_0402_5%

1 2

RC237 10K_0402_5%

1 2

RC248 10K_0402_5%

+3VS

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (5/14)

CPU (5/14)

CPU (5/14)

LA-F251P

LA-F251P

LA-F251P

10 55Tuesday, August 08, 2017

10 55Tuesday, August 08, 2017

10 55Tuesday, August 08, 2017

1

0.3

0.3

0.3

Vinafix.com

5

CLK_PEG_VGA#[48]

GPU

D D

WLAN

LAN

SSD

C C

CC1806

CC1807

CC1808

CLK_PCIE_WLAN_N1[29]

CLK_PCIE_WLAN_P1[29]

CLK_PCIE_WLAN_REQ#[29]

CLK_PCIE_LAN_N2[30]

CLK_PCIE_LAN_P2[30]

CLK_PCIE_LAN_REQ#[30]

CLK_PCIE_SSD_N3[28]

CLK_PCIE_SSD_P3[28]

CLK_PCIE_SSD_REQ#[28]

12

100P_0402_50V8J

@ESD@

12

100P_0201_50V8J

@ESD@

12

100P_0402_50V8J

@ESD@

CLK_PEG_VGA[48]

PEG_CLKREQ#[48]

PCH_PLTRST#

SYS_RESET#

VCCST_PWRGD

RC1112 0_0402_5%@

RC1113 0_0402_5%@

RC189 10K_0402_5%

+3VS

RC1114 0_0402_5%@

RC1115 0_0402_5%@

RC47 10K_0402_5%

+3VS

RC1116 0_0402_5%@

RC1117 0_0402_5%@

RC50 10K_0402_5%

+3VS

RC6655 0_0402_5%@

RC1736 0_0402_5%@

RC6654 10K_0402_5%

+3VS

PCH_PLTRST#

SN74AHC1G08DCKR_SC70-5

12

12

1 2

12

12

1 2

12

12

1 2

1 2

RC1109

1 2

0.1U_0402_10V7K

UC7

+3.3V_ALW_DSW

+3VS

12

12

CLK_PEG_VGA#_R

CLK_PEG_VGA_R

CLK_PCIE_WLAN_N1_R

CLK_PCIE_WLAN_P1_R

CLK_PCIE_LAN_N2_R

CLK_PCIE_LAN_P2_R

CLK_PCIE_SSD_N3_R

CLK_PCIE_SSD_P3_R

CLK_PCIE_SSD_REQ#

+3VS

5

1

P

IN1

4

O

2

IN2

1 2

RC70 10K_0402_5%

1 2

RC291 10K_0402_5%

12

G

3

LAN_WAKE#

SYS_RESET#

PLT_RST#

RC65

100K_0402_5%

Close to CPU side

B B

@

T9

PAD~D

@

1 2

POK

1M_0402_5%

12

RC220

@

SYS_PWROK

PCH_DPWROK

+$.$#.

PCH_RSMRST#[22]

5

PCH_RSMRST#_Q

POK[36,38,40,41]

POK

1 2

RC216 0_0402_5%@

+3VALW

5

1

P

IN1

O

2

IN2

G

UZ6

3

SN74AHC1G08DCKR_SC70-5

PCIE_WAKE#[22,28,30]

LANWAKE#[22]

4

1 2

RC6657 10K_0402_5%

POK

RC1139 0_0402_5%

A A

1U_0402_6.3V6K

12

CC266

4

UC1J

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

SKL-U_BGA1356

PLT_RST# [25,28,29,30,32,48]

SIO_SLP_LAN#

PCH_BATLOW#

AC_PRESENT

SIO_PWRBTN#

1.2V_VTT_PWRGD[39] IMVP_VR_ON [42]

1 2

RC75 10K_0402_5%

RC395 0_0402_5%@

RC391 0_0402_5%

PCH_RSMRST#_Q

4

1 2

RC68 10K_0402_5%@

1 2

RC72 8.2K_0402_5%

1 2

RC243 300K_0402_5%

RC1102

CC1822

0.1U_0402_10V7K

1 2

RC78 60.4_0402_1%

1 2

1 2

@

PCH_RSMRST#_Q [14]

SKL_U LT

CLOCK SIGNALS

12

@

100K_0402_5%

1 2

RC392 0_0402_5%

1

@

2

PCH_RSMRST#_Q

SYS_PWROK[22]

RESET_OUT#[22]

@

T4989

PCH_PCIE_WAKE#

LAN_WAKE#

RTCRST_ON[22]

+3VALW

+3.3V_ALW_DSW

@

PCH_PLTRST#

SYS_RESET#

H_CPUPWRGD

VCCST_PWRGDH_VCCST_PWRGD

PCH_DPWROK

PAD~D

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

SRTCRST#

RTCRST#

12

R1902

10K_0402_5%

+3VS

RC388

1K_0402_5%

1 2

ALL_SYS_PWRGD

RC1134 0_0402_5%

UC1K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL-U_BGA1356

3

1 2

SUSCLK

RC48 1K_0402_5%

F43

E43

BA17

SUSCLK

XTAL24_IN

E37

XTAL24_OUT

E35

XCLK_BIASREF

E42

PCH_RTCX1

AM18

RTCX1

RTCX2

10 OF 20

SIO_SLP_S3#

1 2

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

PCH_RTCX2

AM20

AN18

SRTCRST#

AM16

PCH_RTCRST#

S

Q1901

2N7002K_SOT23-3

RC130 10K_0402_5%

@

SYSTEM POWER MANAGEMENT

3

1 2

RC52 2.7K_0402_1%

RC56 20K_0402_5%

RC57 20K_0402_5%

2

G

13

D

DZ1702

1 2

RB751S40T1G_SOD523-2

1 2

2.2U_0402_6.3V6M

ALL_SYS_PWRGD [22,38]

SKL-U

CC24 1U_0402_6.3V6K

CC25 1U_0402_6.3V6K

SUSCLK [22,29]

+1.0V_CLK5

1 2

1 2

1 2

1 2

12

CLRP1SHORT PADS

@

For S3 timing issue

2

CC93

GPP_B11/EXT_PWR_GATE#

3

74AUP1G07GW_TSSOP5

1 2

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B2/VRALERT#

2

+$%&$9'7

XTAL24_IN

XTAL24_OUT

PCH_RTCX1

PCH_RTCX2

+RTC_CELL

+3VALW

12

CC18210.1U_0402_10V7K

UC13

NC1VCC

A

GND

11 OF 20

5

4

Y

ALL_SYS_PWRGD ALL_SYS_PWRGD_R

SIO_SLP_SUS#

AT11

SIO_SLP_S3#

AP15

BA16

AY16

SIO_SLP_SUS#

AN15

SIO_SLP_LAN#

AW15

SIO_SLP_WLAN#

BB17

SIO_SLP_A#

AN16

BA15

AC_PRESENT

AY15

PCH_BATLOW#

AU13

AU11

PME#

AP16

INTRUDER#

MPHYP_PWR_EN

AM10

AM11

VRALERT#

Buffer with Open Drain Output For VTT power co ntrol

ALL_SYS_PWRGD

ALL_SYS_PWRGD_R

1 2

@

RC1136 0_0402_5%

1 2

@

RC1137 0_0402_5%

SIO_SLP_S0# [16,32]

SIO_SLP_S3# [16,35]

SIO_SLP_S4# [16,39,41]

SIO_SLP_S5# [37]

SIO_PWRBTN# [22]

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

@

T4938

@

T4945

@

T4975

@

T115

@

T4974

1 2

1 2

DELL CONFIDENTIAL/PROPRIETARY

2

1

RC6663

U22@

33_0201_1%

RC6664

U22@

33_0402_1%

1M_0201_1%

RC46

U22@

1 2

RC54

10M_0402_5%

1 2

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSOP5

12

DZ4RB751S40T1G_SOD523-2

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

XTAL24_IN_R

3

4

YC1

24MHZ_12PF_7M24090001

U22@

1

2

XTAL24_OUT_R

12

YC2

32.768KHZ 9PF 20PPM 9H03280012

12

CC18200.1U_0402_10V7K

UC12

+1.0V_VCCST+3VALW

5

4

Y

INTRUDER#

VRALERT#

ACAV_IN [22,36,37]

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

CPU (6/14)

CPU (6/14)

CPU (6/14)

LA-F251P

LA-F251P

LA-F251P

CC21

1 2

15P_0201_50V8J

U22@

CC22

1 2

15P_0201_50V8J

U22@

CC23

1 2

5.6P_0402_50V8C

20ppm / 9pF

ESR <50kohm (MAX)

CC26

1 2

5.6P_0402_50V8C

12

RC1118

1K_0402_5%

H_VCCST_PWRGD

12

RC69 1M_0402_1%

1 2

RC73 10K_0402_5%

11 55Tuesday, August 08, 2017

11 55Tuesday, August 08, 2017

11 55Tuesday, August 08, 2017

1

+RTC_CELL

+3VALW

0.3

0.3

0.3

Vinafix.com

5

+1.0V_VCCST

RC79 49.9_0402_1%

RC80 1K_0402_5%

+1.0V_VCCSTG

RC83 1K_0402_5%

D D

+3VS

RC272 10K_0402_5%

RC277 10K_0402_5%

CC1809

1 2

@

1 2

1 2

1 2

1 2

@ESD@

H_CATERR#

H_THERMTRIP#

H_PROCHOT#

TOUCHPAD_INTR#_D

TOUCH_SCREEN_PD#

TOUCH_SCREEN_PD#[25]

H_PROCHOT#_R

12

100P_0402_50V8J

PECI_EC[22]

H_PROCHOT#[22,36,37,42]

TOUCH_SCREEN_PD# TOUCH_SCREEN_PD#_R

1 2

RC84 499_0402_1%

8/19 DG0.9

1 2

@

RC394 0_0402_5%

12

Close to CPU side

RC88

H_PROCHOT#_RH_PROCHOT#

T4942

T4941

T10

T11

12

49.9_0402_1%

4

@

PAD~D

@

PAD~D

@

PAD~D

@

PAD~D

TOUCHPAD_INTR#_D

CPU_POPIRCOMP

PCH_POPIRCOMP

EDRAM_OPIO_RCOMP

12

RC89

RC90

49.9_0402_1%

49.9_0402_1%

H_CATERR#

H_THERMTRIP#

XDP_OBS0_R

XDP_OBS1_R

XDP_OBS2_R

XDP_OBS3_R

EOPIO_RCOMP

12

RC91

49.9_0402_1%

AT16

AU16

D63

A54

C65

C63

A65

C55

D55

B54

C56

A6

A7

BA5

AY5

H66

H65

SKL-U_BGA1356

UC1D

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

CPU MISC

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

SKL-U

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

3

JTAGX

4 OF 20

CPU_XDP_TCK0

B61

SOC_XDP_TDI

D60

SOC_XDP_TDO

A61

SOC_XDP_TMS

C60

SOC_XDP_TRST#

B59

B56

SOC_XDP_TDI

D59

SOC_XDP_TDO

A56

SOC_XDP_TMS

C59

SOC_XDP_TRST#

C61

CPU_XDP_TCK0

A59

CPU_XDP_TCK0 [14]

SOC_XDP_TDI [14]

SOC_XDP_TDO [14]

SOC_XDP_TMS [14]

SOC_XDP_TRST# [14]

PCH_JTAG_TCK1 [14]

2

1

C C

TP_WAKE_KBC#[22,34]

+:- :

! D ! E +3 $9F $( 'G #6 )( & +‧

* "* D ! E + #'3 $9F $(' #6)( & +‧

B B

+3VALW_PCH +3VALW_PCH

1 2

RC183 8.2K_0402_5%

@

SPKR

*"*

! 0-!1

A A

!

!

5

DZ3

RB751S40T1G_SOD523-2

1 2

PROJECT ID

TOUCHPAD_INTR#_D

HDA_CODEC_SYNC[21]

HDA_CODEC_BITCLK[21]

HDA_CODEC_SDOUT[21]

ME_FWP[22]

HDA_CODEC_RST#[21]

HDA_CODEC_BITCLK

12P_0402_50V8J

1

CC27

RF@

2

Close to RC93

1 2

RC187 4.7K_0402_5%

@

+3VS

RC1111 10K_0402_5%

HDA_SDOUT

-3(B% &B$.6 &$#.A C&.)&

*"*

! 0-!1

PROJECT_ID1

(GPP_F1)

!

!

PROJECT_ID2

(GPP_F0)

RC93 near U C1E, the R/C need between C PU ball out and VIA

EMI@

1 2

PROJECT_ID1

PROJECT_ID0

4

1 2

RC92 33_0402_5%

1 2

RC93 33_0402_5%

1 2

RC94 33_0402_5%

1 2

RC223 1K_0402_5%

1 2

RC95 33_0402_5%

@

DGPU_ALL_PGOOD

DGPU_ALL_PGOOD[48]

+1.8V_PRIM+1.8V_PRIM

12

@

RC6677

10K_0402_5%

12

@

RC6678

10K_0402_5%

SPKR[21]

12

@

RC6675

10K_0402_5%

12

@

RC6676

10K_0402_5%

UC1G

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

HDA_SDIN0[21]

HDA_RST#

PROJECT_ID1

PROJECT_ID0

TPM_ID

DGPU_ALL_PGOOD

BA22

AY22

BB22

BA21

AY21

AW22

J5

AY20

AW20

AK7

AK6

AK9

AK10

H5

D7

D8

C8

AW5

TPM_ID

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

GPP_D19/DMIC_CLK0

GPP_D20/DMIC_DATA0

GPP_D17/DMIC_CLK1

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

SKL-U_BGA1356

+3VS

12

HWTPM@

RC1130

10K_0402_5%

12

SWTPM@

RC1131

10K_0402_5%

AUDIO

SKL-U

TPM ID

SW_TPM

HW_TPM

SDIO/SDXC

GPP_A17/SD_PWR_EN#/ISH_GP7

TPM_ID

(GPP_D17)

0

1

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A16/SD_1P8_SEL

SD_RCOMP

GPP_F23

7 OF 20

2

+3VS

WWAN_CBL_DET#

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

GC6_THM_DIS#

SD_RCOMP

RC6672 10K_0402_5%

RC1108 10K_0201_5%

RC96 200_0402_1%

GC6_THM_DIS# [22]

KB_LED_BL_DET [34]

1 2

1 2

12

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (7/14)

CPU (7/14)

CPU (7/14)

LA-F251P

LA-F251P

LA-F251P

1

0.3

0.3

12 55Tuesday, August 08, 2017

12 55Tuesday, August 08, 2017

12 55Tuesday, August 08, 2017

0.3

Vinafix.com

5

D D

4

3

2

1

CFG[2][5][6][7] for SKYLAKE-H CPU CFG strap pin

1 2

RC113 10K_0402_1%

(33 &B& B&H#&'$&

*"*0-!1

!

C C

1 2

RC109 10K_0402_1%

&&'(I3&

*"*

! 0-!1

B B

CFG0

@

B(3302(3 6&( . '1

B( 3 3

CFG4

.B( I3& )

'(I3&)

1 2

RC112 10K_0402_1%

@

1 2

RC110 10K_0402_1%

@

CFG1

CFG3

+1.0V_XDP

XDP_ITP_PMODE[14]

CFG16[14]

CFG17[14]

CFG18[14]

CFG19[14]

12

12

CFG0

CFG1

CFG3

CFG4

CFG_RCOMP

CFG0[14]

CFG1[14]

CFG2[14]

CFG3[14]

CFG4[14]

CFG5[14]

CFG6[14]

CFG7[14]

CFG8[14]

CFG9[14]

CFG10[14]

CFG11[14]

CFG12[14]

CFG13[14]

CFG14[14]

CFG15[14]

RC114 49.9_0402_1%

CMC@

RC115 1.5K_0402_5%

@

T16

PAD~D

@

T17

PAD~D

AL25

AL27

BA70

BA68

E68

B67

D65

D67

E70

C68

D68

C67

F71

G69

F70

G68

H70

G71

H69

G70

E63

F63

E66

F66

E60

E8

AY2

AY1

D1

D3

K46

K45

C71

B70

F60

A52

J71

J68

F65

G65

F61

E61

UC1S

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG[18]

CFG[19]

CFG_RCOMP

ITP_PMODE

RSVD_AY2

RSVD_AY1

RSVD_D1

RSVD_D3

RSVD_K46

RSVD_K45

RSVD_AL25

RSVD_AL27

RSVD_C71

RSVD_B70

RSVD_F60

RSVD_A52

RSVD_TP_BA70

RSVD_TP_BA68

RSVD_J71

RSVD_J68

VSS_F65

VSS_G65

RSVD_F61

RSVD_E61

SKL-U_BGA1356

RESERVED SIGNALS-1

SKL-U

RSVD_TP_BB68

RSVD_TP_BB69

RSVD_TP_AK13

RSVD_TP_AK12

RSVD_BB2

RSVD_BA3

RSVD_D5

RSVD_D4

RSVD_B2

RSVD_C2

RSVD_B3

RSVD_A3

RSVD_AW1

RSVD_E1

RSVD_E2

RSVD_BA4

RSVD_BB4

RSVD_A4

RSVD_C4

RSVD_A69

RSVD_B69

RSVD_AY3

RSVD_D71

RSVD_C70

RSVD_C54

RSVD_D54

VSS_AY71

ZVM#

RSVD_TP_AW71

RSVD_TP_AW70

MSM#

PROC_SELECT#

19 OF 20

BB68

BB69

AK13

AK12

BB2

BA3

AU5

TP5

AT5

TP6

D5

D4

B2

C2

B3

A3