Dell Inspiron 14 3462 Schematics

Vinafix.com

5

D D

4

3

2

1

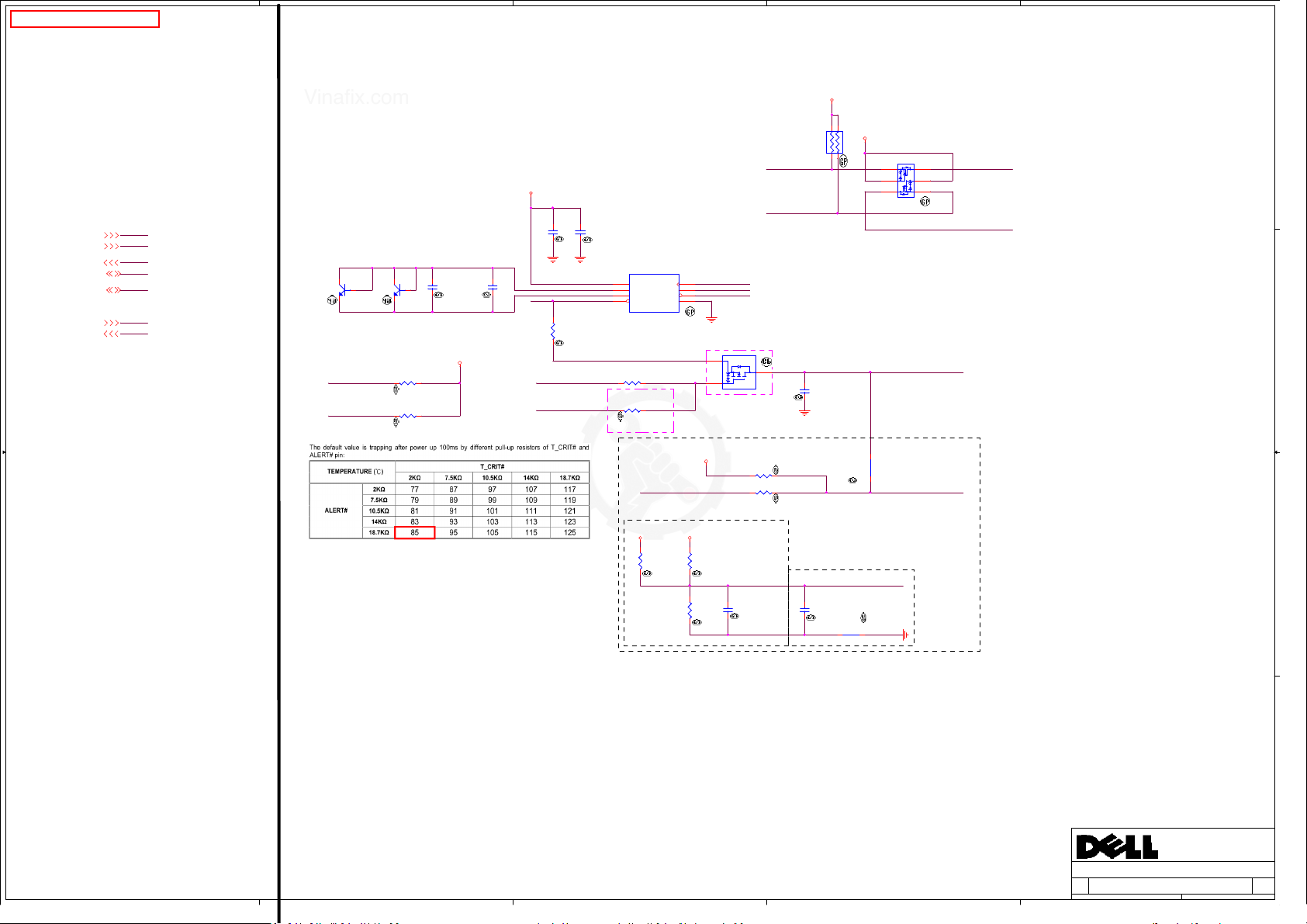

Turis 14" 15" 2SP Schematic

Apollo Lake

C C

2016-09-07

REV : A00

DY : None Installed

B B

A A

5

UMA: UMA only installed

4

3

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Cover Page

Cover Page

Cover Page

Turis APL UMA

Turis APL UMA

Turis APL UMA

1

X02

X02

1 106Wednesd ay, September 07, 20 16

1 106Wednesd ay, September 07, 20 16

1 106Wednesd ay, September 07, 20 16

X02

Vinafix.com

5

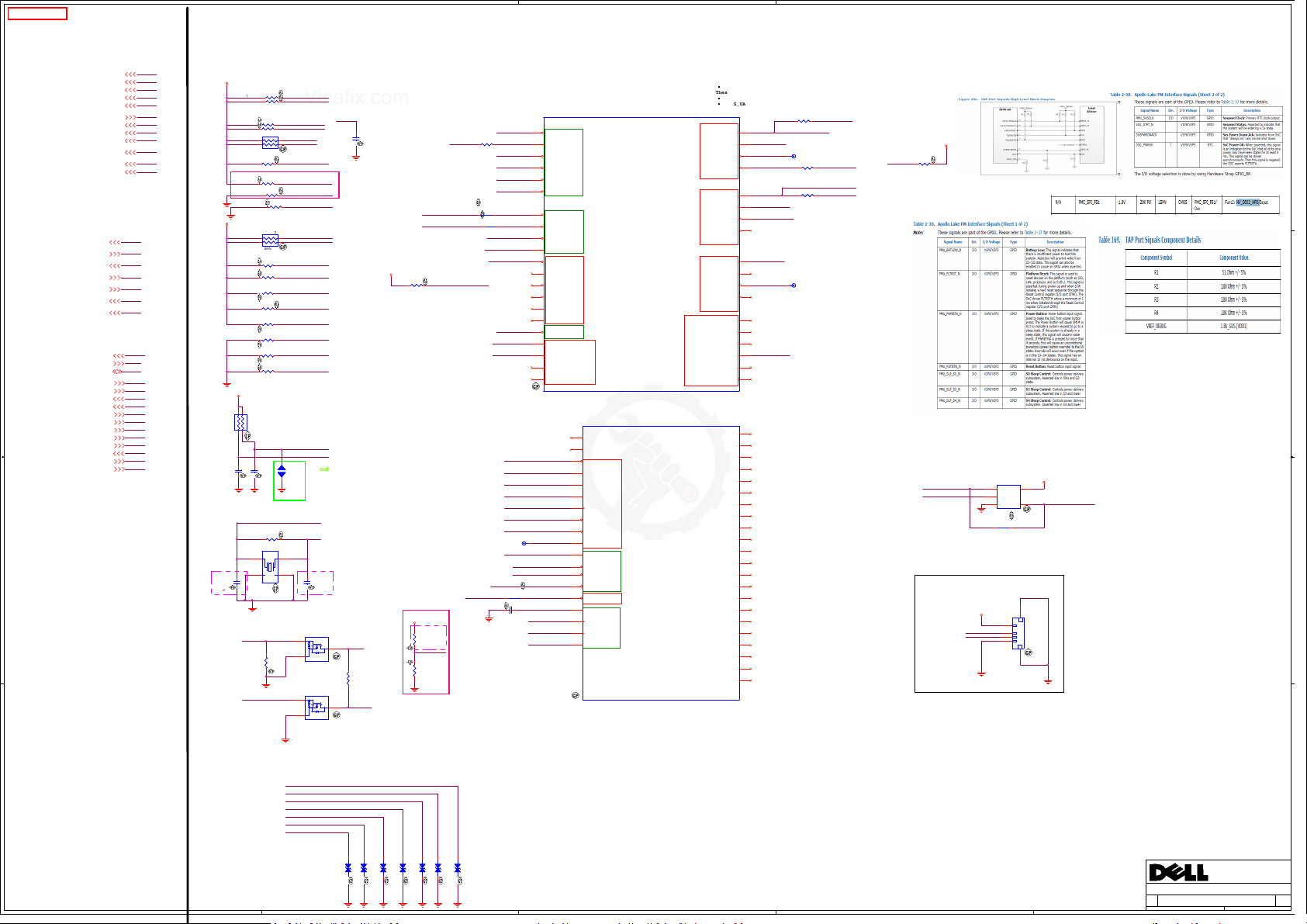

Project Code : 4PD0AG010001

PCB P/N : 16823-1

Revision : A00

D D

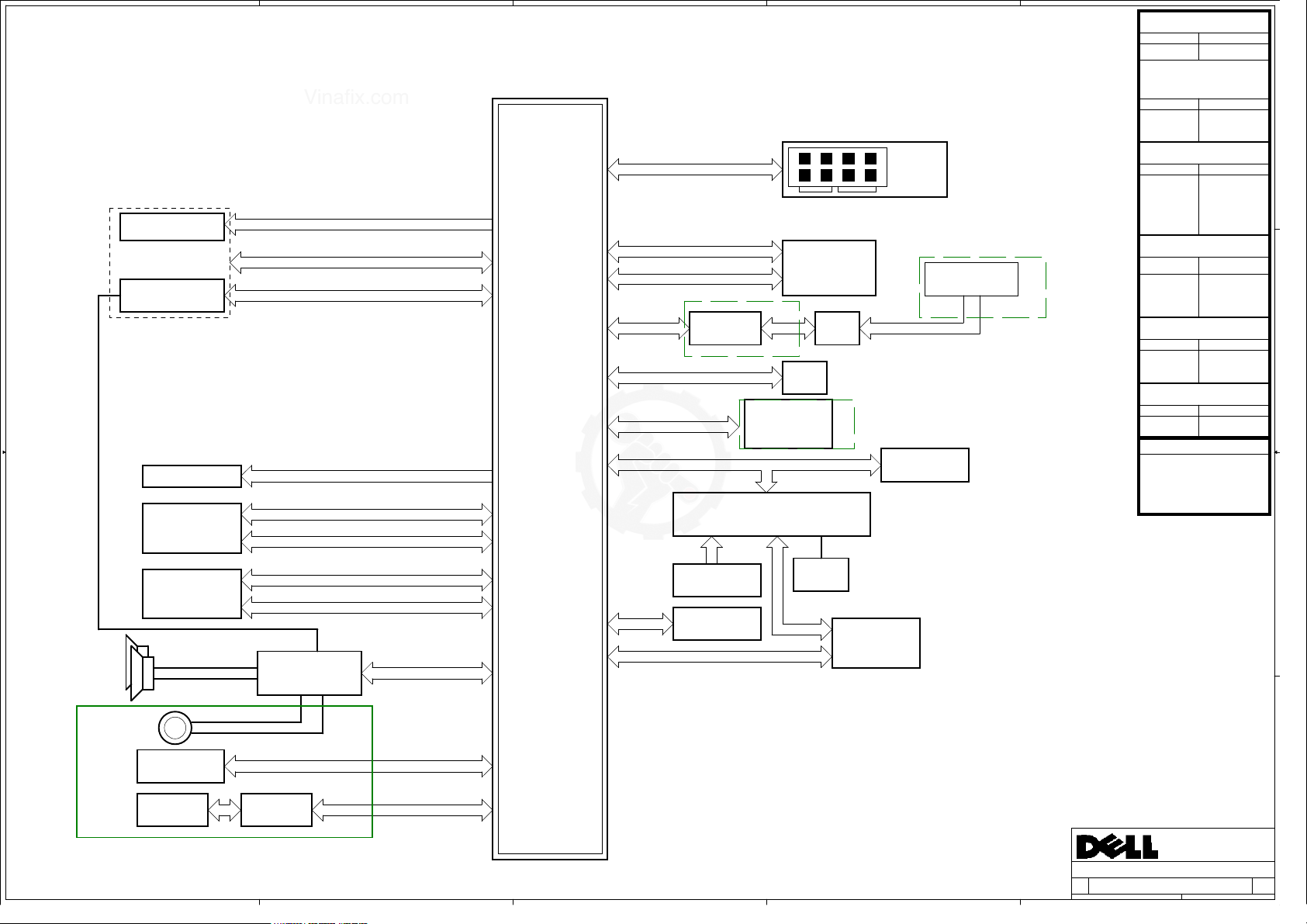

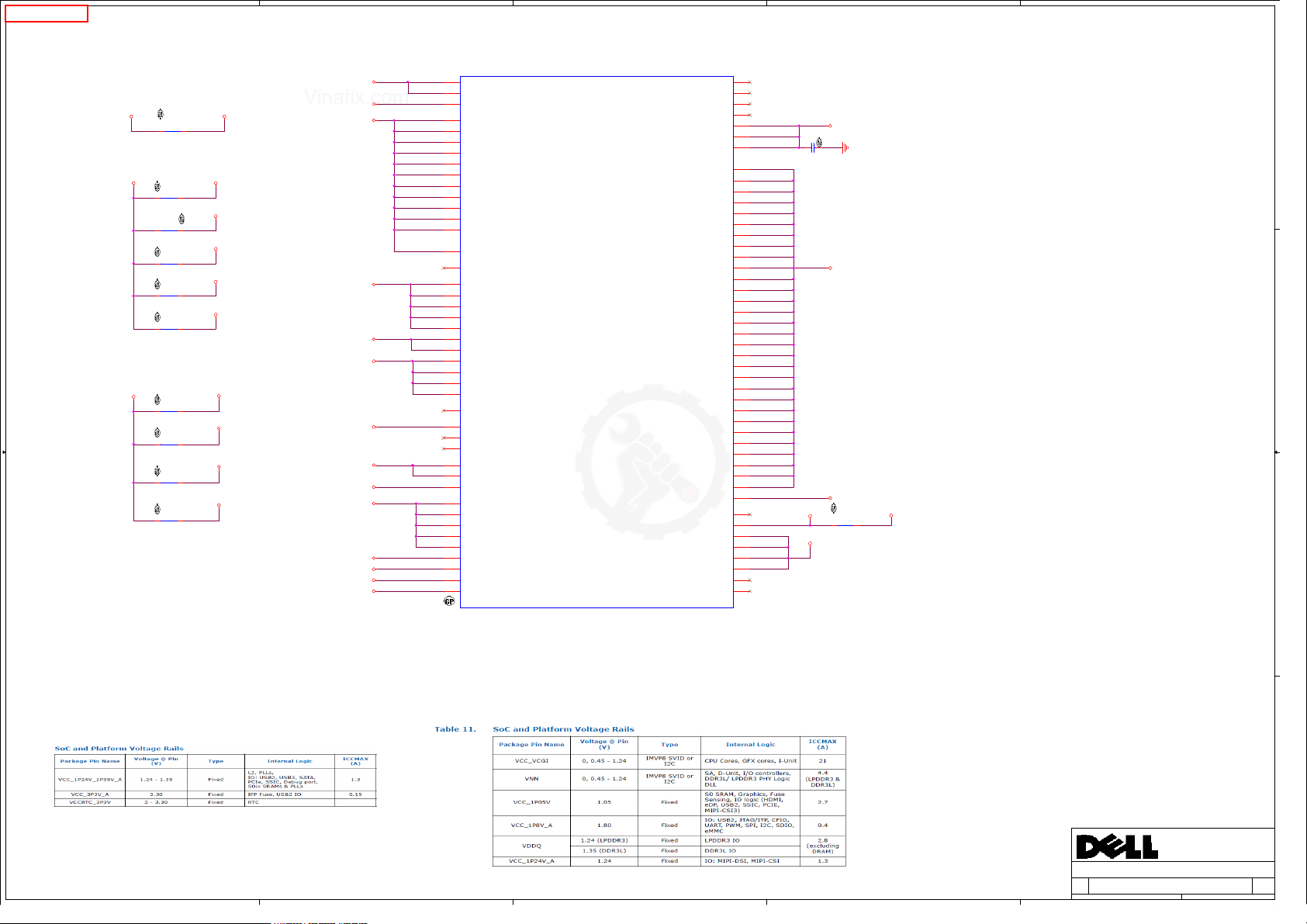

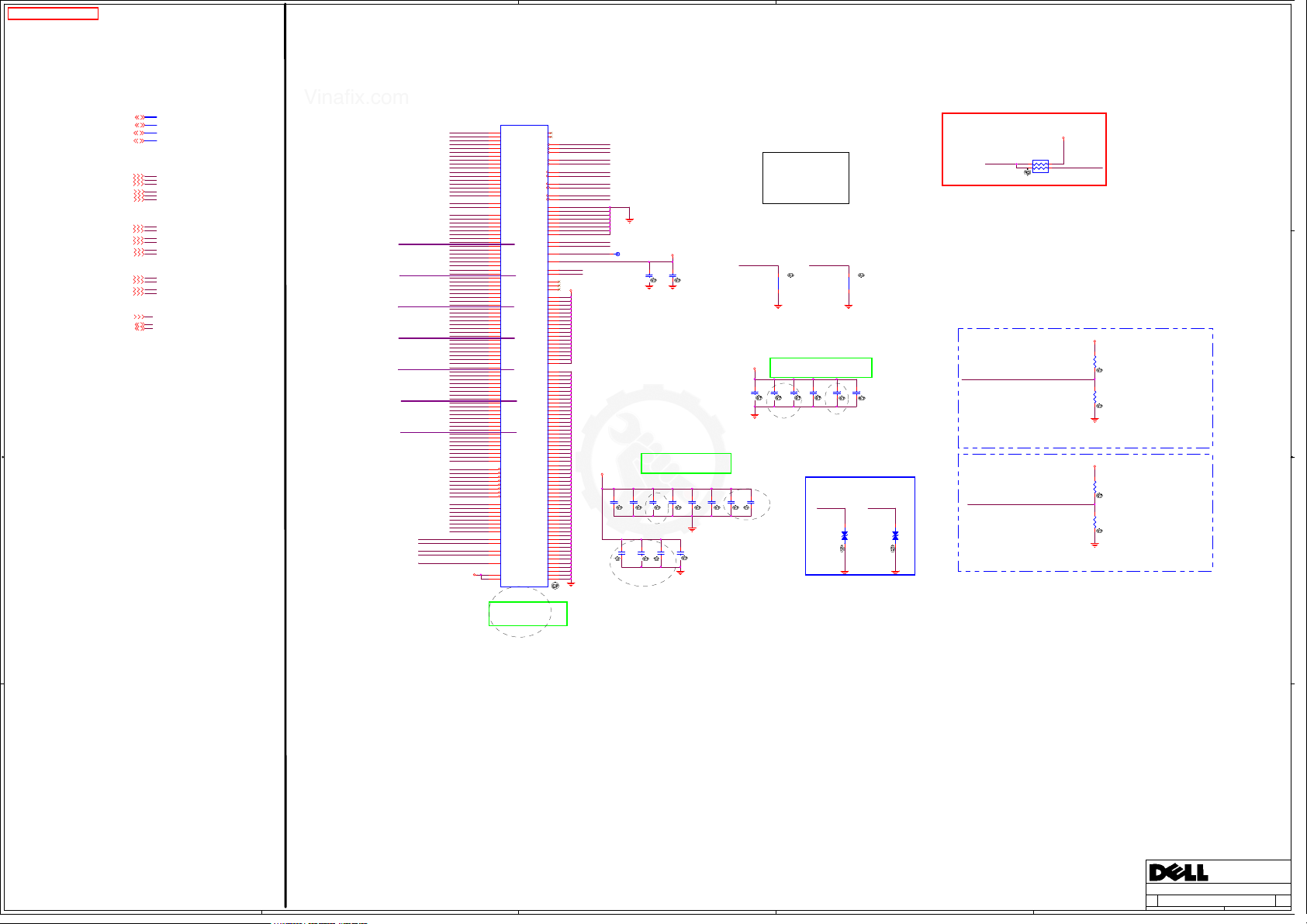

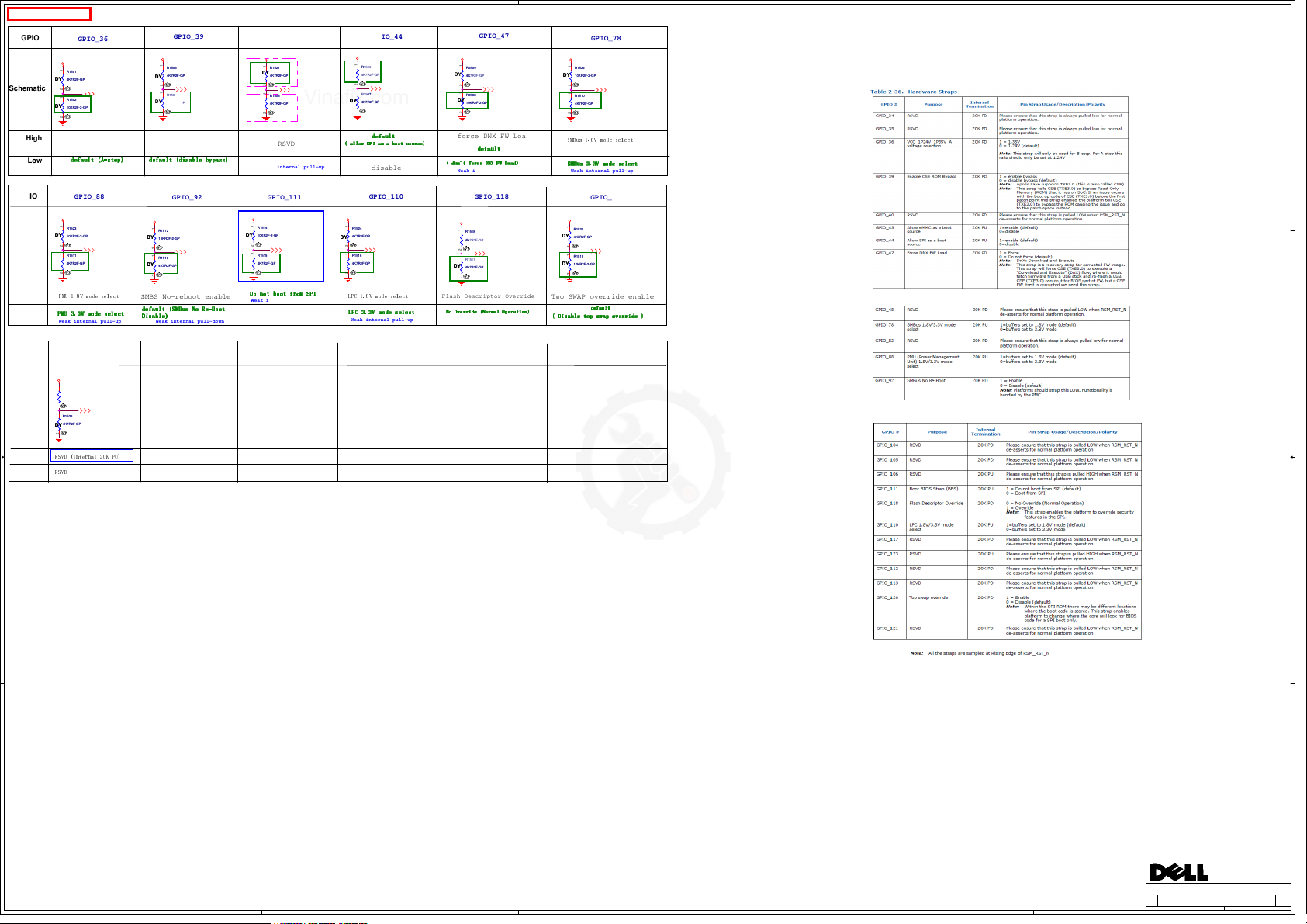

TURIS 14" 15" 2SP Apollo Lake Block Diagram

14"/15" LCD

Touch Panel

Camera

Digital MIC

C C

HDMI V1.4a

Left side

USB1(USB3.0)

B B

Left side

USB2(USB3.0)

4

Intel CPU

Apollo Lake

BGA1296

Package

eDP

USB2.0

USB2.0

DDI1

USB2.0

USB3.0

USB2.0

31*24*1.3

DDI (2) / EDP1.4

MDSI (3) / MCSI (4)

USB 3.0 (6) / 2.0 ports (8)

SATA (2) / PCIE (4)

HDA / I2S (2)

I2C (8) / ISH_I2C (2) / SPI

SD / EMMC

LPC I/F / SMBS (1) / UART (2)

3

DDR3L 1866MHz Channel A

PCIe

USB2.0

SATA (Gen3)

Re-driver

SN75LVCP601RTJR

Reserve

SATA (Gen1)

eMMC BUS

LPC BUS

SPI

Non Share Rom

128K

eMMC

Reserve

KBC

NUVOTON

NPCE985PB1

NGFF WLAN

802.11a/b/g/n

BT V4.0 combo

HDD

ODD

63

Int. KB

65

2

DDR3L 1600

SODIMM A

12

G Sensor

LNG2DMTR-GP

int

LPC debug port

67

Reserve

1

CHARGER

BQ24727RGRR

INPUTS

19V_DCBATOUT

SYSTEM DC/DC

TPS51225RUKR

INPUTS

19V_DCBATOUT

CPU DC/DC PMIC

RT9610BZQW

INPUTS

5V_S5

1D35V_CPU_VDDQ_S3

CPU DC/DC PMIC

RT9610BZQW

INPUTS

5V_S5

SYSTEM LDO

APL3523AQBI

INPUTS OUTPUTS

5V_S5 5V_S0

3D3V_S5

SYSTEM LDO

TPS22965DSGR

INPUTS OUTPUTS

3D3V_AUX_S5

3D3V_S5

5V_S5

0D675V_CPU_VDDQ_S3

1D35V_CPU_VDDQ_S3

PCB LAYER

L1:Top

L2:VCC

L3:Signal

L4:Signal

L5:GND

L6:Bottom

OUTPUTS

BT+

OUTPUTS

OUTPUTS

1D05V_S0

1D8V_S5

1D24V_S5

OUTPUTS

1V_CPU_VNN

1V_CPU_VCGI

3D3V_S0

1D8V_S01D8V_S5

44

45

50

51

40

40

USB3.0

Non Share Rom

16MB

PS2

PrecisionTouch pad

65

2CH SPEAKER

(2CH 2W/4ohm)

Audio Codec

ALC3246

SPI

I2C

HDA

MIC_IN/GND

Universal Jack

USB3(USB2.0)

A A

SD Card Slot

IO Board

5

HP_R/L

Realtek RTS5170

CardReader

USB2.0

USB2.0

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O.C.

Block Diagram

Block Diagram

Block Diagram

Turis APL UMA

Turis APL UMA

Turis APL UMA

1

X02

X02

2 106Monday, Septemb er 05, 2016

2 106Monday, Septemb er 05, 2016

2 106Monday, Septemb er 05, 2016

X02

Vinafix.com

5

4

3

2

1

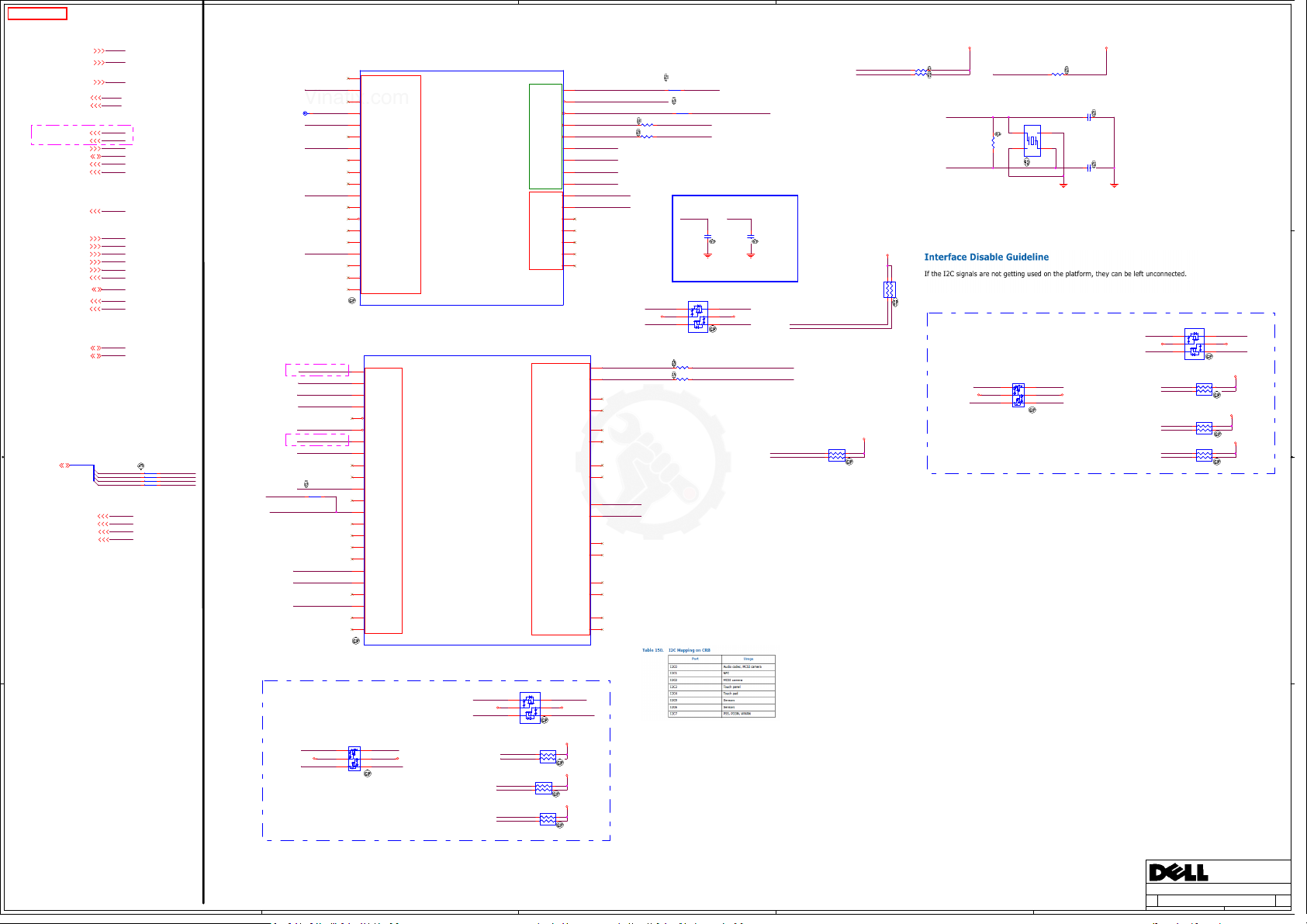

SSID = CPU

D D

C C

Blanking

B B

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

(Reserved)

(Reserved)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

(Reserved)

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Turis APL UMA

Turis APL UMA

Turis APL UMA

3 106Wednesday, July 27, 2016

3 106Wednesday, July 27, 2016

3 106Wednesday, July 27, 2016

1

X02

X02

X02

Vinafix.com

5

4

3

2

1

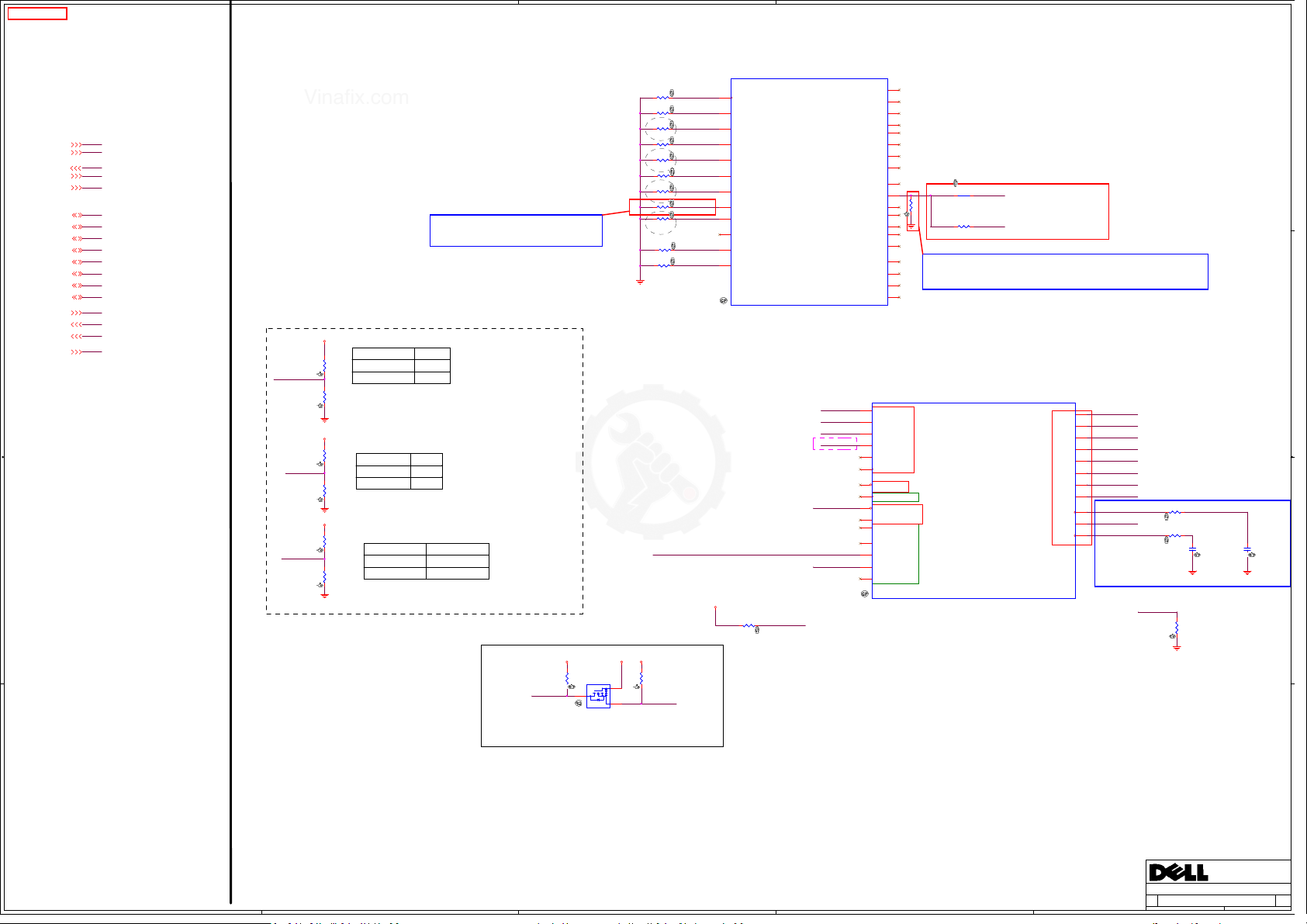

SSID = CPU

D D

C C

Blanking

B B

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

(Reserved)

(Reserved)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

(Reserved)

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Turis APL UMA

Turis APL UMA

Turis APL UMA

4 106Wednesday, July 27, 2016

4 106Wednesday, July 27, 2016

4 106Wednesday, July 27, 2016

1

X02

X02

X02

Vinafix.com

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

5

CPU1A

CPU1A

M_A_DQ0

AY62

MEM_CH0_DQ 0/MEM_CH0 _DQA0

M_A_DQ1

AY61

MEM_CH0_DQ 1/MEM_CH0 _DQA1

M_A_DQ2

BE62

MEM_CH0_DQ 2/MEM_CH0 _DQA2

M_A_DQ3

BG62

MEM_CH0_DQ 3/MEM_CH0 _DQA3

M_A_DQ4

BD63

MEM_CH0_DQ 4/MEM_CH0 _DQA4

M_A_DQ5

AW62

MEM_CH0_DQ 5/MEM_CH0 _DQA5

M_A_DQ6

AW63

MEM_CH0_DQ 6/MEM_CH0 _DQA6

M_A_DQ7

BD62

MEM_CH0_DQ 7/MEM_CH0 _DQA7

M_A_DQ8

AV59

MEM_CH0_DQ 8/MEM_CH0 _DQA8

M_A_DQ9

AU63

MEM_CH0_DQ 9/MEM_CH0 _DQA9

M_A_DQ10

AU62

MEM_CH0_DQ 10/MEM_C H0_DQA1 0

M_A_DQ11

AV58

MEM_CH0_DQ 11/MEM_C H0_DQA1 1

M_A_DQ12

AV57

MEM_CH0_DQ 12/MEM_C H0_DQA1 2

M_A_DQ13

AT55

MEM_CH0_DQ 13/MEM_C H0_DQA1 3

M_A_DQ14

AT54

MEM_CH0_DQ 14/MEM_C H0_DQA1 4

M_A_DQ15

AY59

MEM_CH0_DQ 15/MEM_C H0_DQA1 5

M_A_DQ16

AY57

MEM_CH0_DQ 16/MEM_C H0_DQA1 6

M_A_DQ17

BB57

MEM_CH0_DQ 17/MEM_C H0_DQA1 7

M_A_DQ18

BD59

MEM_CH0_DQ 18/MEM_C H0_DQA1 8

M_A_DQ19

BF59

MEM_CH0_DQ 19/MEM_C H0_DQA1 9

M_A_DQ20

AV54

MEM_CH0_DQ 20/MEM_C H0_DQA2 0

M_A_DQ21

AY55

MEM_CH0_DQ 21/MEM_C H0_DQA2 1

M_A_DQ22

AV52

MEM_CH0_DQ 22/MEM_C H0_DQA2 2

M_A_DQ23

BD58

MEM_CH0_DQ 23/MEM_C H0_DQA2 3

M_A_DQ24

BE56

MEM_CH0_DQ 24/MEM_C H0_DQA2 4

M_A_DQ25

BD54

MEM_CH0_DQ 25/MEM_C H0_DQA2 5

M_A_DQ26

BF58

MEM_CH0_DQ 26/MEM_C H0_DQA2 6

M_A_DQ27

BE50

MEM_CH0_DQ 27/MEM_C H0_DQA2 7

M_A_DQ29

BB50

MEM_CH0_DQ 29/MEM_C H0_DQA2 9

M_A_DQ28

BD50

MEM_CH0_DQ 28/MEM_C H0_DQA2 8

M_A_DQ30

BA50

MEM_CH0_DQ 30/MEM_C H0_DQA3 0

M_A_DQ31

BB54

MEM_CH0_DQ 31/MEM_C H0_DQA3 1

APOLLO-LAKE-GP-U

APOLLO-LAKE-GP-U

CPU1C

CPU1C

BJ26

MEM_CH1_DQ 0/MEM_CH1 _DQA0

BG30

MEM_CH1_DQ 1/MEM_CH1 _DQA1

BH31

MEM_CH1_DQ 2/MEM_CH1 _DQA2

BG31

MEM_CH1_DQ 3/MEM_CH1 _DQA3

BH27

MEM_CH1_DQ 4/MEM_CH1 _DQA4

BG27

MEM_CH1_DQ 5/MEM_CH1 _DQA5

BG26

MEM_CH1_DQ 6/MEM_CH1 _DQA6

BJ30

MEM_CH1_DQ 7/MEM_CH1 _DQA7

BA30

MEM_CH1_DQ 8/MEM_CH1 _DQA8

BB30

MEM_CH1_DQ 9/MEM_CH1 _DQA9

BE30

MEM_CH1_DQ 10/MEM_C H1_DQA1 0

BD30

MEM_CH1_DQ 11/MEM_C H1_DQA1 1

BE25

MEM_CH1_DQ 12/MEM_C H1_DQA1 2

BB27

MEM_CH1_DQ 13/MEM_C H1_DQA1 3

BD25

MEM_CH1_DQ 14/MEM_C H1_DQA1 4

BD27

MEM_CH1_DQ 15/MEM_C H1_DQA1 5

BG24

MEM_CH1_DQ 16/MEM_C H1_DQA1 6

BJ20

MEM_CH1_DQ 17/MEM_C H1_DQA1 7

BH23

MEM_CH1_DQ 18/MEM_C H1_DQA1 8

BJ24

MEM_CH1_DQ 19/MEM_C H1_DQA1 9

BG20

MEM_CH1_DQ 20/MEM_C H1_DQA2 0

BG21

MEM_CH1_DQ 21/MEM_C H1_DQA2 1

BH19

MEM_CH1_DQ 22/MEM_C H1_DQA2 2

BG25

MEM_CH1_DQ 23/MEM_C H1_DQA2 3

AT27

MEM_CH1_DQ 24/MEM_C H1_DQA2 4

AW29

MEM_CH1_DQ 25/MEM_C H1_DQA2 5

AR27

MEM_CH1_DQ 26/MEM_C H1_DQA2 6

AT23

MEM_CH1_DQ 27/MEM_C H1_DQA2 7

AV27

MEM_CH1_DQ 28/MEM_C H1_DQA2 8

AR25

MEM_CH1_DQ 29/MEM_C H1_DQA2 9

AR23

MEM_CH1_DQ 30/MEM_C H1_DQA3 0

AW27

MEM_CH1_DQ 31/MEM_C H1_DQA3 1

APOLLO-LAKE-GP-U

APOLLO-LAKE-GP-U

5

SSID = CPU

DDR_DATA

M_A_DQ[63:0][12]

M_A_DQS_DN[7:0][12]

D D

M_A_DQS_DP[7:0][12]

M_A_A[15:0][12]

M_A_BS0[12]

M_A_BS1[12]

M_A_BS2[12]

M_A_ODT0[12]

M_A_ODT1[12]

M_A_CAS#[12]

M_A_WE#[12]

M_A_RAS#[12]

M_A_CS#1[12]

M_A_CS#0[12]

M_A_CLK1[12]

C C

M_A_CLK#1[12]

M_A_CLK0[12]

M_A_CLK#0[12]

M_A_CKE0[12]

M_A_CKE1[12]

DDR_DRAMRST#[12]

B B

A A

4

1 OF 23

APL_SOC

APL_SOC

4

APL_SOC

APL_SOC

MEM_CH0_DQ 32/MEM_C H0_DQB0

MEM_CH0_DQ 33/MEM_C H0_DQB1

MEM_CH0_DQ 34/MEM_C H0_DQB2

MEM_CH0_DQ 35/MEM_C H0_DQB3

MEM_CH0_DQ 36/MEM_C H0_DQB4

MEM_CH0_DQ 37/MEM_C H0_DQB5

MEM_CH0_DQ 38/MEM_C H0_DQB6

MEM_CH0_DQ 39/MEM_C H0_DQB7

MEM_CH0_DQ 40/MEM_C H0_DQB8

MEM_CH0_DQ 41/MEM_C H0_DQB9

MEM_CH0_DQ 42/MEM_C H0_DQB1 0

MEM_CH0_DQ 43/MEM_C H0_DQB1 1

MEM_CH0_DQ 44/MEM_C H0_DQB1 2

MEM_CH0_DQ 45/MEM_C H0_DQB1 3

MEM_CH0_DQ 46/MEM_C H0_DQB1 4

MEM_CH0_DQ 47/MEM_C H0_DQB1 5

MEM_CH0_DQ 48/MEM_C H0_DQB1 6

MEM_CH0_DQ 49/MEM_C H0_DQB1 7

MEM_CH0_DQ 50/MEM_C H0_DQB1 8

MEM_CH0_DQ 51/MEM_C H0_DQB1 9

MEM_CH0_DQ 52/MEM_C H0_DQB2 0

MEM_CH0_DQ 53/MEM_C H0_DQB2 1

MEM_CH0_DQ 54/MEM_C H0_DQB2 2

MEM_CH0_DQ 55/MEM_C H0_DQB2 3

MEM_CH0_DQ 56/MEM_C H0_DQB2 4

MEM_CH0_DQ 57/MEM_C H0_DQB2 5

MEM_CH0_DQ 58/MEM_C H0_DQB2 6

MEM_CH0_DQ 59/MEM_C H0_DQB2 7

MEM_CH0_DQ 60/MEM_C H0_DQB2 8

MEM_CH0_DQ 61/MEM_C H0_DQB2 9

MEM_CH0_DQ 62/MEM_C H0_DQB3 0

MEM_CH0_DQ 63/MEM_C H0_DQB3 1

1 OF 23

MEM_CH1_DQ 32/MEM_C H1_DQB0

MEM_CH1_DQ 33/MEM_C H1_DQB1

MEM_CH1_DQ 34/MEM_C H1_DQB2

MEM_CH1_DQ 35/MEM_C H1_DQB3

MEM_CH1_DQ 36/MEM_C H1_DQB4

MEM_CH1_DQ 37/MEM_C H1_DQB5

MEM_CH1_DQ 38/MEM_C H1_DQB6

MEM_CH1_DQ 39/MEM_C H1_DQB7

MEM_CH1_DQ 40/MEM_C H1_DQB8

MEM_CH1_DQ 41/MEM_C H1_DQB9

MEM_CH1_DQ 42/MEM_C H1_DQB1 0

MEM_CH1_DQ 43/MEM_C H1_DQB1 1

MEM_CH1_DQ 44/MEM_C H1_DQB1 2

MEM_CH1_DQ 45/MEM_C H1_DQB1 3

MEM_CH1_DQ 46/MEM_C H1_DQB1 4

MEM_CH1_DQ 47/MEM_C H1_DQB1 5

MEM_CH1_DQ 48/MEM_C H1_DQB1 6

MEM_CH1_DQ 49/MEM_C H1_DQB1 7

MEM_CH1_DQ 50/MEM_C H1_DQB1 8

MEM_CH1_DQ 51/MEM_C H1_DQB1 9

MEM_CH1_DQ 52/MEM_C H1_DQB2 0

MEM_CH1_DQ 53/MEM_C H1_DQB2 1

MEM_CH1_DQ 54/MEM_C H1_DQB2 2

MEM_CH1_DQ 55/MEM_C H1_DQB2 3

MEM_CH1_DQ 56/MEM_C H1_DQB2 4

MEM_CH1_DQ 57/MEM_C H1_DQB2 5

MEM_CH1_DQ 58/MEM_C H1_DQB2 6

MEM_CH1_DQ 59/MEM_C H1_DQB2 7

MEM_CH1_DQ 60/MEM_C H1_DQB2 8

MEM_CH1_DQ 61/MEM_C H1_DQB2 9

MEM_CH1_DQ 62/MEM_C H1_DQB3 0

MEM_CH1_DQ 63/MEM_C H1_DQB3 1

M_A_DQ32

AR39

M_A_DQ33

AV37

M_A_DQ34

AW37

M_A_DQ35

AR37

M_A_DQ36

AT37

M_A_DQ37

AT41

M_A_DQ38

AR41

M_A_DQ39

AW35

M_A_DQ40

BJ44

M_A_DQ41

BG39

M_A_DQ42

BG40

M_A_DQ43

BJ40

M_A_DQ44

BG43

M_A_DQ45

BG44

M_A_DQ46

BH45

M_A_DQ47

BH41

M_A_DQ48

BA34

M_A_DQ49

BE34

M_A_DQ50

BD34

M_A_DQ51

BD37

M_A_DQ52

BB37

M_A_DQ53

BE39

M_A_DQ54

BD39

M_A_DQ55

BB34

M_A_DQ56

BJ38

M_A_DQ57

BG34

M_A_DQ58

BG33

M_A_DQ59

BH33

M_A_DQ60

BG38

M_A_DQ61

BH37

M_A_DQ62

BG37

M_A_DQ63

BJ34

3 OF 23

3 OF 23

BF6

BD10

BE14

BB10

BA14

BB14

BD14

BE8

AV12

BD6

BD5

BB7

AV10

AY9

AY7

BF5

AU2

AT10

AT9

AU1

AY5

AV5

AV6

AV7

AY2

BD2

BD1

BE2

AW1

AW2

AY3

BG2

3

CPU1B

CPU1B

M_A_DQS_DP0

BB63

MEM_CH0_DQ SP0/MEM_ CH0_DQS PA0

M_A_DQS_DN0

BC62

MEM_CH0_DQ SN0/MEM_C H0_DQSNA 0

M_A_DQS_DP1

AT59

MEM_CH0_DQ SP1/MEM_ CH0_DQS PA1

M_A_DQS_DN1

AT58

MEM_CH0_DQ SN1/MEM_C H0_DQSNA 1

M_A_DQS_DP2

BB59

MEM_CH0_DQ SP2/MEM_ CH0_DQS PA2

M_A_DQS_DN2

BB58

MEM_CH0_DQ SN2/MEM_C H0_DQSNA 2

M_A_DQS_DP3

BD52

MEM_CH0_DQ SP3/MEM_ CH0_DQS PA3

M_A_DQS_DN3

BB52

MEM_CH0_DQ SN3/MEM_C H0_DQSNA 3

M_A_DQS_DP4

AV39

MEM_CH0_DQ SP4/MEM_ CH0_DQS PB0

M_A_DQS_DN4

AW39

MEM_CH0_DQ SN4/MEM_C H0_DQSNB 0

M_A_DQS_DP5

BJ42

MEM_CH0_DQ SP5/MEM_ CH0_DQS PB1

M_A_DQS_DN5

BG42

MEM_CH0_DQ SN5/MEM_C H0_DQSNB 1

M_A_DQS_DP6

BB35

MEM_CH0_DQ SP6/MEM_ CH0_DQS PB2

M_A_DQS_DN6

BD35

MEM_CH0_DQ SN6/MEM_C H0_DQSNB 2

M_A_DQS_DP7

BG36

MEM_CH0_DQ SP7/MEM_ CH0_DQS PB3

M_A_DQS_DN7

BH35

MEM_CH0_DQ SN7/MEM_C H0_DQSNB 3

M_A_A0

BG50

MEM_CH0_MA0 /MEM_CH0_ CAB7

M_A_A1

BG51

MEM_CH0_MA1 /MEM_CH0_ CAB9

M_A_A2

BH51

MEM_CH0_MA2 /MEM_CH0_ CAB5

M_A_A3

BD41

MEM_CH0_MA3 /NCTF_2 2

M_A_A4

BE41

MEM_CH0_MA4 /NCTF_2 3

M_A_A5

BJ52

MEM_CH0_MA5 /MEM_CH0_ CAA2

M_A_A6

BG53

MEM_CH0_MA6 /MEM_CH0_ CAA0

M_A_A7

BG55

MEM_CH0_MA7 /MEM_CH0_ CAA3

M_A_A8

BH53

MEM_CH0_MA8 /MEM_CH0_ CAA1

M_A_A9

BG52

MEM_CH0_MA9 /MEM_CH0_ CAA4

M_A_A10

BH49

MEM_CH0_MA1 0/MEM_CH0 _CAB6

M_A_A11

BH55

MEM_CH0_MA1 1/MEM_CH0 _CAA6

M_A_A12

BG54

MEM_CH0_MA1 2/MEM_CH0 _CAA5

M_A_A13

BG46

MEM_CH0_MA1 3/MEM_CH0 _CAB0

M_A_A14

BG56

MEM_CH0_MA1 4/MEM_CH0 _CAA8

M_A_A15

BG57

MEM_CH0_MA1 5/MEM_CH0 _CAA9

APOLLO-LAKE-GP-U

APOLLO-LAKE-GP-U

CPU1D

CPU1D

BG28

MEM_CH1_DQ SP0/MEM_ CH1_DQS PA0

BH29

MEM_CH1_DQ SN0/MEM_C H1_DQSNA 0

BD29

MEM_CH1_DQ SP1/MEM_ CH1_DQS PA1

BB29

MEM_CH1_DQ SN1/MEM_C H1_DQSNA 1

BJ22

MEM_CH1_DQ SP2/MEM_ CH1_DQS PA2

BG22

MEM_CH1_DQ SN2/MEM_C H1_DQSNA 2

AV25

MEM_CH1_DQ SP3/MEM_ CH1_DQS PA3

AW25

MEM_CH1_DQ SN3/MEM_C H1_DQSNA 3

BB12

MEM_CH1_DQ SP4/MEM_ CH1_DQS PB0

BD12

MEM_CH1_DQ SN4/MEM_C H1_DQSNB 0

BB5

MEM_CH1_DQ SP5/MEM_ CH1_DQS PB1

BB6

MEM_CH1_DQ SN5/MEM_C H1_DQSNB 1

AT5

MEM_CH1_DQ SP6/MEM_ CH1_DQS PB2

AT6

MEM_CH1_DQ SN6/MEM_C H1_DQSNB 2

BC2

MEM_CH1_DQ SP7/MEM_ CH1_DQS PB3

BB1

MEM_CH1_DQ SN7/MEM_C H1_DQSNB 3

BG9

MEM_CH1_MA0 /MEM_CH1_ CAB7

BG10

MEM_CH1_MA1 /MEM_CH1_ CAB9

BH9

MEM_CH1_MA2 /MEM_CH1_ CAB5

BD16

MEM_CH1_MA3 /NCTF_1

BB16

MEM_CH1_MA4 /NCTF_2

BG11

MEM_CH1_MA5 /MEM_CH1_ CAA2

BJ12

MEM_CH1_MA6 /MEM_CH1_ CAA0

BG14

MEM_CH1_MA7 /MEM_CH1_ CAA3

BG12

MEM_CH1_MA8 /MEM_CH1_ CAA1

BH11

MEM_CH1_MA9 /MEM_CH1_ CAA4

BG7

MEM_CH1_MA1 0/MEM_CH1 _CAB6

BH13

MEM_CH1_MA1 1/MEM_CH1 _CAA6

BG13

MEM_CH1_MA1 2/MEM_CH1 _CAA5

BH3

MEM_CH1_MA1 3/MEM_CH1 _CAB0

BG15

MEM_CH1_MA1 4/MEM_CH1 _CAA8

BG16

MEM_CH1_MA1 5/MEM_CH1 _CAA9

APOLLO-LAKE-GP-U

APOLLO-LAKE-GP-U

3

2

2 OF 23

2 OF 23

APL_SOC

APL_SOC

APL_SOC

APL_SOC

2

MEM_CH0_VR EFCA

MEM_CH0_VR EFDQ

MEM_CH0_BA 0/MEM_CH0 _CAB2

MEM_CH0_BA 1/MEM_CH0 _CAB8

MEM_CH0_BA 2/MEM_CH0 _CAA7

MEM_CH0_OD T0/MEM_C H0_ODTA

MEM_CH0_OD T1/MEM_C H0_ODTB

MEM_CH0_CA S#/MEM_C H0_CAB1

MEM_CH0_W E#/MEM_C H0_CAB4

MEM_CH0_RA S#/MEM_C H0_CAB3

NCTF/MEM_CH0 _CS1A #

NCTF/MEM_CH0 _CS0B #

MEM_CH0_CS 1#/MEM_C H0_CS1B #

MEM_CH0_CS 0#/MEM_C H0_CS0A #

MEM_CH0_CL KP1/MEM_ CH0_CLK P_A

MEM_CH0_CL KN1/MEM_C H0_CLKN_ A

MEM_CH0_CL KP0/MEM_ CH0_CLK P_B

MEM_CH0_CL KN0/MEM_C H0_CLKN_ B

MEM_CH0_CK E0/MEM_C H0_CKE0 A

MEM_CH0_CK E1/MEM_C H0_CKE1 A

NCTF/MEM_CH0 _CKE0 B

NCTF/MEM_CH0 _CKE1 B

MEM_CH1_RE SET#/NC TF_31

MEM_CH0_RE SET#/NC TF_33

MEM_CH0_DQ SP8/NCT F_28

MEM_CH0_DQ SN8/NCTF _30

MEM_CH0_CB 7/NCTF_ 35

MEM_CH0_CB 6/NCTF_ 34

MEM_CH0_CB 5/NCTF_ 32

MEM_CH0_CB 4/NCTF_ 29

MEM_CH0_CB 3/NCTF_ 27

MEM_CH0_CB 2/NCTF_ 26

MEM_CH0_CB 1/NCTF_ 25

MEM_CH0_CB 0/NCTF_ 24

MEM_CH1_VR EFDQ

MEM_CH1_VR EFCA

MEM_CH1_BA 0/MEM_CH1 _CAB2

MEM_CH1_BA 1/MEM_CH1 _CAB8

MEM_CH1_BA 2/MEM_CH1 _CAA7

MEM_CH1_RA S#/MEM_C H1_CAB3

MEM_CH1_CA S#/MEM_C H1_CAB1

MEM_CH1_W E#/MEM_C H1_CAB4

MEM_CH1_OD T0/MEM_C H1_ODTA

MEM_CH1_OD T1/MEM_C H1_ODTB

MEM_CH1_CL KP1/MEM_ CH1_CLK P_A

MEM_CH1_CL KN1/MEM_C H1_CLKN_ A

MEM_CH1_CL KP0/MEM_ CH1_CLK P_B

MEM_CH1_CL KN0/MEM_C H1_CLKN_ B

MEM_CH1_CK E0/MEM_C H1_CKE0 A

MEM_CH1_CK E1/MEM_C H1_CKE1 A

NCTF/MEM_CH1 _CKE0 B

NCTF/MEM_CH1 _CKE1 B

MEM_CH1_CS 0#/MEM_C H1_CS0A #

MEM_CH1_CS 1#/MEM_C H1_CS1B #

NCTF/MEM_CH1 _CS0B #

NCTF/MEM_CH1 _CS1A #

MEM_CH1_DQ SN8/NCTF _9

MEM_CH1_DQ SP8/NCT F_5

MEM_CH1_CB 0/NCTF_ 3

MEM_CH1_CB 1/NCTF_ 4

MEM_CH1_CB 6/NCTF_ 11

MEM_CH1_CB 3/NCTF_ 7

MEM_CH1_CB 4/NCTF_ 8

MEM_CH1_CB 5/NCTF_ 10

MEM_CH1_CB 7/NCTF_ 12

MEM_CH1_CB 2/NCTF_ 6

M_A_VREFDQ_CPU

AT34

M_A_BS0

BJ48

M_A_BS1

BG49

M_A_BS2

BH57

M_A_ODT0

AW43

M_A_ODT1

AW41

M_A_CAS#

BH47

M_A_WE#

BG48

M_A_RAS#

BG47

AT43

BB41

M_A_CS#1

BA41

M_A_CS#0

AR43

M_A_CLK1

BB48

M_A_CLK#1

BD48

M_A_CLK0

BD45

M_A_CLK#0

BE45

M_A_CKE0

BH61

M_A_CKE1

BH60

BH58

BJ58

AR30

DDR_DRAMRST#

AR34

BD47

BB47

BA45

BD43

AV47

AV48

AW45

BB43

AW47

AW48

4 OF 23

4 OF 23

AT30

AR29

BH6

BG8

BH15

BJ6

BH4

BH7

AW16

AV16

BB21

BD21

BD19

BE19

BG18

BG17

BH17

BJ16

BD17

AW17

AV17

BB17

BE23

BD23

AR21

AT21

BA23

AW21

BA19

AW19

BB23

AW23

M_A_VREFCA_CPU

AR35

TP509TP509

1

TP510TP510

1

1

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A1

A1

A1

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU(DDR)

CPU(DDR)

CPU(DDR)

Turis APL UMA

Turis APL UMA

Turis APL UMA

5 106Wednesday, July 27, 2016

5 106Wednesday, July 27, 2016

5 106Wednesday, July 27, 2016

X02

X02

X02

Vinafix.com

5

4

3

2

1

SSID = CPU

22 OF 23

CPU1V

CPU1V

3D3V_USB

D D

R602

R602

R603

R603

1 2

R604

R604

R605

R605

R606

R606

C C

1D05V_S0

R607

R607

R608

R608

R609

R609

R610

R610

B B

3D3V_USB3D3V_S5

R601 0R0402-PAD-2- GPR601 0R0402-PAD-2- GP

12

1D24V_USB21D24V_S5

0R0603-PAD-2- GP-U

0R0603-PAD-2- GP-U

12

1D24V_AUD_ISH_P LL

0R0805-PAD-2- GP-U

0R0805-PAD-2- GP-U

1D24V_MPHY

0R0603-PAD-2- GP-U

0R0603-PAD-2- GP-U

12

1D24V_GLML

0R0603-PAD-2- GP-U

0R0603-PAD-2- GP-U

12

1D24V_DSI_CSI

0R0603-PAD-2- GP-U

0R0603-PAD-2- GP-U

12

1D05V_IO_3PHASEIO

0R0603-PAD-2- GP-U

0R0603-PAD-2- GP-U

12

1D05V_FHV1

0R0603-PAD-2- GP-U

0R0603-PAD-2- GP-U

12

1D05V_FHV0

0R0603-PAD-2- GP-U

0R0603-PAD-2- GP-U

12

1D05V_FUSE

0R0603-PAD-2- GP-U

0R0603-PAD-2- GP-U

12

1D24V_USB2

1V_CPU_VNN

3D3V_USB

1D24V_AUD_ISH_P LL

1D24V_MPHY

1D24V_GLML

1D24V_DSI_CSI

1D24V_AUD_ISH_P LL

1D05V_IO_3PHASEIO

1D05V_FUSE

1D05V_FHV1

1D05V_FHV0

1D05V_IO_3PHASEIO

AJ25

VCC_3P3V_A_6

AK25

VCC_3P3V_A_5

AG20

VDD2_1P24_USB2

AJ37

VNN_SVID

AJ39

VNN_SVID

AJ41

VNN_SVID

AJ42

VNN_SVID

AJ46

VNN_SVID

AK37

VNN_SVID

AK39

VNN_SVID

AK41

VNN_SVID

AK42

VNN_SVID

AK44

VNN_SVID

AK46

VNN_SVID

AM44

VNN_SVID

AJ44

RSVD_11

AA42

VCC_3P3V_A_4

Y44

VCC_3P3V_A_1

V46

VCC_3P3V_A_2

V44

VCC_3P3V_A_3

AC41

VCC_3P3V_A_7

AJ20

VDD2_1P24_AUD_ISH_PLL

AJ22

VDD2_1P24_AUD_ISH_PLL

AE18

VDD2_1P24_MPHY

AE20

VDD2_1P24_MPHY

AE22

VDD2_1P24_MPHY

AG22

VDD2_1P24_MPHY

BJ61

RSVD_7

AK20

VDD2_1P24_GLM

AC20

RSVD_10

AC22

RSVD_9

AA18

VDD2_1P24_DSI_CSI

AA20

VDD2_1P24_DSI_CSI

AK22

VDD2_1P24_AUD_ISH_PLL

AA22

VCCRAM_1P05_IO

AC23

VCCRAM_1P05_IO

V18

VCCRAM_1P05_IO

Y18

VCCRAM_1P05_IO

Y20

VCCRAM_1P05_IO

P16

VCC_1P05V

T15

VCC_1P05V

T13

VCC_1P05V

AA23

VCCRAM_1P05_IO

APOLLO-LAKE-G P-U

APOLLO-LAKE-G P-U

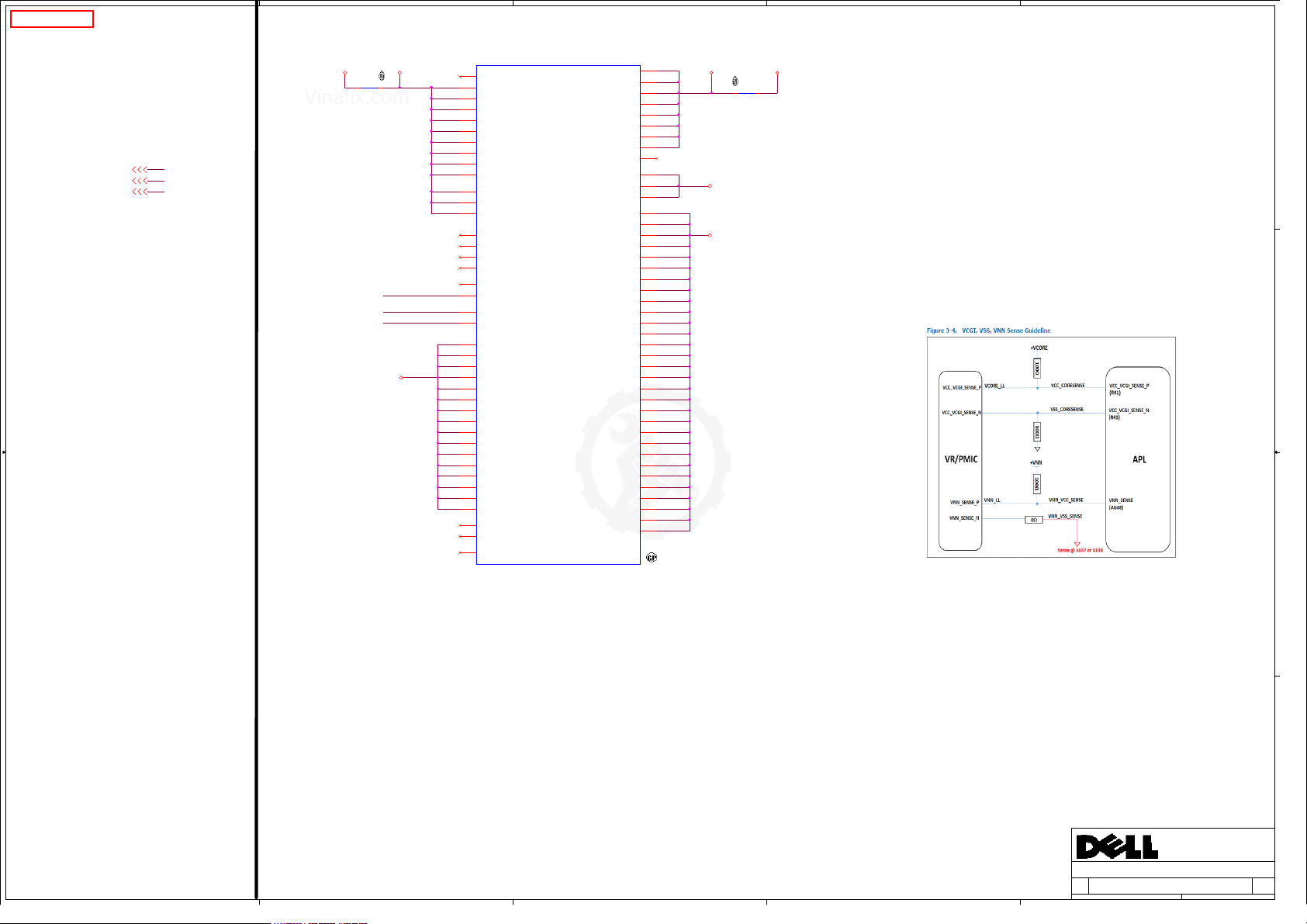

VNN

Max 4.4A

3D3V_S5

Max 0.15A

APL_SOC

APL_SOC

22 OF 23

NCTF_18

NCTF_19

NCTF_17

NCTF_21

VDD2_1P24_GLM

VDD2_1P24_GLM

VDD2_1P24_GLM

VCC_VCGI_43

VCC_VCGI_41

VCC_VCGI_40

VCC_VCGI_39

VCC_VCGI_38

VCC_VCGI_37

VCC_VCGI_36

VCC_VCGI_34

VCC_VCGI_62

VCC_VCGI_60

VCC_VCGI_58

VCC_VCGI_56

VCC_VCGI_54

VCC_VCGI_52

VCC_VCGI_50

VCC_VCGI_48

VCC_VCGI_46

VCC_VCGI_44

VCC_VCGI_42

VCC_VCGI_63

VCC_VCGI_61

VCC_VCGI_59

VCC_VCGI_57

VCC_VCGI_55

VCC_VCGI_53

VCC_VCGI_51

VCC_VCGI_49

VCC_VCGI_47

VCC_VCGI_45

VCC_VCGI_35

VCC_VCGI_64

NCTF_20

VCCRTC_3P3V

VCCIOA

VCCIOA

VCCIOA

VCCIOA

RSVD_8

RSVD_12

D4

T51

L14

E3

AM37

AM20

AM28

AA28

AA30

AA32

AC28

AC30

AC32

AE28

AE30

AE32

AG28

AG30

AG32

AJ28

AJ30

AJ32

AK28

AK30

AK32

AM30

E29

E37

U28

U30

U32

V28

V30

V32

Y28

Y30

Y32

E50

R19

AA44

AM23

AM25

AM41

AM42

BJ62

V49

1D24V_GLML

C601

C601

1 2

SC1U10V2KX-1G P

SC1U10V2KX-1G P

1V_CPU_VCGI

3D3V_VCCRT C

1V_CPU_VNN

VCCIOA Max 1.5A

Tie to VNN for LPDDR3/DDR3L

Tie to VDDQ for for LPDDR4.

Note: AM28 IS INTERNAL SHORTED ON BXT-P PACKAGE TO VDD2

1V_CPU_VCGI

RTC_AUX_S5

R611 0R0402-PAD-2- GPR611 0R0402-PAD-2- GP

12

A A

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Thursday, Augus t 25, 2016

Thursday, Augus t 25, 2016

Thursday, Augus t 25, 2016

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O.C.

CPU (CFG)

CPU (CFG)

CPU (CFG)

Turis APL UMA

Turis APL UMA

Turis APL UMA

1

6 106

6 106

6 106

X02

X02

X02

Vinafix.com

5

4

3

2

1

SSID = CPU

23 OF 23

CPU1W

CPU1W

AM32

AA25

AC25

AE25

AN32

BG63

AG48

AN18

AN20

AN22

AN23

AN41

AN42

AN44

AN46

AR17

AR47

AT13

AT17

AT47

AT51

AV14

AV50

E6

U22

U23

V22

V23

V25

Y23

U20

U25

Y25

D1

V48

R43

R41

F23

E23

BJ3

APOLLO-LAKE-G P-U

APOLLO-LAKE-G P-U

NCTF_16

VCCRAM_1P05

VCCRAM_1P05

VCCRAM_1P05

VCCRAM_1P05

VCCRAM_1P05

VCCRAM_1P05

VCCRAM_1P05

VCCRAM_1P05

VCCRAM_1P05

VCCRAM_1P05

VCCRAM_1P05

VCCRAM_1P05

RSVD_4

RSVD_6

RSVD_2

RSVD_1

RSVD_3

VCC_VCGI_SENSE_N

VCC_VCGI_SENSE_P

VNN_SENSE

VDDQ_15

VDDQ_14

VDDQ_13

VDDQ_12

VDDQ_11

VDDQ_10

VDDQ_9

VDDQ

VDDQ_8

Max 2.8A

VDDQ_6

VDDQ_7

VDDQ_5

VDDQ_4

VDDQ_3

VDDQ_2

VDDQ_1

VDDQ_16

NCTF_14

NCTF_15

RSVD_5

R701

R701

1 2

0R0805-PAD-2- GP-U

0R0805-PAD-2- GP-U

D D

VSS_VCCGI[50]

FB_VCCGI[50]

FB_VNN[50]

VSS_VCCGI

FB_VCCGI

FB_VNN

C C

1D35V_CPU_VD DQ_S3

B B

1D05V_S0

Max 2.7A

APL_SOC

APL_SOC

1D8V_S5

Max 0.4A

23 OF 23

VCC_1P8V_A_1

VCC_1P8V_A_2

VCC_1P8V_A_3

VCC_1P8V_A_4

VCC_1P8V_A_5

VCC_1P8V_A_6

VCC_1P8V_A_7

VCC_1P8V_A_8

NCTF_13

VCC_VCGI_32

VCC_VCGI_31

VCC_VCGI_33

VCC_VCGI_30

VCC_VCGI_27

VCC_VCGI_24

VCC_VCGI_21

VCC_VCGI_18

VCC_VCGI_15

VCC_VCGI_12

VCC_VCGI_9

VCC_VCGI_7

VCC_VCGI_6

VCC_VCGI_3

VCC_VCGI_1

VCC_VCGI_28

VCC_VCGI_25

VCC_VCGI_22

VCC_VCGI_19

VCC_VCGI_16

VCC_VCGI_13

VCC_VCGI_10

VCC_VCGI_8

VCC_VCGI_5

VCC_VCGI_4

VCC_VCGI_2

VCC_VCGI_29

VCC_VCGI_26

VCC_VCGI_23

VCC_VCGI_20

VCC_VCGI_17

VCC_VCGI_14

VCC_VCGI_11

AE42

AE44

AA46

AC42

AC44

AC46

AE46

AG25

R17

F29

E35

AK34

E45

AC37

AE36

AE37

AG36

E43

E48

R45

R47

U36

U37

U39

U41

U42

U44

U46

U47

U48

V36

V37

V39

V41

Y36

Y37

Y39

Y41

AC36

AA36

AA37

AA39

1D8V_PCH1D05V_PCH

0R0603-PAD-2- GP-U

0R0603-PAD-2- GP-U

1V_CPU_VCGI

1V_CPU_VCGI

1D8V_S51D05V_S0

R702

R702

12

A A

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Title

Title

Title

CPU (VCC_CORE)

CPU (VCC_CORE)

CPU (VCC_CORE)

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Thursday, Augus t 25, 2016

Thursday, Augus t 25, 2016

Thursday, Augus t 25, 2016

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O.C.

Turis APL UMA

Turis APL UMA

Turis APL UMA

1

7 106

7 106

7 106

X02

X02

X02

Vinafix.com

5

4

3

2

1

SSID = CPU

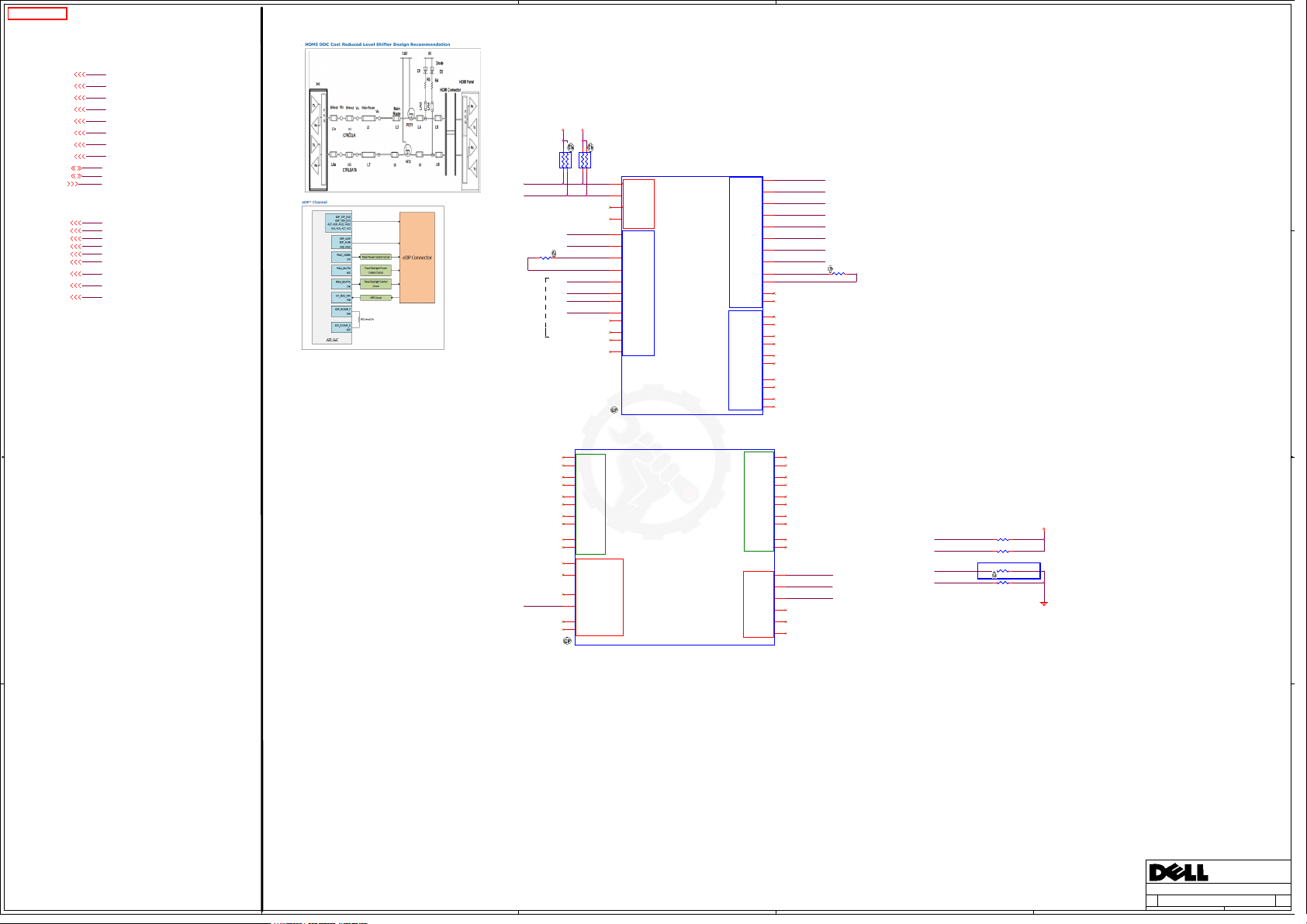

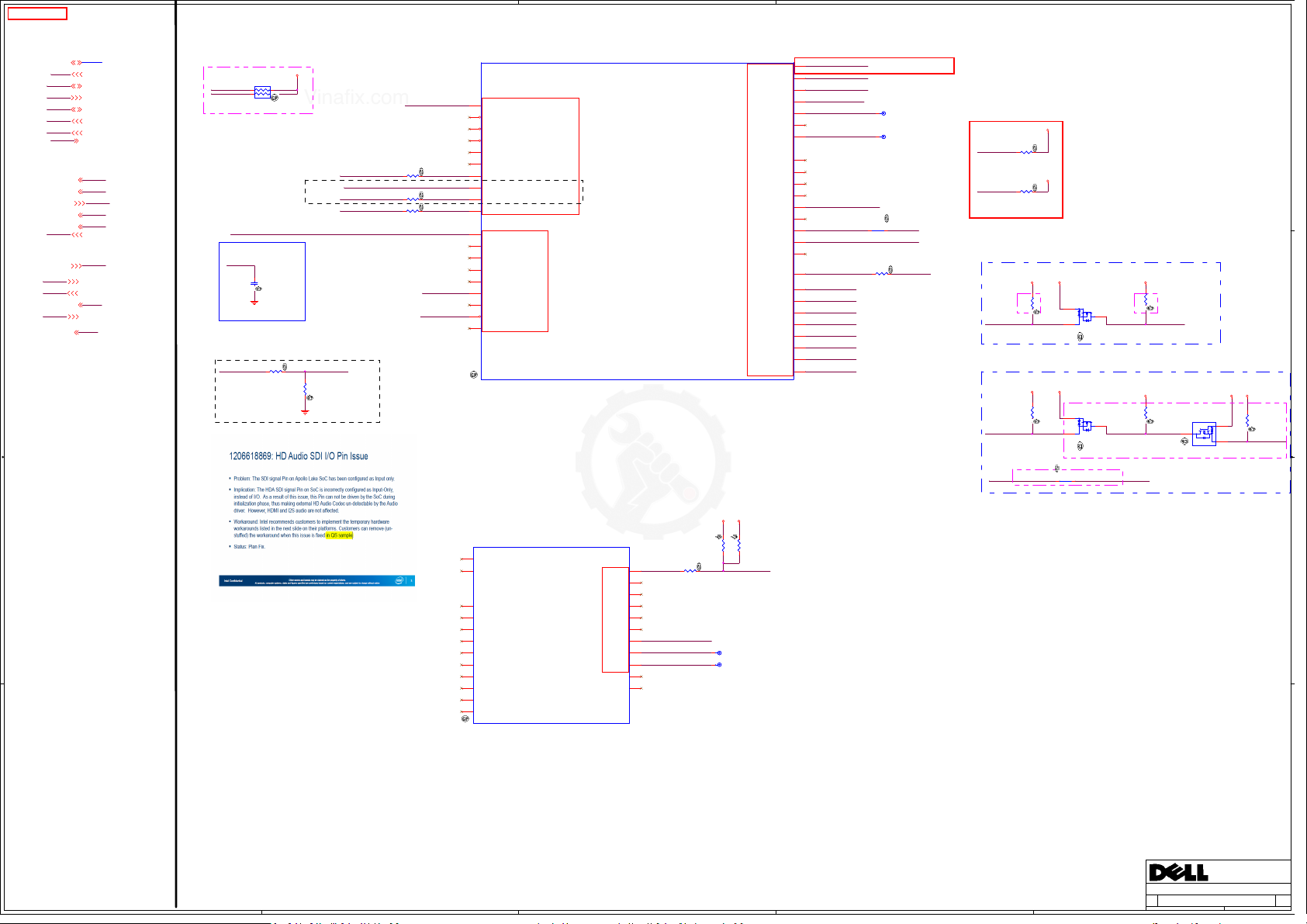

HDMI

HDMI_DATA_CPU_P2[57]

HDMI_DATA_CPU_N2[57]

HDMI_DATA_CPU_P1[57]

HDMI_DATA_CPU_N1[57]

D D

HDMI_DATA_CPU_P0[57]

HDMI_DATA_CPU_N0[57]

HDMI_DATA_CPU_P3[57]

HDMI_DATA_CPU_N3[57]

HDMI_CLK_CPU[57]

HDMI_DATA_CPU[57]

HDMI_DET_CPU#[57]

EDP

eDP_AUX_CPU_P[55]

eDP_AUX_CPU_N[55]

eDP_TX_CPU_P0[55]

eDP_TX_CPU_N0[55]

eDP_TX_CPU_P1[55]

eDP_TX_CPU_N1[55]

eDP_VDDEN_CPU[24,55]

eDP_BLCTRL_CPU[55]

eDP_BLEN_CPU[24]

C C

B B

Space/Width = 20/25 mils

EDP

CRB p39

HDMI_DET_CPU#

HDMI_CLK_CPU

HDMI_DATA_CPU

SRN2K2J-1-GP

SRN2K2J-1-GP

R802

R802

1 2

402R2F-GP

402R2F-GP

RN802

RN802

1D8V_S01D8V_S5

4

DY

DY

1

2 3

eDP_AUX_CPU_P

eDP_AUX_CPU_N

EDP_RCOMP_N

EDP_RCOMP_P

eDP_TX_CPU_N0

eDP_TX_CPU_P1

eDP_TX_CPU_N1

CPU1F

CPU1F

AP12

MDSI_A_ DP_0

AP10

MDSI_A_ DN_0

AR2

MDSI_A_ DP_1

AR1

MDSI_A_ DN_1

AP15

MDSI_A_ DP_2

AP13

MDSI_A_ DN_2

AP6

MDSI_A_ DP_3

AP5

MDSI_A_ DN_3

AP2

MDSI_A_ CLKP

AP3

MDSI_A_ CLKN

B51

MIPI_I2 C_SDA

C51

MIPI_I2 C_SCL

A50

GPIO_1 99/HV_DD I1_HPD

C50

GPIO_2 00/HV_DD I0_HPD

M45

MDSI_A_ TE

M43

MDSI_C_ TE

APOLLO-LAKE-GP-U

APOLLO-LAKE-GP-U

4

RN801

RN801

SRN2K2J-1-GP

SRN2K2J-1-GP

DY

DY

1

2 3

CPU1E

B49

C49

A54

C54

AH10

AH9

AG5

AG6

AG7

AG9

AG12

AG10

AC6

AC5

AC7

AC9

CPU1E

DDI0_D DC_SCL

DDI0_D DC_SDA

DDI1_D DC_SCL

DDI1_D DC_SDA

EDP_AUX P

EDP_AUX N

EDP_RC OMP_N

EDP_RC OMP_P

EDP_TX P_0

EDP_TX N_0

EDP_TX P_1

EDP_TX N_1

EDP_TX P_2

EDP_TX N_2

EDP_TX P_3

EDP_TX N_3

APOLLO-LAKE-GP-U

APOLLO-LAKE-GP-U

1.8V

1.05V

APL_SOC

APL_SOC

APL_SOC

APL_SOC

1.24V

1.8V

1.05V

1.05V

DDI0_R COMP_P

DDI0_R COMP_N

!!Notice:

!!Notice:

AB2/AB3

AB2/AB3

1.24V

1.8V

DDI0_T XP_0

DDI0_T XN_0

DDI0_T XP_1

DDI0_T XN_1

DDI0_T XP_2

DDI0_T XN_2

DDI0_T XP_3

DDI0_T XN_3

DDI0_A UXP

DDI0_A UXN

DDI1_A UXP

DDI1_A UXN

DDI1_T XP_0

DDI1_T XN_0

DDI1_T XP_1

DDI1_T XN_1

DDI1_T XP_2

DDI1_T XN_2

DDI1_T XP_3

DDI1_T XN_3

MDSI_C_ DP_0

MDSI_C_ DN_0

MDSI_C_ DP_1

MDSI_C_ DN_1

MDSI_C_ DP_2

MDSI_C_ DN_2

MDSI_C_ DP_3

MDSI_C_ DN_3

MDSI_C_ CLKP

MDSI_C_ CLKN

PNL0_BK LTEN

PNL0_BK LTCTL

PNL1_BK LTEN

PNL1_BK LTCTL

5 OF 23

5 OF 23

PNL0_VD DEN

PNL1_VD DEN

AK3

AK2

AM3

AM2

AH3

AH2

AL2

AL1

AG1

AG2

AM16

AM15

AK16

AK15

AF2

AF3

AD3

AD2

AC1

AC2

AB3

AB2

6 OF 23

6 OF 23

HDMI_DATA_CPU_P2

HDMI_DATA_CPU_N2

HDMI_DATA_CPU_P1

HDMI_DATA_CPU_N1

HDMI_DATA_CPU_P0

HDMI_DATA_CPU_N0

HDMI_DATA_CPU_P3

HDMI_DATA_CPU_N3

DDI0_RCOMP_P

DDI0_RCOMP_NeDP_TX_CPU_P0

AK7

AK6

AM5

AM6

AM12

AM10

AK13

AM13

AM9

AM7

eDP_VDDEN_CPU

C47

eDP_BLEN_CPU

B47

eDP_BLCTRL_CPU

C46

C52

B53

C53

R801

R801

12

402R2F-GP

402R2F-GP

CRB p132, P190

EDS p43

CRB p39

HDMI

DP to VGA

eDP_BLEN_CPU

eDP_BLCTRL_CPU

eDP_BLEN_CPU

eDP_VDDEN_CPU

R804 100KR2J-1-GP

R804 100KR2J-1-GP

12

DY

DY

R805 100KR2J-1-GP

R805 100KR2J-1-GP

12

DY

DY

R803 1MR2J-1-GP

R803 1MR2J-1-GP

12

DY

DY

R808 100KR2J-1-GP

R808 100KR2J-1-GP

12

DY

DY

1D8V_S0

Intel suggest DY and follow Intel CRB

A A

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A1

A1

A1

Wednesday, July 27, 2016

Wednesday, July 27, 2016

Wednesday, July 27, 2016

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (DDI/EDP/GPIO)

CPU (DDI/EDP/GPIO)

CPU (DDI/EDP/GPIO)

Turis APL UMA

Turis APL UMA

Turis APL UMA

8 106

8 106

8 106

X02

X02

X02

Vinafix.com

5

4

3

2

1

SSID = CPU

7 OF 23

CPU1G

D D

C C

P17

M17

P21

R21

L17

J17

F17

E17

M19

L19

H19

F19

CPU1G

MCSI_DP_0

MCSI_DN_0

MCSI_DP_1

MCSI_DN_1

MCSI_DP_2

MCSI_DN_2

MCSI_DP_3

MCSI_DN_3

MCSI_CLKP_0

MCSI_CLKN_0

MCSI_CLKP_2

MCSI_CLKN_2

APL_SOC

APL_SOC

7 OF 23

MCSI_RX_DATA0_P

MCSI_RX_DATA0_N

MCSI_RX_CLK0_P

MCSI_RX_CLK0_N

MCSI_RX_DATA1_P

MCSI_RX_DATA1_N

MCSI_RX_DATA2_P

MCSI_RX_DATA2_N

MCSI_RX_CLK1_P

MCSI_RX_CLK1_N

MCSI_RX_DATA3_P

MCSI_RX_DATA3_N

M23

P23

L23

J23

J21

H21

M25

L25

F25

E25

H25

J25

L37

GP_CAMERASB0

P34

GP_CAMERASB1

J34

GP_CAMERASB2

H30

GP_CAMERASB3

M37

GP_CAMERASB4

F30

B B

A A

5

GP_CAMERASB5

APOLLO-L AKE-GP-U

APOLLO-L AKE-GP-U

4

3

GP_CAMERASB6

GP_CAMERASB7

GP_CAMERASB8

GP_CAMERASB9

GP_CAMERASB10

GP_CAMERASB11

R35

L34

M34

M35

R34

E30

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

CPU (VSS)

CPU (VSS)

CPU (VSS)

Turis APL UMA

Turis APL UMA

Wednesd ay, July 27, 2016

Wednesd ay, July 27, 2016

Wednesd ay, July 27, 2016

Turis APL UMA

Taipei Hsien 221, Taiwan, R.O.C.

9 106

9 106

9 106

1

X02

X02

X02

Vinafix.com

SSID = CPU

5

4

3

2

1

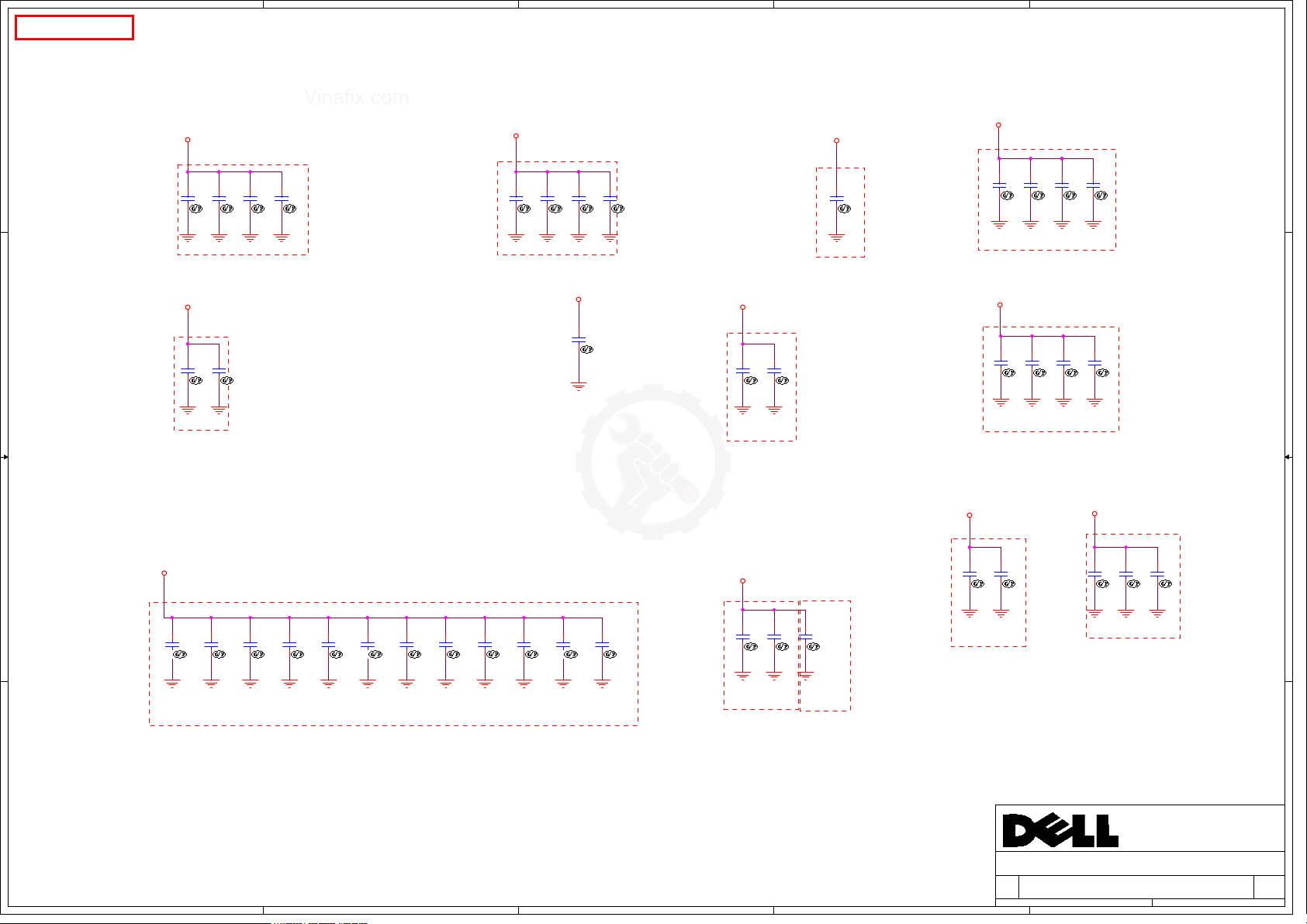

1V_CPU_ VCGI

D D

C C

VNN

1V_CPU_ VNN

B B

IccMax = 21 A

PC1010

PC1010

PC1012

PC1012

PC1013

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1025

PC1025

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1049

PC1049

12

PC1013

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1026

PC1026

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1051

PC1051

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1024

PC1024

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

CRB: 1U 0402 x 3, 22U 0603 x 4

22U 0603 x 4 , DY x2

0.1U 0402 x 1

+VCCSA(ICCMAX.= 6A)

PC1048

PC1048

PC1050

12

PC1050

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

VCCGI

CRB: 1U 0402 x 12, 22U 0603 x 8, 47U 0805 x 10

0.1U 0402 x 1

22U 0603 x 24 , DY x 4

PC1014

PC1014

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1028

PC1028

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

12

PC1015

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1030

PC1030

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1031

PC1031

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

12

PC1017

PC1017

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1032

PC1032

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1016

PC1016

PC1015

follow power team

PC1023

12

PC1009

PC1009

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1011

PC1011

12

DY

DY

PC1023

12

SCD1U25V2KX-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SCD1U25V2KX-GP

12

12

PC1018

PC1018

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1033

PC1033

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

12

PC1019

PC1019

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1034

PC1034

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

follow power team

PC1021

PC1021

PC1020

PC1020

12

12

12

PC1035

PC1035

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

1D24V_M PHY

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1036

PC1036

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

PC1046

PC1046

PC1022

PC1022

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1037

PC1037

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

22U 0603 x 1 1D8V_PCH

But Layout No Space

So change to Cap list 1U 0402

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

CRB p56

PC1044

PC1038

PC1038

12

1D8V_PC H 1D24V_D SI_CSI

12

PC1039

PC1039

12

SCD1U25V2KX-GP

SCD1U25V2KX-GP

DY

DY

22U 0603 x 1

PC1101

PC1101

SC1U10V2KX-1GP

SC1U10V2KX-1GP

PC1044

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

DY

DY

22U 0603 x 1

12

PC1102

PC1102

1D05V_IO_ 3PHASEIO

22U 0603 x 1

PC1008

PC1008

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

1D05V_P CH

22U 0603 x 2

PC1041

PC1041

PC1040

PC1040

12

1D24V_A UD_ISH_PLL

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

3D3V_US B

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

22U 0603 x 1

PC1042

PC1042

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

1D24V_G LML

22U 0603 x 1

PC1043

PC1043

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

22U 0603 x 1

12

PC1103

PC1103

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

(VNN)

1V_CPU_ VNN

for 1V_VCCIOA

22U 0603 x 2

A A

PC1006

PC1006

12

PC1007

PC1007

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

5

4

1D35V_C PU_VDDQ_S3

PC1047

PC1047

PC1045

PC1045

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

12

DY

DY

0.1U 0402 x 1

22U 0603 x 8 , DY x 2

X00_0504

PC1001

PC1001

PC1002

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

PC1052

PC1052

12

DY

DY

3

PC1002

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

DY

DY

SC22U6D3V3MX-1-GP

12

12

PC1003

PC1003

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

DY

DY

PC1027

PC1027

12

follow CRB

<Core Design>

<Core Design>

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

PC1004

PC1004

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

DY

DY

2

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (Power CAP1)

CPU (Power CAP1)

CPU (Power CAP1)

Turis APL UMA

Turis APL UMA

Wednesd ay, July 27, 2016

Wednesd ay, July 27, 2016

Wednesd ay, July 27, 2016

Turis APL UMA

Taipei Hsien 221, Taiwan, R.O.C.

10 106

10 106

10 106

1

X02

X02

X02

Vinafix.com

SSID = CPU

5

4

3

2

1

D D

1D8V_PC H

CRB p57

1U 0402 x 5

C1104

SC1U10V2KX-1GP

C1104

SC1U10V2KX-1GP

C1103

SC1U10V2KX-1GP

C1103

SC1U10V2KX-1GP

C1102

SC1U10V2KX-1GP

C1102

SC1U10V2KX-1GP

C1101

SC1U10V2KX-1GP

C1101

SC1U10V2KX-1GP

12

12

1D24V_D SI_CSI

1U 0402 x 2

C C

B B

1V_CPU_ VCGI

C1107

SC1U10V2KX-1GP

C1107

SC1U10V2KX-1GP

C1106

C1106

12

12

12

12

change from INTEL 559091 MOW Page 4

SC1U10V2KX-1GP

SC1U10V2KX-1GP

3D3V_US B

1U 0402 x 4

C1109

C1109

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

C1108

SC1U10V2KX-1GP

C1108

SC1U10V2KX-1GP

C1111

C1111

12

3D3V_VC CRTC

C1113

C1113

12

1D24V_U SB2

1U 0402 x1

C1112

SC1U10V2KX-1GP

C1112

C1110

SC1U10V2KX-1GP

C1110

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

SC1U10V2KX-1GP

12

(VNN) for 1V_VCCIOA

1V_CPU_ VNN

C1016

C1016

12

1D24V_M PHY

1U 0402 x 2

C1017

C1017

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

1D05V_IO_ 3PHASEIO

1U 0402 x 4

C1001

C1001

12

1D05V_P CH

1U 0402 x 4

C1005

C1005

12

1D24V_A UD_ISH_PLL

1U 0402 x 2

C1009

C1009

C1010

C1010

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1002

C1002

C1003

C1003

C1004

C1004

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1007

C1007

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

1D24V_G LML

12

12

C1008

C1008

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

12

C1006

C1006

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

1U 0402 x 3

C1013

C1013

C1012

C1012

C1011

C1011

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1014

C1014

C1015

C1015

C1018

C1018

12

12

SC1U10V2KX-1GP

12

12

C1019

C1019

C1020

C1020

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

A A

5

12

C1021

C1021

12

C1022

C1022

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

12

C1023

C1023

C1025

C1025

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

4

12

C1024

C1024

12

C1026

C1026

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

C1027

C1027

12

12

C1028

C1028

12

C1030

C1030

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

3

C1029

C1029

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

CPU (Power CAP2)

CPU (Power CAP2)

CPU (Power CAP2)

Turis APL UMA

Turis APL UMA

Wednesd ay, July 27, 2016

Wednesd ay, July 27, 2016

Wednesd ay, July 27, 2016

Turis APL UMA

Taipei Hsien 221, Taiwan, R.O.C.

11 106

11 106

11 106

1

X02

X02

X02

Vinafix.com

5

4

3

2

1

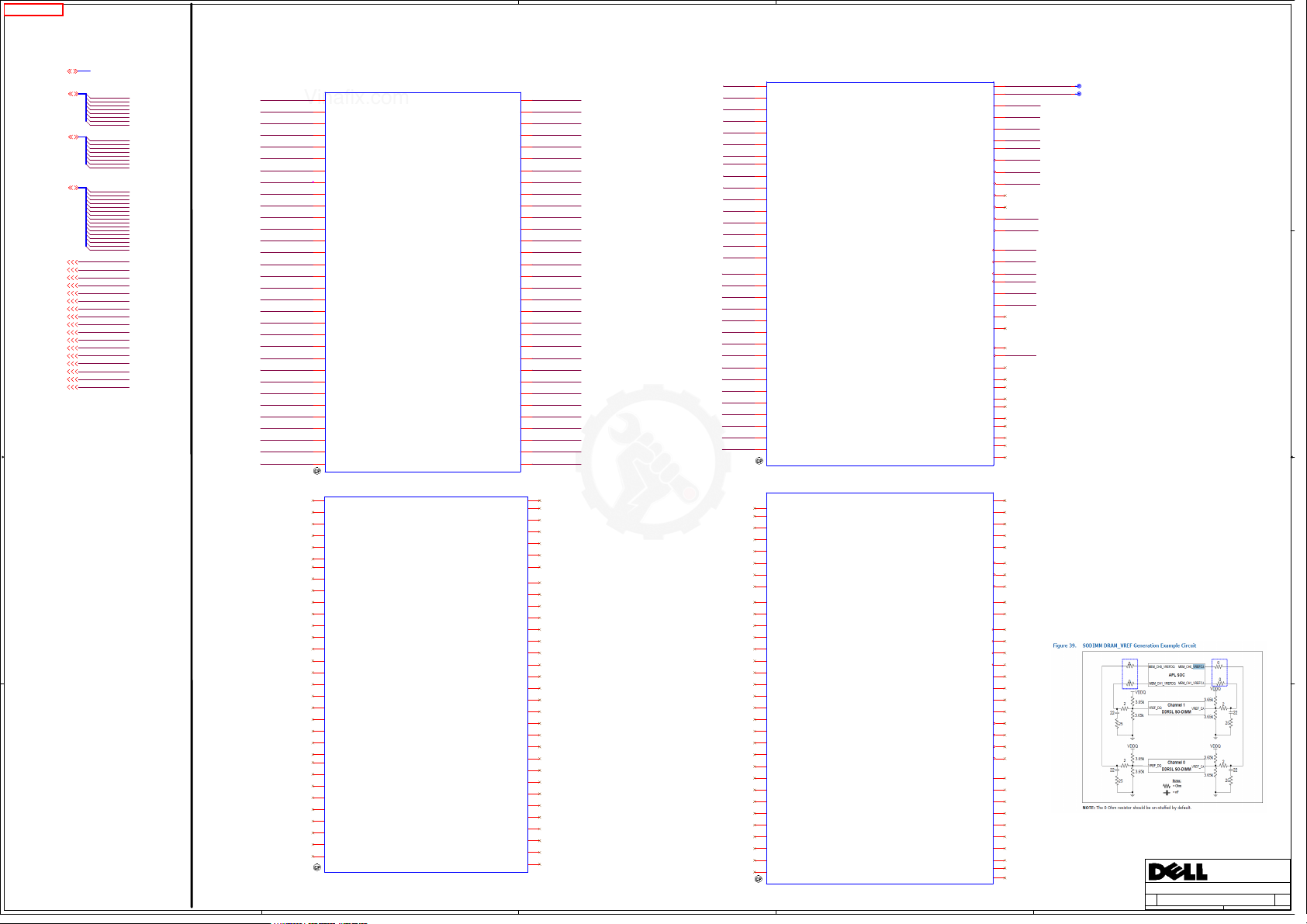

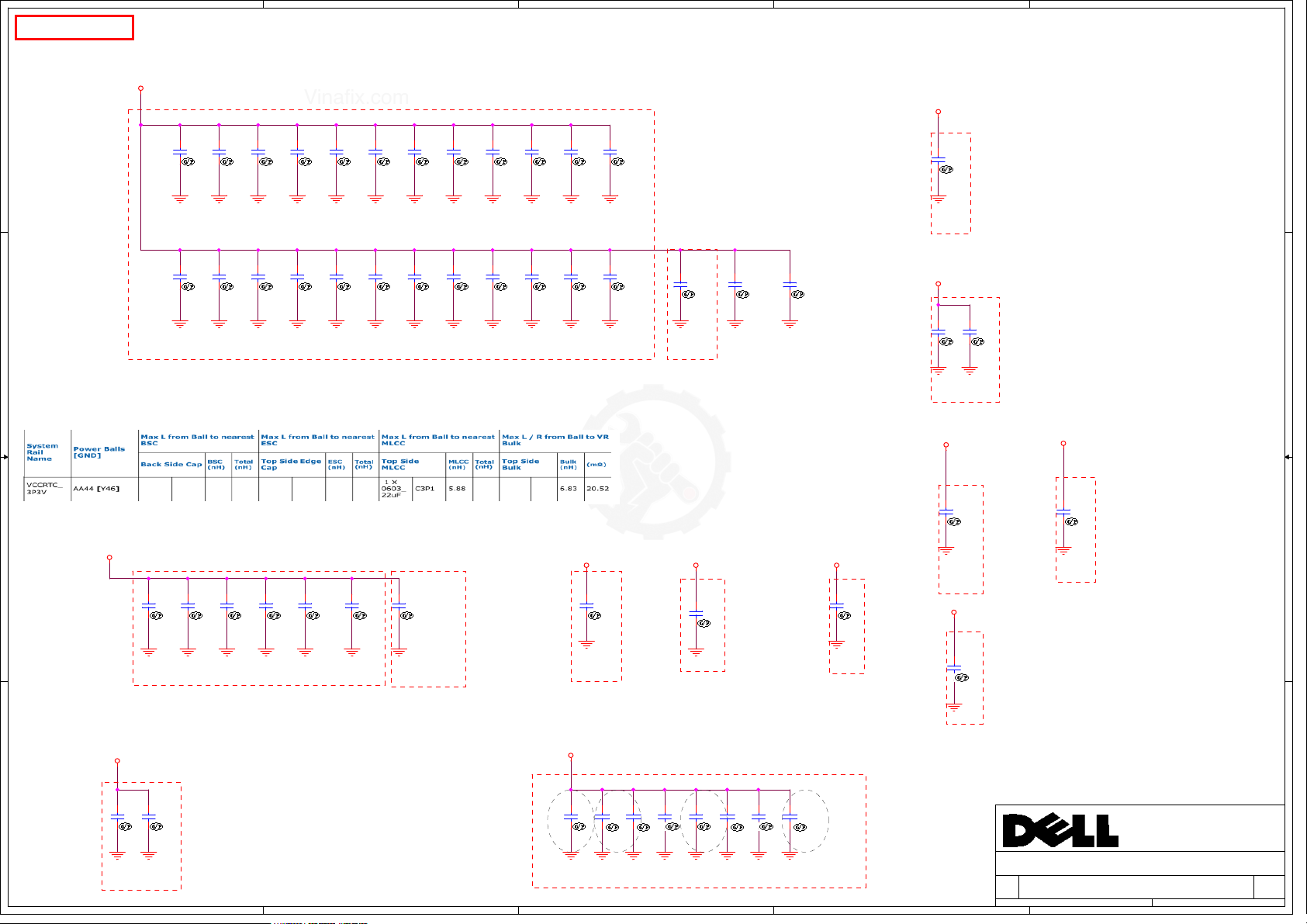

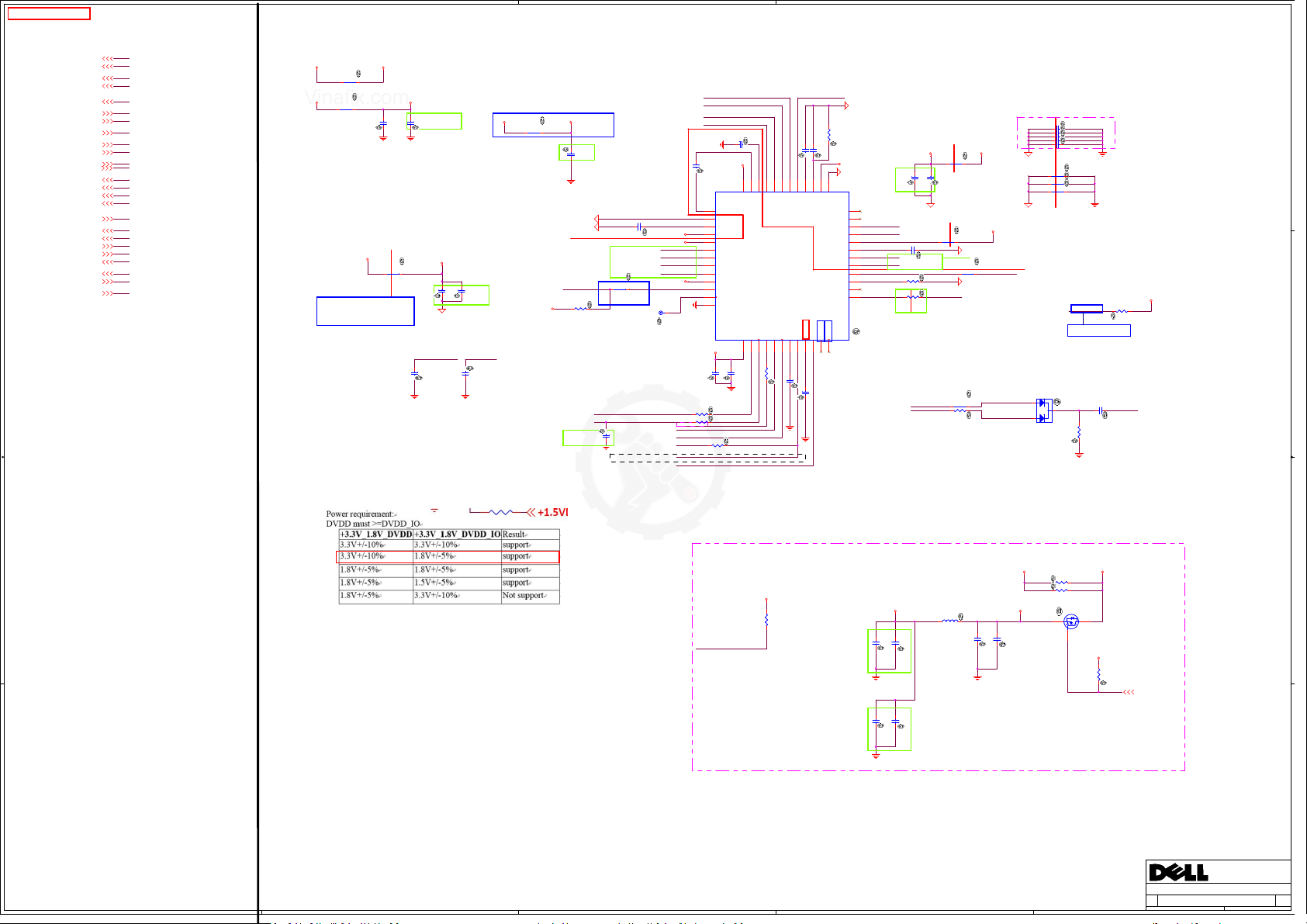

SSID = MEMORY

DDR_DATA

D D

C C

B B

M_A_DQS_DN[7:0][5]

M_A_DQS_DP[7:0][5]

M_A_DQ[63:0][5]

M_A_A[15:0][5]

DDR CMD/ADD

M_A_RAS#[5]

M_A_WE#[5]

M_A_CAS#[5]

M_A_BS2[5]

M_A_BS0[5]

M_A_BS1[5]

DDR CTRL

M_A_CS#0[5]

M_A_CS#1[5]

M_A_CKE0[5]

M_A_CKE1[5]

M_A_ODT0[5]

M_A_ODT1[5]

DDR CLOCK

M_A_CLK0[5]

M_A_CLK#0[5]

M_A_CLK1[5]

M_A_CLK#1[5]

DDR OTHERS

DDR_DRAMRST#[5]

PCH_SMB_DATA[17,65,70]

PCH_SMB_CLK[17,65,70]

M_A_ODT0

M_A_ODT1

VREF_CA

VREF_DQ

DDR_DRAMRST#_R

0D675V_VREF_S0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS2

M_A_BS0

M_A_BS1

M_A_DQ20

M_A_DQ21

M_A_DQ17

M_A_DQ18

M_A_DQ22

M_A_DQ16

M_A_DQ19

M_A_DQ23

M_A_DQ10

M_A_DQ13

M_A_DQ8

M_A_DQ11

M_A_DQ9

M_A_DQ14

M_A_DQ12

M_A_DQ15

M_A_DQ5

M_A_DQ0

M_A_DQ4

M_A_DQ2

M_A_DQ6

M_A_DQ1

M_A_DQ7

M_A_DQ3

M_A_DQ24

M_A_DQ25

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ26

M_A_DQ28

M_A_DQ27

M_A_DQ32

M_A_DQ38

M_A_DQ35

M_A_DQ33

M_A_DQ37

M_A_DQ36

M_A_DQ34

M_A_DQ39

M_A_DQ40

M_A_DQ46

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ41

M_A_DQ47

M_A_DQ53

M_A_DQ54

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ55

M_A_DQ48

M_A_DQ56

M_A_DQ61

M_A_DQ58

M_A_DQ63

M_A_DQ60

M_A_DQ62

M_A_DQ59

M_A_DQ57

M_A_DQS_DN2

M_A_DQS_DN1

M_A_DQS_DN0

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

M_A_DQS_DP2

M_A_DQS_DP1

M_A_DQS_DP0

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

DM1

DM1

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12

119

A13

80

A14

78

A15

79

A16/BA2

109

BA0

108

BA1

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

10

DQS0#

27

DQS1#

45

DQS2#

62

DQS3#

135

DQS4#

152

DQS5#

169

DQS6#

186

DQS7#

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

116

ODT0

120

ODT1

126

VREF_C A

1

VREF_D Q

30

RESET#

203

VTT1

204

VTT2

SKT_DDR 204P SMD

SKT_DDR 204P SMD

DDR3-204P-262-GP-U

DDR3-204P-262-GP-U

62.10024.S21

62.10024.S21

Need Handchange

Main :62.10024.M31

Second :62.10017.X41

EVENT#

VDDSPD

NC#/TEST

NP1

NP1

NP2

NP2

M_A_RAS#

110

RAS#

M_A_WE#

113

WE#

M_A_CAS#

115

CAS#

M_A_CS#0

114

CS0#

M_A_CS#1

121

CS1#

M_A_CKE0

73

CKE0

M_A_CKE1

74

CKE1

M_A_CLK0

101

CK0

M_A_CLK#0

103

CK0#

M_A_CLK1

102

CK1

M_A_CLK#1

104

CK1#

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

PCH_SMB_DATA

200

SDA

PCH_SMB_CLK

202

SCL

TS#_DIMM0_1

198

199

197

SA0

201

SA1

77

NC#1

122

NC#2

125

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

44

VSS

48

VSS

49

VSS

54

VSS

55

VSS

60

VSS

61

VSS

65

VSS

66

VSS

71

VSS

72

VSS

127

VSS

128

VSS

133

VSS

134

VSS

138

VSS

139

VSS

144

VSS

145

VSS

150

VSS

151

VSS

155

VSS

156

VSS

161

VSS

162

VSS

167

VSS

168

VSS

172

VSS

173

VSS

178

VSS

179

VSS

184

VSS

185

VSS

189

VSS

190

VSS

195

VSS

196

VSS

205

VSS

206

VSS

DIMM1_SA0

DIMM1_SA1

1D35V_DIMM_VDDQ_S3

1

X00_0504

1D35V_DIMM_VDDQ_S3

A00_0908

12

C1216

C1216

TP1201 T PAD14-OP-GPTP1201 TPAD14-OP-GP

12

C1224

C1224

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

Layout Note:

Place these Caps near SO-DIMMA.

SODIMM A DECOUPLING

12

12

C1202

C1202

C1201

C1201

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

DY

DY

12

12

12

C1213

C1213

C1214

C1214

C1206

C1206

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

SC100P50V2JN-3GP

SC100P50V2JN-3GP

3D3V_S0

SC100P50V2JN-3GP

SC100P50V2JN-3GP

12

C1223

C1223

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

12

12

12

C1205

C1205

C1218

C1218

C1203

C1203

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C1215

C1215

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

0D675V_VREF_S0

A00_0908

12

C1211

C1211

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

Note:

If SA0 DIM0 = 0, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA0

SO-DIMMA TS Address is 0x30

If SA0 DIM0 = 1, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA2

SO-DIMMA TS Address is 0x32

DIMM1_SA0

R1213

R1213

0R0402-PAD-2-GP

0R0402-PAD-2-GP

1 2

Layout Note:

Place these capsclose to VTT1 and VTT2.

12

12

12

C1209

C1209

C1207

C1207

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

DY

DY

DY

DY

12

C1217

C1217

SC100P50V2JN-3GP

SC100P50V2JN-3GP

DIMM1_SA1

12

C1210

C1210

C1208

C1208

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

For EMI Reserved

DDR_DRAMRST#

ED1202

ED1202

DDR_DRAMRST#

R1201

R1201

0R0402-PAD-2-GP

0R0402-PAD-2-GP

1 2

12

12

C1212

C1212

C1220

C1220

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

DY

DY

For Intel Recommend Close to DIMM

The design of Vref refer to PDG rev.1.0.

VREF_DQ

For Intel Recommend Close to DIMM

DDR_DRAMRST#_R

12

AZ5725-01FDR7G-GP

AZ5725-01FDR7G-GP

DY

DY

12

ED1201

ED1201

AZ5725-01FDR7G-GP

AZ5725-01FDR7G-GP

DY

DY

VREF_CA

RN1201

RN1201

SRN1KJ-7-GP

SRN1KJ-7-GP

1D35V_DIMM_VDDQ_S3

1234

DDR_DRAMRST#_R

1D35V_DIMM_VDDQ_S3

12

R1208

R1208

3K65R2F-1-GP

3K65R2F-1-GP

12

R1212

R1212

3K65R2F-1-GP

3K65R2F-1-GP

1D35V_DIMM_VDDQ_S3

12

R1207

R1207

3K65R2F-1-GP

3K65R2F-1-GP

12

R1211

R1211

3K65R2F-1-GP

3K65R2F-1-GP

A00_0908

X01_0531

A A

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A1

A1

A1

Thursday, September 08, 2016

Thursday, September 08, 2016

Thursday, September 08, 2016

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

DDR3L-Memory Down

DDR3L-Memory Down

DDR3L-Memory Down

Turis APL UMA

Turis APL UMA

Turis APL UMA

12 106

12 106

12 106

X02

X02

X02

Vinafix.com

5

4

3

2

1

SSID = MEMORY

D D

C C

Blanking

B B

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Wednesday, July 27, 2016

Wednesday, July 27, 2016

Wednesday, July 27, 2016

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

(Reserved)

(Reserved)

(Reserved)

Turis APL UMA

Turis APL UMA

Turis APL UMA

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

X02

X02

13 106

13 106

13 106

1

X02

Vinafix.com

5

4

3

2

1

SSID = CPU

D D

C C

Blanking

B B

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

<Core Design>

<Core Design>

<Core Design>

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

application without get Wistron permission

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

(Reserved)

(Reserved)

(Reserved)

Turis APL UMA

Turis APL UMA

Wednesday, July 27, 2016

Wednesday, July 27, 2016

Wednesday, July 27, 2016

2

Turis APL UMA

14 106

14 106

14 106

1

X02

X02

X02

Vinafix.com

5

4

3

2

1

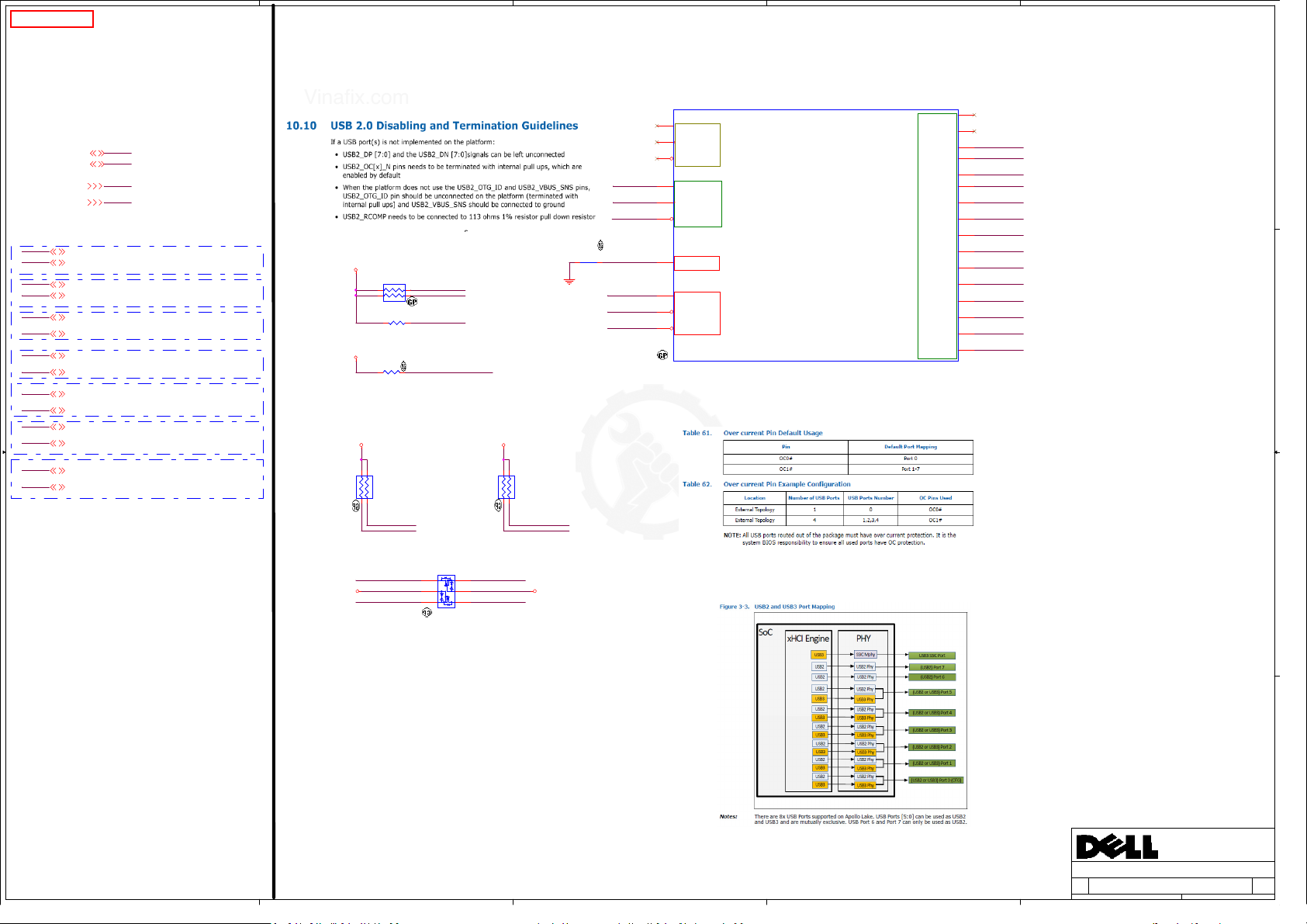

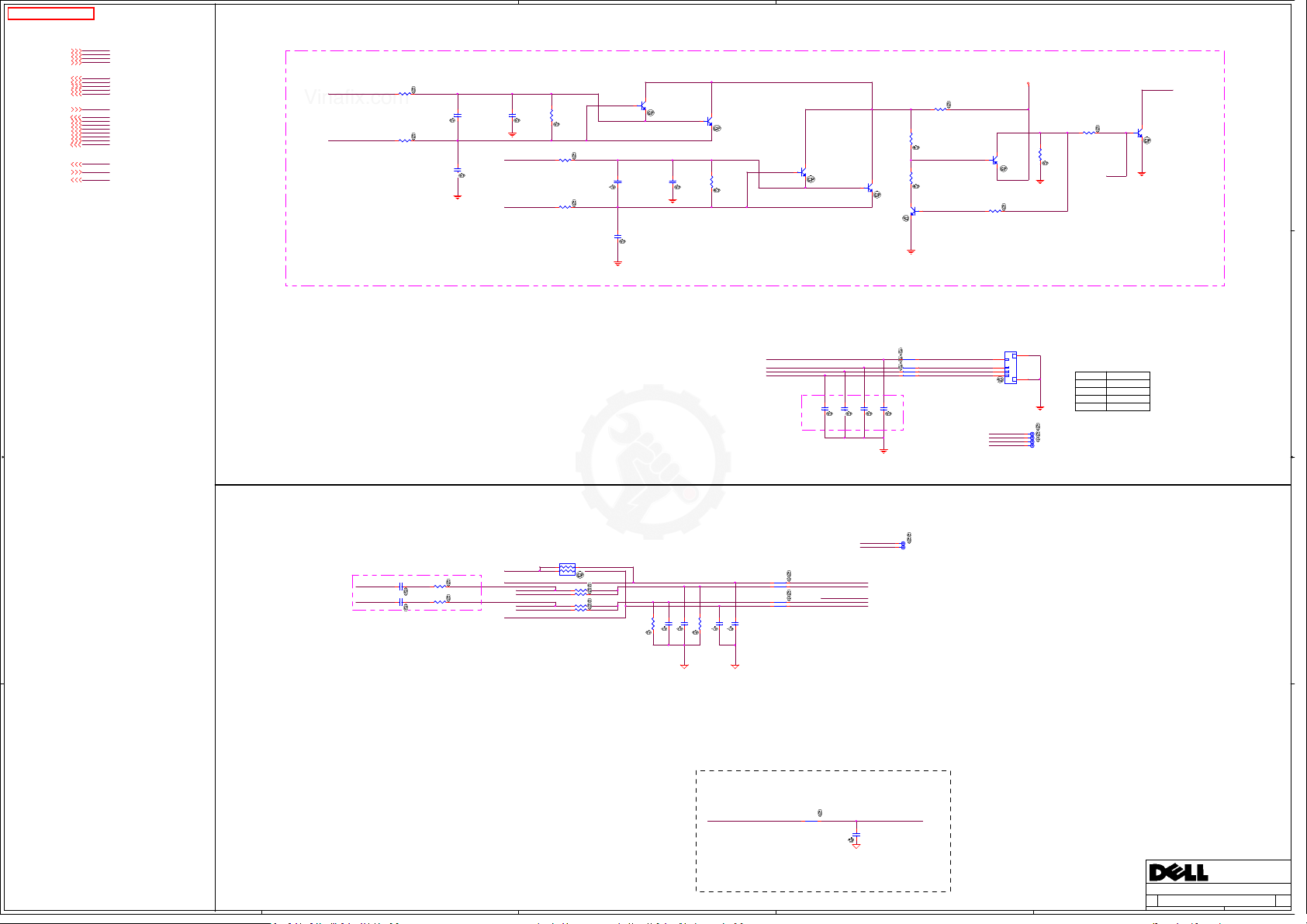

SSID = STRAP

GPIO

Schematic

D D

High

Low

GPIO

Schematic

GPIO_36

1D8V_S5

12

R1501

R1501

DY

DY

4K7R2F-GP

4K7R2F-GP

GPIO36_VCCIO_LEVEL [21]

12

R1502

R1502

DY

DY

10KR2F-2-GP

10KR2F-2-GP

VCCIO used for B-step

default (A-step)

default (A-step)

default (A-step)default (A-step)

Weak internal pull-down Weak internal pull-down

GPIO_88

1D8V_S5

12

R1523

R1523

DY

DY

10KR2F-2-GP

10KR2F-2-GP

12

R1511

R1511

4K7R2F-GP

4K7R2F-GP

High

PMU 3.3V mode select

PMU 3.3V mode select

PMU 3.3V mode selectPMU 3.3V mode select

Low

Weak internal pull-up

C C

GPIO

GPIO_123

1D8V_S5

12

R1525

Schematic

DY

DY

DY

DY

12

R1525

10KR2J-3-GP

10KR2J-3-GP

R1526

R1526

4K7R2F-GP

4K7R2F-GP

GP_SSP2_TXD [19,99]

GPIO_39

1D8V_S5

12

R1503

R1503

4K7R2F-GP

4K7R2F-GP

DY

DY

GPIO39_TXE_BPS [18]

12

R1504

R1504

DY

DY

4K7R2F-GP

4K7R2F-GP

enable CSE ROM bypass

default (disable bypass)

default (disable bypass)

default (disable bypass)default (disable bypass)

GPIO_92 GPIO_111

1D8V_S5

12

R1512

R1512

DY

DY

10KR2F-2-GP

10KR2F-2-GP

GPIO92_SMB_NRB [19]

12

R1513

R1513

DY

DY

4K7R2F-GP

4K7R2F-GP

SMBS No-reboot enable

default (SMBus No Re-Boot

default (SMBus No Re-Boot

default (SMBus No Re-Boot default (SMBus No Re-Boot

Disable)

Disable)

Disable)Disable)

Weak internal pull-down

GPIO_43 GPIO_44

1D8V_S5

12

R1521

R1521

A00_0905

DY

DY

4K7R2F-GP

4K7R2F-GP

GPIO43_EMMC_BOOT [18]

12

R1505

R1505

4K7R2F-GP

4K7R2F-GP

A00_0905

RSVD

Weak internal pull-up

1D8V_S5

12

R1514

R1514

DY

DY

10KR2F-2-GP

10KR2F-2-GP

GPIO111_BBS [19]

12

R1515

R1515

4K7R2F-GP

4K7R2F-GP

Do not boot from SPI

Do not boot from SPI

Do not boot from SPIDo not boot from SPI

Weak internal pull-up

boot from SPI

1D8V_S5

12

R1506

R1506

4K7R2F-GP

4K7R2F-GP

GPIO44_SPI_BOOT [18]

12

R1507

R1507

DY

DY

4K7R2F-GP

4K7R2F-GP

default

default

defaultdefault

( allow SPI as a boot source)

( allow SPI as a boot source)

( allow SPI as a boot source)( allow SPI as a boot source)

Weak internal pull-up

disable

GPIO_110

1D8V_S5

12

R1524

R1524

4K7R2F-GP

4K7R2F-GP

DY

DY

GPIO110_LPC_LEVEL [19]GPIO88_PMU_LEVEL [19]

12

R1516

R1516

4K7R2F-GP

4K7R2F-GP

LPC 1.8V mode selectPMU 1.8V mode select

LPC 3.3V mode select

LPC 3.3V mode select

LPC 3.3V mode selectLPC 3.3V mode select

Weak internal pull-up

GPIO_47

1D8V_S5

12

R1509

R1509

DY

DY

4K7R2F-GP

4K7R2F-GP

GPIO47_DNXFW [18]

12

R1508

R1508

DY

DY

10KR2F-2-GP

10KR2F-2-GP

force DNX FW Load

default

default

defaultdefault

( don't force DNX FW Load)

( don't force DNX FW Load)

( don't force DNX FW Load)( don't force DNX FW Load)

Weak internal pull-down

GPIO_118

1D8V_S5

12

R1518

R1518

4K7R2F-GP

4K7R2F-GP

GPIO118_FLASH_OVR [19]

12

R1517

R1517

DY

DY

4K7R2F-GP

4K7R2F-GP

Flash Descriptor Override

No Override (Normal Operation)

No Override (Normal Operation)

No Override (Normal Operation)No Override (Normal Operation)

Weak internal pull-down

GPIO_78

1D8V_S5

12

R1522

R1522

DY

DY

10KR2F-2-GP

10KR2F-2-GP

GPIO78_SMB_LEVEL [19]

12

R1510

R1510

4K7R2F-GP

4K7R2F-GP

SMBus 1.8V mode select

SMBus 3.3V mode select

SMBus 3.3V mode select

SMBus 3.3V mode selectSMBus 3.3V mode select

Weak internal pull-up

GPIO_120

1D8V_S5

12

R1520

R1520

DY

DY

4K7R2F-GP

4K7R2F-GP

GPIO120_BIOS_SWAP [19]

12

R1519

R1519

DY

DY

10KR2F-2-GP

10KR2F-2-GP

Two SWAP override enable

default

default

defaultdefault

( Disable top swap override )

( Disable top swap override )

( Disable top swap override )( Disable top swap override )

Weak internal pull-down

RSVD (Internal 20K PU)

High

RSVD

Low

B B

A A

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A1

A1

A1

Monday, September 05, 2016

Monday, September 05, 2016

Monday, September 05, 2016

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU(STRAP)

CPU(STRAP)

CPU(STRAP)

Turis APL UMA

Turis APL UMA

Turis APL UMA

15 106

15 106

15 106

X02

X02

X02

Vinafix.com

5

4

3

2

1

SSID = PCH

9 OF 23

1.24V

9 OF 23

T2

PCIE_P 2_TXP

T3

PCIE_P 2_TXN

M5

PCIE_P 2_RXP

M6

PCIE_P 2_RXN

R1

PCIE_P 1_TXP

R2

PCIE_P 1_TXN

T10

PCIE_P 1_RXP

T12

PCIE_P 1_RXN

V3

PCIE_P 0_TXP

V2

PCIE_P 0_TXN

P7

PCIE_P 0_RXP

P6

PCIE_P 0_RXN

PCIE_W AKE3#

PCIE_W AKE2#

1.8V

PCIE_W AKE1#

PCIE_W AKE0#

10 OF 23

10 OF 23

B7

B5

A7

B8

C10

A10

C11

B11

AJ62

AH61

AH62

AK62

AH13

AH12

AG16

AG15

N62

P61

P62

R62

WLAN_CLK_CPU

WLAN_CLK_CPU#

LAN_CLKREQ_CPU#

WLAN_CLKREQ_CPU#

PCIE_CLKREQ1_CPU#

GFX_CLKREQ_CPU#

PCIE_WAKE3_CPU

PCIE_WAKE2_CPU

PCIE_WAKE1_CPU

PCIE_WAKE0_CPU

CRB 122 page

X01_0518

WLAN

X01_0518

VIL=0.35*1.8=0.63 V

WLAN_CLKREQ_CPU# WLAN_CLKREQ_D

X01_0518

RN1607

PCIE_WAKE3_CPU

PCIE_WAKE2_CPU

PCIE_WAKE1_CPU

PCIE_WAKE0_CPU

RN1607

1

2 3

SRN10KJ-5-GP

SRN10KJ-5-GP

RN1608

RN1608

1

2 3

SRN10KJ-5-GP

SRN10KJ-5-GP

X01_0518

PCIE_CLKREQ1_CPU#

GFX_CLKREQ_CPU#

WLAN and LAN side are OD pin,

so no need LS

WLAN_CLKREQ_CPU#

LAN_CLKREQ_CPU#

1

2 3

RN1606

RN1606

SRN10KJ-5-GP

SRN10KJ-5-GP

1

2 3

RN1603

RN1603

SRN10KJ-5-GP

SRN10KJ-5-GP

X01_0616

3D3V_S5

12

R1605

R1605

10KR2J-3-GP

10KR2J-3-GP

DY

DY

LBAS16LT1G-GP

LBAS16LT1G-GP

123

DY

DY

D1601

D1601

83.00016.P11

83.00016.P11

R1607

R1607

4

4

1D8V_S5

4

1D8V_S5

4

12

0R0402-PAD-2-GP

0R0402-PAD-2-GP

1D8V_S5

Q1601

Q1601

D

DY

DY

2N7002K-2-GP

2N7002K-2-GP

84.2N702.J31

84.2N702.J31

2ND = 084.27002.0A31

2ND = 084.27002.0A31

3rd = 84.07002.I31

3rd = 84.07002.I31

3D3V_S0

12

3D3V_S0

R1606

R1606

10KR2J-3-GP

10KR2J-3-GP

DY

DY

G

S

PEG_CLKREQ_WLAN# [61]

CPU1I

CPU1I

L2

PCIE_P 5_USB3_ P2_TX P

L1

PCIE_P 5_USB3_ P2_TX N

K7

PCIE_P 5_USB3_ P2_RX P

M7

D D

WLAN

WLAN_PCIE_TX_P[61]

WLAN_PCIE_TX_N[61]

WLAN_PCIE_RX_P[61]

WLAN_PCIE_RX_N[61]

WLAN_CLK_CPU[61]

C C

B B

WLAN_CLK_CPU#[61]

PEG_CLKREQ_WLAN#[61]

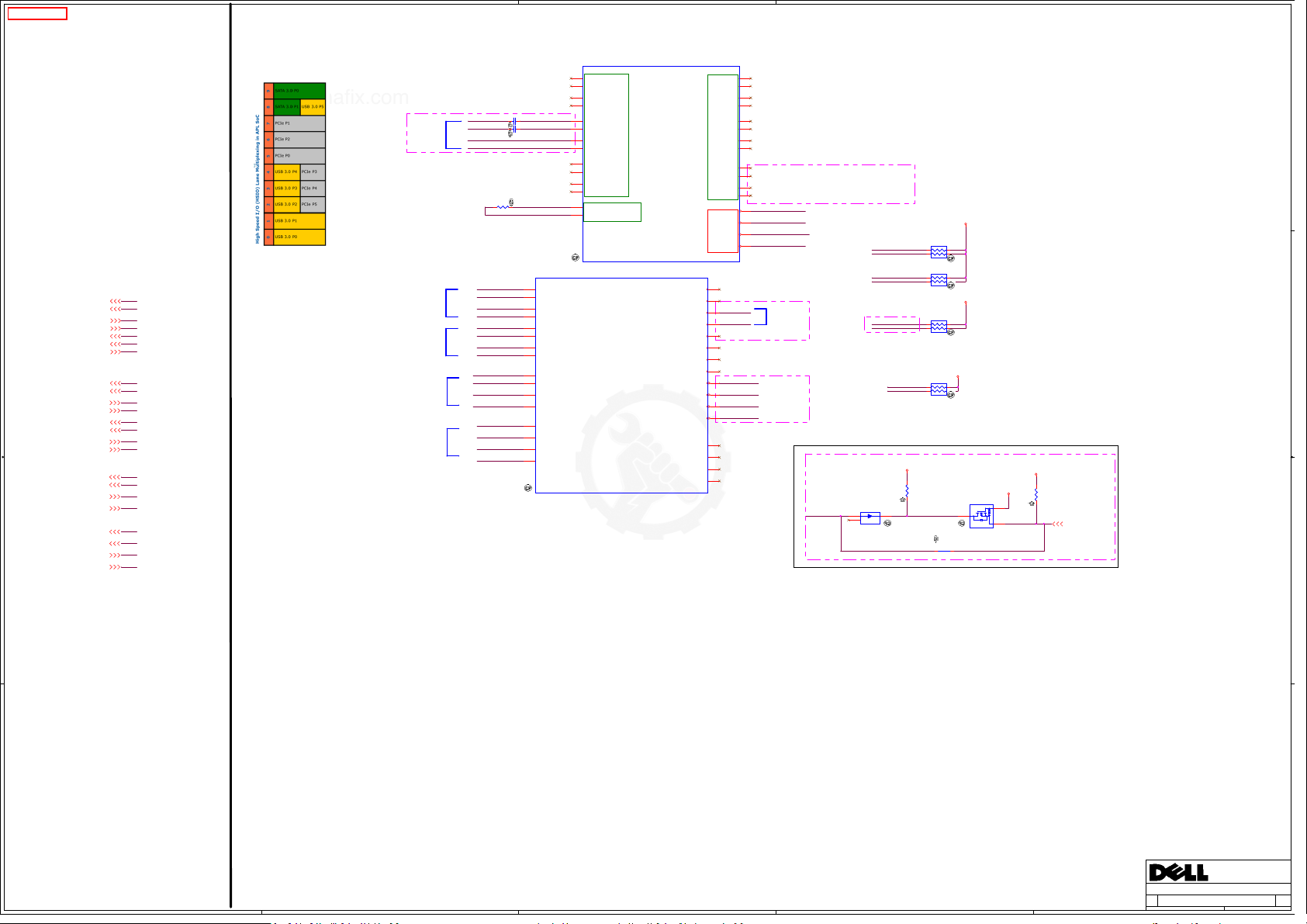

USB3.0

USB1_USB30_TX_P[35]

USB1_USB30_TX_N[35]

USB1_USB30_RX_P[35]

USB1_USB30_RX_N[35]

USB2_USB30_TX_P[35]

USB2_USB30_TX_N[35]

USB2_USB30_RX_P[35]

USB2_USB30_RX_N[35]

ODD

ODD_SATA_TX_P[60]

ODD_SATA_TX_N[60]

ODD_SATA_RX_P[60]

ODD_SATA_RX_N[60]

HDD

HDD_SATA_TX_P[60]

HDD_SATA_TX_N[60]

HDD_SATA_RX_P[60]

HDD_SATA_RX_N[60]

X01_0518

WLAN

USB3.0 port2

USB3.0 port1

ODD

HDD

C1601

C1601

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

12

C1602

C1602

12

R1601

R1601

PCIE_OBSP_CPU

1 2

402R2F-GP

402R2F-GP

PCIE_OBSN_CPU

Impedance / Space = 85R / 20 mils

CPU1J

USB2_USB30_TX_P

USB2_USB30_TX_N

USB2_USB30_RX_P

USB2_USB30_RX_N

USB1_USB30_TX_P

USB1_USB30_TX_N

USB1_USB30_RX_P

USB1_USB30_RX_N

ODD_SATA_TX_P

ODD_SATA_TX_N

ODD_SATA_RX_P

ODD_SATA_RX_N

HDD_SATA_TX_P

HDD_SATA_TX_N

HDD_SATA_RX_P

HDD_SATA_RX_N

CPU1J

K3

K2

F2

G2

J1

J2

K9

K10

W1

W2

T5

T6

Y3

Y2

T9

T7

APOLLO-LAKE-GP-U

APOLLO-LAKE-GP-U

WLAN_CPU_TX_PWLAN_PCIE_TX_P

WLAN_CPU_TX_NWLAN_PCIE_TX_N

WLAN_PCIE_RX_P

WLAN_PCIE_RX_N

USB3_P1 _TXP

USB3_P1 _TXN

USB3_P1 _RXP

USB3_P1 _RXN

USB3_P0 _TXP

USB3_P0 _TXN

USB3_P0 _RXP

USB3_P0 _RXN

SATA_P 1_USB3_ P5_TX P

SATA_P 1_USB3_ P5_TX N

SATA_P 1_USB3_ P5_RX P

SATA_P 1_USB3_ P5_RX N

SATA_P 0_TXP

SATA_P 0_TXN

SATA_P 0_RXP

SATA_P 0_RXN

PCIE_P 5_USB3_ P2_RX N

N2

PCIE_P 4_USB3_ P3_TX P

M2

PCIE_P 4_USB3_ P3_TX N

H5

PCIE_P 4_USB3_ P3_RX P

H6

PCIE_P 4_USB3_ P3_RX N

P3

PCIE_P 3_USB3_ P4_TX P

P2

PCIE_P 3_USB3_ P4_TX N

P12

PCIE_P 3_USB3_ P4_RX P

P10

PCIE_P 3_USB3_ P4_RX N

F6

PCIE2_ USB3_SA TA3_R COMP_P

F5

PCIE2_ USB3_SA TA3_R COMP_N

APOLLO-LAKE-GP-U

APOLLO-LAKE-GP-U

APL_SOC

APL_SOC

1.24V

1.24V

APL_SOC

APL_SOC

PCIE_C LKOUT3P

PCIE_C LKOUT3N

PCIE_C LKOUT2P

PCIE_C LKOUT2N

PCIE_C LKOUT1P

PCIE_C LKOUT1N

PCIE_C LKOUT0P

PCIE_C LKOUT0N

PCIE_C LKREQ3 #

PCIE_C LKREQ2 #

PCIE_C LKREQ1 #

PCIE_C LKREQ0 #

USB_SSI C_0_TX _P

USB_SSI C_0_TX _N

USB_SSI C_0_RX _P

USB_SSI C_0_RX _N

A A

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A1

A1

A1