Page 1

A

ASUS CONFIDENTIAL

B

C

D

E

MODEL NAME :

1

PCB NO :

???

ASUS P/N :

2

Elsa

1

???

2

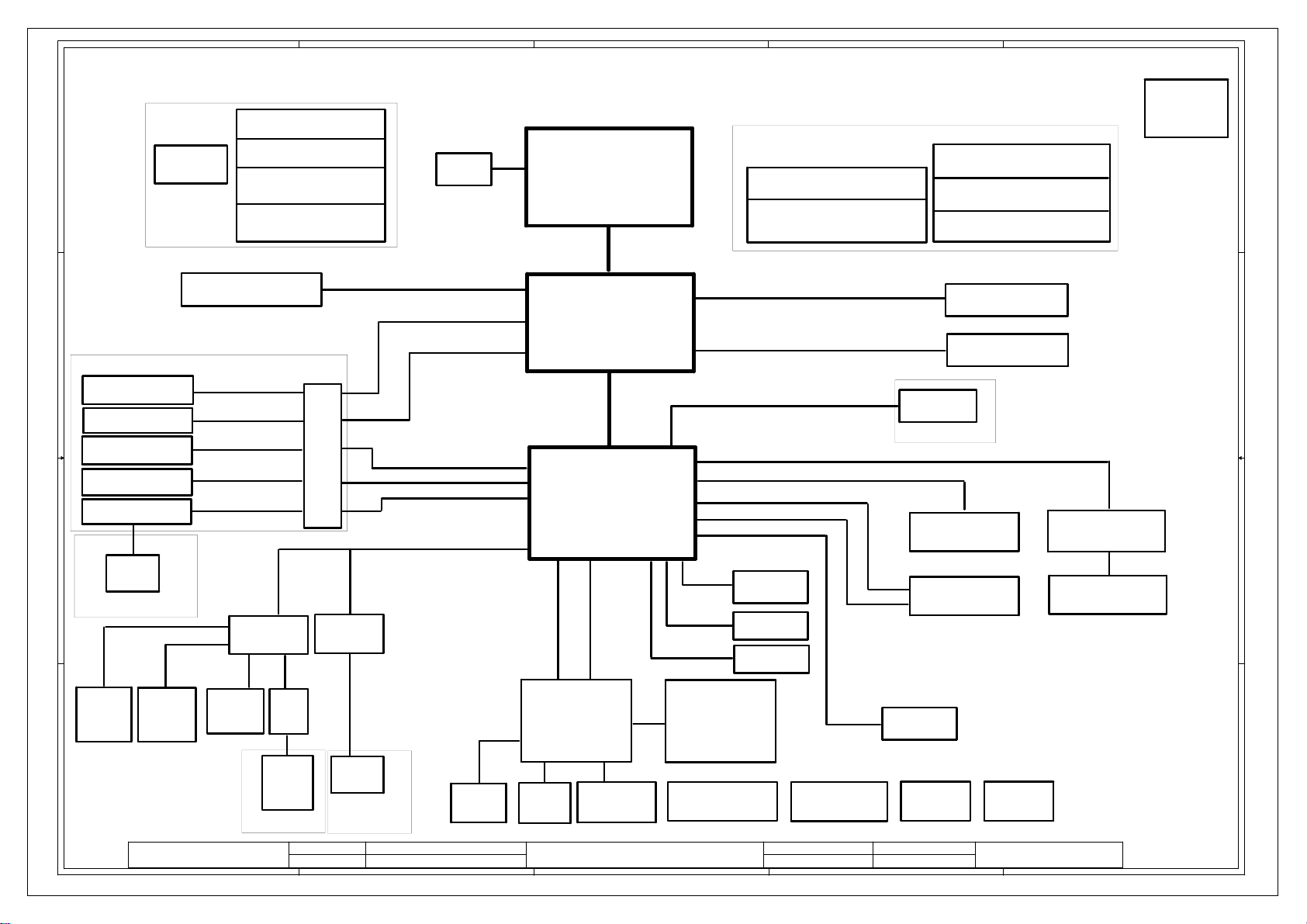

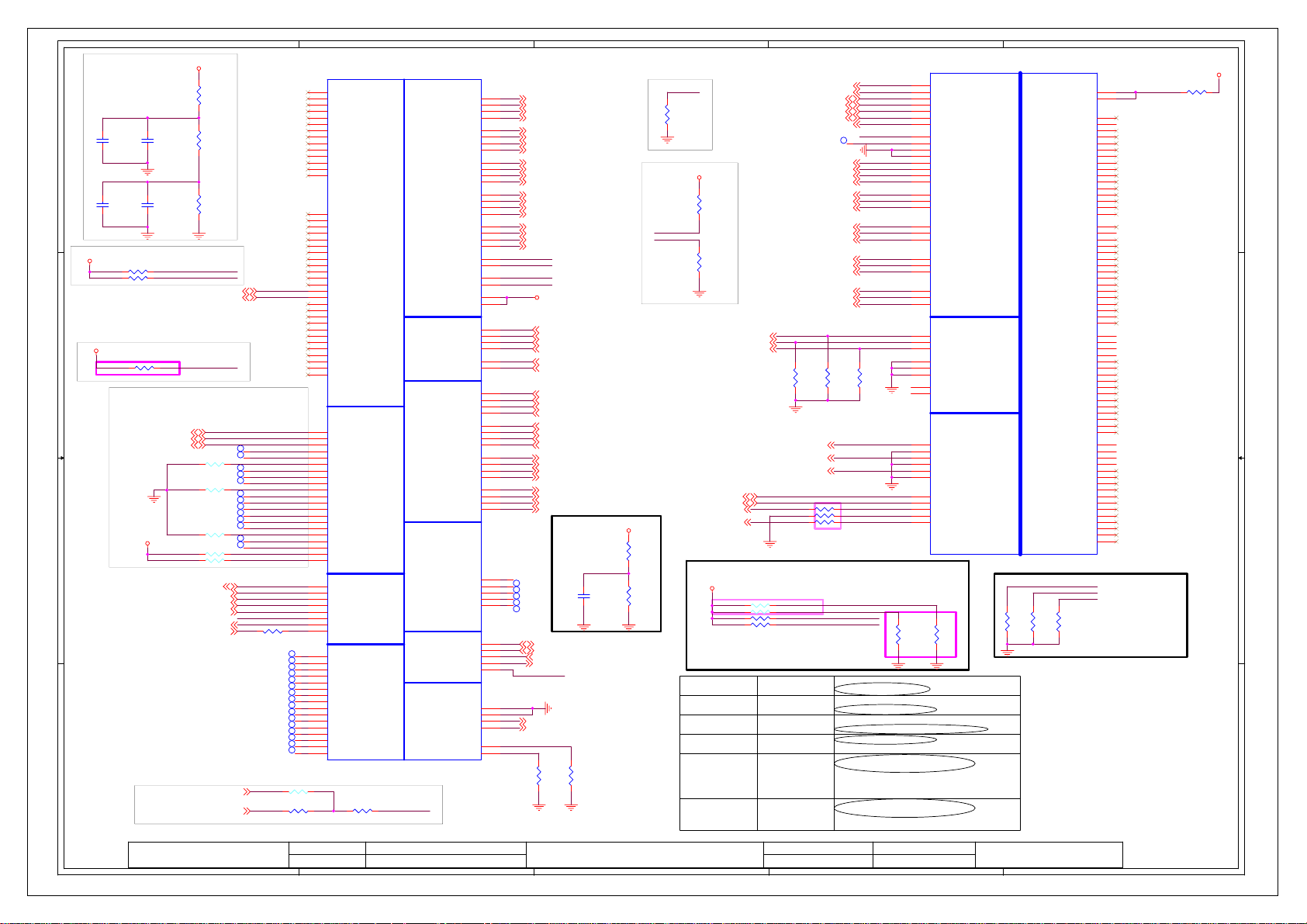

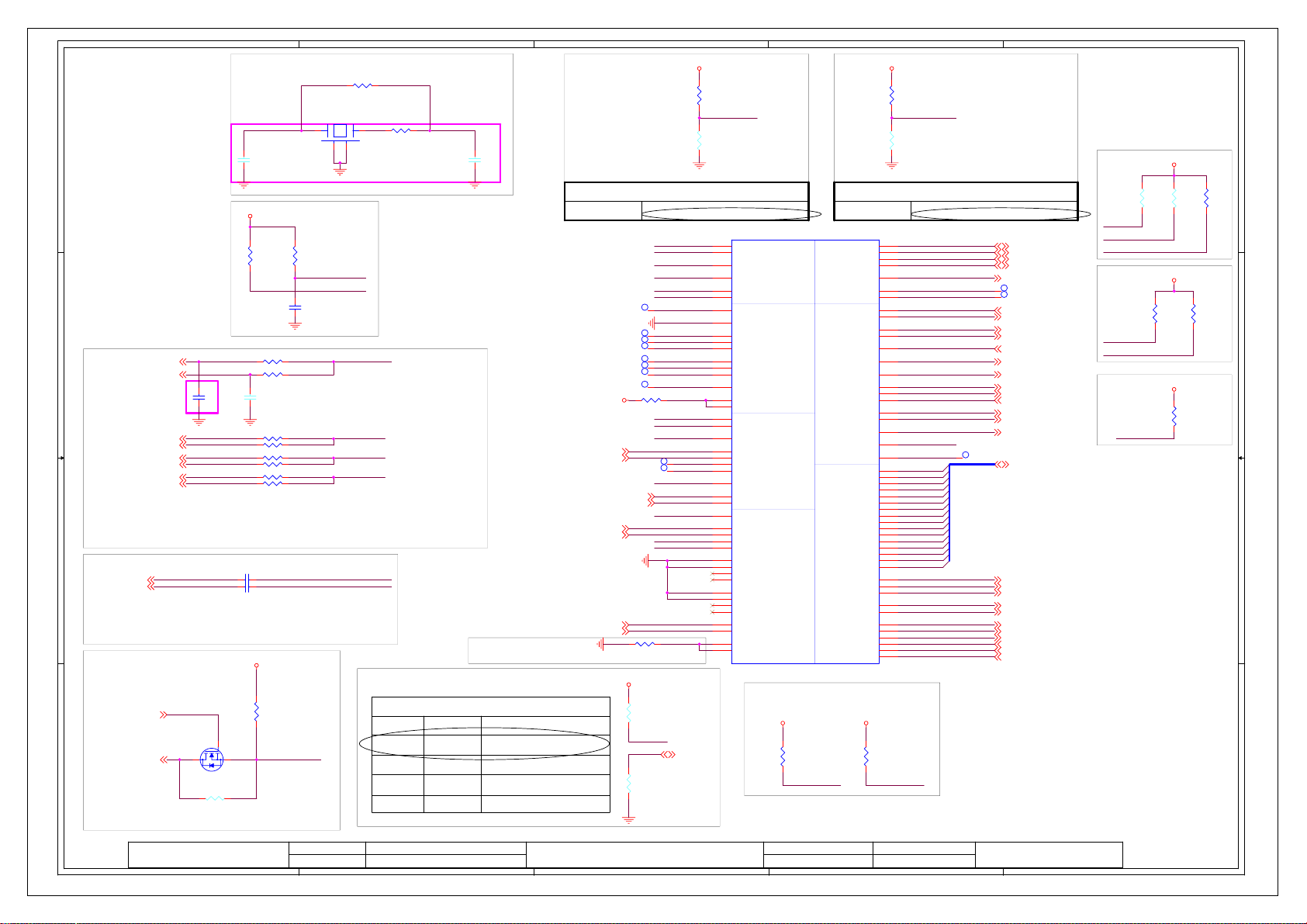

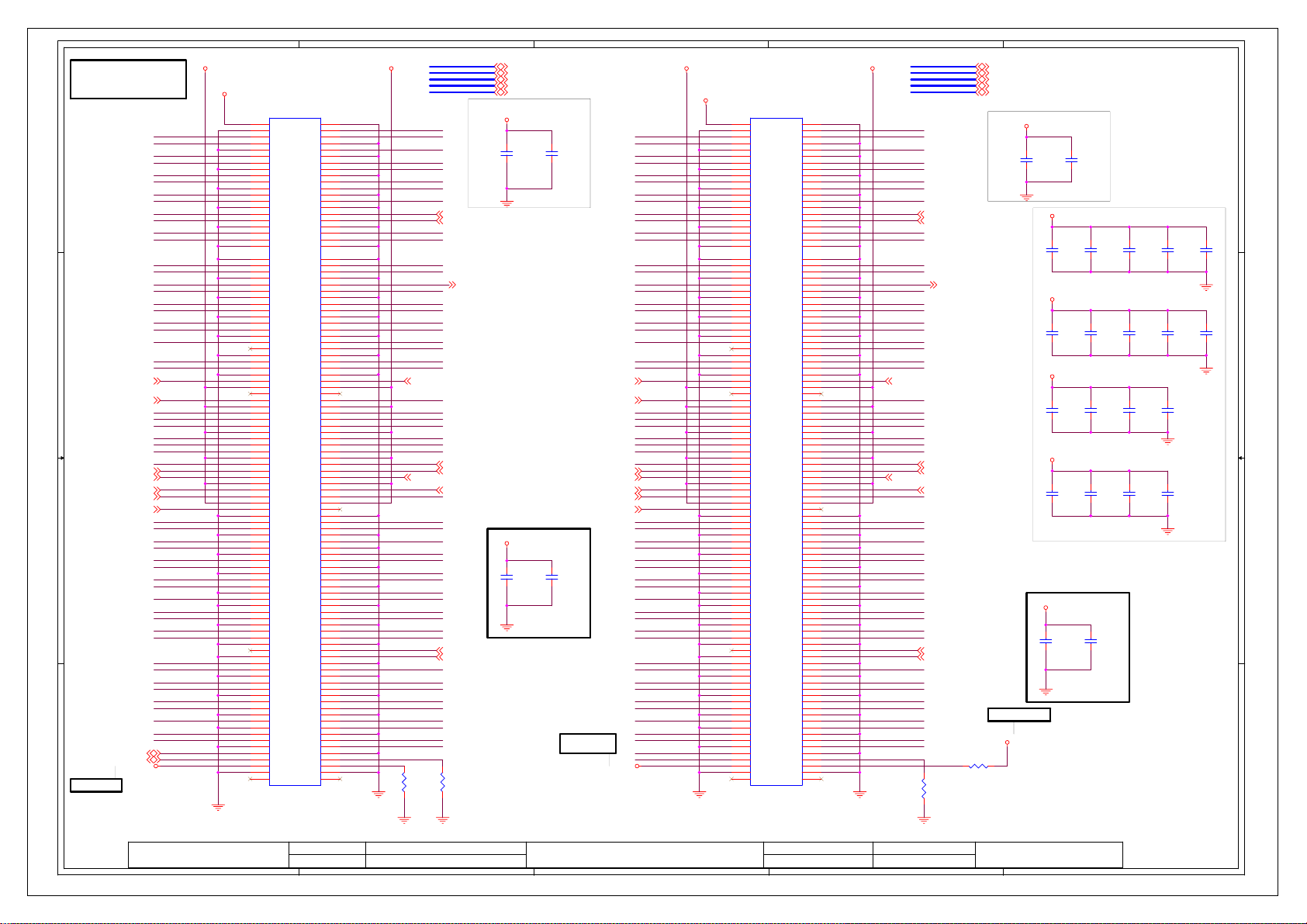

Lanai UMA Schematics Document

uFCPGA Mobile Merom

Intel Crestline-GM + ICH8M

3

3

2007-03-19

REV :1.2(DELL: X02)

4

5

MB PCB

Part Number Description

PCB 00B LA-3071P REV0 M/B

DA800004H0L

PROJECT:

BOM NO. ???

PCB P/N: ???

REVISION

A

1.2 1 68

Monday, March 19, 2007

DATE:

SHEET OF

B

DESCRIPTION:

Cover Page

C

RELEASE DATE :

D

DESIGN ENGINEER :SCHEMATIC FILE NAME :

E

4

5

Page 2

5

4

3

2

1

D

C

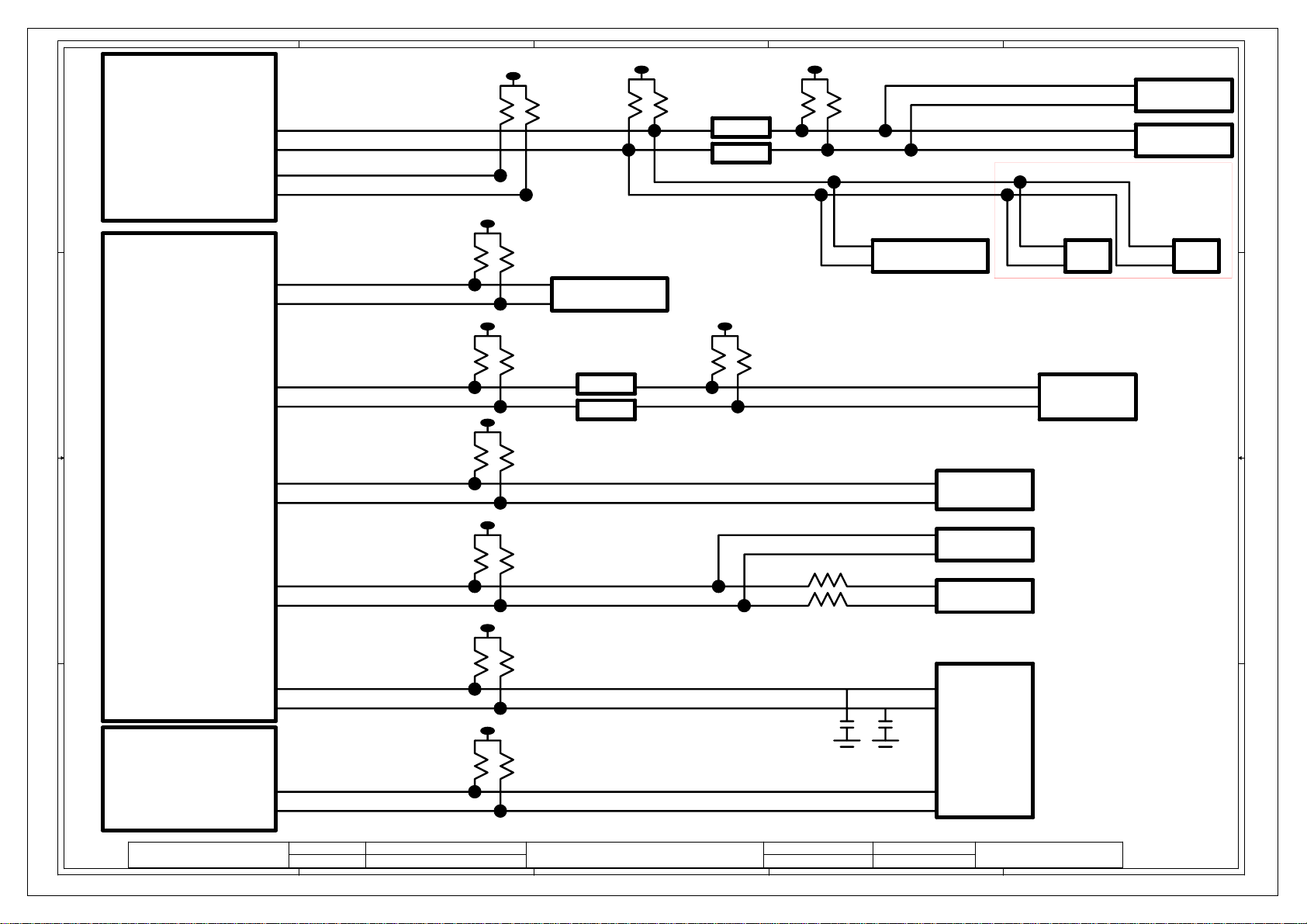

IO Board

CRT CONN.

TV CONN.

USB CONN.x2

MINI-CARD

MINI-CARD

B

SIM CARD Board

S/PDIF

TO TV

CONN.

PG 30

A

POWER

POWER

CON.

WLAN

WWAN

SIM

CARD

DIGITAL

MIC.

PG 28

PROJECT:

POWER SEQUENCE

LOGIC

POWER

CHARGER

POWER CONTROL

SWITCH

DISCHARGE PATH

+3.3V_SUS/+5V_SUS/+3.3V_RUN

+5V/+3.3V/+1.8V/+1.25_RUN

Panel Connector

PG 28

VGA

TVOUT

USB2.0(P2,3)

PCIEx1 (Lane2)

USB2.0(P9)

AUDIO/AMP

PG 44,45,46

Speaker

CON

PG 46

JACK Board

5

PG 51

PG 57

PG 49PG 59

PG 49

LVDS

VGA

TVOUT

D.B

CON

PG 50

USB2.0(P2,3)

PCIEx1 (Lane2)

USB2.0(P9)

MDC

PG 36

WtoB

CON

PG 46

Audio

Jacks

*3

RJ11

RJ11 Board

REVISION

1.2 2 68

Monday, March 19, 2007

DATE:

SHEET OF

4

PG 52

IHDA

LANAI: UMA

Merom

XDP

CIR

PG 41

(478 Micro-FCPGA)

(Symbol Rev.09)

Crestline

1299 uFCBGA

PG 9,10,11,12,13,14

(Symbol Rev.09)

DMI INTERFACE

ICH8-M

PG 15,16,17,18

(Symbol Rev.09)

SPI

SIO

MEC5025

128KB Flash

TMKBC

128 Pins VTQFP

PG 37

SPI

FLASH

PG 40

DESCRIPTION:

BLOCK DIAGRAM

PG 7,8

676 BGA

LPC

PS/2

Touchpad

CON.

PG 41

ECE5011

Expander

BC

USB 2.0 Hub(4)

128 Pins VTQFP

FAN &THERMAL

3

USB2.0(P0,P1)

PCIE (Lane6)

PCI

PCIE (Lane4)

USB2.0(P6)

USB2.0(P7)

USB2.0(P5)

SATA

SATA-HDD

IDE

SIO

PG 38

EMC4001

PG 43

POWER

POWER I/O

+1.5V_RUN/+1.05V_VCCP

REGULATOR

+VCC_GFX_CORE/+1.25V_RUN

533/667 MHZ DDR II

533/667 MHZ DDR II

CAMERA

PG 28

PG 31

CD-ROM

PG 31

USER

INTERFACE

PG 42

RELEASE DATE :

PG 55

PG 58

USB CONN.

PG 39

USB Board

CARD READER

1394/R5C833

EXPRESS-CARD

R5538

Bluetooth

PG 41

SNIFFER

PG 42

2

POWER VCORE

POWER SYSTEM

5V_ALW & 3.3V_ALW

REGULATOR

+1.8V_SUS/+0.9V_DDR_VTT

DDR2-SODIMM1

PG 19

DDR2-SODIMM2

PG 19

PG 32,33,34

PG 35

CAPBTN

CON.

PG 40

DESIGN ENGINEER :SCHEMATIC FILE NAME :

PG 53

PG 54

PG 56

BCM5906KMLG

QFN-68

PG 47

RJ45/Magnetic

PG 48

1

CLOCK

CK410M+LP

PG 21

D

C

B

A

Page 3

A

B

C

D

E

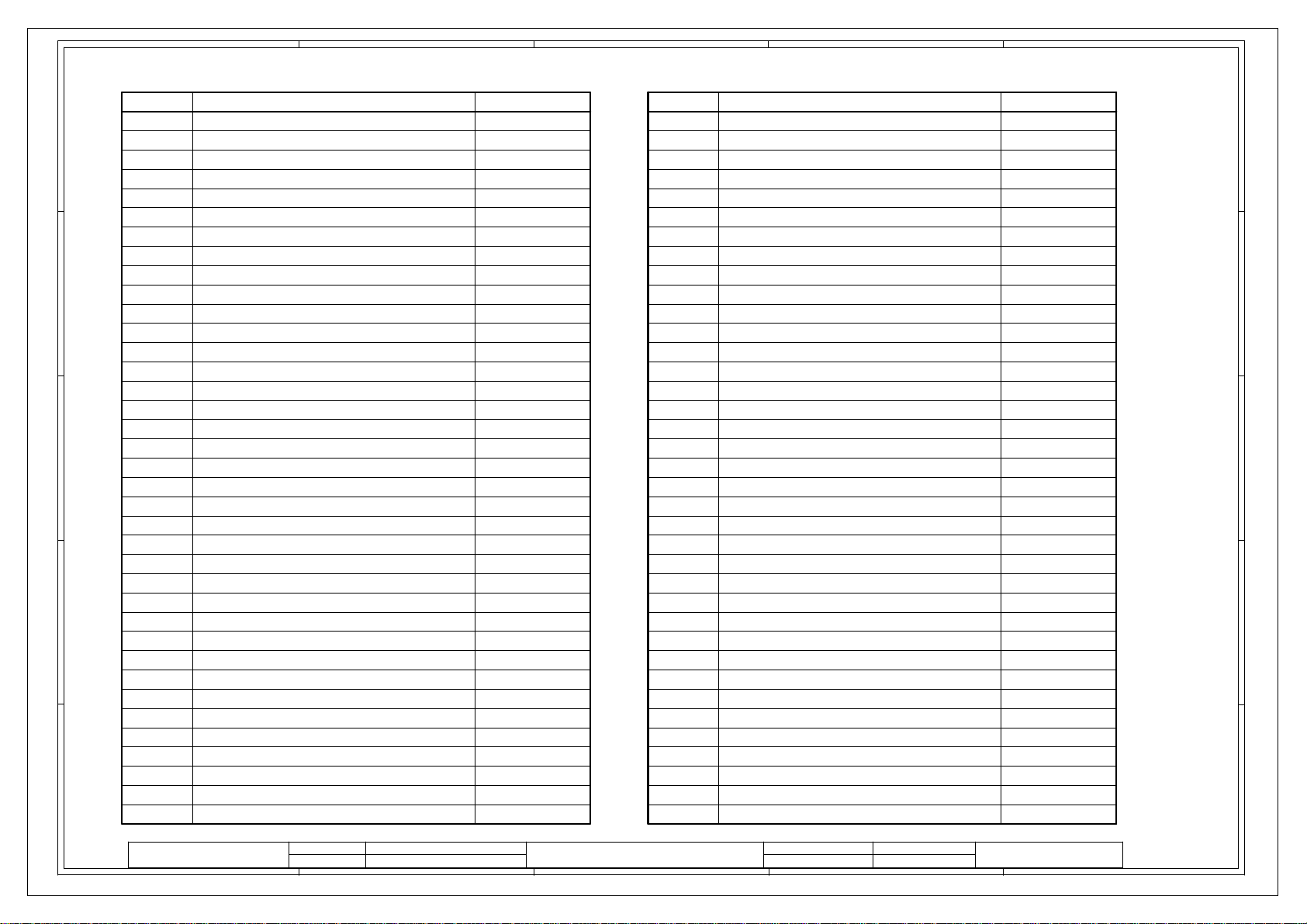

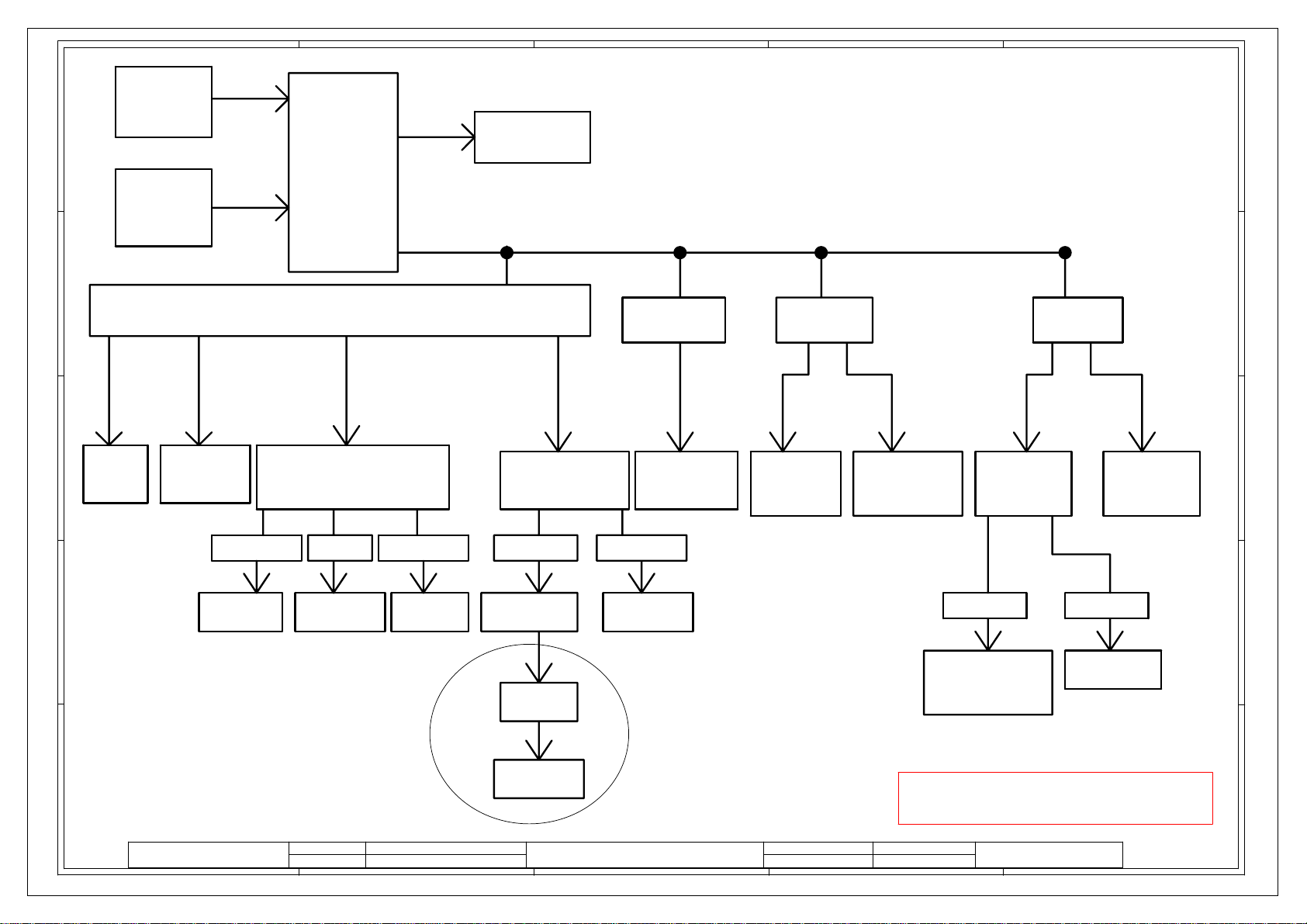

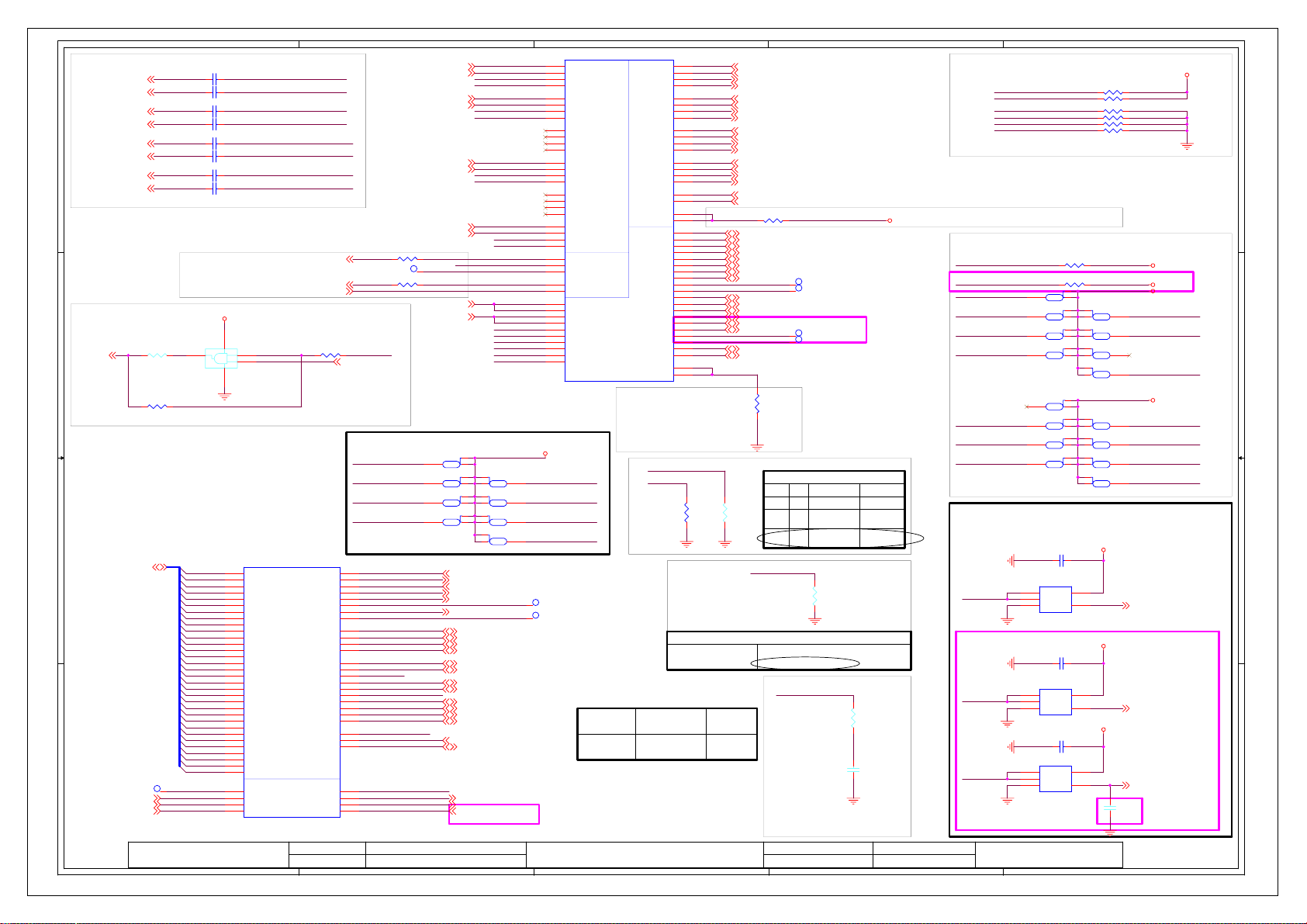

INDEX

Pg# Description DNI LIST

1

01

02

03

04

05

06

07-08

09-14

15-18

2

19-20

21

22-27

28

29

30

31

32-34

3

35

36

37

38

39

40

41

42

43

4

44-46

47

48

49

50

51

52

53-59

5

60

61 Change List 1

Cover Page

Schematic Block Diagram

INDEX

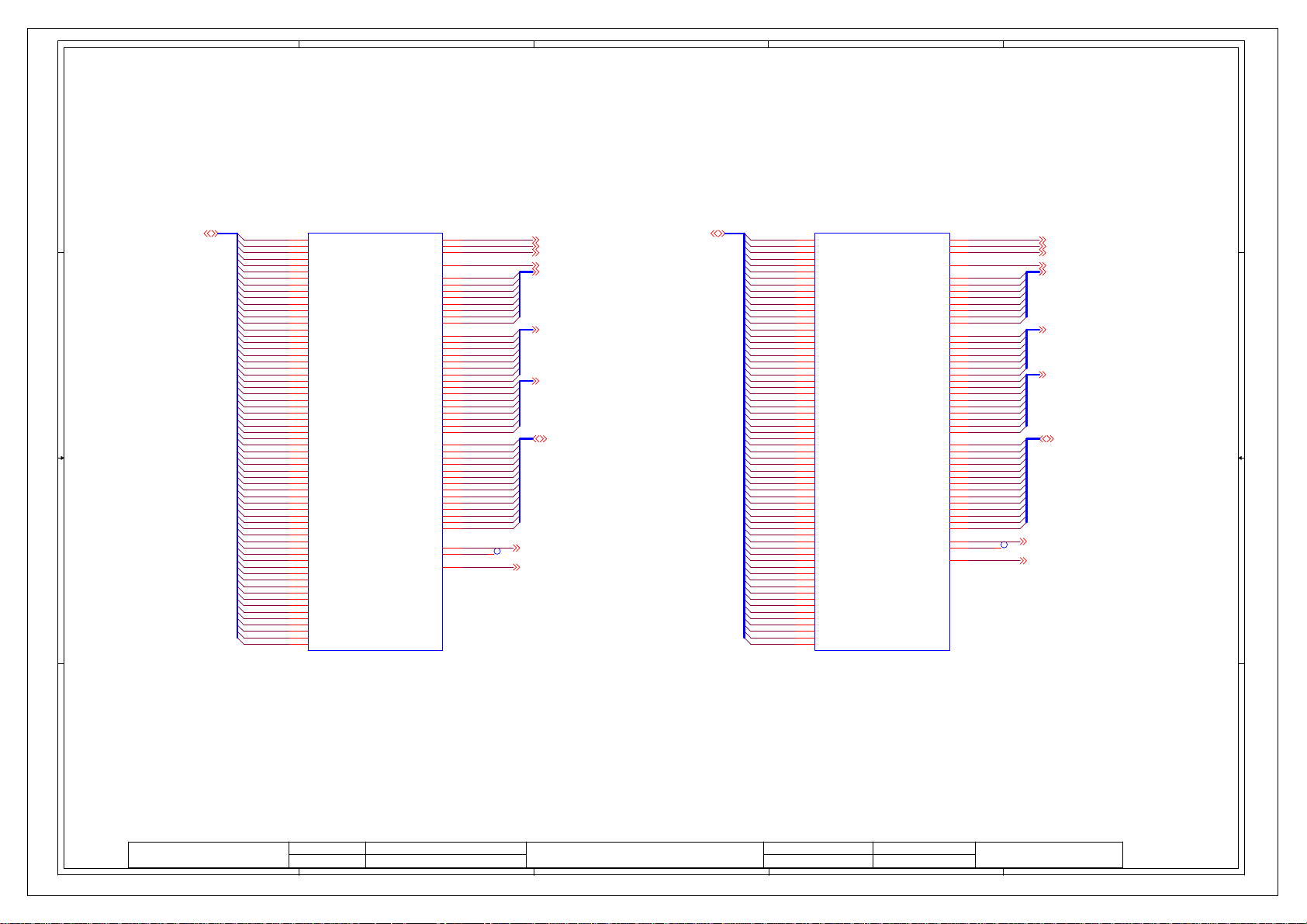

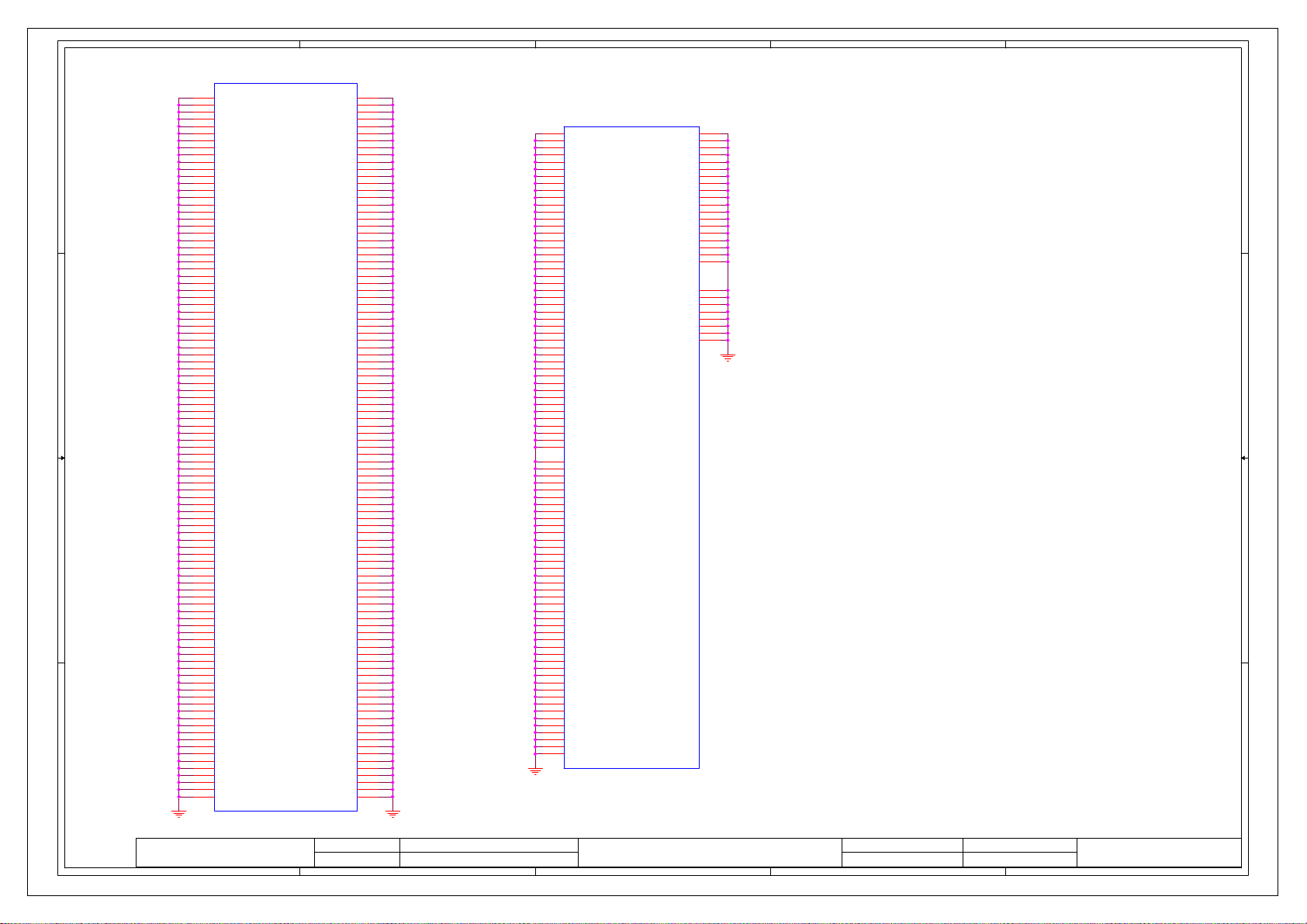

Bus connection

SMBUS BLOCK

Power Rail

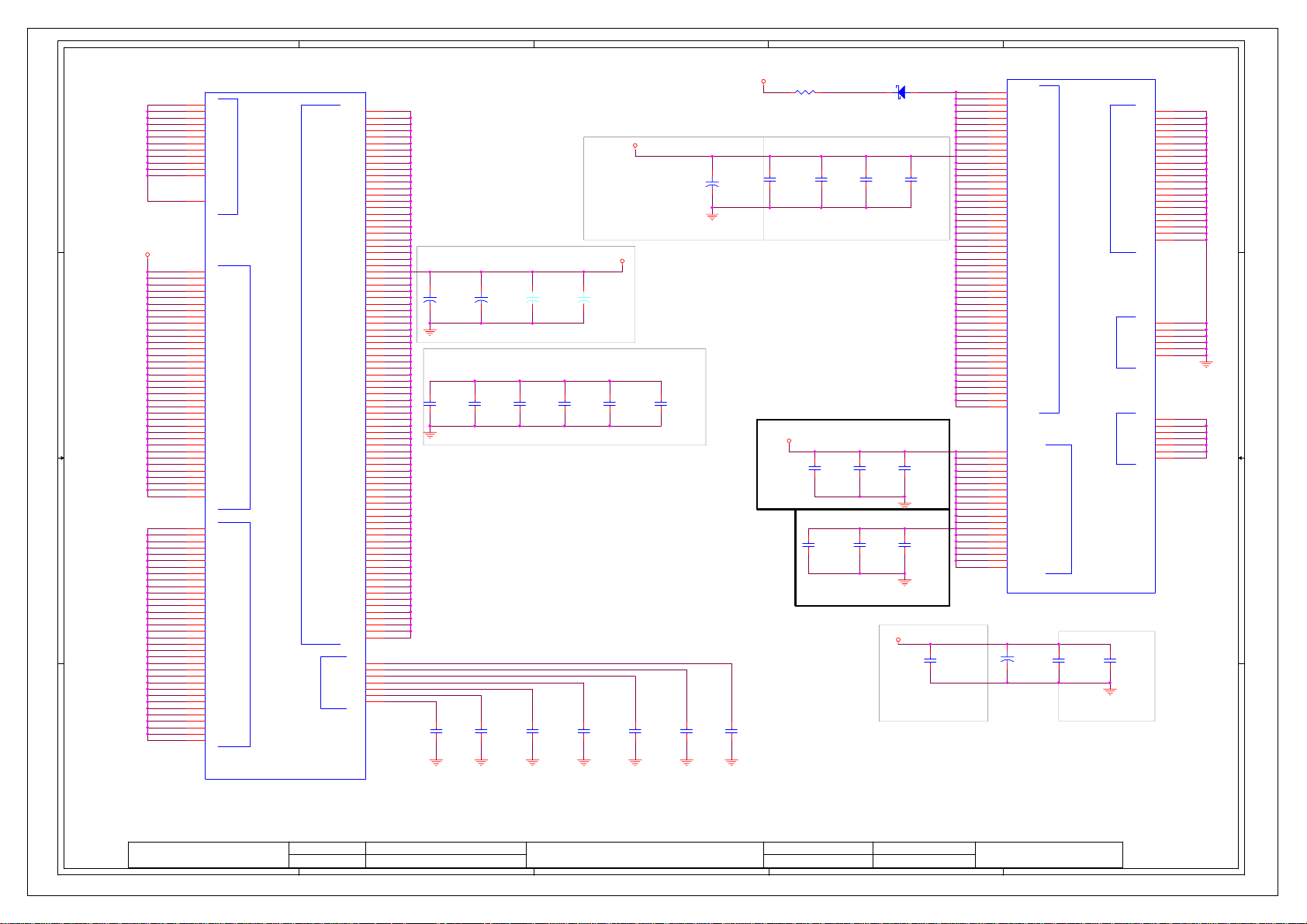

CPU ( Merom

、

Penryn )

Crestline

ICH8M

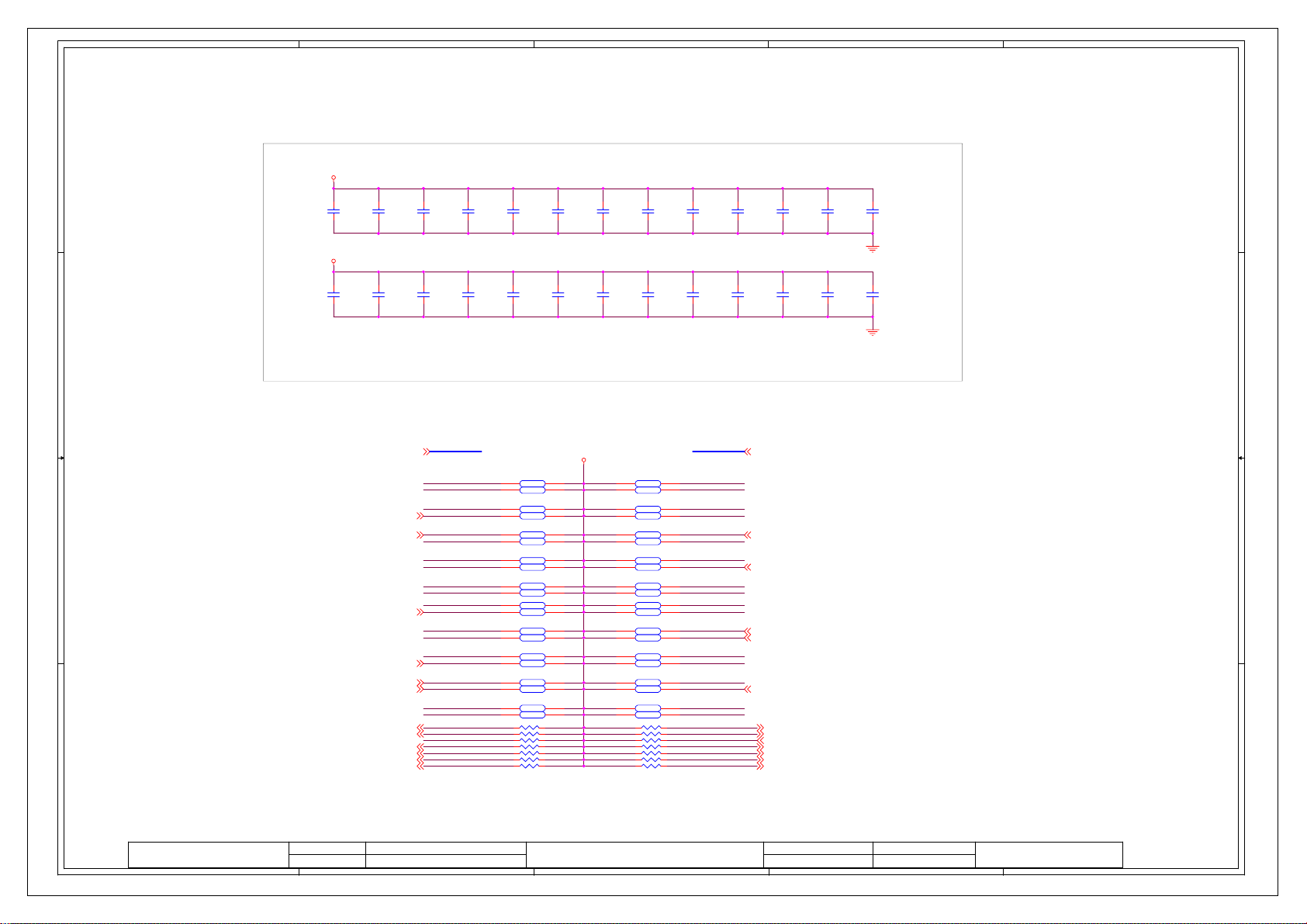

DDRII SO-DIMM( 533MHz 667MHz )

、

Clock Generator ( CK410M+LP )

BLANK PAGE

LVDS CON & Camera & DMIC

RGB CON

TV OUT CON

SATA(HDD & CD_ROM)

MEDIA CARD READER / 1394 ( R5C833 )

PCI-Express Card

MDC CONN

EC ( MEC5025 )

SIO ( ECE5011 )

USB PORT x 2

FLASH & RTC & CAPBTN CONN

TOUCH PAD & BT & CIR & LID

SWITCH & LED

HARDWARE MONITOR ( EMC4001 )

AUDIO CODEC & AMP

LOM BCM5906

Magnetics and RJ-45

Power Control Switch

BtoB CON

Power Sequence Logic

XDP

Power Circuit

SCREW PAD

Pg#

63

64

65

66

67

68

POWER CIRCUIT CHANGE LIST

Modem board cover page

RJ-11 CONN

Modem board change List

USB board cover page

USB PORT ( SINGLE * 2 )

Description

DNI LIST

1

2

3

4

5

Change List 262

PROJECT:

A

Lanai

REVISION

1.2

Monday, March 19, 2007

DATE:

SHEET OF

3 68

B

DESCRIPTION:

INDEX

C

RELEASE DATE :

D

DESIGN ENGINEER :SCHEMATIC FILE NAME :

E

Page 4

A

B

C

D

E

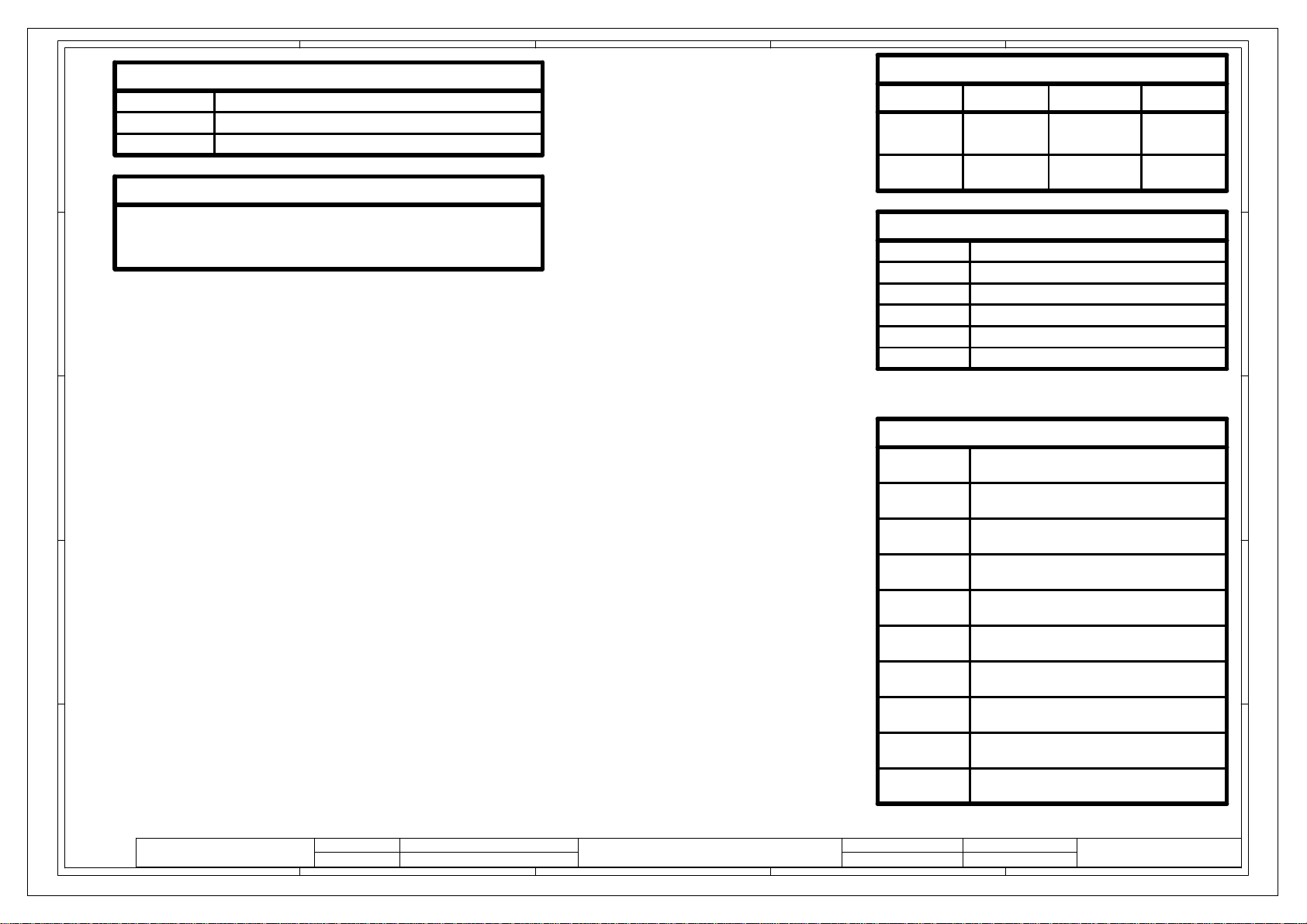

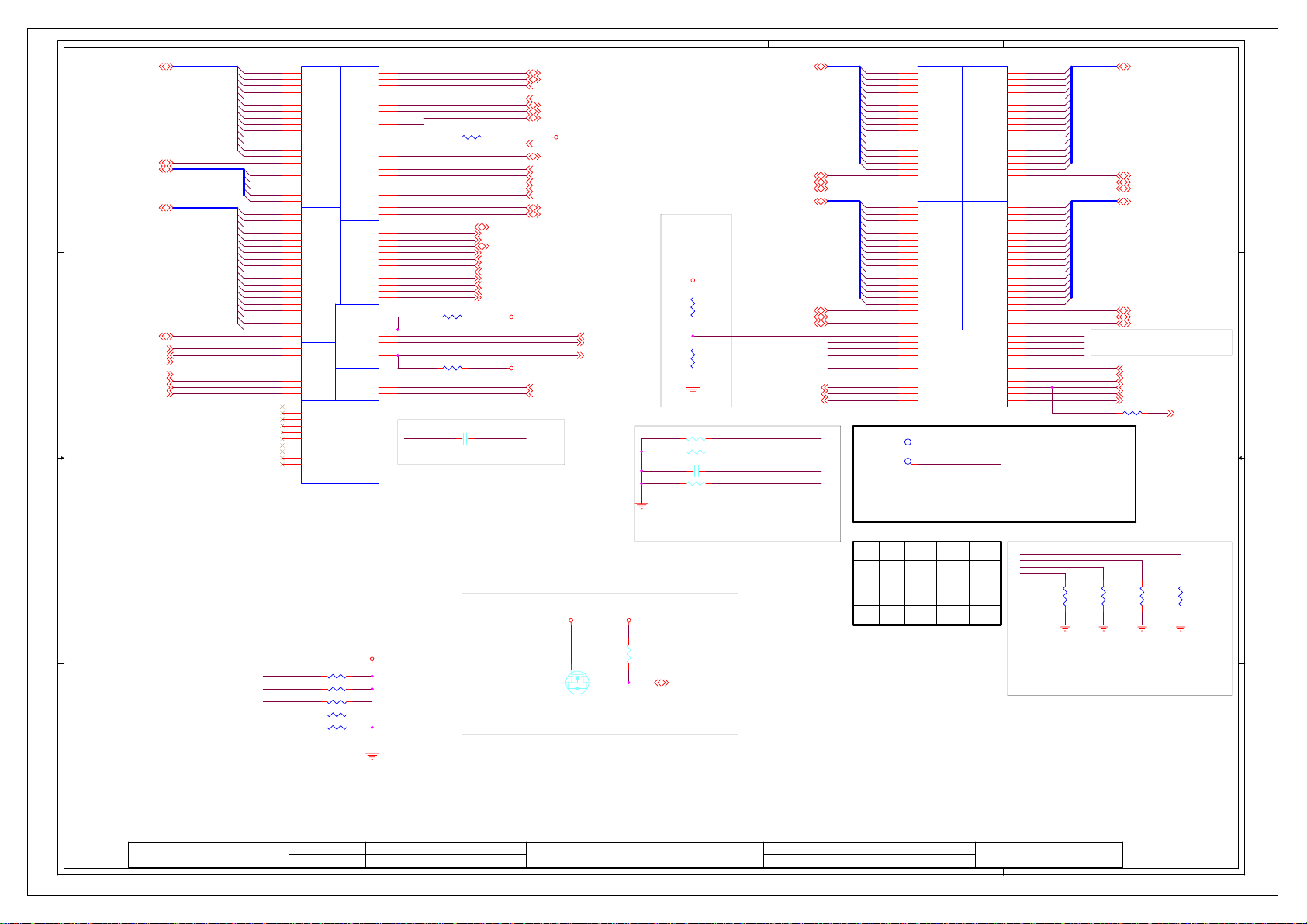

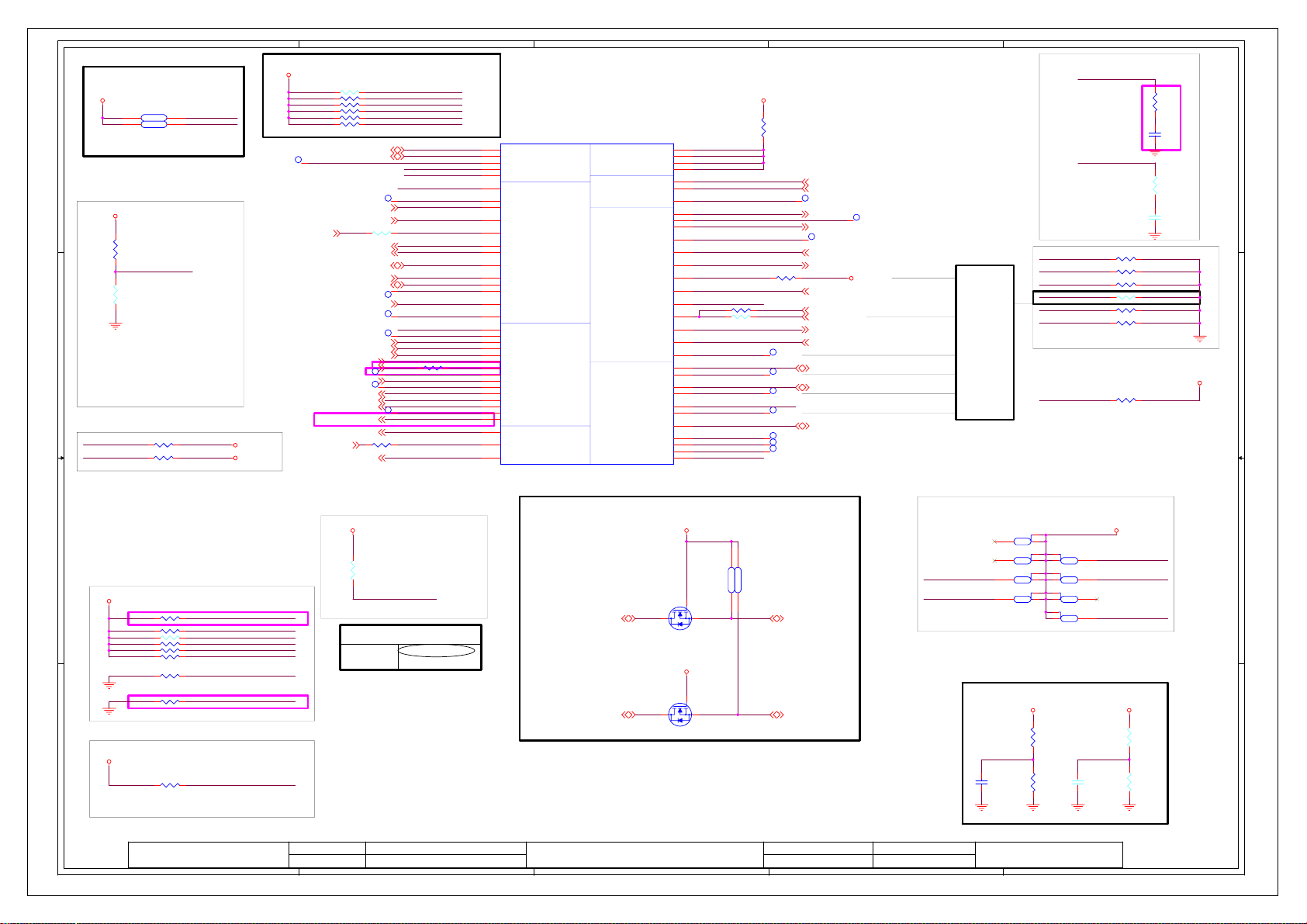

Footprint Definition

Footprint is 0402 if there is no descriptionResistor

1

Capacitor Footprint is 0402 if there is no description

Ferrite Bead

Footprint is 0603 if there is no description

PCI

DEVICE

R5C833

PCI TABLE

IDSEL REQ#/GNT# PIRQ

PCI_AD17

PCI_REQ1#

PCI_GNT1#

PCI_PIRQC#

PCI_PIRQD#

1

Layout Note

For all of ESD diode, they should be placed as close as

possible to connectors and the signals from connectors

should be routed to ESD diodes first. There is no branch

or via before diodes

Lane 2

2

Lane 3

Lane 4

PCI Express TABLE

WWAN / Mini CardLane 1

WLAN / Mini Card

2

ExpressCard

Lane 5

Lane 6

LAN BCM5906KMLG

USB TABLE

3

4

5

ICH8-0

(EHCI#1)

ICH8-1

(EHCI#1)

ICH8-2

(EHCI#1)

ICH8-3

(EHCI#1)

ICH8-4

(EHCI#1)

ICH8-5

(EHCI#1)

ICH8-6

(EHCI#2)

ICH8-7

(EHCI#2)

ICH8-8

(EHCI#2)

ICH8-9

(EHCI#2)

User1

(Single port , in USB BD)

User2

(Single port , in USB BD)

User3

(Dual port-bottom , in I/O BD)

User4

(Dual port-top , in I/O BD)

Camera

ExpressCard

BT Module

WWAN / Mini Card

3

4

5

PROJECT:

A

Lanai

REVISION

1.2

Monday, March 19, 2007

DATE:

SHEET OF

B

4 68

DESCRIPTION:

Bus Connection

C

RELEASE DATE :

D

Note : No USB for WLAN

<OrgName>

DESIGN ENGINEER :SCHEMATIC FILE NAME :

E

Page 5

5

4

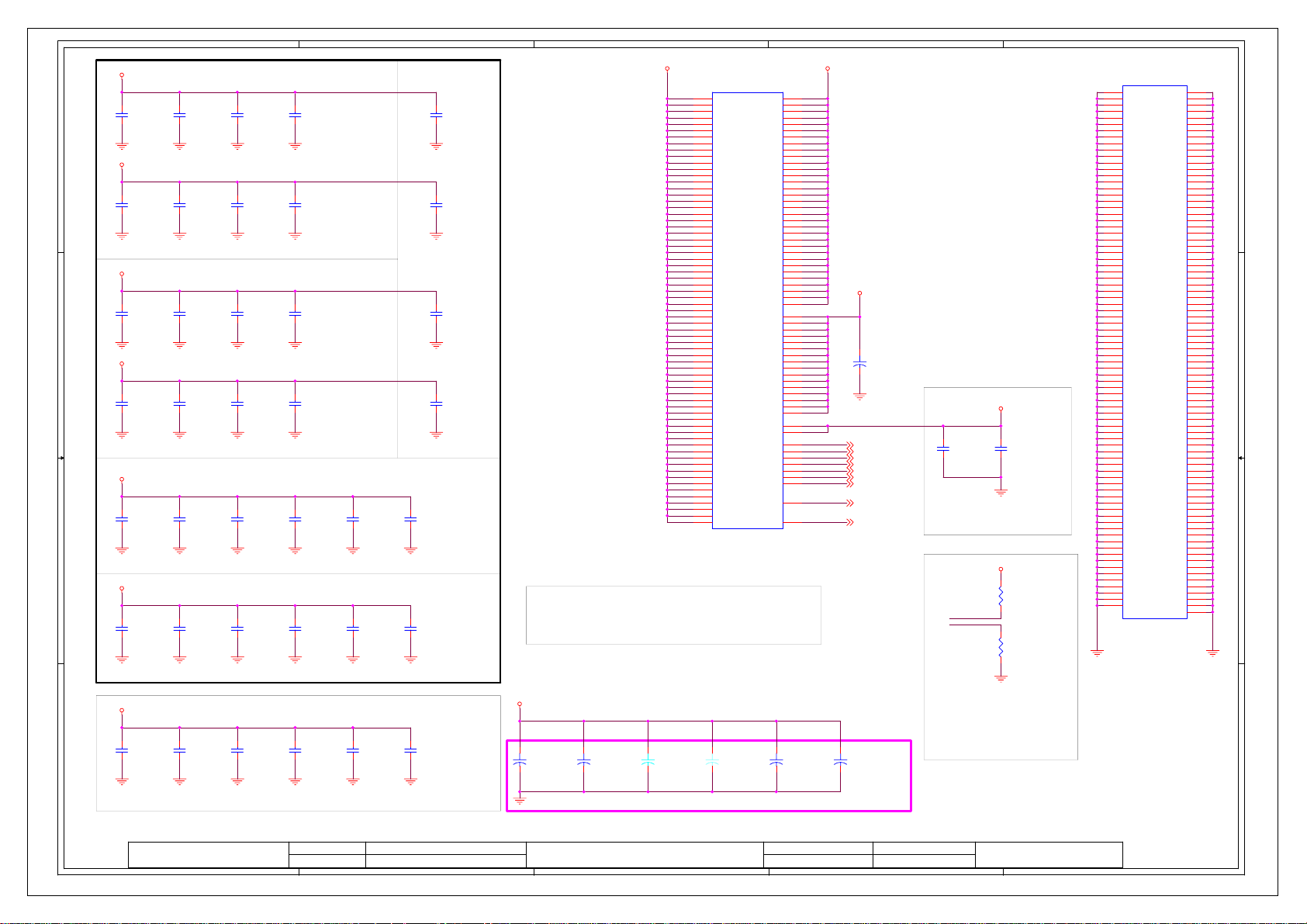

+3.3V_SUS

3

+3.3V_SUS

+3.3V_RUN

2

1

MEM_SCLK 197

10K 10K

2.2K2.2K

ICH8-M

D

AD19 ICH_SMBDATA

AC17 AMT_SMBCLK

AE19 AMT_SMBDAT

+5V_MEDIA

8.2K8.2K

2.2K 2.2K

+3.3V_RUN

7002

7002

MEM_SDATA 195

MEM_SCLK 197AJ26 ICH_SMBCLK

MEM_SDATA 195

7

Express Card WWAN

8

I/O Board

30

32

DIMM 0

DIMM 1

30

32

D

WLAN

6 DOCK_SMBCLK

5 DOCK_SMBDAT

+3.3V_ALW

CAPBTN Board

+3.3V_RUN

C

2.2K

13 CKG_SMBCLK

12 CKG_SMBDAT

+3.3V_ALW

4.7K

2.2K

+3.3V_RUN

7002

7002

4.7K

2.2K

100 THRM_SMBCLK

99 THRM_SMBDAT

SIO

B

MEC5025

+3.3V_ALW

2.2K

2.2K

+3.3V_ALW

112 PBAT_SMBCLK

111 PBAT_SMBDAT

+3.3V_ALW

8.2K

8.2K

+3.3V_ALW

8 LCD_SMBCLK

7 LCD_SMDDAT

+3.3V_RUN

2.2K2.2K

A

+3.3V_ALW

2.2K

100

100

47pF

CLK_SCLK 16

CLK_SDATA 17

12

11

10

9

SMB_CLK 3

SMB_DAT 4

34

35

47pF

ECE4001

CHARGER

Battery

CONN.

LVDS

Connector

C

CLK GEN.

B

A

LCD_DDCCLK 43

VGA

LCD_DDCDAT

+3.3V_RUN

44

PROJECT:

5

Lanai

REVISION

1.2

Monday, March 19, 2007

DATE:

SHEET OF

5 68

4

DESCRIPTION:

SMBUS BLOCK

3

RELEASE DATE :

<OrgName>

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Page 6

A

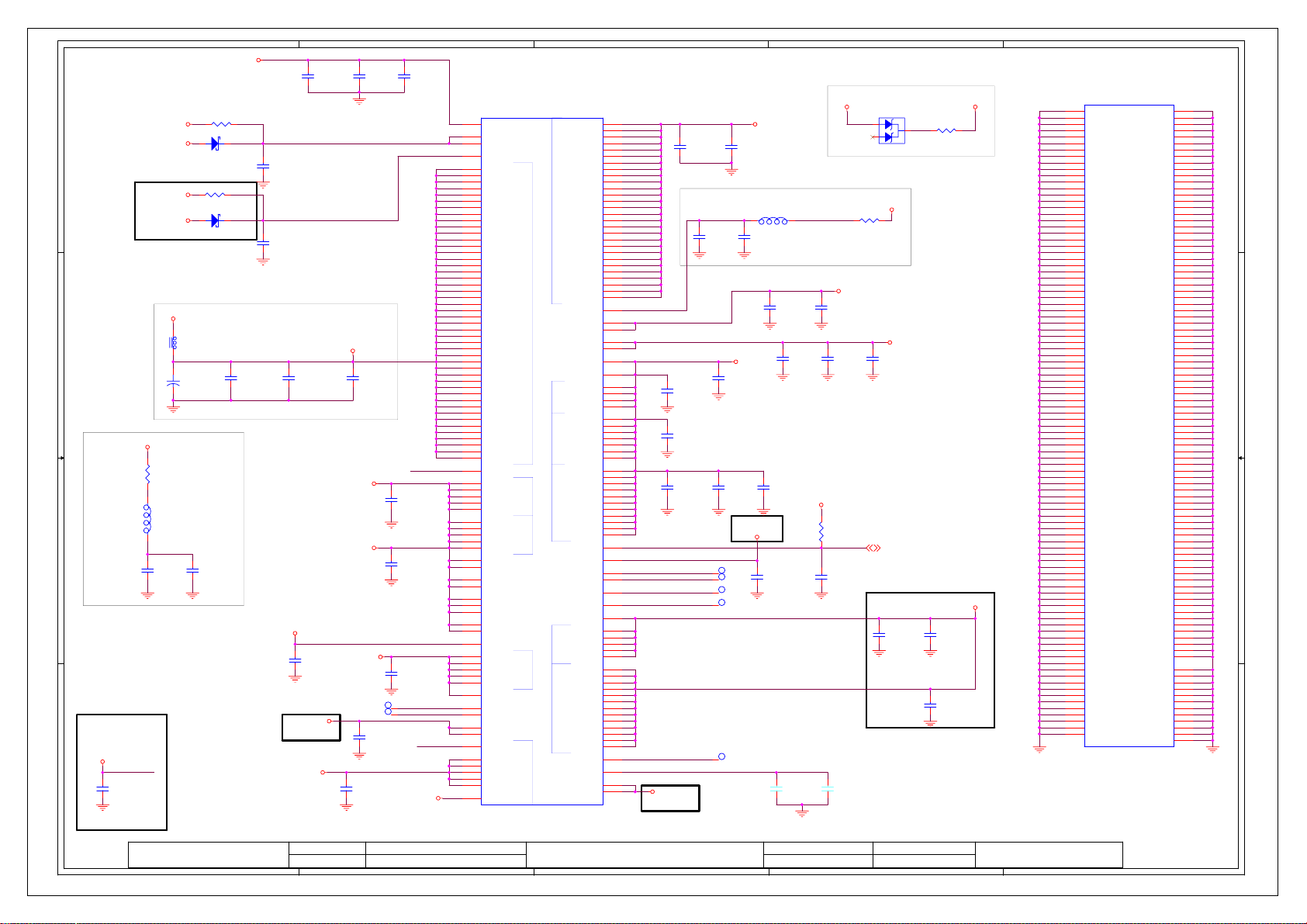

ADAPTER

B

C

D

E

1

+RTC_CELL

1

+PWR_SRC

BATTERY

2

TPS51120

ALWON

THERM_STP#

3

+5V_

ALW2

4

+3.3V_RTC

_LDO

SI4800BDY

RUN_ON

+5V_RUN +3.3V_RUN+15V_ALW

ALWON

THERM_STP#

+5V_ALW

BAT54S

SI4800BDY

+5V_SUS

ALWON

THERM_STP#

FDS6612A SI4800BDY

SUS_ON

3.3V_RUN_ON

3.3V_SUS_ON

ISL6260C

ISL6208

RUNPWROK

+VCC_CORE +1.5V_RUN+3.3V_ALW

+3.3V_SUS

SN0508073

IMVP_VR_ON

1.5V_RUN_ON

1.05_RUN_ON

+1.05V_VCCP

+1.8V_SUS

DDR_ON

0.9V_DDR_VTT_ON

TPS51100

SN0508073

DDR_ON

1.8V_RUN_ON

1.25V_RUN_ON

+1.25V_RUN

FDS6612A

2

3

4

+0.9V_DDR_VTT

EE

SIDE

5

PROJECT:

A

Lanai

REVISION

1.2

Monday, March 19, 2007

DATE:

SHEET OF

6 68

B

EMC4001

+2.5V_RUN

DESCRIPTION:

Power Rail

C

RELEASE DATE :

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

DESIGN ENGINEER :SCHEMATIC FILE NAME :

D

+1.8V_RUN

5

E

Page 7

5

H_A#[3..16]9

D

C

B

H_ADSTB#09

H_REQ#[0..4]9

H_A#[17..35]9

H_ADSTB#19

H_A20M#15

H_FERR#15

H_IGNNE#15

H_STPCLK#15

H_INTR15

H_NMI15

H_SMI#15

H_A#[3..16]

H_REQ#[0..4]

H_A#[17..35]

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

U25A

MOLEX/47387-4781

J4

A3#

L5

A4#

L4

A5#

K5

A6#

M3

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L2

A13#

P4

A14#

P1

A15#

R1

A16#

M1

ADSTB0#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L1

REQ4#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U1

A23#

R4

A24#

T5

A25#

T3

A26#

W2

A27#

W5

A28#

Y4

A29#

U2

A30#

V4

A31#

W3

A32#

AA4

A33#

AB2

A34#

AA3

A35#

V1

ADSTB1#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD01

N5

RSVD02

T2

RSVD03

V3

RSVD04

B2

RSVD05

C3

RSVD06

D2

RSVD07

D22

RSVD08

D3

RSVD09

F6

RSVD10

SOCKET478

ADDR GROUP

0

ADDR GROUP

1

THERMAL

PROCHOT#

ICH

THERMTRIP#

RESERVED

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

RESET#

RS0#

RS1#

RS2#

TRDY#

HIT#

HITM#

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALS

THERMDA

THERMDC

H CLK

BCLK0

BCLK1

TDI

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

CPU_PROCHOT#

D21

A24

B25

C7

A22

A21

4

H_IERR#

12

R159 56Ohm 5%

H_RESET#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_DBRESET#

12

R160 56Ohm 5%

H_THERMDA

H_THERMDC

12

R368 56Ohm 5%

C410 2200PF/50V MLCC/+/-10% /*

XDP_BPM#0 52

XDP_BPM#1 52

XDP_BPM#2 52

XDP_BPM#3 52

XDP_BPM#4 52

XDP_BPM#5 52

XDP_TCK 52

XDP_TDI 52

XDP_TDO 52

XDP_TMS 52

XDP_TRST# 52

XDP_DBRESET# 17,38,52

H_THERMDCH_THERMDA

12

Voltage Level Shift

H_ADS# 9

H_BNR# 9

H_BPRI# 9

H_DEFER# 9

H_DRDY# 9

H_DBSY# 9

H_BR0# 9

H_INIT# 15

H_LOCK# 9

H_RESET# 9,52

H_RS#0 9

H_RS#1 9

H_RS#2 9

H_TRDY# 9

H_HIT# 9

H_HITM# 9

+1.05V_VCCP

+1.05V_VCCP

CLK_CPU_BCLK 21

CLK_CPU_BCLK# 21

+1.05V_VCCP +3.3V_ALW

+1.05V_VCCP

H_THERMDA 43

H_THERMDC 43

H_THERMTRIP# 43

3

H_DSTBN#09

H_DSTBP#09

H_DINV#09

H_D#[0..63]9 H_D#[0..63] 9

Layout note:

Place voltage

divider within

0.5" of GTLREF

pin

+1.05V_VCCP

R163

1KOhm

1%

12

R164

2KOhm

1%

12

R395 1KOhm /*1%

R396 1KOhm /*1%

C409 0.1UF/10V /*MLCC/+/-10%

R399 0Ohm /*5%

12

12

12

12

Place C close to the

CPU_TEST4 pin. Make sure

CPU_TEST4 routing is

reference to GND and away

from other noisy signal.

2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

U25B

MOLEX/47387-4781

E22

F24

E26

G22

F23

G25

E25

E23

K24

G24

J24

J23

H22

F26

K22

H23

J26

H26

H25

N22

K25

P26

R23

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

T25

N25

L26

M26

N24

AD26

C23

D25

C24

AF26

AF1

A26

B22

B23

C21

SOCKET478

T27

1

T15

1

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

DSTBN0#

DSTBP0#

DINV0#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DSTBN1#

DSTBP1#

DINV1#

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

BSEL0

BSEL1

BSEL2

DATA GRP 0

DATA GRP 1

MISC

CPU_TEST3

CPU_TEST5

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

DATA GRP 2DATA GRP 3

D47#

DSTBN2#

DSTBP2#

DINV2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN3#

DSTBP3#

DINV3#

COMP0

COMP1

COMP2

COMP3

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

COMP0

COMP1

COMP2

COMP3

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

CPU_TEST1

CPU_TEST2

CPU_TEST4

CPU_TEST6

H_D#[0..63]

H_D#[0..63]

V_CPU_GTLREF

CPU_TEST1

CPU_TEST2

CPU_TEST3

CPU_TEST4

CPU_TEST5

CPU_TEST6

For the purpose of testability, route these signals

through a ground referenced Zo= 55 ohm trace that

ends in a via that is near a GND via and is

accessible through an oscilloscope connection.

H_D#[0..63]9

H_DSTBN#19

H_DSTBP#19

H_DINV#19

CPU_MCH_BSEL010,21

CPU_MCH_BSEL110,21

CPU_MCH_BSEL210,21

FSB BCLK BSEL2 BSEL1 BSEL0

533 133 0 0 1

667 166 0 1 1

800 200 0 1 0

12

1

H_D#[0..63]

H_D#[0..63]

R120

54.9Ohm

1%

H_D#[0..63] 9

H_DSTBN#2 9

H_DSTBP#2 9

H_DINV#2 9

H_DSTBN#3 9

H_DSTBP#3 9

H_DINV#3 9

Note:

H_DPRTSTP need to daisy chain

from ICH8 to IMVP6 to CPU.

H_DPRSTP# 10,15,53

H_DPSLP# 15

H_DPWR# 9

H_PWRGOOD 15

H_CPUSLP# 9

H_PSI# 53

12

R112 1KOhm 5%

R398

R118

54.9Ohm

27.4Ohm

1%

1%

12

12

H_PWRGD_XDP 52

R397

27.4Ohm

1%

12

D

C

B

+1.05V_VCCP

XDP_TMS

XDP_TDI

XDP_BPM#5

XDP_TCK

XDP_TRST#

A

PROJECT:

5

Lanai

REVISION

12

R122 54.9Ohm 1%

12

R119 54.9Ohm 1%

12

R121 54.9Ohm 1%

12

R114 54.9Ohm 1%

12

R117 649Ohm 1%

1.2

Monday, March 19, 2007

DATE:

SHEET OF

7 68

4

CPU_PROCHOT#

1

G

2

S

Q54

2N7002

Id=280mA/Pd=300mW

/*

DESCRIPTION:

3

D

R161

2.2KOhm

/*

12

EC_CPU_PROCHOT# 37

MEROM CPU (1)

3

RELEASE DATE :

<OrgName>

2

Comp0,2 connect with Zo=27.4ohm, Comp1,3

connect with Zo=55 ohm, make those traces

length shorter than 0.5". Trace should be

at least 25 mils away from any other

toggling signal.

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

A

Page 8

5

+VCC_CORE

D

+VCC_CORE

All use 10U 4V (+-20% , X6S , 0805)Pb-Free.

12

C403

12

C183

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

12

C385

12

C166

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

12

C132

12

C400

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

12

C140

12

C392

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

8 inside cavity, north side, secondary layer.

+VCC_CORE

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

12

C383

12

C391

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

12

C180

C

+VCC_CORE

12

C131

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

12

C157

12

C386

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

12

C159

12

C152

8 inside cavity, south side, secondary layer.

+VCC_CORE

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

12

C181

12

C133

12

C126

B

6 inside cavity, north side, primary layer.

+VCC_CORE

12

C179

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

12

C399

12

C396

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

12

C398

12

C172

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

12

C397

12

C134

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

6 inside cavity, south side, primary layer.

+1.05V_VCCP

12

C381

0.1UF/10V

A

MLCC/+/-10%

Layout out:

Place these inside socket cavity on North side secondary.

12

C380

0.1UF/10V

MLCC/+/-10%

12

C404

0.1UF/10V

MLCC/+/-10%

12

C193

0.1UF/10V

MLCC/+/-10%

12

C405

0.1UF/10V

MLCC/+/-10%

4

12

C145

10UF/4V

MLCC/+/-20%

pt_c0805

12

C158

10UF/4V

MLCC/+/-20%

pt_c0805

12

C124

0.1UF/10V

MLCC/+/-10%

12

C390

12

C176

12

C187

12

C402

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

10UF/4V

MLCC/+/-20%

pt_c0805

3

+VCC_CORE

100U/25V *4 Remove to POWER CIRCUIT .

+VCC_CORE

12

+

CE6

220UF/2V

pt_c7343d_h75

SANYO/2TPF220M7

12

+

CE5

220UF/2V

pt_c7343d_h75

SANYO/2TPF220M7

12

+

CE19

220UF/2V

pt_c7343d_h75

SANYO/2TPF220M7

/*

U25C

MOLEX/47387-4781

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

SOCKET478

12

VCC001

VCC002

VCC003

VCC004

VCC005

VCC006

VCC007

VCC008

VCC009

VCC010

VCC011

VCC012

VCC013

VCC014

VCC015

VCC016

VCC017

VCC018

VCC019

VCC020

VCC021

VCC022

VCC023

VCC024

VCC025

VCC026

VCC027

VCC028

VCC029

VCC030

VCC031

VCC032

VCC033

VCC034

VCC035

VCC036

VCC037

VCC038

VCC039

VCC040

VCC041

VCC042

VCC043

VCC044

VCC045

VCC046

VCC047

VCC048

VCC049

VCC050

VCC051

VCC052

VCC053

VCC054

VCC055

VCC056

VCC057

VCC058

VCC059

VCC060

VCC061

VCC062

VCC063

VCC064

VCCSENSE

VCC065

VCC066

VCC067

VSSSENSE

+

CE16

220UF/2V

pt_c7343d_h75

SANYO/2TPF220M7

/*

VCC068

VCC069

VCC070

VCC071

VCC072

VCC073

VCC074

VCC075

VCC076

VCC077

VCC078

VCC079

VCC080

VCC081

VCC082

VCC083

VCC084

VCC085

VCC086

VCC087

VCC088

VCC089

VCC090

VCC091

VCC092

VCC093

VCC094

VCC095

VCC096

VCC097

VCC098

VCC099

VCC100

VCCP01

VCCP02

VCCP03

VCCP04

VCCP05

VCCP06

VCCP07

VCCP08

VCCP09

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCA01

VCCA02

VID0

VID1

VID2

VID3

VID4

VID5

VID6

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

VCCSENSE

AF7

VSSSENSE

AE7

12

+

CE18

220UF/2V

pt_c7343d_h75

SANYO/2TPF220M7

+VCC_CORE

2

+1.05V_VCCP

12

CE20

+

220UF/4V

pt_c7343d_h79

TAN/Lf_T=2000hrs_105C/+/-20%

VID0 53

VID1 53

VID2 53

VID3 53

VID4 53

VID5 53

VID6 53

VCCSENSE 53

VSSSENSE 53

No.43

12

+

CE7

220UF/2V

pt_c7343d_h75

SANYO/2TPF220M7

+1.5V_RUN

12

C414

Layout Note:

Place 0.01U/25V near PIN

B26.

VCCSENSE

VSSSENSE

Route VCCSENSE and VSSSENSE

traces at 27.4ohms with 50

mils spacing and length

matched to within 25 mil.

Place PU and PD within

1 inch of CPU.

0.01UF/25V

MLCC/+/-10%

pt_c0603

12

C418

10UF/4V

pt_c0805

MLCC/+/-20%

+VCC_CORE

R128

100Ohm

1%

12

R127

100Ohm

1%

12

1

U25D

MOLEX/47387-4781

A4

VSS001

A8

VSS002

A11

VSS003

A14

VSS004

A16

VSS005

A19

VSS006

A23

VSS007

AF2

VSS008

B6

VSS009

B8

VSS010

B11

VSS011

B13

VSS012

B16

VSS013

B19

VSS014

B21

VSS015

B24

VSS016

C5

VSS017

C8

VSS018

C11

VSS019

C14

VSS020

C16

VSS021

C19

VSS022

C2

VSS023

C22

VSS024

C25

VSS025

D1

VSS026

D4

VSS027

D8

VSS028

D11

VSS029

D13

VSS030

D16

VSS031

D19

VSS032

D23

VSS033

D26

VSS034

E3

VSS035

E6

VSS036

E8

VSS037

E11

VSS038

E14

VSS039

E16

VSS040

E19

VSS041

E21

VSS042

E24

VSS043

F5

VSS044

F8

VSS045

F11

VSS046

F13

VSS047

F16

VSS048

F19

VSS049

F2

VSS050

F22

VSS051

F25

VSS052

G4

VSS053

G1

VSS054

G23

VSS055

G26

VSS056

H3

VSS057

H6

VSS058

H21

VSS059

H24

VSS060

J2

VSS061

J5

VSS062

J22

VSS063

J25

VSS064

K1

VSS065

K4

VSS066

K23

VSS067

K26

VSS068

L3

VSS069

L6

VSS070

L21

VSS071

L24

VSS072

M2

VSS073

M5

VSS074

M22

VSS075

M25

VSS076

N1

VSS077

N4

VSS078

N23

VSS079

N26

VSS080

P3

VSS081

SOCKET478

VSS082

VSS083

VSS084

VSS085

VSS086

VSS087

VSS088

VSS089

VSS090

VSS091

VSS092

VSS093

VSS094

VSS095

VSS096

VSS097

VSS098

VSS099

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

D

C

B

A

PROJECT:

5

Lanai

REVISION

1.2

Monday, March 19, 2007

DATE:

SHEET OF

8 68

4

DESCRIPTION:

Merom CPU (2)

3

RELEASE DATE :

<OrgName>

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Page 9

5

4

3

2

1

H_D#[0..63]7

D

+1.05V_VCCP

12

R367

221Ohm

1%

H_SWING

12

12

C371

R366

0.1UF/10V

100Ohm

MLCC/+/-10%

1%

C

+1.05V_VCCP

12

12

R129

R130

54.9Ohm

54.9Ohm

1%

1%

H_SCOMP

H_SCOMP#

H_RCOMP

12

R132

24.9Ohm

1%

Layout Note:

H_RCOMP trace should be

10-mil wide with 20-mil

spacing

B

+1.05V_VCCP

12

12

R364

1KOhm

1%

R365

2KOhm

1%

H_D#[0..63]

12

C367

0.1UF/10V

MLCC/+/-10%

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_RESET#7,52

H_CPUSLP#7

H_REF

U10A

E2

H_D#_0

G2

H_D#_1

G7

H_D#_2

M6

H_D#_3

H7

H_D#_4

H3

H_D#_5

G4

H_D#_6

F3

H_D#_7

N8

H_D#_8

H2

H_D#_9

M10

H_D#_10

N12

H_D#_11

N9

H_D#_12

H5

H_D#_13

P13

H_D#_14

K9

H_D#_15

M2

H_D#_16

W10

H_D#_17

Y8

H_D#_18

V4

H_D#_19

M3

H_D#_20

J1

H_D#_21

N5

H_D#_22

N3

H_D#_23

W6

H_D#_24

W9

H_D#_25

N2

H_D#_26

Y7

H_D#_27

Y9

H_D#_28

P4

H_D#_29

W3

H_D#_30

N1

H_D#_31

AD12

H_D#_32

AE3

H_D#_33

AD9

H_D#_34

AC9

H_D#_35

AC7

H_D#_36

AC14

H_D#_37

AD11

H_D#_38

AC11

H_D#_39

AB2

H_D#_40

AD7

H_D#_41

AB1

H_D#_42

Y3

H_D#_43

AC6

H_D#_44

AE2

H_D#_45

AC5

H_D#_46

AG3

H_D#_47

AJ9

H_D#_48

AH8

H_D#_49

AJ14

H_D#_50

AE9

H_D#_51

AE11

H_D#_52

AH12

H_D#_53

AJ5

H_D#_54

AH5

H_D#_55

AJ6

H_D#_56

AE7

H_D#_57

AJ7

H_D#_58

AJ2

H_D#_59

AE5

H_D#_60

AJ3

H_D#_61

AH2

H_D#_62

AH13

H_D#_63

B3

H_SWING

C2

H_RCOMP

W1

H_SCOMP

W2

H_SCOMP#

B6

H_CPURST#

E5

H_CPUSLP#

B9

H_AVREF

A9

H_DVREF

CRESTLINE_965GM

HOST

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

J13

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_A#[3..35]

H_A#[3..35] 7

H_ADS# 7

H_ADSTB#0 7

H_ADSTB#1 7

H_BNR# 7

H_BPRI# 7

H_BR0# 7

H_DEFER# 7

H_DBSY# 7

CLK_MCH_BCLK 21

CLK_MCH_BCLK# 21

H_DPWR# 7

H_DRDY# 7

H_HIT# 7

H_HITM# 7

H_LOCK# 7

H_TRDY# 7

H_DINV#0 7

H_DINV#1 7

H_DINV#2 7

H_DINV#3 7

H_DSTBN#0 7

H_DSTBN#1 7

H_DSTBN#2 7

H_DSTBN#3 7

H_DSTBP#0 7

H_DSTBP#1 7

H_DSTBP#2 7

H_DSTBP#3 7

H_REQ#0 7

H_REQ#1 7

H_REQ#2 7

H_REQ#3 7

H_REQ#4 7

H_RS#0 7

H_RS#1 7

H_RS#2 7

D

C

B

Layout Note:

Place the 0.1uF

decoupling capacitor

within 100 mils from

GMCH pins.

A

PROJECT:

5

Lanai

REVISION

1.2

Monday, March 19, 2007

DATE:

SHEET OF

9 68

4

DESCRIPTION:

Crestline(HOST)

3

RELEASE DATE :

<OrgName>

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

A

Page 10

SM_RCOMP_VOH

12

D

SM_RCOMP_VOL

12

+3.3V_RUN

R335 10KOhm 5%

R337 10KOhm 5%

+1.05V_VCCP

C

R354

B

A

5

+1.8V_SUS

12

R351

1KOhm

0.1%

12

C351

0.01UF/25V

MLCC/+/-10%

12

C108

0.01UF/25V

MLCC/+/-10%

12

12

No.10

12

56Ohm 5%

Layout Note:

Location of all MCH_CFG strap

resistors needs to be close to

minmize stub.

CPU_MCH_BSEL07,21

CPU_MCH_BSEL17,21

CPU_MCH_BSEL27,21

+3.3V_RUN

12

C353

2.2UF/10V

MLCC/+/-10%

c0603,pt_c0603

C109

2.2UF/10V

MLCC/+/-10%

c0603,pt_c0603

R348

3.01KOhm

1%

12

R352

1KOhm

0.1%

PM_EXTTS#0

PM_EXTTS#1

DDR_A_MA1419,20

DDR_B_MA1419,20

THERMTRIP_MCH#

R356 4.02KOhm /*1%

R355 4.02KOhm /*1%

R359 4.02KOhm /*1%

R333 4.02KOhm /*1%

R336 4.02KOhm /*1%

PM_BMBUSY#17

H_DPRSTP#7,15,53

PM_EXTTS#019

PM_EXTTS#119

ICH_PWRGD17,51

THERMTRIP_MCH#43

DPRSLPVR17,53

SB_NB_PCIE_RST#16

PROJECT:

5

T111

T14

12

T110

T93

T113

12

T105

T107

T109

T100

T112

T98

12

T99

T91

12

12

PLTRST#16,35,37

Lanai

DDR_A_MA14

DDR_B_MA14

1

1

1

1

1

1

1

1

1

1

1

1

1

PM_EXTTS#0

PM_EXTTS#1

PLTRST#_R

THERMTRIP_MCH#

12

R332 0Ohm 5%

T2

T4

T8

T7

T10

T16

T17

T22

T21

T20

T19

T3

T5

T6

T9

T18

12

R357 0Ohm 5% /*

12

R360 0Ohm 5%

4

U10B

P36

RSVD1

P37

RSVD2

R35

RSVD3

N35

RSVD4

AR12

RSVD5

AR13

RSVD6

AM12

RSVD7

AN13

RSVD8

J12

RSVD9

AR37

RSVD10

AM36

RSVD11

AL36

RSVD12

AM37

RSVD13

D20

RSVD14

H10

RSVD20

B51

RSVD21

BJ20

RSVD22

BK22

RSVD23

BF19

RSVD24

BH20

RSVD25

BK18

RSVD26

BJ18

RSVD27

BF23

RSVD28

BG23

RSVD29

BC23

RSVD30

BD24

RSVD31

BJ29

RSVD32

BE24

RSVD33

BH39

RSVD34

AW20

RSVD35

BK20

RSVD36

C48

RSVD37

D47

RSVD38

B44

RSVD39

C44

RSVD40

A35

RSVD41

B37

RSVD42

B36

RSVD43

B34

RSVD44

C34

RSVD45

P27

CFG_0

N27

CFG_1

N24

CFG_2

CFG3

C21

CFG_3

CFG4

C23

CFG_4

CFG5

F23

CFG_5

CFG6

N23

CFG_6

CFG7

G23

CFG_7

CFG8

J20

CFG_8

CFG9

C20

CFG_9

CFG10

R24

CFG_10

CFG11

L23

CFG_11

CFG12

J23

CFG_12

CFG13

E23

CFG_13

CFG14

E20

CFG_14

CFG15

K23

CFG_15

CFG16

M20

CFG_16

CFG17

M24

CFG_17

CFG18

L32

CFG_18

CFG19

N33

CFG_19

CFG20

L35

CFG_20

G41

PM_BM_BUSY#

L39

PM_DPRSTP#

L36

PM_EXT_TS#_0

J36

PM_EXT_TS#_1

AW49

PWROK

AV20

RSTIN#

N20

THERMTRIP#

G36

DPRSLPVR

1

BJ51

NC_1

1

BK51

NC_2

1

BK50

NC_3

1

BL50

NC_4

1

BL49

NC_5

1

BL3

NC_6

1

BL2

NC_7

1

BK1

NC_8

1

BJ1

NC_9

1

E1

NC_10

1

A5

NC_11

1

C51

NC_12

1

B50

NC_13

1

A50

NC_14

1

A49

NC_15

1

BK2 R32

NC_16 TEST_2

CRESTLINE_965GM

R358 100Ohm 5%

12

REVISION

1.2

DATE:

SHEET OF

SM_RCOMP_VOH

SM_RCOMP_VOL

DDR MUXINGCLKDMI

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CFGRSVD

PM

GRAPHICS VID

ME

NC

SDVO_CTRL_CLK

SDVO_CTRL_DATA

MISC

PLTRST#_R

Monday, March 19, 2007

10 68

4

SM_CK_0

SM_CK_1

SM_CK_3

SM_CK_4

SM_CK#_0

SM_CK#_1

SM_CK#_3

SM_CK#_4

SM_CKE_0

SM_CKE_1

SM_CKE_3

SM_CKE_4

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP

SM_RCOMP#

SM_VREF_0

SM_VREF_1

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

CLK_REQ#

ICH_SYNC#

TEST_1

AV29

BB23

BA25

AV23

AW30

BA23

AW25

AW23

BE29

AY32

BD39

BG37

BG20

BK16

BG16

BE13

BH18

BJ15

BJ14

BE16

SMRCOMPP

BL15

SMRCOMPN

BK14

SM_RCOMP_VOH

BK31

SM_RCOMP_VOL

BL31

AR49

AW4

B42

C42

H48

H47

K44

K45

AN47

AJ38

AN42

AN46

AM47

AJ39

AN41

AN45

AJ46

AJ41

AM40

AM44

AJ47

AJ42

AM39

AM43

1

E35

1

A39

1

C38

1

B39

1

E36

AM49

AK50

AT43

AN49

AM50

H35

K36

G39

G40

A37

M_CLK_DDR0 19

M_CLK_DDR1 19

M_CLK_DDR2 19

M_CLK_DDR3 19

M_CLK_DDR#0 19

M_CLK_DDR#1 19

M_CLK_DDR#2 19

M_CLK_DDR#3 19

DDR_CKE0_DIMMA 19,20

DDR_CKE1_DIMMA 19,20

DDR_CKE2_DIMMB 19,20

DDR_CKE3_DIMMB 19,20

DDR_CS0_DIMMA# 19,20

DDR_CS1_DIMMA# 19,20

DDR_CS2_DIMMB# 19,20

DDR_CS3_DIMMB# 19,20

M_ODT0 19,20

M_ODT1 19,20

M_ODT2 19,20

M_ODT3 19,20

V_DDR_MCH_REF

MCH_DREFCLK 21

MCH_DREFCLK# 21

DREF_SSCLK 21

DREF_SSCLK# 21

CLK_MCH_3GPLL 21

CLK_MCH_3GPLL# 21

DMI_MRX_ITX_N0 16

DMI_MRX_ITX_N1 16

DMI_MRX_ITX_N2 16

DMI_MRX_ITX_N3 16

DMI_MRX_ITX_P0 16

DMI_MRX_ITX_P1 16

DMI_MRX_ITX_P2 16

DMI_MRX_ITX_P3 16

DMI_MTX_IRX_N0 16

DMI_MTX_IRX_N1 16

DMI_MTX_IRX_N2 16

DMI_MTX_IRX_N3 16

DMI_MTX_IRX_P0 16

DMI_MTX_IRX_P1 16

DMI_MTX_IRX_P2 16

DMI_MTX_IRX_P3 16

Non-iAMT

T90

T13

T12

T11

T89

CL_CLK0 17

CL_DATA0 17

ICH_CL_PWROK 17,37

ICH_CL_RST0# 17

MCH_CLVREF

CLK_3GPLLREQ# 21

MCH_ICH_SYNC# 17

R339

20KOhm

5%

12

12

DESCRIPTION:

3

L_IBG

R325

2.4KOhm

1%

12

UMA

+1.8V_SUS

12

R110

20Ohm

1%

SMRCOMPP

SMRCOMPN

12

R363

20Ohm

1%

G_CLK_DDC250

G_DAT_DDC250

VGAHSYNC50

+1.25V_RUN

MCH_CLVREF

12

C86

0.1UF/10V

MLCC/+/-10%

12

12

R82

1KOhm

1%

R84

392Ohm

1%

pt_r0603

VGAVSYNC50

+3.3V_RUN

R327 10KOhm 5% /*

R324 10KOhm 5% /*

R329 2.2KOhm 5%

R334 2.2KOhm 5%

CFG5

CFG9

CFG16

CFG19

R326

0Ohm

5%

CFG20

SDVO_CRTL_DATA

Crestline(VGA,DMI)

3

PANEL_BKEN38

LCTLA_CLK52

LCTLB_DATA52

LCD_DDCCLK28

LCD_DDCDAT28

LCD_ACLK-28

LCD_ACLK+28

LCD_BCLK-28

LCD_BCLK+28

TV_CVBS50

TV_Y50

TV_C50

R345

150Ohm

1%

12

VGA_BLU50

VGA_GRN50

VGA_RED50

R341 30Ohm 1%pt_r0603

12

R330 1.3KOhm 0.5%pt_r0603

12

R338 30Ohm 1%pt_r0603

12

R0933,R0937

Intel 30.1

LCTLA_CLK, LCTLB_DATA

connect to XDP CONN.

R327,R324 Stuff.

12

12

12

12

ohm 1%

DMI X2 Select

PCI Express

Graphic Lane

FSB Dynamic

ODT

DMI Lane

Reversal

SDVO/PCIE

Concurrent

Operation

SDVO Present.

RELEASE DATE :

2

U10C

BIA_PWM28

LCTLA_CLK

LCTLB_DATA

LCD_DDCCLK

LCD_DDCDATA

ENVDD28

L_IBG

T86

1

LCD_A0-28

LCD_A1-28

LCD_A2-28

LCD_A0+28

LCD_A1+28

LCD_A2+28

LCD_B0-28

LCD_B1-28

LCD_B2-28

LCD_B0+28

LCD_B1+28

LCD_B2+28

R350

R344

150Ohm

150Ohm

1%

1%

12

12

VGA_BLU

VGA_GRN

VGA_RED

J40

L_BKLT_CTRL

H39

L_BKLT_EN

E39

L_CTRL_CLK

E40

L_CTRL_DATA

C37

L_DDC_CLK

D35

L_DDC_DATA

K40

L_VDD_EN

L41

LVDS_IBG

L43

LVDS_VBG

N41

LVDS_VREFH

N40

LVDS_VREFL

D46

LVDSA_CLK#

C45

LVDSA_CLK

D44

LVDSB_CLK#

E42

LVDSB_CLK

G51

LVDSA_DATA#_0

E51

LVDSA_DATA#_1

F49

LVDSA_DATA#_2

G50

LVDSA_DATA_0

E50

LVDSA_DATA_1

F48

LVDSA_DATA_2

G44

LVDSB_DATA#_0

B47

LVDSB_DATA#_1

B45

LVDSB_DATA#_2

E44

LVDSB_DATA_0

A47

LVDSB_DATA_1

A45

LVDSB_DATA_2

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

M35

TV_DCONSEL_0

P33

TV_DCONSEL_1

H32

CRT_BLUE

G32

CRT_BLUE#

K29

CRT_GREEN

J29

CRT_GREEN#

F29

CRT_RED

E29

CRT_RED#

K33

CRT_DDC_CLK

G35

CRT_DDC_DATA

F33

CRT_HSYNC

C32

CRT_TVO_IREF

E33

CRT_VSYNC

CRESTLINE_965GM

UMA

LCTLA_CLK

LCTLB_DATA

LCD_DDCCLK

LCD_DDCDATA

Low=DMIx2

High=DMIx4 (Default)

Low=Reveise Lane

High=Normal operation

Low=Dynamic ODT Disable

High=Dynamic ODT Enable (default)

Low=Normal (default)

High=Lane Reversed

Low=Only SDVO or PCIEx1 is

operational (defaults)

High=SDVO and PCIEx1 are operating

sumultaneously via PEG port

Low=No SDVO Device Present

(defaults)

High=SDVO Device Prsent

R536

0Ohm

5%

12

<OrgName>

2

No.2

R537

0Ohm

5%

12

DESIGN ENGINEER :SCHEMATIC FILE NAME :

LVDS

TV VGA

PCI-EXPRESS GRAPHICS

R343

R340

150Ohm

150Ohm

1%

1%

12

12

N43

PEG_COMPI

M43

PEG_COMPO

J51

PEG_RX#_0

L51

PEG_RX#_1

N47

PEG_RX#_2

T45

PEG_RX#_3

T50

PEG_RX#_4

U40

PEG_RX#_5

Y44

PEG_RX#_6

Y40

PEG_RX#_7

AB51

PEG_RX#_8

W49

PEG_RX#_9

AD44

PEG_RX#_10

AD40

PEG_RX#_11

AG46

PEG_RX#_12

AH49

PEG_RX#_13

AG45

PEG_RX#_14

AG41

PEG_RX#_15

J50

PEG_RX_0

L50

PEG_RX_1

M47

PEG_RX_2

U44

PEG_RX_3

T49

PEG_RX_4

T41

PEG_RX_5

W45

PEG_RX_6

W41

PEG_RX_7

AB50

PEG_RX_8

Y48

PEG_RX_9

AC45

PEG_RX_10

AC41

PEG_RX_11

AH47

PEG_RX_12

AG49

PEG_RX_13

AH45

PEG_RX_14

AG42

PEG_RX_15

N45

PEG_TX#_0

U39

PEG_TX#_1

U47

PEG_TX#_2

N51

PEG_TX#_3

R50

PEG_TX#_4

T42

PEG_TX#_5

Y43

PEG_TX#_6

W46

PEG_TX#_7

W38

PEG_TX#_8

AD39

PEG_TX#_9

AC46

PEG_TX#_10

AC49

PEG_TX#_11

AC42

PEG_TX#_12

AH39

PEG_TX#_13

AE49

PEG_TX#_14

AH44

PEG_TX#_15

M45

PEG_TX_0

T38

PEG_TX_1

T46

PEG_TX_2

N50

PEG_TX_3

R51

PEG_TX_4

U43

PEG_TX_5

W42

PEG_TX_6

Y47

PEG_TX_7

Y39

PEG_TX_8

AC38

PEG_TX_9

AD47

PEG_TX_10

AC50

PEG_TX_11

AD43

PEG_TX_12

AG39

PEG_TX_13

AE50

PEG_TX_14

AH43

PEG_TX_15

VGA_BLU

VGA_GRN

VGA_RED

R342

150Ohm

Layout Note:

1%

Place 150 ohm

termination resistors

12

close to GMCH

1

VCC3G_PCIE_R

1

24.9Ohm 1%

12

UMA

R90

+VCC_PEG

D

C

B

A

Page 11

5

4

3

2

1

D

DDR_A_D[0..63]19

C

B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38 DDR_A_MA6

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

U10D

AR43

AW44

BA45

AY46

AR41

AR45

AT42

AW47

BB45

BF48

BG47

BJ45

BB47

BG50

BH49

BE45

AW43

BE44

BG42

BE40

BF44

BH45

BG40

BF40

AR40

AW40

AT39

AW36

AW41

AY41

AV38

AT38

AV13

AT13

AW11

AV11

AU15

AT11

BA13

BA11

BE10

BD10

BD8

AY9

BG10

AW9

BD7

BB9

BB5

AY7

AT5

AT7

AY6

BB7

AR5

AR8

AR9

AN3

AM8

AN10

AT9

AN9

AM9

AN11

CRESTLINE_965GM

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

DDR_A_BS0

BB19

SA_BS_0

SA_BS_1

SA_BS_2

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

DDR SYSTEM MEMORY A

SA_RCVEN#

SA_WE#

BK19

BF29

BL17

AT45

BD44

BD42

AW38

AW13

BG8

AY5

AN6

AT46

BE48

BB43

BC37

BB16

BH6

BB2

AP3

AT47

BD47

BC41

BA37

BA16

BH7

BC1

AP2

BJ19

BD20

BK27

BH28

BL24

BK28

BJ27

BJ25

BL28

BA28

BC19

BE28

BG30

BJ16

BE18

AY20

BA19

DDR_A_BS1

DDR_A_BS2

DDR_A_CAS#

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_RAS#

1

DDR_A_WE#

DDR_A_RAS# 19,20

T114

DDR_A_WE# 19,20

DDR_A_BS0 19,20

DDR_A_BS1 19,20

DDR_A_BS2 19,20

DDR_A_CAS# 19,20

DDR_A_DM[0..7] 19

DDR_A_DQS[0..7] 19

DDR_A_DQS#[0..7] 19

DDR_A_MA[0..13] 19,20

DDR_B_D[0..63]19

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15 DDR_B_DQS0

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20 DDR_B_DQS5

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

U10E

AP49

AR51

AW50

AW51

AN51

AN50

AV50

AV49

BA50

BB50

BA49

BE50

BA51

AY49

BF50

BF49

BJ50

BJ44

BJ43

BL43

BK47

BK49

BK43

BK42

BJ41

BL41

BJ37

BJ36

BK41

BJ40

BL35

BK37

BK13

BE11

BK11

BC11

BC13

BE12

BC12

BG12

BJ10

BL9

BK5

BL5

BK9

BK10

BJ8

BJ6

BF4

BH5

BG1

BC2

BK3

BE4

BD3

BJ2

BA3

BB3

AR1

AT3

AY2

AY3

AU2

AT2

CRESTLINE_965GM

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

DDR_B_BS0

AY17

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVEN#

DDR SYSTEM MEMORY B

SB_WE#

BG18

BG36

BE17

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AT50

BD50

BK46

BK39

BJ12

BL7

BE2

AV2

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

AV16

AY18

BC17

DDR_B_BS1

DDR_B_BS2

DDR_B_CAS#

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_RAS#

1

DDR_B_WE#

DDR_B_RAS# 19,20

T108

DDR_B_WE# 19,20

DDR_B_BS0 19,20

DDR_B_BS1 19,20

DDR_B_BS2 19,20

DDR_B_CAS# 19,20

DDR_B_DM[0..7] 19

DDR_B_DQS[0..7] 19

DDR_B_DQS#[0..7] 19

DDR_B_MA[0..13] 19,20

D

C

B

A

PROJECT:

5

Lanai

REVISION

1.2

Monday, March 19, 2007

DATE:

SHEET OF

11 68

4

DESCRIPTION:

Crestline(DDR2)

3

RELEASE DATE :

<OrgName>

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

A

Page 12

5

4

3

2

1

+3.3V_RUN

12

C328

1UF/10V

MLCC/+/-10%

pt_c0603

R143 10Ohm 5%

12

C366

22UF/4V

MLCC/+/-20%

pt_c0805_h53

Layout Note:

Inside GMCH

cavity

+1.05V_VCCP

Non-iAMT

+VCC_GMCH

D

+1.8V_SUS

C

+VCC_AXG

B

A

U10G

AT35

AT34

AH28

AC32

AC31

AK32

AJ31

AJ28

AH32

AH31

AH29

AF32

R30

AU32

AU33

AU35

AV33

AW33

AW35

AY35

BA32

BA33

BA35

BB33

BC32

BC33

BC35

BD32

BD35

BE32

BE33

BE35

BF33

BF34

BG32

BG33

BG35

BH32

BH34

BH35

BJ32

BJ33

BJ34

BK32

BK33

BK34

BK35

BL33

AU30

R20

T14

W13

W14

Y12

AA20

AA23

AA26

AA28

AB21

AB24

AB29

AC20

AC21

AC23

AC24

AC26

AC28

AC29

AD20

AD23

AD24

AD28

AF21

AF26

AA31

AH20

AH21

AH23

AH24

AH26

AD31

AJ20

AN14

CRESTLINE_965GM

VCC_1

VCC_2

VCC_3

VCC_5

VCC_4

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_SM_1

VCC_SM_2

VCC_SM_3

VCC_SM_4

VCC_SM_5

VCC_SM_6

VCC_SM_7

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_SM_11

VCC_SM_12

VCC_SM_13

VCC_SM_14

VCC_SM_15

VCC_SM_16

VCC_SM_17

VCC_SM_18

VCC_SM_19

VCC_SM_20

VCC_SM_21

VCC_SM_22

VCC_SM_23

VCC_SM_24

VCC_SM_25

VCC_SM_26

VCC_SM_27

VCC_SM_28

VCC_SM_29

VCC_SM_30

VCC_SM_31

VCC_SM_32

VCC_SM_33

VCC_SM_34

VCC_SM_35

VCC_SM_36

VCC_AXG_1

VCC_AXG_2

VCC_AXG_3

VCC_AXG_4

VCC_AXG_5

VCC_AXG_6

VCC_AXG_7

VCC_AXG_8

VCC_AXG_9

VCC_AXG_10

VCC_AXG_11

VCC_AXG_12

VCC_AXG_13

VCC_AXG_14

VCC_AXG_15

VCC_AXG_16

VCC_AXG_17

VCC_AXG_18

VCC_AXG_19

VCC_AXG_20

VCC_AXG_21

VCC_AXG_22

VCC_AXG_23

VCC_AXG_24

VCC_AXG_25

VCC_AXG_26

VCC_AXG_27

VCC_AXG_28

VCC_AXG_29

VCC_AXG_30

VCC_AXG_31

VCC_AXG_32

VCC_AXG_33

VCC_AXG_34

VCC CORE

POWER

VCC SMVCC GFX

VCC_AXG_NCTF_1

VCC_AXG_NCTF_2

VCC_AXG_NCTF_3

VCC_AXG_NCTF_4

VCC_AXG_NCTF_5

VCC_AXG_NCTF_6

VCC_AXG_NCTF_7

VCC_AXG_NCTF_8

VCC_AXG_NCTF_9

VCC_AXG_NCTF_10

VCC_AXG_NCTF_11

VCC_AXG_NCTF_12

VCC_AXG_NCTF_13

VCC_AXG_NCTF_14

VCC_AXG_NCTF_15

VCC_AXG_NCTF_16

VCC_AXG_NCTF_17

VCC_AXG_NCTF_18

VCC_AXG_NCTF_19

VCC_AXG_NCTF_20

VCC_AXG_NCTF_21

VCC_AXG_NCTF_22

VCC_AXG_NCTF_23

VCC_AXG_NCTF_24

VCC_AXG_NCTF_25

VCC_AXG_NCTF_26

VCC_AXG_NCTF_27

VCC_AXG_NCTF_28

VCC_AXG_NCTF_29

VCC_AXG_NCTF_30

VCC_AXG_NCTF_31

VCC_AXG_NCTF_32

VCC_AXG_NCTF_33

VCC_AXG_NCTF_34

VCC_AXG_NCTF_35

VCC_AXG_NCTF_36

VCC_AXG_NCTF_37

VCC_AXG_NCTF_38

VCC_AXG_NCTF_39

VCC_AXG_NCTF_40

VCC_AXG_NCTF_41

VCC_AXG_NCTF_42

VCC_AXG_NCTF_43

VCC_AXG_NCTF_44

VCC_AXG_NCTF_45

VCC_AXG_NCTF_46

VCC_AXG_NCTF_47

VCC_AXG_NCTF_48

VCC_AXG_NCTF_49

VCC_AXG_NCTF_50

VCC_AXG_NCTF_51

VCC_AXG_NCTF_52

VCC_AXG_NCTF_53

VCC_AXG_NCTF_54

VCC GFX NCTF

VCC_AXG_NCTF_55

VCC_AXG_NCTF_56

VCC_AXG_NCTF_57

VCC_AXG_NCTF_58

VCC_AXG_NCTF_59

VCC_AXG_NCTF_60

VCC_AXG_NCTF_61

VCC_AXG_NCTF_62

VCC_AXG_NCTF_63

VCC_AXG_NCTF_64

VCC_AXG_NCTF_65

VCC_AXG_NCTF_66

VCC_AXG_NCTF_67

VCC_AXG_NCTF_68

VCC_AXG_NCTF_69

VCC_AXG_NCTF_70

VCC_AXG_NCTF_71

VCC_AXG_NCTF_72

VCC_AXG_NCTF_73

VCC_AXG_NCTF_74

VCC_AXG_NCTF_75

VCC_AXG_NCTF_76

VCC_AXG_NCTF_77

VCC_AXG_NCTF_78

VCC_AXG_NCTF_79

VCC_AXG_NCTF_80

VCC_AXG_NCTF_81

VCC_AXG_NCTF_82

VCC_AXG_NCTF_83

VCC_SM_LF1

VCC_SM_LF2

VCC_SM_LF3

VCC_SM_LF4

VCC_SM_LF5

VCC_SM_LF6

VCC_SM_LF7

VCC SM LF

T17

T18

T19

T21

T22

T23

T25

U15

U16

U17

U19

U20

U21

U23

U26

V16

V17

V19

V20

V21

V23

V24

Y15

Y16

Y17

Y19

Y20

Y21

Y23

Y24

Y26

Y28

Y29

AA16

AA17

AB16

AB19

AC16

AC17

AC19

AD15

AD16

AD17

AF16

AF19

AH15

AH16

AH17

AH19

AJ16

AJ17

AJ19

AK16

AK19

AL16

AL17

AL19

AL20

AL21

AL23

AM15

AM16

AM19

AM20

AM21

AM23

AP15

AP16

AP17

AP19

AP20

AP21

AP23

AP24

AR20

AR21

AR23

AR24

AR26

V26

V28

V29

Y31

AW45

BC39

BE39

BD17

BD4

AW8

AT6

Layout Note:

370mils form edge.

12

+

CE4

220UF/2.5V

pt_c7343d_h75

+/-20%

Layout Note:

Inside GMCH cavity for VCC_AXG.

C332

0.1UF/10V

12

C370

0.1UF/10V

MLCC/+/-10%

12

MLCC/+/-10%

VCCSM_LF1

VCCSM_LF2

VCCSM_LF3

VCCSM_LF4

VCCSM_LF5

VCCSM_LF6

VCCSM_LF7

12

MLCC/+/-10%

12

+

CE9

220UF/2.5V

pt_c7343d_h75

+/-20%

C334

0.1UF/10V

12

C369

0.1UF/10V

MLCC/+/-10%

+VCC_AXG

12

+

CE10

220UF/2.5V

+/-20%

pt_c7343d_h75

/*

12

C368

0.47UF/10V

MLCC/+/-10%

pt_c0603

12

C376

0.22UF/10V

MLCC/+/-10%

pt_c0603

Layout Note:

370 mils form edge.

+1.05V_VCCP

12

+

CE8

220UF/2.5V

+/-20%

pt_c7343d_h75

/*

12

12

C340

1UF/10V

MLCC/+/-10%

MLCC/+/-20%

pt_c0603

12

C360

0.22UF/10V

MLCC/+/-10%

pt_c0603

+1.05V_VCCP

+VCC_AXG

C342

10UF/6.3V

pt_c0805_h53

12

12

C333

0.47UF/10V

MLCC/+/-10%

pt_c0603

C326

22UF/4V

MLCC/+/-20%

pt_c0805_h53

12

12

+

TAN/Lf_T=2000hrs_105C/+/-20%

C344

1UF/10V

MLCC/+/-10%

pt_c0603

CE15

220UF/4V

pt_c7343d_h79

+VCC_GMCH_L

12

12

C343

0.22UF/10V

MLCC/+/-10%

pt_c0603

+VCC_AXM

12

C348

0.1UF/10V

MLCC/+/-10%

12

C321

22UF/4V

MLCC/+/-20%

pt_c0805_h53

Layout Note:

Place close to GMCH edge.

D11

21

RB751V_40

+VCC_GMCH

12

12

C341

C346

0.22UF/10V

MLCC/+/-10%

Layout Note:

Inside GMCH cavity

12

C349

0.1UF/10V

MLCC/+/-10%

12

C350

0.22UF/10V

MLCC/+/-10%

pt_c0603

0.1UF/10V

MLCC/+/-10%

pt_c0603

12

C347

0.1UF/10V

MLCC/+/-10%

12

C337

0.22UF/10V

MLCC/+/-10%

pt_c0603

+1.8V_SUS

Layout Note:

Place C1117 where LVDS

andDDR2 taps

12

C95

0.1UF/10V

MLCC/+/-10%

U10F

AB33

VCC_NCTF_1

AB36

VCC_NCTF_2

AB37

VCC_NCTF_3

AC33

VCC_NCTF_4

AC35

VCC_NCTF_5

AC36

VCC_NCTF_6

AD35

VCC_NCTF_7

AD36

VCC_NCTF_8

AF33

VCC_NCTF_9

AF36

VCC_NCTF_10

AH33

VCC_NCTF_11

AH35

VCC_NCTF_12

AH36

VCC_NCTF_13

AH37

VCC_NCTF_14

AJ33

VCC_NCTF_15

AJ35

VCC_NCTF_16

AK33

VCC_NCTF_17

AK35

VCC_NCTF_18

AK36

VCC_NCTF_19

AK37

VCC_NCTF_20

AD33

VCC_NCTF_21

AJ36

VCC_NCTF_22

AM35

VCC_NCTF_23

AL33

VCC_NCTF_24

AL35

VCC_NCTF_25

AA33

VCC_NCTF_26

AA35

VCC_NCTF_27

AA36

VCC_NCTF_28

AP35

VCC_NCTF_29

AP36

VCC_NCTF_30

AR35

VCC_NCTF_31

AR36

VCC_NCTF_32

Y32

VCC_NCTF_33

Y33

VCC_NCTF_34

Y35

VCC_NCTF_35

Y36

VCC_NCTF_36

Y37 A3

VCC_NCTF_37 VSS_SCB1

T30

VCC_NCTF_38

T34

VCC_NCTF_39

T35

VCC_NCTF_40

U29

VCC_NCTF_41

U31

VCC_NCTF_42

U32

VCC_NCTF_43

U33

VCC_NCTF_44

U35

VCC_NCTF_45

U36

VCC_NCTF_46

V32

VCC_NCTF_47

V33

VCC_NCTF_48

V36

VCC_NCTF_49

V37

VCC_NCTF_50

AL24

VCC_AXM_NCTF_1

AL26

VCC_AXM_NCTF_2

AL28

VCC_AXM_NCTF_3

AM26

VCC_AXM_NCTF_4

AM28

VCC_AXM_NCTF_5

AM29

VCC_AXM_NCTF_6

AM31

VCC_AXM_NCTF_7

AM32

VCC_AXM_NCTF_8

AM33

VCC_AXM_NCTF_9

AP29

VCC_AXM_NCTF_10

AP31

VCC_AXM_NCTF_11

AP32

VCC_AXM_NCTF_12

AP33

VCC_AXM_NCTF_13

AL29

VCC_AXM_NCTF_14

AL31

VCC_AXM_NCTF_15

AL32

VCC_AXM_NCTF_16

AR31

VCC_AXM_NCTF_17

AR32

VCC_AXM_NCTF_18

AR33

VCC_AXM_NCTF_19

CRESTLINE_965GM

12

+

CE11

330UF/6.3V

pt_c7343d_h110

+/-20%

POWER

12

C92

22UF/4V

MLCC/+/-20%

pt_c0805_h53

Layout Note:

Place on the edge

VCC NCTF

VCC AXM NCTF

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

VSS_NCTF_11

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

VSS_NCTF_15

VSS NCTF

VSS_NCTF_16

VSS_NCTF_17

VSS_NCTF_18

VSS_NCTF_19

VSS_NCTF_20

VSS_NCTF_21

VSS_SCB2

VSS_SCB3

VSS_SCB4

VSS_SCB5

VSS_SCB6

VSS SCBVCC AXM

VCC_AXM_1

VCC_AXM_2

VCC_AXM_3

VCC_AXM_4

VCC_AXM_5

VCC_AXM_6

VCC_AXM_7

12

C91

22UF/4V

MLCC/+/-20%

pt_c0805_h53

T27

T37

U24

U28

V31

V35

AA19

AB17

AB35

AD19

AD37

AF17

AF35

AK17

AM17

AM24

AP26

AP28

AR15

AR19

AR28

B2

C1

BL1

BL51

A51

AT33

AT31

AK29

AK24

AK23

AJ26

AJ23

D

C

+VCC_AXM

B

A

PROJECT:

5

Lanai

REVISION

1.2

Monday, March 19, 2007

DATE:

SHEET OF

12 68

4

DESCRIPTION:

Crestline(VCC,NCTF)

3

RELEASE DATE :

<OrgName>

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Page 13

+3.3V_RUN

D

Non-iAMT

+1.25V_RUN

C

+1.25V_RUN

FB_220ohm+-25_100MHz

_2A_0.1ohm DC

B

22nF & 0.1uF for

VCC_TVDACA:C_R should

be placed with in 250

mils from Crestline.

+VCC_TVBG_R

A

+1.5V_RUN

TV DAC Voltage Follower Circuit -700mV.

FB_180ohm+-25_100mHz_1500mA_0.09oh m DC

5

L11 180Ohm

+VCCA_CRTDAC

21

BLM18PG181SN1

45mA MAX.

FB_120ohm+-25%_100mHz

_200mA_0.2ohm DC

L30

120Ohm/100Mhz

21

BLM18AG121SN1D

L16

120Ohm/100Mhz

21

BLM18AG121SN1D

R136

12

0.5Ohm 1%

pt_r0603

+VCC_MPLL_L

12

C382

22UF/10V

MLCC/+80%-20%

pt_c1206_h71

L27

BLM21PG221SN1D

220Ohm/100Mhz

pt_l0805_h41

+VCCA_HPLL

12

C378

22UF/10V

MLCC/+80%-20%

pt_c1206_h71

+VCCA_MPLL

+VCCA_PEG_PLL +VCC_RXR_DMI

21

12

R318

1Ohm 1%

pt_r0603

12

C323

10UF/6.3V

MLCC/+/-20%

pt_c0805_h53

12

12

C375

0.1UF/10V

MLCC/+/-10%

12

C121

0.1UF/10V

MLCC/+/-10%

C100

0.1UF/10V

MLCC/+/-10%

12