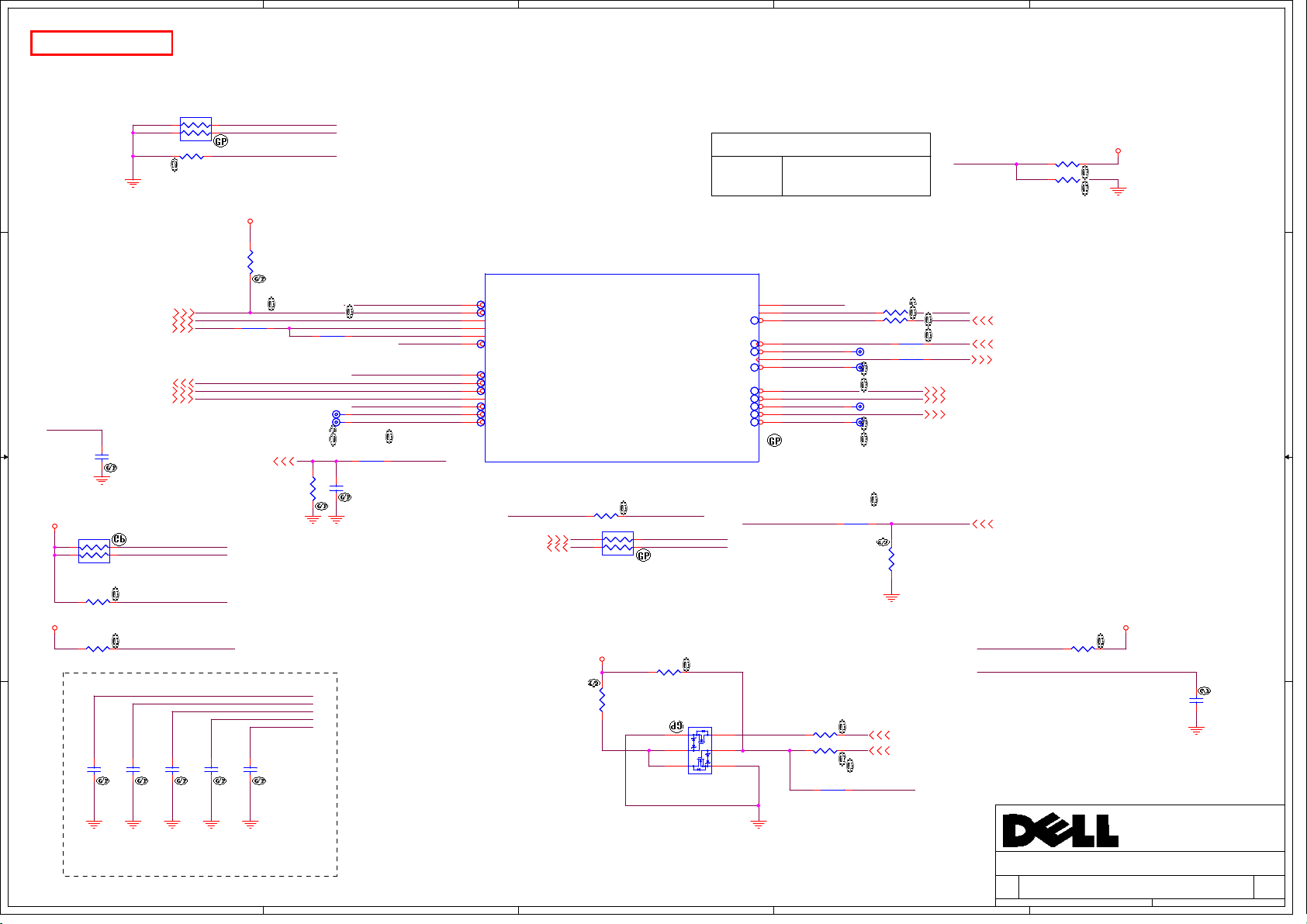

Dell Inspiron 13-7347 Schematics

5

D D

4

3

2

1

Cottonwood Schematic

Broadwell-ULT

C C

2014-06-09

REV : A00

DY : None Installed

B B

https://t.me/schematicslaptop

https://t.me/biosarchive

A A

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Tuesday, June 17, 2 014

Tuesday, June 17, 2 014

Tuesday, June 17, 2 014

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Cover Page

Cover Page

Cover Page

Cottonwood

Cottonwood

Cottonwood

Taipei Hsien 221, Taiwan, R.O.C.

1 104

1 104

1 104

of

of

1

of

A00

A00

A00

5

Project code:4PD01V010001

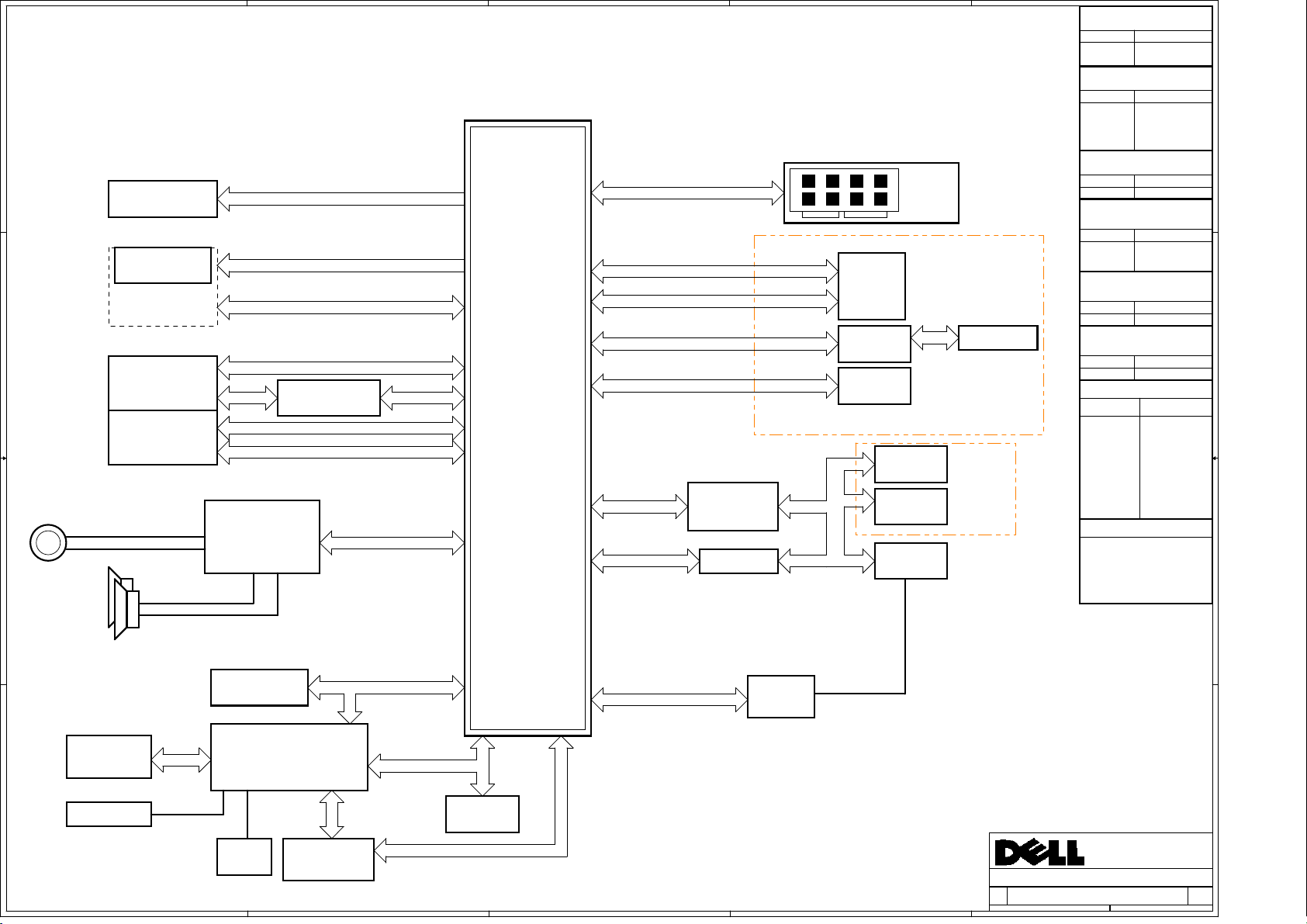

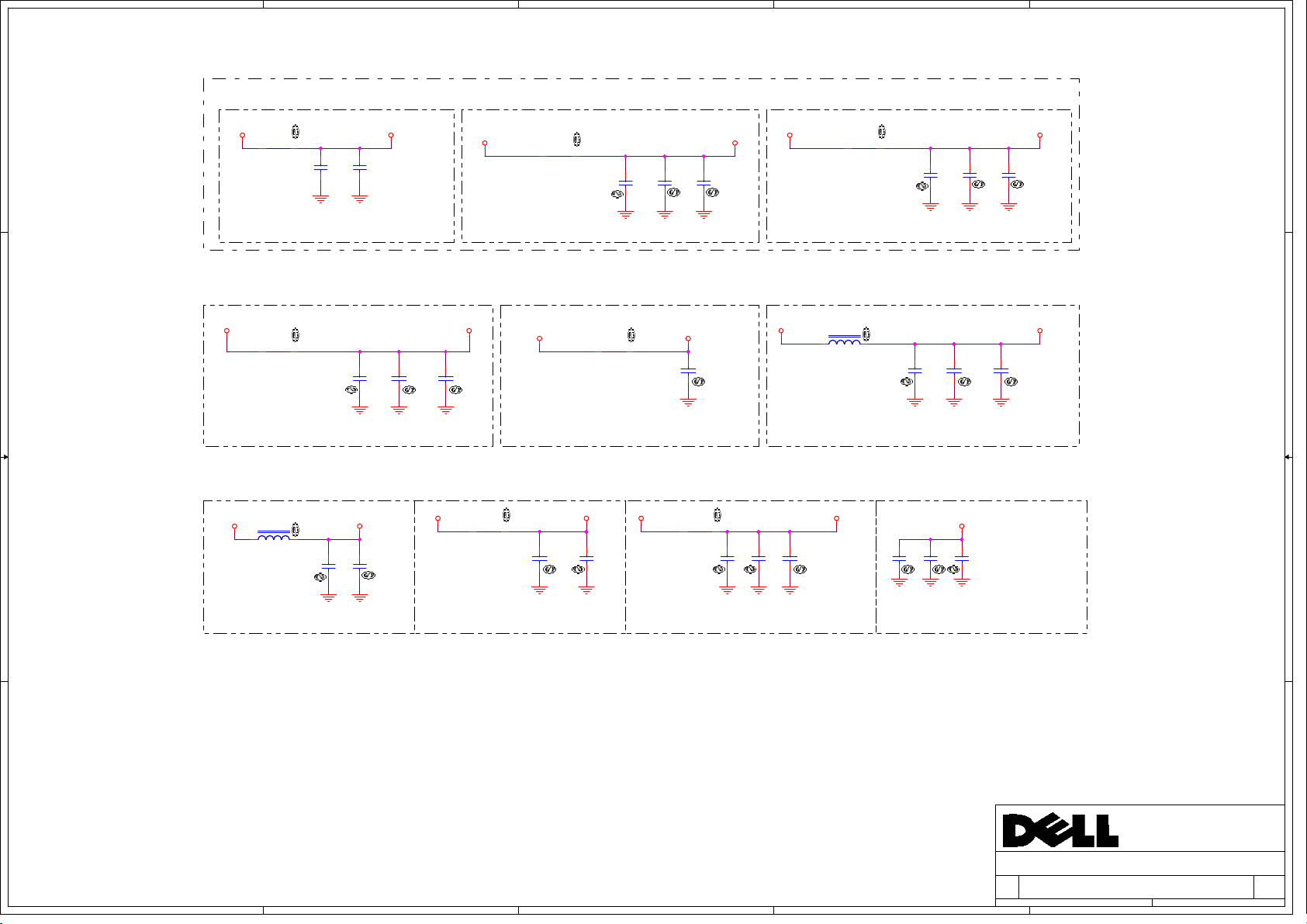

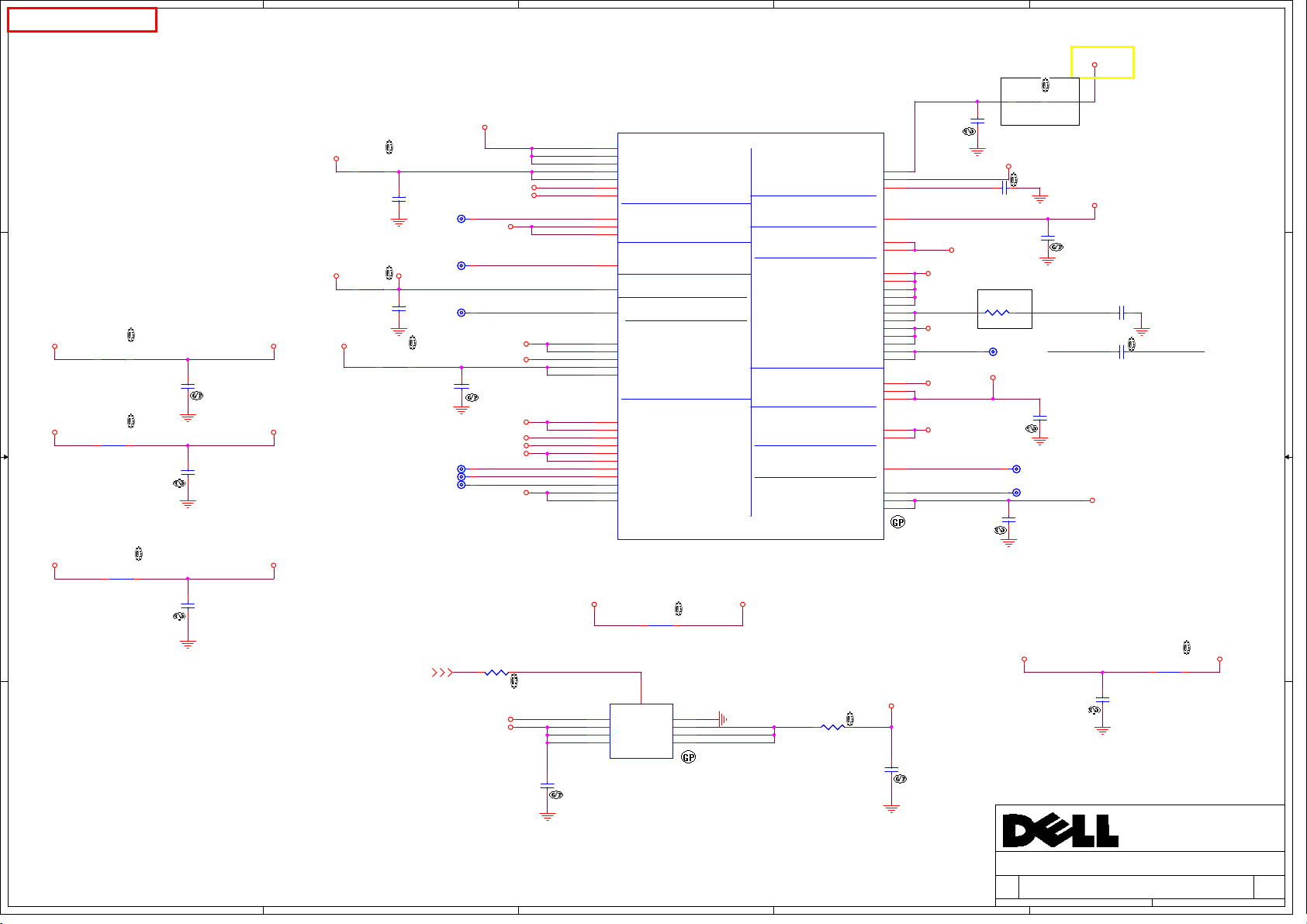

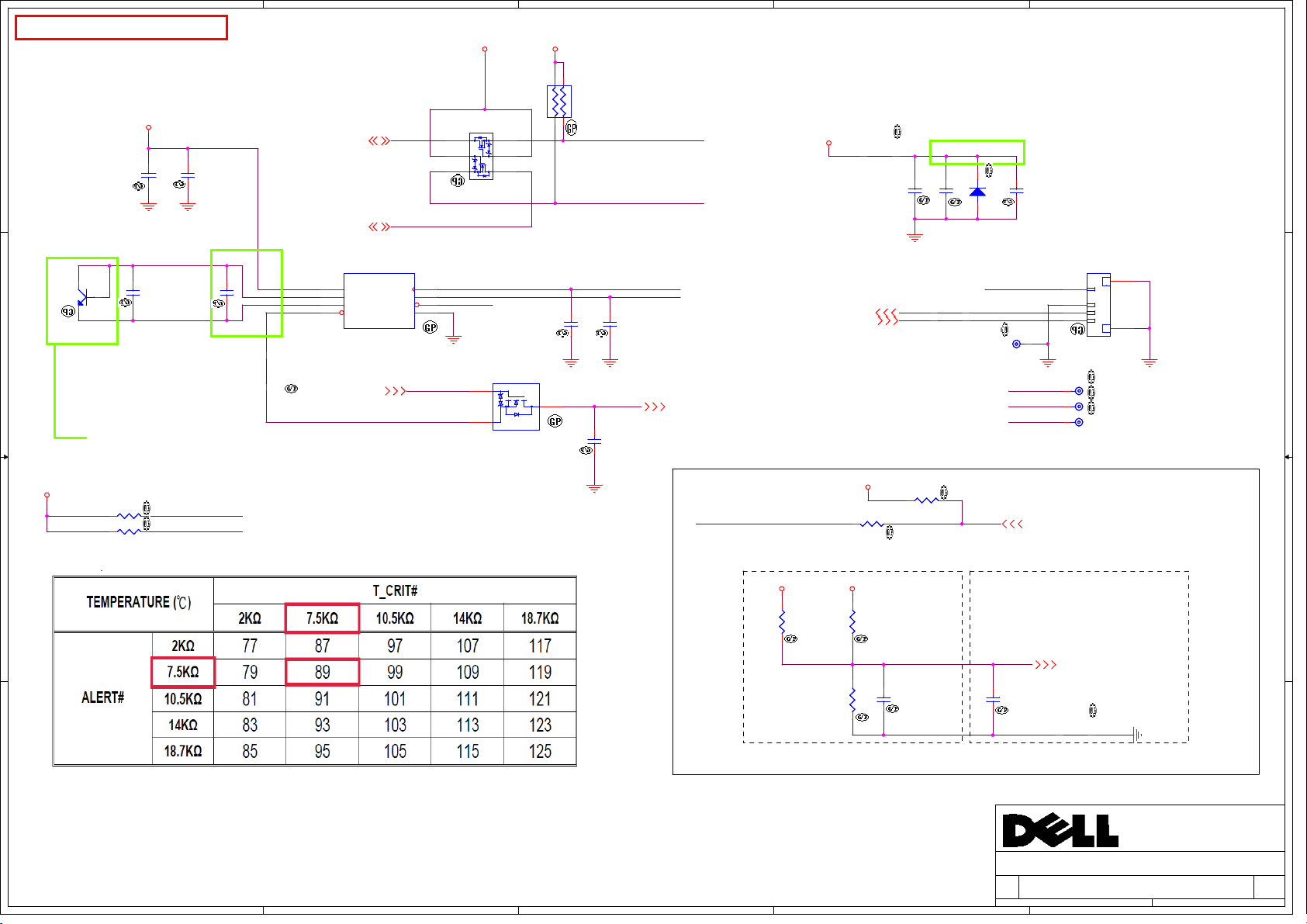

Cottonwood Block Diagram

PCB P/N: 13321

Revision: A00

D D

HDMI V1.4a

13.3" 16:9 eDP

Touch Panel

C C

USB3.0 Port1

Power share

USB3.0 Port2

MIC_IN/GND

29

Combo Jack

B B

HP_R/L

2CH SPEAKER

(2CH 2W/4ohm)

29

54

52

34

34

USB2.0

HDA

CODEC

Realtek

ALC3234

USB PowerShare

TI

TPS2544RTER

27

4

HDMI

eDP

USB2.0 x 1

USB3.0

USB2.0

34

USB3.0

USB2.0

HDA

Intel CPU

Broadwell ULT

15W (UMA)

WPT-LP

8 USB 2.0/1.1 ports

4 USB 3.0 ports

High Definition Audio

4 SATA ports

6 PCIE ports

LPC I/F

ACPI 4.0a

3

DDR3L 1600MHz C hannel A

PCIe x 1

USB2.0 x 1

USB2.0 x 1

USB2.0 x 1

USB2.0

USB2.0 x 1

Sensor Hub

ST

STM32L151CBU6TR

Camera / ALS

IO Board

66

52

I2C

2

DDR3L1600

SODIMM A

NGFF

WLAN & BT

combo module

Card reader

RealTek

RTS5176E

USB2.0 Port3

Gyro

ST

L3GD20

G + E-compass

ST

LSM303D

HOME button BD on Panel side

G Sensor

LNG3DMTR

66

12

SD/SDHC/MMC

1

CHARGER

BQ24770RUYR-GP

INPUTS

AD+

BT+

SYSTEM DC/DC

TPS51225RUKR-GP

INPUTS

DCBATOUT

CPU Core Power

TPS51624RSMR-GP

INPUTS

DCBATOUT

DDR3L SUS

TPS51716RUKR-GP

INPUTS OUTPUTS

DCBATOUT 1D35V_S3

CPU 1.05V

SY8208DQNC-GP-U

DCBATOUT

CPU 1D5V_S0

TLV70215DBVR-GP

3D3V_S5

OUTPUTS

DCBATOUT

OUTPUTS

3D3V_AUX_S5

5V_AUX_S5

5V_S5

3D3V_S5

OUTPUTS

VCC_CORE

0D65V_S0

OUTPUTSINPUTS

1D05V_S0

OUTPUTSINPUTS

1D5V_S0

Switches

46,47

33

36 83

44

45

49

48

51

INPUTS OUTPUTS

63

52

1D35V_S3 1D35V_S0

5V_S5 5V_S0

3D3V_S03D3V_S5

PCB LAYER

L1:Top

L2:VCC

L3:Signal

L4:Signal

L5:GND

L6:Signal

INT2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Block Diagram

Block Diagram

Block Diagram

Cottonwood

Cottonwood

Cottonwood

1

A00

A00

2 104Tuesday, June 17, 2014

2 104Tuesday, June 17, 2014

2 104Tuesday, June 17, 2014

A00

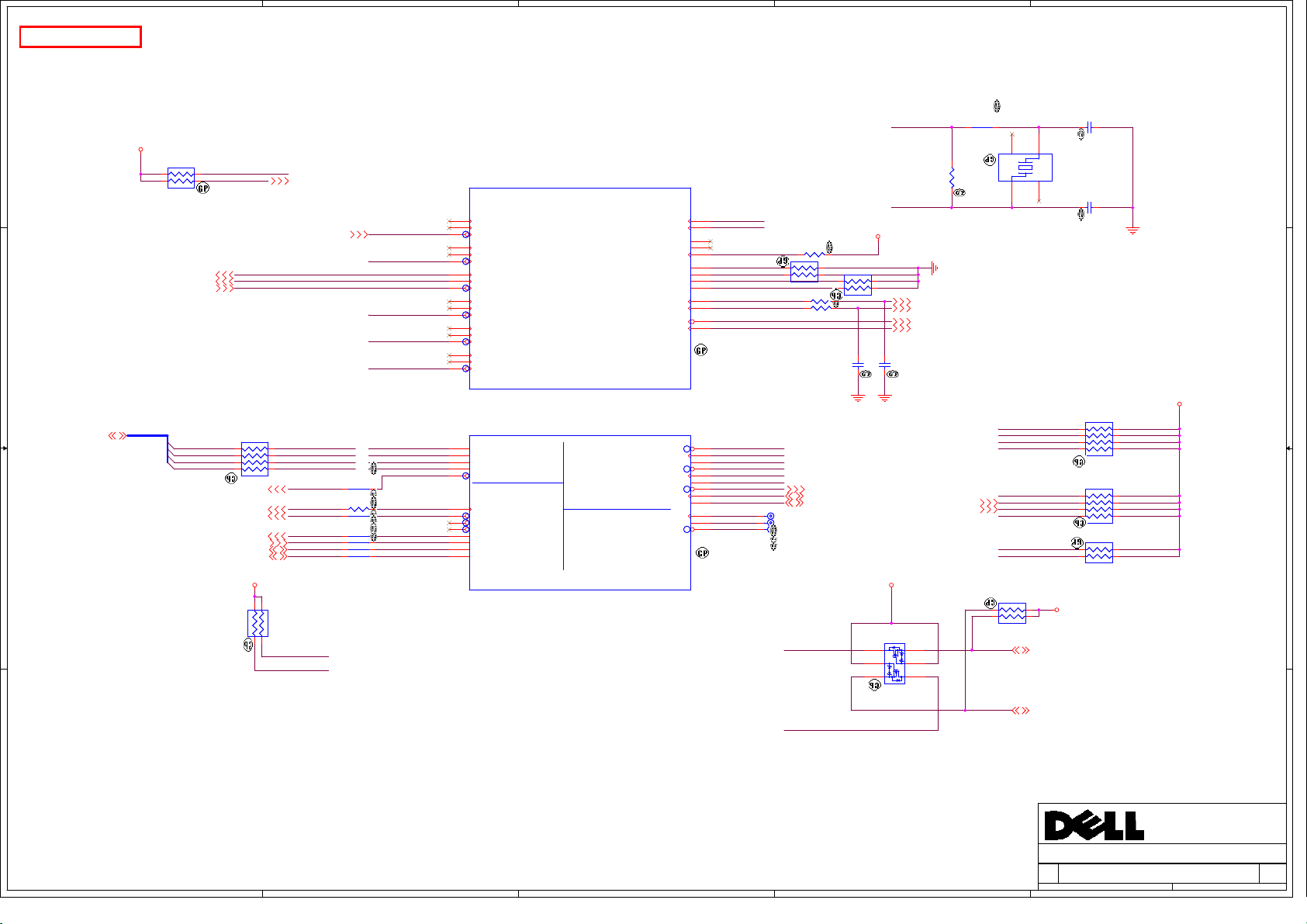

PS2

LPC BUS

24

62

4

SPI

Flash ROM

8MB

Quad Read

I2C

SATA(Gen3) x 1

25

3

HDD

56

LPC debug port

Thermal

NUVOTON

NCT7718W

A A

PWM FAN

SMBUS

26

26

Int.

KB

5

65

KBC

NUVOTON

NPCE285P

Image sensor

62

Touch PAD

5

D D

4

3

2

1

(Blanking)

C C

B B

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

(Reserved)

(Reserved)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

(Reserved)

Cottonwood

Cottonwood

Cottonwood

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

3 104Tuesday, June 17, 2014

3 104Tuesday, June 17, 2014

3 104Tuesday, June 17, 2014

1

A00

A00

A00

5

4

3

2

1

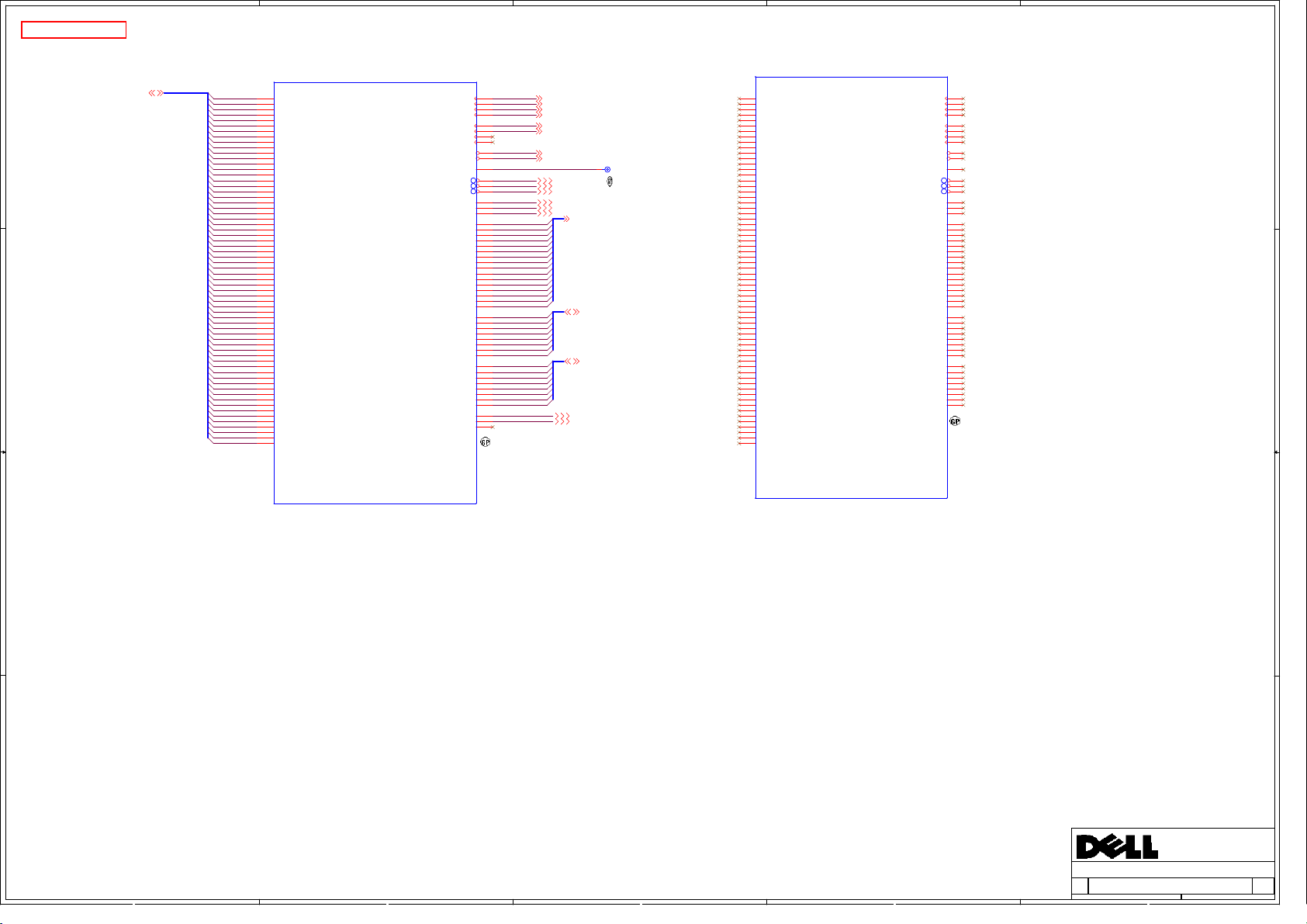

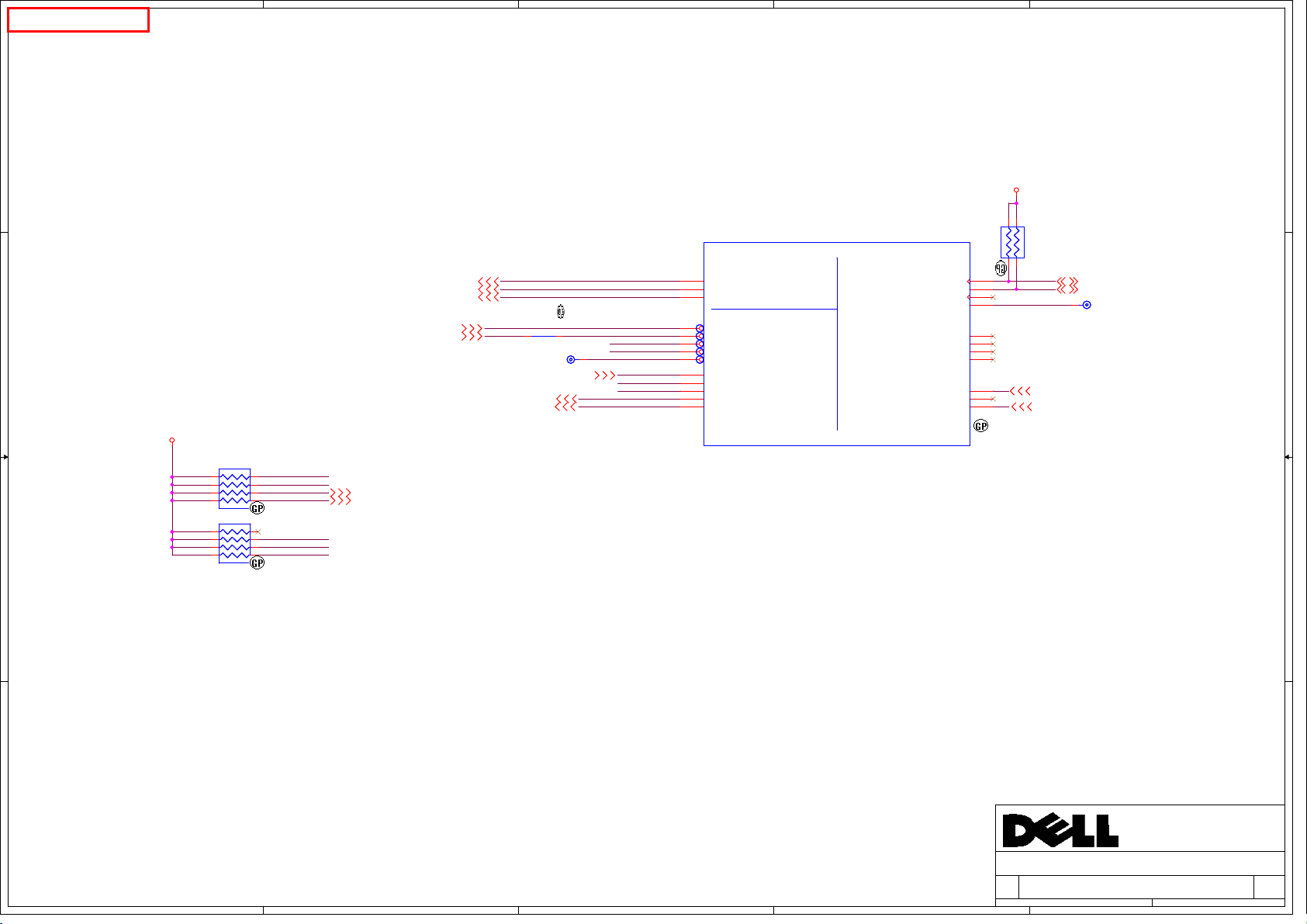

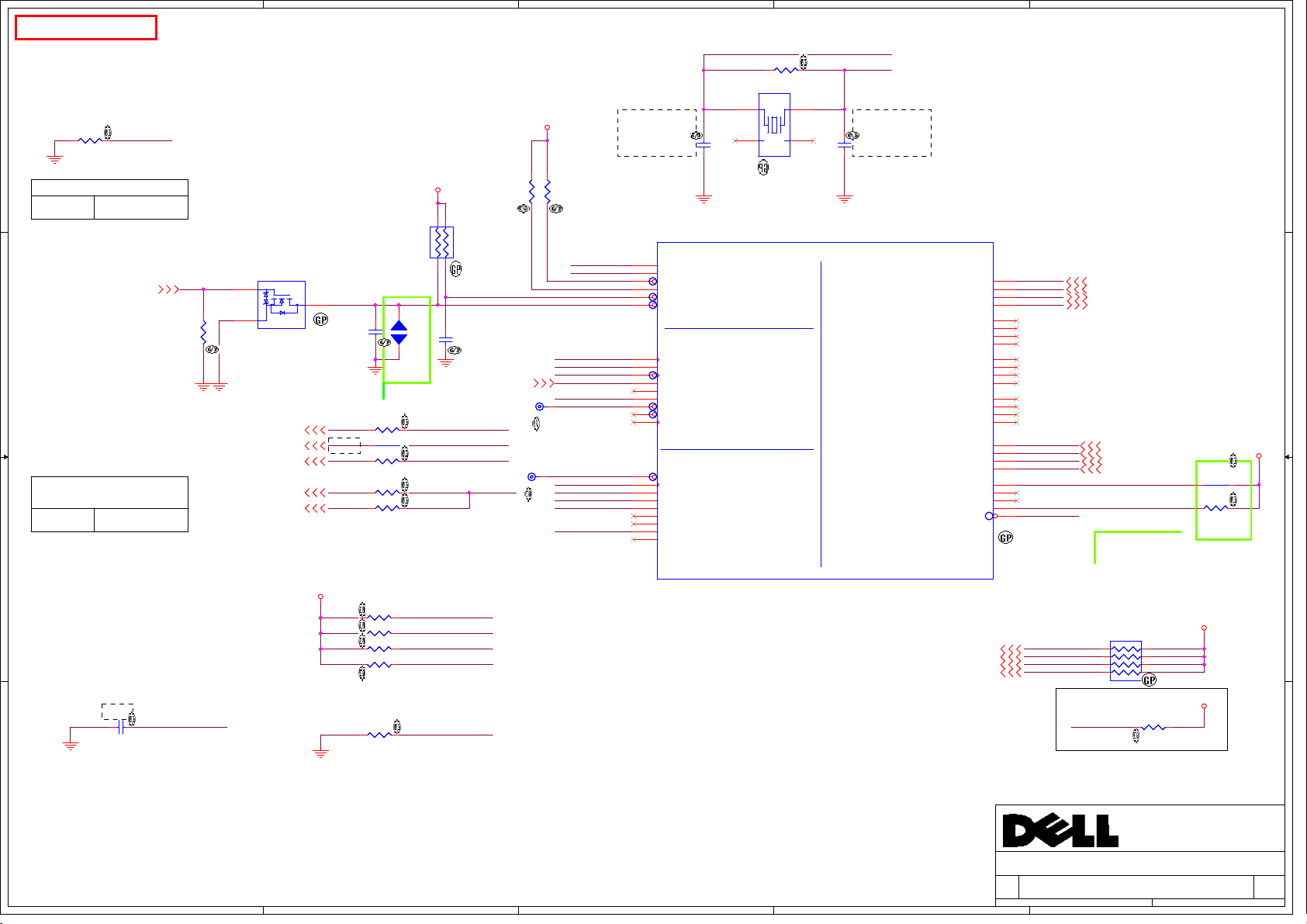

SSID = CPU

1D05S_VCCST

RN401

https://t.me/schematicslaptop

D D

https://t.me/biosarchive

XDP_TMS

XDP_TDI

XDP_TDO

XDP_TRST#

XDP_TCLK

R402 51R2J-2-GP

R402 51R2J-2-GP

R406 51R2J-2-GPR406 51R2J-2-GP

RN401

1

2

3

DY

DY

4 5

SRN51J-1-GP

SRN51J-1-GP

DY

DY

1 2

1 2

8

7

6

1D05S_VCCST

12

R401

R401

62R2J-GP

62R2J-GP

Layout Note:

C C

Impedance control:50 ohm

H_PROCHOT#[24,44,46]

10KR2J-3-GP

10KR2J-3-GP

DDR_PG_CTRL[12]

B B

R407 200R2F-L-GPR407 200R2F-L-GP

1 2

R408 121R2F-GPR408 121R2F-GP

1 2

R409 100R2F-L1-GP-UR409 100R2F-L1-GP-U

1 2

TP402TP402

H_PECI[24]

1 2

R403

R403

56R2J-4-GP

56R2J-4-GP

12

R405

R405

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

H_CATERR#

1

H_PROCHOT#_R XDP_TRST#

H_CPUPWRGD

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

SM_DRAMRST#

DDR_PG_CTRL

CPU1B

CPU1B

D61

PROC_DETECT#

K61

CATERR#

N62

PECI

K63

PROCHOT#

C61

PROCPWRGD

AU60

SM_RCOMP0

AV60

SM_RCOMP1

AU61

SM_RCOMP2

AV15

SM_DRAMRST#

AV61

SM_PG_CNTL1

HASWELL-6-GP-U

HASWELL-6-GP-U

SM_DRAMRST#

Layout Note:

Design Guideline:

MISC

MISC

THERMAL

THERMAL

PWR

PWR

DDR3L

DDR3L

HSW_ULT_DDR3L

HSW_ULT_DDR3L

1D35V_S3

12

R410

R410

470R2J-2-GP

470R2J-2-GP

JTAG

JTAG

X02 0414

R404

R404

1 2

0R0402-PAD-2-GP

0R0402-PAD-2-GP

2 OF 19

2 OF 19

XDP_PRDY#

J62

PRDY#

PREQ#

PROC_TCK

PROC_TMS

PROC_TRST#

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TDI

XDP_TDO

XDP_BPM0

XDP_BPM1

XDP_BPM2

XDP_BPM3

XDP_BPM4

XDP_BPM5

XDP_BPM6

XDP_BPM7

Layout Note:

Place close to DIMM

DDR3_DRAMRST# [12]

<Core Design>

<Core Design>

<Core Design>

XDP_PRDY# [96]

XDP_PREQ# [96]

XDP_TCLK [96]

XDP_TMS [96]

XDP_TRST# [96]

XDP_TDI [96]

XDP_TDO [96]

XDP_BPM[7:0]

XDP_BPM[7:0] [96]

SM_RCOMP keep routing length less than 500 mils.

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

CPU (THERMAL/MISC/PM)

CPU (THERMAL/MISC/PM)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

CPU (THERMAL/MISC/PM)

2

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Cottonwood

Cottonwood

Cottonwood

4 104Tuesday, June 17, 2014

4 104Tuesday, June 17, 2014

4 104Tuesday, June 17, 2014

1

A00

A00

A00

5

4

3

2

1

SSID = CPU

DDR3L ball type: Non-Interleaved Type

HSW_ULT_DDR3L

CPU1D

AW31

AW29

AW27

AW25

AM29

AM26

AW23

AW21

AW19

AW17

AY31

AY29

AV31

AU31

AV29

AU29

AY27

AY25

AV27

AU27

AV25

AU25

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AK25

AL25

AY23

AY21

AV23

AU23

AV21

AU21

AY19

AY17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

CPU1D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HSW_ULT_DDR3L

CPU1C

AM63

AM62

AM61

AM60

AM57

AM54

AW58

AW56

AW54

AW52

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AP63

AP62

AP61

AP60

AP58

AR58

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AK54

AL55

AK55

AR54

AN54

AY58

AY56

AV58

AU58

AV56

AU56

AY54

AY52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

CPU1C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

M_A_DQ[63:0][12]

D D

C C

M_A_DQ[63:0]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

HSW_ULT_DDR3L

DDR CHANNEL A

DDR CHANNEL A

3 OF 19

3 OF 19

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS#

SA_WE#

SA_CAS#

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

+V_SM_VREF_C NT

M_A_DIMA_CLK_DD R#0 [12]

M_A_DIMA_CLK_DD R0 [12]

M_A_DIMA_CLK_DD R#1 [12]

M_A_DIMA_CLK_DD R1 [12]

M_A_DIMA_CKE0 [12]

M_A_DIMA_CKE1 [12]

M_A_DIMA_CS#0 [12]

M_A_DIMA_CS#1 [12]

TP_M_A_DIMA_ODT 0

M_A_RAS# [12]

M_A_WE# [12]

M_A_CAS# [12]

M_A_BS0 [12]

M_A_BS1 [12]

M_A_BS2 [12]

M_A_A[15:0] [12]

M_A_DQS#[7:0] [ 12]

M_A_DQS[7:0] [12]

+V_SM_VREF_C NT [37]

DDR_W R_VREF01 [37]

TP501TP501

1

HSW_ULT_DDR3L

DDR CHANNEL B

DDR CHANNEL B

4 OF 19

4 OF 19

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS#

SB_WE#

SB_CAS#

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

HASWELL- 6-GP-U

HASWELL- 6-GP-U

HASWELL- 6-GP-U

B B

A A

5

4

3

HASWELL- 6-GP-U

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Date: Sheet

Date: Sheet

2

Date: Sheet

Taipei Hsie n 221, Taiwan, R.O.C.

CPU (DDR)

CPU (DDR)

CPU (DDR)

Cottonwood

Cottonwood

Cottonwood

1

A00

A00

5 104Tuesday, June 17, 2014

5 104Tuesday, June 17, 2014

5 104Tuesday, June 17, 2014

A00

of

of

of

5

4

3

2

1

SSID = CPU

D D

HSW_ULT_DDR3L

CPU1S

CPU1S

HSW_ULT_DDR3L

19 OF 19

19 OF 19

#514405

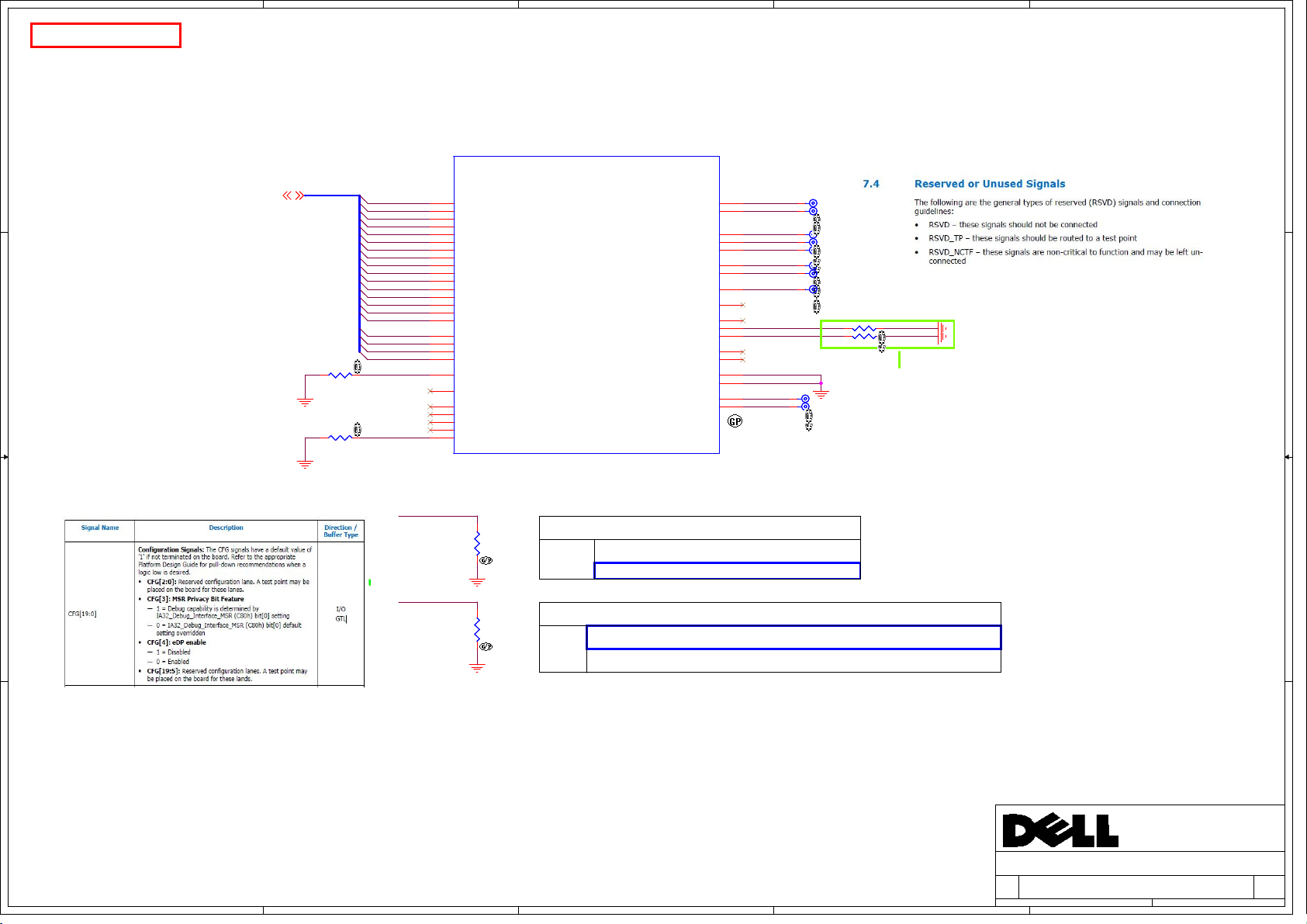

CFG[19:0][96]

C C

PCH strap pin:

#514405

B B

CFG[19:0]

1 2

R601

R601

49D9R2F -GP

49D9R2F -GP

1 2

R603

R603

8K2R2F-1 -GP

8K2R2F-1 -GP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCO MP

TD_IREF

CFG3

CFG4

AC60

AC62

AC63

AA63

AA60

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

AA62

U63

AA61

U62

V63

H18

B12

Y62

J20

A5

E1

D1

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD#A5

RSVD#E1

RSVD#D1

RSVD#J20

RSVD#H18

TD_IREF

12

DY

DY

12

R604

R604

1KR2J-1-G P

1KR2J-1-G P

R605

R605

1KR2J-1-G P

1KR2J-1-G P

RSVD_TP#AV63

RSVD_TP#AU63

RSVD_TP#C63

RSVD_TP#C62

RSVD#B43

RSVD_TP#A51

RSVD_TP#B51

RESERVED

RESERVED

RSVD_TP#L60

RSVD#N60

RSVD#W23

RSVD#Y22

PROC_OPI_RCOMP

RSVD#AV62

RSVD#D58

VSS

VSS

RSVD#P20

RSVD#R20

PHYSICAL_DEBUG_ ENABLED (DFX P RIVACY)

0 : ENABLED

CFG[3]

SET DFX ENABLED BIT IN DEBUG INTERFACE MSR

1 : DISABLED

DISPLAY PORT PR ESENCE STRAP

0 : ENABLED

CFG[4]

AN EXTERNAL DIS PLAY PORT DEVI CE IS CONNECTED TO THE EMBEDD ED DISPLAY POR T

1 : DISABLED

NO PHYSICAL DIS PLAY PORT ATTA CHED TO EMBEDDE D DISPLAY PORT

AV63

AU63

C63

C62

B43

A51

B51

L60

N60

W23

PROC_OP I_COMP3

Y22

PROC_OP I_COMP

AY15

AV62

D58

P22

N21

HVM_CLK #

P20

HVM_CLK

R20

RSVDAV6 3

RSVDAU6 3

RSVDC63

RSVDC62

EDP_SPA RE

RSVDA51

RSVDB51

RSVDL60

TP601TP601

1

TP602TP602

1

TP603TP603

1

TP604TP604

1

TP605TP605

1

TP606TP606

1

TP607TP607

1

TP608TP608

1

Intel Recommend

R606 49D 9R2F-GP

R606 49D 9R2F-GP

1 2

DY

DY

R602 49D 9R2F-GPR602 49D 9R2F-GP

1 2

1

TP619TP619

1

TP620TP620

Layout Note:

1.Referenced "continuous" VSS plane only.

2.Avoid routing next to clock pins or noisy

signals.

3.Trace width: 12~15mil

4.Isolation Spacing: 12mil

5.Max length: 500mil

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

CPU (CFG)

CPU (CFG)

CPU (CFG)

Cottonwood

Cottonwood

Cottonwood

1

6 104Tuesday, June 17, 2 014

6 104Tuesday, June 17, 2 014

6 104Tuesday, June 17, 2 014

of

of

of

A00

A00

A00

5

SSID = CPU

4

3

2

1

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

VCC_COR E

HSW_ULT_DDR3L

CPU1L

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

N58

AC58

AB23

AD23

AA23

AE59

N63

C59

D63

H59

N59

N61

AD60

AD59

AA59

AE60

AC59

AG58

U59

AC22

AE22

AE23

AB57

AD57

AG57

C24

C28

C32

L59

F59

E63

A59

E20

L62

L63

B59

F60

P62

P60

P61

T59

V59

J58

CPU1L

RSVD#L59

RSVD#J58

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD#N58

RSVD#AC58

VCC_SENSE

RSVD#AB23

VCCIO_OUT

VCCIOA_OUT

RSVD#AD23

RSVD#AA23

RSVD#AE59

VIDALERT#

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG#

VSS

RSVD_TP#P60

RSVD_TP#P61

RSVD_TP#N59

RSVD_TP#N61

RSVD#T59

RSVD#AD60

RSVD#AD59

RSVD#AA59

RSVD#AE60

RSVD#AC59

RSVD#AG58

RSVD#U59

RSVD#V59

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

HASW ELL-6-GP-U

HASW ELL-6-GP-U

D D

1D35V_S 3

1D05S_V CCST

NC#1

VCC

A

DY

DY

GND3Y

VR_SVID_A LERT#

H_CPU_S VIDDAT

3D3V_S5

1D05S_V CCST

12

DY

DY

C702

C702

5

4

12

R709

R709

47KR2F-G P

47KR2F-G P

DY

DY

12

R706

R706

10KR2J-3 -GP

10KR2J-3 -GP

DY

DY

12

EC701

EC701

Layout Note:

1. Place close to CPU

2. VCC_SENSE/ VSS_SENSE

impedance=50 ohm

3. Length match<25mil

H_VCCST _PWRGD [96 ]

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

VR_SVID_A LERT#[46]

H_CPU_S VIDCLK[46]

H_CPU_S VIDDAT[46]

H_VR_EN ABLE[46]

PWR_ DEBUG[96]

1D05V_S 0

0R0603-P AD-2-GP-U

0R0603-P AD-2-GP-U

1D05S_V CCST

X02 0414

R711

R711

1 2

VCC_SEN SE[46]

1D05S_V CCST

VCC_COR E

12

R702

R702

100R2F-L 1-GP-U

100R2F-L 1-GP-U

TP701TP701

43R2J-GP

43R2J-GP

1 2

H_CPU_S VIDCLK

H_CPU_S VIDDAT

R710 10K R2J-3-GP

R710 10K R2J-3-GP

1 2

IMVP_PW RGD_R

150R2J-L 1-GP-U

150R2J-L 1-GP-U

R705

R705

1 2

TP702TP702

TP703TP703

TP704TP704

TP705TP705

0.1A

C701

SC22U6D3V3MX-1-GPDYC701

SC22U6D3V3MX-1-GP

C703

SC1U6D3V2KX-GPDYC703

DY

SC1U6D3V2KX-GP

12

12

DY

+VCCIOA_O UT

R701

R701

H_VCCST _PWRGD

DY

DY

1

1

1

1

VCC_COR E

VCC_COR E

TP_VCCIO_ OUT

1

H_CPU_S VIDALRT#

PWR_ DEBUG

RSVDP60

RSVDP61

RSVDN59

RSVDN61

1D05S_V CCST

R703 75R 2F-2-GPR703 75R 2F-2-GP

1 2

R704 130 R2F-1-GPR704 130 R2F-1-GP

1 2

#487822

C C

SCD1U10 V2KX-5GP

SCD1U10 V2KX-5GP

U701

U701

1

1D05V_V TT_PWRGD[36,48]

B B

2

74LVC1G 07GW-GP

74LVC1G 07GW-GP

73.01G07.0HG

73.01G07.0HG

1 2

R707

R707

100KR2F -L1-GP

100KR2F -L1-GP

Need to fine tu ne to 1.05V.

HSW_ULT_DDR3L

HSW ULT POWER

HSW ULT POWER

12 OF 19

12 OF 19

IMVP_PW RGD[24,46]

A A

5

4

1 2

R713

R713

100KR2F -L1-GP

100KR2F -L1-GP

IMVP_PW RGD_R

12

R712

R712

47KR2F-G P

47KR2F-G P

3

DY

DY

12

EC702

EC702

<Core Design>

<Core Design>

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

2

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Tuesday, June 17, 2 014

Tuesday, June 17, 2 014

Tuesday, June 17, 2 014

Date: Sheet

Date: Sheet

Date: Sheet

CPU (VCC CORE)

CPU (VCC CORE)

CPU (VCC CORE)

Cottonwood

Cottonwood

Cottonwood

Taipei Hsien 221, Taiwan, R.O.C.

7 104

7 104

7 104

of

of

1

of

A00

A00

A00

5

4

3

2

1

SSID = CPU

D D

HSW_ULT_DDR3L

CPU1A

CPU1A

HSW_ULT_DDR3L

1 OF 19

1 OF 19

HDMI_DATA 2#[54]

HDMI_DATA 2[54]

HDMI

C C

HDMI_DATA 1#[54]

HDMI_DATA 1[54]

HDMI_DATA 0#[54]

HDMI_DATA 0[54]

HDMI_CLK#[54]

HDMI_CLK[54]

C54

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

DDI1_TXP2

A57

DDI1_TXN3

B57

DDI1_TXP3

C51

DDI2_TXN0

C50

DDI2_TXP0

C53

DDI2_TXN1

B54

DDI2_TXP1

C49

DDI2_TXN2

B50

DDI2_TXP2

A53

DDI2_TXN3

B53

DDI2_TXP3

HASW ELL-6-GP-U

HASW ELL-6-GP-U

EDPDDI

EDPDDI

EDP_RCOMP

EDP_DISP_UTIL

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

EDP_COM P

EDP_BRIGH TNESS

EDP_TX0 _DN [52]

EDP_TX0 _DP [52]

EDP_TX1 _DN [52]

EDP_TX1 _DP [52]

EDP_AUX _DN [52]

EDP_AUX _DP [52 ]

1

TP801TP801

R801

R801

24D9R2F -L-GP

24D9R2F -L-GP

+VCCIOA_O UT

Design Guidelin e:

EDP_COMP keep r outing length max 100 mils.

12

Trace Width:20 mils.

B B

<Core Design>

<Core Design>

A A

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

CPU (DDI/EDP)

CPU (DDI/EDP)

CPU (DDI/EDP)

Cottonwood

Cottonwood

Cottonwood

8 104Tuesday, June 17, 2 014

8 104Tuesday, June 17, 2 014

8 104Tuesday, June 17, 2 014

of

of

of

A00

A00

A00

5

4

3

2

1

SSID = CPU

HSW_ULT_DDR3L

CPU1P

CPU1P

D33

VSS

D34

D D

C C

B B

VSS

D35

VSS

D37

VSS

D38

VSS

D39

VSS

D41

VSS

D42

VSS

D43

VSS

D45

VSS

D46

VSS

D47

VSS

D49

VSS

D5

VSS

D50

VSS

D51

VSS

D53

VSS

D54

VSS

D55

VSS

D57

VSS

D59

VSS

D62

VSS

D8

VSS

E11

VSS

E17

VSS

F20

VSS

F26

VSS

F30

VSS

F34

VSS

F38

VSS

F42

VSS

F46

VSS

F50

VSS

F54

VSS

F58

VSS

F61

VSS

G18

VSS

G22

VSS

G3

VSS

G5

VSS

G6

VSS

G8

VSS

H13

VSS

HASWELL-6-GP-U

HASWELL-6-GP-U

HSW_ULT_DDR3L

16 OF 19

16 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_SENSE

VSS

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

VSS_SENSE

12

VSS_SENSE [46]

Layout Note:

R901

R901

100R2F-L1-GP-U

100R2F-L1-GP-U

1. Place close to CPU

2. VCC_SENSE/ VSS_SENSE

impedance=50 ohm

3. Length match<25mil

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

CPU (VSS)

CPU (VSS)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

CPU (VSS)

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Cottonwood

Cottonwood

Cottonwood

9 104Tuesday, June 17, 2014

9 104Tuesday, June 17, 2014

9 104Tuesday, June 17, 2014

1

A00

A00

A00

5

4

3

2

1

SSID = CPU

1D35V_S 3

D D

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C1001

C1001

12

12

C C

SC10U6D3V3MX-GP

C1002

C1002

C1003

C1018

C1018

BDW CAP

BDW CAP

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

C1003

12

C1019

C1019

12

12

12

C1017

C1017

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC2200P50V2KX-2GP

SC2200P50V2KX-2GP

BDW CAP

BDW CAP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C1004

C1004

12

12

DY

DY

DY

DY

C1020

SC2200P50V2KX-2GP

C1020

SC2200P50V2KX-2GP

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C1006

C1006

C1005

C1005

12

DY

DY

Layout Note:

Direct tie to CPU VccIn/Vss balls

Layout Note:

As close to CPU as possible

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU (Power CAP1)

CPU (Power CAP1)

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

CPU (Power CAP1)

Cottonwood

Cottonwood

Cottonwood

Taipei Hsien 221, Taiwan, R.O.C.

10 104Tuesday, June 17, 2 014

10 104Tuesday, June 17, 2 014

10 104Tuesday, June 17, 2 014

of

of

1

of

A00

A00

A00

5

4

3

2

1

MAX: 1.92A

1.838A 41mA 42mA

D D

X02 0414

R1101

R1101

1 2

0R0805-P AD-2-GP-U

0R0805-P AD-2-GP-U

+V1.05DX _MODPHY_PCH1D05V_H SIO

C1102

SC1U6D3V2KX-GP

C1102

SC1U6D3V2KX-GP

C1101

SC1U6D3V2KX-GP

C1101

12

SC1U6D3V2KX-GP

12

CAP need close to pin K9 L10

1D05V_H SIO

X02 0414

L1101

L1101

1 2

0R0603-P AD-2-GP-U

0R0603-P AD-2-GP-U

12

CAP need close to pin B18

+V1.05S_ AUSB3PLL

C1103

SC1U6D3V2KX-GP

C1103

SC1U6D3V2KX-GP

12

DY

DY

+V1.05S_ AUSB3PLL

12

DY

DY

C1104

C1104

C1123

C1123

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

1D05V_H SIO

X02 0414

L1102

L1102

1 2

0R0603-P AD-2-GP-U

0R0603-P AD-2-GP-U

12

CAP need close to pin B11

+V1.05S_ ASATA3PLL

C1105

SC1U6D3V2KX-GP

C1105

SC1U6D3V2KX-GP

12

DY

DY

+V1.05S_ ASATA3PLL

12

DY

DY

C1106

C1106

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1107

C1107

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

57mA 62mA

12

DY

+V1.05S_ APLLOPI

C1110

SC10U6D3V3MX-GPDYC1110

SC10U6D3V3MX-GP

DY

X02 0414X02 0414

R1103

R1103

C1124

SC10U6D3V3MX-GPDYC1124

SC10U6D3V3MX-GP

12

1 2

0R0603-P AD-2-GP-U

0R0603-P AD-2-GP-U

CAP need close to pin AC9

+V3.3A_P SUS3D3V_S5 _PCH

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C1108

C1108

12

DY

DY

L1103 IND-2 D2UH-196-GP

L1103 IND-2 D2UH-196-GP

1 2

68.2R21D.10R

68.2R21D.10R

CAP need close to pin J18

1D05V_S 0

C C

R1102

R1102

1 2

0R0603-P AD-2-GP-U

0R0603-P AD-2-GP-U

+V1.05S_ APLLOPI

C1109

SC1U6D3V2KX-GP

C1109

SC1U6D3V2KX-GP

12

CAP need close to pin AA21

185mA

12

C1111

SC1U6D3V2KX-GP

C1111

SC1U6D3V2KX-GP

+V1.05S_ AXCK_DCB

C1112

SC10U6D3V3MX-GPDYC1112

SC10U6D3V3MX-GP

12

DY

DY

+V1.05S_ AXCK_DCB1D05V_S 0

C1125

SC10U6D3V3MX-GPDYC1125

SC10U6D3V3MX-GP

12

31mA 658mA 1.632A 1mA

X02 0414

1D05V_S 0

IND-2D2UH-1 96-GP

IND-2D2UH-1 96-GP

L1104

L1104

1 2

68.2R21D.10R

68.2R21D.10R

B B

+V1.05S_ AXCK_LCPLL

C1113

SC1U6D3V2KX-GP

C1113

SC1U6D3V2KX-GP

12

12

DY

DY

C1114

C1114

CAP need close to pin A20

1D05V_S 0

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

CAP need close to pin AE9

R1104

R1104

1 2

0R0603-P AD-2-GP-U

0R0603-P AD-2-GP-U

DY

C1115

SC10U6D3V3MX-GPDYC1115

SC10U6D3V3MX-GP

C1116

SC1U6D3V2KX-GP

C1116

12

SC1U6D3V2KX-GP

12

1D05V_S 0

0R0805-P AD-2-GP-U

0R0805-P AD-2-GP-U

X02 0414

R1105

R1105

1 2

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C1117

C1117

C1118

SC1U6D3V2KX-GP

C1118

SC1U6D3V2KX-GP

12

+V1.05S_ CORE_PCH+1.05M_A SW

C1119

SC10U6D3V3MX-GPDYC1119

SC10U6D3V3MX-GP

12

12

DY

CAP need close to pin AE8 J11

RTC_AUX _S5

C1121

SCD1U10V2KX-5GP

C1121

SCD1U10V2KX-5GP

C1122

SC1U6D3V2KX-GP

C1122

C1120

SCD1U10V2KX-5GPDYC1120

SCD1U10V2KX-5GP

12

12

SC1U6D3V2KX-GP

12

DY

CAP need close to pin AG10

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU (Power CAP2)

CPU (Power CAP2)

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

CPU (Power CAP2)

Cottonwood

Cottonwood

Cottonwood

Taipei Hsien 221, Taiwan, R.O.C.

11 104Tuesday, June 17, 2 014

11 104Tuesday, June 17, 2 014

11 104Tuesday, June 17, 2 014

of

of

1

of

A00

A00

A00

5

4

3

2

1

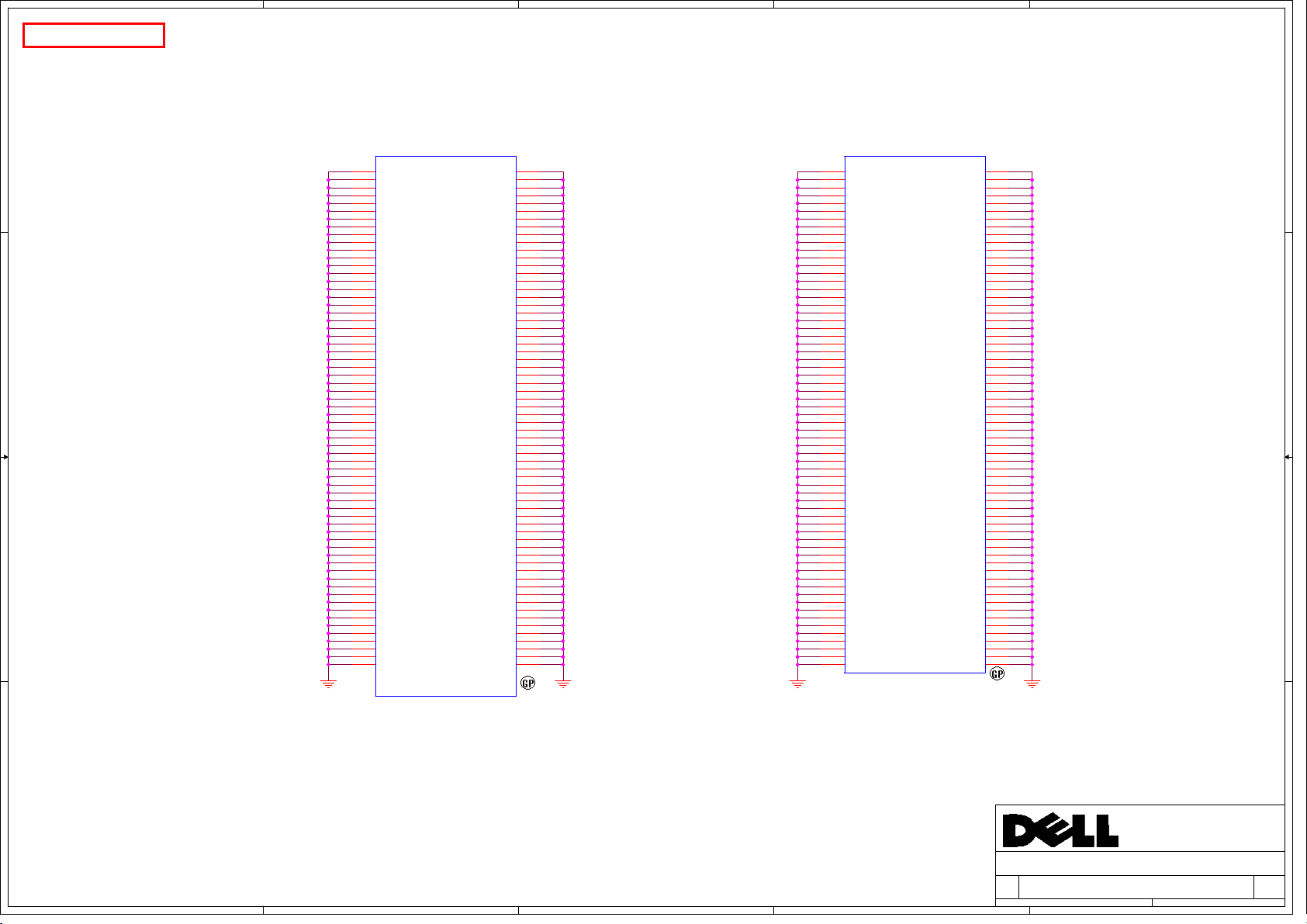

SSID = MEMORY

SA0_DIMA

SA1_DIMA

DIMM1

D D

M_VREF_CA_D IMMA

12

12

12

C1201

C1201

C1218

C1218

C1202

C1202

C C

B B

A A

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

DY

DY

C1204

C1204

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

0D675V_S0

12

12

C1214

C1214

DY

DY

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

Layout Note:

All VREF traces should

have width=20mil;

spacing=20 mil

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

M_VREF_DQ_D IMMA

12

C1205

C1205

SC2D2U10V3KX-1GP

SC2D2U10V3KX-1GP

12

C1215

C1215

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

5

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

C1206

C1206

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

C1216

C1216

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

M_A_A[15:0][5]

M_A_DQ[63:0][5]

Layout Note:

Place these caps

close to VREF_CA

Layout Note:

Place these caps

close to VREF_DQ

Layout Note:

Place these caps

close to VTT1 and

VTT2.

M_A_DQS#[7:0][5]

M_A_DQS[7:0][5]

M_VREF_CA_D IMMA

M_VREF_DQ_D IMMA

DDR3_DR AMRST#[4]

M_A_BS2[5]

M_A_BS0[5]

M_A_BS1[5]

M_A_DIMA_ODT0

M_A_DIMA_ODT1

12

ED1217

ED1217

AZ5725-01FDR 7G-GP

AZ5725-01FDR 7G-GP

close to dimm

0D675V_S0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQ13

M_A_DQ8

M_A_DQ14

M_A_DQ10

M_A_DQ9

M_A_DQ12

M_A_DQ15

M_A_DQ11

M_A_DQ29

M_A_DQ28

M_A_DQ30

M_A_DQ31

M_A_DQ25

M_A_DQ24

M_A_DQ27

M_A_DQ26

M_A_DQ44

M_A_DQ41

M_A_DQ43

M_A_DQ47

M_A_DQ45

M_A_DQ40

M_A_DQ42

M_A_DQ46

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ7

M_A_DQ21

M_A_DQ20

M_A_DQ17

M_A_DQ16

M_A_DQ18

M_A_DQ19

M_A_DQ22

M_A_DQ23

M_A_DQ36

M_A_DQ33

M_A_DQ34

M_A_DQ38

M_A_DQ37

M_A_DQ32

M_A_DQ35

M_A_DQ39

M_A_DQ62

M_A_DQ58

M_A_DQ60

M_A_DQ61

M_A_DQ63

M_A_DQ59

M_A_DQ56

M_A_DQ57

M_A_DQS#1

M_A_DQS#3

M_A_DQS#5

M_A_DQS#6

M_A_DQS#0

M_A_DQS#2

M_A_DQS#4

M_A_DQS#7

M_A_DQS1

M_A_DQS3

M_A_DQS5

M_A_DQS6

M_A_DQS0

M_A_DQS2

M_A_DQS4

M_A_DQS7

DIMM1

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12

119

A13

80

A14

78

A15

79

A16/BA2

109

BA0

108

BA1

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

10

DQS0#

27

DQS1#

45

DQS2#

62

DQS3#

135

DQS4#

152

DQS5#

169

DQS6#

186

DQS7#

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

116

ODT0

120

ODT1

126

VREF_CA

1

VREF_DQ

30

RESET#

203

VTT1

204

VTT2

SKT_DDR 204P SMD

SKT_DDR 204P SMD

DDR3-204P- 215-GP-U

DDR3-204P- 215-GP-U

62.10024.M31

62.10024.M31

4

RAS#

CAS#

CKE0

CKE1

EVENT#

VDDSPD

NC#1

NC#2

NC#/TEST

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

CS0#

CS1#

CK0#

CK1#

NP1

NP1

NP2

NP2

110

113

WE#

115

114

121

73

74

101

CK0

103

102

CK1

104

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

200

SDA

202

SCL

198

199

SA0_DIMA

197

SA0

SA1_DIMA

201

SA1

77

122

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

44

VSS

48

VSS

49

VSS

54

VSS

55

VSS

60

VSS

61

VSS

65

VSS

66

VSS

71

VSS

72

VSS

127

VSS

128

VSS

133

VSS

134

VSS

138

VSS

139

VSS

144

VSS

145

VSS

150

VSS

151

VSS

155

VSS

156

VSS

161

VSS

162

VSS

167

VSS

168

VSS

172

VSS

173

VSS

178

VSS

179

VSS

184

VSS

185

VSS

189

VSS

190

VSS

195

VSS

196

VSS

205

VSS

206

VSS

1D35V_S3

M_A_RAS# [5]

M_A_WE# [5]

M_A_CAS# [5]

M_A_DIMA_CS#0 [5]

M_A_DIMA_CS#1 [5]

M_A_DIMA_CKE0 [5]

M_A_DIMA_CKE1 [5]

M_A_DIMA_CLK_DD R0 [5]

M_A_DIMA_CLK_DD R#0 [5]

M_A_DIMA_CLK_DD R1 [5]

M_A_DIMA_CLK_DD R#1 [5]

PCH_SMBDAT A [18,67,96]

PCH_SMBCLK [18,67,96]

X02 0414

0R0402-PAD-2- GP

0R0402-PAD-2- GP

3D3V_S0

12

C1203

C1203

DY

DY

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

1D35V_S3

X01 0224

C1210

C1210

Layout Note:

Place these Caps near SO-DIMMA.

3

12

R1202

R1202

BDW CAP

BDW CAP

C1207

C1207

12

12

TC1201

TC1201

DY

DY

BDW CAP

BDW CAP

ST330U2VDM-4-GP

ST330U2VDM-4-GP

12

12

C1211

C1211

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

DDR_PG_CT RL[4]

Q1201 must use Vth=1V.

SC2D2U10V3KX-1GP

SC2D2U10V3KX-1GP

12

12

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

X02 0414

Note:

SA0 DIM0 = 0, SA1_DIM0 = 0

12

SO-DIMMA SPD Address is 0xA0

R1201

R1201

0R0402-PAD-2- GP

0R0402-PAD-2- GP

SO-DIMMA TS Address is 0x30

BDW CAP

BDW CAP

C1208

SC2D2U6D3V2MX-GP

C1208

SC2D2U6D3V2MX-GP

C1209

SC2D2U10V3KX-1GP

C1209

SC2D2U10V3KX-1GP

12

12

12

C1213

C1213

C1212

C1212

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

R1205

R1205

1 2

0R0402-PAD-2- GP

0R0402-PAD-2- GP

12

12

C1221

C1221

C1222

C1220

C1220

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

C1222

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

1D35V_S3

S D

3rd = 84.3K329.031

3rd = 84.3K329.031

G

Q1201

Q1201

FDV301N-NL -GP

FDV301N-NL -GP

Vth = 1V max.

D

D

84.00301.A31

84.00301.A31

2nd = 84.05067.031

2nd = 84.05067.031

2

5V_S5

12

12

DY

DY

R1208

R1208

220KR2J-L2-GP

220KR2J-L2-GP

DDR_VTT_P G_CTRLDDR_PG_CT RL_R

R1204

R1204

2MR2-GP

2MR2-GP

1D35V_S3

D

G

Q1202

Q1202

2N7002K-2-GP

2N7002K-2-GP

84.2N702.J31

84.2N702.J31

2ND = 84.2N702.031

2ND = 84.2N702.031

S

M_A_B_DIMM_ODT

DDR_VTT_P G_CTRL [49]

R1206 66D5R2F-GPR1206 66D5R2F-GP

1 2

R1207 66D5R2F-GPR1207 66D5R2F-GP

1 2

<Core Desig n>

<Core Desig n>

<Core Desig n>

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Date: Sheet

Date: Sheet

Date: Sheet

Tuesday, June 17, 2014

Tuesday, June 17, 2014

Tuesday, June 17, 2014

DDR3-SODIMM1

DDR3-SODIMM1

DDR3-SODIMM1

Cottonwood

Cottonwood

Cottonwood

M_A_DIMA_ODT0

M_A_DIMA_ODT1

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

12 104

12 104

1

12 104

of

of

of

A00

A00

A00

5

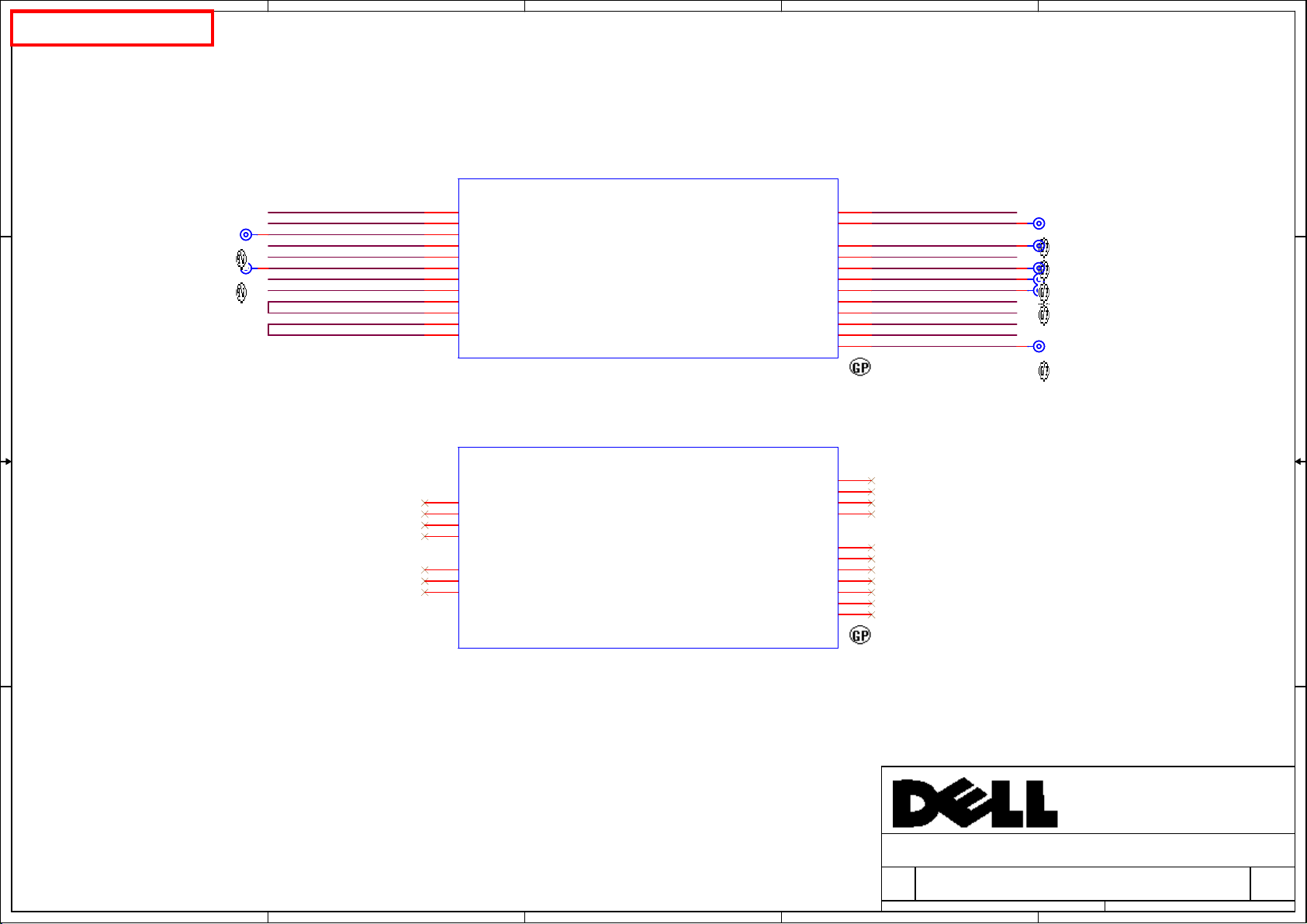

D D

C C

4

3

2

1

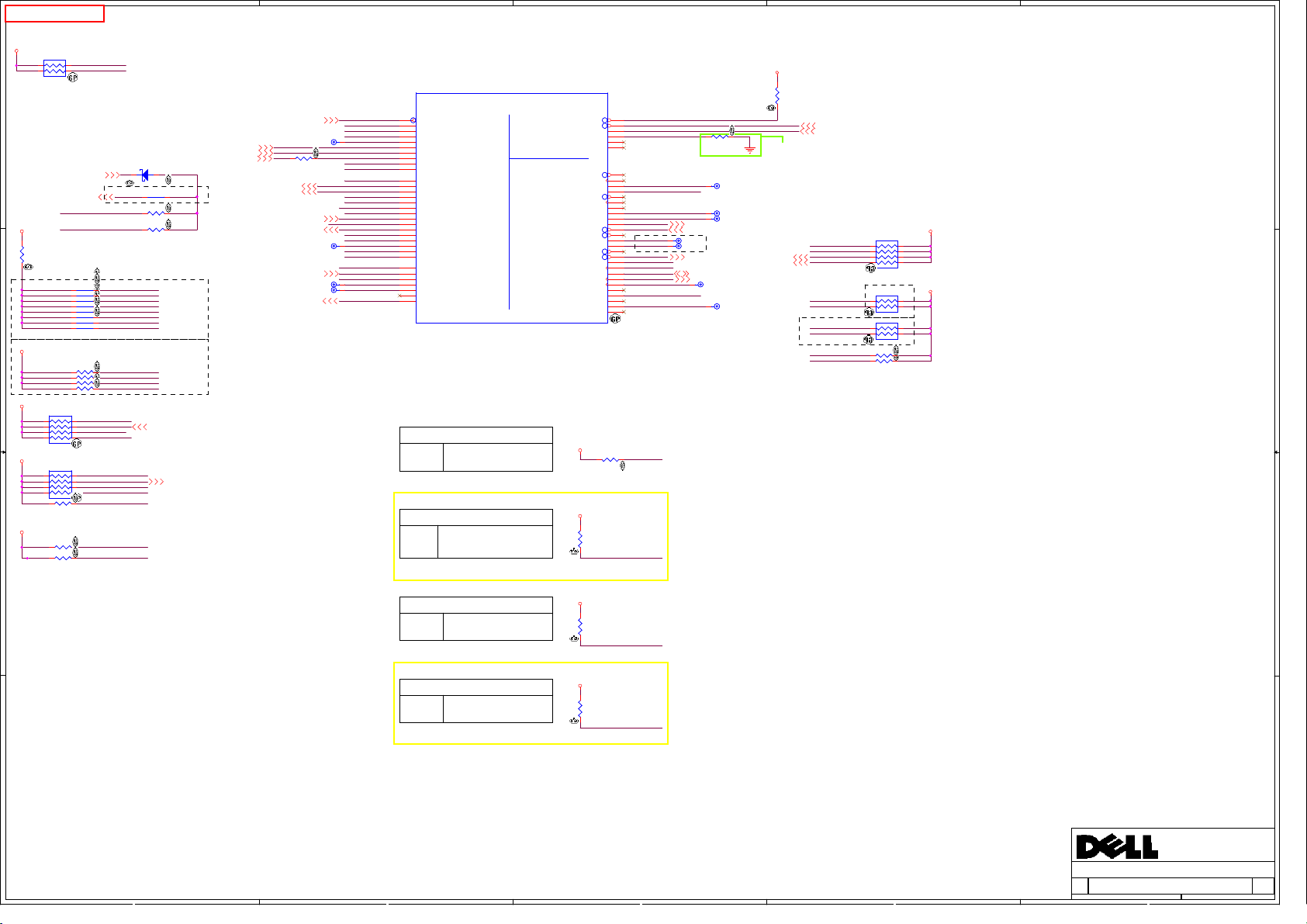

(Blanking)

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

(Reserved)DDR3-SODIMM2

(Reserved)DDR3-SODIMM2

(Reserved)DDR3-SODIMM2

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Tuesday, June 17, 2 014

Tuesday, June 17, 2 014

Tuesday, June 17, 2 014

Date: Sheet

Date: Sheet

Date: Sheet

Cottonwood

Cottonwood

Cottonwood

Taipei Hsien 221, Taiwan, R.O.C.

13 104

13 104

13 104

of

of

1

of

A00

A00

A00

5

D D

4

3

2

1

C C

(Blanking)

B B

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

(Reserved)_SODIMM _SODIMM4

(Reserved)_SODIMM _SODIMM4

(Reserved)_SODIMM _SODIMM4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Cottonwood

Cottonwood

Cottonwood

14 104Tuesday, June 17, 2014

14 104Tuesday, June 17, 2014

14 104Tuesday, June 17, 2014

1

A00

A00

A00

5

4

3

2

1

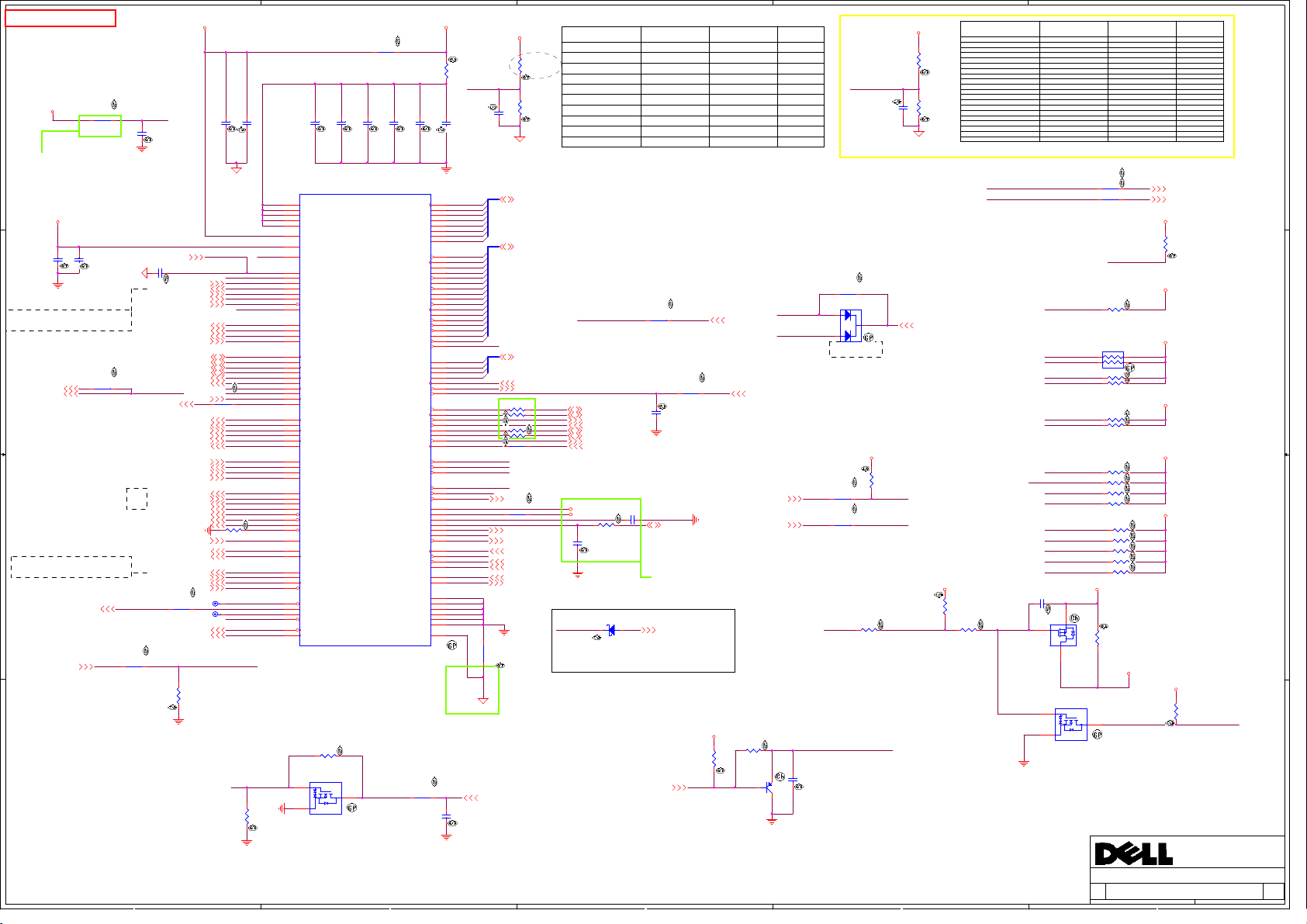

SSID = CPU

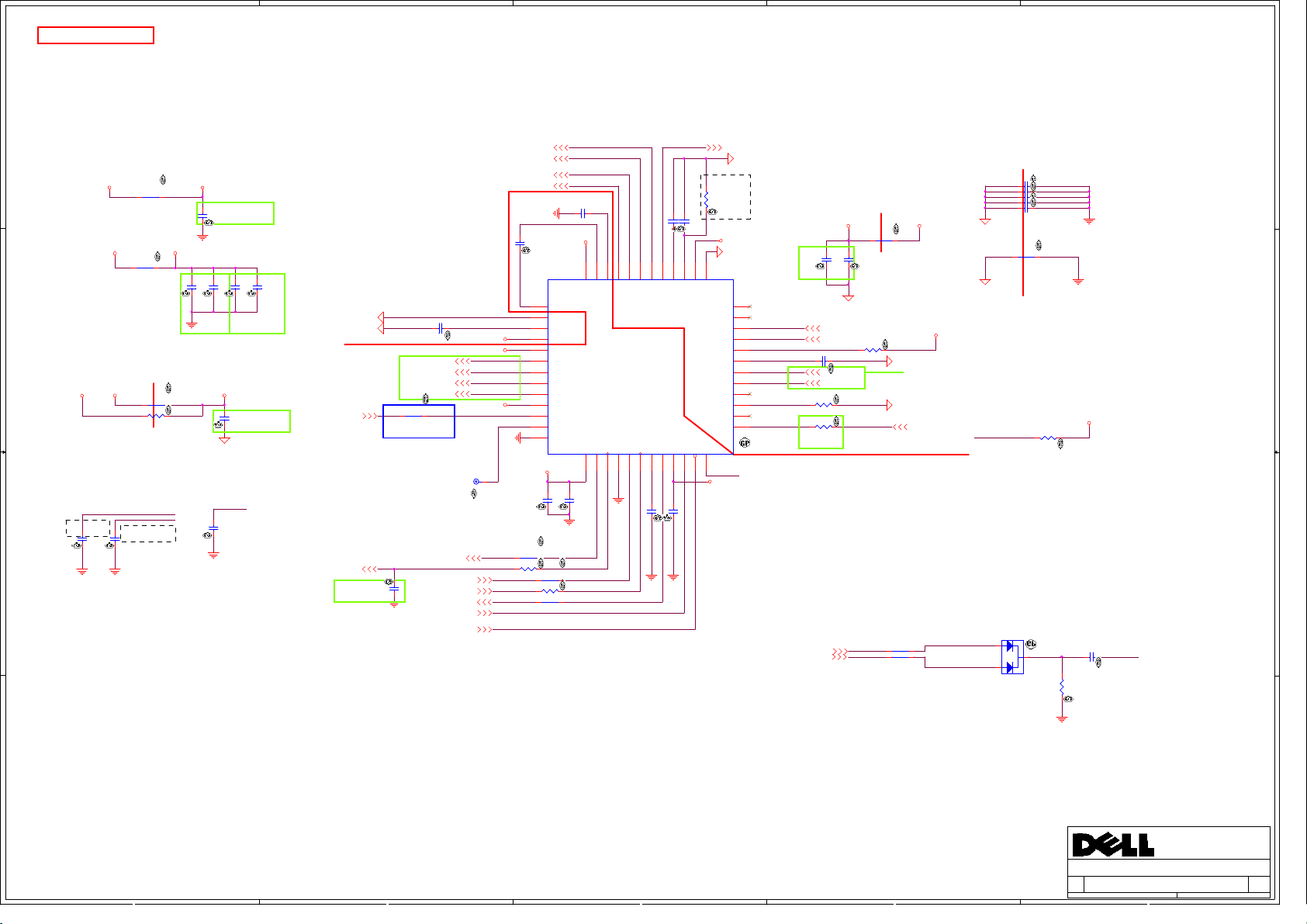

D D

3D3V_S0

1

23

RN1501

RN1501

SRN2K2J -1-GP

HSW_ULT_DDR3L

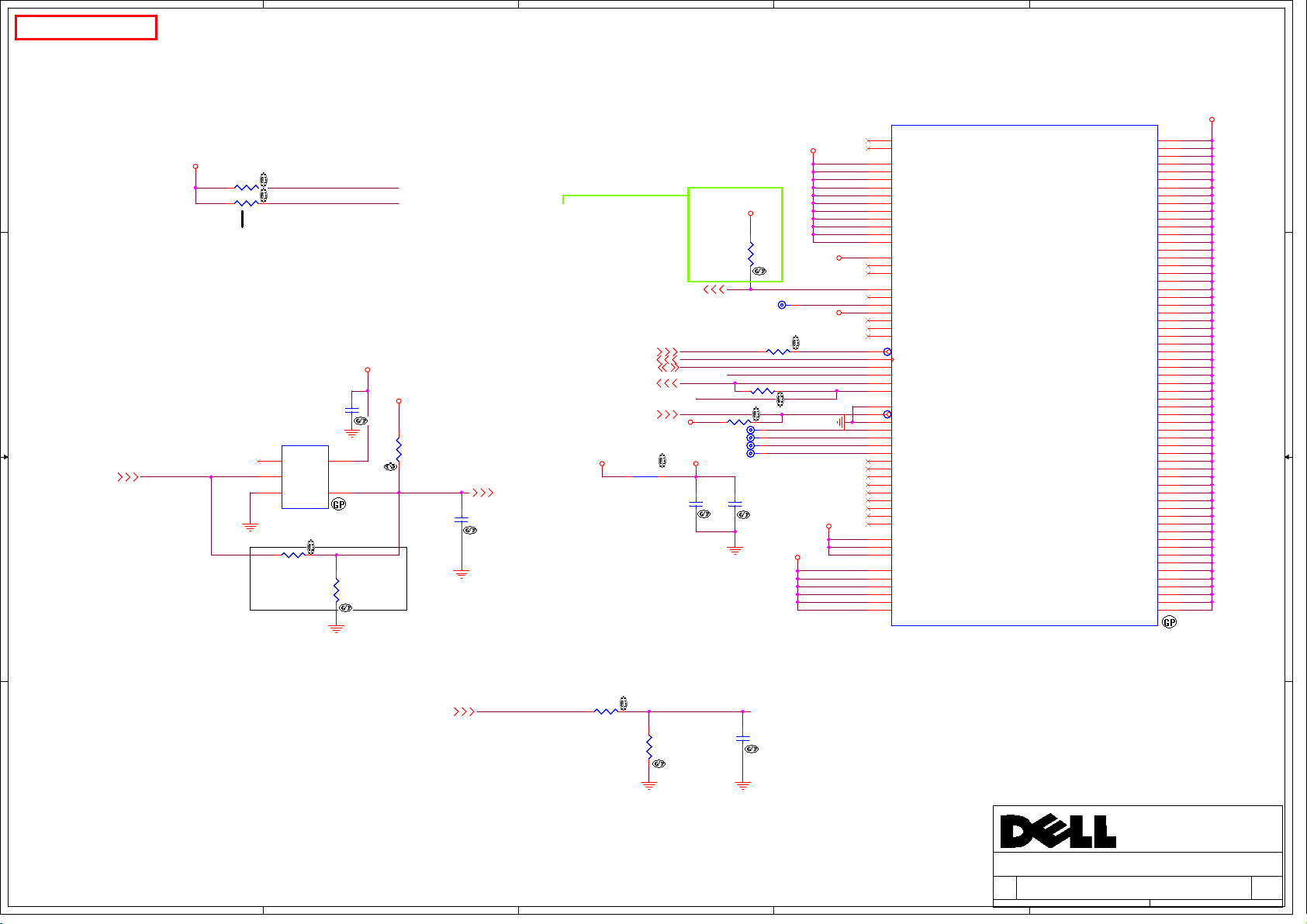

eDP SIDEBAND

eDP SIDEBAND

PCIE

PCIE

HSW_ULT_DDR3L

DISPLAY

DISPLAY

CPU1I

CPU1I

L_BKLT_ CTRL[5 2]

L_BKLT_ EN[24]

EDP_VDD _EN[52]

X02 0414

PIRQA#[19]

C C

3D3V_S0

SRN10KJ -6-GP

SRN10KJ -6-GP

1

2

3

4 5

RN1505

RN1505

SRN10KJ -6-GP

SRN10KJ -6-GP

1

2

3

4 5

RN1506

B B

RN1506

8

7

6

8

7

6

PIRQD#

PIRQB#

MCP_GPIO5 4

MCP_GPIO5 2

PIRQC#

MCP_GPIO1 7 [20 ]

MCP_GPIO3 5 [19 ]

HDD_FAL L_INT[66,67]

R1501

R1501

1 2

0R0402-P AD-2-GP

0R0402-P AD-2-GP

MCP_GPIO5 1[20]

SENSOR_ HUB_RST#[66]

TP1501TP1501

MCP_GPIO5 5[19,20]

1

PIRQB#

PIRQC#

PIRQD#

PCI_PME#

MCP_GPIO5 5

MCP_GPIO5 2

MCP_GPIO5 4

B8

EDP_BKLCTL

A9

EDP_BKLEN

C6

EDP_VDDEN

U6

PIRQA#/GPIO77

P4

PIRQB#/GPIO78

N4

PIRQC#/GPIO79

N2

PIRQD#/GPIO80

AD4

PME#

U7

GPIO55

L1

GPIO52

L3

GPIO54

R5

GPIO51

L4

GPIO53

HASW ELL-6-GP-U

HASW ELL-6-GP-U

9 OF 19

9 OF 19

HDMI

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

SRN2K2J -1-GP

4

DDPC_CT RLDATA

HDMI_PCH_ DET [54]

EDP_HPD [52]

PCH_HDM I_CLK [54]

PCH_HDM I_DATA [54]

TP1502TP1502

1

https://t.me/schematicslaptop

https://t.me/biosarchive

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

PCH ( EDP/GPIO/DDI )

PCH ( EDP/GPIO/DDI )

PCH ( EDP/GPIO/DDI )

Cottonwood

Cottonwood

Cottonwood

15 104Tuesday, June 17, 2 014

15 104Tuesday, June 17, 2 014

15 104Tuesday, June 17, 2 014

of

of

1

of

A00

A00

A00

5

4

3

2

1

SSID = PCH

HSW_ULT_DDR3L

CPU1K

CPU1K

F10

PERN5_L0

E10

https://t.me/schematicslaptop

D D

C C

B B

https://t.me/biosarchive

PCIE_PRX_ WLANTX_N3[63]

PCIE_PRX_ WLANTX_P3[63]

PCIE_PTX_ WLANRX_N3 _C[63]

PCIE_PTX_ WLANRX_P3 _C[63]

+V1.05S_ AUSB3PLL

C1601

C1601

C1602 SCD1U10 V2KX-5GPC1602 SCD1U10V2K X-5GP

Layout Note:

1. PCIE_RCOMP/ PCIE_IREF trac e width=12~15mi l

2. Isolation Sp acing: 12mil

3. Total trace length<500mil

1 2

1 2

R1601

R1601

3KR2F-GP

3KR2F-GP

1 2

SCD1U10 V2KX-5GP

SCD1U10 V2KX-5GP

PCIE_PTX_ WLANRX_N3

PCIE_PTX_ WLANRX_P3

PCIE_RCOM P

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PETN5_L1

A23

PETP5_L1

H10

PERN5_L2

G10

PERP5_L2

B21

PETN5_L2

C21

PETP5_L2

E6

PERN5_L3

F6

PERP5_L3

B22

PETN5_L3

A21

PETP5_L3

G11

PERN3

F11

PERP3

C29

PETN3

B30

PETP3

F13

PERN4

G13

PERP4

B29

PETN4

A29

PETP4

G17

PERN1/USB3RN3

F17

PERP1/USB3RP3

C30

PETN1/USB3TN3

C31

PETP1/USB3TP3

F15

PERN2/USB3RN4

G15

PERP2/USB3RP4

B31

PETN2/USB3TN4

A31

PETP2/USB3TP4

E15

RSVD#E15

E13

RSVD#E13

A27

PCIE_RCOMP

B27

PCIE_IREF

WLAN

HASW ELL-6-GP-U

HASW ELL-6-GP-U

HSW_ULT_DDR3L

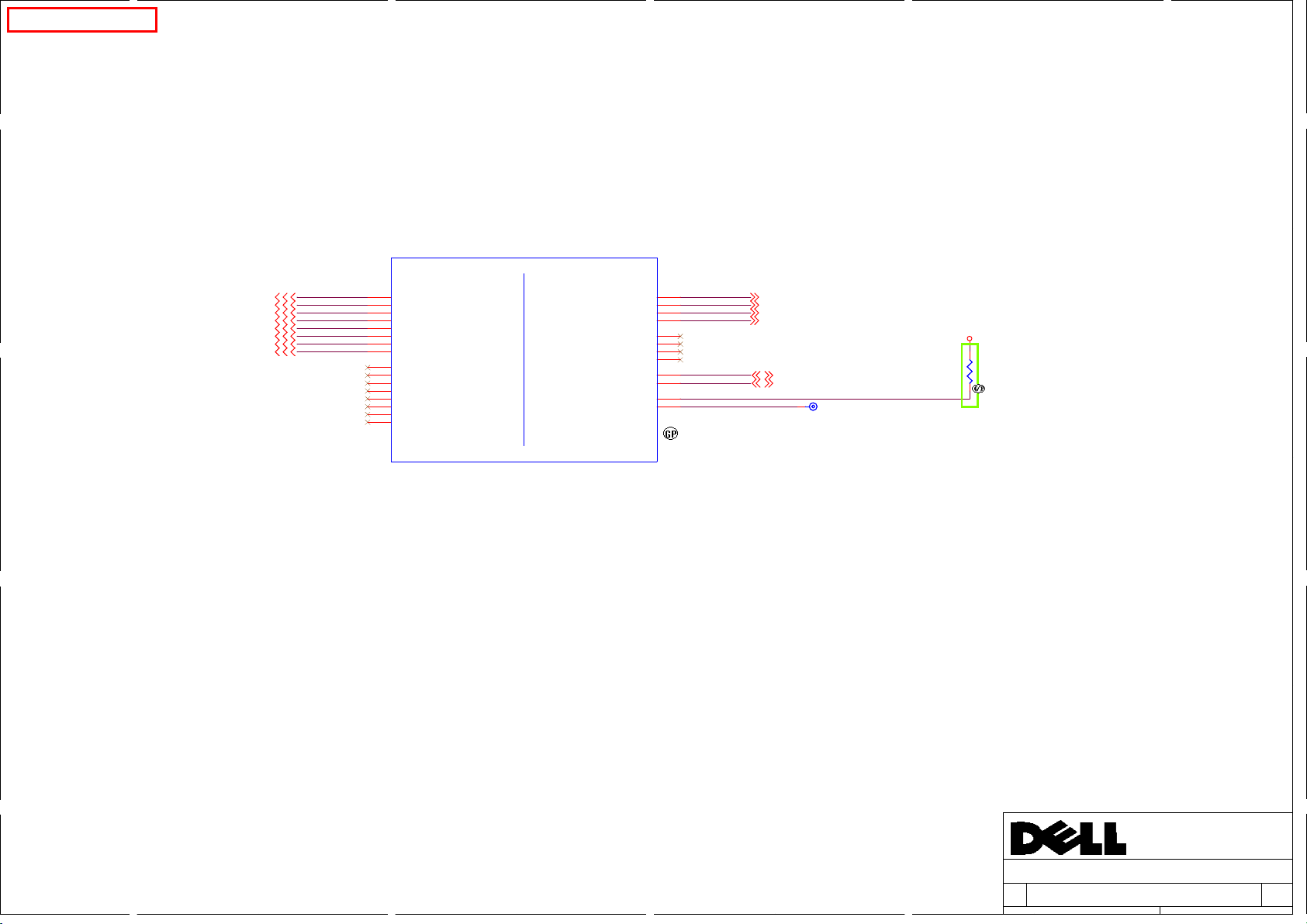

PCIE USB

PCIE USB

11 OF 19

11 OF 19

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS#

USBRBIAS

RSVD#AN10

RSVD#AM10

OC0/GPIO40#

OC1/GPIO41#

OC2/GPIO42#

OC3/GPIO43#

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USB_COM P

USB_OC# 0_1

USB_OC# 2_3

USB_OC# 4_5

USB_OC# 6_7

PM_SUSW ARN#_R[17]

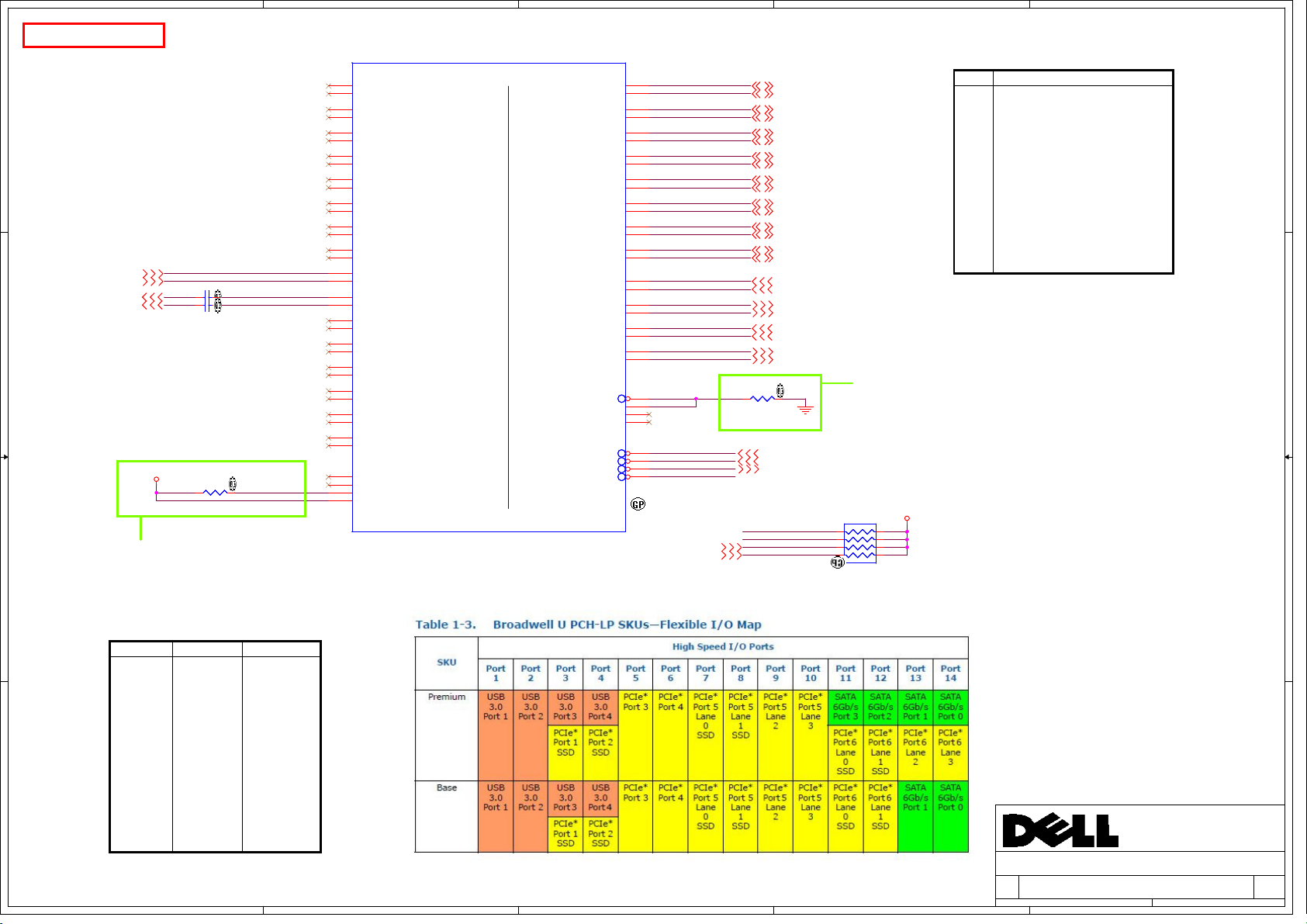

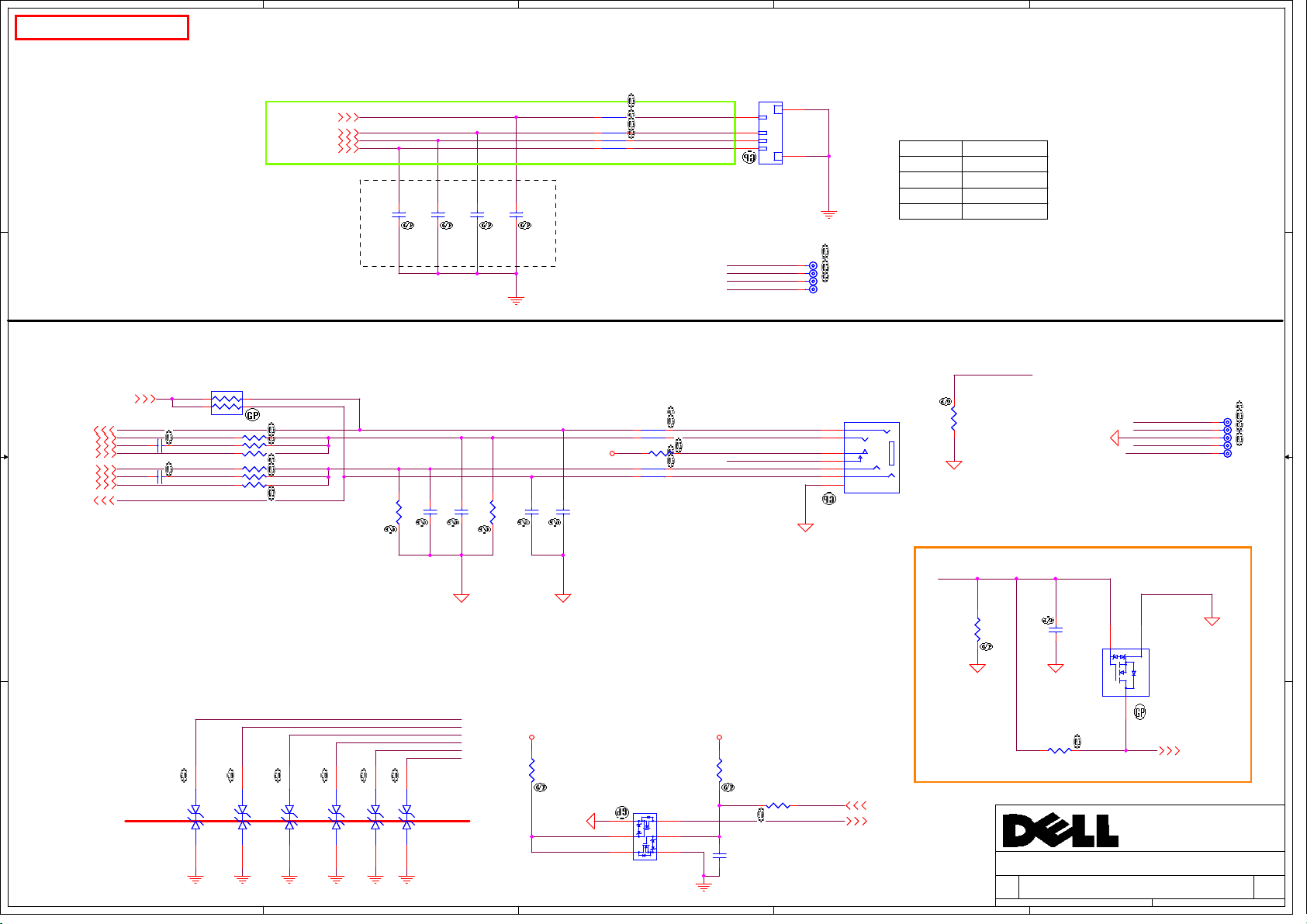

USB 2.0 Table

Pair

USB_PN0 [34]

USB_PP0 [3 4]

USB_PN1 [35]

USB_PP1 [3 5]

USB_PN2 [63]

USB_PP2 [6 3]

USB_PN3 [66]

USB_PP3 [6 6]

USB_PN4 [52]

USB_PP4 [5 2]

USB_PN5 [63]

USB_PP5 [6 3]

USB_PN6 [52]

USB_PP6 [5 2]

USB_PN7 [63]

USB_PP7 [6 3]

USB3_PR X_CTX_N0 [34 ]

USB3_PR X_CTX_P0 [34]

USB3_PT X_CRX_N0 [34 ]

USB3_PT X_CRX_P0 [34]

USB3_PR X_CTX_N1 [34 ]

USB3_PR X_CTX_P1 [34]

USB3_PT X_CRX_N1 [34 ]

USB3_PT X_CRX_P1 [34]

Layout Note:

1 2

R1602

R1602

22D6R2F -L1-GP

22D6R2F -L1-GP

USB_OC# 0_1 [18,35]

USB_OC# 2_3 [63]

USB_OC# 4_5 [20]

USB_OC# 2_3

MCP_GPIO7 3[18]

USB_OC# 6_7

1. USB_COMP usi ng 50 ohm sing le-ended impeda nce

2. Isolation Sp acing :15mil

3. Total trace length<500mil

RN1601

RN1601

8

7

6

SRN10KJ -6-GP

SRN10KJ -6-GP

3D3V_S5 _PCH

1

2

3

45

Device

USB3.0 port2

0

USB3.0 Port1 (Debug Port)

1

USB2.0 Port3 (IOBD)

2

Sensor HUB

3

CAMERA

4

WLAN

5

Touch Panel

6

Card Reader

7

#515621

PCIE Table

Port

1

2

3

4

5(L0~L3)

A A

6(L3)

6(L2)

6(L0~L1)

5

Device

N/A

N/A

WLAN

N/A

N/A

HDD

N/A

N/A

Share BUS

USB3.0_3

USB3.0_4

SATA0

SATA1

GPU GPU GPU GPU

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

GPU GPU GPU GPU

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

PCH (PCIE/USB)

PCH (PCIE/USB)

PCH (PCIE/USB)

Cottonwood

Cottonwood

Cottonwood

16 104Tuesday, June 17, 2 014

16 104Tuesday, June 17, 2 014

16 104Tuesday, June 17, 2 014

1

A00

A00

of

of

of

A00

5

4

3

2

1

SSID = PCH

https://t.me/schematicslaptop

https://t.me/biosarchive

RN1703

RN1703

1

D D

R1717 10KR2J-3-GP

R1717 10KR2J-3-GP

XDP_DBR ESET#[96]

SYS_PW ROK[24,96]

PCH_PW ROK[24,26,36]

C C

PM_SUSW ARN#_R[16]

PM_PW RBTN#[24,96]

AC_PRES ENT[24]

AC_PRES ENT

12

DY

DY

EC1707

EC1707

SCD1U10V2KX-5GP

DY

DY

12

EC1702

EC1702

4

DY

DY

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

SCD1U10V2KX-5GP

(CRB#514469)

12

DY

DY

EC1703

EC1703

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

5

BATLOW #

AC_PRES ENT

PM_SUS_ STAT#

3D3V_S5

RN1701

RN1701

2 3

1

SRN10KJ -5-GP

B B

A A

SRN10KJ -5-GP

R1703

R1703

1 2

1KR2J-1-G P

1KR2J-1-G P

3D3V_S5 _PCH

1 2

R1724 10KR2J-3 -GP

R1724 10KR2J-3 -GP

DY

DY

EC1706

EC1706

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

2 3

SRN10KJ -5-GP

SRN10KJ -5-GP

DY

DY

R1706

R1706

0R0402-P AD-2-GP

0R0402-P AD-2-GP

PCH_W AKE#

12

DY

DY

EC1704

EC1704

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

12

4

12

EC1705

EC1705

3D3V_S0

12

1 2

X02 0414

PLT_RST #[24,63,65]

100KR2J -1-GP

100KR2J -1-GP

XDP_DBR ESET#

12

DY

DY

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

PM_RSMR ST#

PM_PCH_ PWROK

SYS_PW ROK

R1701

R1701

10KR2J-3 -GP

10KR2J-3 -GP

R1715

R1715

SYS_PW ROK

PLT_RST #

PCH_PW ROK

KBC_DPW ROK

R1707

R1707

1 2

0R0402-P AD-2-GP

0R0402-P AD-2-GP

1

TP1706TP1706

1

TP1705TP1705

X02 0414

1 2

0R0402-P AD-2-GP

0R0402-P AD-2-GP

12

12

DY

DY

DY

DY

PM_SUSA CK#_R

XDP_DBR ESET# PCH_DPW ROK PM_RSMR ST#

SYS_PW ROK

PM_PCH_ PWROK

MPWR OK

PCI_PLTRS T#

PM_RSMR ST#

PM_SUSW ARN#_R

PM_PW RBTN#

AC_PRES ENT

BATLOW #

PCH_SLP _S0#

PCH_SLP _WLAN#

PCI_PLTRS T#

R1713

R1713

C1701

C1701

SC220P5 0V2KX-3GP

SC220P5 0V2KX-3GP

4

CPU1H

CPU1H

AK2

SUSACK#

AC3

SYS_RESET#

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST#

AW6

RSMRST#

AV4

SUSWARN#/SUSPWRDNACK#/GPIO30

AL7

PWRBTN#

AJ8

ACPRESENT/GPIO31

AN4

BATLOW#/GPIO72

AF3

SLP_S0#

AM5

SLP_WLAN#/GPIO29

HASW ELL-6-GP-U

HASW ELL-6-GP-U

PM_SUSA CK#[24]

PM_SUSW ARN#[24]

HSW_ULT_DDR3L

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

SYSTEM POWER MANAGEMENT

NON DS3

NON DS3

R1708

R1708

1 2

0R2J-2-GP

0R2J-2-GP

SRN0J-6-G P

SRN0J-6-G P

1

4

2 3

DS3

DS3

RN1702

RN1702

3D3V_AU X_S5

R1726

R1726

10KR2J-3 -GP

10KR2J-3 -GP

1 2

3V_5V_P OK#

SUS_STAT#/GPIO61

PM_SUSA CK#_RPM_SUSW ARN#_R

PM_SUSA CK#_R

PM_SUSW ARN#_R

R1727

R1727

100KR2J -1-GP

100KR2J -1-GP

1 2

NON DS3

NON DS3

Q1701

Q1701

5

6

2N7002K DW-GP

2N7002K DW-GP

84.2N702.A3F

84.2N702.A3F

2nd = 84.2N702.E3F

2nd = 84.2N702.E3F

3rd = 75.00601.07C

3rd = 75.00601.07C

4th = 84.DMN66.03F

4th = 84.DMN66.03F

3

PCH strap pin:

DSWODVREN

8 OF 19

8 OF 19

DSWVRMEN

DPWROK

WAKE#

CLKRUN#/GPIO32

SUSCLK/GPIO62

SLP_S5#/GPIO63

SLP_S4#

SLP_S3#

SLP_A#

SLP_SUS#

SLP_LAN#

34

2

1

On Die DSW VR Enable

Low = Disable

High = Enable (default)

*

DSWO DVREN

AW7

AV5

PCH_W AKE#

AJ5

PM_CLKR UN#

V5

PM_SUS_ STAT#

AG4

SUS_CLK _PCH

AE6

PM_SLP_ S5#

AP5

PM_SLP_ S4#

AJ6

PM_SLP_ S3#

AT4

PM_SLP_ A#

AL5

PM_SLP_ SUS#

AP4

PM_SLP_ LAN#

AJ7

PCH_DPW ROK

A00 0609

1KR2J-1-G P

1KR2J-1-G P

R1702

PM_RSMR ST#

3V_5V_P OK_C

R1702

1 2

R1728

R1728

1 2

NON DS3

NON DS3

0R2J-2-GP

0R2J-2-GP

1 2

0R0402-P AD-2-GP

0R0402-P AD-2-GP

R1704

R1704

0R2J-2-GP

0R2J-2-GP

NON DS3

NON DS3

1 2

1 2

DY

DY

R1705 0R2 J-2-GP

R1705 0R2 J-2-GP

R1705: DY for O BFF disable

1

1

1

1

1 2

0R0402-P AD-2-GP

0R0402-P AD-2-GP

TP1702TP1702

1 2

0R0402-P AD-2-GP

0R0402-P AD-2-GP

TP1703TP1703

TP1704TP1704

TP1707TP1707

R1709

R1709

R1710

R1710

A00 0604

A00 0609

R1718

R1718

1 2

0R0402-P AD-2-GP

0R0402-P AD-2-GP

R1725

R1725

DS3

DS3

100KR2F -L1-GP

100KR2F -L1-GP

1 2

RSMRST# _KBC [24]

3V_5V_P OK [45]

R1729

R1729

PM_SLP_ SUS#

2

DSWO DVREN

PCIE_W AKE# [20,24 ]

PM_CLKR UN#_EC [24]

SUS_CLK [24]

PM_SLP_ S4# [24,49]

PM_SLP_ S3# [24,36,48,4 9,51]

PM_SLP_ SUS# [24,38 ]

KBC_DPW ROK [24]

PM_CLKR UN#

SUS_CLK _PCH

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

R1720

R1720

330KR2J -L1-GP

330KR2J -L1-GP

1 2

1 2

DY

DY

R1721

R1721

330KR2J -L1-GP

330KR2J -L1-GP

R1714

R1714

8K2R2F-1 -GP

8K2R2F-1 -GP

1 2

RTC_AUX _S5

3D3V_S0

EC1701

SC4D7P5 0V2CN-1GP

SC4D7P5 0V2CN-1GP

PCH (PM)

PCH (PM)

PCH (PM)

Cottonwood

Cottonwood

Cottonwood

EC1701

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

17 104Tuesday, June 17, 2 014

17 104Tuesday, June 17, 2 014

17 104Tuesday, June 17, 2 014

1

DY

DY

1 2

A00

A00

of

of

of

A00

SSID = PCH

5

4

3

2

1

D D

3D3V_S0

RN1801

RN1801

SRN10KJ-5-GP

SRN10KJ-5-GP

LPC_AD1

LPC_AD2

CLK_PCIE_WLAN_REQ3#

4

Based on the swap report.

RN1806

RN1806

8

7

6

SRN0J-7-GP-U

SRN0J-7-GP-U

LPC_FRAME#[24,65]

SPI_CLK_R[24,25]

SPI_CS0#_R[24,2 5]

SPI_SI_R[24 ,25]

SPI_SO_R[24,25]

SPI_WP#[25]

SPI_HOLD#[25]

3D3V_S5

1

23

4

MCP_GPIO37 [19 ]

CLK_PCIE_REQ#[19]

LPC_LAD0_PCHLPC_AD0

1

LPC_LAD1_PCH

2

LPC_LAD2_PCH

3

LPC_LAD3_PCHLPC_AD3

45

RN1802

RN1802

SRN1KJ-7-GP

SRN1KJ-7-GP

PCH_SPI_DQ3

PCH_SPI_DQ2

R1801

R1801

0R0402-PAD-2-GP

0R0402-PAD-2-GP

R1807

R1807

0R0402-PAD-2-GP

0R0402-PAD-2-GP

X02 0414

CLK_PCIE_REQ#

CLK_PCIE_REQ#

CLK_PCIE_WLAN_REQ3#

CLK_PCIE_REQ#

CLK_PCIE_REQ#

CLK_PCIE_REQ#

1 2

1 2

1 2

1 2

1 2

1 2

1 2

LPC_LAD0_PCH

LPC_LAD1_PCH

LPC_LAD2_PCH

LPC_LAD3_PCH

LPC_LFRAME#_PCH

PCH_SPI_CLK

R180633R2J-2-GP R180633R2J-2-GP

PCH_SPI_CS0#

PCH_SPI_SI

R18080R0402-PAD-2-GP R18080R0402-PAD-2-G P

PCH_SPI_SO

R18090R0402-PAD-2-GP R18090R0402-PAD-2-G P

PCH_SPI_DQ2

R18110R0402-PAD-2-GP R18110R0402-PAD-2-G P

PCH_SPI_DQ3

R18120R0402-PAD-2-GP R18120R0402-PAD-2-G P

CPU1F

CPU1F

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0#/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1#/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2#/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3#/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4#/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5#/GPIO23

HASWELL-6-GP-U

HASWELL-6-GP-U

CPU1G

CPU1G

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME#

AA3

SPI_CLK

Y7

SPI_CS0#

Y4

SPI_CS1#

AC2

SPI_CS2#

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

HASWELL-6-GP-U

HASWELL-6-GP-U

HSW_ULT_DDR3L

HSW_ULT_DDR3L

WLAN

HSW_ULT_DDR3L

HSW_ULT_DDR3L

LPC

LPC

CLOCK

CLOCK

SIGNALS

SIGNALS

SMBUS

SMBUS

C-LINKSPI

C-LINKSPI

DIFFCLK_BIASREF

CLKOUT_ITPXDP_P

SMBALERT#/GPIO11

SML0ALERT#/GPIO60

SML1ALERT#/PCHHOT#/GPIO73

SML1DATA/GPIO74

6 OF 19

6 OF 19

XTAL24_IN

XTAL24_OUT

RSVD#K21

RSVD#M21

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP#

7 OF 19

7 OF 19

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK/GPIO75

CL_CLK

CL_DATA

CL_RST#

A25

B25

K21

M21

C26

C35

C34

AK8

AL8

AN15

AP15

B35

A35

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

MCP_TESTLOW1

MCP_TESTLOW2

MCP_TESTLOW3

MCP_TESTLOW4

CLK_PCI_LPC_R

CLK_PCI_KBC_R

MCP_GPIO11

SMB_CLK

SMB_DATA

CARD_PWR_EN

SML0_CLK

SML0_DATA

MCP_GPIO73

SML1_CLK

SML1_DATA

TP_CL_CLK

TP_CL_DATA

TP_CL_RST#

R1803 3KR2F-GPR1803 3KR2F-GP

1 2

SRN10KJ-5-GP

SRN10KJ-5-GP

4

RN1803

RN1803

DEBUG

DEBUG

R1804 0R2J-2-GP

R1804 0R2J-2-GP

1 2

R1805 33R2J-2-GPR1805 33R2J-2-GP

1 2

MCP_GPIO73 [16 ]

SML1_CLK [24,26]

SML1_DATA [24,26]

TP1801TP1801

1

TP1802TP1802

1

TP1803TP1803

1

SMB_DATA

84.2N702.A3F

84.2N702.A3F

2nd = 84.2N702.E3F

2nd = 84.2N702.E3F

3rd = 75.00601.07C

3rd = 75.00601.07C

4th = 84.DMN66.03F

4th = 84.DMN66.03F

+V1.05S_AXCK_LCPLL

23

1

4

1

2 3

CLK_PCIE_WLAN_N3[63]

CLK_PCIE_WLAN_P3[63]

CLK_PCIE_WLAN_REQ3#[63]

C C

LPC_AD[3..0][24,65]

B B

LPC_AD[3..0]

DY

12

SRN10KJ-5-GP

SRN10KJ-5-GP

1

23

RN1804

RN1804

EC1801

SC10P50V2JN-4GPDYEC1801

SC10P50V2JN-4GP

DY

12

3D3V_S0

2N7002KDW-GP

2N7002KDW-GP

6

5

Q1801

Q1801

XTAL24_IN

XTAL24_OUT

EC1802

SC10P50V2JN-4GPDYEC1802

SC10P50V2JN-4GP

https://t.me/schematicslaptop

https://t.me/biosarchive

SMB_CLK

X02 0414

0R0402-PAD-2-GP

0R0402-PAD-2-GP

12

CLK_PCI_LPC [65]

CLK_PCI_KBC [24 ]

PCIE_CLK_XDP_N [96]

PCIE_CLK_XDP_P [96]

USB_OC#0_1[16,35]

EC_SCI#[20,24]

1

2

34

R1810

R1810

1 2

R1802

R1802

1MR2J-1-GP

1MR2J-1-GP

23

SML0_DATA

SML0_CLK

SMB_CLK

SMB_DATA

CARD_PWR_EN

MCP_GPIO11

SML1_DATA

SML1_CLK

RN1810

RN1810

4

SRN10KJ-5-GP

SRN10KJ-5-GP

XTAL24_IN_R

4 1

23

1

PCH_SMBDATA [12,67,96]

PCH_SMBCLK [12,67,96]

C1801

C1801

12

SC15P50V2JN-2-GP

SC15P50V2JN-2-GP

X1801

X1801

XTAL-24MHZ-86-GP

XTAL-24MHZ-86-GP

82.30004.891