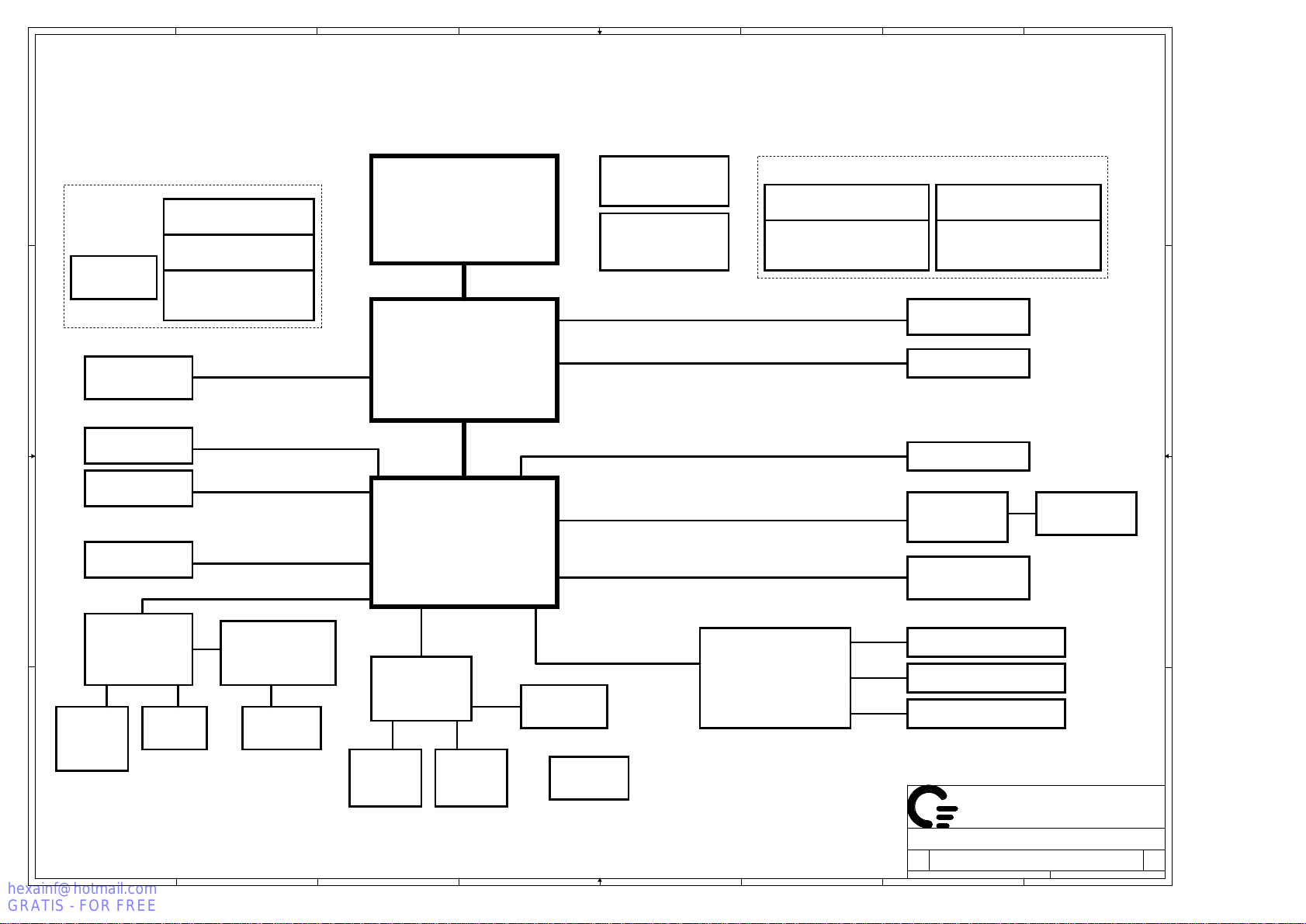

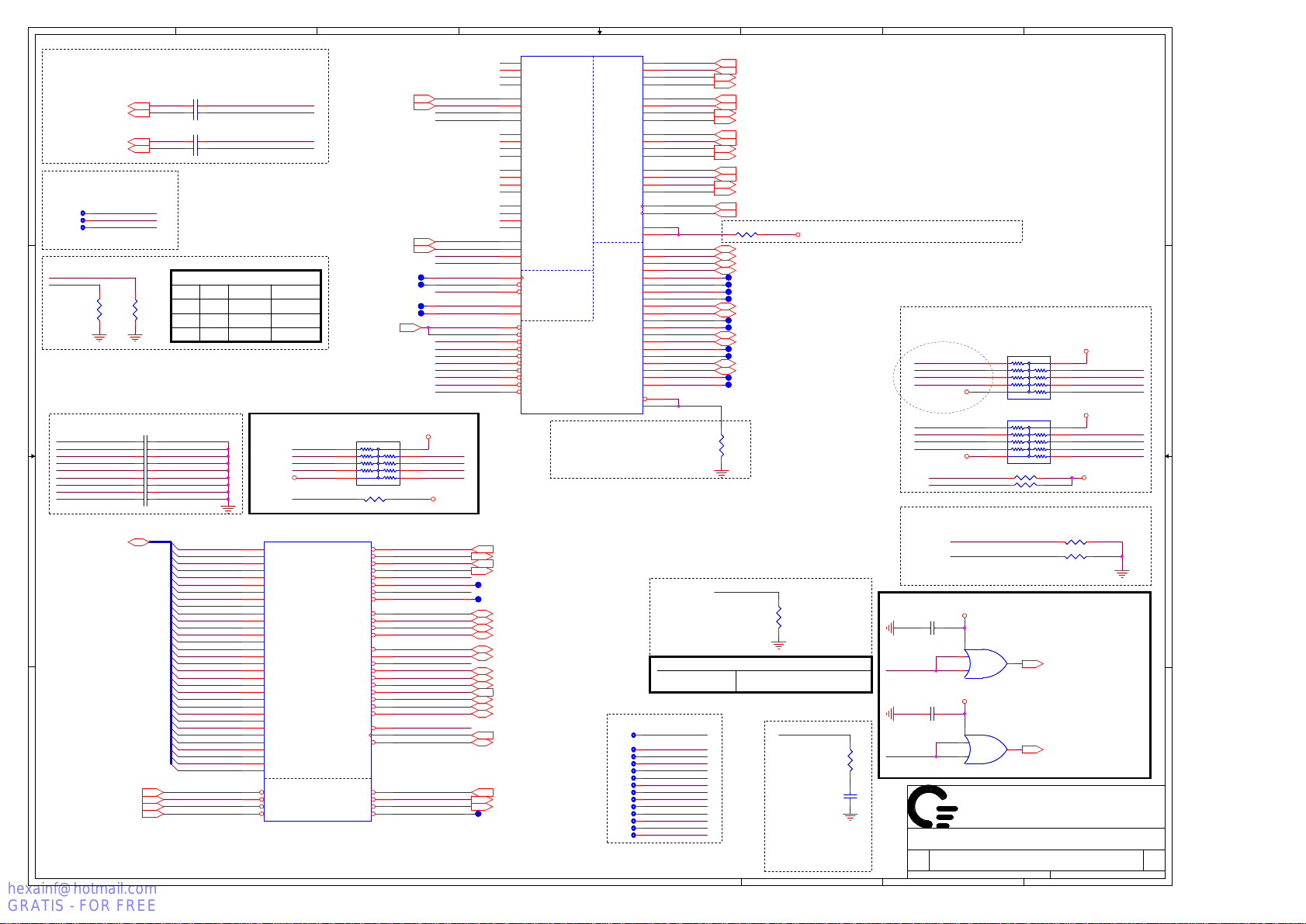

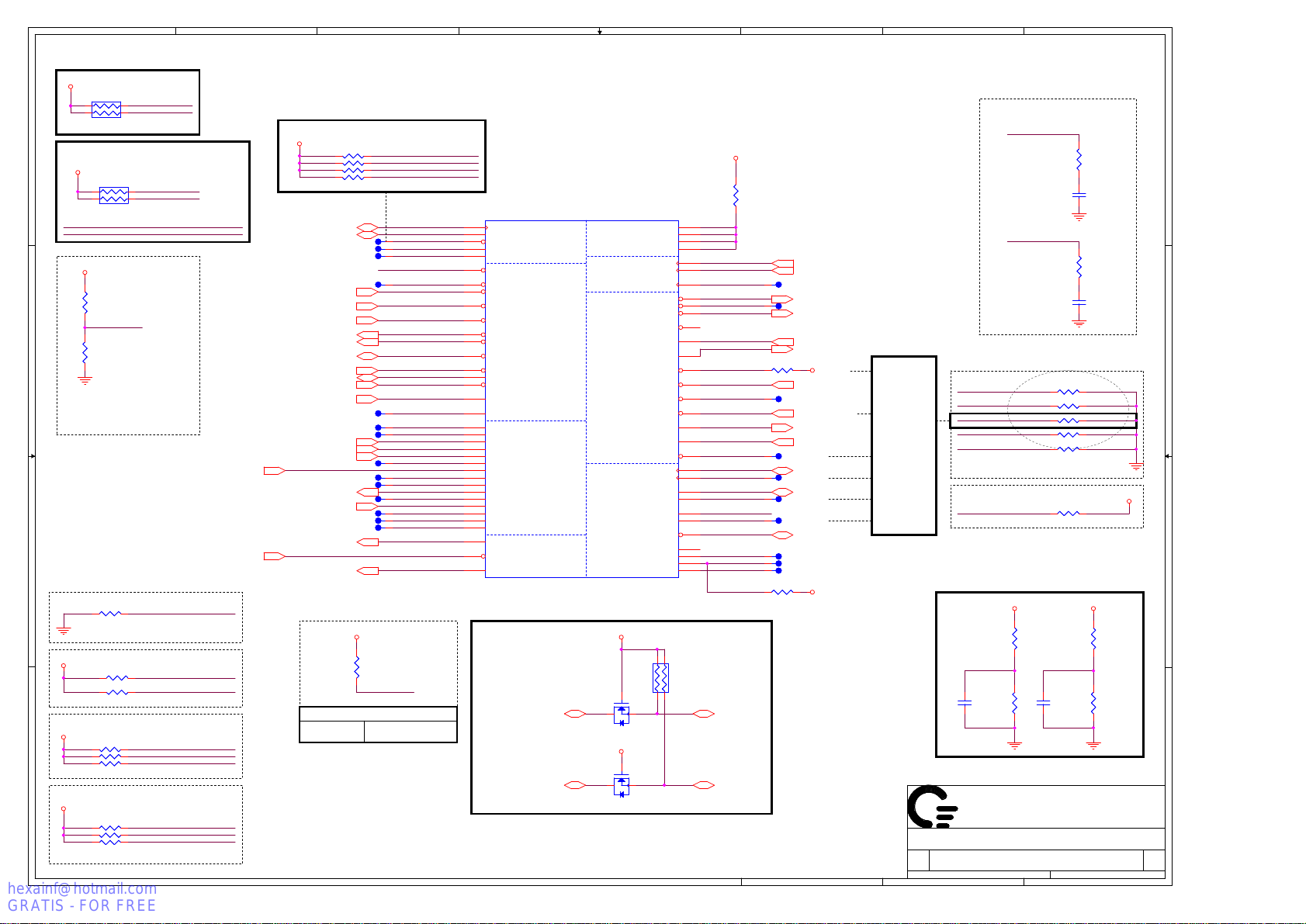

Dell A840, A860, A1088 Schematics

1

hexainf@hotmail.com

GRATIS - FOR FREE

2

3

4

5

6

7

8

VER : 1A

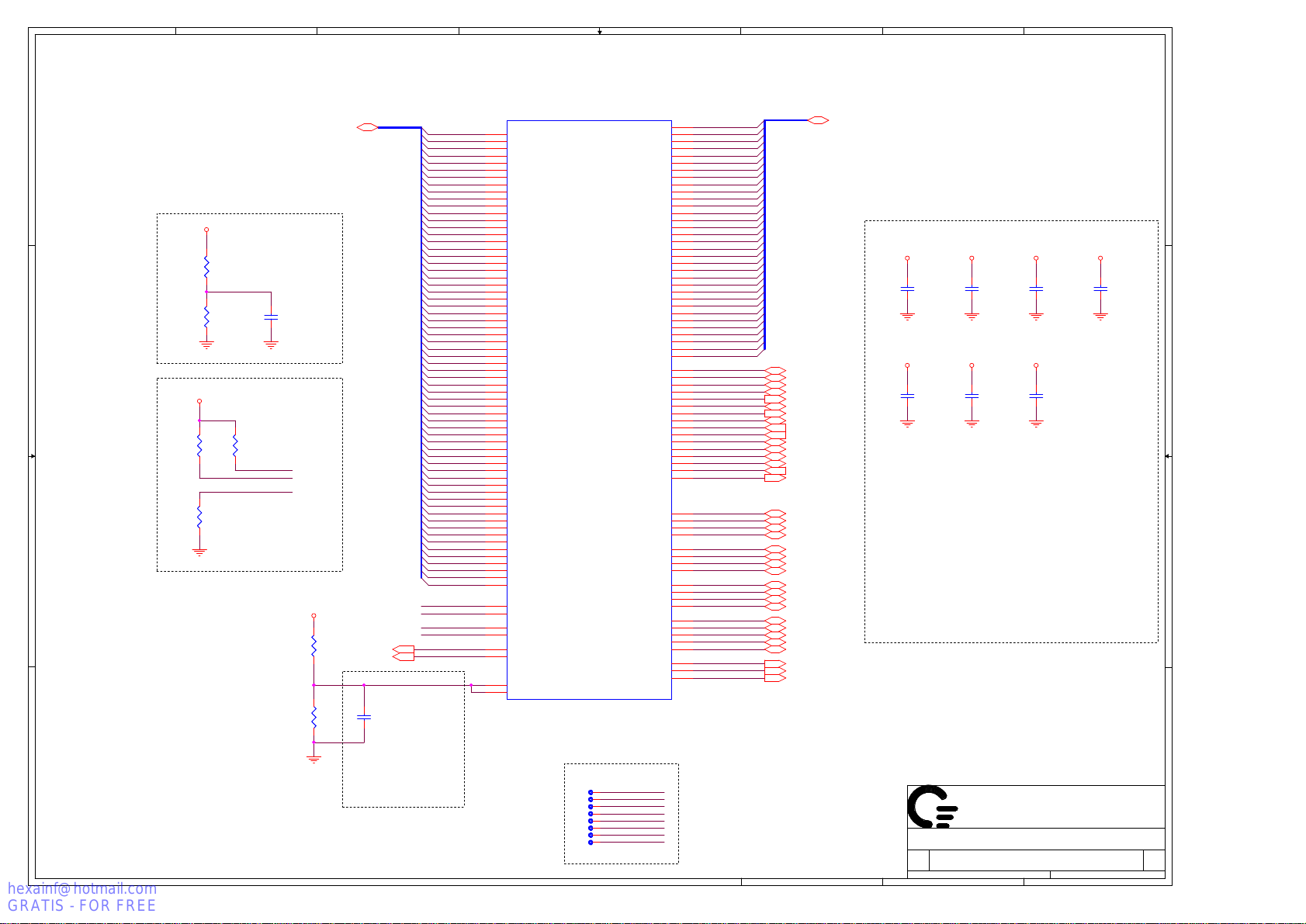

VM9/VM8 Block Diagram

AA

FAN & THERMAL

EMC1423-1-AIZL-TR

CLOCK

SLG8SP513V

(QFN-64)

LVDS

PG 31

PG 17

POWER

AC/BATT

CONNECTOR

PG 42

SYSTEM

RESET CIRCUIT

BATT

CHARGER

RUN POWER SW

+3.3V_SUS/+5V_SUS

+5V/+3.3V/+1.8V

PG 35

PG 36

PG 41

Celeron M540

(478 Pin)

PG 3,4

533 MHz FSB

Crestline

BB

DDR2-SODIMM*2

533 MHZ DDR II

965GM

1299 uFCBGA

VGA

POWER

+1.5V_RUN/+1.05V_VCCP

REGULATOR

+1.8V_SUS/+1.25V_RUN

/+0.9V_DDR_VTT

PG 37

CPU VRREGULATOR

REGULATOR

+3.3V_ALW/+5V_SUS/+15V_ALW

PG 38

Panel Connector

(WXGA)

CRT CONN.

PG 39

PG 40

PG 18

PG 19

PG 15,16

PG 5,6,7,8,9,10

SATA-ODD

PG 28

SATA-HDD

PG 28

CC

Bluetooth

PG 26

SATA

SATA

USB 2.0

IHDA

DMI interface

ICH8-M

676 BGA

PG 11,12,13,14

USB2.0 x 2

PCIE

PCIE

USB conn x 2

RTL8102EL

(10/100)

MINI-CARD

WLAN

PG 34

PG 27

RJ45/Magnetics

PG 34

PG 26

AUDIO/AMP

CX20561-12Z

TPA6017A2

PG 32

Audio SPK

conn 2Wx1

Audio

Jacks x3

PG 32

PG 32

DD

1

MODEM (AMOM)

CX20548-11Z

PG 33

RJ-11conn

PG 33

FLASH

2M bytes

2

LPC

KBC

ITE8502

18X8

PG 23

SPIPS/2

Touchpad

PG 24PG 29

3

Keyboard

USER

INTERFACE

4

PG 29

33MHz PCI

PG 20

3-in-1 Card Reader

PCMCIA

IEEE1394

R5C847

5

PG 20

6

1394

1394 CONN.

Card Reader CONN.

PCMCIA CONN.

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Date:Sheet of

Date:Sheet of

Date:Sheet of

COMPUTER

Schematic Block Diagram

Schematic Block Diagram

Schematic Block Diagram

VM9/VM81A

VM9/VM81A

VM9/VM81A

7

PG 22

PG 21

PG 21

153Friday, July 18, 2008

153Friday, July 18, 2008

153Friday, July 18, 2008

8

1

hexainf@hotmail.com

GRATIS - FOR FREE

2

3

4

5

6

7

8

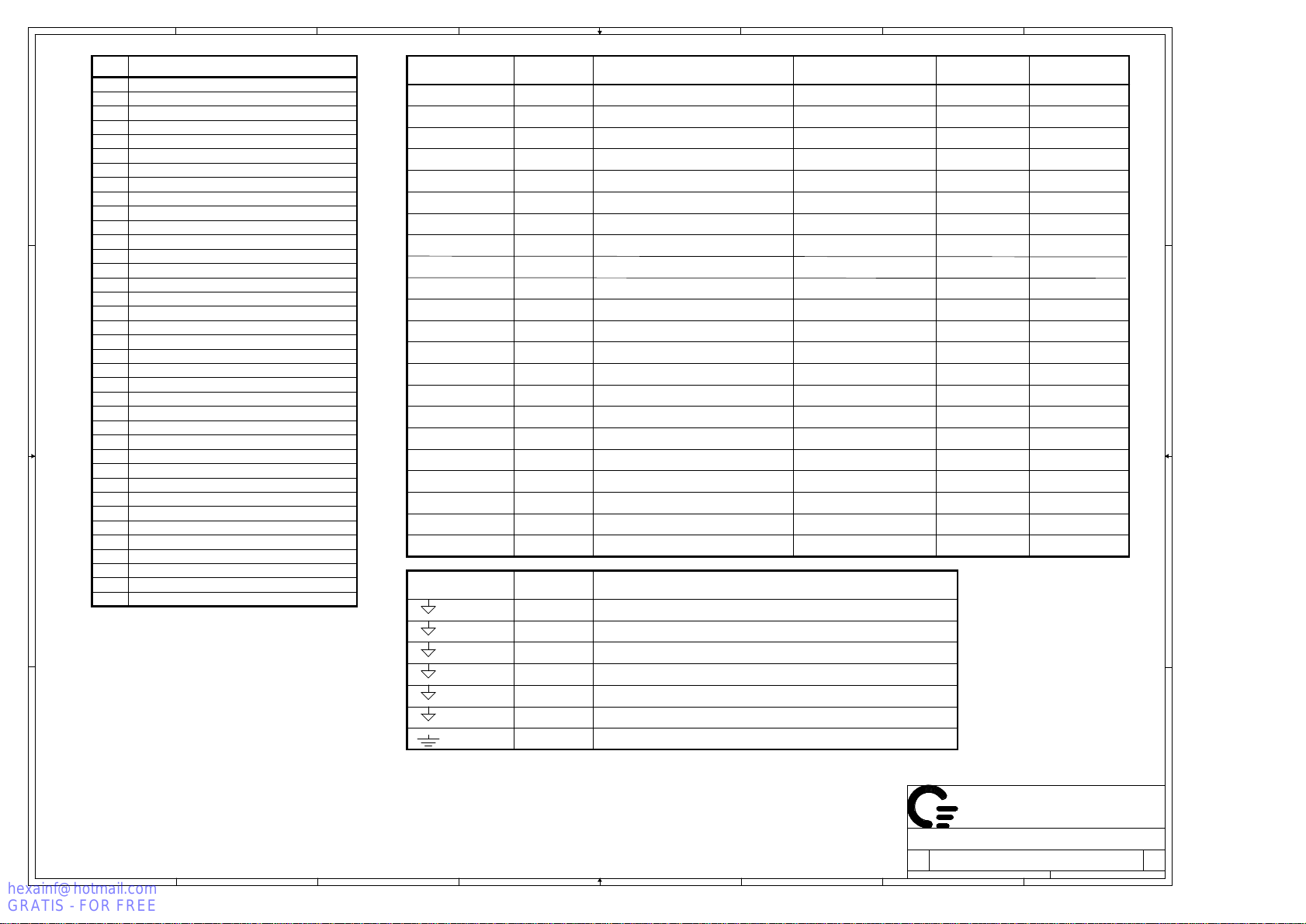

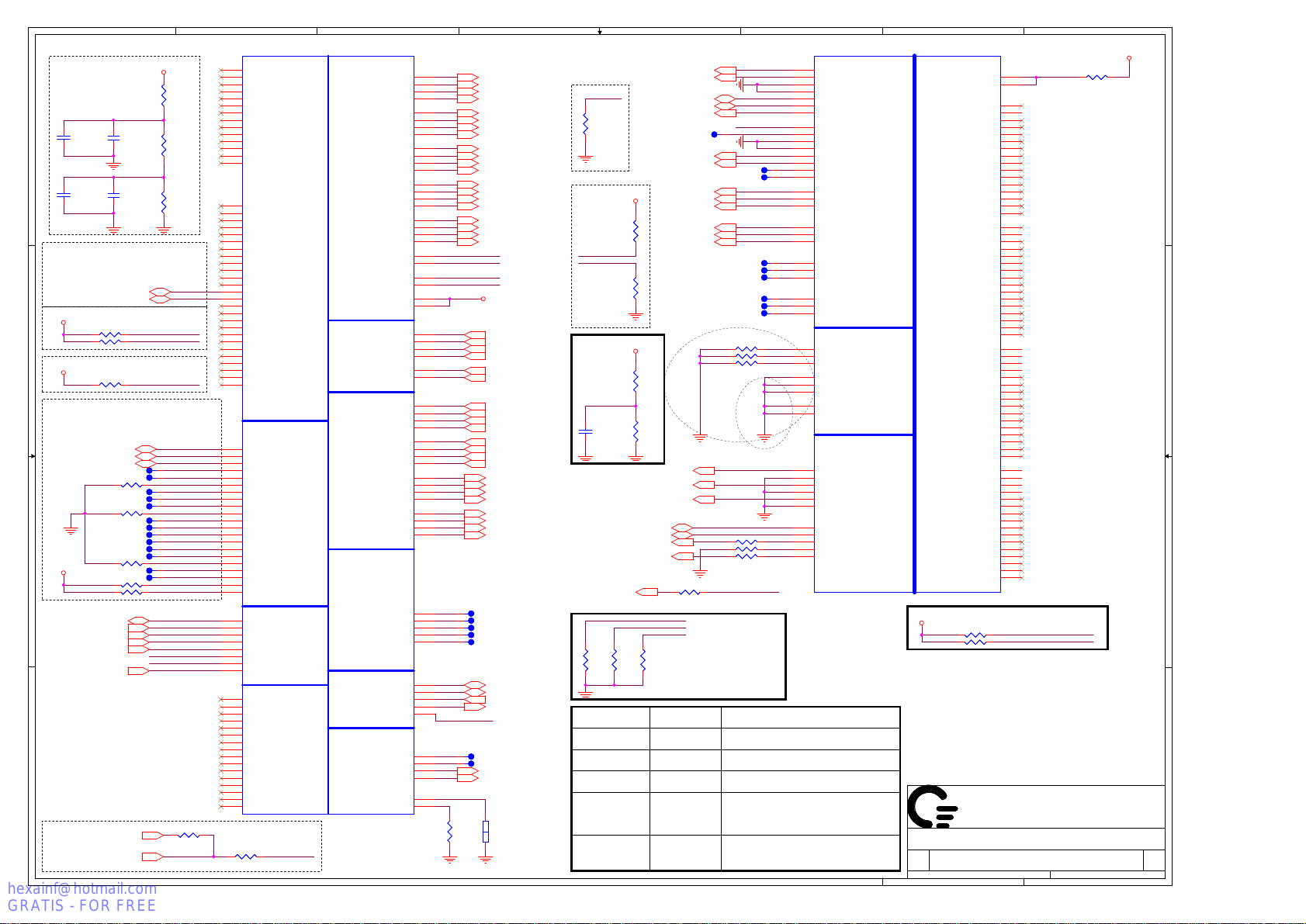

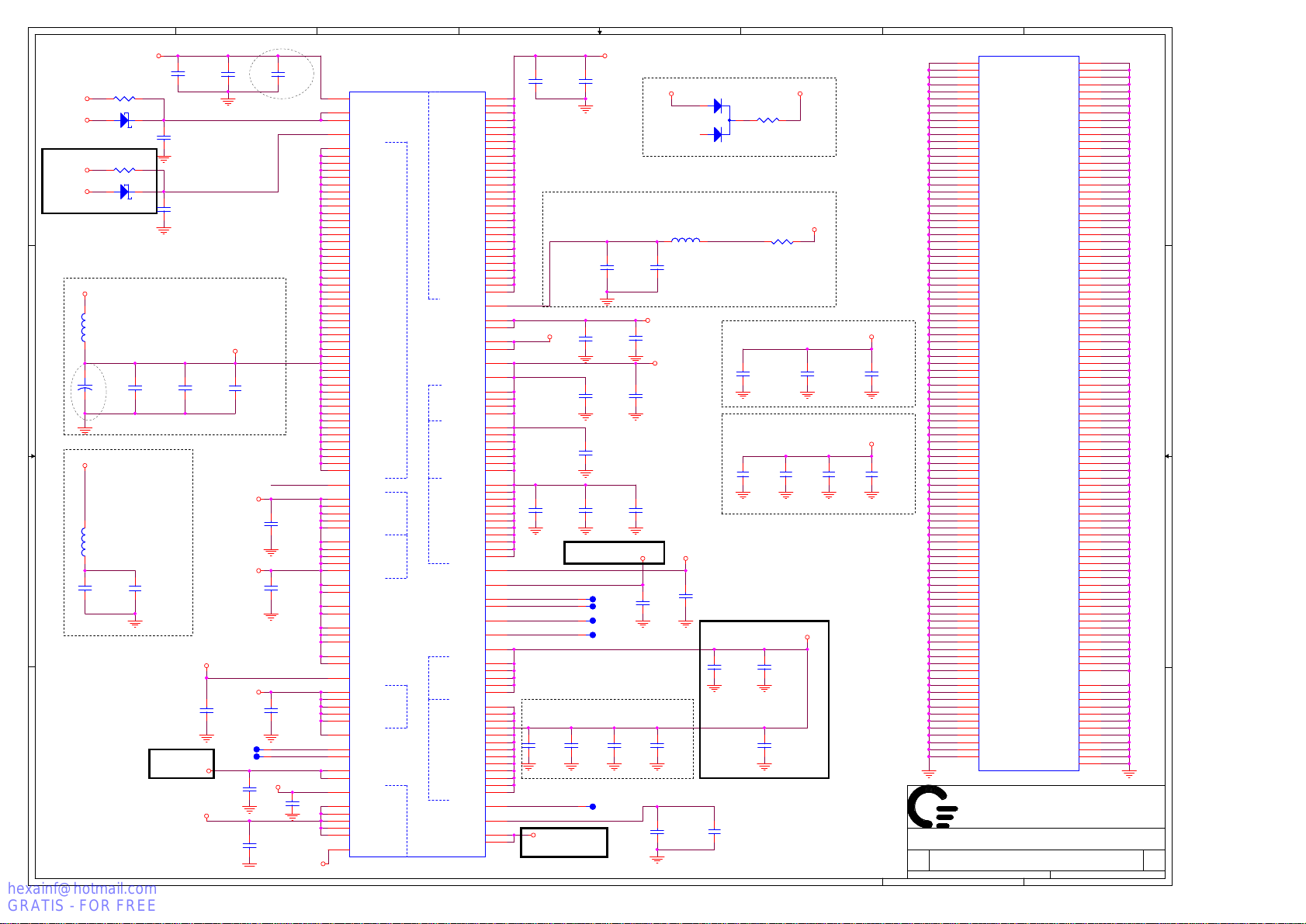

Table of ContentsPower States

PAGEDESCRIPTION

Schematic Block Diagram

1

2

Front Page

3-4

Merom

Crestline

5-10

ICH8M

AA

BB

CC

11-14

15-16

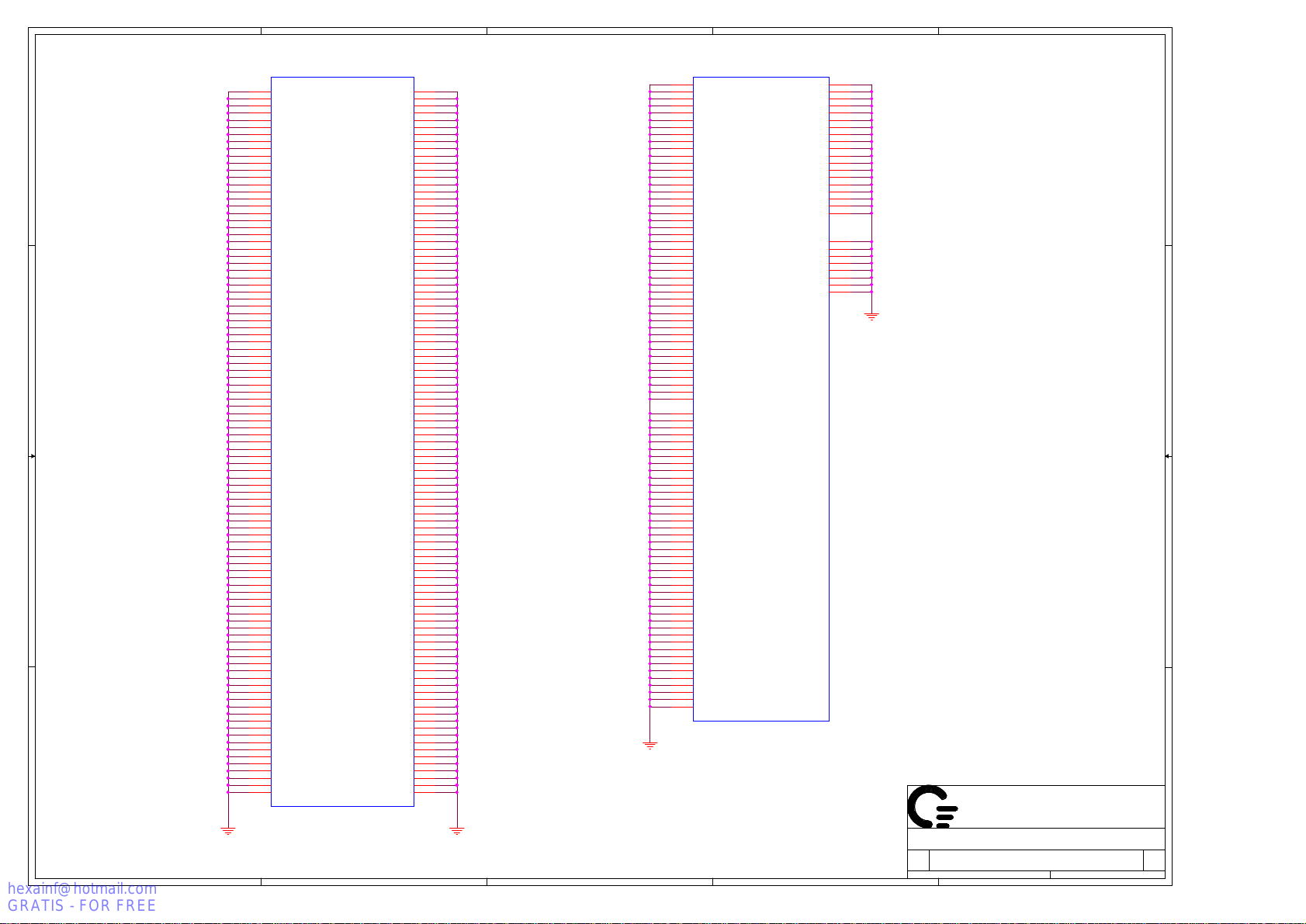

DDRII SO-DIMM(200P)

Clock Generator

17

18

HDMI

LCD Conn. & SSP

23

CRT Conn

24

SATA Conn

25

CARD READER/Conn & 1394

26-27

Express Card & Smart Card

28

Mini Card

29-30

SIO (ITE8512)

31

FLASH/RTC

32

33

USB

35

TP / KEYBOARD

SWITCH /LED

36

37

FAN & Thermal

38-39

Audio CODEC(ALC888)/Phone Jack

LOM / Switch

40-41

System Reset Circuit

44

Battery Selector & Charger

46

1.05VCCP / 1.5VRUJN

48

DDR2_1.8VSUS, 0.9V

49

CPU_ISL6266(2phase)

51

52

MAX8744 (+5.5V,+3,3V)

RUN Power Switch

53

DCIN,Batt

54

PAD& SCREW

55

EMI CAP

56

SMBUS BLOCK

57

Power Block Dianram

58

POWER PLANE

+PWR_SRC

+RTC_CELL

+3.3V_ALW

+5V_ALW

+15V_ALW

+3.3V_LAN

+5V_SUS

+3.3V_SUS

+1.8V_SUS

+0.9V_DDR_VTT

+5V_RUN

+3.3V_RUN

+1.8V_RUN

+1.5V_RUN

+1.25V_RUN

+1.05V_VCCP

+VCC_CORE

+LCDVCC

+5V_MOD

+5V_HDD

+PBATT

+SBATT

10V~+19V

+3.0V~+3.3V

+3.3V

+5V

+15V

+3.3V

+5V

+3.3V

+1.8V

+0.9V

+5V

+3.3V

+1.8V

+1.5V

+1.25V

+1.05V

+0.7V~+1.77V

+3.3V

+5V

+5V

+10V~+17V

+10V~+17V

GND PLANEPAGE

8731AGND

AGND_0.9V

AGND_DC/DC

AGND_DC2

AGND_DDR

AGND_ISL6260

GND

46

49

52

48

49

51

ALL

4,26,32,34,46,48,49,51,52,56

11,14,31,32

3,31,32,34,36,37,38,44,46,49,52,53,54

35,36,46,48,49,52,53,54,56

26,36,37,52,53

42,43

14,38,51,53

3,11,12,13,14,26,30,37,38,43,48,49,51,53

6,8,9,15,48,49,53

16,49,53

14,18,27,36,37,38,39,40,41,53

14,18,27,36,37,38,39,40,41,53

18,38,53

4,9,14,30,33,34,48,53,56

6,9,14,49,53

3,4,5,6,8,9,11,14,48,56

4,51,56

26

36

36

DESCRIPTION

DESCRIPTION

MAIN POWER

RTC

8051 POWER

LCD/CHARGE POWER

LARGE POWER

LAN POWER

SLP_S5# CTRLD POWER

SLP_S5# CTRLD POWER

SODIMM POWER

SODIMM POWER

SLP_S3# CTRLD POWER

SLP_S3# CTRLD POWER

SDVO POWER

CALISTOGA/ICH8 POWER

CALISTOGA/ICH8 POWER

CPU/CALISTOGA/ICH8 POWER

CPU CORE POWER

LCD Power

Module Power

HDD Power

MAIN BATTERY

SECOND BATTERY

CONTROL

SIGNAL

ALWON

ALWON

+5V_ALW

AUX_ON

SUS_ON

3.3V_SUS_ON

DDR_ON

0.9V_DDR_VTT_ON

RUN_ON

3.3V_RUN_ON

RUN_ON

1.5V_RUN_ON

1.25V_RUN_ON

1.05V_RUN_ON

IMVP_VR_ON

LCDVCC_TST_EN

& ENVDD

MODC_EN#

HDDC_EN#

CHG_PBATT

CHG_SBATT

ACTIVE INVOLTAGEPAGE

S0~S5

S0~S5

S0~S5

S0~S5

S0~S5

DD

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Date:Sheet of

Date:Sheet of

1

2

3

4

5

6

Date:Sheet of

COMPUTER

Index & Power Status

Index & Power Status

Index & Power Status

VM9/VM81A

VM9/VM81A

VM9/VM81A

7

253Tuesday, May 27, 2008

253Tuesday, May 27, 2008

253Tuesday, May 27, 2008

8

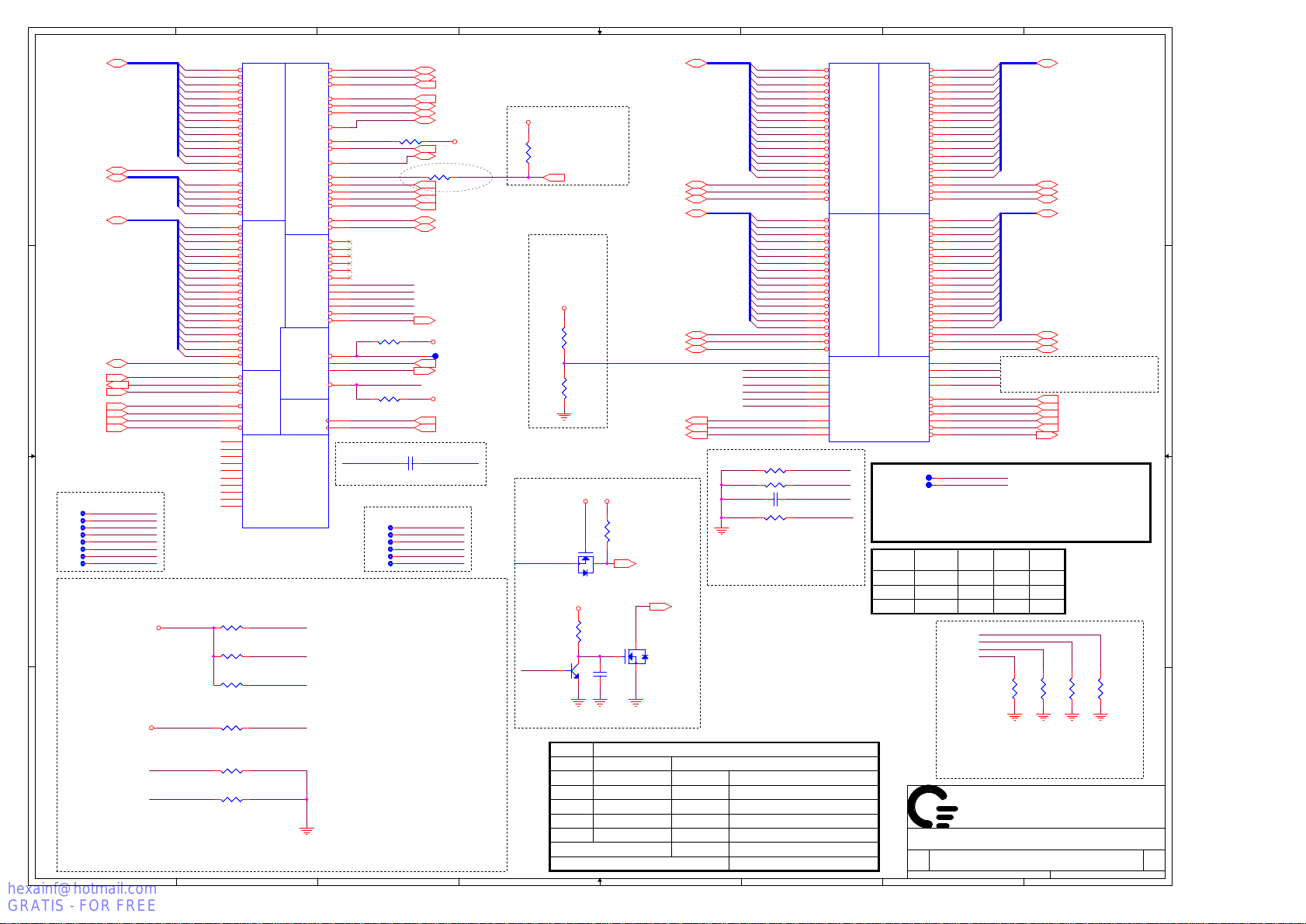

1 2 3 4 5 6

hexainf@hotmail.com

GRATIS - FOR FREE

7

8

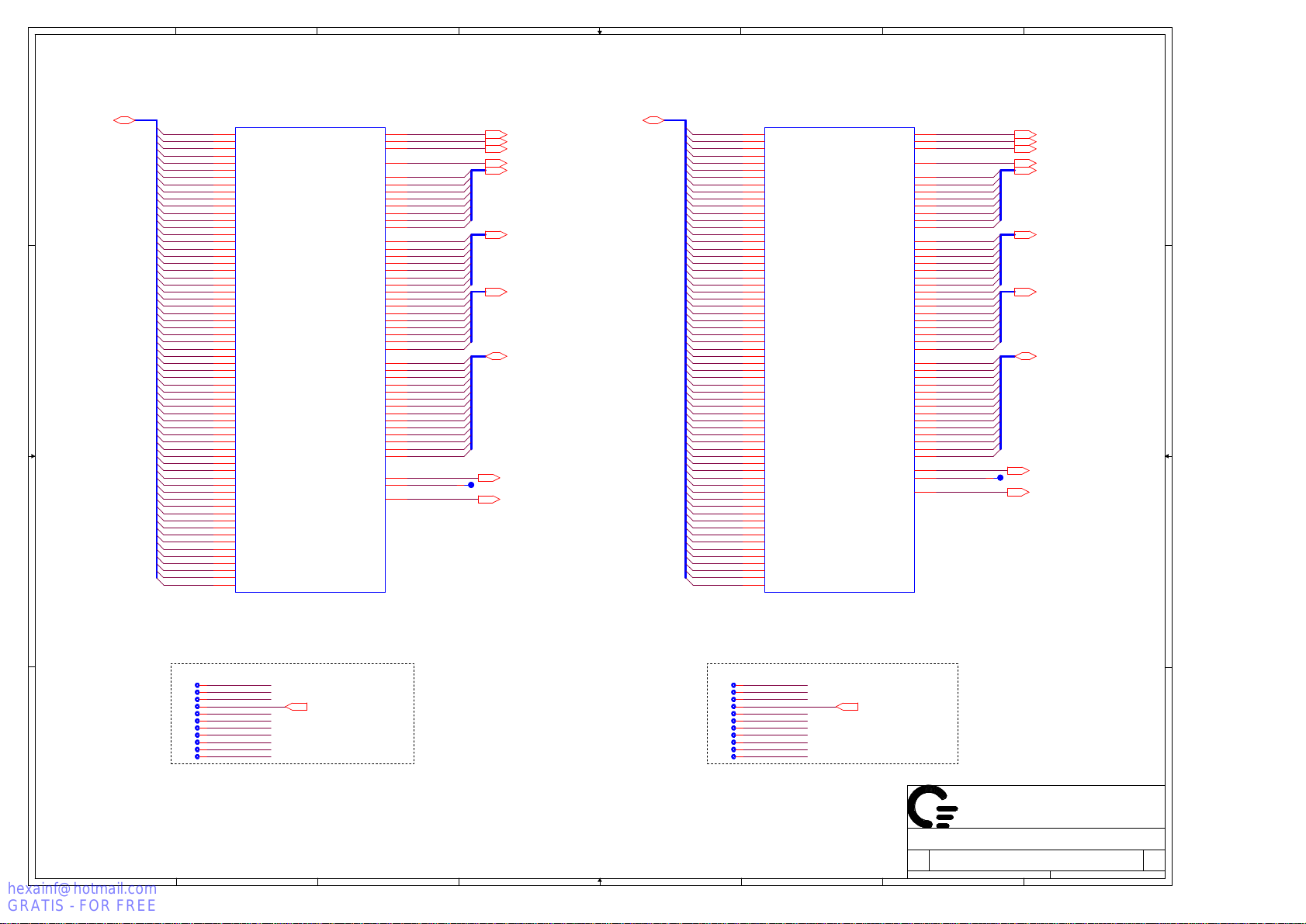

H_A#[3..16]5

AA

H_ADSTB#05

H_REQ#[0..4]5

H_A#[17..35]5

BB

H_ADSTB#15

H_A20M#11

H_FERR#11

H_IGNNE#11

H_STPCLK#11

H_INTR11

H_NMI11

H_SMI#11

H_A#[3..16]

H_REQ#[0..4]

H_A#[17..35]

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

For EA test use

H_DSTBN#0

1

ET11ET11

H_DSTBN#2

1

ET17ET17

H_DSTBP#2

1

ET16ET16

H_D#41

1

ET15ET15

H_DSTBN#3

1

ET22ET22

H_DSTBP#3

1

ET21ET21

H_D#50

1

ET20ET20

H_D#58

1

ET19ET19

CC

Populate ITP700Flex for bringup

+1.05V_VCCP

+3.3V_SUS

DD

ITP_TCK

ITP_TRST#

J4

L5

L4

K5

M3

N2

J1

N3

P5

P2

L2

P4

P1

R1

M1

K3

H2

K2

J3

L1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

U2

V4

W3

AA4

AB2

AA3

V1

A6

A5

C4

D5

C6

B4

A3

M4

N5

T2

V3

B2

C3

D2

D22

D3

F6

R19

R19

150

150

R18

R18

39/F

39/F

R1351R13

51

R3150R3150

R1527/FR1527/F

R16649/FR16649/F

U22A

U22A

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

RSVD[10]

12

12

12

12

12

12

DEFER#

ADDR GROUP 0

ADDR GROUP 0

CONTROLXDP/ITP SIGNALS

CONTROLXDP/ITP SIGNALS

RESET#

BPM[0]#

ADDR GROUP 1

ADDR GROUP 1

BPM[1]#

BPM[2]#

BPM[3]#

THERMAL

THERMAL

PROCHOT#

THERMDA

THERMDC

ICH

ICH

THERMTRIP#

H CLK

H CLK

BCLK[0]

BCLK[1]

RESERVED

RESERVED

47387-4784

47387-4784

ITP_TDI

ITP_TMS

ITP_TDO

ITP_DBRESET#

H1

ADS#

E2

BNR#

G5

BPRI#

H5

F21

DRDY#

E1

DBSY#

F1

BR0#

IERR#

INIT#

LOCK#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

H_IERR#

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

ITP_TCK

AC5

ITP_TDI

AA6

TDI

ITP_TDO

AB3

ITP_TMS

AB5

ITP_TRST#

AB6

ITP_DBRESET#

C20

R6756R67

H_PROCHOT#

D21

H_THERMDA

A24

H_THERMDC

B25

H_THERM

H_THERM

C7

R4456R44

1 2

A22

A21

C487*2200P_NC

C487*2200P_NC

H_THERMDA H_THERMDC

For EA test use

ET5ET5

ET12ET12

ET1ET1

ET4ET4

ET6ET6

ET7ET7

Layout Note:

Place R74,R26,

R19, R23, R16

, R17 close to CPU

H_ADS#5

H_BNR#5

H_BPRI#5

H_DEFER#5

H_DRDY#5

H_DBSY#5

H_BR0#5

R6256R6256

1 2

H_INIT#11

H_LOCK#5

R4100603R4100603

1 2

H_RS#05

H_RS#15

H_RS#25

H_TRDY#5

H_HIT#5

H_HITM#5

12

1 2

50

50

H_ADSTB#0

1

H_A#14

1

H_A#16

1

H_ADSTB#1

1

H_A#21

1

H_A#26

1

ITP_DBRESET#13

+1.05V_VCCP

H_THERMDA31

H_THERMDC31

+1.05V_VCCP

CLK_CPU_BCLK17

CLK_CPU_BCLK#17

56

56

4

+1.05V_VCCP

10

T3PAD T3PAD

+1.05V_VCCP

12

R40

R40

51/F

51/F

Layout Note:

Place voltage

divider within

0.5" of GTLREF

pin

+1.05V_VCCP

+1.05V_VCCP

H_PROCHOT#

H_THERM

Q6

Q6

MMST3904-7-F

MMST3904-7-F

Layout Note:

Place R44

close to

CPU.

H_RESET#5

R380

R380

1K/F

1K/F

1 2

12

R379

R379

2K/F

2K/F

+3.3V_ALW

2

1 2

31

Q7

Q7

*2N7002W_NC

*2N7002W_NC

+3.3V_RUN

R51

R51

10M

10M

12

2

Signal

C68

C68

0.1U

0.1U

1 3

10

10

ITP disable guidelines

Resistor Value

TDI

150 ohm +/- 5%

TMS

39 ohm +/- 5%

TRST#

680 ohm +/- 5%

TCK

27 ohm +/- 5%

Open

TDO

ITP_EN

R268 Depop

H_D#[0..63]5

H_DSTBN#05

H_DSTBP#05

H_DINV#05

H_D#[0..63]5

H_DSTBN#15

H_DSTBP#15

H_DINV#15

CPU_MCH_BSEL06,17

CPU_MCH_BSEL16,17

CPU_MCH_BSEL26,17

Voltage Level shift

R50

R50

*2.2K_NC

*2.2K_NC

CPU_PROCHOT#

31

Q5

2N7002WQ52N7002W

2

H_D#[0..63] H_D#[0..63]

H_D#[0..63]

H_THERMTRIP#6,23,31,40

Connect To

VTT

VTT

GND

GND

VTT

+3VRUN

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

V_CPU_GTLREF

CPU_TEST1

CPU_TEST2

CPU_TEST3

CPU_TEST4

CPU_TEST5

CPU_TEST6

R75*1K/F_NCR75*1K/F_NC

R74*1K/F_NCR74*1K/F_NC

C509*0.1U_NC

C509*0.1U_NC

10

10

R373*0_NCR373*0_NC

Place C close to the

CPU_TEST4 pin. Make sure

CPU_TEST4 routing is

reference to GND and away

from other noisy signal.

Resistor Placement

Within 2.0" of the ITP

Within 2.0" of the ITP

Within 2.0" of the ITP

Within 2.0" of the ITP

Within 2.0" of the ITP

Close to CK410M Pin8

U22B

U22B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

K24

G24

J24

J23

H22

F26

K22

H23

J26

H26

H25

N22

K25

P26

R23

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

T25

N25

L26

M26

N24

AD26

C23

D25

C24

AF26

AF1

A26

B22

B23

C21

CPU_TEST1

12

CPU_TEST2

12

CPU_TEST4

12

CPU_TEST6

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

BSEL[0]

BSEL[1]

BSEL[2]

47387-4784

47387-4784

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

DATA GRP 2DATA GRP 3

DATA GRP 2DATA GRP 3

MISC

MISC

For the purpose of testability, route these signals

through a ground referenced Z0 = 55ohm trace that

ends in a via that is near a GND via and is

accessible through an oscilloscope connection.

FSB

53300

667

800

6

Y22

D[32]#

AB24

D[33]#

V24

D[34]#

V26

D[35]#

V23

D[36]#

T22

D[37]#

U25

D[38]#

U23

D[39]#

Y25

D[40]#

W22

D[41]#

Y23

D[42]#

W24

D[43]#

W25

D[44]#

AA23

D[45]#

AA24

D[46]#

AB25

D[47]#

Y26

DSTBN[2]#

AA26

DSTBP[2]#

U22

DINV[2]#

AE24

D[48]#

AD24

D[49]#

AA21

D[50]#

AB22

D[51]#

AB21

D[52]#

AC26

D[53]#

AD20

D[54]#

AE22

D[55]#

AF23

D[56]#

AC25

D[57]#

AE21

D[58]#

AD21

D[59]#

AC22

D[60]#

AD23

D[61]#

AF22

D[62]#

AC23

D[63]#

AE25

DSTBN[3]#

AF24

DSTBP[3]#

AC20

DINV[3]#

R26

COMP[0]

U26

COMP[1]

AA1

COMP[2]

Y1

COMP[3]

E5

DPRSTP#

B5

DPSLP#

D24

DPWR#

D6

PWRGOOD

D7

SLP#

AE6

PSI#

T145PAD T145PAD

T146PAD T146PAD

BCLK

133

166

200

Comp0,2 connect with Zo=27.4ohm,Comp1,3

connect with Zo=55ohm, make those traces

length shorter than 0.5".Trace should be

at least 25 mils away from any other

toggling signal.

Title

Title

Title

Merom Processor (HOST BUS)

Merom Processor (HOST BUS)

Merom Processor (HOST BUS)

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

VM9/VM81A

VM9/VM81A

VM9/VM81A

Date:Sheet of

Date:Sheet of

Date:Sheet of

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#[0..63]

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

CPU_TEST3

CPU_TEST5

Note:

H_DPRTSTP need to daisy chain

from ICH8 to IMVP6 to CPU.

BSEL2BSEL1BSEL0

0

1

COMP0

COMP1

COMP2

COMP3

R36

R36

54.9/F

54.9/F

1 2

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

7

H_D#[0..63]5

H_DSTBN#25

H_DSTBP#25

H_DINV#25

H_D#[0..63]5

H_DSTBN#35

H_DSTBP#35

H_DINV#35

H_DPRSTP#6,11,39

H_DPSLP#11

H_DPWR#5

H_PWRGOOD11

H_CPUSLP#5

H_PSI#39

1

0011

R35

R35

27.4/F

27.4/F

1 2

1 2

R38

R38

54.9/F

54.9/F

R42

R42

27.4/F

27.4/F

1 2

353Monday, June 23, 2008

353Monday, June 23, 2008

353Monday, June 23, 2008

8

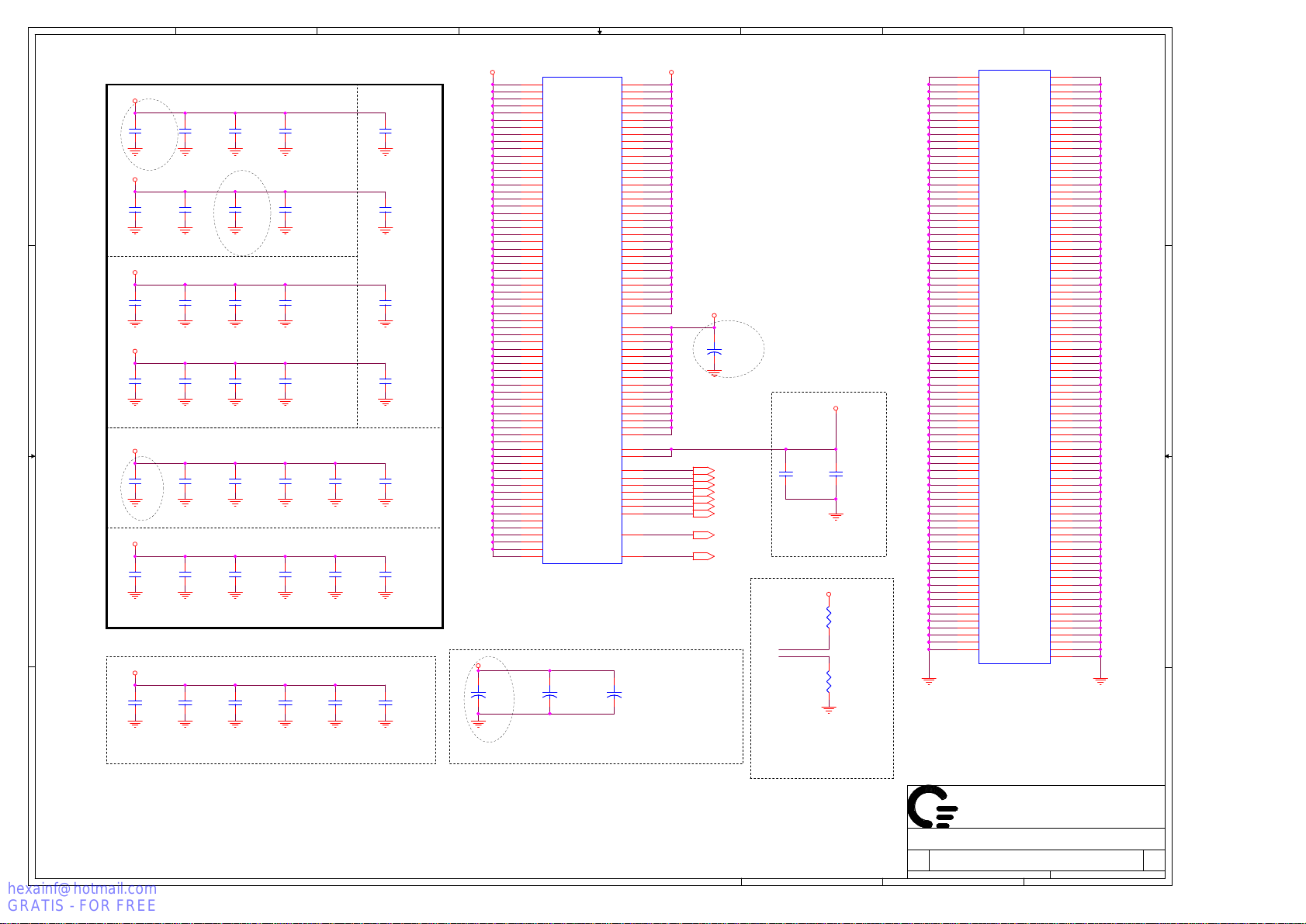

1 2 3 4 5 6

hexainf@hotmail.com

GRATIS - FOR FREE

7

8

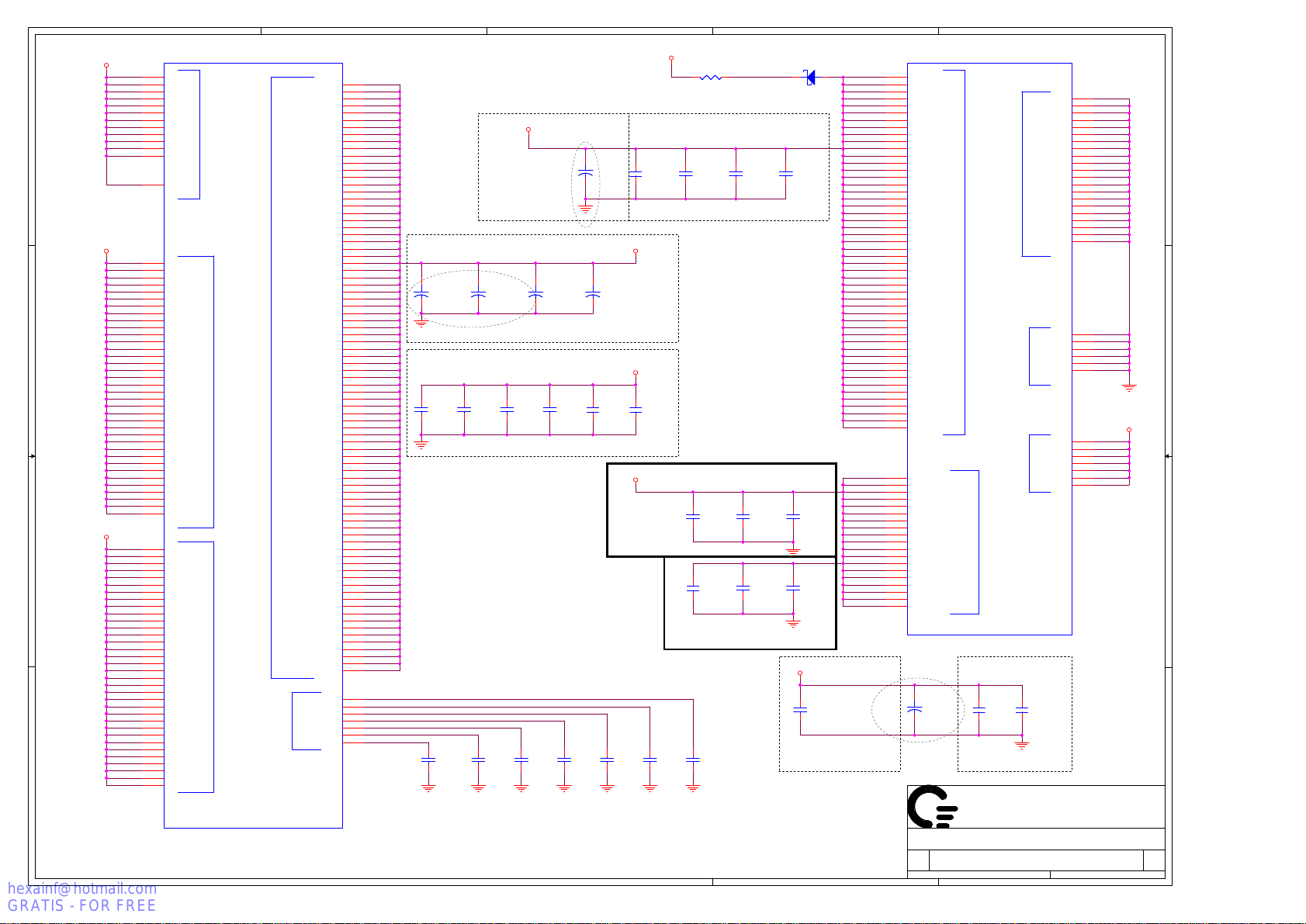

+VCC_CORE +VCC_CORE

+VCC_CORE

All use 10U 4V(+-20%,X6S,0805)Pb-Free.

55

12

AA

+VCC_CORE

12

C50

C50

*10U_NC

*10U_NC

0805

0805

4

4

C45

C45

10U

10U

0805

0805

4

4

12

C49

C49

10U

10U

0805

0805

4

4

12

C48

C48

10U

10U

0805

0805

4

4

12

C47

C47

10U

10U

0805

0805

4

4

12

C46

C46

10U

10U

0805

0805

4

4

55

C44

C44

10U

10U

0805

0805

4

4

12

12

C43

C43

*10U_NC

*10U_NC

0805

0805

4

4

12

C52

C52

10U

10U

0805

0805

4

4

12

C53

C53

10U

10U

0805

0805

4

4

8 inside cavity, north side, secondary layer.

+VCC_CORE

C71

C71

10U

10U

0805

0805

4

4

C499

C499

*10U_NC

*10U_NC

0805

0805

4

4

12

12

12

BB

+VCC_CORE

12

C76

C76

10U

10U

0805

0805

4

4

C500

C500

*10U_NC

*10U_NC

0805

0805

4

4

12

12

C73

C73

10U

10U

0805

0805

4

4

C69

C69

*10U_NC

*10U_NC

0805

0805

4

4

12

12

C503

C503

10U

10U

0805

0805

4

4

C496

C496

*10U_NC

*10U_NC

0805

0805

4

4

12

C60

C60

10U

10U

0805

0805

4

4

12

C497

C497

*10U_NC

*10U_NC

0805

0805

4

4

8 inside cavity, south side, secondary layer.

+VCC_CORE

55

C74

C74

10U

10U

0805

0805

4

4

12

C498

C498

10U

10U

0805

0805

4

4

12

C66

C66

10U

10U

0805

0805

4

4

12

C72

C72

10U

10U

0805

0805

4

4

12

C70

C70

10U

10U

0805

0805

4

4

12

C495

C495

10U

10U

0805

0805

4

4

12

6 inside cavity, north side, primary layer.

+VCC_CORE

CC

12

C508

C508

10U

10U

0805

0805

4

4

12

C507

C507

10U

10U

0805

0805

4

4

12

C506

C506

10U

10U

0805

0805

4

4

12

C504

C504

10U

10U

0805

0805

4

4

12

C505

C505

10U

10U

0805

0805

4

4

12

C75

C75

10U

10U

0805

0805

4

4

6 inside cavity, south side, primary layer.

+1.05V_VCCP

12

Layout out:

Place these inside socket cavity on North side secondary.

DD

C55

C55

0.1U

0.1U

10

10

12

C56

C56

0.1U

0.1U

10

10

12

C54

C54

0.1U

0.1U

10

10

12

C65

C65

0.1U

0.1U

10

10

12

C58

C58

0.1U

0.1U

10

10

12

C64

C64

0.1U

0.1U

10

10

+PWR_SRC

63

+

+

C523

C523

100U

100U

25

25

Layout Note:

Need to add 100uF cap on PWR_SRC for cap singing.

Place on PWR_SRC near +VCC_CORE.

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AC10

AB10

AB12

AB14

AB15

AB17

AB18

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AB9

U22C

U22C

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

47387-4784

47387-4784

+

+

C519

C519

*100U_NC

*100U_NC

25

25

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

.

.

+

+

C518

C518

*100U_NC

*100U_NC

25

25

VCCSENSE

VSSSENSE

+1.05V_VCCP

12

+

+

C502

C502

220U

220U

7343

7343

2.5

2.5

VID039

VID139

VID239

VID339

VID439

VID539

VID639

VCCSENSE39

VSSSENSE39

55

+1.5V_RUN

12

Layout Note:

Place C468 near PIN

B26.

VCCSENSE

VSSSENSE

Route VCCSENSE and VSSSENSE

traces at 27.4ohms and

length matched to within 25

mil. Place PU and PD within

2 inch of CPU.

C493

C493

0.01U

0.01U

25

25

+VCC_CORE

12

12

12

R32

R32

100/F

100/F

R33

R33

100/F

100/F

C494

C494

10U

10U

0805

0805

4

4

U22D

U22D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

47387-4784

47387-4784

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

.

.

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Date:Sheet of

Date:Sheet of

6

Date:Sheet of

COMPUTER

Merom Processor (POWER)

Merom Processor (POWER)

Merom Processor (POWER)

VM9/VM81A

VM9/VM81A

VM9/VM81A

7

453Friday, May 30, 2008

453Friday, May 30, 2008

453Friday, May 30, 2008

8

1 2 3 4 5 6

hexainf@hotmail.com

GRATIS - FOR FREE

7

8

U20A

H_D#[0..63]

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_RESET#3

H_CPUSLP#3

H_REF

12

C121

C121

0.1U

0.1U

10

10

Layout Note:

Place the 0.1 uF

decoupling capacitor

within 100 mils from

GMCH pins.

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

C107

C107

0.1U

0.1U

1 2

10

10

H_D#[0..63]3

+1.05V_VCCP

1 2

12

R94

R94

1K/F

1K/F

R96

R96

2K/F

2K/F

AA

+1.05V_VCCP

12

R93

R93

221/F

221/F

H_SWING

12

R92

R92

100/F

100/F

BB

+1.05V_VCCP

R139

R139

R141

R141

54.9/F

54.9/F

54.9/F

54.9/F

1 2

1 2

1 2

CC

DD

H_SCOMP

H_SCOMP#

H_RCOMP

R91

R91

24.9/F

24.9/F

Layout Note:

H_RCOMP trace should be

10-mil wide with 20-mil

spacing.

U20A

E2

H_D#_0

G2

H_D#_1

G7

H_D#_2

M6

H_D#_3

H7

H_D#_4

H3

H_D#_5

G4

H_D#_6

F3

H_D#_7

N8

H_D#_8

H2

H_D#_9

M10

H_D#_10

N12

H_D#_11

N9

H_D#_12

H5

H_D#_13

P13

H_D#_14

K9

H_D#_15

M2

H_D#_16

W10

H_D#_17

Y8

H_D#_18

V4

H_D#_19

M3

H_D#_20

J1

H_D#_21

N5

H_D#_22

N3

H_D#_23

W6

H_D#_24

W9

H_D#_25

N2

H_D#_26

Y7

H_D#_27

Y9

H_D#_28

P4

H_D#_29

W3

H_D#_30

N1

H_D#_31

AD12

H_D#_32

AE3

H_D#_33

AD9

H_D#_34

AC9

H_D#_35

AC7

H_D#_36

AC14

H_D#_37

AD11

H_D#_38

AC11

H_D#_39

AB2

H_D#_40

AD7

H_D#_41

AB1

H_D#_42

Y3

H_D#_43

AC6

H_D#_44

AE2

H_D#_45

AC5

H_D#_46

AG3

H_D#_47

AJ9

H_D#_48

AH8

H_D#_49

AJ14

H_D#_50

AE9

H_D#_51

AE11

H_D#_52

AH12

H_D#_53

AJ5

H_D#_54

AH5

H_D#_55

AJ6

H_D#_56

AE7

H_D#_57

AJ7

H_D#_58

AJ2

H_D#_59

AE5

H_D#_60

AJ3

H_D#_61

AH2

H_D#_62

AH13

H_D#_63

B3

H_SWING

C2

H_RCOMP

W1

H_SCOMP

W2

H_SCOMP#

B6

H_CPURST#

E5

H_CPUSLP#

B9

H_AVREF

A9

H_DVREF

LE82GM965-SLA5T-MM#891181

LE82GM965-SLA5T-MM#891181

H_ADSTB#_0

H_ADSTB#_1

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HOST

HOST

HPLL_CLK#

H_DPWR#

H_DRDY#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

For EA test use

H_DSTBP#0

1

ET10ET10

H_D#7

1

ET2ET2

H_D#12

1

ET14ET14

H_DSTBN#1

1

ET9ET9

H_DSTBP#1

1

ET8ET8

H_D#29

1

ET13ET13

H_D#21

1

ET3ET3

H_D#32

1

ET18ET18

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_BNR#

H_BPRI#

H_HIT#

H_HITM#

H_RS#_0

H_RS#_1

H_RS#_2

J13

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

76

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_A#[3..35]

H_ADS#3

H_ADSTB#03

H_ADSTB#13

H_BNR#3

H_BPRI#3

H_BR0#3

H_DEFER#3

H_DBSY#3

CLK_MCH_BCLK17

CLK_MCH_BCLK#17

H_DPWR#3

H_DRDY#3

H_HIT#3

H_HITM#3

H_LOCK#3

H_TRDY#3

H_DINV#03

H_DINV#13

H_DINV#23

H_DINV#33

H_DSTBN#03

H_DSTBN#13

H_DSTBN#23

H_DSTBN#33

H_DSTBP#03

H_DSTBP#13

H_DSTBP#23

H_DSTBP#33

H_REQ#03

H_REQ#13

H_REQ#23

H_REQ#33

H_REQ#43

H_RS#03

H_RS#13

H_RS#23

6

H_A#[3..35]3

+1.05V_VCCP +1.05V_VCCP +1.05V_VCCP +1.05V_VCCP

C113

C131

C131

*0.1U_NC

*0.1U_NC

1 2

10

10

+1.05V_VCCP +1.05V_VCCP +1.05V_VCCP

C141

C141

*0.1U_NC

*0.1U_NC

1 2

10

10

Layout Note:

C131 should be near AB1,AB2,AC2,Y3

C113

*0.1U_NC

*0.1U_NC

1 2

10

10

C165

C165

*0.1U_NC

*0.1U_NC

1 2

10

10

1 2

1 2

C145

C145

*0.1U_NC

*0.1U_NC

10

10

C159

C159

*0.1U_NC

*0.1U_NC

10

10

C142

C142

*0.1U_NC

*0.1U_NC

1 2

10

10

C90 should be near AD2,AE2,AG3,AE3

C113 should be near

AC5,AC6,AD7,AC7,AC9,AD9,AD11,AC11,AD12,AD13,AC14

C127 should be near E2,F3,H2,H3,G4,H5,G7,H7

C129 should be near

M6,L7,K9,M7,N8,N9,M10,M11,N12,P13

C149 should be near

H13,J13,L13,M14,L16,K16,J17,H17

C146 should be near

E13,G17,F16,C15,B14,C11,B11,A11,B12

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Date:Sheet of

Date:Sheet of

Date:Sheet of

COMPUTER

Crestline (HOST)

Crestline (HOST)

Crestline (HOST)

VM9/VM81A

VM9/VM81A

VM9/VM81A

7

553Monday, June 02, 2008

553Monday, June 02, 2008

553Monday, June 02, 2008

8

1 2 3 4 5 6

hexainf@hotmail.com

GRATIS - FOR FREE

U20C

U20B

+1.8V_SUS

R179

R179

1K/F

1K/F

SM_RCOMP_VOH

12

AA

SM_RCOMP_VOL

12

Santa Rosa Platform MOW WW15

For 4Gb DRAM support,

change Pin-BJ29 to DDR_A_MA14,

change Pin-BE24 to DDR_B_MA14.

+3.3V_RUN

BB

+1.05V_VCCP

Layout Note:

Location of all MCH_CFG strap

resistors needs to be close to

minmize stub.

CC

+3.3V_RUN

DD

12

C238

C238

0.01U

0.01U

25

25

12

C241

C241

0.01U

0.01U

25

25

DDR_A_MA1415,16

DDR_B_MA1415,16

R12510KR12510K

1 2

R12110KR12110K

1 2

R13256R132

1 2

CPU_MCH_BSEL03,17

CPU_MCH_BSEL13,17

CPU_MCH_BSEL23,17

PAD

PAD

R117*4.02K/F_NCR117*4.02K/F_NC

PAD

PAD

PAD

PAD

R100*4.02K/F_NCR100*4.02K/F_NC

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

R129*4.02K/F_NCR129*4.02K/F_NC

PAD

PAD

PAD

PAD

R127*4.02K/F_NCR127*4.02K/F_NC

R120*4.02K/F_NCR120*4.02K/F_NC

PM_BMBUSY#13

H_DPRSTP#3,11,39

PM_EXTTS#015

PM_EXTTS#115

ICH_PWRGD13,35

DPRSLPVR13,39

SB_NB_PCIE_RST#12

PLTRST#12,23,26,34

C232

C232

2.2U

2.2U

0805

0805

10

10

C237

C237

2.2U

2.2U

0805

0805

10

10

56

THERMTRIP_MCH#

T15PAD T15PAD

T140

T140

12

T29PAD T29PAD

T16

T16

T22

T22

12

T30

T30

T26

T26

T23

T23

T12

T12

T13

T13

T24

T24

12

T27

T27

T25

T25

12

12

1 2

12

R178

R178

3.01K/F

3.01K/F

R175

R175

1K/F

1K/F

1 2

PM_EXTTS#0

PM_EXTTS#1

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

PM_EXTTS#0

PM_EXTTS#1

PLTRST#_R

THERMTRIP_MCH#

*0_NC

*0_NC

R148

R148

U20B

P36

RSVD1

P37

RSVD2

R35

RSVD3

N35

RSVD4

AR12

RSVD5

AR13

RSVD6

AM12

RSVD7

AN13

RSVD8

J12

RSVD9

AR37

RSVD10

AM36

RSVD11

AL36

RSVD12

AM37

RSVD13

D20

RSVD14

H10

RSVD20

B51

RSVD21

BJ20

RSVD22

BK22

RSVD23

BF19

RSVD24

BH20

RSVD25

BK18

RSVD26

BJ18

RSVD27

BF23

RSVD28

BG23

RSVD29

BC23

RSVD30

BD24

RSVD31

BJ29

RSVD32

BE24

RSVD33

BH39

RSVD34

AW20

RSVD35

BK20

RSVD36

C48

RSVD37

D47

RSVD38

B44

RSVD39

C44

RSVD40

A35

RSVD41

B37

RSVD42

B36

RSVD43

B34

RSVD44

C34

RSVD45

P27

CFG_0

N27

CFG_1

N24

CFG_2

C21

CFG_3

C23

CFG_4

F23

CFG_5

N23

CFG_6

G23

CFG_7

J20

CFG_8

C20

CFG_9

R24

CFG_10

L23

CFG_11

J23

CFG_12

E23

CFG_13

E20

CFG_14

K23

CFG_15

M20

CFG_16

M24

CFG_17

L32

CFG_18

N33

CFG_19

L35

CFG_20

G41

PM_BM_BUSY#

L39

PM_DPRSTP#

L36

PM_EXT_TS#_0

J36

PM_EXT_TS#_1

AW49

PWROK

AV20

RSTIN#

N20

THERMTRIP#

G36

DPRSLPVR

BJ51

NC_1

BK51

NC_2

BK50

NC_3

BL50

NC_4

BL49

NC_5

BL3

NC_6

BL2

NC_7

BK1

NC_8

BJ1

NC_9

E1

NC_10

A5

NC_11

C51

NC_12

B50

NC_13

A50

NC_14

A49

NC_15

BK2

NC_16

LE82GM965-SLA5T-MM#891181

LE82GM965-SLA5T-MM#891181

R149

R149

100

100

PLTRST#_R

12

DDR MUXINGCLKDMI

DDR MUXINGCLKDMI

CFGRSVD

CFGRSVD

PM

PM

GRAPHICS VIDME

GRAPHICS VIDME

NC

NC

MISC

MISC

SM_CK_0

SM_CK_1

SM_CK_3

SM_CK_4

SM_CK#_0

SM_CK#_1

SM_CK#_3

SM_CK#_4

SM_CKE_0

SM_CKE_1

SM_CKE_3

SM_CKE_4

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF_0

SM_VREF_1

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLK_REQ#

ICH_SYNC#

TEST_1

TEST_2

AV29

BB23

BA25

AV23

AW30

BA23

AW25

AW23

BE29

AY32

BD39

BG37

BG20

BK16

BG16

BE13

BH18

BJ15

BJ14

BE16

BL15

BK14

BK31

BL31

AR49

AW4

B42

C42

H48

H47

K44

K45

AN47

AJ38

AN42

AN46

AM47

AJ39

AN41

AN45

AJ46

AJ41

AM40

AM44

AJ47

AJ42

AM39

AM43

E35

A39

C38

B39

E36

AM49

AK50

AT43

AN49

AM50

H35

K36

G39

G40

A37

R32

M_CLK_DDR015

M_CLK_DDR115

M_CLK_DDR315

M_CLK_DDR415

M_CLK_DDR#015

M_CLK_DDR#115

M_CLK_DDR#315

M_CLK_DDR#415

DDR_CKE0_DIMMA15,16

DDR_CKE1_DIMMA15,16

DDR_CKE3_DIMMB15,16

DDR_CKE4_DIMMB15,16

DDR_CS0_DIMMA#7,15,16

DDR_CS1_DIMMA#15,16

DDR_CS2_DIMMB#15,16

DDR_CS3_DIMMB#7,15,16

M_ODT015,16

M_ODT115,16

M_ODT215,16

M_ODT315,16

SMRCOMPP

SMRCOMPN

SM_RCOMP_VOH

SM_RCOMP_VOL

V_DDR_MCH_REF

T10

T10

T144

T144

T143

T143

T142

T142

T141

T141

MCH_CLVREF

T17

T17

T28

T28

CLK_3GPLLREQ#17

MCH_ICH_SYNC#13

2

R134

R134

20K

20K

1

1 2

MCH_DREFCLK17

MCH_DREFCLK#17

DREF_SSCLK17

DREF_SSCLK#17

CLK_MCH_3GPLL17

CLK_MCH_3GPLL#17

DMI_MRX_ITX_N012

DMI_MRX_ITX_N112

DMI_MRX_ITX_N212

DMI_MRX_ITX_N312

DMI_MRX_ITX_P012

DMI_MRX_ITX_P112

DMI_MRX_ITX_P212

DMI_MRX_ITX_P312

DMI_MTX_IRX_N012

DMI_MTX_IRX_N112

DMI_MTX_IRX_N212

DMI_MTX_IRX_N312

DMI_MTX_IRX_P012

DMI_MTX_IRX_P112

DMI_MTX_IRX_P212

DMI_MTX_IRX_P312

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

CL_CLK013

CL_DATA013

ICH_CL_PWROK13,23

ICH_CL_RST0#13

PAD

PAD

PAD

PAD

SJ5SJ5

2

1

BIA_PWM18

PANEL_BKEN23

L_IBG

R123

R123

2.4K/F

2.4K/F

1 2

UMA

SMRCOMPP

SMRCOMPN

+1.8V_SUS

R180

R180

20/F

20/F

R177

R177

20/F

20/F

LCD_DDCCLK18

LCD_DDCDAT18

ENVDD18

T21PAD T21PAD

LCD_ACLK-18

LCD_ACLK+18

LCD_A0-18

LCD_A1-18

LCD_A2-18

12

LCD_A0+18

LCD_A1+18

LCD_A2+18

12

7

+1.25V_RUN

Non-iAMT

MCH_CLVREF

C214

C214

0.1U

0.1U

1 2

10

10

H_THERMTRIP#3,23,31,40

R116

R116

150/F

150/F

1 2

SDVO_CRTL_DATASDVO Present.

CFG5

CFG9

CFG16

CFG19

CFG20

G_CLK_DDC219

G_DAT_DDC219

R119

R119

150/F

150/F

1 2

R166

R166

1K/F

1K/F

1 2

12

R165

R165

392/F

392/F

VGA_BLU19

VGA_GRN19

VGA_RED19

VGAHSYNC19

VGAVSYNC19

R43*0_NCR43*0_NC

VGA_BLU

VGA_GRN

VGA_RED

R103

R103

Layout Note:

150/F

150/F

Place 150 ohm

termination resistors

1 2

close to GMCH.

DMI X2 Select

PCI Express

Graphic Lane

FSB Dynamic

ODT

DMI Lane

Reversal

SDVO/PCIE

Concurrent

Operation

R10430/FR10430/F

R3621.3K/FR3621.3K/F

R9930/FR9930/F

LCD_DDCCLK

LCD_DDCDAT

L_IBG

T19PAD T19PAD

T11PAD T11PAD

T14PAD T14PAD

T4PAD T4PAD

T6PAD T6PAD

T9PAD T9PAD

T5PAD T5PAD

T7PAD T7PAD

R675/FR675/F

R875/FR875/F

R1475/FR1475/F

21

VGA_BLU

VGA_GRN

VGA_RED

1 2

1 2

1 2

THERMTRIP_MCH#

UMA

Low=DMIx2

High=DMIx4(Default)

Low= Reveise Lane

High=Normal operation

Low=Dynamic ODT Disable

High=Dynamic ODT Enable(default).

Low=Normal(default).

High=Lane Reversed

Low=Only SDVO or PCIEx1 is

operational (defaults)

High=SDVO and PCIEx1 are operating

simultaneously via PEG port

Low=No SDVO Device Present

(default)

High=SDVO Device Present

U20C

J40

L_BKLT_CTRL

H39

L_BKLT_EN

E39

L_CTRL_CLK

E40

L_CTRL_DATA

C37

L_DDC_CLK

D35

L_DDC_DATA

K40

L_VDD_EN

L41

LVDS_IBG

L43

LVDS_VBG

N41

LVDS_VREFH

N40

LVDS_VREFL

D46

LVDSA_CLK#

C45

LVDSA_CLK

D44

LVDSB_CLK#

E42

LVDSB_CLK

G51

LVDSA_DATA#_0

E51

LVDSA_DATA#_1

F49

LVDSA_DATA#_2

G50

LVDSA_DATA_0

E50

LVDSA_DATA_1

F48

LVDSA_DATA_2

G44

LVDSB_DATA#_0

B47

LVDSB_DATA#_1

B45

LVDSB_DATA#_2

E44

LVDSB_DATA_0

A47

LVDSB_DATA_1

A45

LVDSB_DATA_2

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

M35

TV_DCONSEL_0

P33

TV_DCONSEL_1

H32

CRT_BLUE

G32

CRT_BLUE#

K29

CRT_GREEN

J29

CRT_GREEN#

F29

CRT_RED

E29

CRT_RED#

K33

CRT_DDC_CLK

G35

CRT_DDC_DATA

F33

CRT_HSYNC

C32

CRT_TVO_IREF

E33

CRT_VSYNC

LE82GM965-SLA5T-MM#891181

LE82GM965-SLA5T-MM#891181

6

LVDS

LVDS

TV VGA

TV VGA

7

VCC3G_PCIE_R

N43

PEG_COMPI

PEG_COMPO

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_TX#_10

PEG_TX#_11

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

+3.3V_RUN

R1022.2KR1022.2K

R1052.2KR1052.2K

Title

Title

Title

Crestline (VGA,DMI)

Crestline (VGA,DMI)

Crestline (VGA,DMI)

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

VM9/VM81A

VM9/VM81A

VM9/VM81A

Date:Sheet of

Date:Sheet of

Date:Sheet of

7

M43

J51

PEG_RX#_0

L51

PEG_RX#_1

N47

PEG_RX#_2

T45

PEG_RX#_3

T50

PEG_RX#_4

U40

PEG_RX#_5

Y44

PEG_RX#_6

Y40

PEG_RX#_7

AB51

PEG_RX#_8

W49

PEG_RX#_9

AD44

AD40

AG46

AH49

AG45

AG41

J50

PEG_RX_0

L50

PEG_RX_1

M47

PEG_RX_2

U44

PEG_RX_3

T49

PEG_RX_4

T41

PEG_RX_5

W45

PEG_RX_6

W41

PEG_RX_7

AB50

PEG_RX_8

Y48

PEG_RX_9

AC45

PEG_RX_10

AC41

PEG_RX_11

AH47

PEG_RX_12

AG49

PEG_RX_13

AH45

PEG_RX_14

AG42

PEG_RX_15

N45

PEG_TX#_0

U39

PEG_TX#_1

U47

PEG_TX#_2

N51

PEG_TX#_3

R50

PEG_TX#_4

T42

PEG_TX#_5

Y43

PEG_TX#_6

W46

PEG_TX#_7

W38

PEG_TX#_8

AD39

PEG_TX#_9

AC46

AC49

AC42

AH39

AE49

AH44

M45

PEG_TX_0

T38

PEG_TX_1

T46

PEG_TX_2

N50

PEG_TX_3

R51

PEG_TX_4

U43

PEG_TX_5

W42

PEG_TX_6

Y47

PEG_TX_7

Y39

PEG_TX_8

AC38

PEG_TX_9

AD47

PEG_TX_10

AC50

PEG_TX_11

AD43

PEG_TX_12

AG39

PEG_TX_13

AE50

PEG_TX_14

AH43

PEG_TX_15

12

12

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

LCD_DDCCLK

LCD_DDCDAT

8

R12624.9/FR12624.9/F

1 2

UMA

653Thursday, June 12, 2008

653Thursday, June 12, 2008

653Thursday, June 12, 2008

8

+VCC_PEG

1

hexainf@hotmail.com

GRATIS - FOR FREE

2

3

4

5

6

7

8

DDR_A_D[0..63]15

AA

BB

CC

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

U20D

U20D

AR43

SA_DQ_0

AW44

SA_DQ_1

BA45

SA_DQ_2

AY46

SA_DQ_3

AR41

SA_DQ_4

AR45

SA_DQ_5

AT42

SA_DQ_6

AW47

SA_DQ_7

BB45

SA_DQ_8

BF48

SA_DQ_9

BG47

SA_DQ_10

BJ45

SA_DQ_11

BB47

SA_DQ_12

BG50

SA_DQ_13

BH49

SA_DQ_14

BE45

SA_DQ_15

AW43

SA_DQ_16

BE44

SA_DQ_17

BG42

SA_DQ_18

BE40

SA_DQ_19

BF44

SA_DQ_20

BH45

SA_DQ_21

BG40

SA_DQ_22

BF40

SA_DQ_23

AR40

SA_DQ_24

AW40

SA_DQ_25

AT39

SA_DQ_26

AW36

SA_DQ_27

AW41

SA_DQ_28

AY41

SA_DQ_29

AV38

SA_DQ_30

AT38

SA_DQ_31

AV13

SA_DQ_32

AT13

SA_DQ_33

AW11

SA_DQ_34

AV11

SA_DQ_35

AU15

SA_DQ_36

AT11

SA_DQ_37

BA13

SA_DQ_38

BA11

SA_DQ_39

BE10

SA_DQ_40

BD10

SA_DQ_41

BD8

SA_DQ_42

AY9

SA_DQ_43

BG10

SA_DQ_44

AW9

SA_DQ_45

BD7

SA_DQ_46

BB9

SA_DQ_47

BB5

SA_DQ_48

AY7

SA_DQ_49

AT5

SA_DQ_50

AT7

SA_DQ_51

AY6

SA_DQ_52

BB7

SA_DQ_53

AR5

SA_DQ_54

AR8

SA_DQ_55

AR9

SA_DQ_56

AN3

SA_DQ_57

AM8

SA_DQ_58

AN10

SA_DQ_59

AT9

SA_DQ_60

AN9

SA_DQ_61

AM9

SA_DQ_62

AN11

SA_DQ_63

LE82GM965-SLA5T-MM#891181

LE82GM965-SLA5T-MM#891181

DDR_A_BS0

BB19

SA_BS_0

SA_BS_1

SA_BS_2

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVEN#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_WE#

BK19

BF29

BL17

AT45

BD44

BD42

AW38

AW13

BG8

AY5

AN6

AT46

BE48

BB43

BC37

BB16

BH6

BB2

AP3

AT47

BD47

BC41

BA37

BA16

BH7

BC1

AP2

BJ19

BD20

BK27

BH28

BL24

BK28

BJ27

BJ25

BL28

BA28

BC19

BE28

BG30

BJ16

BE18

AY20

BA19

DDR_A_BS1

DDR_A_BS2

DDR_A_CAS#

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_RAS#

DDR_A_WE#

DDR_A_BS015,16

DDR_A_BS115,16

DDR_A_BS215,16

DDR_A_CAS#15,16

DDR_A_DM[0..7]15

DDR_A_DQS[0..7]15

DDR_A_DQS#[0..7]15

DDR_A_MA[0..13]15,16

DDR_A_RAS#15,16

T38PADT38PAD

DDR_A_WE#15,16

DDR_B_D[0..63]15

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

U20E

U20E

AP49

SB_DQ_0

AR51

SB_DQ_1

AW50

SB_DQ_2

AW51

SB_DQ_3

AN51

SB_DQ_4

AN50

SB_DQ_5

AV50

SB_DQ_6

AV49

SB_DQ_7

BA50

SB_DQ_8

BB50

SB_DQ_9

BA49

SB_DQ_10

BE50

SB_DQ_11

BA51

SB_DQ_12

AY49

SB_DQ_13

BF50

SB_DQ_14

BF49

SB_DQ_15

BJ50

SB_DQ_16

BJ44

SB_DQ_17

BJ43

SB_DQ_18

BL43

SB_DQ_19

BK47

SB_DQ_20

BK49

SB_DQ_21

BK43

SB_DQ_22

BK42

SB_DQ_23

BJ41

SB_DQ_24

BL41

SB_DQ_25

BJ37

SB_DQ_26

BJ36

SB_DQ_27

BK41

SB_DQ_28

BJ40

SB_DQ_29

BL35

SB_DQ_30

BK37

SB_DQ_31

BK13

SB_DQ_32

BE11

SB_DQ_33

BK11

SB_DQ_34

BC11

SB_DQ_35

BC13

SB_DQ_36

BE12

SB_DQ_37

BC12

SB_DQ_38

BG12

SB_DQ_39

BJ10

SB_DQ_40

BL9

SB_DQ_41

BK5

SB_DQ_42

BL5

SB_DQ_43

BK9

SB_DQ_44

BK10

SB_DQ_45

BJ8

SB_DQ_46

BJ6

SB_DQ_47

BF4

SB_DQ_48

BH5

SB_DQ_49

BG1

SB_DQ_50

BC2

SB_DQ_51

BK3

SB_DQ_52

BE4

SB_DQ_53

BD3

SB_DQ_54

BJ2

SB_DQ_55

BA3

SB_DQ_56

BB3

SB_DQ_57

AR1

SB_DQ_58

AT3

SB_DQ_59

AY2

SB_DQ_60

AY3

SB_DQ_61

AU2

SB_DQ_62

AT2

SB_DQ_63

LE82GM965-SLA5T-MM#891181

LE82GM965-SLA5T-MM#891181

DDR_B_BS0

AY17

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVEN#

SB_WE#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

BG18

BG36

BE17

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AT50

BD50

BK46

BK39

BJ12

BL7

BE2

AV2

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

AV16

AY18

BC17

DDR_B_BS1

DDR_B_BS2

DDR_B_CAS#

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_RAS#

DDR_B_WE#

DDR_B_BS015,16

DDR_B_BS115,16

DDR_B_BS215,16

DDR_B_CAS#15,16

DDR_B_DM[0..7]15

DDR_B_DQS[0..7]15

DDR_B_DQS#[0..7]15

DDR_B_MA[0..13]15,16

DDR_B_RAS#15,16

T39PADT39PAD

DDR_B_WE#15,16

For EA test use

76

DD

1

ET42ET42

ET37ET37

ET31ET31

ET39ET39

ET32ET32

ET44ET44

ET28ET28

ET27ET27

ET23ET23

ET26ET26

ET40ET40

DDR_A_CAS#

1

DDR_A_RAS#

1

DDR_A_WE#

1

DDR_CS0_DIMMA#

1

DDR_A_MA9

1

DDR_A_MA13

1

DDR_A_DQS0

1

DDR_A_DQS#0

1

DDR_A_D63

1

DDR_A_D55

1

DDR_A_D22

1

DDR_CS0_DIMMA#6,15,16 DDR_CS3_DIMMB#6,15,16

2

3

4

76

5

For EA test use

DDR_B_CAS#

1

ET36ET36

DDR_B_RAS#

1

ET29ET29

DDR_B_WE#

1

ET33ET33

DDR_CS3_DIMMB#

1

ET38ET38

DDR_B_MA11

1

ET35ET35

DDR_B_MA1

1

ET41ET41

DDR_B_DQS0

1

ET24ET24

DDR_B_DQS#0

1

ET25ET25

DDR_B_D6

1

ET30ET30

DDR_B_D8

1

ET34ET34

DDR_B_D41

1

ET43ET43

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Date:Sheet of

Date:Sheet of

6

Date:Sheet of

COMPUTER

Crestline (DDR2)

Crestline (DDR2)

Crestline (DDR2)

VM9/VM81A

VM9/VM81A

VM9/VM81A

7

753Friday, May 30, 2008

753Friday, May 30, 2008

753Friday, May 30, 2008

8

5 4 3 2

hexainf@hotmail.com

GRATIS - FOR FREE

+1.05V_VCCP

DD

+1.8V_SUS

CC

+1.05V_VCCP

BB

AA

U20G

U20G

AT35

VCC_1

AT34

VCC_2

AH28

VCC_3

AC32

VCC_5

AC31

VCC_4

AK32

VCC_6

AJ31

VCC_7

AJ28

VCC_8

AH32

VCC_9

AH31

VCC_10

AH29

VCC_11

AF32

VCC_12

R30

VCC_13

AU32

VCC_SM_1

AU33

VCC_SM_2

AU35

VCC_SM_3

AV33

VCC_SM_4

AW33

VCC_SM_5

AW35

VCC_SM_6

AY35

VCC_SM_7

BA32

VCC_SM_8

BA33

VCC_SM_9

BA35

VCC_SM_10

BB33

VCC_SM_11

BC32

VCC_SM_12

BC33

VCC_SM_13

BC35

VCC_SM_14

BD32

VCC_SM_15

BD35

VCC_SM_16

BE32

VCC_SM_17

BE33

VCC_SM_18

BE35

VCC_SM_19

BF33

VCC_SM_20

BF34

VCC_SM_21

BG32

VCC_SM_22

BG33

VCC_SM_23

BG35

VCC_SM_24

BH32

VCC_SM_25

BH34

VCC_SM_26

BH35

VCC_SM_27

BJ32

VCC_SM_28

BJ33

VCC_SM_29

BJ34

VCC_SM_30

BK32

VCC_SM_31

BK33

VCC_SM_32

BK34

VCC_SM_33

BK35

VCC_SM_34

BL33

VCC_SM_35

AU30

VCC_SM_36

R20

VCC_AXG_1

T14

VCC_AXG_2

W13

VCC_AXG_3

W14

VCC_AXG_4

Y12

VCC_AXG_5

AA20

VCC_AXG_6

AA23

VCC_AXG_7

AA26

VCC_AXG_8

AA28

VCC_AXG_9

AB21

VCC_AXG_10

AB24

VCC_AXG_11

AB29

VCC_AXG_12

AC20

VCC_AXG_13

AC21

VCC_AXG_14

AC23

VCC_AXG_15

AC24

VCC_AXG_16

AC26

VCC_AXG_17

AC28

VCC_AXG_18

AC29

VCC_AXG_19

AD20

VCC_AXG_20

AD23

VCC_AXG_21

AD24

VCC_AXG_22

AD28

VCC_AXG_23

AF21

VCC_AXG_24

AF26

VCC_AXG_25

AA31

VCC_AXG_26

AH20

VCC_AXG_27

AH21

VCC_AXG_28

AH23

VCC_AXG_29

AH24

VCC_AXG_30

AH26

VCC_AXG_31

AD31

VCC_AXG_32

AJ20

VCC_AXG_33

AN14

VCC_AXG_34

LE82GM965-SLA5T-MM#891181

LE82GM965-SLA5T-MM#891181

VCC CORE

VCC CORE

POWER

POWER

VCC SMVCC GFX

VCC SMVCC GFX

VCC_AXG_NCTF_1

VCC_AXG_NCTF_2

VCC_AXG_NCTF_3

VCC_AXG_NCTF_4

VCC_AXG_NCTF_5

VCC_AXG_NCTF_6

VCC_AXG_NCTF_7

VCC_AXG_NCTF_8

VCC_AXG_NCTF_9

VCC_AXG_NCTF_10

VCC_AXG_NCTF_11

VCC_AXG_NCTF_12

VCC_AXG_NCTF_13

VCC_AXG_NCTF_14

VCC_AXG_NCTF_15

VCC_AXG_NCTF_16

VCC_AXG_NCTF_17

VCC_AXG_NCTF_18

VCC_AXG_NCTF_19

VCC_AXG_NCTF_20

VCC_AXG_NCTF_21

VCC_AXG_NCTF_22

VCC_AXG_NCTF_23

VCC_AXG_NCTF_24

VCC_AXG_NCTF_25

VCC_AXG_NCTF_26

VCC_AXG_NCTF_27

VCC_AXG_NCTF_28

VCC_AXG_NCTF_29

VCC_AXG_NCTF_30

VCC_AXG_NCTF_31

VCC_AXG_NCTF_32

VCC_AXG_NCTF_33

VCC_AXG_NCTF_34

VCC_AXG_NCTF_35

VCC_AXG_NCTF_36

VCC_AXG_NCTF_37

VCC_AXG_NCTF_38

VCC_AXG_NCTF_39

VCC_AXG_NCTF_40

VCC_AXG_NCTF_41

VCC_AXG_NCTF_42

VCC_AXG_NCTF_43

VCC_AXG_NCTF_44

VCC_AXG_NCTF_45

VCC_AXG_NCTF_46

VCC_AXG_NCTF_47

VCC_AXG_NCTF_48

VCC_AXG_NCTF_49

VCC_AXG_NCTF_50

VCC_AXG_NCTF_51

VCC_AXG_NCTF_52

VCC_AXG_NCTF_53

VCC_AXG_NCTF_54

VCC_AXG_NCTF_55

VCC GFX NCTF

VCC GFX NCTF

VCC_AXG_NCTF_56

VCC_AXG_NCTF_57

VCC_AXG_NCTF_58

VCC_AXG_NCTF_59

VCC_AXG_NCTF_60

VCC_AXG_NCTF_61

VCC_AXG_NCTF_62

VCC_AXG_NCTF_63

VCC_AXG_NCTF_64

VCC_AXG_NCTF_65

VCC_AXG_NCTF_66

VCC_AXG_NCTF_67

VCC_AXG_NCTF_68

VCC_AXG_NCTF_69

VCC_AXG_NCTF_70

VCC_AXG_NCTF_71

VCC_AXG_NCTF_72

VCC_AXG_NCTF_73

VCC_AXG_NCTF_74

VCC_AXG_NCTF_75

VCC_AXG_NCTF_76

VCC_AXG_NCTF_77

VCC_AXG_NCTF_78

VCC_AXG_NCTF_79

VCC_AXG_NCTF_80

VCC_AXG_NCTF_81

VCC_AXG_NCTF_82

VCC_AXG_NCTF_83

VCC_SM_LF1

VCC_SM_LF2

VCC_SM_LF3

VCC_SM_LF4

VCC_SM_LF5

VCC_SM_LF6

VCC_SM_LF7

VCC SM LF

VCC SM LF

T17

T18

T19

T21

T22

T23

T25

U15

U16

U17

U19

U20

U21

U23

U26

V16

V17

V19

V20

V21

V23

V24

Y15

Y16

Y17

Y19

Y20

Y21

Y23

Y24

Y26

Y28

Y29

AA16

AA17

AB16

AB19

AC16

AC17

AC19

AD15

AD16

AD17

AF16

AF19

AH15

AH16

AH17

AH19

AJ16

AJ17

AJ19

AK16

AK19

AL16

AL17

AL19

AL20

AL21

AL23

AM15

AM16

AM19

AM20

AM21

AM23

AP15

AP16

AP17

AP19

AP20

AP21

AP23

AP24

AR20

AR21

AR23

AR24

AR26

V26

V28

V29

Y31

AW45

BC39

BE39

BD17

BD4

AW8

AT6

Layout Note:

370 mils from edge.

Layout Note:

370 mils from edge.

C192

C192

0.1U

0.1U

10

10

12

+

+

C114

C114

*220U_NC

*220U_NC

7343

7343

2.5

2.5

12

C170

C170

0.1U

0.1U

10

10

12

C191

C191

0.1U

0.1U

10

10

12

+

+

C124

C124

*220U_NC

*220U_NC

7343

7343

2.5

2.5

Layout Note:

Inside GMCH cavity for VCC_AXG.

12

C167

C167

0.1U

0.1U

10

10

VCCSM_LF1

VCCSM_LF2

VCCSM_LF3

VCCSM_LF4

VCCSM_LF5

VCCSM_LF6

VCCSM_LF7

12

+1.05V_VCCP

+

+

55

12

C161

C161

0.47U

0.47U

0603

0603

10

10

12

C219

C219

0.22U

0.22U

0603

0603

10

10

12

C136

C136

*220U_NC

*220U_NC

7343

7343

6.3

6.3

65

12

+

+

C468

C468

220U

220U

7343

7343

2.5

2.5

12

+

+

C477

C477

*220U_NC

*220U_NC

7343

7343

6.3

6.3

12

12

C182

C182

1U

1U

0603

0603

10

10

C158

C158

10U

10U

0603

0603

6.3

6.3

12

12

C218

C218

0.22U

0.22U

0603

0603

10

10

+3.3V_RUN

12

C151

C151

22U

22U

0805

0805

4

4

Layout Note:

Inside GMCH cavity.

+1.05V_VCCP

+1.05V_VCCP

12

C150

C150

22U

22U

0805

0805

4

4

+1.05V_VCCP

Non-iAMT

Layout Note:

Place close to GMCH edge.

12

C215

C215

C216

C216

1U

1U

0.47U

0.47U

0603

0603

0603

0603

10

10

10

10

R8610R8610

1 2

12

C155

C155

0.22U

0.22U

0603

0603

10

10

12

C178

C178

0.1U

0.1U

10

10

12

C458

C458

22U

22U

0805

0805

4

4

12

C202

C202

1U

1U

0603

0603

10

10

D8

+VCC_GMCH_L

12

C181

C181

0.22U

0.22U

0603

0603

10

10

Layout Note:

Inside GMCH cavity.

12

12

D8

SDMK0340L-7-F

SDMK0340L-7-F

12

C168

C168

0.1U

0.1U

10

10

12

C179

C177

C177

0.1U

0.1U

10

10

C188

C188

0.22U

0.22U

0603

0603

10

10

C179

0.1U

0.1U

10

10

12

C187

C187

0.22U

0.22U

0603

0603

10

10

+1.8V_SUS

12

Layout Note:

Place C195 where LVDS

and DDR2 taps.

C204

C204

0.1U

0.1U

10

10

U20F

21

U20F

AB33

VCC_NCTF_1

AB36

VCC_NCTF_2

AB37

VCC_NCTF_3

AC33

VCC_NCTF_4

AC35

VCC_NCTF_5

AC36

VCC_NCTF_6

AD35

VCC_NCTF_7

AD36

VCC_NCTF_8

AF33

VCC_NCTF_9

AF36

VCC_NCTF_10

AH33

VCC_NCTF_11

AH35

VCC_NCTF_12

AH36

VCC_NCTF_13

AH37

VCC_NCTF_14

AJ33

VCC_NCTF_15

AJ35

VCC_NCTF_16

AK33

VCC_NCTF_17

AK35

VCC_NCTF_18

AK36

VCC_NCTF_19

AK37

VCC_NCTF_20

AD33

VCC_NCTF_21

AJ36

VCC_NCTF_22

AM35

VCC_NCTF_23

AL33

VCC_NCTF_24

AL35

VCC_NCTF_25