Page 1

5

hexainf@hotmail.com

D D

4

3

2

1

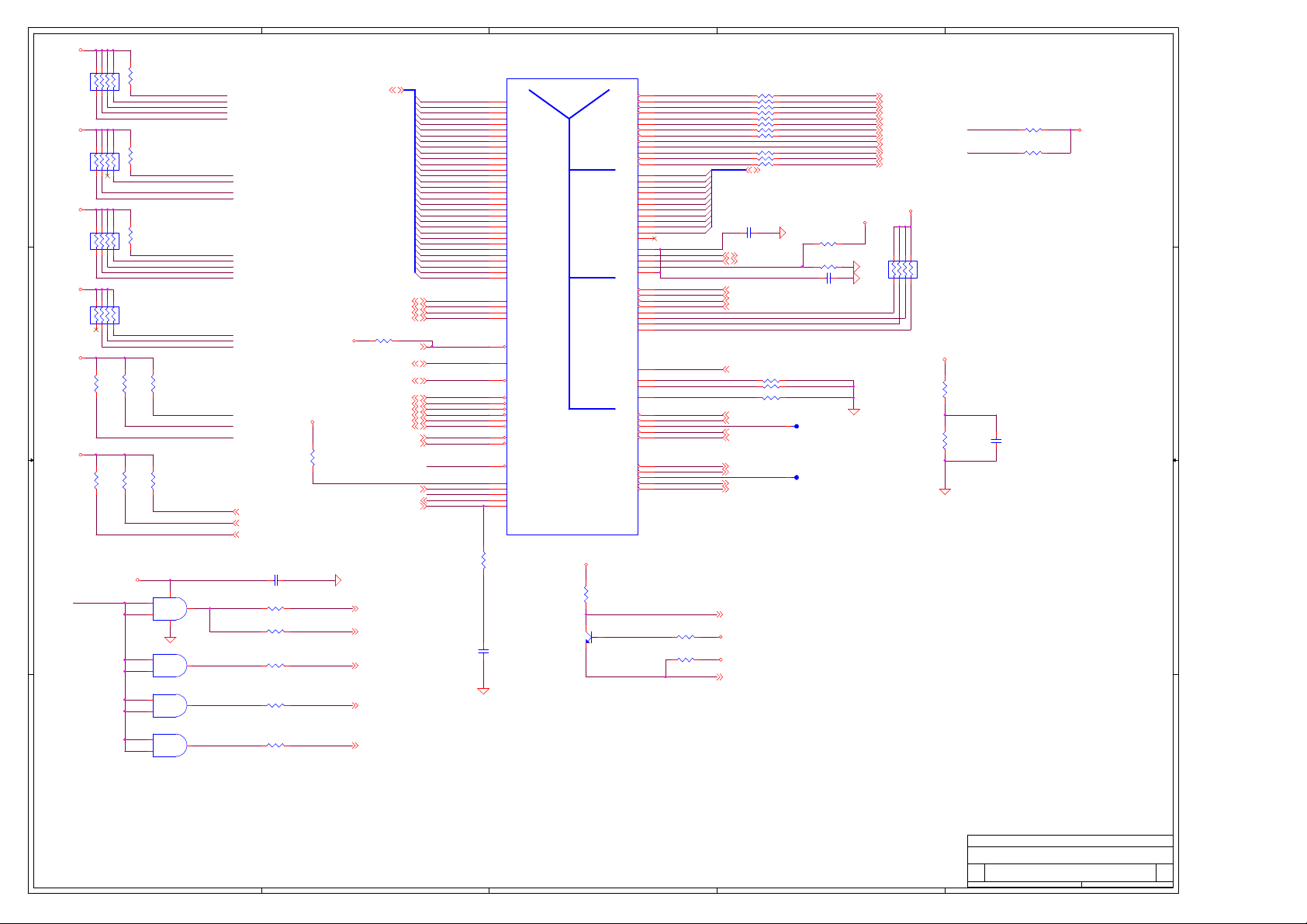

LKB-ADDs, Plus Schematic

REV : A02

C C

@ : Depop Component for All

1@ : Pop Component for Lindbergh Series

2@ : Pop Component for Kapalua series

3@ : Depop Component for Lindbergh Plus series

4@ : Pop Component for Lindbergh Plus series

B B

DDQ12/LA1901 Schematic with Capture CIS and Function field

uFCPGA Banias

A A

01-02-2004

REV: 3.0

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

DDQ12/11/01 with LA-1901

1

1 59Wednesday, January 07, 2004

3.0

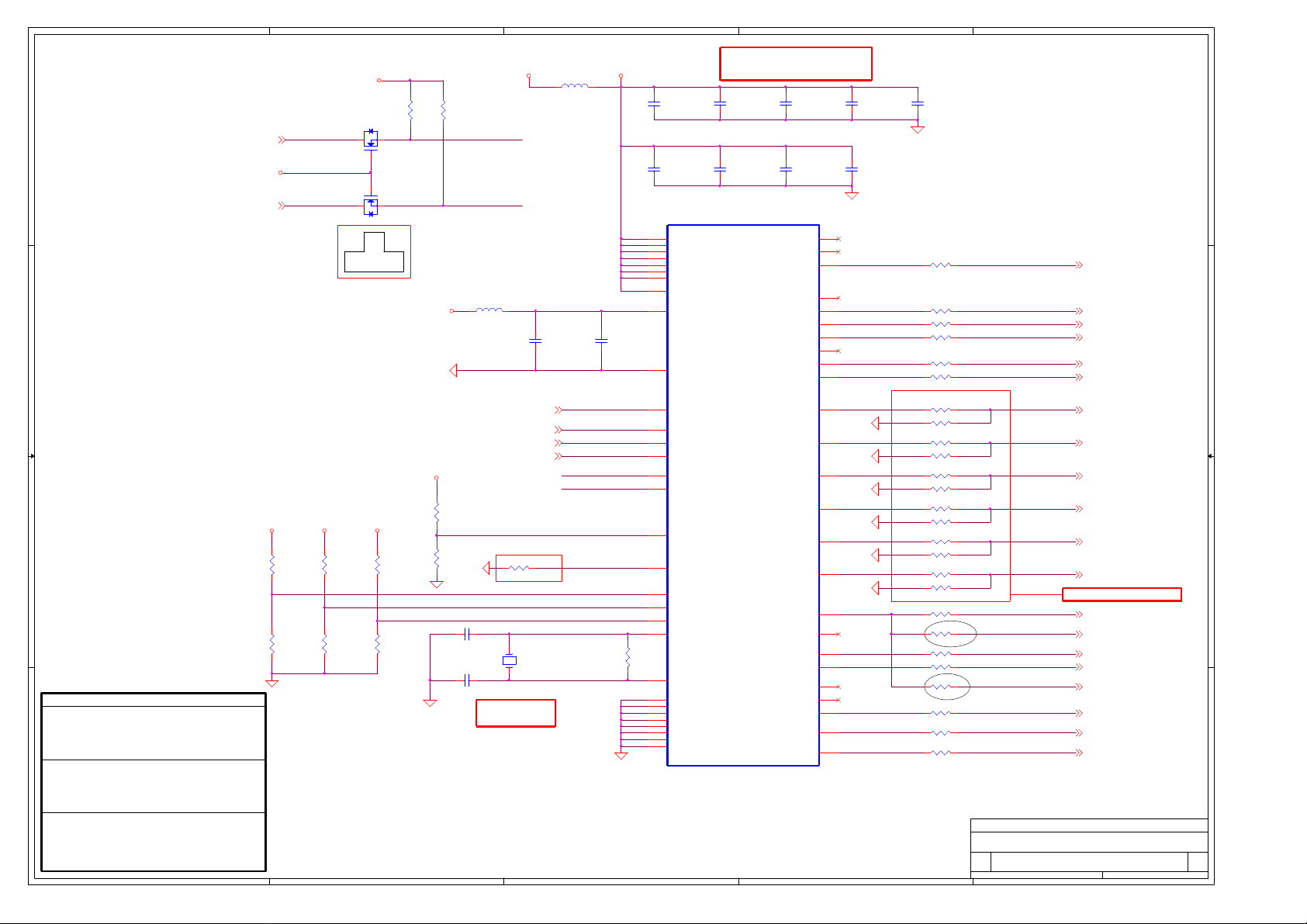

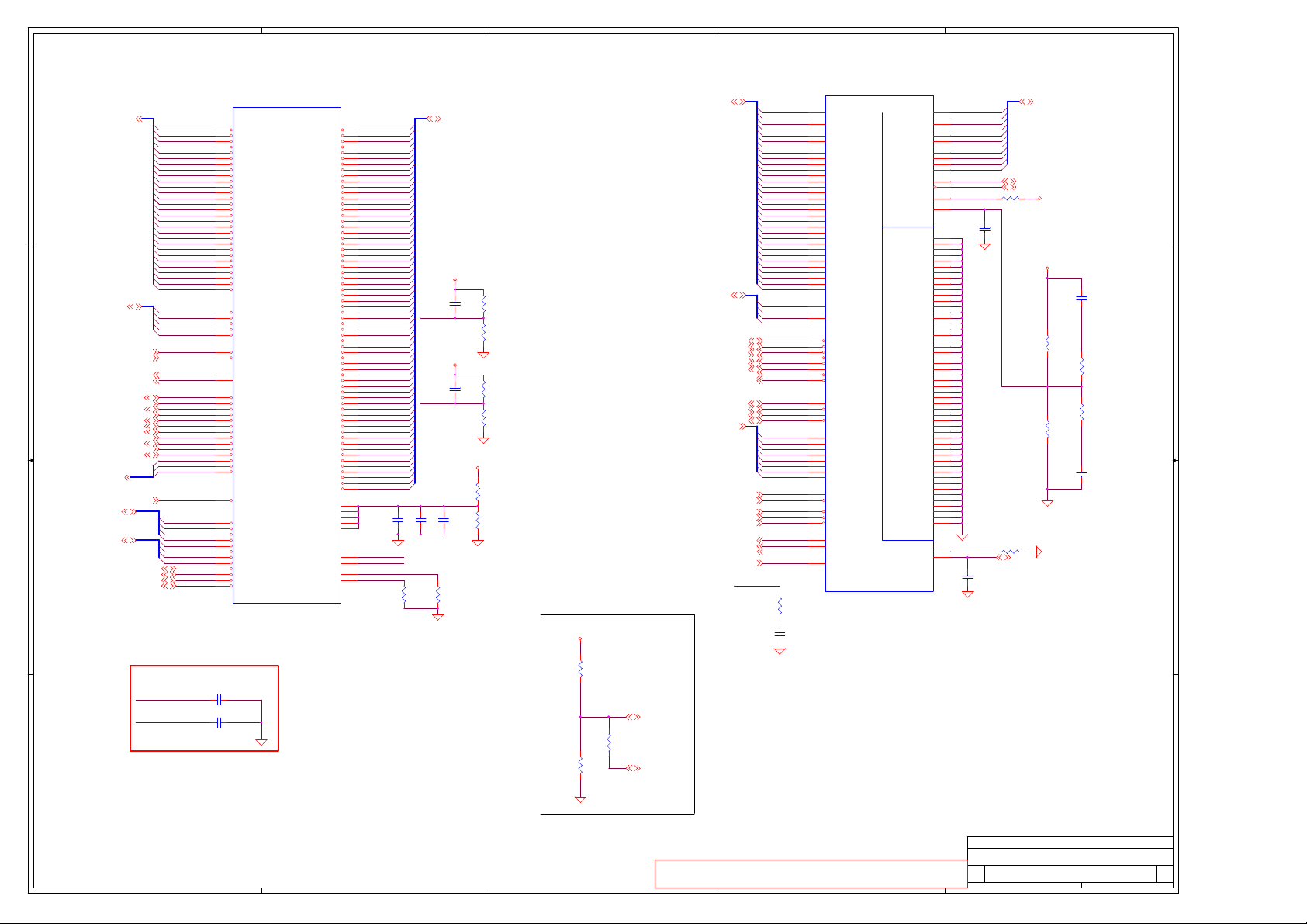

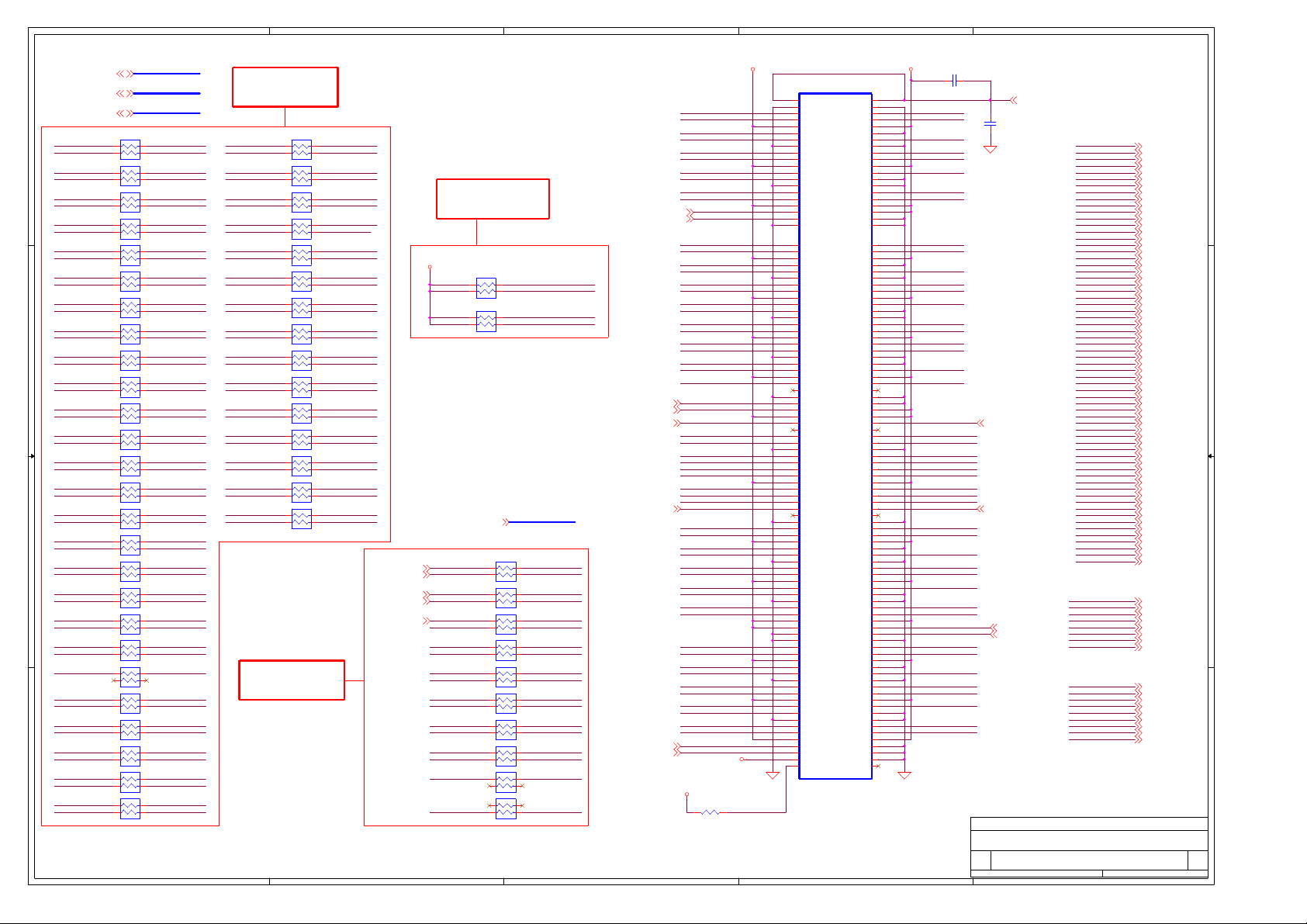

Page 2

5

hexainf@hotmail.com

Compal confidential

4

3

2

1

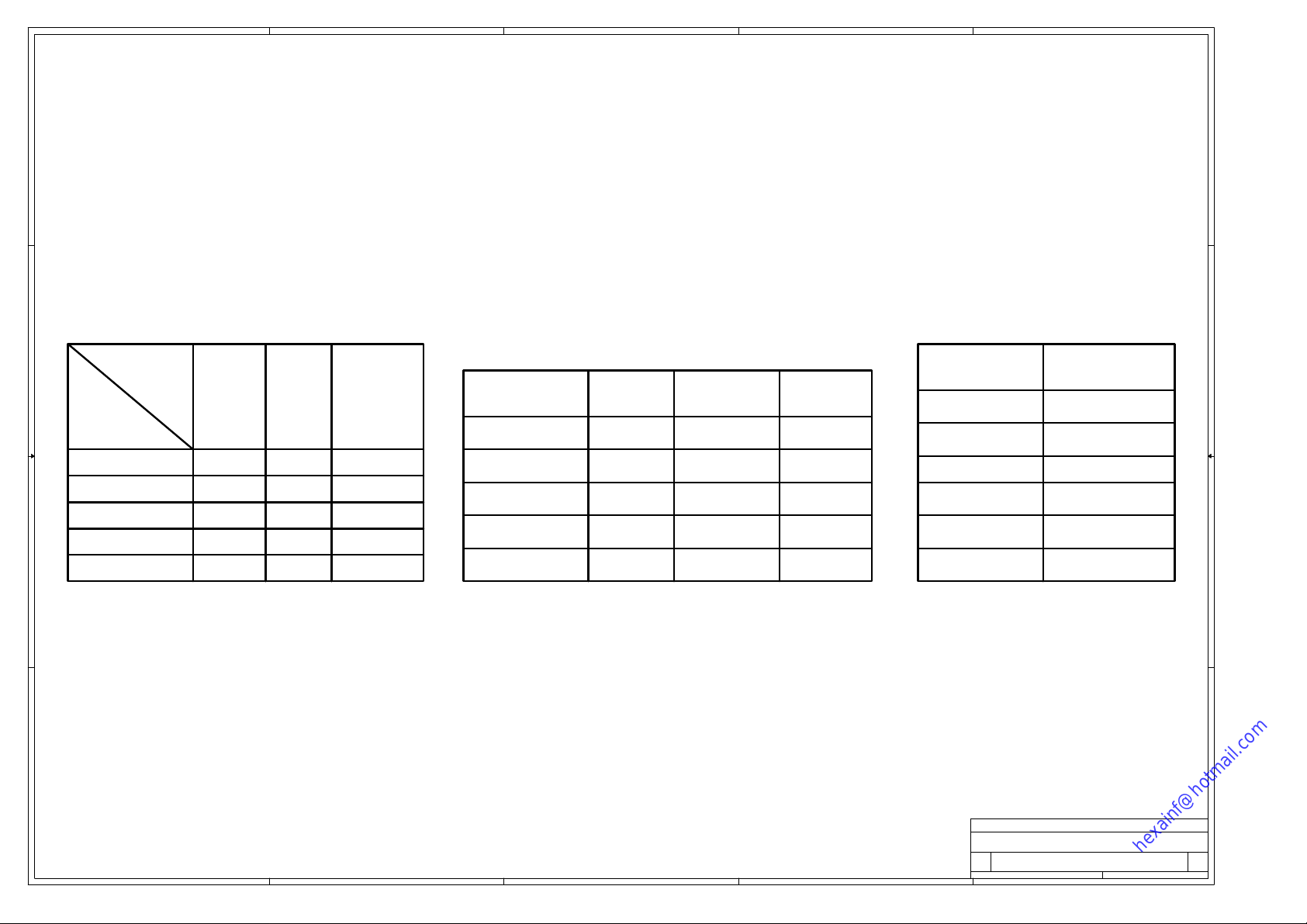

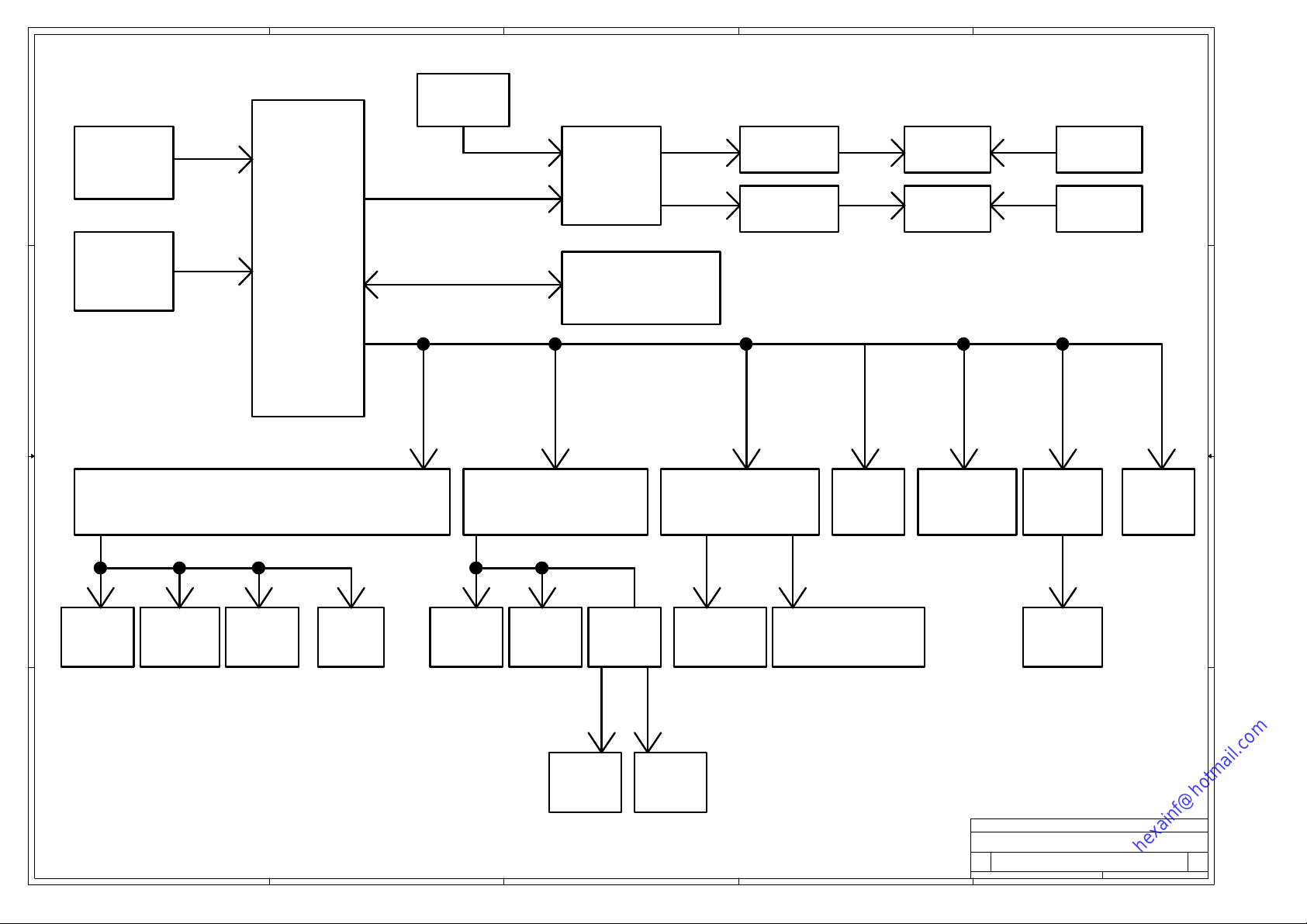

Block Diagram

D D

ADM1032 Thermal sensor

page 13

Banias

uFCPGA CPU

page 7,8,9

Fan Control

page 13

CK408

page 6

VGA

Board

HA#(3..31)

CRT CONN.

& TV-OUT

page 17

AGP4X(1.5V)

System Bus

400MHz

ODEM-2

MCH-M

593 FC-BGA

AGP CONN.

C C

page 16

HD#(0..63)

page

10,11,12

Memory

BUS(DDR)

2.5V 100 / 133 / 166MHz

PC1600 / PC2100 / PC2700

SO-DIMM X2

BANK 0, 1, 2, 3

page 14,15

Clock Generator

HUB Link

DOCKING

PORT

PAGE 33

B B

LAN

BCM5705M

BCM4410

Transformer

RJ45

BUFFER

USB

IDSEL:AD20

(PIRQA/B#,GNT#2,REQ#2)

page 27

page 28

page 28

PAGE 32

CardBus Controller

PCI7510 / 4510

1394, Smart

card

page30

DOCKING

MINI PCI

page 31

3.3V 33MHz

page 29

Slot 0

page30

X BUS

PCI BUS

LPC BUS

3.3V 33MHz

SST39VF080

A A

5

page 36

4

COM

Touch Pad

page 36

1.8V

66MHz

266MB/S

Macallen

LPC to X-BUS

& Super I/O

page

34,35

ICH4-M

421 BGA

LPT

page 37page 37

Int.KBD

page

18,19,20,21

48MHz / 480Mb

page 36

3

3.3V 24.576MHz

3.3V ATA100

ATA100

CDROM

USB

FDD

USB2.0

page 22

page 22

page 25

page 26

page 33

ATA100

HDD

page 19

USB

USBPORT 0

USBPORT 1

USBPORT 2

USBPORT 3

USBPORT 4

USBPORT 5

AC-LINK

MDC

page 26

AC97

Codec

STAC9750

page 23

AMP& Phone

Jack

page 24

BACK

BT

BACK

DOG

MOD

DOCK

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

2

Date: Sheet of

Compal Electronics, Inc.

DC IN

BATT

IN

1.2V/1.8V

page

42

page

43

page

44

1.5V/1.05V(+VCCP)

page 45

1.25V/2.5V

page

46

VCORE

page 47

5V/3.3V

page 48

CHARGER

Block Diagram

DDQ12/11/01 with LA-1901

1

page

49,50

2 59Wednesday, January 07, 2004

3.0

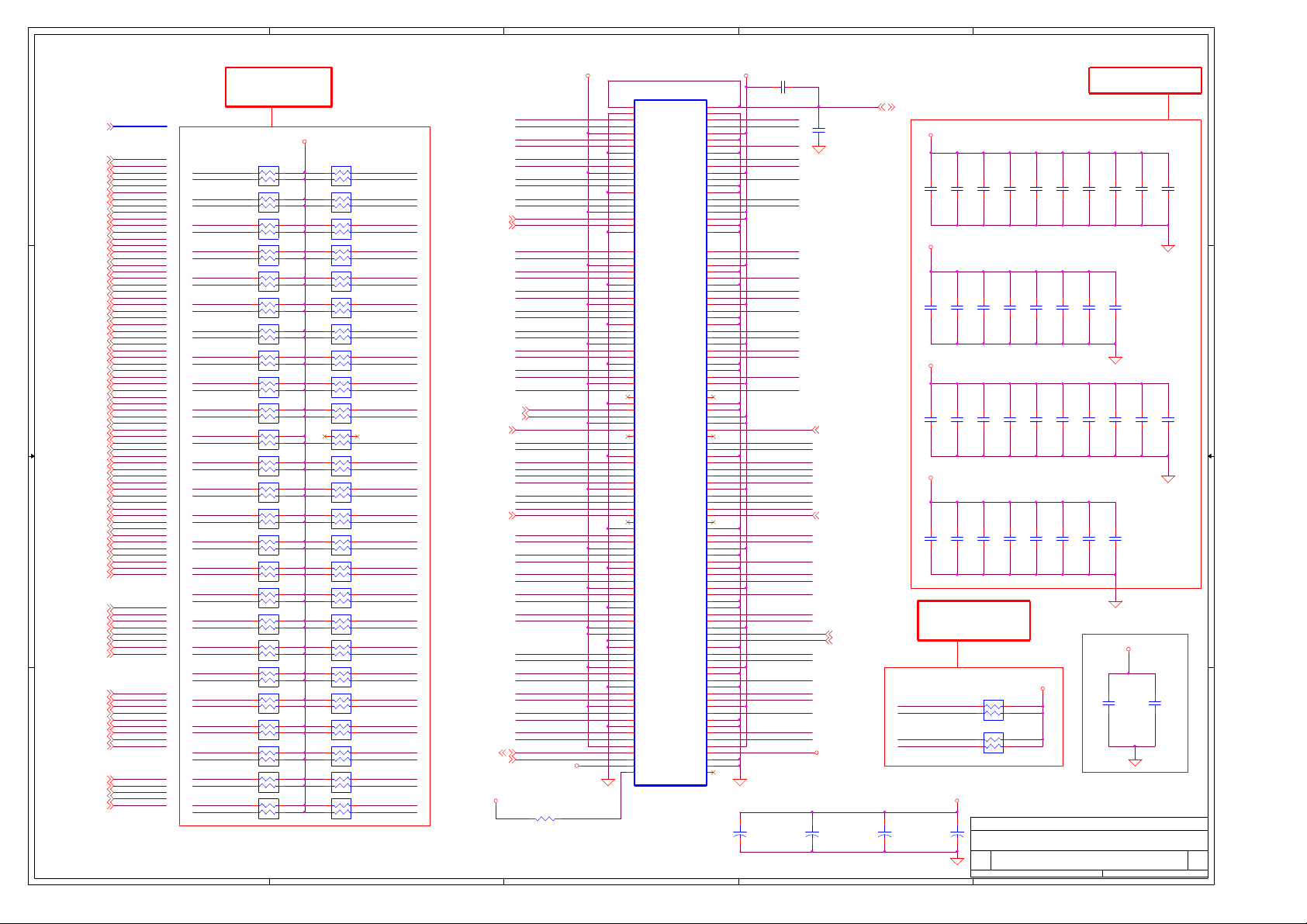

Page 3

5

hexainf@hotmail.com

D D

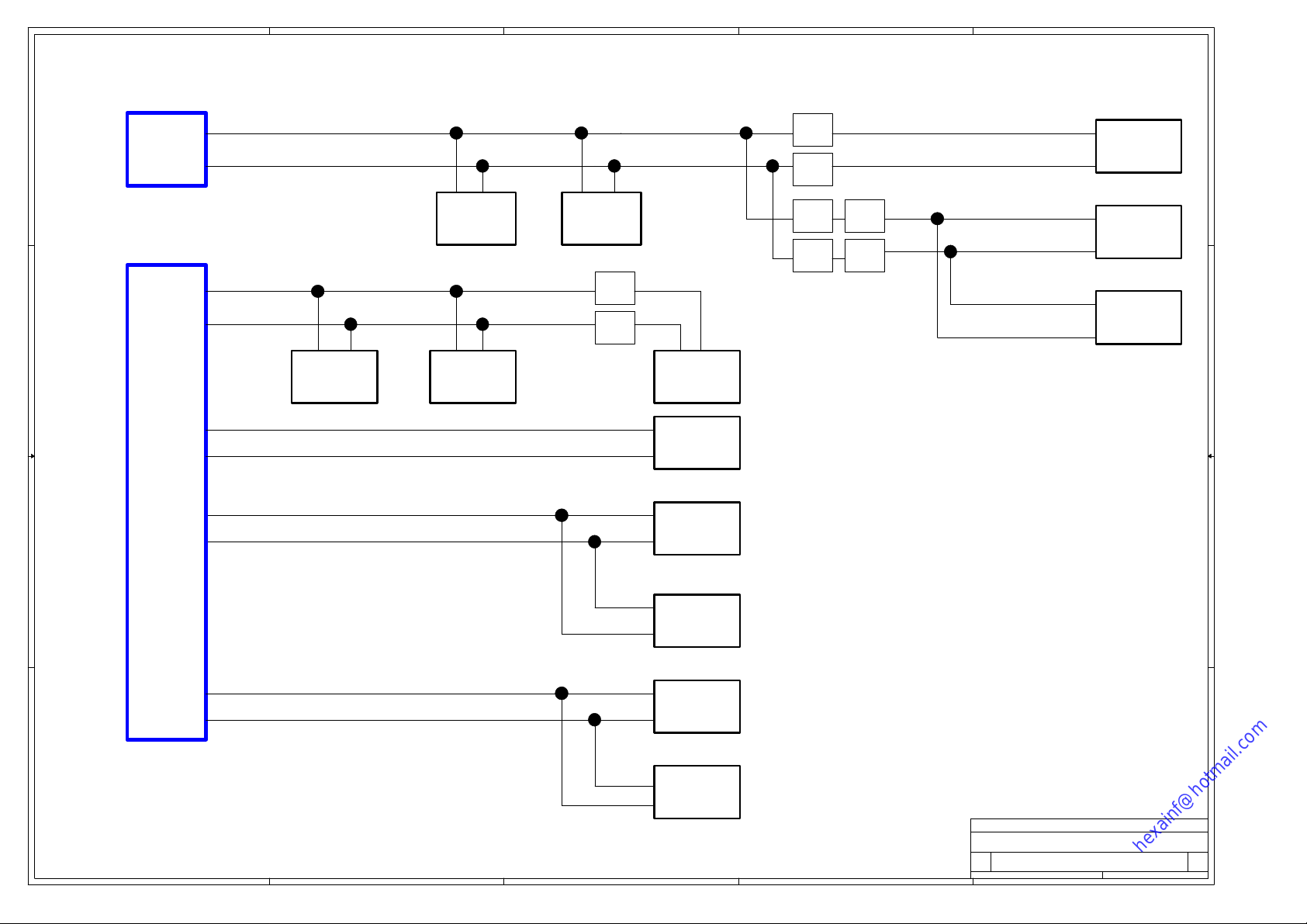

PM TABLE

C C

power

plane

State

S0

S1

S3

S5 S4/AC

B B

S5 S4/AC don't exist

+3VALW

+5VALW

ON

ON

ON

ON

+3VSUS

+5VSUS

+2.5V_MEM

+1.5VSUS

ON

ON

ON

OFF

OFF

4

+5VRUN

+3VRUN

+1.8VRUN

+1.5VRUN

+1.2VRUN

+VCC_CORE

+VCCP

+12V

ON

ON

OFF

OFF

OFFOFF

TABLE

PCI

PCI DEVICE

CARD BUS

LAN

DOCK

MINI PCI

VGA

3

IDSEL

AD17

AD16

AD24

AD19

REQ#/GNT#

1

4

0

3

PIRQ

D,C

C

B

D,B(NP)

A,B(NP)

2

TABLE

USB

1

USB PORT# DESTINATION

0

1

2

3

4

5

BACK

BLUETOOTH

BACK

DOG

MOD

DOCK

A A

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

Compal Electronics, Inc.

Index and Config.

DDQ12/11/01 with LA-1901

3 59Wednesday, January 07, 2004

1

3.0

Page 4

5

hexainf@hotmail.com

4

3

2

1

RBAT

D D

ADAPTER

+RTC_PWR

+5VALW

+5VSUS

+RTCSRC

PWR_SRC

+3.3VRTC

+3VALW

+3VSUS

BATTERY

DOCK _PWR_SRC

C C

SUS_ON

+5VSUS

B B

RUN_ON RUN_ON

SUS_ON

+3VSRC

SUSPWROK_5V

SUSPWROK_5V

+2.5VMEMP

PJP8,PJP10

ENAB_1.25V

RUNPWROK

+VCCP

RUNPWROK

+VCC_CORE

SUSPWROK_5V

+1.5VSUS

RUN_ON

EN_12V

+12V

+5VMOD

A A

VDDA+5VRUN +2.5V_MEM+3VSUS

+3VRUN

V3P3LAN

+1.2VRUN

RUNPWROK

V_1P25V_DDR_VTT

RUN_ON

+1.8VRUN

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

+1.5VRUN+5VHDD

Compal Electronics, Inc.

Power Rail

DDQ12/11/01 with LA-1901

4 59Wednesday, January 07, 2004

1

3.0

Page 5

5

hexainf@hotmail.com

4

3

2

1

+3VRUN

ICH_SMBCLK

D D

ICH4

ICH_SMBDATA

+3VSUS

7002

7002

CK_SCLK

CK_SDATA

CLK GEN.

DIMM0

CLK_SMB

DAT_SMB

C C

24C05

+3VALW

ADM1032

DIMM1

7002

7002

DH PORT

7002

7002

7002

7002

V_3P3_LAN

LAN_SMBCLK

LAN_SMBDATA

LOM

MPCI

DOCK_SMB_CLK

SIO

DOCK_SMB_DAT

+5VALW

DOCKING

Macallen

SBAT_SMBCLK

SBAT_SMBDAT

B B

+5VALW

2'nd

BATTERY

VGA

PBAT_SMBCLK

1'nd

PBAT_SMBDAT

A A

+5VALW

BATTERY

CHARGER

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

Compal Electronics, Inc.

SMBUS TOPOLOGY

DDQ12/11/01 with LA-1901

5 59Wednesday, January 07, 2004

1

3.0

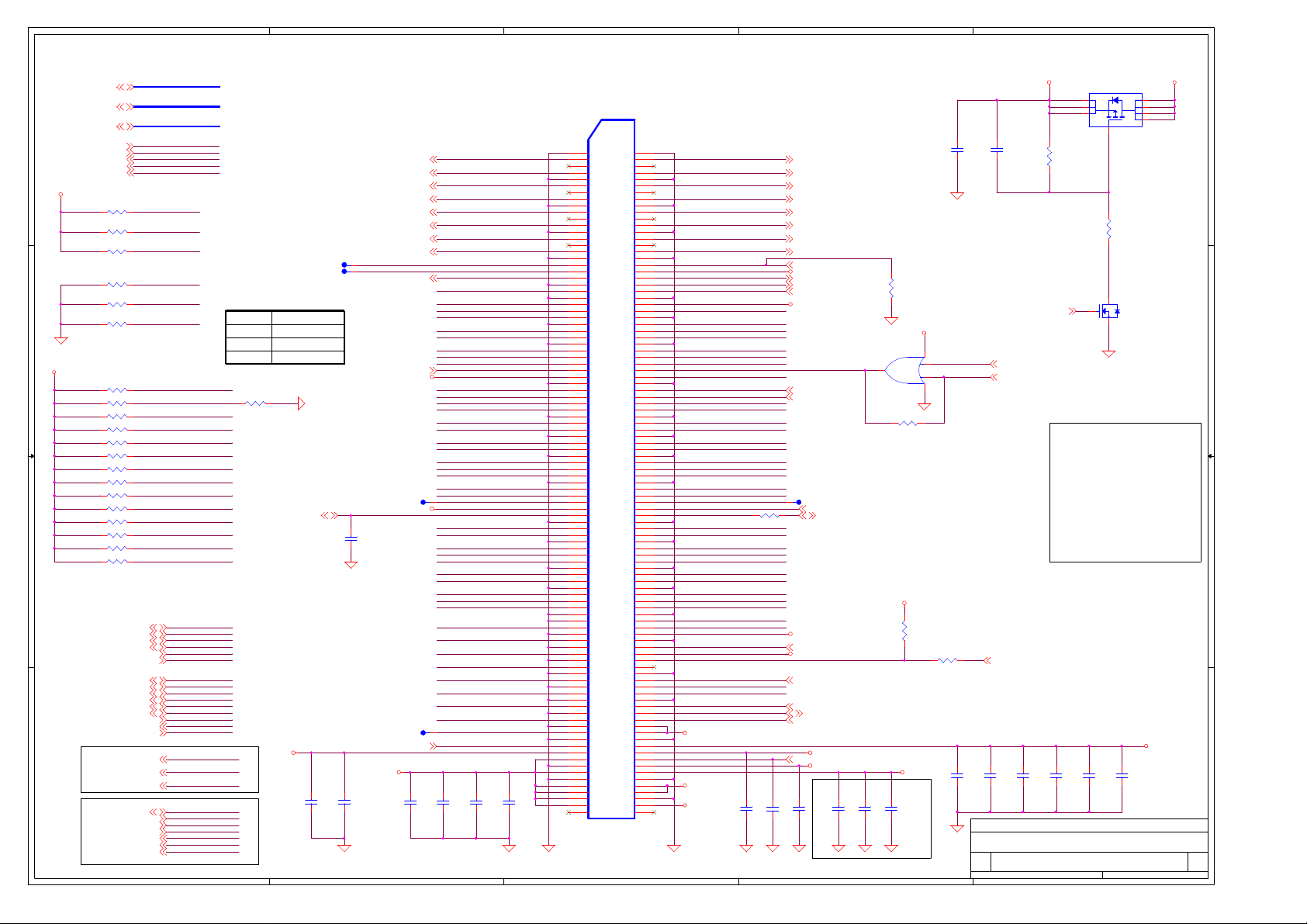

Page 6

5

4

3

2

1

Place near each pin

+3VRUN

R57

D D

ICH_SMBDATA<<14,15,19,31>>

ICH_SMBCLK<<14,15,19,31>>

ICH_SMBDATA

+3VRUN

ICH_SMBCLK

D

1 3

2

2

1 3

D

S

Q6

2N7002_SOT23~L

G

G

Q8

2N7002_SOT23~L

S

12

R61

100K_0402_5%~L

100K_0402_5%~L

12

CK_SDATA

CK_SCLK

+3VRUN

1 2

BLM21PG600SN1D_0805~L

D

1

3

G

C C

+3VRUN

B B

R96

1K_0402_5%~L

1 2

R91

1K_0402_5%~L

@

1 2

+3VRUN

R95

1K_0402_5%~L

@

1 2

R90

1K_0402_5%~L

1 2

S2 S1 S0 CPU 3V66[0..4] 3V66_5/66IN

1 0 0 66 66IN 66 Input

1 0 1 100 66IN 66 Input

2

2N7002

+3VRUN

1 2

1 2

S

R65

1K_0402_5%~L

@

R66

1K_0402_5%~L

+3VRUN

CK_VDD_MAIN

12

R76

10K_0402_5%~L

R69

1K_0402_5%~L

@

1 2

10P_0402_50V8J~L@

10P_0402_50V8J~L@

L29

BLM11A601S_0603~L

1 2

1 2

C90

12

C93

12

Place crystal within

500 mils of CK408

W=20 mils

1

C81

10U_1206_6.3V7K~L

2

H_STP_CPU#<<20,47>>

H_STP_PCI#<<20>>

CK_VTT_PG#<<38>>

ICH_SLP_S1#<<20>>

MULT0

Please closely pin42

R67

475_0603_1%~L

12

X1

14.31818MHz_20P_1BX14318CC1A~L

1 1 0 200 66IN 66 Input

1 1 1 133 66IN 66 Input

0 0 0 66 66 66 Input

A A

0 0 1 100 66 66 Input

CK_VDD_MAIN

L33

CLK_VDD_CORE

1

C80

0.1U_0402_16V4Z~L

2

H_STP_CPU# CK_CPU0

H_STP_PCI#

CK_VTT_PG#

ICH_SLP_S1#

CK_SCLK

CK_SDATA

CLKIREF

CLKSEL0

CLKSEL1

CLKSEL2

CK_XTAL_OUT

CK_XTAL_IN

12

R89

CK_VDD_MAIN

2

C89

10U_1206_6.3V7K~L

1

1

C88

0.1U_0402_10V6K~L

2

U8

1

VDD_REF

8

VDD_PCI

14

VDD_PCI

19

VDD_3V66

32

VDD_3V66

46

VDD_CPU

50

VDD_CPU

37

VDD_48MHZ

26

VDD_CORE

27

GND_CORE

53

CPU_STOP#

34

PCI_STOP#

28

VTT_PWRGD#

25

PWR_DWN#

30

SCLK

29

SDATA

43

MULT0

42

IREF

54

SEL0

55

SEL1

40

SEL2

3

XTAL_OUT

@

2M_0603_5%~L

2

XTAL_IN

4

GND_REF

9

GND_PCI

15

GND_PCI

20

GND_3V66

31

GND_3V66

36

GND_48MHZ

41

GND_IREF

47

GND_CPU

CY28346ZCT_TSSOP56~D

0 1 0 200 66 66 Input

0 1 1 133 66 66 Input

Mid

Mid

Mid

0Mid

0

0

1

Hi-z

TCLK/21

Reserve1

0 Reserve

1

Reserve

Hi-z

TCLK/2

Reserve

5

Hi-z

TCLK/2

Reserve

Reserve

4

3

W>40 mil

1

C94

0.1U_0402_10V6K~L

2

1

C92

0.1U_0402_10V6K~L

2

CK408

Rev 1.1

1

C91

0.1U_0402_10V6K~L

2

1

C83

0.1U_0402_10V6K~L

2

PCICLK_F0

PCICLK_F1

PCICLK_F2

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

CPUCLKT2

CPUCLKC2

REF

3V66_0/DRCG

48MHZ_DOT

48MHZ_USB

3V66_1/VCH_CLK

66MHZ_IN/3V66_5

66MHZ_OUT0/3V66_2

66MHZ_OUT1/3V66_3

66MHZ_OUT2/3V66_4

5

6

7

10

11

12

13

16

17

18

52

51

49

48

45

44

56

33

38

39

35

24

21

22

23

1

C87

0.1U_0402_10V6K~L

2

1

C82

0.1U_0402_10V6K~L

2

PCICLK_F2

PCICLK1

PCICLK2

PCICLK3

PCICLK5

PCICLK6

CK_CPU0#

CK_CPU1

CK_CPU1#

CK_CPU2

CK_CPU2#

CLKREF

CLK48M_OUT1

CLK48M_OUT0

CLK66M_OUT0

CLK66M_OUT2

CLK66M_OUT3

2

1

C85

0.1U_0402_10V6K~L

2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

R88

33_0402_5%~L

R83

33_0402_5%~L

R81

33_0402_5%~L

R79

33_0402_5%~L

R72

33_0402_5%~L

R68

33_0402_5%~L

R93

33_0402_5%~L

R92

49.9_0402_1%~L

R87

33_0402_5%~L

R86

49.9_0402_1%~L

R85

33_0402_5%~L

R84

49.9_0402_1%~L

R82

33_0402_5%~L

R80

49.9_0402_1%~L

R78

33_0402_5%~L

R77

49.9_0402_1%~L

R71

33_0402_5%~L

R70

49.9_0402_1%~L

R99

33_0402_5%~L

R98

10_0402_5%~L

R59

33_0402_5%~L

R62

33_0402_5%~L

R551

10_0402_5%~L

R64

33_0402_5%~L

R63

33_0402_5%~L

R60

33_0402_5%~L

Title

Size Document Number Rev

Date: Sheet of

CK_33M_ICHPCI

CK_33M_SIOPCI

CK_33M_LANPCI

CK_33M_DOCKPCI

CK_33M_CBPCI

CK_33M_MINIPCI

CK_BCLK

CK_BCLK#

CK_ITP

CK_ITP#

CK_HCLK

CK_HCLK#

CK_33M_ICHPCI <<18>>

CK_33M_SIOPCI <<35>>

CK_33M_LANPCI <<27>>

CK_33M_DOCKPCI <<32>>

CK_33M_CBPCI <<29>>

CK_33M_MINIPCI <<31>>

CK_BCLK <<7>>

CK_BCLK# <<7>>

CK_ITP <<7>>

CK_ITP# <<7>>

CK_HCLK <<10>>

CK_HCLK# <<10>>

Place near CK408

CK_14M_ICH

CK_14M_SIO

CK_48M_SCR

CK_48M_ICH

CK_14M_CODEC

06/18/2003 Item 129

CK_66M_ICH

CK_66M_MCH

CK_66M_AGP

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

CK_14M_ICH <<19>>

CK_14M_SIO <<35>>

CK_48M_SCR <<29>>

CK_48M_ICH <<19>>

CK_14M_CODEC <<23>>

CK_66M_ICH <<19>>

CK_66M_MCH <<10>>

CK_66M_AGP <<16>>

Clock Generator

DDQ12/11/01 with LA-1901

1

6 59Wednesday, January 07, 2004

3.0

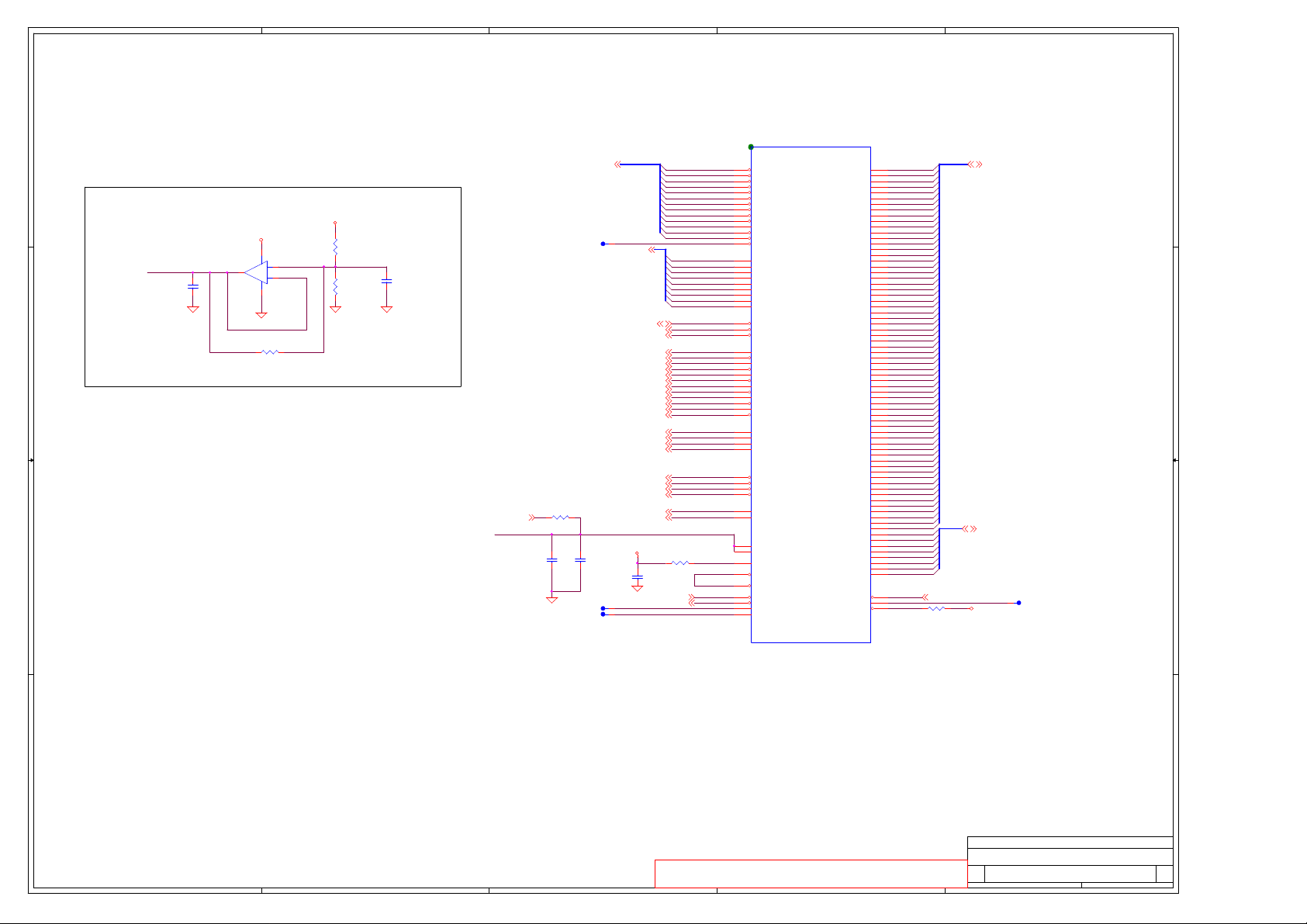

Page 7

5

4

3

2

1

H_A#[3..31]<<10>>

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

1 4

2 3

12

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CPU_CK_ITP

CPU_CK_ITP#

CK_BCLK

CK_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_DBRESET#

H_DBSY#

H_DPSLP#

ITP_BPM#4

ITP_BPM#5

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

D D

H_REQ#[0..4]<<10>>

RN11

0_4P2R_0402_5%~L

CK_ITP_R#

CK_ITP_R

CK_ITP<<6>>

CK_ITP#<<6>>

C C

+VCCP

B B

Those two shall be

pop per intel doc.

Placed near CPU

CK_BCLK

CK_BCLK#

56_0603_5%~L

1 2

2.2P_0402_50V8C~L@

2.2P_0402_50V8C~L@

R624

14

23

H_RS#[0..2]<<10>>

C450

C452

H_ADSTB#0<<10>>

H_ADSTB#1<<10>>

0_4P2R_0402_5%~L

CK_BCLK<<6>>

CK_BCLK#<<6>>

H_BPRI#<<10>>

H_DEFER#<<10>>

H_DRDY#<<10>>

H_LOCK#<<10>>

H_RESET#<<10>>

H_TRDY#<<10>>

ITP_DBRESET#<<38>>

H_PROCHOT#<<18>>

H_PWRGOOD<<18>>

1K_0603_5%~L@

1 2

1K_0402_5%~D@

H_THERMDA<<13>>

H_THERMDC<<13>>

H_THERMTRIP#<<20,38>>

12

12

RN10

@

H_ADS#<<10>>

H_BNR#<<10>>

H_BR0#<<10>>

H_HIT#<<10>>

H_HITM#<<10>>

H_DBSY#<<10>>

H_DPSLP#<<11,18>>

H_DPWR#<<11>>

H_CPUSLP#<<18>>

R632

R633

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

JCPUA

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

AA3

Y3

AA2

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

R2

P3

T2

P1

T1

U3

AE5

A16

A15

B15

B14

N2

L1

J3

N4

L4

H2

K3

K4

A4

J2

B11

H1

K1

L2

M3

C8

B8

A9

C9

A7

M2

B7

C19

A10

B10

B17

E4

A6

A13

C12

A12

C5

F23

C11

B13

B18

A18

C17

AMP_1473129-1~L

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

ADDR GROUP

A25#

A26#

A27#

A28#

A29#

A30#

A31#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADSTB0#

ADSTB1#

ITP_CLK0

ITP_CLK1

BCLK0

BCLK1

ADS#

BNR#

BPRI#

BR0#

DEFER#

DRDY#

HIT#

HITM#

IERR#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

BPM0#

BPM1#

BPM2#

BPM3#

DBR#

DBSY#

DPSLP#

DPWR#

PRDY#

PREQ#

PROCHOT#

PWRGOOD

SLP#

TCK

TDI

TDO

TEST1

TEST2

TMS

TRST#

THERMDA

THERMDC

THERMTRIP#

Banias

HOST CLK

CONTROL GROUP

MISC

THERMAL

DIODE

DATA GROUP

LEGACY CPU

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

D25

J26

T24

AD20

C23

K24

W25

AE24

C22

L24

W24

AE25

C2

D3

A3

B5

D1

D4

C6

B4

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23H_A#26

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

H_DINV#0 <<10>>

H_DINV#1 <<10>>

H_DINV#2 <<10>>

H_DINV#3 <<10>>

H_A20M# <<18>>

H_FERR# <<18>>

H_IGNNE# <<18>>

H_INIT# <<18>>

H_INTR <<18>>

H_NMI <<18>>

H_STPCLK# <<18>>

H_SMI# <<18>>

H_D#0H_A#3

A19

H_D#[0..63] <<10>>

H_DSTBN#[0..3] <<10>>

H_DSTBP#[0..3] <<10>>

H_RESET#

ITP_TDO

R621

22.6_0603_1%~L

1 2

R620

22.6_0603_1%~L

1 2

+VCCP

ITP_DBRESET#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

CK_ITP_R

CK_ITP_R#

ITP_TCK

ITP_TRST#

ITP_TMS

ITP_TDI

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

JITP

VTT1

VTT0

VTAP

DBR#

DBA#

BPM0#

GND5

BPM1#

GND4

BPM2#

GND3

BPM3#

GND2

BPM4#

GND1

BPM5#

RESET#

FBO

GND0

BCLKP

BCLKN

TDO

NC2

TCK

NC1

TRST#

TMS

TDI

29

GND6

GND7

MOLEX_52435-2891_28P~L

30

@

need double check this power plane

+3VSUS

R743

150_0603_1%~L

1 2

+VCCP

R622

54.9_0603_1%~L

1 2

R623

54.9_0603_1%~L

1 2

+VCCP

R618

39.2_0603_1%~L

1 2

R619

150_0603_1%~L

1 2

This shall place near CPU

R615

680_0603_5%~L

1 2

R617

27.4_0603_1%~L

1 2

+VCCP

1

C914

0.1U_0603_25V7M~L

2

ITP_DBRESET#

ITP_TDO

H_RESET#

ITP_TMS

ITP_TDI

ITP_TRST#

ITP_TCK

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Banias Processor in mFCPGA479

Size Document Number Rev

C

Date: Sheet of

DDQ12/11/01 with LA-1901

1

7 59Wednesday, January 07, 2004

3.0

Page 8

5

4

3

2

1

R634

54.9_0402_1%@

VCCSENSE

1 2

1 2

R635

54.9_0402_1%@

+VCCP

R639 1K_0402@

R640 1K_0402@

R641 1K_0402@

R642 1K_0402@

R643 1K_0402@

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

VSSSENSE

R_A

12

R50

1K_0603_1%~L

R_B

12

R51

2K_0603_1%~L

12

27.4_0603_1%~L

R645

+1.8VS_PROC

12

54.9_0603_1%~L

R646

12

27.4_0603_1%~L

R647

+VCC_CORE

not use in power side

V_CPU_GTLREF

12

54.9_0603_1%~L

PJP11

+1.8VRUN

2 1

PAD-OPEN 2x2m

D D

C C

B B

A A

SHORT

PJP16

+1.5VRUN

2 1

PAD-OPEN 2x2m

OPEN

+VCCP

V_CPU_GTLREF

R644

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

miles away from any

other toggling signal.

AE7

AF6

F26

B1

N1

AC26

P23

W4

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

K6

L5

L21

M6

M22

N5

N21

P6

P22

R5

R21

T6

T22

U21

D6

D8

D18

D20

D22

E5

E7

E9

E17

E19

E21

F6

F8

F18

E1

H_VID0

E2

H_VID1

F2

H_VID2

F3

H_VID3

G3

H_VID4

G4

H_VID5

H4

AD26

E26

G1

AC1

COMP0

P25

COMP1

P26

COMP2

AB2

COMP3

AB1

B2

AF7

C14

C3

C16

R341 0_0402_5%~L

R337 0_0402_5%~L

R338 0_0402_5%~L

R339 0_0402_5%~L

R340 0_0402_5%~L

R747 0_0402_5%~L

JCPUB

VCCSENSE

VSSSENSE

VCCA0

VCCA1

VCCA2

VCCA3

VCCQ0

VCCQ1

Banias

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

POWER, GROUNG, RESERVED SIGNALS AND NC

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

PSI#

VID0

VID1

VID2

VID3

VID4

VID5

GTLREF0

GTLREF1

GTLREF2

GTLREF3

COMP0

COMP1

COMP2

COMP3

RSVD

RSVD

RSVD

RSVD

TEST3

AMP_1473129-1~L

A2

VSS

A5

VSS

A8

VSS

A11

VSS

A14

VSS

A17

VSS

A20

VSS

A23

VSS

A26

VSS

B3

VSS

B6

VSS

B9

VSS

B12

VSS

B16

VSS

B19

VSS

B22

VSS

B25

VSS

C1

VSS

C4

VSS

C7

VSS

C10

VSS

C13

VSS

C15

VSS

C18

VSS

C21

VSS

C24

VSS

D2

VSS

D5

VSS

D7

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

D19

VSS

D21

VSS

D23

VSS

D26

VSS

E3

VSS

E6

VSS

E8

VSS

E10

VSS

E12

VSS

E14

VSS

E16

VSS

E18

VSS

E20

VSS

E22

VSS

E25

VSS

F1

VSS

F4

VSS

F5

VSS

F7

VSS

F9

VSS

F11

VSS

F13

VSS

F15

VSS

F17

VSS

F19

VSS

F21

VSS

F24

VSS

G2

VSS

G6

VSS

G22

VSS

G23

VSS

G26

VSS

H3

VSS

H5

VSS

H21

VSS

H25

VSS

J1

VSS

J4

VSS

J6

VSS

J22

VSS

J24

VSS

K2

VSS

K5

VSS

K21

VSS

K23

VSS

K26

VSS

L3

VSS

L6

VSS

L22

VSS

L25

VSS

M1

VSS

For test only ,Cmos output

CPU Voltage ID

VID0

12

VID1

12

VID2

12

VID3

12

VID4

12

VID5

12

B_VID6

B_VID4

OPEN

2

2

OPEN

2

2

2

2

B_VID3

OPEN

+3VSUS

RN9

10K_8P4R_1206_5%~L@

B_VID2

OPEN

2

2

2

2

B_VID1

OPEN

B_VID5

OPEN

2

2

+VCC_CORE

12

R333

1 8

2 7

3 6

4 5

10K_0402_5%@

AA11

AA13

AA15

AA17

AA19

AA21

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC11

AC13

AC15

AC17

AC19

AD10

AD12

AD14

AD16

AD18

AE11

AE13

AE15

AE17

AE19

AF10

AF12

AF14

AF16

AF18

F20

F22

G5

G21

H6

H22

J5

J21

K22

U5

V6

V22

W5

W21

Y6

Y22

AA5

AA7

AA9

AB6

AB8

AC9

AD8

AE9

AF8

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

R6

R22

R25

T3

T5

T21

T23

JCPUC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

POWER, GROUND

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AMP_1473129-1~L

Banias

T26

VSS

U2

VSS

U6

VSS

U22

VSS

U24

VSS

V1

VSS

V4

VSS

V5

VSS

V21

VSS

V25

VSS

W3

VSS

W6

VSS

W22

VSS

W23

VSS

W26

VSS

Y2

VSS

Y5

VSS

Y21

VSS

Y24

VSS

AA1

VSS

AA4

VSS

AA6

VSS

AA8

VSS

AA10

VSS

AA12

VSS

AA14

VSS

AA16

VSS

AA18

VSS

AA20

VSS

AA22

VSS

AA25

VSS

AB3

VSS

AB5

VSS

AB7

VSS

AB9

VSS

AB11

VSS

AB13

VSS

AB15

VSS

AB17

VSS

AB19

VSS

AB21

VSS

AB23

VSS

AB26

VSS

AC2

VSS

AC5

VSS

AC8

VSS

AC10

VSS

AC12

VSS

AC14

VSS

AC16

VSS

AC18

VSS

AC21

VSS

AC24

VSS

AD1

VSS

AD4

VSS

AD7

VSS

AD9

VSS

AD11

VSS

AD13

VSS

AD15

VSS

AD17

VSS

AD19

VSS

AD22

VSS

AD25

VSS

AE3

VSS

AE6

VSS

AE8

VSS

AE10

VSS

AE12

VSS

AE14

VSS

AE16

VSS

AE18

VSS

AE20

VSS

AE23

VSS

AE26

VSS

AF2

VSS

AF5

VSS

AF9

VSS

AF11

VSS

AF13

VSS

AF15

VSS

AF17

VSS

AF19

VSS

AF21

VSS

AF24

VSS

12

R746

10K_0402_5%@

VID0 <<47>>

VID1 <<47>>

VID2 <<47>>

VID3 <<47>>

VID4 <<47>>

VID5 <<47>>

1

1

5

4

1

1

OPEN OPEN OPEN OPEN OPEN OPEN

1

1

1

1

1

1

1

1

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

Banias Processor in mFCPGA479

Size Document Number Rev

C

Date: Sheet of

DDQ12/11/01 with LA-1901

1

8 59Wednesday, January 07, 2004

3.0

Page 9

5

4

3

2

1

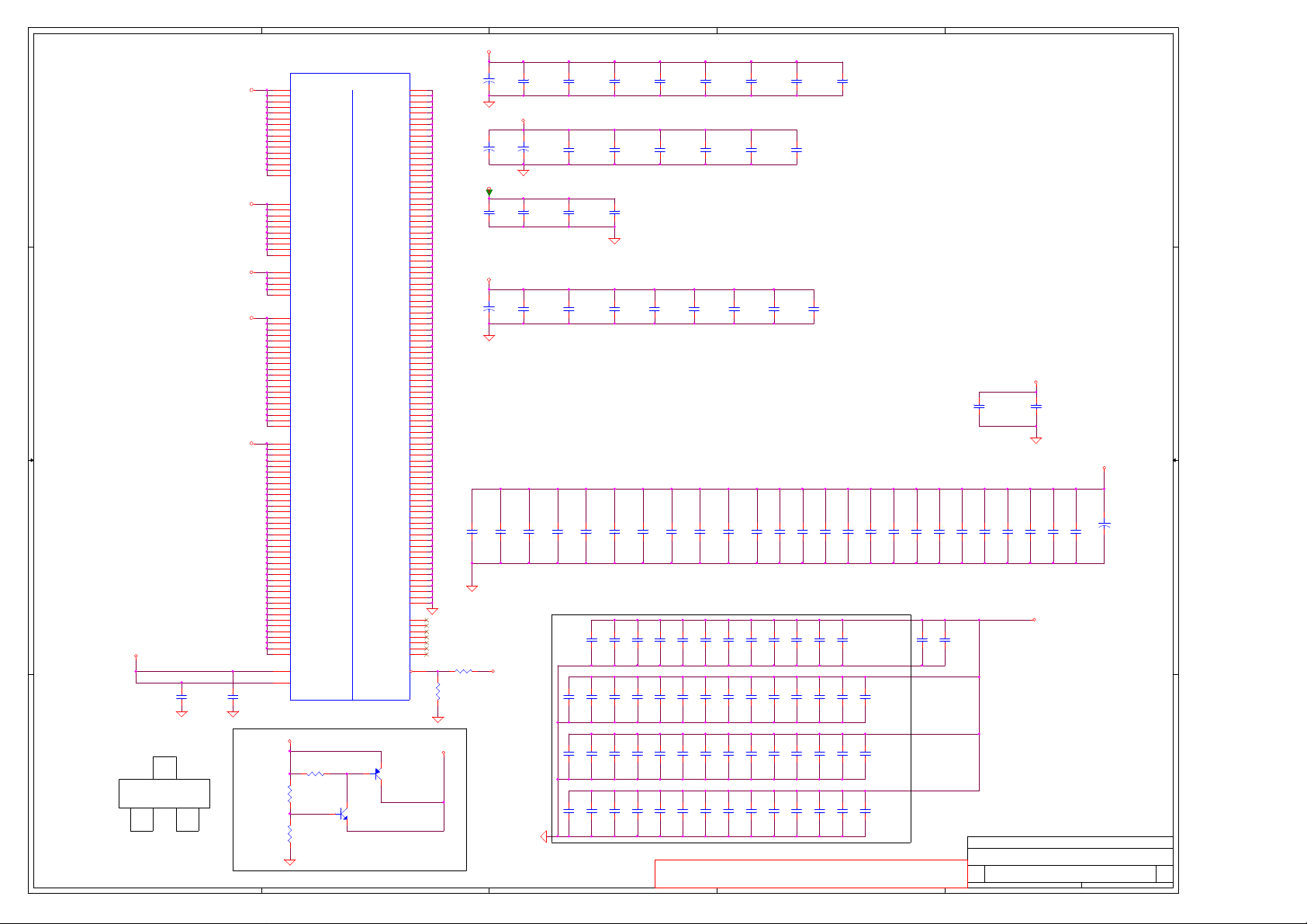

+VCC_CORE

C415

10U_1206_6.3V7K~L

C403

10U_1206_6.3V7K~L

C404

10U_1206_6.3V7K~L

C376

10U_1206_6.3V7K~L

@

1

C386

10U_1206_6.3V7K~L

2

1

C418

10U_1206_6.3V7K~L

2

1

C440

10U_1206_6.3V7K~L

2

1

C414

10U_1206_6.3V7K~L

2

1

C49

0.22U_0603_10V7M~L

2

1

2

D D

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C C

+VCC_CORE

1

C50

0.22U_0603_10V7M~L

2

1

C412

10U_1206_6.3V7K~L

2

1

C413

10U_1206_6.3V7K~L

2

1

C396

10U_1206_6.3V7K~L

2

1

C445

10U_1206_6.3V7K~L

2

1

C57

0.22U_0603_10V7M~L

@

2

1

C406

10U_1206_6.3V7K~L

2

1

C378

10U_1206_6.3V7K~L

2

1

C387

10U_1206_6.3V7K~L

2

1

C398

10U_1206_6.3V7K~L

2

1

C56

0.22U_0603_10V7M~L

@

2

1

C395

10U_1206_6.3V7K~L

2

1

C405

10U_1206_6.3V7K~L

2

1

C439

10U_1206_6.3V7K~L

2

1

C444

10U_1206_6.3V7K~L

2

1

C61

0.22U_0603_10V7M~L

2

@

@

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

10uF 1206 X5R -> 85

degree

1

C60

0.22U_0603_10V7M~L

2

@

C925

10U_1206_6.3V7K~L

C427

10U_1206_6.3V7K~L

C441

10U_1206_6.3V7K~L

1

C926

10U_1206_6.3V7K~L

2

1

C379

10U_1206_6.3V7K~L

2

1

C394

10U_1206_6.3V7K~L

2

1

C927

10U_1206_6.3V7K~L

2

1

C373

10U_1206_6.3V7K~L

2

1

C372

10U_1206_6.3V7K~L

2

High Frequence Decoupling

1

2

1

2

1

2

X7R

+VCC_CORE

C928

10U_1206_6.3V7K~L

C438

10U_1206_6.3V7K~L

C374

10U_1206_6.3V7K~L

1

C929

10U_1206_6.3V7K~L

2

1

C377

10U_1206_6.3V7K~L

2

1

C426

10U_1206_6.3V7K~L

2

B B

+VCC_CORE

1

2

1

+

C910

150U_D_6.3VM_R55~D

2

@

5

1

+

C672

220U_D2_2VM~D

@

2

C724

0.1U_0402_16V4Z~L

1

+

2

1

C725

0.1U_0402_16V4Z~L

2

1

C732

0.1U_0402_16V4Z~L

2

C673

220U_D2_2VM~D

@

1

+

C671

220U_D2_2VM~D

@

2

+1.8VS_PROC

1

C723

0.1U_0402_16V4Z~L

2

A A

+VCCP

1

+

C731

150U_D2_4VK~D

2

1

C726

0.1U_0402_16V4Z~L

2

1

C733

0.1U_0402_16V4Z~L

2

1

+

C674

220U_D2_2VM~D

@

2

1

C727

10U_1206_10V4Z~L

2

1

C734

0.1U_0402_16V4Z~L

2

1

+

C675

220U_D2_2VM~D

@

2

4

1

C728

10U_1206_10V4Z~L

2

1

C735

0.1U_0402_16V4Z~L

2

1

+

C678

220U_D2_2VM~D

@

2

1

C729

10U_1206_10V4Z~L

2

1

C736

0.1U_0402_16V4Z~L

2

C941

220U_D2_2VM~D

1

C730

10U_1206_10V4Z~L

2

1

C737

0.1U_0402_16V4Z~L

2

1

+

2

9mOhm

7343

PS CAP

1

+

C942

2

220U_D2_2VM~D

9mOhm

7343

PS CAP

1

2

3

1

+

C943

2

220U_D2_2VM~D

9mOhm

7343

PS CAP

C738

0.1U_0402_16V4Z~L

1

+

C944

2

220U_D2_2VM~D

9mOhm

7343

PS CAP

1

C739

0.1U_0402_16V4Z~L

2

1

C740

0.1U_0402_16V4Z~L

2

1

C741

0.1U_0402_16V4Z~L

2

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

C

2

Date: Sheet of

Compal Electronics, Inc.

CPU Bypass

DDQ12/11/01 with LA-1901 3.0

1

9 59Wednesday, January 07, 2004

Page 10

5

4

3

2

1

AA28

AB25

AB27

AA27

AB26

AB23

AA24

AA25

AB24

AC25

AC24

AC22

AD24

AA23

W28

W27

W24

W23

W25

AG24

AH25

AC27

AC28

AH28

AH27

AG28

AG27

AE28

AE27

AE24

AE25

AF27

AF26

AE22

AE23

AF22

AG25

AF24

AG26

R662

22_0402_5%~L@

C749

10P_0402_50V8J~L

@

U68B

R27

GAD0

R28

GAD1

T25

GAD2

R25

GAD3

T26

GAD4

T27

GAD5

U27

GAD6

U28

GAD7

V26

GAD8

V27

GAD9

T23

GAD10

U23

GAD11

T24

GAD12

U24

GAD13

U25

GAD14

V24

GAD15

Y27

GAD16

Y26

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

Y23

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

V25

GCBE#0

V23

GCBE#1

Y25

GCBE#2

GCBE#3

Y24

GFRAME#

GDEVSEL#

GIRDY#

GTRDY#

GSTOP#

GPAR

GREQ#

GGNT#

R24

AD_STB0

R23

AD_STB#0

AD_STB1

AD_STB#1

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SB_STB

SB_STB#

RBF#

WBF#

PIPE#

ST0

ST1

ST2

P22

66IN

RG8294300M_FCBGA593

Odem

AGP

HUB

GND

HI_10

HI_STB

HI_STB#

HLRCOMP

HI_REF

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

GRCOMP

AGPREF

1 2

R648

36.5_0603_1%~L

150_0402_1%~D

150_0402_1%~D

R658

36.5_0603_1%~L

1 2

VREFGC <<16>>

HUB_HL[0..10] <<18>>

HUB_HLSTRB <<18>>

HUB_HLSTRB# <<18>>

+1.8VRUN

+1.8VRUN

12

R412

R_C

HL_REF

12

R414

R_D

2

C468

470P_0402_50V7K~L

@

1

HLREF_TERMHHLREF_TERML

R413

56.2_0402_1%@

1 2

R415

0_0402_5%~L

1 2

1

C470

0.01U_0402_25V7K~L

2

HUB_HL0

P25

HI_0

HUB_HL1

P24

HI_1

HUB_HL2

N27

HI_2

HUB_HL3

P23

HI_3

HUB_HL4

M26

HI_4

HUB_HL5

M25

HI_5

HUB_HL6

L28

HI_6

HUB_HL7

L27

HI_7

HUB_HL8

M27

HI_8

HUB_HL9

N28

HI_9

HUB_HL10

M24

HUB_HLSTRB

N25

HUB_HLSTRB#

N24

HUB_RCOMP

P27

HL_REF

P26

AB9

AD10

AF9

AJ9

A7

F8

J7

L8

N8

R8

U8

W8

AA8

AD8

AF7

AJ7

D5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

AF5

AJ5

A3

J4

L4

N4

R4

U4

W4

AA4

AC4

AE4

AJ3

E1

J1

L1

N1

R1

U1

W1

AA1

AC1

AE1

AG1

AD25

AA21

C742

AGP_RCOMP

1

2

1

2

0.01U_0402_16V7K~D

C748

0.1U_0603_16V7K~L

VREFCG <<16>>

VREFGC <<16>>

G_AD[0..31]<<16>>

G_C/BE#[0..3]<<16>>

G_FRAME#<<16>>

G_DEVSEL#<<16>>

G_IRDY#<<16>>

G_TRDY#<<16>>

G_STOP#<<16>>

G_PAR<<16>>

G_REQ#<<16>>

G_GNT#<<16>>

G_AD_STB0<<16>>

G_AD_STB0#<<16>>

G_AD_STB1<<16>>

G_AD_STB1#<<16>>

G_SBA[0..7]<<16>>

G_SB_STB<<16>>

G_SB_STB#<<16>>

G_PIPE#<<16>>

G_ST0<<16>>

G_ST1<<16>>

G_ST2<<16>>

CK_66M_MCH<<6>>

G_RBF#<<16>>

G_WBF#<<16>>

CK_66M_MCH

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_C/BE#0

G_C/BE#1

G_C/BE#2

G_C/BE#3

G_FRAME#

G_DEVSEL#

G_IRDY#

G_TRDY#

G_STOP#

G_PAR

G_REQ#

G_GNT#

G_AD_STB0

G_AD_STB0#

G_AD_STB1

G_AD_STB1#

G_SBA0

G_SBA1

G_SBA2

G_SBA3

G_SBA4

G_SBA5

G_SBA6

G_SBA7

G_SB_STB

G_SB_STB#

G_RBF#

G_WBF#

G_PIPE#

G_ST0

G_ST1

G_ST2

CK_66M_MCH

12

1

2

U68A

C743

0.01U_0402_16V7K~D

C744

0.01U_0402_16V7K~D

H_SWNG0

MCH_GTLREF

1

1

2

2

C746

220P_0603_50V8J~L

1 2

H_D#[0..63] <<7>>

+VCCP

H_SWNG1

+VCCP

1

1U_0603_6.3V6M~D

2

1 2

1

2

1

2

+VCCP

C747

R661

27.4_0603_1%~L

12

12

12

12

12

R656

49.9_0603_1%~L

12

R657

100_0603_1%~L

R649

301_0402_1%~D

R650

150_0402_1%~D

R652

301_0402_1%~D

R653

150_0402_1%~D

R418

1K_0603_1%

R_M

R417

1K_0603_1%

R_N

+1.5VRUN

12

1 2

12

R416

0_0402_5%~L

@

H_A#[3..31]<<7>>

D D

H_REQ#[0..4]<<7>>

C C

B B

A A

H_ADSTB#0<<7>>

H_ADSTB#1<<7>>

CK_HCLK#<<6>>

CK_HCLK<<6>>

H_ADS#<<7>>

H_TRDY#<<7>>

H_DRDY#<<7>>

H_DEFER#<<7>>

H_HITM#<<7>>

H_HIT#<<7>>

H_LOCK#<<7>>

H_BR0#<<7>>

H_BNR#<<7>>

H_BPRI#<<7>>

H_DBSY#<<7>>

H_RS#[0..2]<<7>>

H_RESET#<<7>>

H_DSTBN#[0..3]<<7>>

H_DSTBP#[0..3]<<7>>

H_DINV#0<<7>>

H_DINV#1<<7>>

H_DINV#2<<7>>

H_DINV#3<<7>>

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_RS#0

H_RS#1

H_RS#2

H_RESET#

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

Placed near MCH

CK_HCLK

CK_HCLK#

U6

T5

R2

U3

R3

P7

T3

P4

P3

P5

R6

N2

N5

N3

J3

M3

M4

M5

L5

K3

J2

N6

L6

L2

K5

L3

L7

K4

J5

U2

T7

R7

U5

T4

R5

N7

K8

J8

U7

V4

W2

Y4

Y3

Y5

W3

V7

V3

Y7

V5

W7

W5

W6

AE17

AD4

AF6

AD11

AC15

AD3

AG6

AE11

AC16

AD5

AG5

AH9

AD15

C380

2.2P_0402_50V8C~L@

12

C381

2.2P_0402_50V8C~L@

12

Odem

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HADSTB#0

HADSTB#1

BCLK#

BCLK

ADS#

HTRDY#

DRDY#

DEFER#

HITM#

HIT#

HLOCK#

BR0#

BNR#

BPRI#

DBSY#

RS#0

RS#1

RS#2

CPURST#

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

DBI#0

DBI#1

DBI#2

DBI#3

RG8294300M_FCBGA593

HOST

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HVREF0

HVREF1

HVREF2

HVREF3

HVREF4

HSWNG1

HSWNG0

HRCOMP1

HRCOMP0

AA2

AB5

AA5

AB3

AB4

AC5

AA3

AA6

AE3

AB7

AE5

AF3

AC6

AC3

AF4

AE2

AG4

AG2

AE7

AE8

AH2

AC7

AG3

AD7

AH7

AE6

AC8

AG8

AG7

AH3

AF8

AH5

AC11

AC12

AE9

AC10

AE10

AD9

AG9

AC9

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

M7

P8

AA9

AB12

AB16

AD13

AA7

AC13

AC2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

C745

220P_0603_50V8J~L

H_SWNG1

H_SWNG0

H_RCOMP1

H_RCOMP0

27.4_0603_1%~L

R660

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

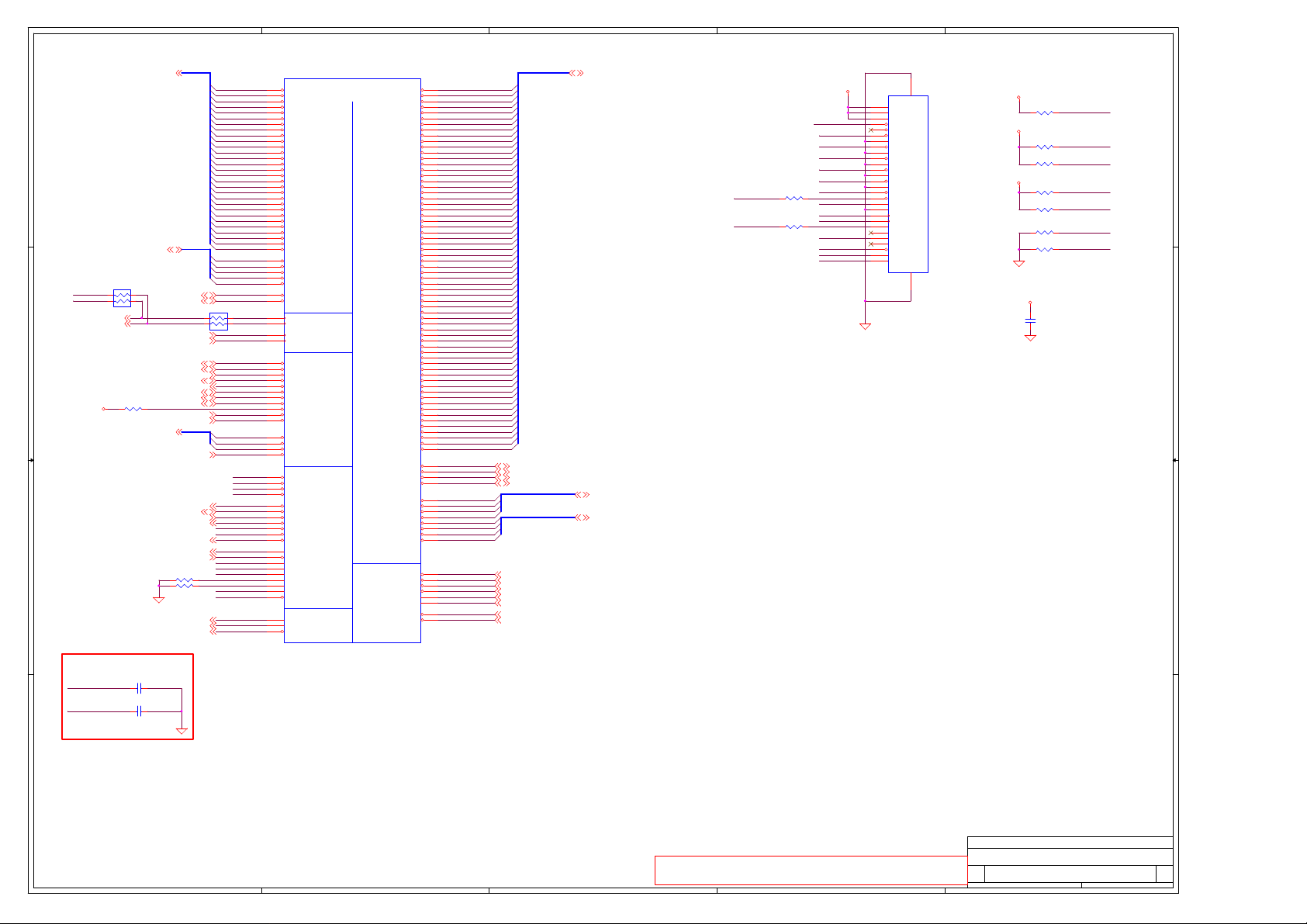

Odem(1 of 3)

C

DDQ12/11/01 with LA-1901

1

10 59Wednesday, January 07, 2004

3.0

Page 11

5

4

3

2

1

D D

R748

0_0603_5%~L

1

C752

C753

2

0.1U_0603_16V7K~L

DDR_MA[0..12]<<14,15>>

T281

PAD

V_1P25V_DDR_VTT

1

2

0.1U_0603_16V7K~L

T5

PAD

T6

PAD

DDR_DS[0..8]<<14>>

DDR_CKE0_DIMM0<<14>>

DDR_CKE1_DIMM0<<14>>

DDR_CKE2_DIMM1<<15>>

DDR_CKE3_DIMM1<<15>>

DDR_CS0_DIMM0#<<14>>

DDR_CS1_DIMM0#<<14>>

DDR_CS2_DIMM1#<<15>>

DDR_CS3_DIMM1#<<15>>

DDR_WE#<<14,15>>

DDR_RAS#<<14,15>>

DDR_CAS#<<14,15>>

CK_DDR_CK0<<14>>

CK_DDR_CK0#<<14>>

CK_DDR_CK1<<14>>

CK_DDR_CK1#<<14>>

CK_DDR_CK2<<14>>

CK_DDR_CK2#<<14>>

CK_DDR_CK3<<15>>

CK_DDR_CK3#<<15>>

CK_DDR_CK4<<15>>

CK_DDR_CK4#<<15>>

CK_DDR_CK5<<15>>

CK_DDR_CK5#<<15>>

DDR_BS0<<14,15>>

DDR_BS1<<14,15>>

1

2

C754

0.1U_0603_16V7K~L

H_DPSLP#<<7,18>>

H_DPWR#<<7>>

All of thsoe schematic shall be changed to

un-pop

NEED CHECK THIS POWER

PLANE

NEED CHECK THIS POWER

PLANE

DDR_VREF_MCH

1

C751

10U_1206_10V4Z@

2

C C

B B

1

+12V

OUT

1 2

8

U69A

LM358M_SO8~L@

P

3

IN+

2

ING

4

R760

0_0402_5%~D@

+2.5V_MEM

12

12

R664

10K_0603_1%~L@

1

R666

10K_0603_1%~L@

C750

0.1U_0603_16V7K~L@

2

V_DDR_MCH_REF<<14,15,46>>

DDR_VREF_MCH

DDR_CKE0_DIMM0

DDR_CKE1_DIMM0

DDR_CKE2_DIMM1

DDR_CKE3_DIMM1

DDR_CS0_DIMM0#

DDR_CS1_DIMM0#

DDR_CS2_DIMM1#

DDR_CS3_DIMM1#

R667

30.1_0603_1%~L

1 2

DDR_MA0

DDR_MA1

DDR_MA2

DDR_MA3

DDR_MA4

DDR_MA5

DDR_MA6

DDR_MA7

DDR_MA8

DDR_MA9

DDR_MA10

DDR_MA11

DDR_MA12

DDR_DS5

DDR_DS4

DDR_DS6

DDR_DS7

DDR_DS3

DDR_DS2

DDR_DS1

DDR_DS0

DDR_DS8

DDR_WE#

DDR_RAS#

DDR_CAS#

CK_DDR_CK0

CK_DDR_CK0#

CK_DDR_CK1

CK_DDR_CK1#

CK_DDR_CK2

CK_DDR_CK2#

CK_DDR_CK3

CK_DDR_CK3#

CK_DDR_CK4

CK_DDR_CK4#

CK_DDR_CK5

CK_DDR_CK5#

DDR_BS0

DDR_BS1

DDR_RCOMP

100mils

M_RCV#

U68C

E12

SMA0

F17

SMA1

E16

SMA2

G17

SMA3

G18

SMA4

E18

SMA5

F19

SMA6

G20

SMA7

G19

SMA8

F21

SMA9

F13

SMA10

E20

SMA11

G21

SMA12

G22

RSVD2

F26

SDQS0

C26

SDQS1

C23

SDQS2

B19

SDQS3

D12

SDQS4

C8

SDQS5

C5

SDQS6

E3

SDQS7

E15

SDQS8

G11

SWE#

F11

SRAS#

G8

SCAS#

J25

SCK0

K25

SCK#0

G5

SCK1

F5

SCK#1

G24

SCK2

E24

SCK#2

G25

SCK3

J24

SCK#3

G6

SCK4

G7

SCK#4

K23

SCK5

J23

SCK#5

G23

SCKE0

E22

SCKE1

H23

SCKE2

F23

SCKE3

E9

SCS#0

F7

SCS#1

F9

SCS#2

E7

SCS#3

G12

SBS0

G13

SBS1

J9

SMVREF0

J21

SMVREF1

J28

SMRCOMP

G15

RCVENIN#

G14

RCVENOUT#

V8

DPSLP#

Y8

DPWR#

AD26

NC0

AD27

NC1

RG82855PM_FCBGA593

Odem

MEMORY

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

SDQ64

SDQ65

SDQ66

SDQ67

SDQ68

SDQ69

SDQ70

SDQ71

RSTIN#

RSVD1

TESTIN#

DDR_D45

G28

DDR_D46

F27

DDR_D44

C28

DDR_D41

E28

DDR_D47

H25

DDR_D42

G27

DDR_D43

F25

DDR_D40

B28

DDR_D39

E27

DDR_D37

C27

DDR_D36

B25

DDR_D33

C25

DDR_D32

B27

DDR_D38

D27

DDR_D34

D26

DDR_D35

E25

DDR_D49

D24

DDR_D53

E23

DDR_D51

C22

DDR_D55

E21

DDR_D50

C24

DDR_D48

B23

DDR_D54

D22

DDR_D52

B21

DDR_D56

C21

DDR_D60

D20

DDR_D58

C19

DDR_D63

D18

DDR_D57

C20

DDR_D61

E19

DDR_D62

C18

DDR_D59

E17

DDR_D27

E13

DDR_D30

C12

DDR_D29

B11

DDR_D24

C10

DDR_D31

B13

DDR_D26

C13

DDR_D25

C11

DDR_D28

D10

DDR_D22

E10

DDR_D18

C9

DDR_D17

D8

DDR_D21

E8

DDR_D23

E11

DDR_D19

B9

DDR_D20

B7

DDR_D16

C7

DDR_D11

C6

DDR_D15

D6

DDR_D12

D4

DDR_D8

B3

DDR_D10

E6

DDR_D14

B5

DDR_D13

C4

DDR_D9

E4

DDR_D7

C3

DDR_D6

D3

DDR_D5

F4

DDR_D0

F3

DDR_D3

B2

DDR_D2

C2

DDR_D1

E2

DDR_D4

G4

DDR_CB2

C16

DDR_CB6

D16

DDR_CB5

B15

DDR_CB0

C14

DDR_CB3

B17

DDR_CB7

C17

DDR_CB1

C15

DDR_CB4

D14

J27

H27

H26

MCH_TEST#

PCIRST_1# <<18,27>>

1 2

R668

4.7K_0603_5%~L@

DDR_D[0..63] <<14>>

DDR_CB[0..7] <<14>>

+1.5VRUN

T282

PAD

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

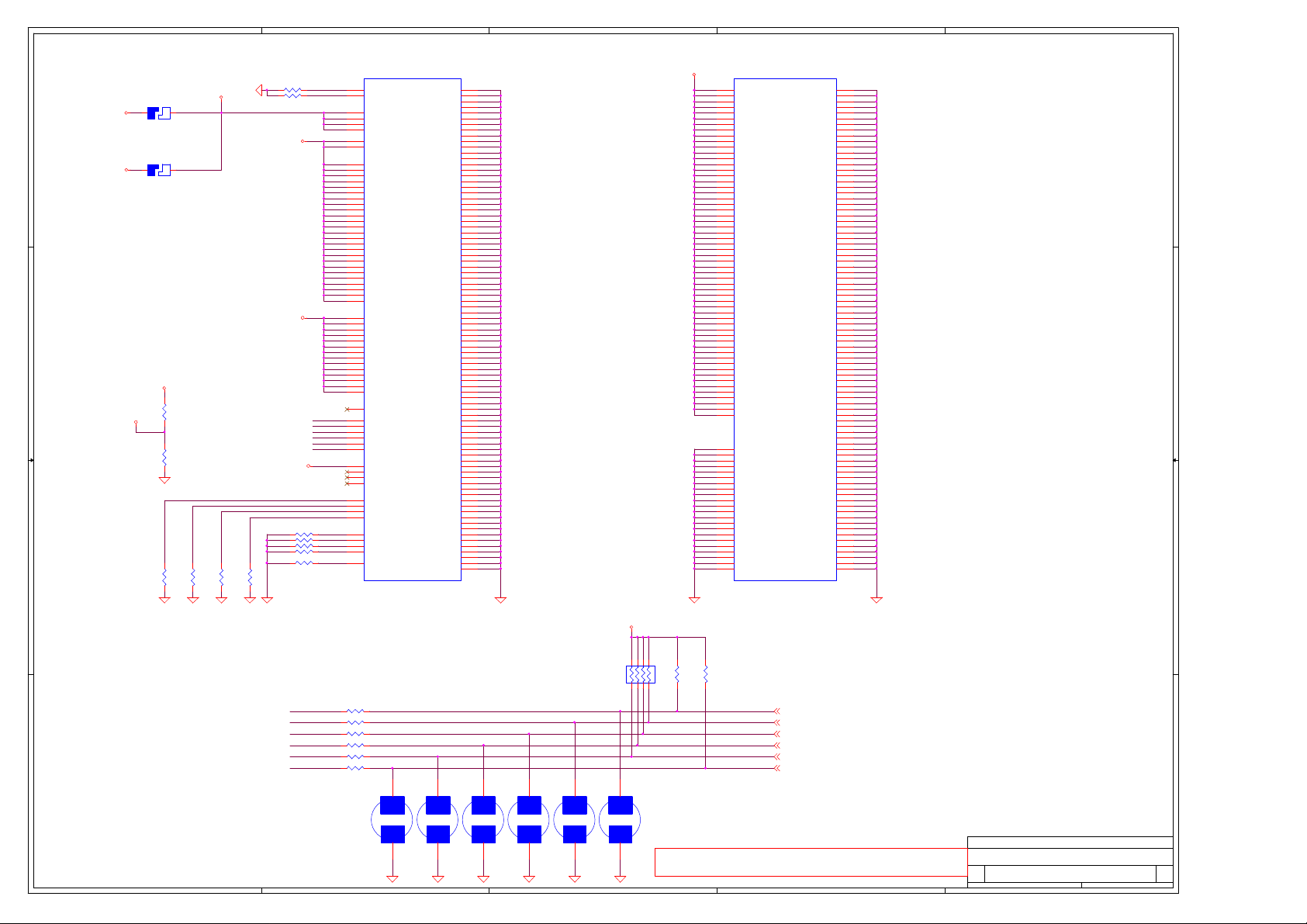

Odem(2 of 3)

Size Document Number Rev

C

Date: Sheet of

DDQ12/11/01 with LA-1901

1

11 59Wednesday, January 07, 2004

3.0

Page 12

5

U68D

1

C806

0.01U_0402_16V7K~L

2

470_0402_5%@

470_0402_5%@

R29

VCCAGP0

W29

VCCAGP1

AC29

VCCAGP2

AG29

VCCAGP3

U26

VCCAGP4

AA26

VCCAGP5

AE26

VCCAGP6

AJ25

VCCAGP7

AD23

VCCAGP8

AF23

VCCAGP9

R22

VCCAGP10

U22

VCCAGP11

W22

VCCAGP12

AA22

VCCAGP13

AB21

VCCAGP14

AD21

VCCAGP15

P17

VCC0

N16

VCC1

P15

VCC2

R16

VCC3

T15

VCC4

U16

VCC5

N14

VCC6

P13

VCC7

R14

VCC8

U14

VCC9

L29

VCCHL0

L25

VCCHL1

N26

VCCHL2

N23

VCCHL3

M22

VCCHL4

POWER GND

AG23

VCCP0

AJ23

VCCP1

AE21

VCCP2

AG21

VCCP3

AJ21

VCCP4

AB20

VCCP5

AC19

VCCP6

AD20

VCCP7

AE19

VCCP8

AF20

VCCP9

AG19

VCCP10

AJ19

VCCP11

AB18

VCCP12

AD18

VCCP13

AF18

VCCP14

AB14

VCCP15

AB10

VCCP16

M8

VCCP17

T8

VCCP18

AB8

VCCP19

C29

VCCSM0

G29

VCCSM1

A25

VCCSM2

D25

VCCSM3

K26

VCCSM4

D23

VCCSM5

H24

VCCSM6

K24

VCCSM7

L23

VCCSM8

A21

VCCSM9

F22

VCCSM10

H22

VCCSM11

K22

VCCSM12

D19

VCCSM13

H20

VCCSM14

A17

VCCSM15

F18

VCCSM16

H18

VCCSM17

D15

VCCSM18

F16

VCCSM19

H16

VCCSM20

A13

VCCSM21

F14

VCCSM22

H14

VCCSM23

D11

VCCSM24

H12

VCCSM25

A9

VCCSM26

F10

VCCSM27

H10

VCCSM28

D7

VCCSM29

H8

VCCSM30

K7

VCCSM31

A5

VCCSM32

E5

VCCSM33

H5

VCCSM34

J6

VCCSM35

C1

VCCSM36

G1

VCCSM37

T17

VCCGA

T13

VCCHA

RG8294300M_FCBGA593

+3VRUN

R773

220_0402_5%@

1 2

R774

1 2

R775

Odem 1.5V Rail Leakage

1 2

Current Issue Solution

2

+1.5VRUN

D D

+1.2VRUN

+1.8VRUN

+VCCP

C C

+2.5V_MEM

B B

+1.8VRUN

one .01uf and 10

uf each two pins

1

C919

10U_1206_10V4Z~L

2

C

1

A A

MMBT3904_SOT23

MMBT3906_SOT23

2

B

3

E

Transistoe

illustration

5

Odem

Q87

MMBT3904_SOT23~D@

3 1

4

+1.5VRUN

1

1

+

C779

C780

E29

VSS0

J29

VSS1

N29

VSS2

U29

VSS3

AA29

VSS4

AE29

VSS5

A27

VSS6

K27

VSS7

AJ27

VSS8

E26

VSS9

G26

VSS10

J26

VSS11

L26

VSS12

R26

VSS13

W26

VSS14

AC26

VSS15

AF25

VSS16

A23

VSS17

F24

VSS18

L24

VSS19

M23

VSS20

AC23

VSS21

AH23

VSS22

D21

VSS23

H21

VSS24

J22

VSS25

L22

VSS26

N22

VSS27

T22

VSS28

V22

VSS29

Y22

VSS30

AB22

VSS31

AC21

VSS32

AD22

VSS33

AF21

VSS34

AG22

VSS35

AH21

VSS36

A19

VSS37

F20

VSS38

H19

VSS39

AB19

VSS40

AC20

VSS41

AD19

VSS42

AE20

VSS43

AF19

VSS44

AG20

VSS45

AH19

VSS46

D17

VSS47

H17

VSS48

N17

VSS49

R17

VSS50

U17

VSS51

AB17

VSS52

AC18

VSS53

AE18

VSS54

AF17

VSS55

AG18

VSS56

AJ17

VSS57

A15

VSS58

F15

VSS59

H15

VSS60

N15

VSS61

P16

VSS62

R15

VSS63

T16

VSS64

U15

VSS65

AB15

VSS66

AD16

VSS67

AF15

VSS68

AJ15

VSS69

D13

VSS70

E14

VSS71

H13

VSS72

N13

VSS73

P14

VSS74

R13

VSS75

T14

VSS76

U13

VSS77

AB13

VSS78

AD14

VSS79

AF13

VSS80

AJ13

VSS81

A11

VSS82

F12

VSS83

H11

VSS84

AB11

VSS85

AD12

VSS86

AF11

VSS87

AJ11

VSS88

D9

VSS89

H9

VSS90

G16

RSVD3

G10

RSVD4

G9

RSVD5

H7

RSVD6

G2

RSVD7

RSVD8

RSVD9

31

Q86

2

4

internal pull up

G3

H3

H4

ETS#

12

+1.2VRUN

2SA1036K_SOT23@

R669

10K_0402_5%~L@

1 2

R670

1K_0402_5%~L@

2

@

150U_D2_4VK~D

1

+

C788

150U_D2_4VK~D

2

+1.8VRUN

1

C775

2

@

10U_1206_10V4Z~L

+VCCP

1

+

C796

2

150U_D_6.3VM_R55~D

@

1

1

2

2

C407

0.047U_0402_16V4M~L

+2.5V_MEM

@

@

@

2

10U_1206_10V4Z~L

+1.2VRUN

1

+

C789

150U_D2_4VK~D

2

1

C776

2

0.1U_0402_16V4Z~L

1

C797

2

0.1U_0402_16V4Z~L

@

1

2

C363

C462

0.047U_0402_16V4M~L

0.047U_0402_16V4M~L

C781

@

C790

C777

C798

1

2

10U_1206_10V4Z~L

1

2

2.2U_0805_16VFZ~L

1

2

0.1U_0402_16V4Z~L

1

2

0.1U_0402_16V4Z~L

1

1

2

2

C466

0.047U_0402_16V4M~L

1

2

C532

0.1U_0402_10V6K~L

1

2

C519

0.1U_0402_10V6K~L

1

2

C525

0.1U_0402_10V6K~L

3

1

C782

2

0.01U_0402_16V7K~D

1

C791

2

0.22U_0603_10V7K~L

1

C778

2

0.1U_0402_16V4Z~L

1

C799

2

0.1U_0402_16V4Z~L

@

1

2

C420

0.047U_0402_16V4M~L

1

1

2

2

C537

0.1U_0402_10V6K~L

1

1

2

2

C510

0.1U_0402_10V6K~L

1

1

2

2

C520

0.1U_0402_10V6K~L

1

1

2

2

C503

0.1U_0402_10V6K~L

3

2

1

1

1

1

C784

C783

0.01U_0402_16V7K~D

C792

0.015U_0402_16V7K~D

1

C800

2

0.1U_0402_16V4Z~L

@

1

2

C388

C358

0.047U_0402_16V4M~L

1

2

C516

C538

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

2

C534

C533

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

2

C512

C502

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

2

C554

C501

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

2

2

0.01U_0402_16V7K~D

1

1

C793

2

2

0.01U_0603_50V7K~L

1

C802

2

1

2

C455

0.047U_0402_16V4M~L

1

2

C552

C553

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

2

C518

C551

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

2

C515

C513

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

2

C160

C499

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

2

0.1U_0402_16V4Z~L

1

2

1

2

1

2

1

2

1

2

C801

0.1U_0402_16V4Z~L

@

1

2

C460

0.047U_0402_16V4M~L

0.047U_0402_16V4M~L

1

1

2

2

C547

0.1U_0402_10V6K~L

1

1

2

2

C517

0.1U_0402_10V6K~L

1

1

2

2

C514

0.1U_0402_10V6K~L

1

1

2

2

C500

0.1U_0402_10V6K~L

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C785

2

0.01U_0402_16V7K~D

1

C794

2

0.022U_0402_16V7K~D

1

C803

2

0.1U_0402_16V4Z~L

1

2

C449

C391

0.047U_0402_16V4M~L

0.047U_0402_16V4M~L

1

1

2

2

C544

C524

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

1

2

2

C549

C550

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

1

2

2

C539

C540

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

1

2

2

C564

C192

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

C786

0.01U_0402_16V7K~D

C795

0.047U_0603_25V7M~L

@

1

2

C397

C545

0.1U_0402_10V6K~L

C548

0.1U_0402_10V6K~L

C541

0.1U_0402_10V6K~L

C563

0.1U_0402_10V6K~L

C787

2

0.01U_0402_16V7K~D

1

2

1

C804

2

0.1U_0402_16V4Z~L

@

1

1

2

2

C422

C421

0.047U_0402_16V4M~L

0.047U_0402_16V4M~L

1

1

2

2

C536

C546

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

1

2

2

C523

C555

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

1

2

2

C542

C543

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

1

2

2

C526

C527

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

2

1

2

@

1

1

2

2

C410

C351

0.047U_0402_16V4M~L

0.047U_0402_16V4M~L

1

0402

2

C535

0.1U_0402_10V6K~L

1

1

2

2

C522

C521

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

1

2

2

C530

C531

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

1

1

2

2

C528

C529

0.1U_0402_10V6K~L

0.1U_0402_10V6K~L

22U_1206_10V4Z~D

1

1

2

2

C350

C401

0.047U_0402_16V4M~L

0.047U_0402_16V4M~L

12

1

+2.5V_MEM

1

C930

22U_1206_10V4Z~D

2

@

1

1

1

2

2

2

C366

C451

0.047U_0402_16V4M~L

0.047U_0402_16V4M~L

0.047U_0402_16V4M~L

V_1P25V_DDR_VTT

12

C557

C190

10U_1206_6.3V7K

10U_1206_6.3V7K

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

C

Date: Sheet of

1

C931

2

1

1

1

2

C360

0.047U_0402_16V4M~L

1

2

2

C457

C383

0.047U_0402_16V4M~L

0.047U_0402_16V4M~L

V_1P25V_DDR_VTT

2

C382

0.047U_0402_16V4M~L

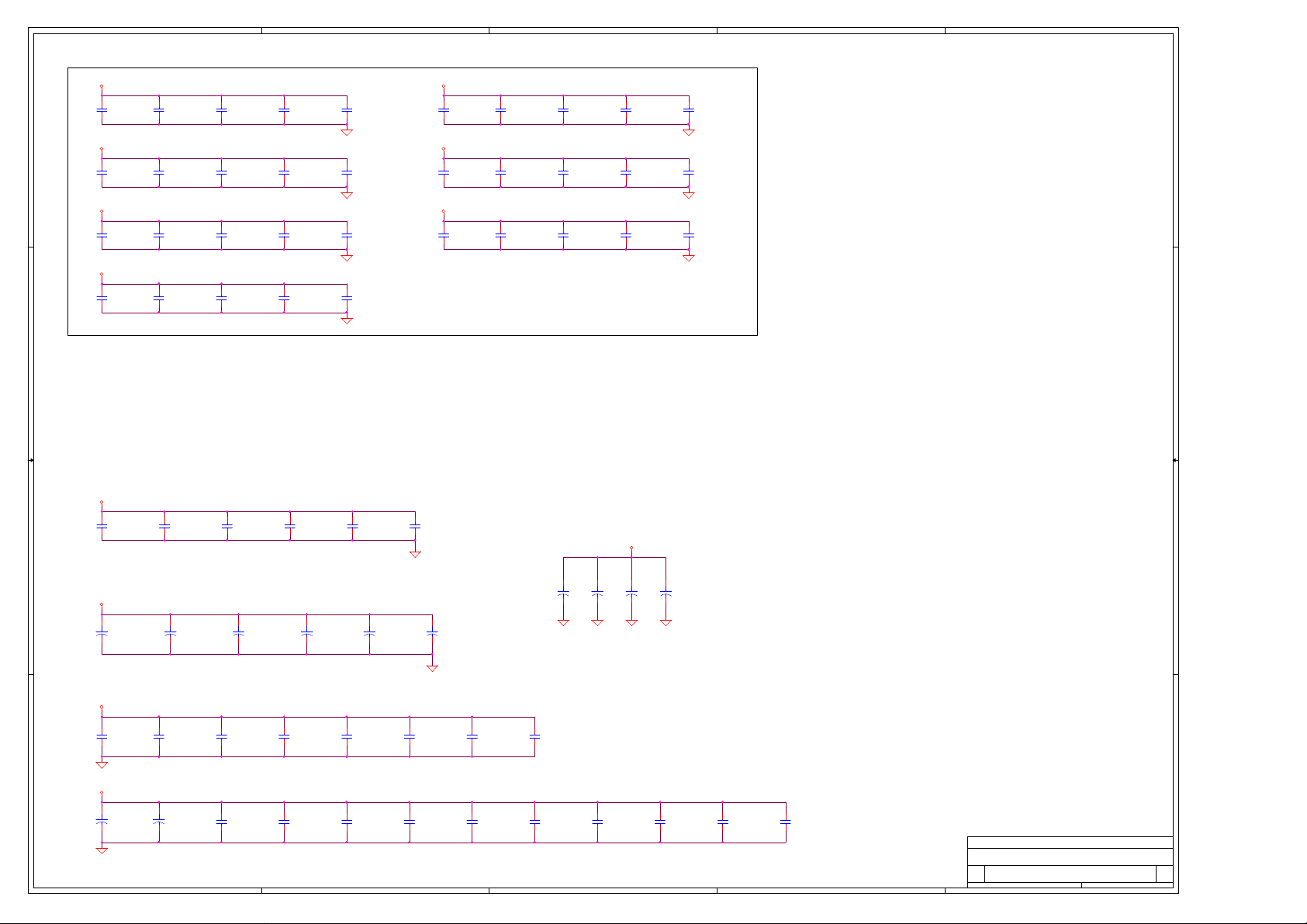

Compal Electronics, Inc.

Odem(3 of 3)

DDQ12/11/01 with LA-1901

1

+2.5V_MEM

1

+

@

2

C392

0.047U_0402_16V4M~L

12 59Wednesday, January 07, 2004

C78

150U_D_6.3VM_R55~D

@

3.0

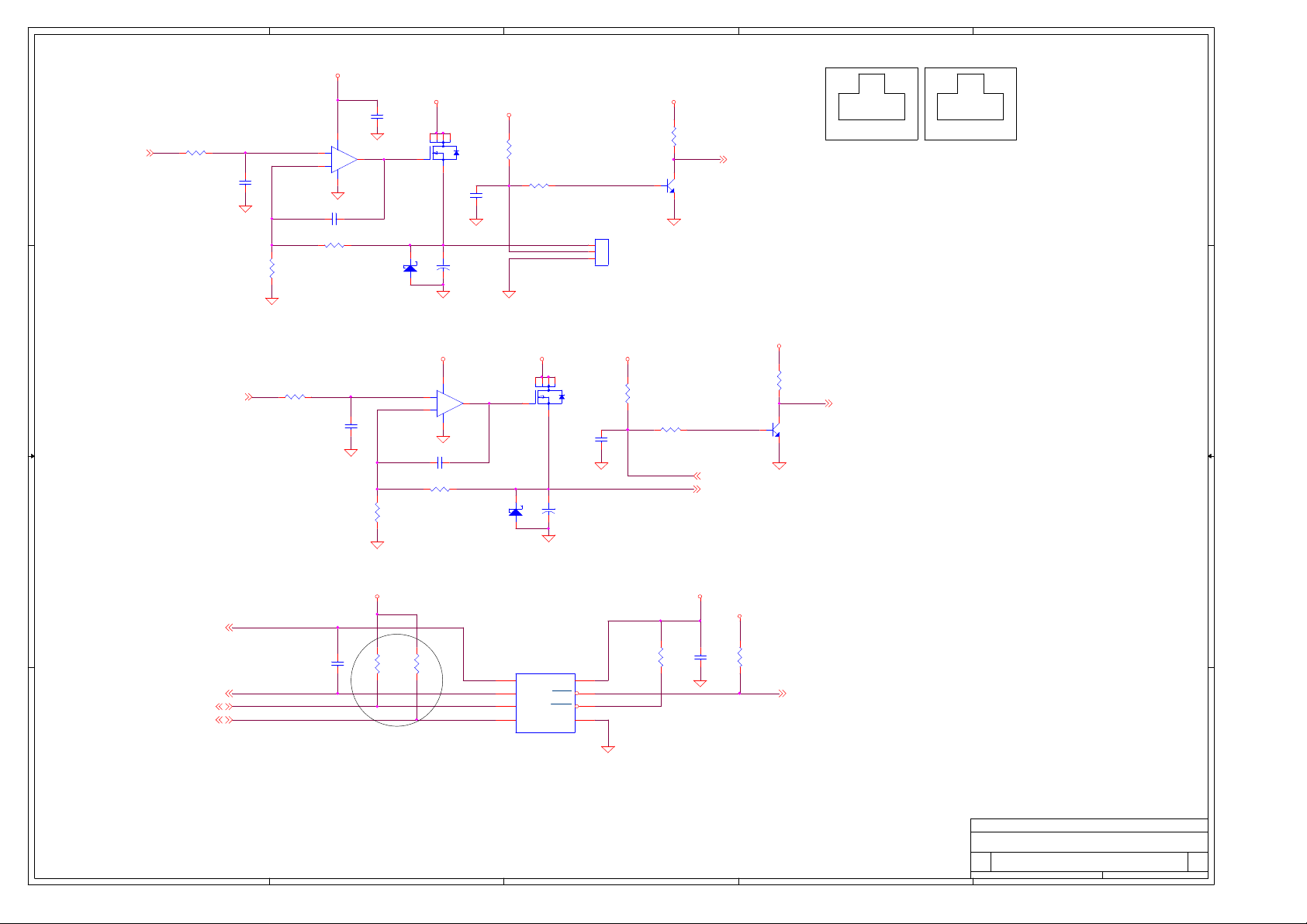

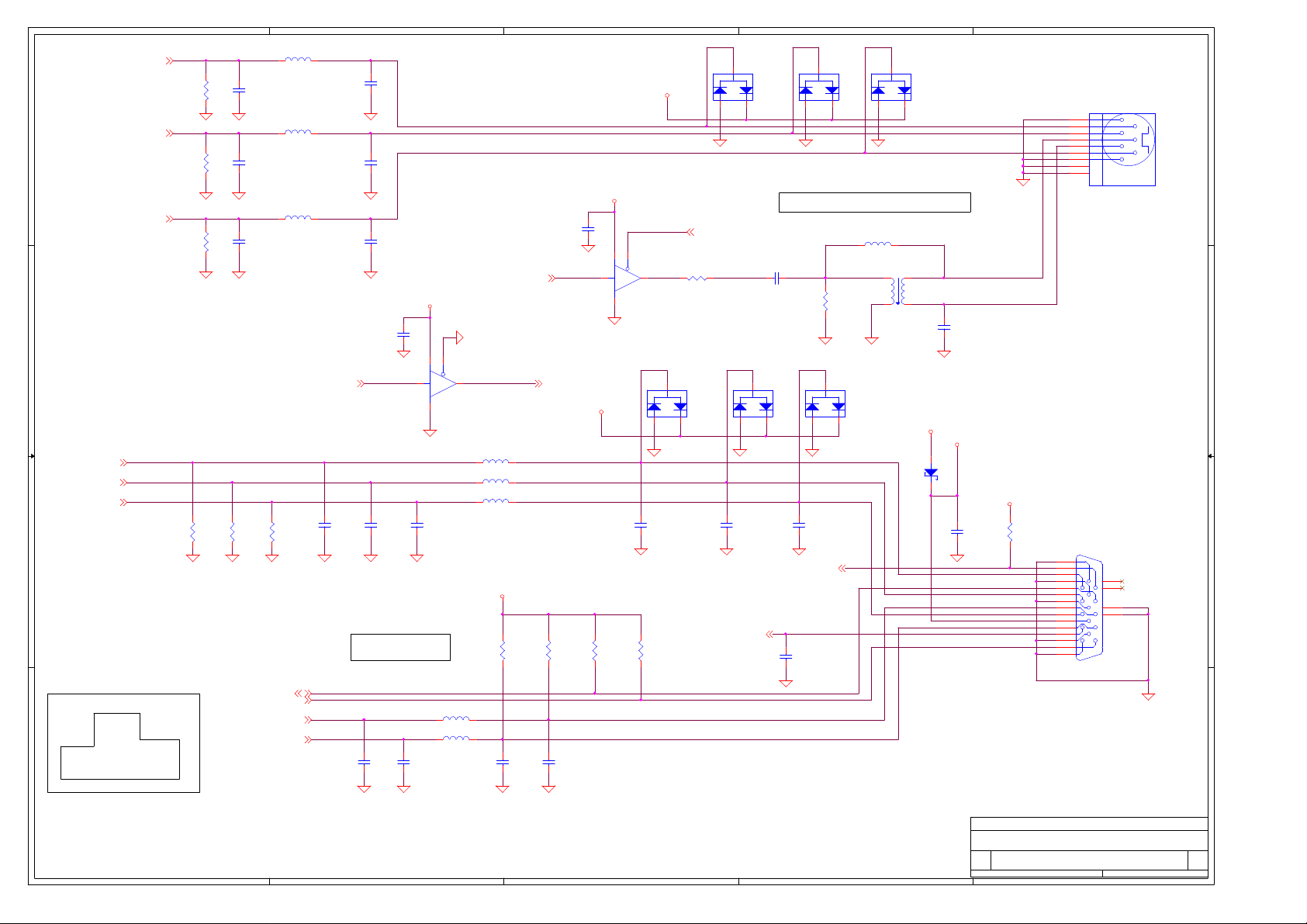

Page 13

5

+12V

D D

FAN1_PWM<<35>>

R130

100K_0402_5%~L

1 2

1

C128

2

1U_0805_10V6K~L

R128

FAN1VREF

FAN1_VFB

1 2

150K_0603_5%~L

8

5

IN+

6

IN-

4

C127

2200P_0603_50V7K~L @

1 2

R129

100K_0402_5%~L

4

FAN1 Control and Tachometer

C121

0.1U_0402_16V4Z~L

G

3

D9

2 1

+5VRUN

Q15

SI3456DV-T1_TSOP6~L

6

2

1

D

S

4 5

C476

FAN1_VOUT

1

+

C479

100U_D_10VM~L

2

+5VRUN

1

2

0.47U_1206_16V7K~L

U49B

LM358M_SO8~L

P

7

OUT

G

12

RB751V_SOD323~L

1

2

FAN1_ON

R110

10K_0402_5%~L

1 2

1K_0402_5%~L

1 2

R109

FAN1_TACH_FB

3

FAN1TACH_ON

FAN1

JFAN1

1

2

3

FOX_BP26037-H1R~L

+3VRUN

2

12

R117

10K_0402_5%~L

Q11

PMBT2222_SOT23~L

3 1

FAN1_TACH <<35>>

2

C

B

E 3

2

2222 SYMBOL(SOT23-NEW)

1

1

+3VALW

R41

1 2

10K_0402_5%~L

+3VRUN

12

2

3 1

R174

10K_0402_5%~L

FAN2_TACH <<35>>

Q18

PMBT2222_SOT23~L

ATF_INT# <<34>>

C C

R437

100K_0402_5%~L

FAN2_PWM<<35>>

B B

1 2

FAN2VREF

FAN2_VFB

1

C478

2

1U_0805_10V6K~L

R435

1 2

150K_0603_5%~L

+3VALW +3VRUN

+12V

8

P

3

IN+

OUT

2

IN-

G

4

C110

2200P_0603_50V7K~L@

1 2

R436

100K_0402_5%~L

U49A

LM358M_SO8~L

FAN2_ON

1

12

RB751V_SOD323~L

Q17

SI3456DV-T1_TSOP6~D

1

C472

2

0.47U_1206_16V7K~L

+5VRUN

R163

10K_0402_5%~L

1 2

FAN2_TACH_FB

FAN2

R168

1K_0402_5%~L

1 2

FAN2TACH_ON

FAN2_TACH_FB <<16>>

FAN2_5V <<16>>

+5VRUN

6

2

1

D

G

3

S

4 5

FAN2_5V

1

+

C495

D10

100U_D_10VM~L

2

2 1

CPU Temperature Sensor

H_THERMDA<<7>>

H_THERMDC<<7>>

CLK_SMB<<25,35,36>>

DAT_SMB<<25,35,36>>

A A

H_THERMDA

H_THERMDC

CLK_SMB

DAT_SMB

12

C44

R43

R42

1 2

2.2K_0603_5%

2200P_0603_50V7K

1 2

2.2K_0603_5%

06/18/2003 Item 128

U5

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032AR_SOP-8

VDD1

ALERT

THERM

GND

1

6

ADM1032_THERM#

4

5

R33

C36

1 2

1 2

10K_0402_5%~L@

0.1U_0402_16V4Z~L

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

Compal Electronics, Inc.

ITP Debug CONN. & FAN

DDQ12/11/01 with LA-1901

13 59Wednesday, January 07, 2004

1

3.0

Page 14

5

DDR_D[0..63]<<11>>

DDR_CB[0..7]<<11>>

DDR_DS[0..8]<<11>>

D D

DDR_CB4

DDR_CB0

DDR_D31

DDR_D27

DDR_D30

DDR_D26

DDR_DS3

DDR_D29

DDR_D25

DDR_D28

DDR_D24

DDR_D23

DDR_D19

DDR_D22

DDR_D18

DDR_DS2

C C

DDR_D21

DDR_D17

DDR_D20

DDR_D16

DDR_D15

DDR_D11

DDR_D14

DDR_D10

DDR_DS1

DDR_D13

DDR_D9

DDR_D12

DDR_D8

DDR_D7

DDR_D3

DDR_D6

B B

DDR_D2

DDR_DS0

DDR_D5

DDR_D1

DDR_D4

DDR_D0

DDR_CB7

DDR_CB3

DDR_CB6

DDR_CB2

DDR_DS8

DDR_CB5

DDR_CB1

DDR_D63

DDR_D59

A A

DDR_D62

DDR_D58

DDR_DS7

DDR_D61

RN20

1 4

2 3

RN40

1 4

2 3

RN19

1 4

2 3

RN39

1 4

2 3

RN18

1 4

2 3

RN38

1 4

2 3

RN17

1 4

2 3

RN37

1 4

2 3

RN16

1 4

2 3

RN36

1 4

2 3

RN35

1 4

2 3

RN15

1 4

2 3

RN34

1 4

2 3

RN14

1 4

2 3

RN33

1 4

2 3

RN13

1 4

2 3

RN32

1 4

2 3

RN12

1 4

2 3

RN31

1 4

2 3

RN22

1 4

2 3

RN42

1 4

2 3

RN21

1 4

2 3

RN41

1 4

2 3

RN57

1 4

2 3

RN30

1 4

2 3

RN56

1 4

2 3

DDR_CB4_R

DDR_CB0_R

10_4P2R_0402_5%~L

DDR_D31_R

DDR_D27_R

10_4P2R_0402_5%~L

DDR_D30_R

DDR_D26_R

10_4P2R_0402_5%~L

DDR_DS3_R

DDR_D29_R

10_4P2R_0402_5%~L

DDR_D25_R

DDR_D28_R

10_4P2R_0402_5%~L

DDR_D24_R

DDR_D23_R

10_4P2R_0402_5%~L

DDR_D19_R

DDR_D22_R

10_4P2R_0402_5%~L

DDR_D18_R

DDR_DS2_R

10_4P2R_0402_5%~L

DDR_D21_R

DDR_D17_R

10_4P2R_0402_5%~L

DDR_D20_R

DDR_D16_R

10_4P2R_0402_5%~L

DDR_D15_R

DDR_D11_R

10_4P2R_0402_5%~L

DDR_D14_R

DDR_D10_R

10_4P2R_0402_5%~L

DDR_DS1_R

DDR_D13_R

10_4P2R_0402_5%~L

DDR_D9_R

DDR_D12_R

10_4P2R_0402_5%~L

DDR_D8_R

DDR_D7_R

10_4P2R_0402_5%~L

DDR_D3_R

DDR_D6_R

10_4P2R_0402_5%~L

DDR_D2_R

DDR_DS0_R

10_4P2R_0402_5%~L

DDR_D5_R

DDR_D1_R

10_4P2R_0402_5%~L

DDR_D4_R

DDR_D0_R

10_4P2R_0402_5%~L

DDR_CB7_R

DDR_CB3_R

10_4P2R_0402_5%~L

DDR_CB6_R

10_4P2R_0402_5%~L

DDR_CB2_R

DDR_DS8_R

10_4P2R_0402_5%~L

DDR_CB5_R

DDR_CB1_R

10_4P2R_0402_5%~L

DDR_D63_R

DDR_D59_R

10_4P2R_0402_5%~L

DDR_D62_R

DDR_D58_R

10_4P2R_0402_5%~L

DDR_DS7_R

DDR_D61_R