Dell 9300 Schematics

5

D D

4

3

2

1

SULLIVAN

REV : X01

C C

B B

@ : Depop Component for All

DothanSchematic with Capture CIS and Functionfield

uFCPGADothan

A A

02-11-2004

REV: 0.2

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

DELL CONFIDENTIAL/PROPRIETARY

Title

Size DocumentNumber Rev

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

LA-2171

1 50, 12, 2004

1

0.2

5

4

3

2

1

Compal confidential

GUARDIAN

D D

EMC6N300

page 15

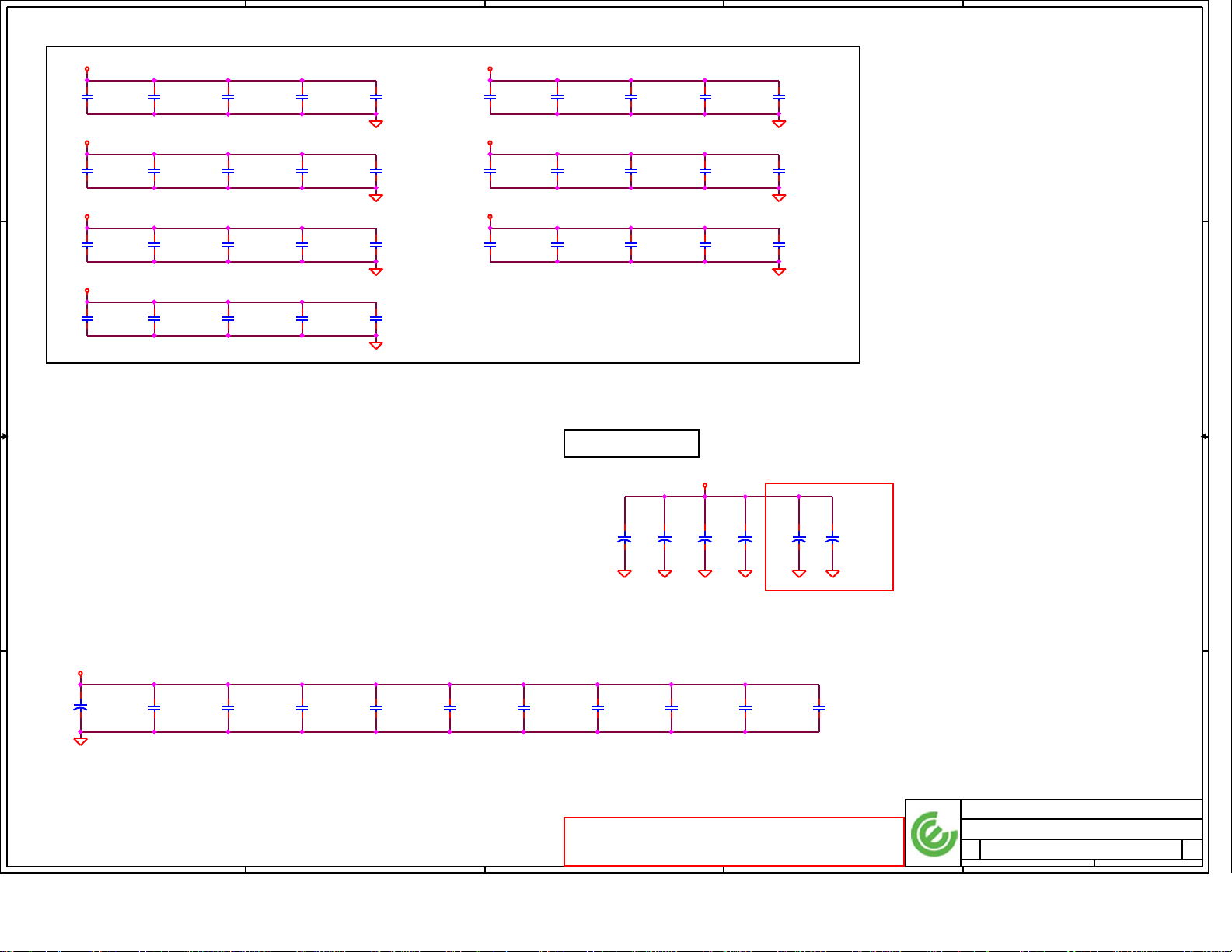

HA#(3..31)

CRT CONN.

& TV-OUT

VGA

page 19

Board

PCI-E 16X

VGA CONN.

C C

page 18

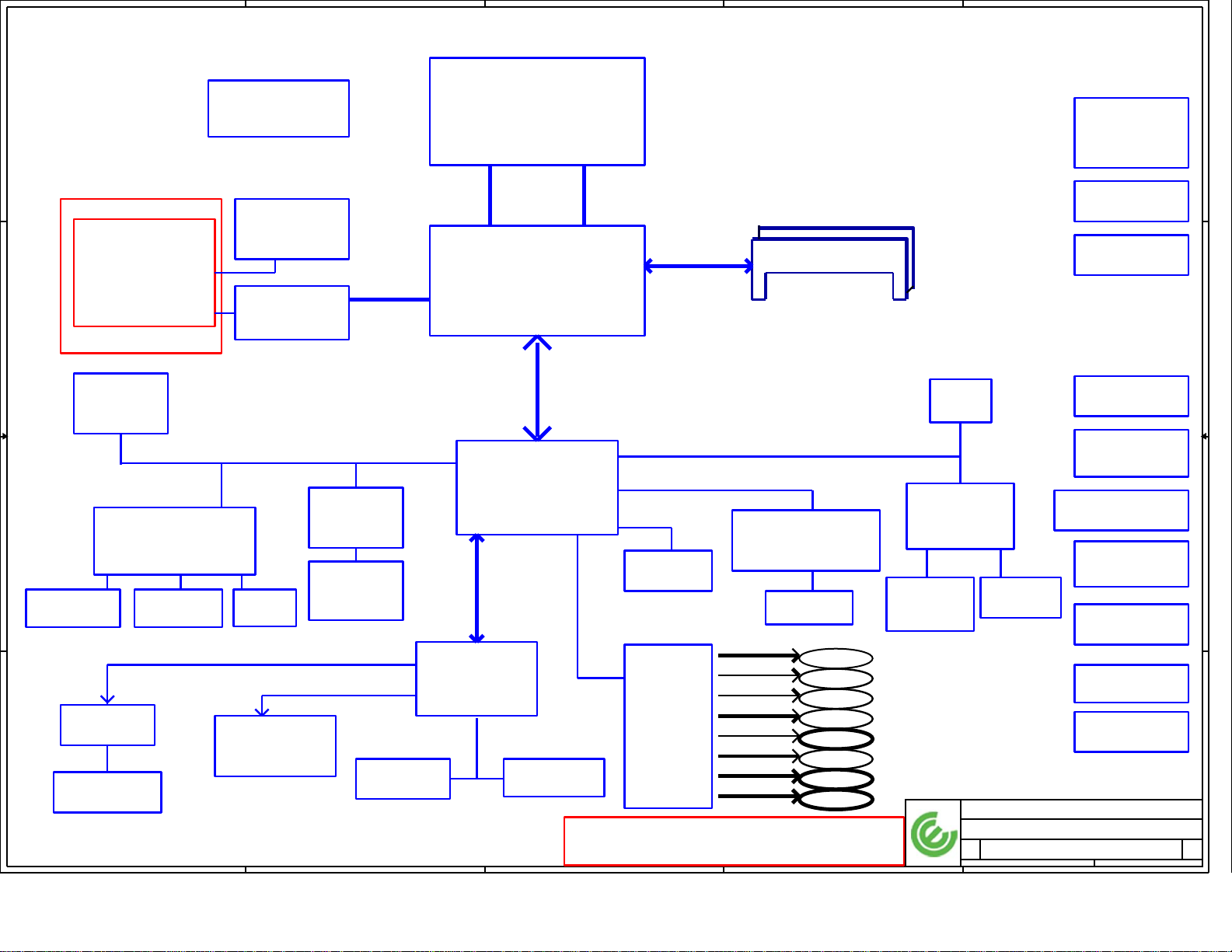

Dothan

uFCPGA CPU

System Bus

400 /533MHz

Alviso

GMCH-M

1257 FC-BGA

page 10,11,12,13,14

page 7,8,9

HD#(0..63)

Memory

BUS(DDRII)

1.8V 400 / 533MHz

SO-DIMM X2

BANK0, 1, 2, 3

page 16,17

Block Diagram

Clock Generator

CK410M

page 6

Fan Control

page 15

LED/B

page 37

DMI

MINI PCI

page 33

PCI BUS

IDSEL:AD17

(PIRQA/B#,GNT#2,REQ#2)

3.3V 33MHz

LAN

BCM4401

CardBus Controller

B B

RICHO R5C841

page 31,32

page 29

Transformer

SDIO CONN.

page32

1394 CONN.

page31

Slot 0

page32

GPIO

& RJ45

page 30

LPC BUS

3.3V 33MHz

Macallan III

X BUS

LCM CONN.

page36

A A

Multi-media

SST39VF080

page 36

Touch Pad

page 36

Board

5

4

1.5V

100MHz

LPC toX-BUS

& Super I/O

page 34,35

ICH6

609 BGA

Int.KBD

3.3V 24.576MHz

3.3V or 5V SATA

ATA100

SATA

SATA to PATA Bridge

Marvell 88SA8040

CDROM

page 24

HDD

USBPORT 0

USBPORT 1

48MHz / 480Mb

page 36

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

USB2.0

page 28

3

USBPORT 2

USBPORT 3

USBPORT 4

USBPORT 5

USBPORT 6

USBPORT 7

NEW CARD

page 24

page 24

JUSB1 U

JUSB1 D

Blue Tooth

JUSB2 U

JUSB2 D

JUSB3 U

JUSB3 D

2

MDC

page 27

AC-LINK

AC97 CODEC

STAC9751

AMP &

Phone Jack

page 26

DC IN

page 41

BATT IN/+2.5V

page 42

1.5V/1.05V(+VCCP)

page 25

page 43page 20,21,22,23

5V/3.3V/15V

page 44

Subwoofer

page 27

1.8V / 0.9V

VCORE

page 45

page 46

CHARGER

page 47

DELL CONFIDENTIAL/PROPRIETARY

Title

Size DocumentNumber Rev

Date: Sheet of

Compal Electronics, Inc.

Block Diagram

LA-2171

2 50, 12, 2004

1

0.2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

5

D D

4

3

2

1

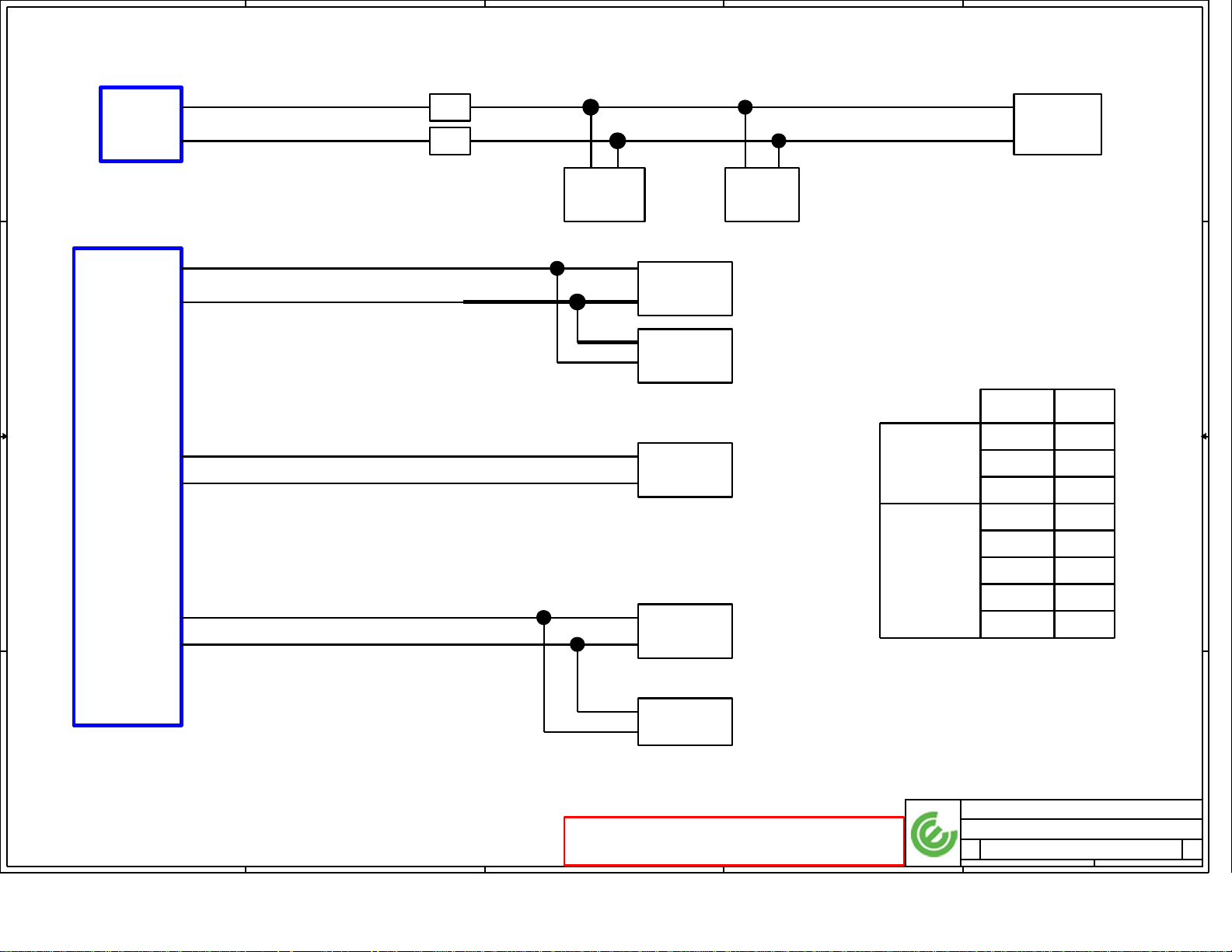

PM TABLE

C C

power

plane

State

S0

S1

S3

S5 S4/AC

B B

S5 S4/AC don't exist

A A

+3VALW

+5VALW

ON

ON

ON

ON

+3VSUS

+5VSUS

+1.8VSUS

+1.5VSUS

ON ON

ON

ON

OFF

OFFOFF

+5VRUN

+3VRUN

+0.9V_DDR_VTT

+2.5VRUN

+1.8VRUN

+1.5VRUN

+VCC_CORE

+VCCP

+15V

ON

OFF

OFF

OFF

PCI TABLE

PCI DEVICE

CARD BUS

MINI PCI

IDSEL

AD17

AD19

REQ#/GNT#

1

3

LAN AD16 4 C

PIRQ

D,C

D,B

USB TABLE

USB PORT#0DESTINATION

JUSB1 (Top)

1

2

3

4

5

6

7

JUSB1 (Bottom)

Blue Tooth

NEW CARD

JUSB2 (Top)

JUSB2 (Bottom)

JUSB3 (Top)

JUSB3 (Bottom)

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

DELL CONFIDENTIAL/PROPRIETARY

Title

Size DocumentNumber Rev

Date: Sheet of

Compal Electronics, Inc.

Index and Config.

LA-2171

3 50, 12, 2004

1

0.2

5

D D

4

3

2

1

+5VALW

ADAPTER

PWR_SRC

+3VALW

BATTERY

C C

SUS_ON

+5VSUS

B B

+5VHDD +5VMOD +5VRUN VDDA

A A

RUN_ON

PL9

+15V +2.5VRUN

(Option)

AUDIO_AVDD_ON

+3VRUN

L10

SUS_ON

+3VSRC

RUN_ON

V3P3LAN

SUSPWROK_5V

+3VSUS

+VCC_CORE

RUN_ON_D

RUNPWROK

+1.5VSUS

RUN_ON SUSPWROK_1.5V

RUNPWROK

+VCCP

+1.5VRUN

SUSPWROK_5V

+1.8VSUSP +0.9V_DDR_VTT

PJP11,PJP12

+1.8VSUS

RUN_ON

SUSPWROK_5V

+1.8VRUN

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size DocumentNumber Rev

Date: Sheet of

Compal Electronics, Inc.

Power Rail

LA-2171

4 50, 12, 2004

1

0.2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

5

4

3

2

1

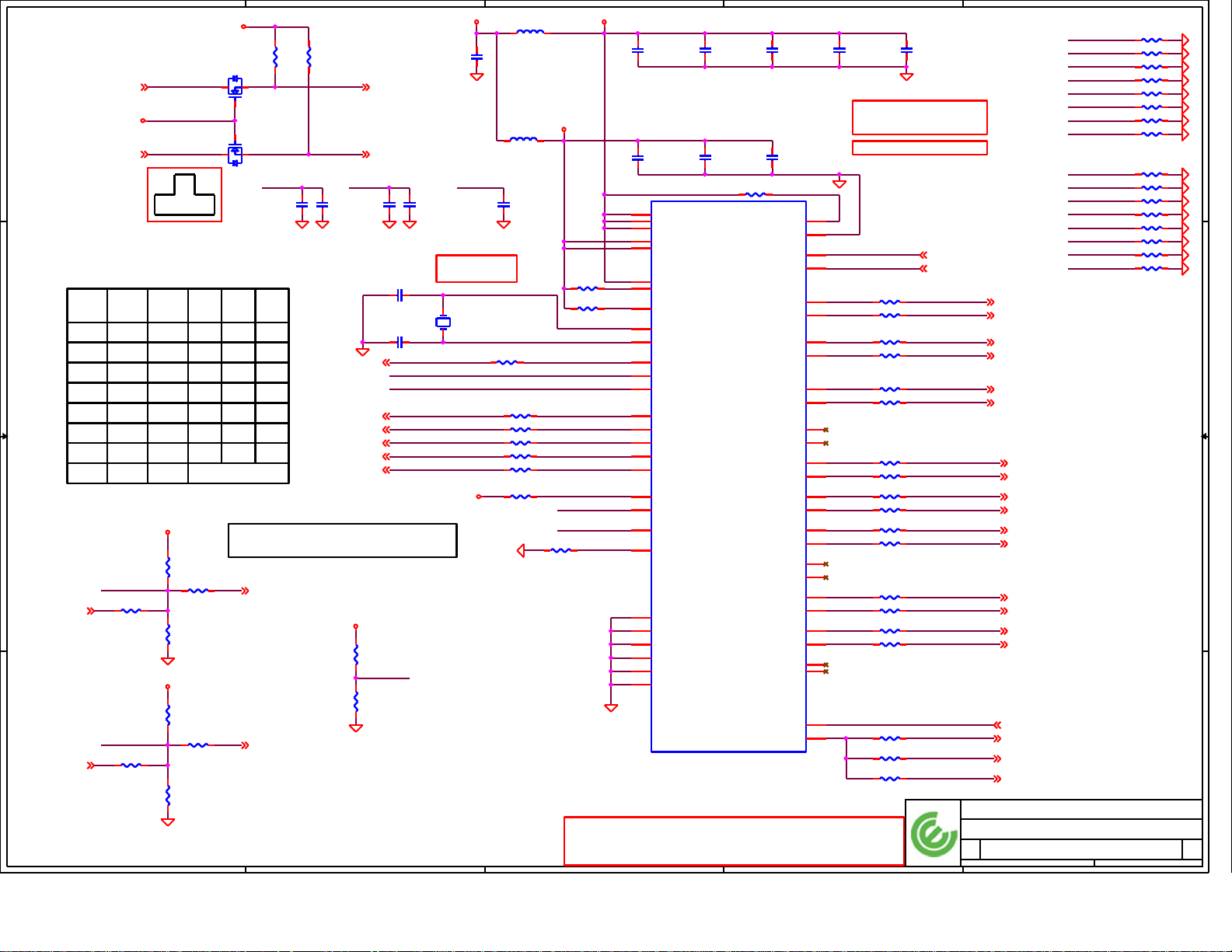

ICH_SMBCLK

D D

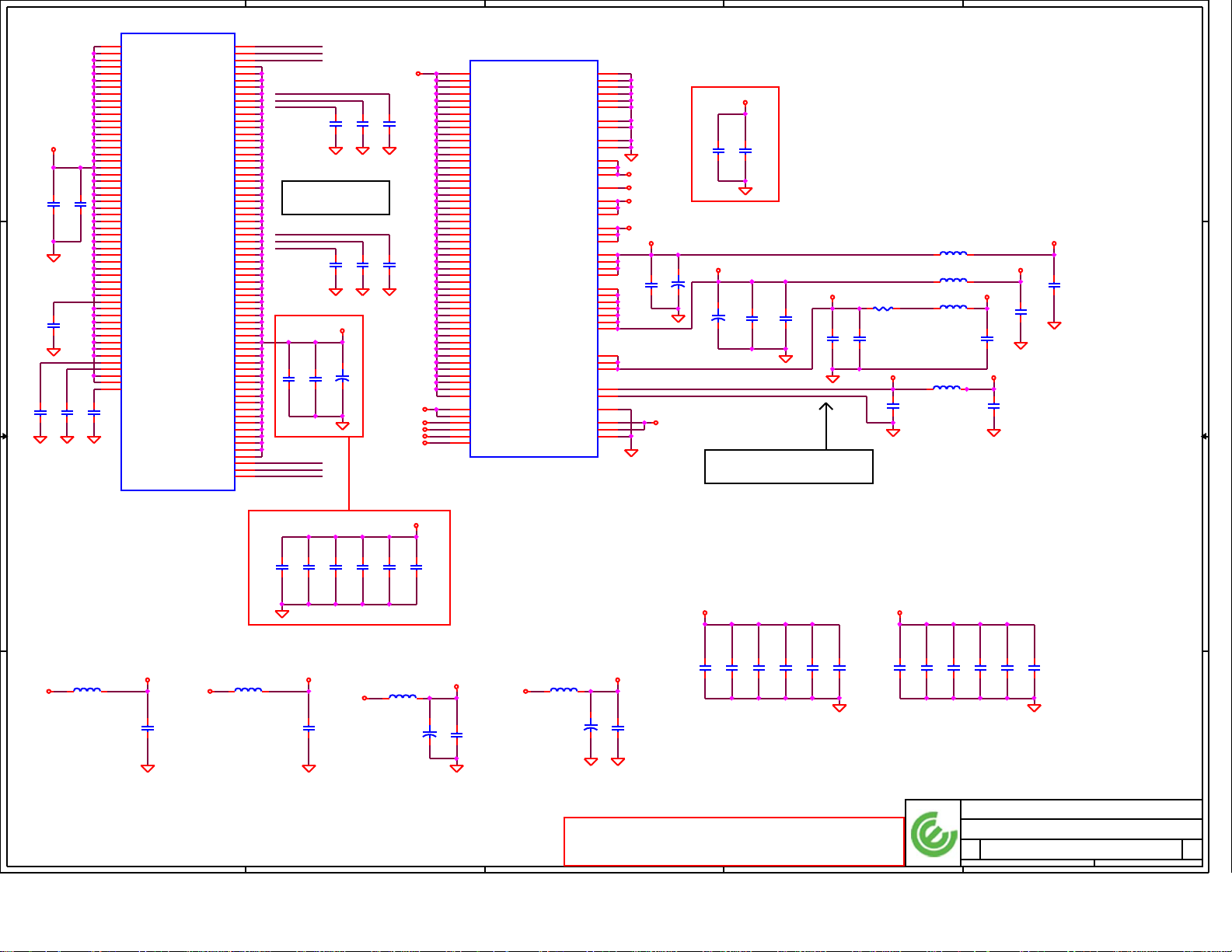

ICH6

ICH_SMBDATA

+3VSUS

7002

+3VRUN

7002

CK_SCLK

CK_SDATA

CLK GEN.

DIMM1DIMM0

CLK_SMB

DAT_SMB

C C

+3VALW

GUARDIAN

24C04

Device Address

SIO

Macallan III

B B

SMBCLK_VGA

SMBDAT_VGA +5VALW VGA

ICH6-SMBus

DIM0

DIM1

CLK GEN.

GUARDIAN

24C04

A0h

A2h

D2h

5Eh

A2h

PBAT_SMBCLK

PBAT_SMBDAT +5VALW BATTERY

EC-SMBus

VGA

Battery

Charger

58h

16h

12h

CHARGER

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size DocumentNumber Rev

Date: Sheet of

Compal Electronics, Inc.

SMBUS TOPOLOGY

LA-2171

5 50, 12, 2004

1

0.2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

5

+3VRUN

ICH_SMBDATA<22>

D D

ICH_SMBCLK<22>

ICH_SMBDATA

+3VRUN

ICH_SMBCLK

D

1 3

1 3

D

D

1

3

G

S

2

2N7002

12

12

R117

R118

Q9

100K_0402_5%~D

100K_0402_5%~D

S

2N7002_SOT23~D

G

2

2

G

Q10

2N7002_SOT23~D

S

CK_VDD_A CK_VDD_REF

CK_SDATA

CK_SCLK

1

2

C401

4.7U_0805_6.3V6K~D

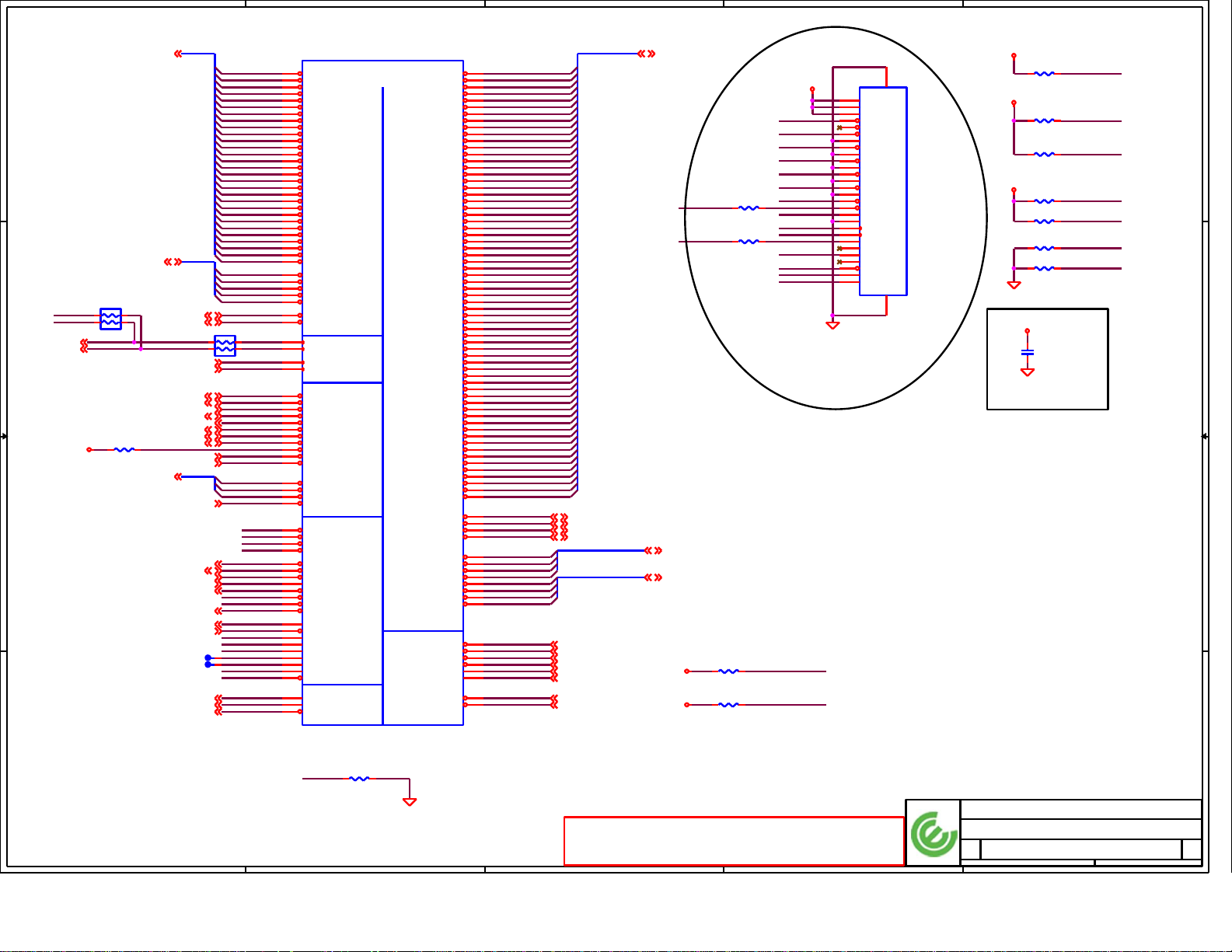

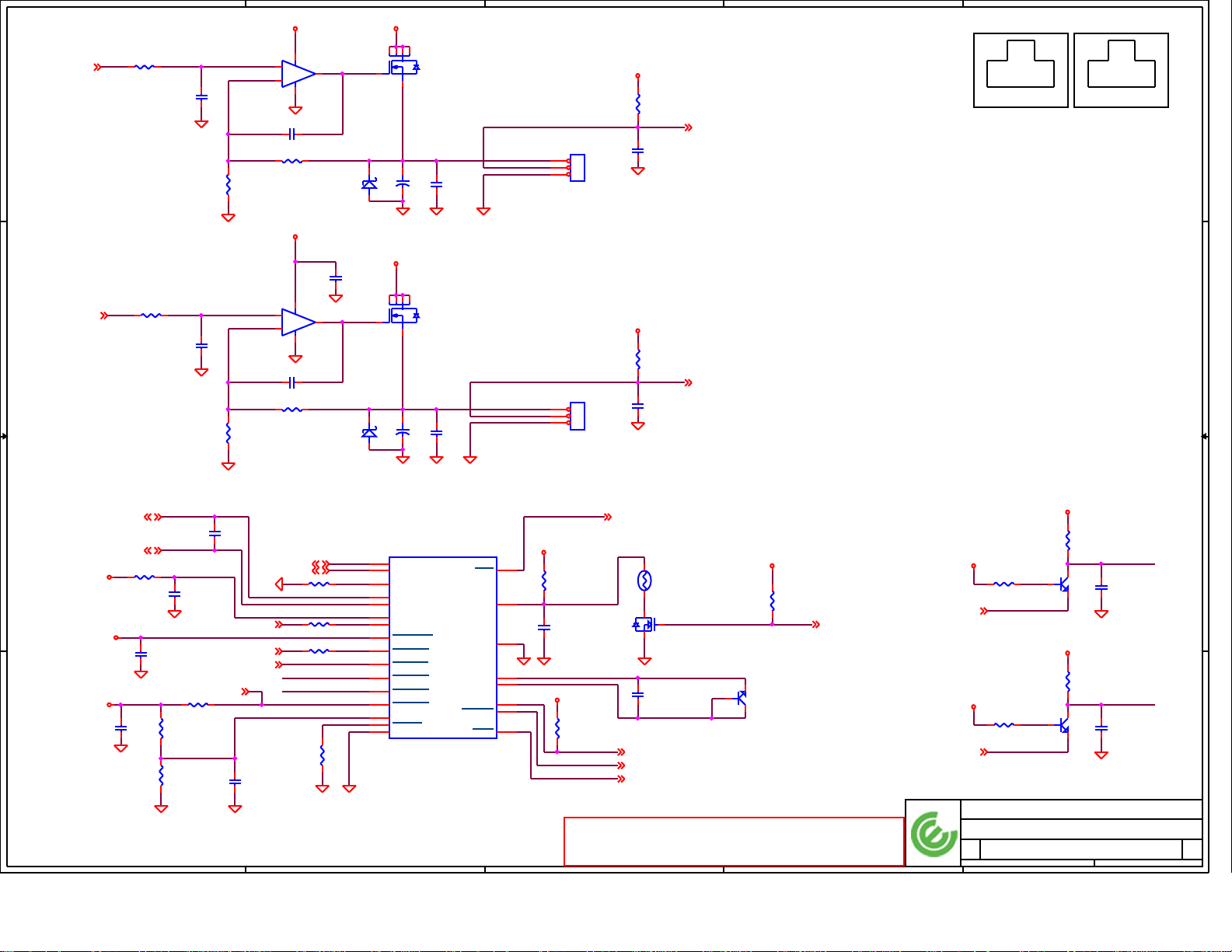

0 0 1 for Dothan-A 533Mhz

1 0 1 for Dothan-A 400Mhz

FSC FSB FSA CPU

CLKSEL0 CLKSEL1 CLKSEL2

C C

*

00

0

1

1 1

0

0

1

11

1

0

0

1

0

0

0

0

0

1

1

1

Table :ICS 954201 / Cypress CY28411

+VCCP

B B

CLKSEL0

CPU_BSEL0<8>

A A

CPU_BSEL1<8>

1 2

R395

0_0402_5%~D@

CLKSEL1

1 2

R396

0_0402_5%~D@

5

1 2

1 2

+VCCP

1 2

1 2

R390

1 2

R391

1K_0402_5%~D

R394

0_0402_5%~D

R389

1K_0402_5%~D

@

1 2

R392

1K_0402_5%~D

R393

0_0402_5%~D

MHz

266

133

200

166

333

100

400

1K_0402_5%~D@

SRC

PCI

MHz

MHz

100 33.30

33.3

100

33.3

100

33.3

100

33.3

100

33.3

100

33.3

100

RESERVED

Dothan-A 400MHz, Install R390, Nopop. R394, R395

Dothan-A 533MHz, Install R394, Nopop. R390, R395

MCH_CLKSEL0 <10>

MCH_CLKSEL1 <10>

4

CK_SDATA <16,17>

CK_SCLK <16,17>

CK_VDD_48

1

2

C57

0.047U_0402_10V7K~D

CK_48M_ICH<22>

CK_33M_CBPCI<31>

CK_33M_SIOPCI<34>

CK_33M_MINIPCI<33>

CK_33M_LANPCI<29>

CK_33M_ICHPCI<20>

+3VRUN

1

1

2

2

C405

R86

10K_0402_5%~D

1 2

CLKSEL2

R94

10K_0402_5%~D

@

1 2

C69

4.7U_0805_6.3V6K~D

C83

33P_0402_50V8J~D@

12

C77

33P_0402_50V8J~D@

12

CLKSEL1

CLKSEL0 CK_ITP

CK_33M_CBPCI

CK_33M_SIOPCI

CK_33M_MINIPCI

CK_33M_LANPCI

CK_33M_ICHPCI

+3VRUN

1 2

L20

BLM21PG600SN1D_0805~D

1

C100

2

0.1U_0402_16V4Z~D

1 2

L21

BLM21PG600SN1D_0805~D

1

2

C72

0.047U_0402_10V7K~D

Placecrystal within

500milsofCK410

X2

14.31818MHz_20P_1BX14318CC1A~D12R113

R84 33_0402_5%~D

+3VRUN

0.047U_0402_10V7K~D

CK_XTAL_IN

CK_XTAL_OUT

12

12

R93 33_0402_5%~D

12

R95 33_0402_5%~D

12

R106 33_0402_5%~D

12

R123 33_0402_5%~D

12

R83 33_0402_5%~D

R85

10K_0402_5%~D

1 2

CK_VDD_MAIN2

1 2

R385 475_0603_1%~D

1 2

R119

1_0402_5%~D

1 2

2.2_0402_5%~D

PCICLKF0

3

CK_VDD_MAIN

CK_VDD_REF

CK_VDD_48

CLKSEL2CK_48M_ICH

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLKF1

CK_SCLK

CK_SDATA

CLKIREF

2

C42

10U_0805_10V4M~D

1

2

C94

10U_0805_10V4M~D

1

U7

21

VDD_SRC0

28

VDD_SRC1

34

VDD_SRC2

1

VDD_PCI0

7

VDD_PCI1

42

VDD_CPU

48

VDD_REF

11

VDD_48

50

XTAL_IN

49

XTAL_OUT

12

FSA/USB_48

16

FSB/TEST_MODE

53

FSC/TEST_SEL

5

PCI5

4

PCI4

3

PCI3

56

PCI2

9

PCIF1

8

PCIF0/ITP_EN

46

SCLOCK

47

SDATA

39

IREF

13

VSS_48

29

VSS_SRC

2

VSS_PCI0

45

VSS_CPU

51

VSS_REF

6

VSS_PCI1

CY28411ZCT_TSSOP56~D

1

C49

0.047U_0402_10V7K~D

2

1

C78

0.047U_0402_10V7K~D

2

R376

2.2_0402_5%~D

1 2

CPU_2_ITP/SRC_7

CPU_2_ITP/SRC7#

VTT_PWRGD#/PD

1

C62

0.047U_0402_10V7K~D

2

1

C89

0.047U_0402_10V7K~D

2

CK_VDD_A

37

VDD_A

38

VSS_A

55

PCI_STOP#

54

CPU_STOP#

41

CPU1

40

CPU1#

44

CPU0

43

CPU0#

36

35

33

SRC6

32

SRC6#

31

SRC5

30

SRC5#

26

SRC4

27

SRC4#

24

SRC3

25

SRC3#

22

SRC2

23

SRC2#

19

SRC1

20

SRC1#

17

SRC0

18

SRC0#

14

DOT96

15

DOT96#

10

52

REF

2

1

C44

0.047U_0402_10V7K~D

2

1

C53

0.047U_0402_10V7K~D

2

Place near each pin

W>40 mil

Place near CK410M

H_STP_PCI#

H_STP_CPU#

CK_CPU1

1 2

R71 33_0402_5%~D

CK_CPU1#

1 2

R66 33_0402_5%~D

CK_CPU0

1 2

R81 33_0402_5%~D

CK_CPU0#

1 2

R76 33_0402_5%~D

CK_CPU2

1 2

R59 33_0402_5%~D

CK_CPU2#

1 2

R54 33_0402_5%~D

SCR5 CLK_MCH_3GPLL

1 2

R47 33_0402_5%~D

SRC5#

1 2

R41 33_0402_5%~D

SRC4

1 2

R48 33_0402_5%~D

SRC4#

1 2

R42 33_0402_5%~D

SRC3 CLK_PCIE_TV

1 2

R551 33_0402_5%~D

SRC3#

1 2

R552 33_0402_5%~D

SRC1

1 2

R67 33_0402_5%~D

SRC1#

1 2

R63 33_0402_5%~D

SRC2

1 2

R55 33_0402_5%~D

SRC2# CLK_PCIE_ICH#

1 2

R50 33_0402_5%~D

CLK_ENABLE#

CLKREF

1 2

R116 12.1_0402_1%~D

1 2

R112 12.1_0402_1%~D

1 2

R122 12.1_0402_1%~D

H_STP_PCI# <22>

H_STP_CPU# <22,46>

CLK_MCH_BCLK

CLK_MCH_BCLK#

CK_BCLK

CK_BCLK#

CK_ITP#

CLK_MCH_3GPLL#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_TV#

CLK_PCIE_VGA

CLK_PCIE_VGA#

CLK_PCIE_ICH

CK_14M_ICH

CK_14M_SIO

CK_14M_CODEC

CLK_MCH_BCLK <10>

CLK_MCH_BCLK# <10>

CK_BCLK <7>

CK_BCLK# <7>

CK_ITP <7>

CK_ITP# <7>

CLK_MCH_3GPLL <12>

CLK_MCH_3GPLL# <12>

CLK_PCIE_SATA <21>

CLK_PCIE_SATA# <21>

CLK_PCIE_TV <37>

CLK_PCIE_TV# <37>

CLK_PCIE_VGA <18>

CLK_PCIE_VGA# <18>

CLK_PCIE_ICH <22>

CLK_PCIE_ICH# <22>

CLK_ENABLE# <46>

CK_14M_ICH <22>

CK_14M_SIO <34>

CK_14M_CODEC <25>

1

CLK_MCH_BCLK

CLK_MCH_BCLK#

CK_BCLK

CK_BCLK#

CK_ITP

CK_ITP#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_VGA

CLK_PCIE_VGA#

CLK_PCIE_TV

CLK_PCIE_TV#

R70

49.9_0402_1%~D

R65

49.9_0402_1%~D

R80

49.9_0402_1%~D

R75

49.9_0402_1%~D

R58

49.9_0402_1%~D

R53

49.9_0402_1%~D

R49

1 2

49.9_0402_1%~D

R43

1 2

49.9_0402_1%~D

R56

1 2

49.9_0402_1%~D

R51

1 2

49.9_0402_1%~D

R46

1 2

49.9_0402_1%~D

R40

1 2

49.9_0402_1%~D

R68

1 2

49.9_0402_1%~D

R64

1 2

49.9_0402_1%~D

R553

1 2

49.9_0402_1%~D

R554

1 2

49.9_0402_1%~D

12

12

12

12

12

12

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size DocumentNumber Rev

Date: Sheet of

Compal Electronics, Inc.

Clock Generator

LA-2171

6 50, 12, 2004

1

0.2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

5

4

3

2

1

H_A#[3..31]<10>

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

1 4

2 3

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CPU_CK_ITP

CPU_CK_ITP#

CK_BCLK

CK_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_DBRESET#

H_DBSY#

H_DPSLP#

H_DPRSLP#

ITP_BPM#4

ITP_BPM#5

H_PROCHOT#

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

D D

H_REQ#[0..4]<10>

RN2

0_0404_4P2R_5%~D

CK_ITP_R#

1 4

CK_ITP_R

C C

B B

2 3

+VCCP

CK_ITP

CK_ITP#

R92

56_0402_5%~D

1 2

CK_ITP<6>

CK_ITP#<6>

H_ADSTB#0<10>

H_ADSTB#1<10>

0_0404_4P2R_5%~D

CK_BCLK<6>

CK_BCLK#<6>

H_DEFER#<10>

H_DRDY#<10>

H_LOCK#<10>

H_RESET#<10>

H_RS#[0..2]<10>

H_TRDY#<10>

ITP_DBRESET#<39>

H_PROCHOT#<35>

T2 PAD~D

T21 PAD~D

H_THERMDA<15>

H_THERMDC<15>

H_THERMTRIP#<15>

RN3

@

H_ADS#<10>

H_BNR#<10>

H_BPRI#<10>

H_BR0#<10>

H_HIT#<10>

H_HITM#<10>

H_DBSY#<10>

H_DPSLP#<21>

H_DPRSLP#<21>

H_DPWR#<10>

H_PWRGOOD<21>

H_CPUSLP#<10,21>

JCPUA

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

ADDR GROUP

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

U3

ADSTB0#

AE5

ADSTB1#

A16

ITP_CLK0

A15

ITP_CLK1

B15

BCLK0

B14

BCLK1

N2

ADS#

L1

BNR#

J3

BPRI#

N4

BR0#

L4

DEFER#

H2

DRDY#

K3

HIT#

K4

HITM#

A4

IERR#

J2

LOCK#

B11

RESET#

H1

RS0#

K1

RS1#

L2

RS2#

M3

TRDY#

C8

BPM0#

B8

BPM1#

A9

BPM2#

C9

BPM3#

A7

DBR#

M2

DBSY#

B7

DPSLP#

G1

DPRSTP#

C19

DPWR#

A10

PRDY#

B10

PREQ#

B17

PROCHOT#

E4

PWRGOOD

A6

SLP#

A13

TCK

C12

TDI

A12

TDO

C5

TEST1

F23

TEST2

C11

TMS

B13

TRST#

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

AMP_1473129-1_Dothan~D

Dothan

DATA GROUP

HOST CLK

CONTROL GROUP

MISC

THERMAL

DIODE

LEGACY CPU

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

D25

J26

T24

AD20

C23

K24

W25

AE24

C22

L24

W24

AE25

C2

D3

A3

B5

D1

D4

C6

B4

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20H_A#23

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

H_DINV#0 <10>

H_DINV#1 <10>

H_DINV#2 <10>

H_DINV#3 <10>

H_A20M# <21>

H_FERR# <21>

H_IGNNE# <21>

H_INIT# <21>

H_INTR <21>

H_NMI <21>

H_STPCLK# <21>

H_SMI# <21>

H_D#0H_A#3

A19

H_D#[0..63] <10>

H_RESET#

ITP_TDO

H_DSTBN#[0..3] <10>

H_DSTBP#[0..3] <10>

+VCCP

+VCCP

R20

22.6_0603_1%~D

1 2

R31

22.6_0603_1%~D

1 2

R397

75_0402_5%~D

1 2

R405

200_0402_5%~D

1 2

+VCCP

ITP_DBRESET# ITP_TDO

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

CK_ITP_R

CK_ITP_R#

ITP_TCK

ITP_TRST#

ITP_TMS

ITP_TDI

29

JITP

28

VTT1

GND6

27

VTT0

26

VTAP

25

DBR#

24

DBA#

23

BPM0#

22

GND5

21

BPM1#

20

GND4

19

BPM2#

18

GND3

17

BPM3#

16

GND2

15

BPM4#

14

GND1

13

BPM5#

12

RESET#

11

FBO

10

GND0

9

BCLKP

8

BCLKN

7

TDO

6

NC2

5

TCK

4

NC1

3

TRST#

2

TMS

1

TDI

GND7

MOLEX_52435-2891_28P~D@

30

Check ITP connector.

H_THERMTRIP#

H_PWRGOOD

Add pullupsfor PWRGOOD and THERMTRIP per INTEL

+3VSUS

R11

150_0402_5%~D

1 2

+VCCP

R36

54.9_0603_1%~D

1 2

R19

54.9_0603_1%~D

1 2

+VCCP

R61

39.2_0603_1%~D

1 2

R62

150_0402_5%~D

1 2

R45

680_0402_5%~D

1 2

R44

27.4_0603_1%~D

1 2

+VCCP

1

C20

0.1U_0402_10V7K~D

2

Place near JITP

ITP_DBRESET#

H_RESET#

ITP_TMS

ITP_TDI

Thisshallplace near CPU

ITP_TRST#

ITP_TCK

A A

5

TEST1

R99

1 2

1K_0402_5%~D@

4

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

DELL CONFIDENTIAL/PROPRIETARY

Title

Size DocumentNumber Rev

2

Date: Sheet of

Compal Electronics, Inc.

Dothan Processor(1/2)

LA-2171

7 50, 12, 2004

1

0.2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

5

4

3

2

1

R208

+VCCA_PROC

OPEN

+1.8VRUN

D D

For test only ,Cmos output

CPU Voltage ID

10K_1206_8P4R_5%~D

H_VID0

R383 0_0402_5%~D

H_VID1

R382 0_0402_5%~D

H_VID2

R381 0_0402_5%~D

H_VID3

R380 0_0402_5%~D

H_VID4

R379 0_0402_5%~D

H_VID5

R378 0_0402_5%~D

C C

12

12

12

12

12

12

B_VID6

OPEN~D

2

2

1

1

OPEN OPEN OPEN OPEN OPEN OPEN

@

+VCCP

10K_0402_5%~D

10K_0402_5%~D

12

RN1

4 5

B_VID5

OPEN~D

2

2

1

1

@

12

R38

R37

1 8

2 7

3 6

B_VID4

OPEN~D

2

2

1

1

@

B_VID3

OPEN~D

2

2

1

1

@

+1.5VRUN

B_VID2

OPEN~D

2

2

1

1

@

PJP5

2 1

PAD-OPEN 2x2m~D@

PJP3

2 1

PAD-OPEN 2x2m~D

SHORT

B_VID1

OPEN~D

2

2

1

1

@

1

C117

C122

2

0.01U_0402_16V7K~D

VID0 <46>

VID1 <46>

VID2 <46>

VID3 <46>

VID4 <46>

VID5 <46>

H_PSI#<46>

10U_1206_6.3V6M~D

54.9_0603_1%~D@

54.9_0603_1%~D@

1

2

+VCC_CORE

Layout Note:

500 mil max length

+VCCP

B B

Layout close CPU

V_CPU_GTLREF

R_A

12

R201

1K_0603_1%~D

R_B

12

R203

2K_0603_1%~D

12

12

R417

R416

27.4_0603_1%~D

R426

54.9_0603_1%~D

12

12

27.4_0603_1%~D

R427

54.9_0603_1%~D

Resistor placed within

0.5" of CPU pin.Trace

shouldbe at least 25

milesaway from any

other togglingsignal.

V_CPU_GTLREF

CPU_BSEL0<6>

CPU_BSEL1<6>

1 2

1 2

R207

+VCCP

T42 PAD~D

T43 PAD~D

T44 PAD~D

T45 PAD~D

VCCSENSE

VSSSENSE

H_PSI#

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

CPU_BSEL0

CPU_BSEL1

COMP0

COMP1

COMP2

COMP3

JCPUB

AE7

VCCSENSE

AF6

VSSSENSE

F26

VCCA0

B1

VCCA1

N1

VCCA2

AC26

VCCA3

P23

VCCQ0

W4

VCCQ1

D10

VCCP

D12

VCCP

D14

VCCP

D16

VCCP

E11

VCCP

E13

VCCP

E15

VCCP

F10

VCCP

F12

VCCP

F14

VCCP

F16

VCCP

K6

VCCP

L5

VCCP

L21

VCCP

M6

VCCP

M22

VCCP

N5

VCCP

N21

VCCP

P6

VCCP

P22

VCCP

R5

VCCP

R21

VCCP

T6

VCCP

T22

VCCP

U21

VCCP

D6

VCC

D8

VCC

D18

VCC

D20

VCC

D22

VCC

E5

VCC

E7

VCC

E9

VCC

E17

VCC

E19

VCC

E21

VCC

F6

VCC

F8

VCC

F18

VCC

E1

PSI#

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AD26

GTLREF

C16

BSEL0

C14

BSEL1

P25

COMP0

P26

COMP1

AB2

COMP2

AB1

COMP3

B2

RSVD

C3

RSVD

E26

RSVD

AF7

RSVD

AC1

RSVD

AMP_1473129-1_Dothan~D

Dothan

POWER, GROUNG, RESERVED SIGNALS AND NC

A2

VSS

A5

VSS

A8

VSS

A11

VSS

A14

VSS

A17

VSS

A20

VSS

A23

VSS

A26

VSS

B3

VSS

B6

VSS

B9

VSS

B12

VSS

B16

VSS

B19

VSS

B22

VSS

B25

VSS

C1

VSS

C4

VSS

C7

VSS

C10

VSS

C13

VSS

C15

VSS

C18

VSS

C21

VSS

C24

VSS

D2

VSS

D5

VSS

D7

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

D19

VSS

D21

VSS

D23

VSS

D26

VSS

E3

VSS

E6

VSS

E8

VSS

E10

VSS

E12

VSS

E14

VSS

E16

VSS

E18

VSS

E20

VSS

E22

VSS

E25

VSS

F1

VSS

F4

VSS

F5

VSS

F7

VSS

F9

VSS

F11

VSS

F13

VSS

F15

VSS

F17

VSS

F19

VSS

F21

VSS

F24

VSS

G2

VSS

G6

VSS

G22

VSS

G23

VSS

G26

VSS

H3

VSS

H5

VSS

H21

VSS

H25

VSS

J1

VSS

J4

VSS

J6

VSS

J22

VSS

J24

VSS

K2

VSS

K5

VSS

K21

VSS

K23

VSS

K26

VSS

L3

VSS

L6

VSS

L22

VSS

L25

VSS

M1

VSS

+VCC_CORE

JCPUC

F20

VCC

F22

VCC

G5

VCC

G21

VCC

H6

VCC

H22

VCC

J5

VCC

J21

VCC

K22

VCC

U5

VCC

V6

VCC

V22

VCC

W5

VCC

W21

VCC

Y6

VCC

Y22

VCC

AA5

VCC

AA7

VCC

AA9

VCC

AA11

VCC

AA13

VCC

AA15

VCC

AA17

VCC

AA19

VCC

AA21

VCC

AB6

VCC

AB8

VCC

AB10

VCC

AB12

VCC

AB14

VCC

AB16

VCC

AB18

VCC

AB20

VCC

AB22

VCC

AC9

VCC

AC11

VCC

AC13

VCC

AC15

VCC

AC17

VCC

AC19

VCC

AD8

VCC

AD10

VCC

AD12

VCC

AD14

VCC

AD16

VCC

AD18

VCC

AE9

VCC

AE11

VCC

AE13

VCC

AE15

VCC

AE17

VCC

AE19

VCC

AF8

VCC

AF10

VCC

AF12

VCC

AF14

VCC

AF16

VCC

AF18

VCC

M4

VSS

M5

VSS

M21

VSS

M24

VSS

N3

VSS

N6

VSS

N22

VSS

N23

VSS

N26

VSS

P2

VSS

P5

VSS

P21

VSS

P24

VSS

R1

VSS

R4

VSS

R6

VSS

R22

VSS

R25

VSS

T3

VSS

T5

VSS

T21

VSS

T23

VSS

AMP_1473129-1_Dothan~D

Dothan

POWER, GROUND

T26

VSS

U2

VSS

U6

VSS

U22

VSS

U24

VSS

V1

VSS

V4

VSS

V5

VSS

V21

VSS

V25

VSS

W3

VSS

W6

VSS

W22

VSS

W23

VSS

W26

VSS

Y2

VSS

Y5

VSS

Y21

VSS

Y24

VSS

AA1

VSS

AA4

VSS

AA6

VSS

AA8

VSS

AA10

VSS

AA12

VSS

AA14

VSS

AA16

VSS

AA18

VSS

AA20

VSS

AA22

VSS

AA25

VSS

AB3

VSS

AB5

VSS

AB7

VSS

AB9

VSS

AB11

VSS

AB13

VSS

AB15

VSS

AB17

VSS

AB19

VSS

AB21

VSS

AB23

VSS

AB26

VSS

AC2

VSS

AC5

VSS

AC8

VSS

AC10

VSS

AC12

VSS

AC14

VSS

AC16

VSS

AC18

VSS

AC21

VSS

AC24

VSS

AD1

VSS

AD4

VSS

AD7

VSS

AD9

VSS

AD11

VSS

AD13

VSS

AD15

VSS

AD17

VSS

AD19

VSS

AD22

VSS

AD25

VSS

AE3

VSS

AE6

VSS

AE8

VSS

AE10

VSS

AE12

VSS

AE14

VSS

AE16

VSS

AE18

VSS

AE20

VSS

AE23

VSS

AE26

VSS

AF2

VSS

AF5

VSS

AF9

VSS

AF11

VSS

AF13

VSS

AF15

VSS

AF17

VSS

AF19

VSS

AF21

VSS

AF24

VSS

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size DocumentNumber Rev

Date: Sheet of

Compal Electronics, Inc.

Dothan Processor(2/2)

LA-2171

8 50, 12, 2004

1

0.2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

5

4

3

2

1

+VCC_CORE

1

C213

10U_1206_6.3V6M~D

D D

C C

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C463

10U_1206_6.3V6M~D

C165

10U_1206_6.3V6M~D

C214

10U_1206_6.3V6M~D

1

C138

10U_1206_6.3V6M~D

2

1

C464

10U_1206_6.3V6M~D

2

1

C127

10U_1206_6.3V6M~D

2

1

C465

10U_1206_6.3V6M~D

2

1

C128

10U_1206_6.3V6M~D

2

1

C208

10U_1206_6.3V6M~D

2

1

C166

10U_1206_6.3V6M~D

2

1

C209

10U_1206_6.3V6M~D

2

1

C139

10U_1206_6.3V6M~D

2

1

C163

10U_1206_6.3V6M~D

2

1

C215

10U_1206_6.3V6M~D

2

1

C466

10U_1206_6.3V6M~D

2

1

C212

10U_1206_6.3V6M~D

2

1

C168

10U_1206_6.3V6M~D

2

1

C211

10U_1206_6.3V6M~D

2

1

C210

10U_1206_6.3V6M~D

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C167

10U_1206_6.3V6M~D

C443

10U_1206_6.3V6M~D

C144

10U_1206_6.3V6M~D

1

2

1

2

1

2

10uF 1206 X5R -> 85 degree

C526

10U_1206_6.3V6M~D

C532

10U_1206_6.3V6M~D

C441

10U_1206_6.3V6M~D

1

C528

10U_1206_6.3V6M~D

2

1

C527

10U_1206_6.3V6M~D

2

1

C531

10U_1206_6.3V6M~D

2

X7R

High Frequence Decoupling

1

C530

10U_1206_6.3V6M~D

2

1

C440

10U_1206_6.3V6M~D

2

1

C525

10U_1206_6.3V6M~D

2

1

C529

10U_1206_6.3V6M~D

2

1

C207

10U_1206_6.3V6M~D

2

1

C444

10U_1206_6.3V6M~D

2

Near VCORE regulator.

+VCC_CORE

220U_D2_2VM~D

1

C415

B B

+

2

220U_D2_2VM~D

1

C416

+

2

NOTE:Place close to CPU south side

@

220U_D2_2VM~D@

220U_D2_2VM~D

1

1

C408

C407

+

+

2

2

220U_D2_2VM~D

1

1

C665

C85

+

+

2

2

220U_D2_2VM~D

ESR <= 3m ohm

Capacitor > 880 uF

+VCCP

1

+

C160

150U _D2_6.3VM~D

2

A A

1

C446

0.1U_0402_10V7K~D

2

1

C447

0.1U_0402_10V7K~D

2

1

C448

0.1U_0402_10V7K~D

2

1

C457

0.1U_0402_10V7K~D

2

1

C452

0.1U_0402_10V7K~D

2

1

C437

0.1U_0402_10V7K~D

2

1

C436

0.1U_0402_10V7K~D

2

1

C432

0.1U_0402_10V7K~D

2

1

C435

0.1U_0402_10V7K~D

2

1

C445

0.1U_0402_10V7K~D

2

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size DocumentNumber Rev

Date: Sheet of

Compal Electronics, Inc.

Dothan Bypass

LA-2171

9 50, 12, 2004

1

0.2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

5

4

3

2

1

DMI_TXN0

DMI_TXN0<22>

DMI_TXN1

DMI_TXN1<22>

D D

C C

LayoutGuide will show

these signals routed

differentially.

B B

A A

H_A#[3..31]<7>

T1 PAD~D

H_REQ#[0..4]<7>

H_ADSTB#0<7>

H_ADSTB#1<7>

CLK_MCH_BCLK#<6>

CLK_MCH_BCLK<6>

H_DSTBN#[0..3]<7>

H_DSTBP#[0..3]<7>

H_DINV#0<7>

H_DINV#1<7>

H_DINV#2<7>

H_DINV#3<7>

H_RESET#<7>

H_ADS#<7>

H_TRDY#<7>

H_DPWR#<7>

H_DRDY#<7>

H_DEFER#<7>

T3 PAD~D

H_HITM#<7>

H_HIT#<7>

H_LOCK#<7>

H_BR0#<7>

H_BNR#<7>

H_BPRI#<7>

H_DBSY#<7>

H_RS#[0..2]<7>

H_CPUSLP#<7,21>

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

TP_H_PCREQ#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_RESET#

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

TP_H_EDRDY#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_R_CPUSLP#

H_RS#0

H_RS#1

H_RS#2

H_CPUSLP# H_R_CPUSLP#

Note:

"Do not install R97 for Dothan-A,

Install R97 for Dothan-B"

U15A

G9

C9

E9

B7

A10

F9

D8

B10

E10

G10

D9

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

A11

A7

D7

B8

C7

A8

B9

E13

AB1

AB2

G4

K1

R3

V3

G5

K2

R2

W4

H8

K3

T7

U5

H10

F8

B5

G6

F7

E6

F6

D6

D4

B3

E7

A5

D5

C6

G8

A4

C5

B4

ALVISO_BGA1257~D

R97

0_0402_5%~D@

1 2

HA3#

Alviso

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HPCREQ#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HADSTB#0

HADSTB#1

HCLKN

HCLKIN

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HCPURST#

HADS#

HTRDY#

HDPWR#

HDRDY#

HDEFER#

HEDRDY#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HSLPCPU#

HRS0#

HRS1#

HRS2#

HOST

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HVREF

HXRCOMP

HXSCOMP

HYRCOMP

HYSCOMP

HXSWING

HYSWING

H_D#0

E4

H_D#1

E1

H_D#2

F4

H_D#3

H7

H_D#4

E2

H_D#5

F1

H_D#6

E3

H_D#7

D3

H_D#8

K7

H_D#9

F2

H_D#10

J7

H_D#11

J8

H_D#12

H6

H_D#13

F3

H_D#14

K8

H_D#15

H5

H_D#16

H1

H_D#17

H2

H_D#18

K5

H_D#19

K6

H_D#20

J4

H_D#21

G3

H_D#22

H3

H_D#23

J1

H_D#24

L5

H_D#25

K4

H_D#26

J5

H_D#27

P7

H_D#28

L7

H_D#29

J3

H_D#30

P5

H_D#31

L3

H_D#32

U7

H_D#33

V6

H_D#34

R6

H_D#35

R5

H_D#36

P3

H_D#37

T8

H_D#38

R7

H_D#39

R8

H_D#40

U8

H_D#41

R4

H_D#42

T4

H_D#43

T5

H_D#44

R1

H_D#45

T3

H_D#46

V8

H_D#47

U6

H_D#48

W6

H_D#49

U3

H_D#50

V5

H_D#51

W8

H_D#52

W7

H_D#53

U2

H_D#54

U1

H_D#55

Y5

H_D#56

Y2

H_D#57

V4

H_D#58

Y7

H_D#59

W1

H_D#60

W3

H_D#61

Y3

H_D#62

Y6

H_D#63

W2

H_VREF

J11

H_XRCOMP

C1

H_XSCOMP

C2

H_YRCOMP

T1

H_YSCOMP

L1

H_SWNG0

D1

H_SWNG1

P1

R180

12

24.9_0603_1%~D

H_D#[0..63] <7>

H_SWNG1

C146

H_SWNG0

C112

0.1U_0402_16V4Z~D

+VCCP

12

R121

54.9_0603_1%~D

12

R125

24.9_0603_1%~D

+VCCP

12

R157

221_0603_1%~D

12

1

R176

2

100_0603_1%~D

0.1U_0402_16V4Z~D

+VCCP

12

R131

221_0603_1%~D

12

1

R132

2

100_0603_1%~D

12

R156

54.9_0603_1%~D

C124

0.1U_0402_10V7K~D

1

2

Layout Guide

will show these

signalsrouted

differentially.

+1.8VSUS

+VCCP

12

R143

100_0603_1%~D

12

R142

200_0603_1%~D

M_CLK_DDR0<17>

M_CLK_DDR1<17>

M_CLK_DDR3<16>

M_CLK_DDR4<16>

M_CLK_DDR#0<17>

M_CLK_DDR#1<17>

M_CLK_DDR#3<16>

M_CLK_DDR#4<16>

DDR_CKE0_DIMMA<17>

DDR_CKE1_DIMMA<17>

DDR_CKE2_DIMMB<16>

DDR_CKE3_DIMMB<16>

DDR_CS0_DIMMA#<17>

DDR_CS1_DIMMA#<17>

DDR_CS2_DIMMB#<16>

DDR_CS3_DIMMB#<16>

R458 80.6_0603_1%~D

1 2

V_DDR_MCH_REF<16,17,45>

12

R457

80.6_0603_1%~D

Layout Note:

Rote as short

as possible

12

12

R455

R456

40.2_0603_1%~D

40.2_0603_1%~D

DMI_TXN2<22>

DMI_TXN3<22>

DMI_TXP0<22>

DMI_TXP1<22>

DMI_TXP2<22>

DMI_TXP3<22>

DMI_RXN0<22>

DMI_RXN1<22>

DMI_RXN2<22>

DMI_RXN3<22>

DMI_RXP0<22>

DMI_RXP1<22>

DMI_RXP2<22>

DMI_RXP3<22>

M_OCDOCMP0

M_OCDOCMP1

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_ODT0<17>

M_ODT1<17>

M_ODT2<16>

M_ODT3<16>

C490

0.1U_0402_16V4Z~D

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR3

M_CLK_DDR4

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#3

M_CLK_DDR#4

M_OCDOCMP0

M_OCDOCMP1

M_ODT0

M_ODT1

M_ODT2

M_ODT3

SMRCOMPN

SMRCOMPP

1

C484

2

0.1U_0402_16V4Z~D

U15B

AA31

DMIRXN0

AB35

DMIRXN1

AC31

DMIRXN2

AD35

DMIRXN3

Y31

DMIRXP0

AA35

DMIRXP1

AB31

DMIRXP2

AC35

DMIRXP3

AA33

DMITXN0

AB37

DMITXN1

AC33

DMITXN2

AD37

DMITXN3

Y33

DMITXP0

AA37

DMITXP1

AB33

DMITXP2

AC37

DMITXP3

AM33

SM_CK0

AL1

SM_CK1

AE11

SM_CK2

AJ34

SM_CK3

AF6

SM_CK4

AC10

SM_CK5

AN33

SM_CK0#

AK1

SM_CK1#

AE10

SM_CK2#

AJ33

SM_CK3#

AF5

SM_CK4#

AD10

SM_CK5#

AP21

SM_CKE0

AM21

SM_CKE1

AH21

SM_CKE2

AK21

SM_CKE3

AN16

SM_CS0#

AM14

SM_CS1#

AH15

SM_CS2#

AG16

SM_CS3#

AF22

SM_OCDCOMP0

AF16

SM_OCDCOMP1

AP14

SM_ODT0

AL15

SM_ODT1

AM11

SM_ODT2

AN10

SM_ODT3

AK10

SMRCOMPN

AK11

SMRCOMPP

AF37

SMVREF0

AD1

SMVREF1

AE27

SMXSLEWIN

AE28

SMXSLEWOUT

AF9

1

2

SMYSLEWIN

AF10

SMYSLEWOUT

ALVISO_BGA1257~D

DMIDDR MUXING

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

CFG/RSVD

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

PM

RSTIN#

DREF_CLKN

DREF_CLKP

DREF_SSCLKP

DREF_SSCLKN

CLK

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC

NC9

NC10

NC11

PM_EXTTS#0

PM_EXTTS#1

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

D37

C37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

CFG0

MCH_CLKSEL1

MCH_CLKSEL0

T19PAD~D

T20PAD~D

CFG5

CFG6

CFG7

CFG9

CFG12

CFG13

CFG16

CFG18

CFG19

THERMTRIP_MCH#

PM_EXTTS#0

PM_EXTTS#1

THERMTRIP_MCH#

PLTRST_R#

+1.5VRUN

R413

10K_0402_5%~D

R398

10K_0402_5%~D

CFG0 <12>

MCH_CLKSEL1 <6>

MCH_CLKSEL0 <6>

CFG5 <12>

CFG6 <12>

CFG7 <12>

CFG9 <12>

CFG12 <12>

CFG13 <12>

CFG16 <12>

CFG18 <12>

CFG19 <12>

R114

75_0402_5%~D

1 2

PM_BMBUSY# <22>

THERMTRIP_MCH# <15>

IMVP_PWRGD <22,39,46>

1 2

R200 100_0603_1%~D

+2.5VRUN

12

12

+VCCP

PLTRST_MCH# <20>

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

DELL CONFIDENTIAL/PROPRIETARY

Title

Size DocumentNumber Rev

Date: Sheet of

Compal Electronics, Inc.

Alviso(1 of 5)

LA-2171

10 50, 12, 2004

1

0.2

5

D D

4

3

2

1

DDR_A_BS#0<17>

DDR_A_BS#1<17>

DDR_A_BS#2<17>

DDR_A_DM[0..7]<17>

DDR_A_DQS[0..7]<17>

This Symbol assame

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

C C

B B

DDR_A_DQS#[0..7]<17>

DDR_A_MA[0..13]<17>

DDR_A_CAS#<17>

DDR_A_RAS#<17>

DDR_A_WE#<17>

DDR_A_BS#0

DDR_A_BS#1

DDR_A_BS#2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5 DDR_A_D18

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_CAS#

DDR_A_RAS#

TP_MA_RCVENIN#

DDR_A_WE#

U15C

AK15

SA_BS0#

AK16

SA_BS1#

AL21

SA_BS2#

AJ37

SA_DM0

AP35

SA_DM1

AL29

SA_DM2

AP24

SA_DM3

AP9

SA_DM4

AP4

SA_DM5

AJ2

SA_DM6

AD3

SA_DM7

AK36

SA_DQS0

AP33

SA_DQS1

AN29

SA_DQS2

AP23

SA_DQS3

AM8

SA_DQS4

AM4

SA_DQS5

AJ1

SA_DQS6

AE5

SA_DQS7

AK35

SA_DQS0#

AP34

SA_DQS1#

AN30

SA_DQS2#

AN23

SA_DQS3#

AN8

SA_DQS4#

AM5

SA_DQS5#

AH1

SA_DQS6#

AE4

SA_DQS7#

AL17

SA_MA0

AP17

SA_MA1

AP18

SA_MA2

AM17

SA_MA3

AN18

SA_MA4

AM18

SA_MA5

AL19

SA_MA6

AP20

SA_MA7

AM19

SA_MA8

AL20

SA_MA9

AM16

SA_MA10

AN20

SA_MA11

AM20

SA_MA12

AM15

SA_MA13

AN15

SA_CAS#

AP16

SA_RAS#

AF29

SA_RCVENIN#

AF28

SA_RCVENOUT#

AP15

SA_WE#

ALVISO_BGA1257~D

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

DDR MEMORY SYSTEM A

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

This Symbol assame

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

DDR_B_BS#0<16>

DDR_B_BS#1<16>

DDR_B_BS#2<16>

DDR_B_DM[0..7]<16>

DDR_B_DQS[0..7]<16>

DDR_B_DQS#[0..7]<16>

DDR_B_MA[0..13]<16>

DDR_B_CAS#<16>

T22 PAD~DT25 PAD~D

T23 PAD~DT24 PAD~D

DDR_B_RAS#<16>

DDR_B_WE#<16>

DDR_B_BS#0

DDR_B_BS#1 DDR_B_D1

DDR_B_BS#2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_CAS#

DDR_B_RAS#

TP_MB_RCVENIN#

TP_MB_RCVENOUT#TP_MA_RCVENOUT#

DDR_B_WE#

U15D

AJ15

SB_BS0#

AG17

SB_BS1#

AG21

SB_BS2#

AF32

SD_DM0

AK34

SD_DM1

AK27

SD_DM2

AK24

SD_DM3

AJ10

SD_DM4

AK5

SD_DM5

AE7

SD_DM6

AB7

SD_DM7

AF34

SB_DQS0

AK32

SB_DQS1

AJ28

SB_DQS2

AK23

SB_DQS3

AM10

SB_DQS4

AH6

SB_DQS5

AF8

SB_DQS6

AB4

SB_DQS7

AF35

SB_DQS0#

AK33

SB_DQS1#

AK28

SB_DQS2#

AJ23

SB_DQS3#

AL10

SB_DQS4#

AH7

SB_DQS5#

AF7

SB_DQS6#

AB5

SB_DQS7#

AH17

SB_MA0

AK17

SB_MA1

AH18

SB_MA2

AJ18

SB_MA3

AK18

SB_MA4

AJ19

SB_MA5

AK19

SB_MA6

AH19

SB_MA7

AJ20

SB_MA8

AH20

SB_MA9

AJ16

SB_MA10

AG18

SB_MA11

AG20

SB_MA12

AG15

SB_MA13

AH14

SB_CAS#

AK14

SB_RAS#

AF15

SB_RCVENIN#

AF14

SB_RCVENOUT#

AH16

SB_WE#

ALVISO_BGA1257~D

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

DDR SYSTEM MEMORY B

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AJ9

AK9

AJ7

AK6

AJ4

AH5

AK8

AJ8

AJ5

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_D0

AE31

SBDQ0

AE32

DDR_B_D[0..63] <16>DDR_A_D[0..63] <17>

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size DocumentNumber Rev

Date: Sheet of

Compal Electronics, Inc.

Alviso(2 of 5)

LA-2171

11 50, 12, 2004

1

0.2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

5

4

3

2

1

U15G

H24

SDVOCTRL_DATA

H25

SDVOCTRL_CLK

D D

C C

B B

CLK_MCH_3GPLL#<6>

CLK_MCH_3GPLL<6>

+VCCP

AB29

GCLKN

AC29

GCLKP

A15

TVDAC_A

C16

TVDAC_B

A17

TVDAC_C

J18

TV_REFSET

B15

TV_IRTNA

B16

TV_IRTNB

B17

TV_IRTNC

E24

DDCCLK

E23

DDCDATA

E21

BLUE

D21

BLUE#

C20

GREEN

B20

GREEN#

A19

RED

B19

RED#

H21

VSYNC

G21

HSYNC

J20

REFSET

E25

LBKLT_CTL

F25

LBKLT_EN

C23

LCTLA_CLK

C22

LCTLB_DATA

F23

LDDC_CLK

F22

LDDC_DATA

F26

LVDD_EN

C33

LIBG

C31

LVBG

F28

LVREFH

F27

LVREFL

B30

LACLKN

B29

LACLKP

C25

LBCLKN

C24

LBCLKP

B34

LADATAN0

B33

LADATAN1

B32

LADATAN2

A34

LADATAP0

A33

LADATAP1

B31

LADATAP2

C29

LBDATAN0

D28

LBDATAN1

C27

LBDATAN2

C28

LBDATAP0

D27

LBDATAP1

C26

LBDATAP2

ALVISO_BGA1257~D

EXP_COMPI

EXP_ICOMPO

EXP_RXN0

EXP_RXN1

MISC

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

TVVGALVDS

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

PCI - EXPRESS GRAPHICS

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

PEGCOMP

D36

D34

PEG_RXN0

E30

PEG_RXN1

F34

PEG_RXN2

G30

PEG_RXN3

H34

PEG_RXN4

J30

PEG_RXN5

K34

PEG_RXN6

L30

PEG_RXN7

M34

PEG_RXN8

N30

PEG_RXN9

P34

PEG_RXN10

R30

PEG_RXN11

T34

PEG_RXN12

U30

PEG_RXN13

V34

PEG_RXN14

W30

PEG_RXN15

Y34

PEG_RXP0

D30

PEG_RXP1

E34

PEG_RXP2

F30

PEG_RXP3

G34

PEG_RXP4

H30

PEG_RXP5

J34

PEG_RXP6

K30

PEG_RXP7

L34

PEG_RXP8

M30

PEG_RXP9

N34

PEG_RXP10

P30

PEG_RXP11

R34

PEG_RXP12

T30

PEG_RXP13

U34

PEG_RXP14

V30

PEG_RXP15

W34

PEG_TXN0

E32

PEG_TXN1

F36

PEG_TXN2

G32

PEG_TXN3

H36

PEG_TXN4

J32

PEG_TXN5

K36

PEG_TXN6

L32

PEG_TXN7

M36

PEG_TXN8

N32

PEG_TXN9

P36

PEG_TXN10

R32

PEG_TXN11

T36

PEG_TXN12

U32

PEG_TXN13

V36

PEG_TXN14

W32

PEG_TXN15

Y36

PEG_TXP0

D32

PEG_TXP1

E36

PEG_TXP2

F32

PEG_TXP3

G36

PEG_TXP4

H32

PEG_TXP5

J36

PEG_TXP6

K32

PEG_TXP7

L36

PEG_TXP8

M32

PEG_TXP9

N36

PEG_TXP10

P32

PEG_TXP11

R36

PEG_TXP12

T32

PEG_TXP13

U36

PEG_TXP14

V32

PEG_TXP15

W36

R129

24.9_0603_1%~D

1 2

PEG_RXN[0..15]

PEG_RXP[0..15]

PEG_TXN[0..15]

PEG_TXP[0..15]

+1.5VRUN_PCIE

PEG_RXN[0..15] <18>

PEG_RXP[0..15] <18>

This Symbol assame

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

PEG_TXN[0..15] <18>

PEG_TXP[0..15] <18>

CFG[2:0]

CFG5

CFG6

CFG7

CFG9

CFG[13:12]

CFG16

(FSB Dynamic

ODT)

CFG18

(VCC Select)

CFG19

(VTT Select)

Refer tosheet 6 for FSB

frequencyselect

Low = DMIx 2

High =DMI x 4

Low = DDR-II

High =DDR-I

*

*

Low = DT/Transportable CPU

High =Mobile CPU

Low =Reverse Lane

High =Normal Operation

00 = Reserved

01 = XOR Mode Enabled

10 = All ZMode Enabled

11 = Normal Operation(Default)

*

Low = Disabled

High =Enabled

Low = 1.05V (Default)

High =1.5V

*

*

Low = 1.05V (Default)

High =1.2V

+VCCP

R415 10K_0402_5%~D

CFG0<10>

R408 2.2K_0402_5%~D@

CFG5<10>

R404 2.2K_0402_5%~D

CFG6<10>

R108 2.2K_0402_5%~D@

CFG7<10>

R401 2.2K_0402_5%~D@

CFG9<10>

R402 2.2K_0402_5%~D@

CFG12<10>

R411 2.2K_0402_5%~D@

CFG13<10>

R412 2.2K_0402_5%~D@

*

CFG16<10>

12

1 2

1 2

1 2

1 2

1 2

1 2

1 2

CFG[17:3] have internal pull-up

*

+2.5VRUN

R406 1K_0402_5%~D@

CFG18<10>

CFG19<10>

*

1 2

1 2

R407 1K_0402_5%~D@

CFG[19:18] have internal pull-down

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size DocumentNumber Rev

Date: Sheet of

Compal Electronics, Inc.

Alviso(3 of 5)

LA-2171

12 50, 12, 2004

1

0.2

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

5

4

3

2

1

U15F

K13

VTT0

J13

VTT1

K12

VTT2

W11

VTT3

V11

VTT4

U11

VTT5

T11

VTT6

R11

VTT7

P11

POWER

VTT8

N11

VTT9

M11

1

2

C449

1

2

0.22U_0603_10V7K~D

VTT10

L11

VTT11

K11

VTT12

W10

VTT13

V10

VTT14

U10

VTT15

T10

VTT16

R10

VTT17

P10

VTT18

N10

VTT19

M10

VTT20

K10

VTT21

J10

VTT22

Y9

VTT23

W9

VTT24

U9

VTT25

R9

VTT26

P9

VTT27

N9

VTT28

M9

VTT29

L9

VTT30

J9

VTT31

N8

VTT32

M8

VTT33

N7

VTT34

M7

VTT35

N6

VTT36

M6

VTT37

A6

VTT38

N5

VTT39

M5

VTT40

N4

VTT41

M4

VTT42

N3

VTT43

M3

VTT44

N2

VTT45

M2

VTT46

B2

VTT47

V1

VTT48

N1

VTT49

M1

VTT50

G1

VTT51

C118

0.22U_0603_10V7K~D

ALVISO_BGA1257~D

D D

+VCCP

1

C453

C460

2

2.2U_0805_10V6K~D

4.7U_0805_6.3V6K~D

1

C422

C C

B B

2

0.47U_0603_16V7K~D

1

1

C423

2

2

0.47U_0603_16V7K~D

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

V1.8_DDR_CAP1

AM37

V1.8_DDR_CAP2

AH37

V1.8_DDR_CAP5

AP29

AD28

AD27

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

AG26

AF26

AE26

AP25

AN25

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

AE15

AE14

AP13

AN13

AM13

Note: Place near chip.

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AP12

AN12

AM12

AL12

AK12

AJ12

AH12

AG12

AF12

AE12

AD11

AC11

AB11

AB10

AB9

V1.8_DDR_CAP6

AP8

V1.8_DDR_CAP4

AM1

V1.8_DDR_CAP3

AE1

C639

V1.8_DDR_CAP1

V1.8_DDR_CAP2

V1.8_DDR_CAP5

Note : AllVCCSM pin

shorted internally.

V1.8_DDR_CAP6

V1.8_DDR_CAP4

V1.8_DDR_CAP3

C495

+1.8VSUS

10U_1206_6.3V6M~D

10U_1206_6.3V6M~D

C233

C232

1

2

C238

1

1

2

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

C641

C640

2

1

2

1

2

1

2

C523

0.1U_0402_10V7K~D

C513

330U_D2E_2.5VM~D@

1

+

2

0.1U_0402_16V4Z~D

C642

1

C504

2

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

1

2

+1.5VRUN_DPLLA

+1.5VRUN_DPLLB

+1.5VRUN_HPLL

+1.5VRUN_MPLL

0.1U_0402_16V4Z~D

1

2

W=20 mils

+VCCP

1

C515

2

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

C519

1

2

+1.5VRUN

+1.8VSUS

0.1U_0402_16V4Z~D

1

1

C644

C643

2

2

0.1U_0402_16V4Z~D

U15E

T29

VCC0

R29

VCC1

N29

VCC2

M29

VCC3

K29

VCC4

J29

VCC5

V28

VCC6

U28

VCC7

T28

VCC8

R28

VCC9

P28

VCC10

N28

VCC11

M28

VCC12

L28

VCC13

K28

VCC14

J28

VCC15

H28

VCC16

G28

VCC17

V27

VCC18

U27

VCC19

T27

VCC20

R27

VCC21

P27

VCC22

N27

VCC23

M27

VCC24

L27

VCC25

K27

VCC26

J27

VCC27

H27

VCC28

K26

VCC29

H26

VCC30

K25

VCC31

J25

VCC32

K24

VCC33

K23

VCC34

K22

VCC35

K21

VCC36

W20

VCC37

U20

VCC38

T20

VCC39

K20

VCC40

V19

VCC41

U19

VCC42

K19

VCC43

W18

VCC44

V18

VCC45

T18

VCC46

K18

VCC47

K17

VCC48

AC2

VCCD_HMPLL1

AC1

VCCD_HMPLL2

B23

VCCA_DPLLA

C35

VCCA_DPLLB

AA1

VCCA_HPLL

AA2

VCCA_MPLL

ALVISO_BGA1257~D

POWER