Dell 5470 Schematics

5

4

3

2

1

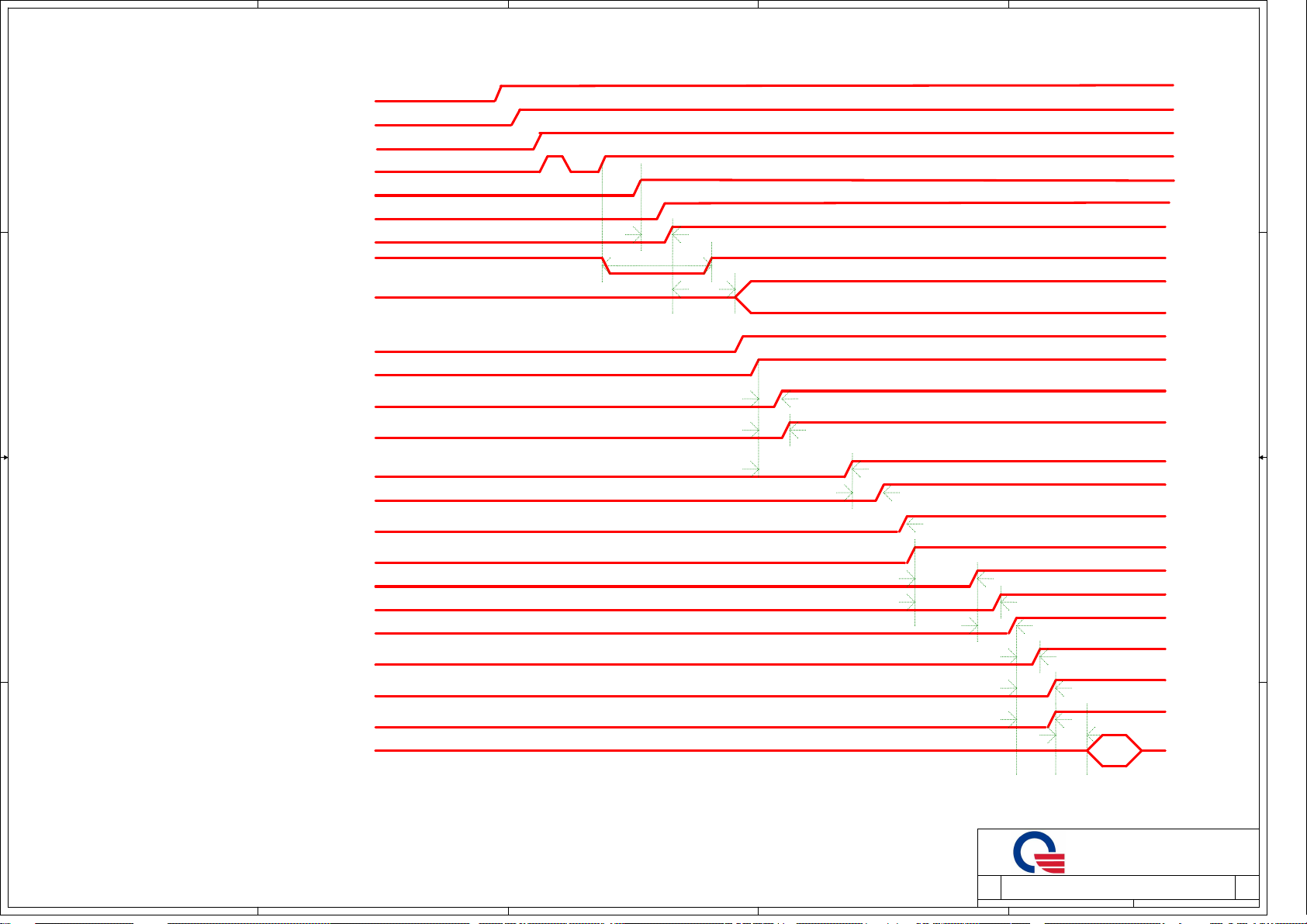

PAGE 34

PAGE 35

PAGE 36

PAGE 37

PAGE 38/39

PAGE 40/41

PAGE 42/43

PAGE 44

JW8

JW8

JW8

01

of

of

of

3A

3A

3A

JW8 DIS (14") Super Ultra

D D

Channel A

DDR3 On Board

Channel B

DDR3 SO-DIMM2

Maxima 4GB

RVS

C C

SATA - 1st HDD

Package :

Power :

mSATA - 2nd HDD

Package :

Power :

B B

System BIOS

SPI ROM

EC SPI ROM

2M

PAGE 11

4M

PAGE 32

Keyboard

Touch Pad

PAGE 25

PAGE 25

FAN1/2 Control

PAGE 25

A A

5

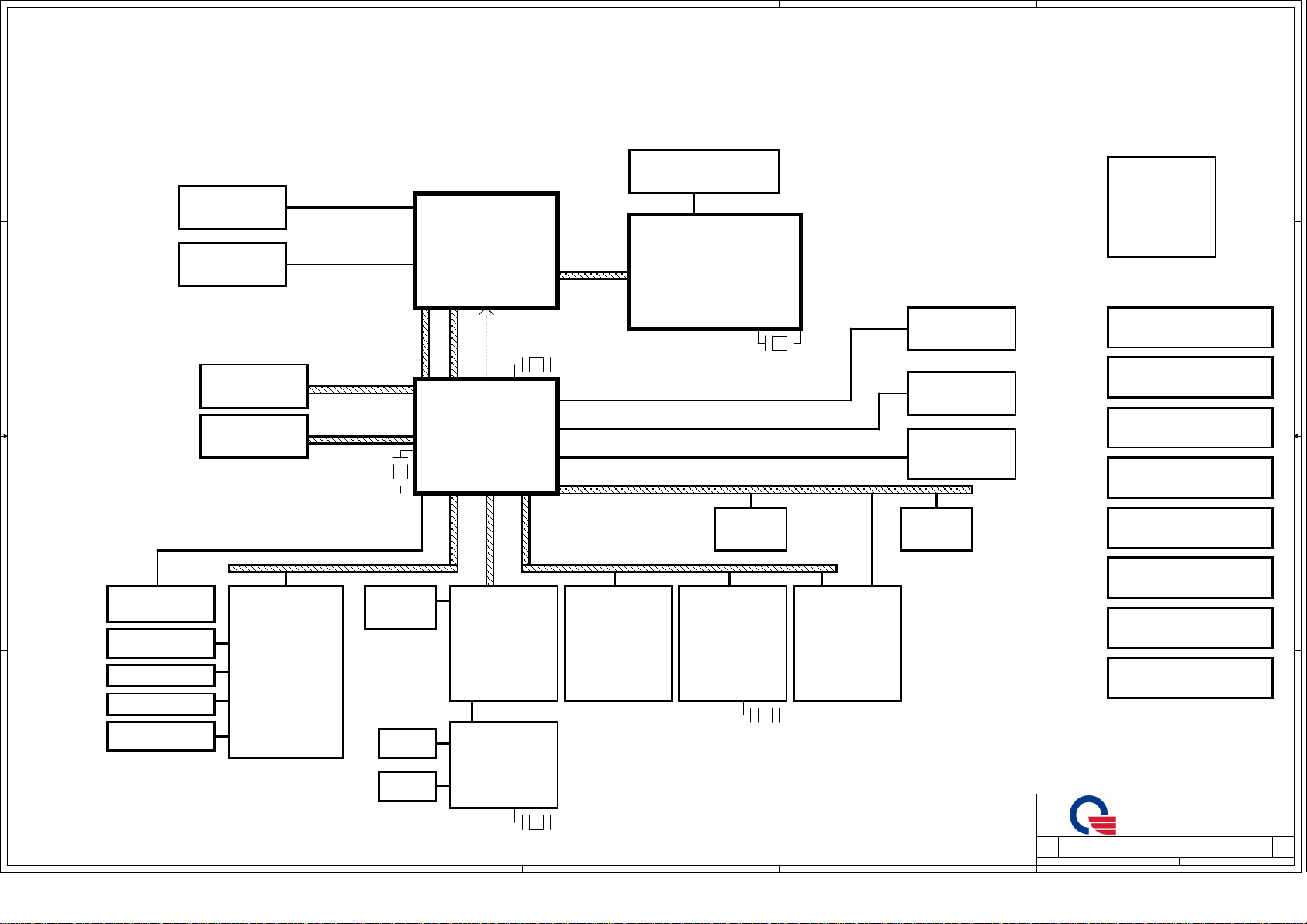

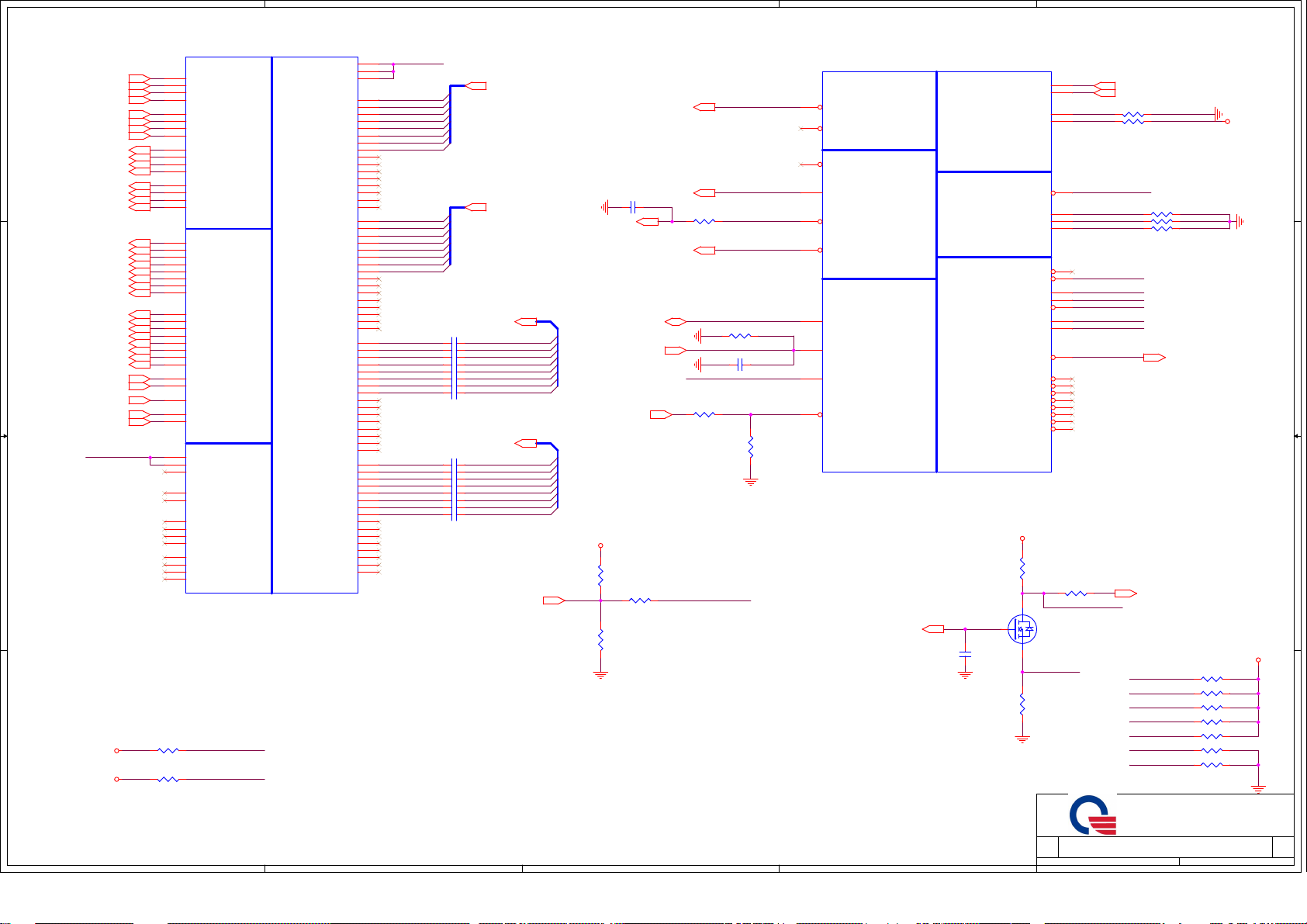

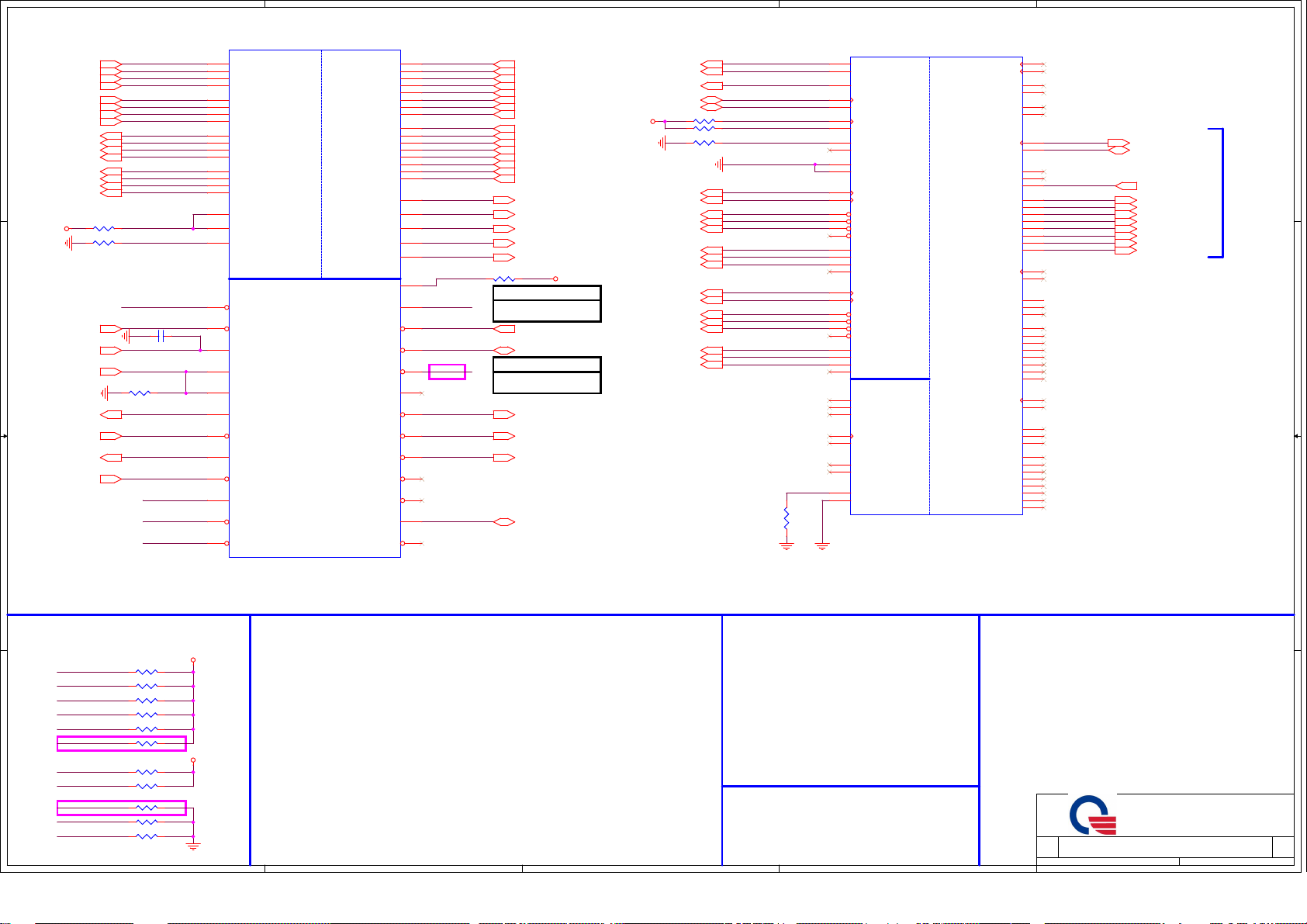

Intel Chief River Platform Block Diagram

VRAM DDR3 x 4

DDR3 1333/1600 MT/s

PAGE 16~17

DDR3 1333/1600 MT/s

PAGE 18

PAGE 31

PAGE 31

SPI Interface

LPC Interface

IT8518E/HX

Embedded Controller

Power :

Package : LQFP128

Size : 16 x 16 mm

PAGE 32

SATA0 6GB/s

SATA1 6GB/s

Green CLK

25MHz

PAGE 21

DMI x 4

Combo Jack

iPHONE type

PAGE 26

DMIC1

PAGE 33

DMIC2

PAGE 33

4

Intel Ivy Bridge

Processor : Daul Core

Power : 35/17 Watt

Package : BGA1023

Size : 31 x 24 mm

PAGE 6~9

Green CLK

32.768KHz

FDI x 8

PAGE 21

BCLK 100MHz

Intel Panther Point

Platform Controller Hub

Power : 4.1 Watt

Package : FCBGA989

Size : 25 x 25 mm

HM76

HM77

PAGE 10~15

Azalia

Realtek

ALC290Q-GR

Power :

Package : QFN48

Size : 7 x 7 mm

PAGE 26

I2S Interface

Audience

eS305BQ

Power :

Package : LQPF48

Size : 7 x 7 mm

PAGE 33

Green CLK

12.288MHz

PAGE 21

PCI-E Gen3

x 8 Lane

LVDS Interface

HDMI Interface

USB3.0 Interface

USB2.0 Interface

PCIE Gen 1 x 1 Lane

RTS5229-GR

Card Reader

Power :

Package : LQPF48

Size : 7 x 7 mm

Max 1GB

Nvidia N13P-GB2 (64bit)

Power : 27.5 Watt

Package : FCBGA595

Size : 23 x 23 mm

DP PortB

USB 3.0 Port1/2/4(USB 2.0 Port0/1/3)

Atheros

AR8161-BL3A-R

LAN Controller

Power :

Package : OFN48

Size : 6 x 6 mm

PAGE 28

3

PAGE 23

PAGE 19~22

Camera

Power :

Package :

PAGE 27

Green CLK

25MHz

PAGE 21

27MHz

PAGE 17

Port2

Port1Port2Port3

Halt Mini Card

WLAN / BT Combo

PAGE 30

Port10

Touch Screen

Power :

Package :

2

LVDS Conn (14")

HDMI Conn

USB3.0 Port x 3

Support USB Charger

IC : SLG55583AVTR

PAGE 33PAGE 33

Port12

PAGE 24

PAGE 24

PAGE 29

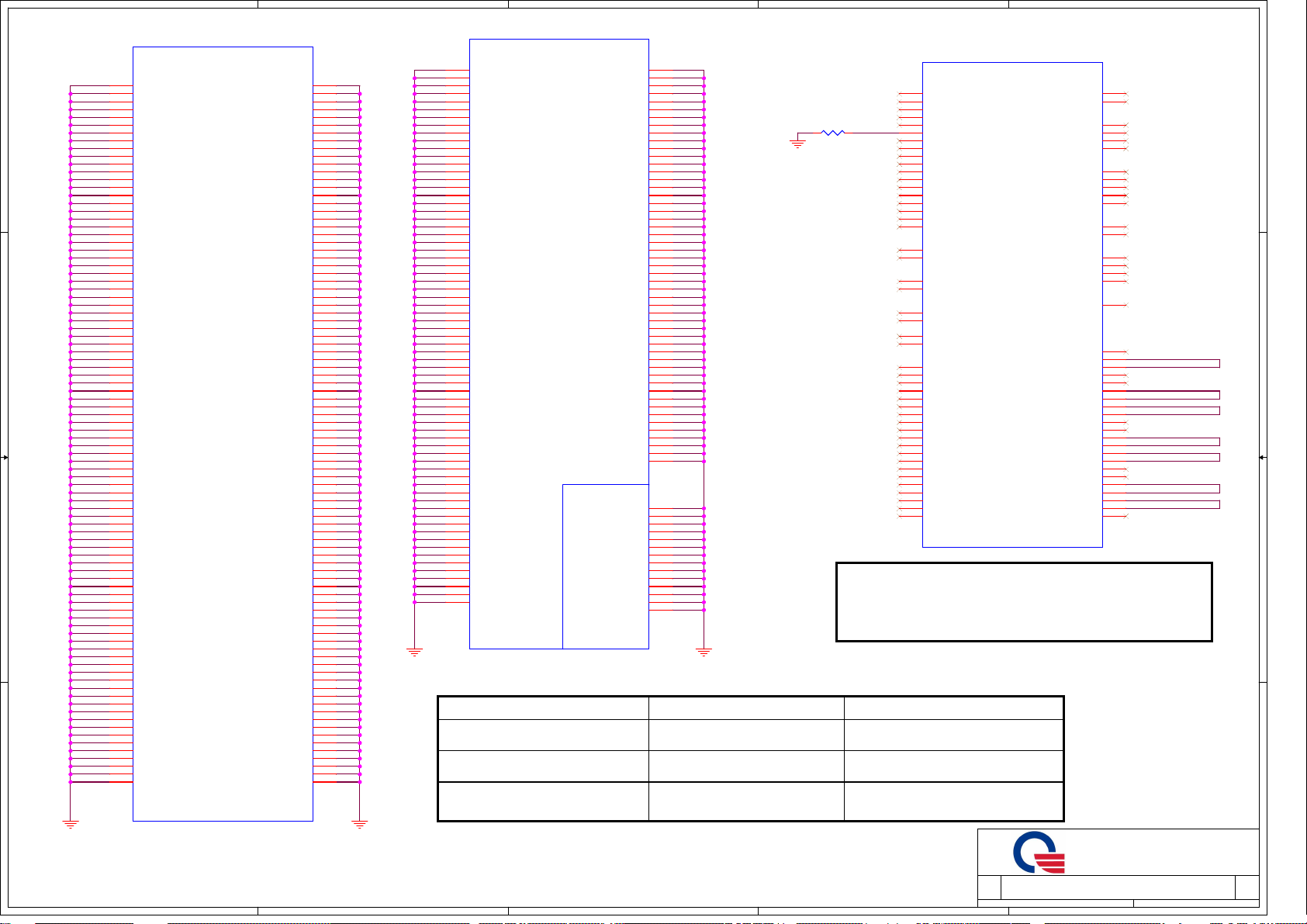

PCB 6L STACK UP

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1(High)

LAYER 4 : IN2(Low)

LAYER 5 : SVCC

LAYER 6 : BOT

Power Source

OZ8681

System Charger Power (+BATCHG)

RT8223P

System Power (+3VS5/+5VS5)

RT8207

System Memory Power (+1.5VSUS/

+0.75V_DDR_VTT/DDR_VTTREF)

G978F1

Processor Power (+VCCSA)

RT8240/G5173R4

PCH Power (+1.05V/+1.8V)

NCP3218G

DGPU Power (+VGACORE/+3V_GFX/

+1.5V_GFX/+1.05V_GFX)

NCP6132

Processor Power (+VCC_CORE/

+VCC_GFX)

SLG55448V

System Discharger Power

(+3V/+5V/+3VLANVCC)

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Friday, November 02, 2012 01 46

Friday, November 02, 2012 01 46

Friday, November 02, 2012 01 46

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT :

Block Diagram

Block Diagram

Block Diagram

1

1

2

3

4

5

6

7

8

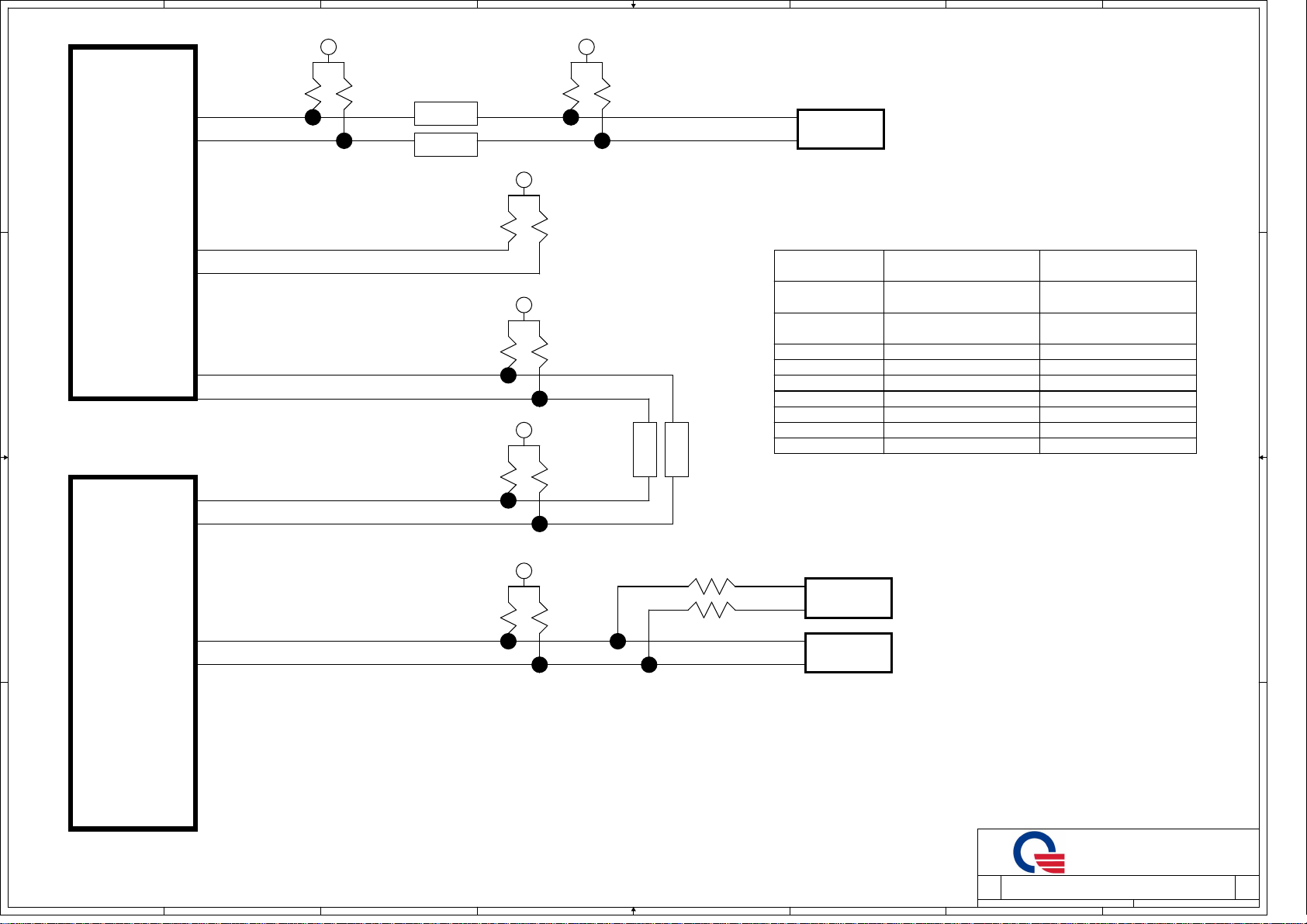

+3VS5

+3VS5

02

2.2K2.2K

H14

A A

SMB_PCH_CLK

C9

SMB_PCH_DAT

+3V

N-MOSFET

N-MOSFET

+3V

+3VS5

PCH

C8

SMB_ME0_CLK

G12

SMB_ME0_DAT

2.2K

2.2K

+3VS5

B B

E14

SMB_ME1_CLK

M16

SMB_ME1_DAT

2.2K2.2K

+3V

10K10K

MBDATA2116

MBCLK2

115

4.7K4.7K

SMB_RUN_CLK

SMB_RUN_DAT

+3V

N-MOS

20

30

JDIM1

Function

DDR3 Module

Charge IC

Battery

+3V

N-MOS

A0

OZ8681NL

Battery

SMBus AddressIC

A0hJDIM1

0b0001001x (0x12h)

16h

+3VPCU

C C

10K10K

SIO

ITE8518E

D D

1

110

MBCLK

111 MBDATA

2

3

4

330

330

5

6

Battery

10

11

Charger

5

16h

12

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, November 02, 2012 02 46

Date: Sheet of

Friday, November 02, 2012 02 46

Date: Sheet of

6

Friday, November 02, 2012 02 46

7

PROJECT :

SMB

SMB

SMB

JW8

JW8

JW8

3A

3A

3A

8

1

2

3

4

5

6

7

8

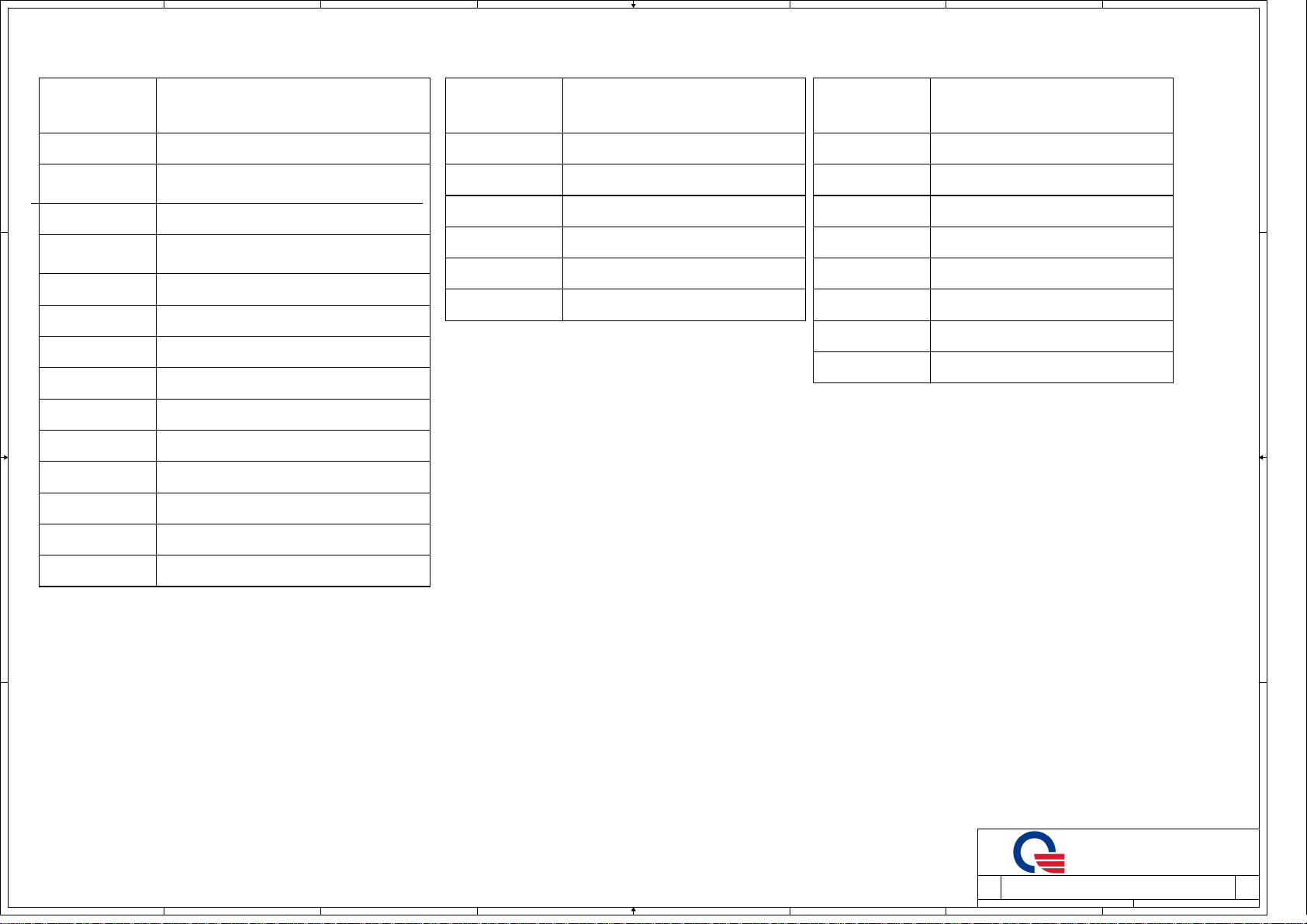

03

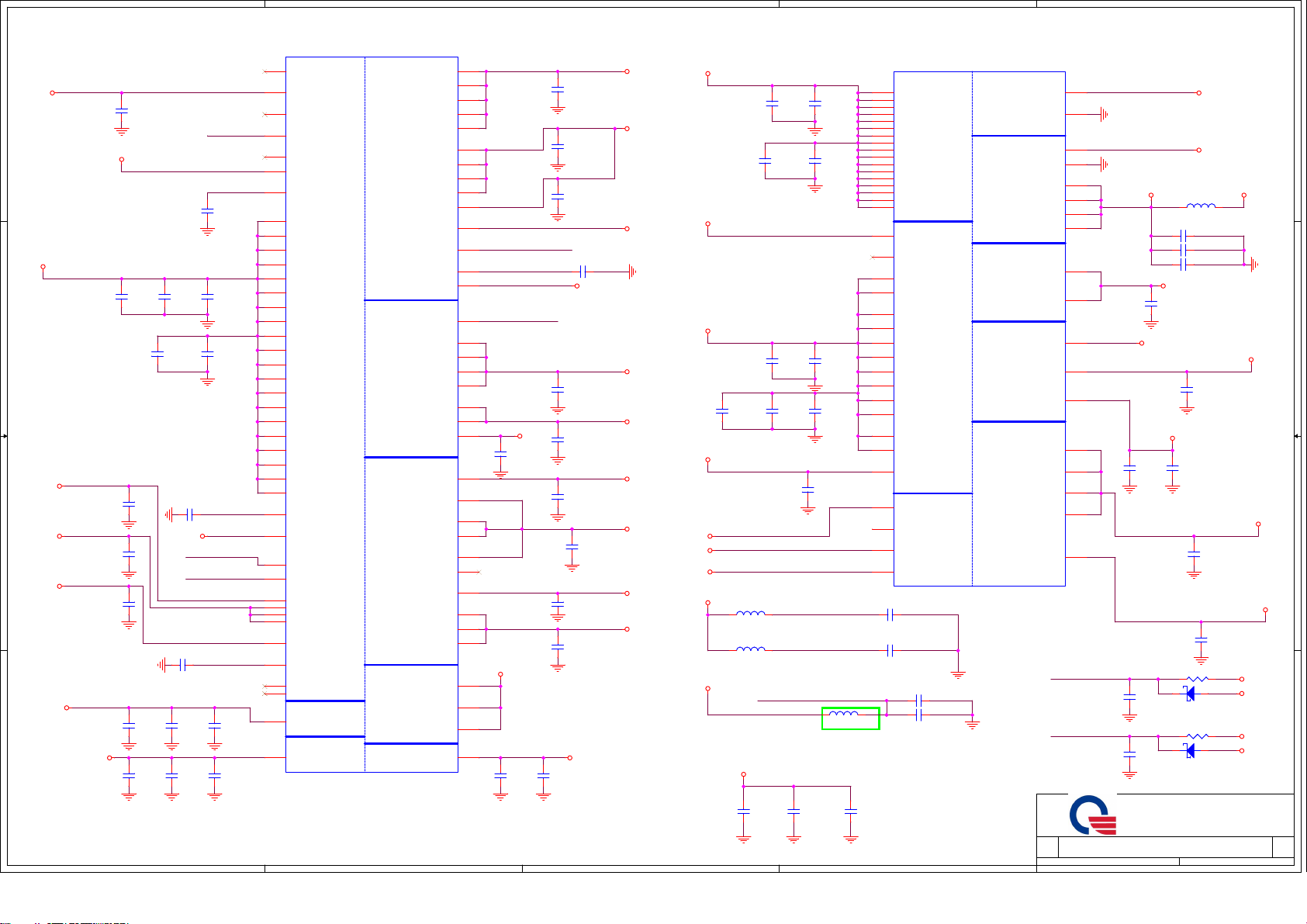

USB Master

A A

USB0

USB1

USB2

USB3

USB4

USB5

B B

USB6

Port Assignment

External port#1 (USB3.0)

External port#2 (USB3.0) mSATA

Camera

SATA0

SATA1

SATA2

SATA3

Port AssignmentSATA Master

HDD

NC

NC

External port#3 (USB3.0)

SATA4

NC

NC

SATA5

NC

NC

NC

PCIE 1

PCIE 2

PCIE 3

PCIE 4

PCIE 5

PCIE 6

PCIE 7

Port AssignmentPCIE Master

WLAN

LAN

Card reader

NC

NC

NC

NC

NCPCIE 8

USB7

USB8

USB9

USB10

USB11

USB12

NC

NC

Debug

WLAN

NC

Touch Screen

C C

D D

USB13

1

NC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, November 02, 2012 03 46

Date: Sheet of

Friday, November 02, 2012 03 46

Date: Sheet of

2

3

4

5

6

Friday, November 02, 2012 03 46

7

PROJECT :

PORT ASSIGNMENT

PORT ASSIGNMENT

PORT ASSIGNMENT

JW8

JW8

JW8

3A

3A

3A

8

5

4

3

2

1

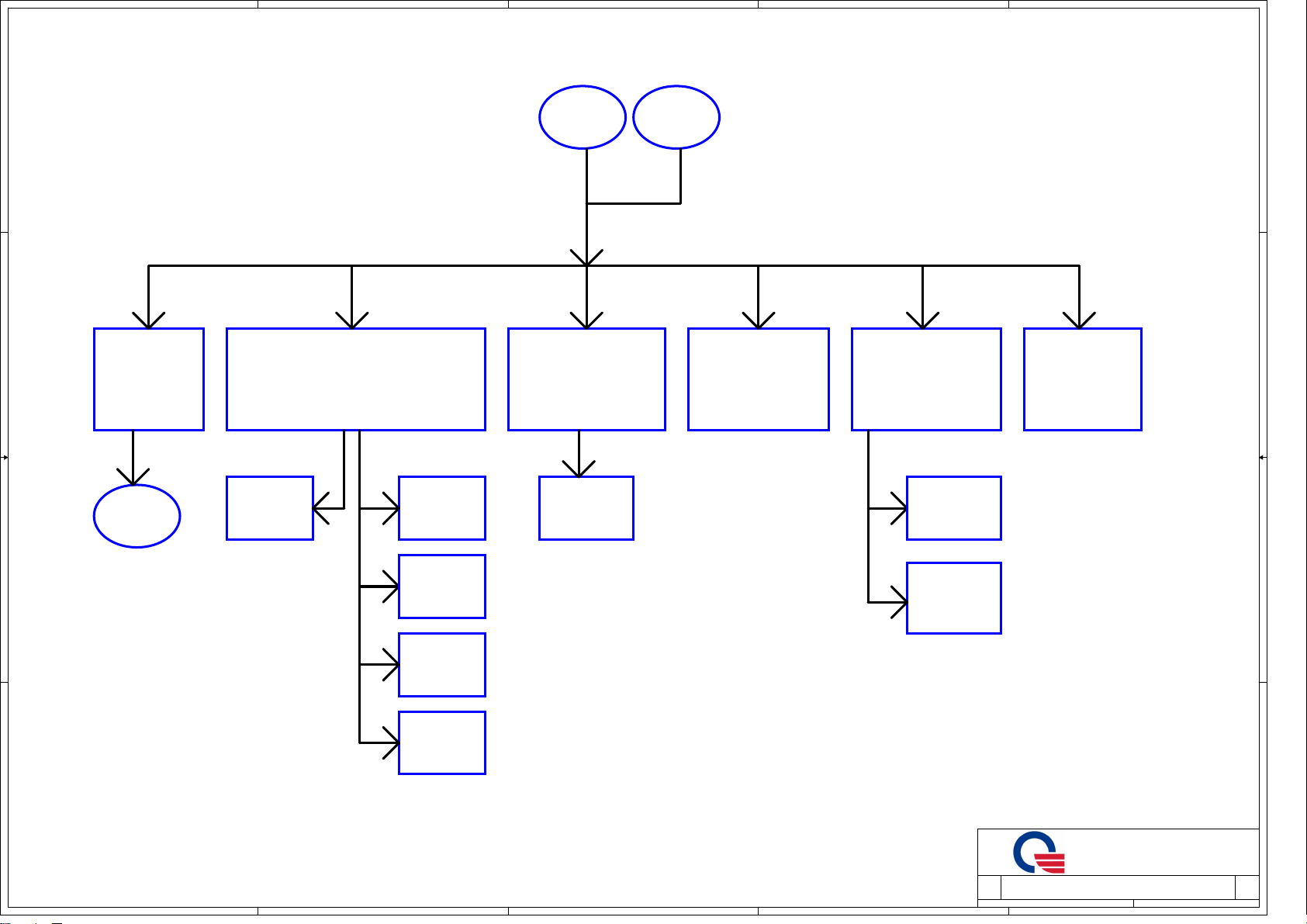

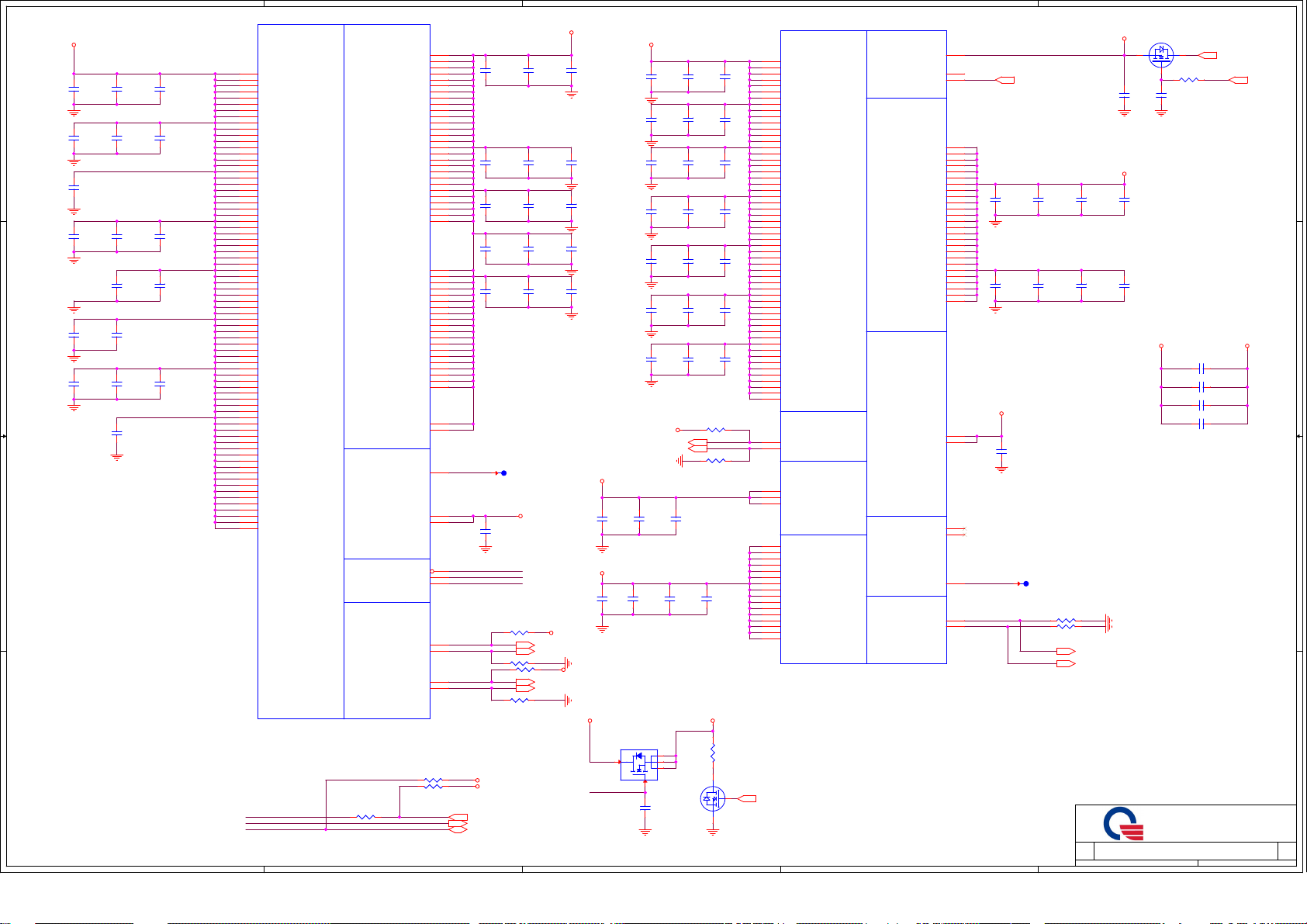

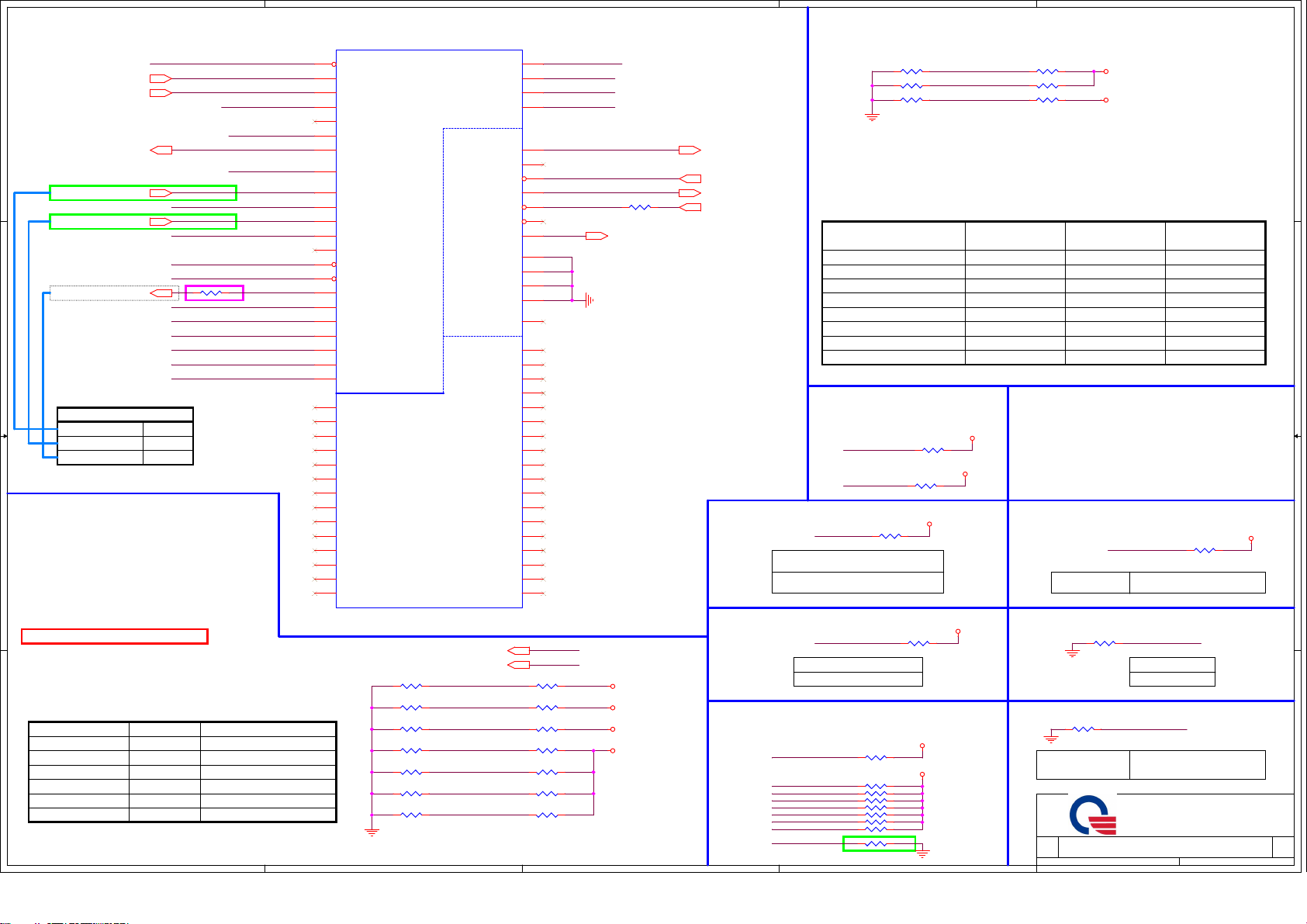

Main Power tree

D D

ADAPTER BATTERY

04

+PRWSRC

+VIN

+VIN

+VGACORE

+3VS5

+5VS5

+VIN

MEM Power

(RT8207)

+1.5VSUS

+0.75V_DDR_VTT

+VIN

C C

CHARGER

(OZ8682)

System +3/+5V

(RT8223P)

+VIN +VIN

CPU Power

(NCP6132)

(NCP5911)

+VCC_CORE

+VIN

Core Logic

(RT8240)

+1.05V

GPU Power

(NCP3218)

+VCC_GFXDDR_VTTREF

PU2

+BATCHG

BATTERY

PU3

+5VS5

EMB20N03V

+5V

PQ17

+3VS5

PU5

G5173R4

+1.8V

PU9

PU6

PU8

+1.5VSUS +1.05V

RJK03J3

+1.5V_GFX

PQ35

PU1

RJK03J3

+1.05V_GFX

PQ31

B B

EMB20N03V

+3V

PQ22

CPU Power

(G978F1)

+VCCSA

PU7

QM3002

+3VLANVCC

PQ10

QM3002

+3V_GFX

PQ38

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Power Tree

Power Tree

Power Tree

Friday, November 02, 2012 04 46

Friday, November 02, 2012 04 46

Friday, November 02, 2012 04 46

PROJECT :

JW8

JW8

JW8

3A

3A

3A

1

5

4

3

2

1

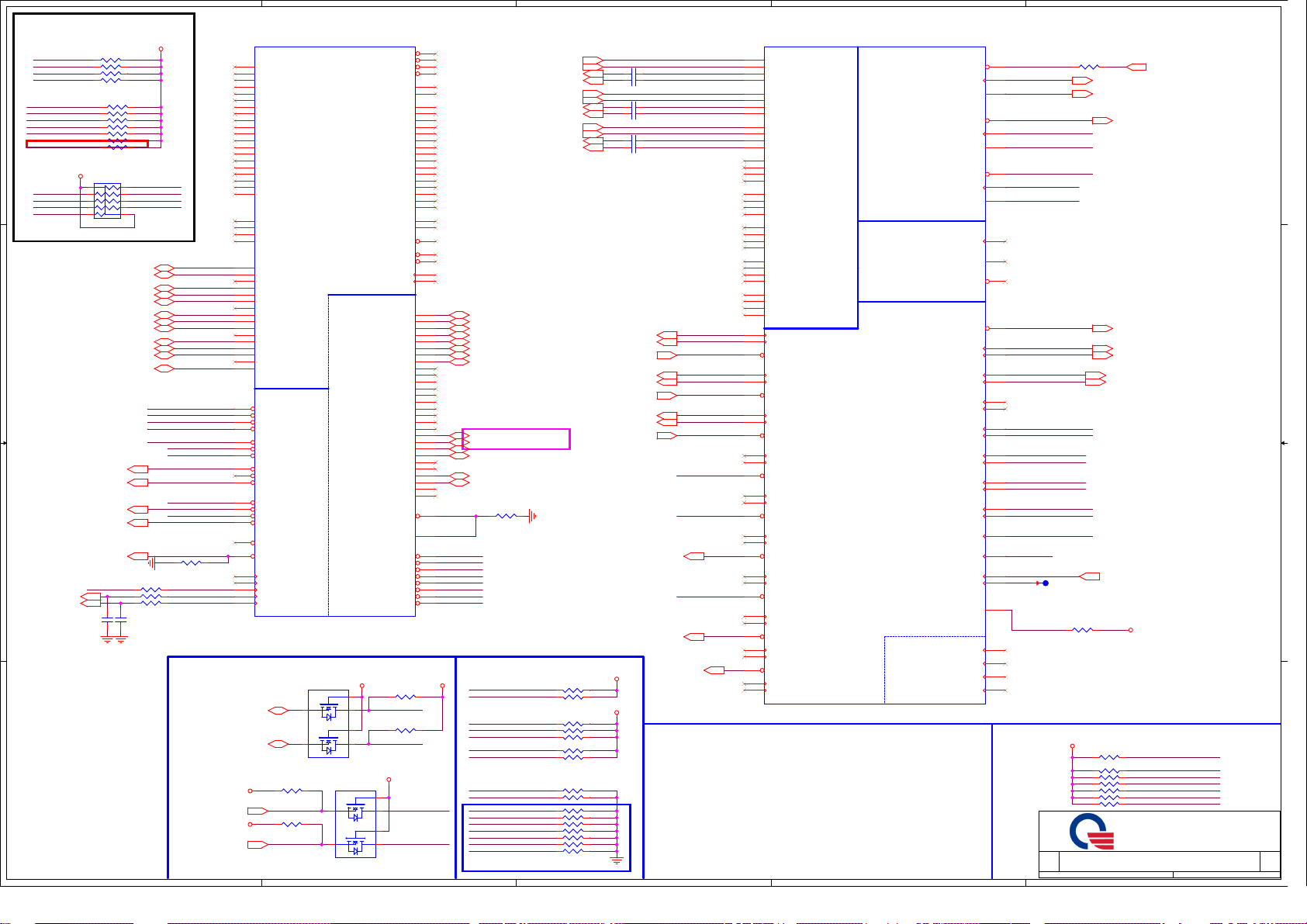

Chief River mainly Power On Sequence(G3 to S0)

From Coin Cell BAT

D D

From AC,BATT

Sys +3v/+5v VR internal power

From PW On Button to EC

EC Assert S5_On when received NBSWON#

From EC(S5_ON) to System +3V/+5V PWM

From EC to PCH

VCCRTC

VIN

+5VPCU/ +3VPCU

NBSWON#

S5_ON

+3VS5/+5VS5

EC_RSMRST#

17ms

EC defined 17ms from S5_ON to RSMRST#

05

EC defined 80ms from NBSWON# to assert DNBSWON# to PCH

From EC to PCH

DNBSWON#

PCH assert SUSCLK SUSCLK

C C

EC Assert SUS_ON

SUSB#/SUSC#From PCH to EC

SUS_ON

SUSON Power rail +1.5VSUS

EC Assert LAN_POWERON

LAN_POWERON

EC Assert MAIN_ON MAIN_ON

MainOn Power Rails

+3V/+5V/+1.05V/+1.8V/+1.05V_VTT

80ms

mini duration => 16ms(Intel Chief River)

5ms

SUSCLK RUNNING

PCH Asserted SUSB#/SUSC# to EC to assert SUSON..

?ms

10ms

EC defined 10ms from SUS_ON to LAN_POWERON Asserted

110ms

EC defined 110ms from SUS_ON to MAINON Asserted

?ms

1.05V_VTT_PWRGD to enable +VCCSA

EC Received HW_PG

B B

from MainOn/SUSON/VCCSA PowerGD

EC Assert VR_ON

EC Assert EC_PWROK

IMVP_PWRGD to PCH SYS_PWROK

PCH Assert PLTRST# PLTRST#

A A

5

1.05V_VTT_PWRGD

HW_PG

VR_ON

EC_PWROK(PCH PWROK)

IMVP_PWRGD(PCH SYS_PWROK)

DRAMPWROKDRAMPWROK

H_POWERGDPCH assert UNCOREPWRGOOD to CPU

DMI BUSDMI

4

EC defined 105ms from HWPG to VRON

EC defined 125ms from HWPG to ECPWROK

3

105ms

125ms

1ms+60uS

2

INT defined 99ms for minimum

5ms

0

2ms

200us

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Power On Sequence

Power On Sequence

Power On Sequence

Friday, November 02, 2012 05 46

Friday, November 02, 2012 05 46

Friday, November 02, 2012 05 46

PROJECT :

JW8

JW8

JW8

1

3A

3A

3A

5

4

3

2

1

Ivy Bridge Processor (DMI,PEG,FDI)

PEG_COMP connect to PIN G3&G4 W:4mils/S:15mils/L: 500mils.

U18A

DMI_TXN010

DMI_TXN110

DMI_TXN210

DMI_TXN310

D D

C C

B B

A A

DMI_TXP010

DMI_TXP110

DMI_TXP210

DMI_TXP310

DMI_RXN010

DMI_RXN110

DMI_RXN210

DMI_RXN310

DMI_RXP010

DMI_RXP110

DMI_RXP210

DMI_RXP310

FDI_TXN010

FDI_TXN110

FDI_TXN210

FDI_TXN310

FDI_TXN410

FDI_TXN510

FDI_TXN610

FDI_TXN710

FDI_TXP010

FDI_TXP110

FDI_TXP210

FDI_TXP310

FDI_TXP410

FDI_TXP510

FDI_TXP610

FDI_TXP710

FDI_FSYNC010

FDI_FSYNC110

FDI_INT10

FDI_LSYNC010

FDI_LSYNC110

eDP_COMP

eDP_COMPIO and ICOMPO signals should be shorted

near balls and routed with typical impedance <25 mohms

+1.05V

+1.05V

M2

DMI_RX#[0]

P6

DMI_RX#[1]

P1

DMI_RX#[2]

P10

DMI_RX#[3]

N3

DMI_RX[0]

P7

DMI_RX[1]

P3

DMI_RX[2]

P11

DMI_RX[3]

K1

DMI_TX#[0]

M8

DMI_TX#[1]

N4

DMI_TX#[2]

R2

DMI_TX#[3]

K3

DMI_TX[0]

M7

DMI_TX[1]

P4

DMI_TX[2]

T3

DMI_TX[3]

U7

FDI0_TX#[0]

W11

FDI0_TX#[1]

W1

FDI0_TX#[2]

AA6

FDI0_TX#[3]

W6

FDI1_TX#[0]

V4

FDI1_TX#[1]

Y2

FDI1_TX#[2]

AC9

FDI1_TX#[3]

U6

FDI0_TX[0]

W10

FDI0_TX[1]

W3

FDI0_TX[2]

AA7

FDI0_TX[3]

W7

FDI1_TX[0]

T4

FDI1_TX[1]

AA3

FDI1_TX[2]

AC8

FDI1_TX[3]

AA11

FDI0_FSYNC

AC12

FDI1_FSYNC

U11

FDI_INT

AA10

FDI0_LSYNC

AG8

FDI1_LSYNC

AF3

eDP_COMPIO

AD2

eDP_ICOMPO

AG11

eDP_HPD#

AG4

eDP_AUX#

AF4

eDP_AUX

AC3

eDP_TX#[0]

AC4

eDP_TX#[1]

AE11

eDP_TX#[2]

AE7

eDP_TX#[3]

AC1

eDP_TX[0]

AA4

eDP_TX[1]

AE10

eDP_TX[2]

AE6

eDP_TX[3]

IC,IVB_2CBGA,0P7

R262 24.9/F_4

R230 24.9/F_4

4mils

12mils

eDP_COMP

PEG_COMPPEG_COMP

DMI Intel(R) FDI

eDP

PEG_COMP connect to PIN G1 W:12mils/S:15mils/L: 500mils.

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

PEG_COMP

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

C_PEG_TX#0

C_PEG_TX#1

C_PEG_TX#2

C_PEG_TX#3

C_PEG_TX#4

C_PEG_TX#5

C_PEG_TX#6

C_PEG_TX#7

C_PEG_TX0

C_PEG_TX1

C_PEG_TX2

C_PEG_TX3

C_PEG_TX4

C_PEG_TX5

C_PEG_TX6

C_PEG_TX7

PEG_TX#[0..7]19

C4 0.22U/10V_4

C513 0.22U/10V_4

C511 0.22U/10V_4

C26 0.22U/10V_4

C8 0.22U/10V_4

C515 0.22U/10V_4

C30 0.22U/10V_4

C27 0.22U/10V_4

PEG x8

PEG_TX[0..7]19

C5 0.22U/10V_4

C512 0.22U/10V_4

C510 0.22U/10V_4

C25 0.22U/10V_4

C7 0.22U/10V_4

C514 0.22U/10V_4

C29 0.22U/10V_4

C28 0.22U/10V_4

PM_DRAM_PWRGD10

PEG_RX#[0..7] 19

PEG_RX[0..7] 19

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

H_PROCHOT#32,42

+1.5V_CPU

C525 47P/50V_4

PM_THRMTRIP#13,32

PM_SYNC10

H_PWRGOOD13

PLTRST#12,19,27,28,30,32

R44

200/F_4

R42 130/F_4

R36

*3K/F_4_NC

U18B

MISC THERMAL PWR MANAGEMENT

H_SNB_IVB#11

H_PECI32

R239 56.2/F_4 R305 25.5/F_4

Close to CPU.

CPU RESET#

R234 1.5K/F_4

H_PROCHOT#_R

R4 10K/F_4

C9 *43P/50V_4_NC

PM_DRAM_PWRGD_R

CPU_RESET#

R235

750/F_4

F49

C57

C49

A48

C45

D45

C48

B46

BE45

D44

IC,IVB_2CBGA,0P7

PROC_SELECT#

PROC_DETECT#

CATERR#

PECI

PROCHOT#

THERMTRIP#

PM_SYNC

UNCOREPWRGOOD

SM_DRAMPWROK

RESET#

CLOCKS

DDR3

JTAG & BPM

DPLL_REF_CLK#

MISC

DPLL_REF_CLK

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

J3

BCLK

H2

BCLK#

AG3

AG1

AT30

BF44

BE43

BG43

SM_RCOMP[0] W:20mils/S:20mils/L: 500mils,

SM_RCOMP[1] W:20mils/S:20mils/L: 500mils,

SM_RCOMP[2] W:15mils/S:20mils/L: 500mils,

N53

PRDY#

N55

PREQ#

L56

TCK

L55

TMS

J58

TRST#

M60

TDI

L59

TDO

K58

DBR#

G58

BPM#[0]

E55

BPM#[1]

E59

BPM#[2]

G55

BPM#[3]

G59

BPM#[4]

H60

BPM#[5]

J59

BPM#[6]

J61

BPM#[7]

R265 1K/F_4

R264 1K/F_4

CPU_DRAMRST#

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI_R

XDP_TDO

CLK_CPU_BCLKP 12

CLK_CPU_BCLKN 12

DDR3 DRAM RESET

+1.5VSUS

R45

1K/F_4

PM_DRAM_PWRGD_R

DRAMRST_CNTRL_PCH12,18

2

C189

0.047U/10V_4

3

Q1

2N7002K

1

CPU_DRAMRST#

R40

4.99K/F_4

R46 1K/F_4

CPU_DRAMRST#_R

Processor pull-up (CPU)

R304 140/F_4

R306 200/F_4

XDP_DBRST# 10

DDR3_DRAMRST# 16,17,18

H_PROCHOT#

XDP_TDO

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TCLK

XDP_TRST#

06

+1.05V

+1.05V

R243 62_4

R255 51_4

R245 51_4

R251 51_4

R254 *51_4_NC

R249 51_4

R250 51_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Friday, November 02, 2012 06 46

Friday, November 02, 2012 06 46

Friday, November 02, 2012 06 46

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

PROJECT :

Processor 1/4 (Host/GPU)

Processor 1/4 (Host/GPU)

Processor 1/4 (Host/GPU)

JW8

JW8

JW8

3A

3A

3A

of

of

1

of

5

4

3

2

1

Ivy Bridge Processor (DDR3)

07

D D

M_A_DQ[63:0]16,17

C C

B B

M_A_BS#016,17

M_A_BS#116,17

M_A_BS#216,17

M_A_CAS#16,17

M_A_RAS#16,17

M_A_WE#16,17

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

U18C IC,IVB_2CBGA,0P7

AG6

SA_DQ[0]

AJ6

SA_DQ[1]

AP11

SA_DQ[2]

AL6

SA_DQ[3]

AJ10

SA_DQ[4]

AJ8

SA_DQ[5]

AL8

SA_DQ[6]

AL7

SA_DQ[7]

AR11

SA_DQ[8]

AP6

SA_DQ[9]

AU6

SA_DQ[10]

AV9

SA_DQ[11]

AR6

SA_DQ[12]

AP8

SA_DQ[13]

AT13

SA_DQ[14]

AU13

SA_DQ[15]

BC7

SA_DQ[16]

BB7

SA_DQ[17]

BA13

SA_DQ[18]

BB11

SA_DQ[19]

BA7

SA_DQ[20]

BA9

SA_DQ[21]

BB9

SA_DQ[22]

AY13

SA_DQ[23]

AV14

SA_DQ[24]

AR14

SA_DQ[25]

AY17

SA_DQ[26]

AR19

SA_DQ[27]

BA14

SA_DQ[28]

AU14

SA_DQ[29]

BB14

SA_DQ[30]

BB17

SA_DQ[31]

BA45

SA_DQ[32]

AR43

SA_DQ[33]

AW48

SA_DQ[34]

BC48

SA_DQ[35]

BC45

SA_DQ[36]

AR45

SA_DQ[37]

AT48

SA_DQ[38]

AY48

SA_DQ[39]

BA49

SA_DQ[40]

AV49

SA_DQ[41]

BB51

SA_DQ[42]

AY53

SA_DQ[43]

BB49

SA_DQ[44]

AU49

SA_DQ[45]

BA53

SA_DQ[46]

BB55

SA_DQ[47]

BA55

SA_DQ[48]

AV56

SA_DQ[49]

AP50

SA_DQ[50]

AP53

SA_DQ[51]

AV54

SA_DQ[52]

AT54

SA_DQ[53]

AP56

SA_DQ[54]

AP52

SA_DQ[55]

AN57

SA_DQ[56]

AN53

SA_DQ[57]

AG56

SA_DQ[58]

AG53

SA_DQ[59]

AN55

SA_DQ[60]

AN52

SA_DQ[61]

AG55

SA_DQ[62]

AK56

SA_DQ[63]

BD37

SA_BS[0]

BF36

SA_BS[1]

BA28

SA_BS[2]

BE39

SA_CAS#

BD39

SA_RAS#

AT41

SA_WE#

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

AU36

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

M_A_CLKP1

M_A_CLKN1

R27 *75/F_4_NC

M_A_CLKP0 16,17

M_A_CLKN0 16,17

M_A_CKE0 16,17

M_A_CS#0 16,17

M_A_ODT0 16,17

M_A_DQSN0 16

M_A_DQSN1 16

M_A_DQSN2 16

M_A_DQSN3 16

M_A_DQSN4 17

M_A_DQSN5 17

M_A_DQSN6 17

M_A_DQSN7 17

M_A_DQSP0 16

M_A_DQSP1 16

M_A_DQSP2 16

M_A_DQSP3 16

M_A_DQSP4 17

M_A_DQSP5 17

M_A_DQSP6 17

M_A_DQSP7 17

DDR SYSTEM MEMORY A

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_A[15:0] 16,17

M_B_DQ[63:0]18

M_B_BS#018

M_B_BS#118

M_B_BS#218

M_B_CAS#18

M_B_RAS#18

M_B_WE#18

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

U18D IC,IVB_2CBGA,0P7

AL4

SB_DQ[0]

AL1

SB_DQ[1]

AN3

SB_DQ[2]

AR4

SB_DQ[3]

AK4

SB_DQ[4]

AK3

SB_DQ[5]

AN4

SB_DQ[6]

AR1

SB_DQ[7]

AU4

SB_DQ[8]

AT2

SB_DQ[9]

AV4

SB_DQ[10]

BA4

SB_DQ[11]

AU3

SB_DQ[12]

AR3

SB_DQ[13]

AY2

SB_DQ[14]

BA3

SB_DQ[15]

BE9

SB_DQ[16]

BD9

SB_DQ[17]

BD13

SB_DQ[18]

BF12

SB_DQ[19]

BF8

SB_DQ[20]

BD10

SB_DQ[21]

BD14

SB_DQ[22]

BE13

SB_DQ[23]

BF16

SB_DQ[24]

BE17

SB_DQ[25]

BE18

SB_DQ[26]

BE21

SB_DQ[27]

BE14

SB_DQ[28]

BG14

SB_DQ[29]

BG18

SB_DQ[30]

BF19

SB_DQ[31]

BD50

SB_DQ[32]

BF48

SB_DQ[33]

BD53

SB_DQ[34]

BF52

SB_DQ[35]

BD49

SB_DQ[36]

BE49

SB_DQ[37]

BD54

SB_DQ[38]

BE53

SB_DQ[39]

BF56

SB_DQ[40]

BE57

SB_DQ[41]

BC59

SB_DQ[42]

AY60

SB_DQ[43]

BE54

SB_DQ[44]

BG54

SB_DQ[45]

BA58

SB_DQ[46]

AW59

SB_DQ[47]

AW58

SB_DQ[48]

AU58

SB_DQ[49]

AN61

SB_DQ[50]

AN59

SB_DQ[51]

AU59

SB_DQ[52]

AU61

SB_DQ[53]

AN58

SB_DQ[54]

AR58

SB_DQ[55]

AK58

SB_DQ[56]

AL58

SB_DQ[57]

AG58

SB_DQ[58]

AG59

SB_DQ[59]

AM60

SB_DQ[60]

AL59

SB_DQ[61]

AF61

SB_DQ[62]

AH60

SB_DQ[63]

BG39

SB_BS[0]

BD42

SB_BS[1]

AT22

SB_BS[2]

AV43

SB_CAS#

BF40

SB_RAS#

BD45

SB_WE#

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_CLKP0 18

M_B_CLKN0 18

M_B_CKE0 18

M_B_CLKP1 18

M_B_CLKN1 18

M_B_CKE1 18

M_B_CS#0 18

M_B_CS#1 18

M_B_ODT0 18

M_B_ODT1 18

M_B_DQSN[7:0] 18

M_B_DQSP[7:0] 18

DDR SYSTEM MEMORY B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_A[15:0] 18

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, November 02, 2012 07 46

Date: Sheet of

Friday, November 02, 2012 07 46

Date: Sheet of

5

4

3

2

Friday, November 02, 2012 07 46

PROJECT :

Processor 2/5 (DDR3 I/F)

Processor 2/5 (DDR3 I/F)

Processor 2/5 (DDR3 I/F)

JW8

JW8

JW8

3A

3A

3A

1

5

U18F

+VCC_CORE

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

C19

C76

10U/6.3VS_6

D D

C23

10U/6.3VS_6

C24

10U/6.3VS_6

C15

10U/6.3VS_6

C C

B B

A A

C70

10U/6.3VS_6

C82

10U/6.3VS_6

22uF_8 x8 Socket TOP cavity

22uF_8 x10 Socket BOT cavity

22uF_8 x8 Socket TOP edge

470uF_7343 x4

10U/6.3VS_6

C22

10U/6.3VS_6

C81

*22U/6.3VS_6_NC

C17

10U/6.3VS_6

C20

10U/6.3VS_6

C21

10U/6.3VS_6

C16

10U/6.3VS_6

5

C71

10U/6.3VS_6

C83

10U/6.3VS_6

C72

10U/6.3VS_6

C14

10U/6.3VS_6

C18

10U/6.3VS_6

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

IC,IVB_2CBGA,0P7

H_CPU_SVIDALRT#

POWER

CORE SUPPLY

R229 43_4

4

VCCIO[1]

VCCIO[3]

VCCIO[4]

VCCIO[5]

VCCIO[6]

VCCIO[7]

VCCIO[8]

VCCIO[9]

VCCIO[10]

VCCIO[11]

VCCIO[12]

VCCIO[13]

VCCIO[14]

VCCIO[15]

VCCIO[16]

VCCIO[17]

VCCIO[18]

VCCIO[19]

VCCIO[20]

VCCIO[21]

VCCIO[22]

VCCIO[23]

VCCIO[24]

VCCIO[25]

VCCIO[26]

VCCIO[27]

VCCIO[28]

VCCIO[29]

VCCIO[30]

VCCIO[31]

VCCIO[32]

PEG IO AND DDR IO

VCCIO[33]

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

RAILS

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES SVID QUIET

R231 130/F_4

R232 75_4

4

IVB:8.5A

AF46

AG48

AG50

AG51

AJ17

AJ21

AJ25

AJ43

AJ47

AK50

AK51

AL14

AL15

AL16

AL20

AL22

AL26

AL45

AL48

AM16

AM17

AM21

AM43

AM47

AN20

AN42

AN45

AN48

AA14

AA15

AB17

AB20

AC13

AD16

AD18

AD21

AE14

AE15

22uF_8 x7 Socket TOP cavity

AF16

22uF_8 x5 Socket BOT cavity

AF18

22uF_8 x2 Socket TOP cavity (no stuff)

AF20

22uF_8 x5 Socket BOT cavity (no stuff)

AG15

330uF_7343 x2

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

VCCIO_SEL

AM25

AN22

A44

H_CPU_SVIDALRT#

B43

VR_SVID_CLK

C44

VR_SVID_DATA

100ohm±1% pull-up to VCC near processor.

F43

G43

AN16

AN17

+1.05V

+1.05V

VR_SVID_ALERT# 42

VR_SVID_CLK 42

VR_SVID_DATA 42

C151

1U/6.3V_4

C105

*22U/6.3VS_6_NC

10U/6.3VS_6

C119

*22U/6.3VS_6_NC

C131

*22U/6.3VS_6_NC

TP3

+1.05V

C117

1U/6.3V_4

R12 100/F_4

R13 100/F_4

R24 10/F_4

R30 10/F_4

C162

1U/6.3V_4

C134

10U/6.3VS_6

C154

10U/6.3VS_6

C96

10U/6.3VS_6

C113

10U/6.3VS_6

+VCC_CORE

VCC_SENSE 42

VSS_SENSE 42

VCCP_SENSE 38

VSSP_SENSE 38

+1.05V

C155

1U/6.3V_4

C121

*22U/6.3VS_6_NC

C132

*22U/6.3VS_6_NC

C144

10U/6.3VS_6

C118

10U/6.3VS_6

+1.8V

+VCC_GFX

C106

10U/6.3VS_6

C139

10U/6.3VS_6

C147

*22U/6.3VS_6_NC

C172

*22U/6.3VS_6_NC

C141

1U/6.3V_4

C538

1U/6.3V_4

C120

1U/6.3V_4

+VCC_GFX

VCC_AXG_SENSE42

VSS_AXG_SENSE42

IVB: 1.5A

C555

C554

1U/6.3V_4

1U/6.3V_4

330uF x1, 10uF_8 x1, 1uF_4 x2

Socket BOT edge.

+VCCSA

C73

C77

10U/6.3V_6

10U/6.3V_6

330uF x1, 10uF_8 x1 Socket BOT edge,

10uF_8 x2 Socket BOT cavity.

Zo impedance: 27.4ohm

+1.05V

Zo impedance: 27.4ohm

Q4

AON7410

5 2

4

MAIND

CPU VDDQ

3

22uF_8 x2 Socket TOP cavity

22uF_8 x2 Socket BOT cavity

22uF_8 x4 Socket TOP edge

22uF_8 x4 Socket BOT edge

470uF_7343 x2

C89

C163

10U/6.3VS_6

*22U/6.3VS_6_NC

C153

C88

C158

C536

C143

C129

C87

10U/6.3VS_6

C75

*22U/6.3VS_6_NC

C94

*22U/6.3VS_6_NC

C142

1U/6.3V_4

C140

1U/6.3V_4

C164

1U/6.3V_4

R15 10/F_4

R14 10/F_4

C557

10U/6.3V_6

10U/6.3VS_6

10U/6.3VS_6

10U/6.3VS_6

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

IVB: 6A

C80

10U/6.3V_6

10U/6.3V_6

+1.5V_CPU+1.5VSUS

1

3

C191

*470P/50V_4_NC

3

2

U18G

AA46

VAXG[1]

AB47

VAXG[2]

AB50

VAXG[3]

AB51

VAXG[4]

AB52

VAXG[5]

AB53

VAXG[6]

AB55

VAXG[7]

AB56

VAXG[8]

AB58

VAXG[9]

AB59

VAXG[10]

AC61

VAXG[11]

AD47

VAXG[12]

AD48

VAXG[13]

AD50

VAXG[14]

AD51

VAXG[15]

AD52

VAXG[16]

AD53

VAXG[17]

AD55

VAXG[18]

AD56

VAXG[19]

AD58

VAXG[20]

AD59

VAXG[21]

AE46

VAXG[22]

N45

VAXG[23]

P47

VAXG[24]

P48

VAXG[25]

P50

VAXG[26]

P51

VAXG[27]

P52

VAXG[28]

P53

VAXG[29]

P55

VAXG[30]

P56

VAXG[31]

P61

VAXG[32]

T48

VAXG[33]

T58

VAXG[34]

T59

VAXG[35]

T61

VAXG[36]

U46

VAXG[37]

V47

VAXG[38]

V48

VAXG[39]

V50

VAXG[40]

V51

VAXG[41]

V52

VAXG[42]

V53

VAXG[43]

V55

VAXG[44]

V56

VAXG[45]

V58

VAXG[46]

V59

VAXG[47]

W50

VAXG[48]

W51

VAXG[49]

W52

VAXG[50]

W53

VAXG[51]

W55

VAXG[52]

W56

VAXG[53]

W61

VAXG[54]

Y48

VAXG[55]

Y61

VAXG[56]

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL[1]

BC1

VCCPLL[2]

BC4

VCCPLL[3]

L17

VCCSA[1]

L21

VCCSA[2]

N16

VCCSA[3]

N20

VCCSA[4]

N22

VCCSA[5]

P17

VCCSA[6]

P20

VCCSA[7]

R16

VCCSA[8]

R18

VCCSA[9]

R41

220_8

Q2

2N7002K

2

R21

VCCSA[10]

U15

VCCSA[11]

V16

VCCSA[12]

V17

VCCSA[13]

V18

VCCSA[14]

V21

VCCSA[15]

W20

VCCSA[16]

IC,IVB_2CBGA,0P7

MAIN_ONG 44

C90

3

1

POWER

VREF

DDR3 - 1.5V RAILS

GRAPHICS

SENSE

LINES

1.8V RAIL

SA RAIL

VCCSA VID

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VDDQ[10]

VDDQ[11]

VDDQ[12]

VDDQ[13]

VDDQ[14]

VDDQ[15]

VDDQ[16]

VDDQ[17]

VDDQ[18]

VDDQ[19]

VDDQ[20]

VDDQ[21]

VDDQ[22]

VDDQ[23]

VDDQ[24]

VDDQ[25]

VDDQ[26]

VCCDQ[1]

VCCDQ[2]

QUIET RAILS

VDDQ_SENSE

VSS_SENSE_VDDQ

VCCSA_SENSE

SENSE LINES

VCCSA_VID[0]

VCCSA_VID[1]

lines

2

VDDQ[1]

VDDQ[2]

VDDQ[3]

VDDQ[4]

VDDQ[5]

VDDQ[6]

VDDQ[7]

VDDQ[8]

VDDQ[9]

AY43

BE7

BG7

20mils width

AJ28

AJ33

AJ36

AJ40

AL30

AL34

AL38

AL42

AM33

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

C108

10U/6.3V_6

C128

10U/6.3V_6

CPU center

CRB: 1uf*1

+1.5V_CPU

AM28

AN26

BC43

BA43

100R pull high ??

U10

VCCSA_SENSE

D48

D49

CAD Note: +VDDR_REF_CPU should

have 10 mil trace width

SMDDR_VREF_DQ1_M3 18

+VDDR_REF_CPU and DDR_VTTREF must use 10mils width

IVB: 5A

C107

10U/6.3V_6C138

C126

10U/6.3V_6

C157

1U/6.3V_4

TP1

R6 1K/F_4

R5 1K/F_4

+VDDR_REF_CPU

+1.5V_CPU

C196

10U/6.3V_6

C112

10U/6.3V_6

VCCSA_SEL0 37

VCCSA_SEL 37

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, November 02, 2012 08 46

Date: Sheet of

Friday, November 02, 2012 08 46

Date: Sheet of

Friday, November 02, 2012 08 46

1

Q3

1

C186

0.1U/10V_4

C97

10U/6.3V_6

C135

10U/6.3V_6

3

DDR_VTTREF 16,18,36

2N7002K

2

R50 3.3K/F_4

C190

470P/50V_4

C194 0.1U/10V_4

C195 0.1U/10V_4

C193 0.1U/10V_4

C192 0.1U/10V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Processor 3/4 (POWER)

Processor 3/4 (POWER)

Processor 3/4 (POWER)

1

JW8

JW8

JW8

08

MAIND 44

+1.5VSUS+1.5V_CPU

3A

3A

3A

5

4

3

2

1

U18H

A13

VSS[1]

A17

VSS[2]

A21

VSS[3]

A25

VSS[4]

A28

VSS[5]

D D

C C

B B

A A

A33

A37

A40

A45

A49

A53

AA1

AA13

AA50

AA51

AA52

AA53

AA55

AA56

AA8

AB16

AB18

AB21

AB48

AB61

AC10

AC14

AC46

AC6

AD17

AD20

AD4

AD61

AE13

AE8

AF1

AF17

AF21

AF47

AF48

AF50

AF51

AF52

AF53

AF55

AF56

AF58

AF59

AG10

AG14

AG18

AG47

AG52

AG61

AG7

AH4

AH58

AJ13

AJ16

AJ20

AJ22

AJ26

AJ30

AJ34

AJ38

AJ42

AJ45

AJ48

AJ7

AK1

AK52

AL10

AL13

AL17

AL21

AL25

AL28

AL33

AL36

AL40

AL43

AL47

AL61

AM13

AM20

AM22

AM26

AM30

AM34

VSS[6]

VSS[7]

VSS[8]

VSS[9]

VSS[10]

VSS[11]

A9

VSS[12]

VSS[13]

VSS[14]

VSS[15]

VSS[16]

VSS[17]

VSS[18]

VSS[19]

VSS[20]

VSS[21]

VSS[22]

VSS[23]

VSS[24]

VSS[25]

VSS[26]

VSS[27]

VSS[28]

VSS[29]

VSS[30]

VSS[31]

VSS[32]

VSS[33]

VSS[34]

VSS[35]

VSS[36]

VSS[37]

VSS[38]

VSS[39]

VSS[40]

VSS[41]

VSS[42]

VSS[43]

VSS[44]

VSS[45]

VSS[46]

VSS[47]

VSS[48]

VSS[49]

VSS[50]

VSS[51]

VSS[52]

VSS[53]

VSS[54]

VSS[55]

VSS[56]

VSS[57]

VSS[58]

VSS[59]

VSS[60]

VSS[61]

VSS[62]

VSS[63]

VSS[64]

VSS[65]

VSS[66]

VSS[67]

VSS[68]

VSS[69]

VSS[70]

VSS[71]

VSS[72]

VSS[73]

VSS[74]

VSS[75]

VSS[76]

VSS[77]

VSS[78]

VSS[79]

VSS[80]

VSS[81]

VSS[82]

VSS[83]

VSS[84]

VSS[85]

VSS[86]

VSS[87]

VSS[88]

VSS[89]

VSS[90]

VSS

VSS[91]

VSS[92]

VSS[93]

VSS[94]

VSS[95]

VSS[96]

VSS[97]

VSS[98]

VSS[99]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

VSS[164]

VSS[165]

VSS[166]

VSS[167]

VSS[168]

VSS[169]

VSS[170]

VSS[171]

VSS[172]

VSS[173]

VSS[174]

VSS[175]

VSS[176]

VSS[177]

VSS[178]

VSS[179]

VSS[180]

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

U18I

BG17

BG21

BG24

BG28

BG37

BG41

BG45

BG49

BG53

BG9

C29

C35

C40

D10

D14

D18

D22

D26

D29

D35

D4

D40

D43

D46

D50

D54

D58

D6

E25

E29

E3

E35

E40

F13

F15

F19

F29

F35

F40

F55

G51

G6

G61

H10

H14

H17

H21

H4

H53

H58

J1

J49

J55

K11

K21

K51

K8

L16

L20

L22

L26

L30

L34

L38

L43

L48

L61

M11

M15

IC,IVB_2CBGA,0P7

VSS[181]

VSS[182]

VSS[183]

VSS[184]

VSS[185]

VSS[186]

VSS[187]

VSS[188]

VSS[189]

VSS[190]

VSS[191]

VSS[192]

VSS[193]

VSS[194]

VSS[195]

VSS[196]

VSS[197]

VSS[198]

VSS[199]

VSS[200]

VSS[201]

VSS[202]

VSS[203]

VSS[204]

VSS[205]

VSS[206]

VSS[207]

VSS[208]

VSS[209]

VSS[210]

VSS[211]

VSS[212]

VSS[213]

VSS[214]

VSS[215]

VSS[216]

VSS[217]

VSS[218]

VSS[219]

VSS[220]

VSS[221]

VSS[222]

VSS[223]

VSS[224]

VSS[225]

VSS[226]

VSS[227]

VSS[228]

VSS[229]

VSS[230]

VSS[231]

VSS[232]

VSS[233]

VSS[234]

VSS[235]

VSS[236]

VSS[237]

VSS[238]

VSS[239]

VSS[240]

VSS[241]

VSS[242]

VSS[243]

VSS[244]

VSS[245]

VSS[246]

VSS[247]

VSS[248]

VSS[249]

VSS

VSS[250]

VSS[251]

VSS[252]

VSS[253]

VSS[254]

VSS[255]

VSS[256]

VSS[257]

VSS[258]

VSS[259]

VSS[260]

VSS[261]

VSS[262]

VSS[263]

VSS[264]

VSS[265]

VSS[266]

VSS[267]

VSS[268]

VSS[269]

VSS[270]

VSS[271]

VSS[272]

VSS[273]

VSS[274]

VSS[275]

VSS[276]

VSS[277]

VSS[278]

VSS[279]

VSS[280]

VSS[281]

VSS[282]

VSS[283]

VSS[284]

VSS[285]

VSS[286]

VSS[287]

VSS[288]

VSS[289]

VSS[290]

VSS[291]

VSS[292]

VSS[293]

VSS[294]

VSS[295]

VSS[296]

VSS[297]

VSS[298]

VSS[299]

VSS[300]

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

VSS_NCTF_11

NCTF

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

Processor Strapping

CFG2

(PCIe Static x16 Lane Numbering Reversal.)

CFG4

(DP Presence Strap)

M4

M58

M6

N1

N17

N21

N25

N28

N33

Need check GPU

N36

eDP Enable

N40

N43

N47

N48

N51

N52

N56

N61

P14

P16

P18

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

CF2~CF7 ??

U13

U8

V20

V61

W13

W15

W18

W21

W46

W8

Y4

Y47

Y58

Y59

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

R247 1K/F_4

CFG[6:5] (PCIE Port Bifurcation Straps)

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG5

C51

B54

D53

A51

C53

C55

H49

A55

H51

K49

K53

F53

G53

F51

D52

H43

K43

H45

K45

F48

G48

H48

K48

BA19

AV19

AT21

BB21

BB19

AY21

BA22

AY22

AU19

AU21

BD21

BD22

BD25

BD26

BG22

BE22

BG26

BE26

BF23

BE24

B50

L51

L53

The CFG signals have a default value of '1' if not terminated on the board.

1 0

Normal Operation(Default) Lane Reversed

Disable; No physical DP attached to eDP

Enable; An ext DP device is connected to eDP

U18E

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

VCC_VAL_SENSE

VSS_VAL_SENSE

VAXG_VAL_SENSE

VSSAXG_VAL_SENSE

VCC_DIE_SENSE

RSVD47

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

IC,IVB_2CBGA,0P7

RESERVED

BCLK_ITP

BCLK_ITP#

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

N59

N58

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

09

IC,IVB_2CBGA,0P7

5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, November 02, 2012 09 46

Date: Sheet of

Friday, November 02, 2012 09 46

Date: Sheet of

4

3

2

Friday, November 02, 2012 09 46

PROJECT :

Processor 4/4 (RSV,Ground)

Processor 4/4 (RSV,Ground)

Processor 4/4 (RSV,Ground)

JW8

JW8

JW8

3A

3A

3A

1

5

Cougar Point/Panther Point (DMI,FDI,PM)

U23C

CPT_PPT_Rev_0p7

DMI_RXN006

DMI_RXN106

DMI_RXN206

DMI_RXN306

DMI_RXP006

DMI_RXP106

+1.05V

PM_DRAM_PWRGD06

DMI_RXP206

DMI_RXP306

DMI_TXN006

DMI_TXN106

DMI_TXN206

DMI_TXN306

DMI_TXP006

DMI_TXP106

DMI_TXP206

DMI_TXP306

XDP_DBRST#06

IMVP_PWRGD42

EC_PWROK32

RSMRST#32

SUS_PWR_ACK32

DNBSWON#32

R336 49.9/F_4

R335 750/F_4

R167 *100K/F_4_NC

DMI_COMP

DMI_RBIAS

SUS_PWR_ACK

C373 *1U/6.3V_4_NC

AC_PRESENT_R

PM_BATLOW#

PM_RI#

D D

C C

B B

BC24

DMI0RXN

BE20

DMI1RXN

BG18

DMI2RXN

BG20

DMI3RXN

BE24

DMI0RXP

BC20

DMI1RXP

BJ18

DMI2RXP

BJ20

DMI3RXP

AW24

DMI0TXN

AW20

DMI1TXN

BB18

DMI2TXN

AV18

DMI3TXN

AY24

DMI0TXP

AY20

DMI1TXP

AY18

DMI2TXP

AU18

DMI3TXP

BJ24

DMI_ZCOMP

BG25

DMI_IRCOMP

BH21

DMI2RBIAS

C12

SUSACK#

K3

SYS_RESET#

P12

SYS_PWROK

L22

PWROK

L10

APWROK

B13

DRAMPWROK

C21

RSMRST#

(+3VS5)

K16

SUSWARN#/SUSPWRDNACK/GPIO30

E20

PWRBTN#

(DSW)

H20

ACPRESENT / GPIO31

(+3VS5)

E10

BATLOW# / GPIO72

A10

RI#

DMI

FDI

CLKRUN# / GPIO32

SUS_STAT# / GPIO61

SUSCLK / GPIO62

SLP_S5# / GPIO63

System Power Management

SLP_LAN# / GPIO29

FDI_RXN0

FDI_RXN1

FDI_RXN2

FDI_RXN3

FDI_RXN4

FDI_RXN5

FDI_RXN6

FDI_RXN7

FDI_RXP0

FDI_RXP1

FDI_RXP2

FDI_RXP3

FDI_RXP4

FDI_RXP5

FDI_RXP6

FDI_RXP7

FDI_INT

FDI_FSYNC0

FDI_FSYNC1

FDI_LSYNC0

FDI_LSYNC1

DSWVRMEN

DPWROK

WAKE#

(+3V)

(+3VS5)

(+3VS5)

(+3VS5)

SLP_S4#

SLP_S3#

SLP_A#

SLP_SUS#

PMSYNCH

(+3VS5)

4

3

2

1

Cougar Point/Panther Point (LVDS,DDI)

BJ14

AY14

BE14

BH13

BC12

BJ12

BG10

BG9

BG14

BB14

BF14

BG13

BE12

BG12

BJ10

BH9

AW16

AV12

BC10

AV14

BB10

A18

E22

B9

N3

G8

N14

D10

H4

F4

G10

G16

AP14

K14

DSWVREN

RSMRST#

AP_STAT

PT

FDI_TXN0 06

FDI_TXN1 06

FDI_TXN2 06

FDI_TXN3 06

FDI_TXN4 06

FDI_TXN5 06

FDI_TXN6 06

FDI_TXN7 06

FDI_TXP0 06

FDI_TXP1 06

FDI_TXP2 06

FDI_TXP3 06

FDI_TXP4 06

FDI_TXP5 06

FDI_TXP6 06

FDI_TXP7 06

FDI_INT 06

FDI_FSYNC0 06

FDI_FSYNC1 06

FDI_LSYNC0 06

FDI_LSYNC1 06

R422 330K_4

On Die DSW VR Enable

High = Enable (Default)

Low = Disable

PCIE_WAKE# 27,30

CLKRUN# 32

Audience Feature Enable

High = Enable (Default)

Low = Disable

SLP_S5 32

SUSC# 32

SUSB# 32

PM_SYNC 06

+3V_RTC

PCH_LVDS_BLON24

PCH_DISP_ON24

PCH_DPST_PWM24

PCH_EDIDCLK24

PCH_EDIDDATA24

+3V

PCH_LA_CLK#24

PCH_LA_CLK24

PCH_LA_DATAN024

PCH_LA_DATAN124

PCH_LA_DATAN224

PCH_LA_DATAP024

PCH_LA_DATAP124

PCH_LA_DATAP224

PCH_LB_CLK#24

PCH_LB_CLK24

PCH_LB_DATAN024

PCH_LB_DATAN124

PCH_LB_DATAN224

PCH_LB_DATAP024

PCH_LB_DATAP124

PCH_LB_DATAP224

R122 2.2K_4

R128 2.2K_4

R97 2.37K/F_4

CTRL_CLK

CTRL_DATA

LVD_IBG

DAC_IREF

R126

1K/F_4

U23D

CPT_PPT_Rev_0p7

J47

M45

P45

T40

K47

T45

P39

AF37

AF36

AE48

AE47

AK39

AK40

AN48

AM47

AK47

AJ48

AN47

AM49

AK49

AJ47

AF40

AF39

AH45

AH47

AF49

AF45

AH43

AH49

AF47

AF43

N48

P49

T49

T39

M40

M47

M49

T43

T42

L_BKLTEN

L_VDD_EN

L_BKLTCTL

L_DDC_CLK

L_DDC_DATA

L_CTRL_CLK

L_CTRL_DATA

LVD_IBG

LVD_VBG

LVD_VREFH

LVD_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSA_DATA#0

LVDSA_DATA#1

LVDSA_DATA#2

LVDSA_DATA#3

LVDSA_DATA0

LVDSA_DATA1

LVDSA_DATA2

LVDSA_DATA3

LVDSB_CLK#

LVDSB_CLK

LVDSB_DATA#0

LVDSB_DATA#1

LVDSB_DATA#2

LVDSB_DATA#3

LVDSB_DATA0

LVDSB_DATA1

LVDSB_DATA2

LVDSB_DATA3

CRT_BLUE

CRT_GREEN

CRT_RED

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_VSYNC

DAC_IREF

CRT_IRTN

SDVO_INTN

SDVO_INTP

DDPB_HPD

DDPB_0N

DDPB_0P

DDPB_1N

DDPB_1P

DDPB_2N

DDPB_2P

DDPB_3N

DDPB_3P

DDPC_HPD

DDPC_0N

DDPC_0P

DDPC_1N

DDPC_1P

DDPC_2N

DDPC_2P

DDPC_3N

DDPC_3P

DDPD_HPD

DDPD_0N

DDPD_0P

DDPD_1N

DDPD_1P

DDPD_2N

DDPD_2P

DDPD_3N

DDPD_3P

AP43

AP45

AM42

AM40

AP39

AP40

P38

M39

AT49

AT47

AT40

AV42

AV40

AV45

AV46

AU48

AU47

AV47

AV49

P46

P42

AP47

AP49

AT38

AY47

AY49

AY43

AY45

BA47

BA48

BB47

BB49

M43

M36

AT45

AT43

BH41

BB43

BB45

BF44

BE44

BF42

BE42

BJ42

BG42

SDVO_CLK 24

SDVO_DATA 24

HDMI_HPD_CON 24

IN_D2# 24

IN_D2 24

IN_D1# 24

IN_D1 24

IN_D0# 24

IN_D0 24

IN_CLK# 24

IN_CLK 24

SDVO_TVCLKINN

SDVO_TVCLKINP

SDVO_STALLN

SDVO_STALLP

SDVO_CTRLCLK

SDVO_CTRLDATA

DDPB_AUXN

DDPB_AUXP

LVDS

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPC_AUXN

DDPC_AUXP

Digital Display Interface

DDPD_CTRLCLK

DDPD_CTRLDATA

DDPD_AUXN

CRT

DDPD_AUXP

10

INT. HDMI

R126 Change 5%

PCH Pull-high/low(CLG)

+3VS5

PM_RI#

PM_BATLOW#

PCIE_WAKE#

SUS_PWR_ACK

AC_PRESENT_R

AP_STAT

PT

A A

PT

CLKRUN#

XDP_DBRST#

AP_STAT

RSMRST#

IMVP_PWRGD

R419 10K/F_4

R188 8.2K_4

R418 10K/F_4

R192 10K/F_4

R195 10K/F_4

R457 10K/F_4

+3V

R370 8.2K_4

R131 1K/F_4

R459 *10K/F_4_NC

R425 10K/F_4

R127 *100K/F_4_NC

5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Friday, November 02, 2012 10 46

Friday, November 02, 2012 10 46

Friday, November 02, 2012 10 46

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

PROJECT :

PCH 1/6 (Host/Display)

PCH 1/6 (Host/Display)

PCH 1/6 (Host/Display)

JW8

JW8

JW8

3A

3A

3A

of

of

1

of

5

Cougar Point/Panther Point (HDA,JTAG,SATA)

CLKGEN_RTC_X125

D D

+3V_RTC

TP33

R155 1M_4

SPKR26

ACZ_SDIN026

RTC_RST#

SRTC_RST#

SM_INTRUDER#

PCH_INVRMEN

ACZ_BCLK

ACZ_SYNC

ACZ_RST#

PCH_MELOCK?? Pin A36

ACZ_SDOUT

PT

GPIO33

R123 10K/F_4

C C

+3VS5

GPIO13

Test Point??

PCH_SPI_CLK32

PCH_SPI_CS1#32

PCH_SPI_SI32

PCH_SPI_SO32

PCH_SPI_CS0#

U23A

CPT_PPT_Rev_0p7

A20

RTCX1

C20

RTCX2

D20

RTCRST#

G22

SRTCRST#

K22

INTRUDER#

C17

INTVRMEN

N34

HDA_BCLK

L34

HDA_SYNC

T10

SPKR

K34

HDA_RST#

E34

HDA_SDIN0

G34

HDA_SDIN1

C34

HDA_SDIN2

A34

HDA_SDIN3

A36

HDA_SDO

(+3V)

C36

HDA_DOCK_EN# / GPIO33

(+3VS5)

N32

HDA_DOCK_RST# / GPIO13

J3

JTAG_TCK

H7

JTAG_TMS

K5

JTAG_TDI

H1

JTAG_TDO

T3

SPI_CLK

Y14

SPI_CS0#

T1

SPI_CS1#

V4

SPI_MOSI

U3

SPI_MISO

JTAG

RTCIHDA

SPI

4

FWH0 / LAD0

FWH1 / LAD1

FWH2 / LAD2

FWH3 / LAD3

LPC

FWH4 / LFRAME#

LDRQ0#

LDRQ1# / GPIO23

(+3V)

SERIRQ

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA 6G

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA4RXN

SATA4RXP

SATA4TXN

SATA

SATA4TXP

SATA5RXN

SATA5RXP

SATA5TXN

SATA5TXP

SATAICOMPO

SATAICOMPI

SATA3RCOMPO

SATA3COMPI

SATA3RBIAS

SATALED#

(+3V)

SATA0GP / GPIO21

(+3V)

SATA1GP / GPIO19

C38

A38

B37

C37

D36

E36

K36

V5

AM3

AM1

AP7

AP5

AM10

AM8

AP11

AP10

AD7

AD5

AH5

AH4

AB8

AB10

AF3

AF1

Y7

Y5

AD3

AD1

Y3

Y1

AB3

AB1

Y11

Y10

AB12

AB13

AH1

P3

V14

P1

SATA_COMP

SATA3_COMP

SATA3_RBIAS

BBS_BIT0

R357 *10K/F_4_NC

LAD0 30,32

LAD1 30,32

LAD2 30,32

LAD3 30,32

LFRAME# 30,32

R107 8.2K_4

SATA_RXN0 31

SATA_RXP0 31

SATA_TXN0 31

SATA_TXP0 31

SATA_RXN1 31

SATA_RXP1 31

SATA_TXN1 31

SATA_TXP1 31

R106 37.4/F_4

R104 49.9/F_4

R345 750/F_4

R352 10K/F_4

R96 10K/F_4

+3V

3

+3V

SERIRQ 32

HDD0 (SATA3 6.0Gb/s)

mSATA (SATA3 6.0Gb/s)

DG recommended that AC coupling capacitors should be

close to the connector (<100 mils) for optimal signal quality.

+1.05V

SATA_LED# 30

+3V

2

R168 10K/F_4

+5V

C409

10P/50V_4

R182 33_4

ACZ_SYNC_AUDIO26

R181

ACZ_SYNC_R1

1M_4

RTC Circuitry(RTC)

+3V_RTC_0

PT

CN1

1

2

BAT_CONN

C507

1U/6.3V_4

2

Q11

1

PT

2N7002K

3

ACZ_SYNC

30mils

+3V_RTC

RTC Power trace width 20mils.

R424

20K/F_4

R170

20K/F_4

C423

1U/6.3V_4

1

11

RTC_RST#

C636

1U/6.3V_4

SRTC_RST#

C425

1U/6.3V_4

HDA Bus(CLG)

ACZ_RST#_AUDIO26

ACZ_SDOUT_AUDIO26

BIT_CLK_AUDIO26

R197 33_4

R415 33_4

R171 33_4

C414

22P/50V_4

ACZ_RST#

ACZ_SDOUT

ACZ_BCLK

B B

A A

PCH Strap Table

Pin Name Strap description Sampled Configuration

SPKR

GNT3# / GPIO55 Top-Block Swap Override

No reboot mode setting PWROK

PWROK

INTVRMEN Integrated 1.05V VRM enable ALWAYS

HDA_DOCK_EN#/GPIO33

GNT1# / GPIO51

GPIO19

Different from

Calpella

GNT2# / GPIO53

NV_ALE

NV_CLE

Flash Descriptor Security

Only for Interposer

Boot BIOS Selection 1 [bit-1]

Boot BIOS Selection 0 [bit-0]

ESI strap (Server only)

Intel Anti-Theft HDD protection

Only for Interposer

DMI Termination voltage weak pull-down 20kohm

PWROK

PWROK

PWROK

PWROK

PWROK

PWROK

HDA_SYNC On-Die PLL VR Voltage Select RSMRST

HDA_SDO PWROKFlash Descriptor Security

GPIO8

GPIO28

Different from

Calpella

Integrated Clock Chip Enable Should be pull-down (weak pull-up 20K)RSMRST#

On-die PLL Voltage Regulator RSMRST#

SPI_MOSI iTPM function Disable APWROK

5

0 = Default (weak pull-down 20K)

1 = Setting to No-Reboot mode

0 = "top-block swap" mode

1 = Default (weak pull-up 20K)

Should be always pull-up

0 = Override

1 = Default (weak pull-up 20K)

Should not be pull-down

(weak pull-up 20K)

0 = Disable (Internal pull-down 20kohm)

0 = Support by 1.8V (weak pull-down)

1 = Support by 1.5V

0 = Override

1 = Default (weak pull-up 20K)

0 = Disable

1 = Enable (Default)

0 = Default (weak pull-down 20K)

1 = Enable

4

Circuit

Vender

R387 10K/F_4

+3V

+3V_RTC

GNT0#GNT1#

Boot Location

11

SPI

00

LPC

R423 330K_4

GPIO33

R444 *1K/F_4_NC

[Need external pull-down for LPC BIOS]

Default weak pull-up on GNT0/1#

R356 *1K/F_4_NC

R381 *1K/F_4_NC

PCI_GNT3# 12

PCH_INVRMEN

ACZ_SDOUT 32

BBS_BIT0

PT

BBS_BIT1 12

AMIC

GGD

USE GPIO PIN

+1.8V

+3VS5

+3VS5

R343 2.2K_4

R164 1K/F_4

R445 *1K/F_4_NC

R344 1K/F_4

3

ACZ_SYNC

ACZ_SDOUT

PT

NV_CLE 13

H_SNB_IVB# 06

Size

P/N

2MB AKE38ZN0802 (A25LQ16M-F/Q)

2MB AKE38GN0Q00 (GD25Q16BSIGR)

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_SI PCH_SPI1_SI_R

PCH_SPI_SO

2

QT

R340 *0_4/S

R382 33_4

R377 33_4

R341 33_4

R342 3.3K_4

+3V

PCH_SPI_CS0#_R

PCH_SPI1_CLK_R

PCH_SPI1_SO_R

C618

22P/50V_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Friday, November 02, 2012 11 46

Friday, November 02, 2012 11 46

Friday, November 02, 2012 11 46

Date: Sheet

Date: Sheet

Date: Sheet

PCH SPI ROM(CLG)

U22

1

CE#

6

SCK

5

SI

2

SO

3

WP#

A25LQ16M-F/Q

8

VDD

7

R374 3.3K_4

HOLD#

4

VSS

PCH_SPI_CS0#_R

PCH_SPI1_CLK_R

PCH_SPI1_SI_R

PCH_SPI1_SO_R

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

PCH 2/6 (HDA/RTC/SATA/SPI)

PCH 2/6 (HDA/RTC/SATA/SPI)

PCH 2/6 (HDA/RTC/SATA/SPI)

0.1U/10V_4

JW8

JW8

JW8

1

C615

TP25

TP28

TP29

TP26

+3V

3A

3A

3A

of

of

of

5

PCI/USBOC# Pull-up(CLG)

1

2

3

56

USB30_RX1-29

USB30_RX2-29

USB30_RX4-29

USB30_RX1+29

USB30_RX2+29

USB30_RX4+29

USB30_TX1-29

USB30_TX2-29

USB30_TX4-29

USB30_TX1+29

USB30_TX2+29

USB30_TX4+29

R140 22_4

R139 22_4

R145 22_4

C391

18P/50V_4

+3V

USB_OC6#

USB_OC0#

USB_OC7#

USB_OC5#

EMI(near PCH)

PCI_PIRQA#

R178 8.2K_4

PCI_PIRQB#

R177 8.2K_4

PCI_PIRQC#

R175 8.2K_4

PCI_PIRQD#

R172 8.2K_4

PCH_GPIO4

MPC_PWR_CTRL#

BT_COMBO_EN#

D D

LCD_BK

PCH_GPIO52

PCH_GPIO54

INT_H

USB_OC4#

USB_OC1#

USB_OC2#

USB_OC3#

R395 10K/F_4

R151 10K/F_4

R391 10K/F_4

R176 10K/F_4

R179 10K/F_4

R174 10K/F_4

R351 10K/F_4

QT.Close to CN2

+3VS5

RP6

10

9

8

7 4

10K_10P8R_6

USB3.0

C C

BBS_BIT111

PCI_GNT3#11

LCD_BK24

INT_H33

B B

CLK_33M_DEBUG30

CLK_33M_KBC32

CLK_PCI_FB

C382

18P/50V_4

PLTRST#06,19,27,28,30,32

Cougar Point-M/Panther Point (PCI,USB,NVRAM)

PCI_PIRQA#

PCI_PIRQB#

PCI_PIRQC#

PCI_PIRQD#

BT_COMBO_EN#

PCH_GPIO52

PCH_GPIO54

MPC_PWR_CTRL#

PCH_GPIO4

R393 100K/F_4

CLK_PCI_FB_R

CLK_PCI_LPC_R

CLK_PCI_EC_R

U23E

CPT_PPT_Rev_0p7

BG26

BJ26

BH25

BJ16

BG16

AH38

AH37

AK43

AK45

C18

N30

H3

AH12

AM4

AM5

Y13

K24

L24

AB46

AB45

B21

M20

AY16

BG46

BE28

BC30

BE32

BJ32

BC28

BE30

BF32

BG32

AV26

BB26

AU28

AY30

AU26

AY26

AV28

AW30

K40

K38

H38

G38

C46

C44

E40

D47

E42

F46

G42

G40

C42

D44

K10

C6

H49

H43

J48

K42

H40

TP1

TP2

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

TP12

TP13

TP14

TP15

TP16

TP17

TP18

TP19

TP20

TP21

TP22

TP23

TP24

USB3Rn1

USB3Rn2

USB3Rn3

USB3Rn4

USB3Rp1

USB3Rp2

USB3Rp3

USB3Rp4

USB3Tn1

USB3Tn2

USB3Tn3

USB3Tn4

USB3Tp1

USB3Tp2

USB3Tp3

USB3Tp4

PIRQA#

PIRQB#

PIRQC#

PIRQD#

REQ1# / GPIO50

REQ2# / GPIO52

REQ3# / GPIO54

GNT1# / GPIO51

GNT2# / GPIO53

GNT3# / GPIO55

PIRQE# / GPIO2

PIRQF# / GPIO3

PIRQG# / GPIO4

PIRQH# / GPIO5

PME#

PLTRST#

CLKOUT_PCI0

CLKOUT_PCI1

CLKOUT_PCI2

CLKOUT_PCI3

CLKOUT_PCI4

RSVD

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

PCI

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

SMBus/Pull-up(CLG)

Q28

MBCLK218,22,32,33

MBDATA218,22,32,33

A A

+3V

SMB_RUN_DAT18,25

+3V

SMB_RUN_CLK18,25

5

4 3

1

2N7002DW

R432 4.7K_4

R401 4.7K_4

Q27

4 3

1

2N7002DW

4

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

USBP0N

USBP0P

USBP1N

USBP1P

USBP2N

USBP2P

USBP3N

USBP3P

USBP4N

USBP4P

USBP5N

USBP5P

USBP6N

USBP6P

USBP7N

USBP7P

USBP8N

USBP8P

USBP9N

USBP9P

USBP10N

USBP10P

USB

USBP11N

USBP11P

USBP12N

USBP12P

USBP13N

USBP13P

USBRBIAS#

USBRBIAS

OC0# / GPIO59

OC1# / GPIO40

OC2# / GPIO41

OC3# / GPIO42

OC4# / GPIO43

OC5# / GPIO9

OC6# / GPIO10

OC7# / GPIO14

+3V +3VS5

5

R416 2.2K_4

SMB_ME1_CLK

2

R417 2.2K_4

6

SMB_ME1_DAT

+3V

5

SMB_PCH_DAT

2

6

SMB_PCH_CLK

4

AY7

AV7

AU3

BG4

AT10

BC8

AU2

AT4

AT3

AT1

AY3

AT5

AV3

AV1

BB1

BA3

BB5

BB3

BB7

BE8

BD4

BF6

AV5

AV10

AT8

AY5

BA2

AT12

BF3

C24

A24

C25

B25

C26

A26

K28

H28

E28

D28

C28

A28

C29

B29

N28

M28

L30

K30

G30

E30

C30

A30

L32

K32

G32

E32

C32

A32

C33

B33

A14

K20

B17

C16

L16

A16

D14

C14

WLAN

PCIE_RXN2_LAN27

USB3.0

USB3.0

Camera

USB3.0

BIOS Debug

WLAN

Touch Screen

R412

22.6/F_4

PCIE_RXP2_LAN27

PCIE_TXN2_LAN27

PCIE_TXP2_LAN27

PCIE_RXN3_CR28

PCIE_RXP3_CR28

PCIE_TXN3_CR28

PCIE_TXP3_CR28

Cardreader

Cardreader

PT

USB_BIAS

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

USB_OC4#

USB_OC5#

USB_OC6#

USB_OC7#

LAN

USBP0- 29

USBP0+ 29

USBP1- 29

USBP1+ 29

USBP2- 33

USBP2+ 33

USBP3- 29

USBP3+ 29

USBP9- 29

USBP9+ 29

USBP10- 30

USBP10+ 30

USBP12- 33

USBP12+ 33

CLK_REQ/Strap Pin(CLG)

PCIE_CLKREQ_LAN#

PCIE_CLKREQ_CR#

PCIE_CLKREQ_WLAN#

CLK_PCIE_REQ3#

CLK_PCIE_REQ4#

CLK_PEGB_REQ#

CLK_PEGA_REQ#

CLK_BUF_BCLK_N

CLK_BUF_BCLK_P

CLK_BUF_PCIE_3GPLL#

CLK_BUF_PCIE_3GPLL

CLK_BUF_DREFCLK#

CLK_BUF_DREFCLK

CLK_BUF_DREFSSCLK#

CLK_BUF_DREFSSCLK

CLK_PCH_14M

CLOCK TERMINATION for FCIM

PCIE_RXN130

PCIE_RXP130

PCIE_TXN130

PCIE_TXP130

WLAN

PCIE_CLKREQ_WLAN#30

LAN

PCIE_CLKREQ_LAN#27

PCIE_CLKREQ_CR#28

R373 10K/F_4

R103 10K/F_4

R389 10K/F_4

R397 10K/F_4

R189 10K/F_4

R147 10K/F_4

R141 10K/F_4

R338 10K/F_4

R337 10K/F_4

R334 10K/F_4

R333 10K/F_4

R137 10K/F_4

R148 10K/F_4

R81 10K/F_4

R80 10K/F_4

R132 10K/F_4

C232 0.1U/10V_4

C231 0.1U/10V_4

C250 0.1U/10V_4

C254 0.1U/10V_4

C233 0.1U/10V_4

C234 0.1U/10V_4

CLK_PCIE_WLANN30

CLK_PCIE_WLANP30

CLK_PCIE_LANN27

CLK_PCIE_LANP27

CLK_PCIE_CRN28

CLK_PCIE_CRP28

INT_BT_COMBO_EN#30

+3V

+3VS5

3

BOARD_ID013

3

2

Cougar Point-M/Panther Point (PCI-E,SMBUS,CLK)

PCIE_TXN1_C

PCIE_TXP1_C

PCIE_TXN2_LAN_C

PCIE_TXP2_LAN_C

PCIE_TXN3_CR_C

PCIE_TXP3_CR_C