Page 1

5

4

3

2

1

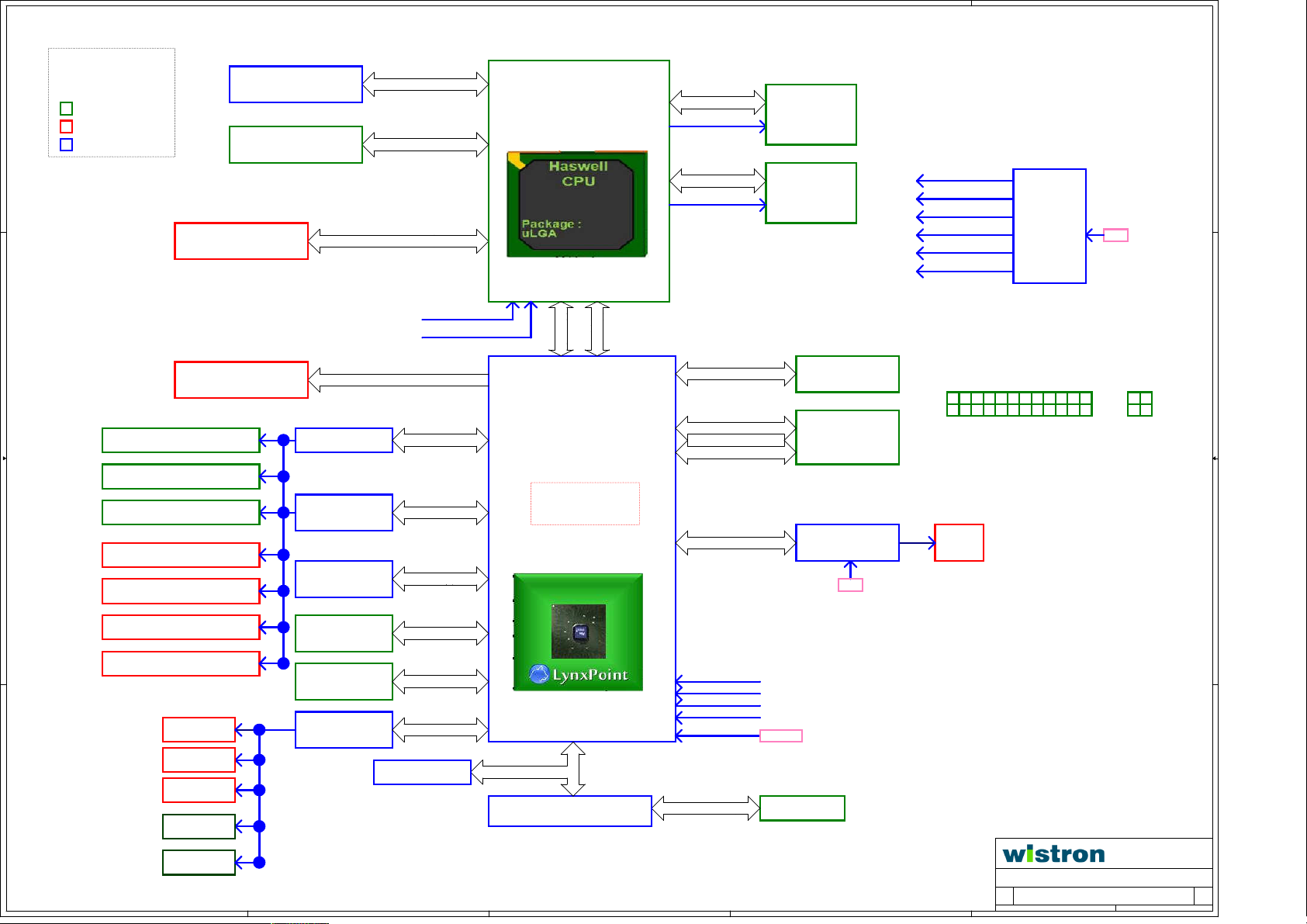

Shark Bay Platform

PCB Version

Project name

Project Code

D D

PCB Number

PCB Size

PCB P/N 48.3KZ06.011

SCH Ver A00

-1

General-SFF

91.3KZ01.001

12127

244mmX 200mm, t=1.6mm, 4-layers

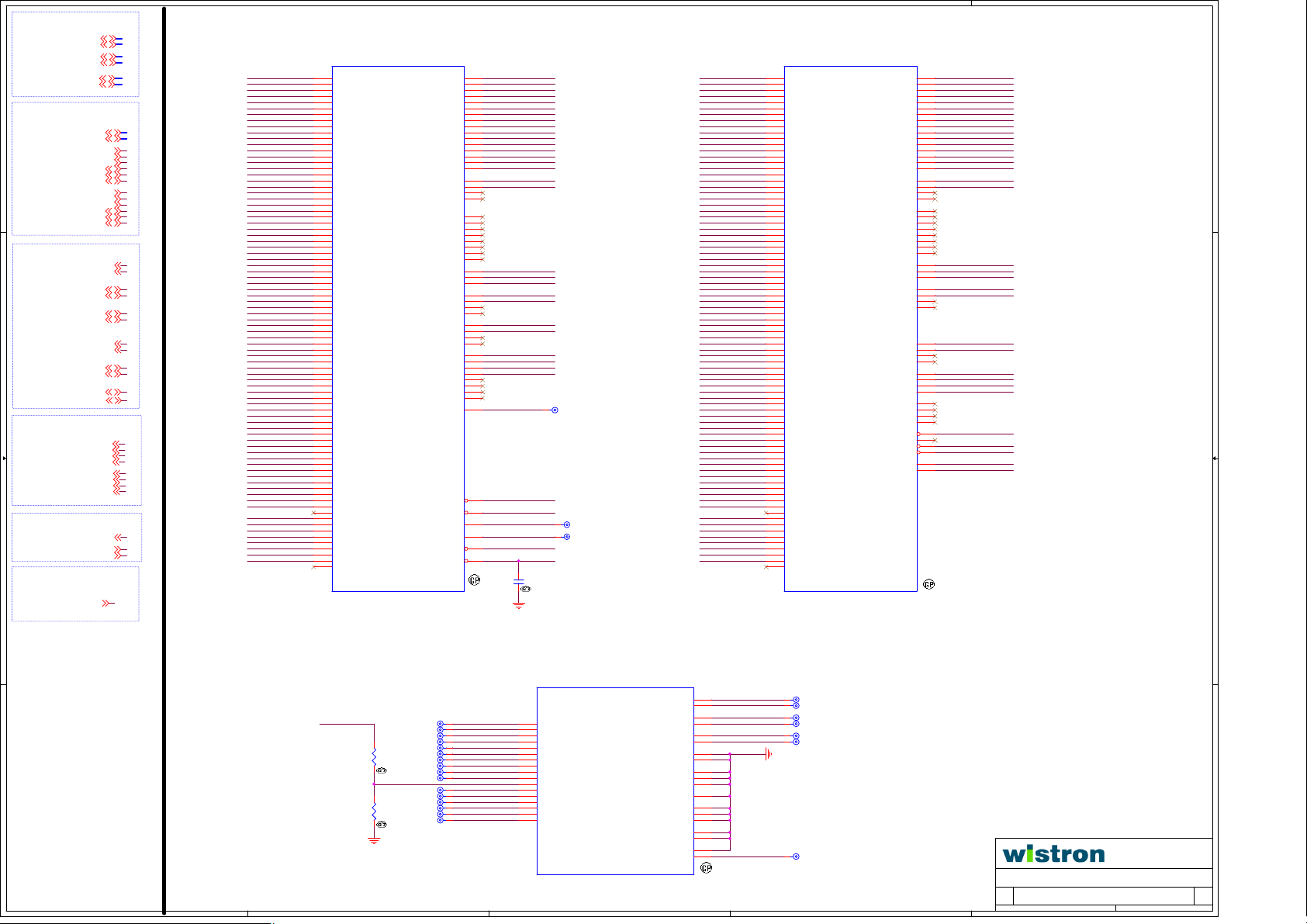

On Board Header and Jump setting

CONN DESCRIPTION

CMCLR1 1-3 Reset CMOS data (Debug Only)

PWCLR1

USBF3

USBF1

C C

FNCPU1

XDPC1

LPC1

LEDH1 2X6 Front Panel Header

USBF2 2X5 pin USB2.0 header

ATX12V 2X2 ATX12V POWER CONN

Default

1-3

FOR AUD_LINK_SDO_R ENABLE AND FLASH1-XMECLR1

PASSWORD CLEAR

2X10 pin USB3.0 header

2X5 pin USB2.0 header

2X5 Front Panel Audio headerAUDF1

1X4 pin CPU FAN

2X12 ATX POWER CONNATX1

60 pin XDP connector for CPU

2X7 LPC debug port header (Debug Only)

Board ID

[4..1] Description

1110

B B

Major IC version/part number/vender

FUNCTION Description Version WST P/N Vendor

PCH

Realtek Lan 71.08151.M06 REALTEKIC LAN RTL8151GD-CG QFN 32P(DELL)

SIO

IC SUPER IO IT8772E/EX LQFP 64P

Audio Codec

IC AUDIO CODEC ALC3600-CG LQFP 48P

C1

71.08772.B0G

71.03600.00G

INTEL

ITE

REALTEK

Index

PAGE

TITLE

01

Cover Page

02

BLOCK DIAGRAM

03 Power Delivery

POWER GOOD AND RESET DIAGRAM

04

CLOCKS DIAGRAM

05

06

Power Sequence

POWER Map

07

08

GPIO TABLE

09

TBD

CPU uLGA 1150_1

10

11

CPU uLGA 1150_2

12

CPU uLGA 1150_3

13

CPU uLGA 1150_4

14 XDP/80 PORT HEADER

15

DDR3 CHA DIMM 0

16

TBD

17

DDR3 CHB DIMM 0

18

TBD

19

Lynxpoint_AUDIO/GPIO/SPI

20

Lynxpoint_CLK

21

Lynxpoint_SATA/FAN/DP/VGA

22

Lynxpoint_FDI/PCIE/DMI/USB

Lynxpoint_GND/STRAPS

23

Lynxpoint_POWER

24

25

SATA Port

PCIEX16 CONNECTOR

26

VGA Port

27

28

HDMI Port

Display Port (TBD)

29

30

FRONT USB3.0&2.0 HEADER

31

USB+RJ45

32 TBD

33

REAR USB3.0

34

USB2.0

35

LAN RTL8151GD

36

AUDIO CODEC_ALC3600

AUDIO CODEC JACKS

37

38

TBD

39

SIO_ITE8772

40

FAN CIRCUITS/HOLE

TPM(NEW)

41

PCIEX1 CONNECTOR

42

MINI PCIE SLOT

43

EMC(TBD)

44

PWR/FNT PNL45

DUAL POWER

46

DDR POWER

47

SYSTEM POWER

48

TBD49

50 CPU_VRD 12-5_1

51 CPU_VRD 12-5_2

Quantity

BOM Configuration

Unmount:(R)

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

C

ROSA General-SFF

C

ROSA General-SFF

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

151Monday, September 09, 2013

151Monday, September 09, 2013

151Monday, September 09, 2013

-1A

-1A

-1A

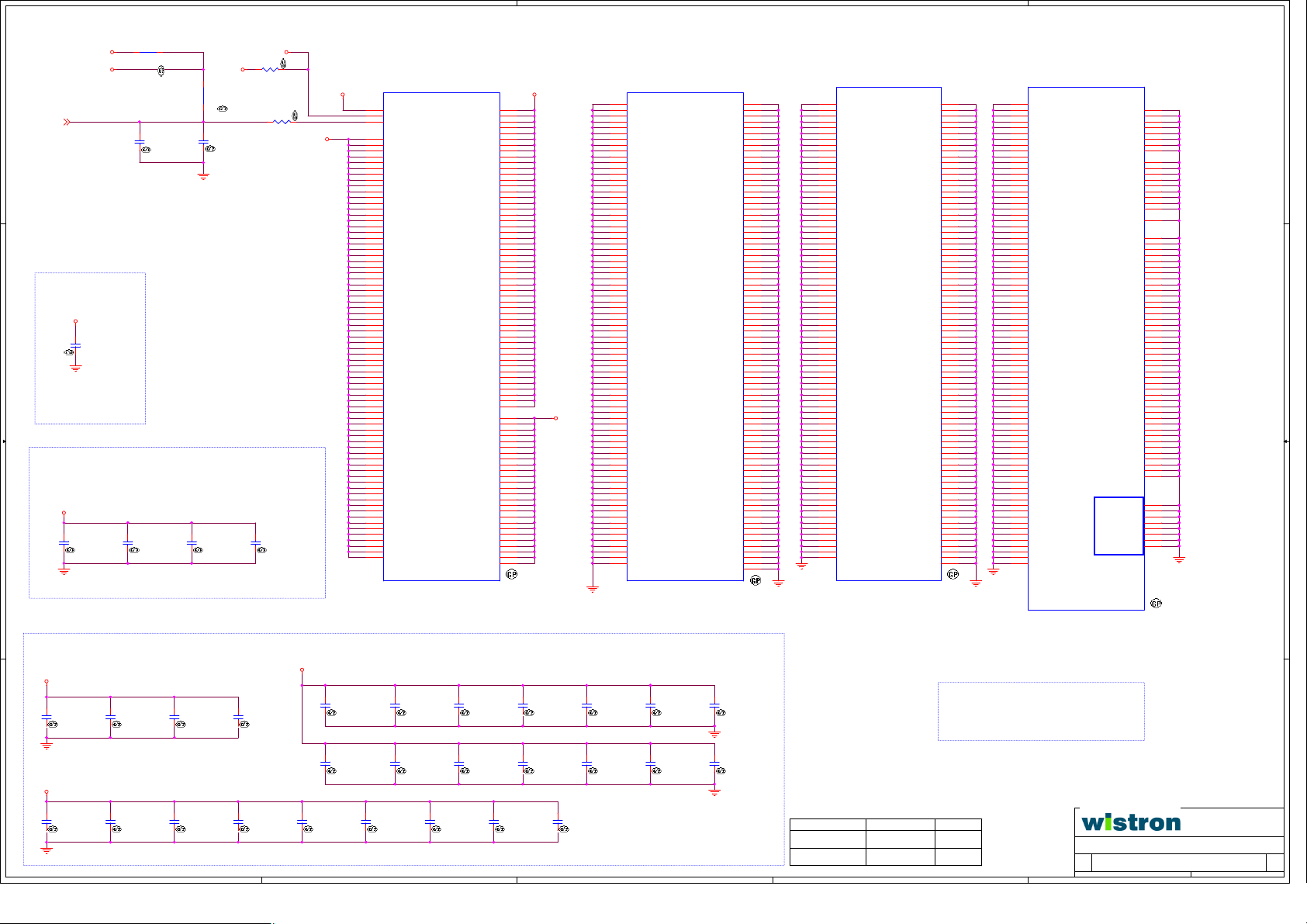

Page 2

5

PCB BOARD SIZE

200mmX 244mm

4 Layer

D D

Internal Slot/Header

Front/Rear IO

Chipset

VRM 12.5

( 3 Phase 95W)

PCIE_X16

HDMI PORT v1.4

4

PCI EXPRESS Gen3

Port C

3

INTEL

SOCKET H3 uLGA LGA1150

Haswell

(65W)

0.9144mmX0.9144mm

Channel A

64 bit

1600MHZ/1333MHZ

Channel B

64 bit

1600MHZ/1333MHZ

DDR3 DIMM

Unbuffered 4GB

DDR3 DIMM

Unbuffered 4GB

2

14.318MHz

33MHz

24MHz or 48MHz

100 MHz

120 MHz

133 MHz

PCH

CLOCK

Buffer

1

25M

100MHz

100MHz

C C

D-SUB PORT

USB3.0X1 FRONT HEADER

USB 3.0 *2

RGB

5.0Gb/S

FDI

DMI

INTEL PCH

Lynx Point

PCIE Port3

PCIE Gen1 Interface 2. 5Gbps

PCIE Port5

PCIE Gen1 Interface 2. 5Gbps

USB2.0X1

PCIE X1

MINI CARD

ATX-24PIN PWR CONN CPU-4PIN CONN

USB2.0X1 FRONT HEADER

FCBGA 708PIN

USB2.0X2 FRONT HEADER

USB 2.0 *10

USB2.0x2 REAR (+RJ45)

B B

USB3.0X1 REAR

USB2.0x2 REAR

SPI Flash ROM

8MB

SATA *HDD

USB2.0X1 REAR

SATA *ODD

REAR

Line - IN

REAR

Line - OUT

REAR

5

MIC -IN

FRONT

MIC -IN

FRONT

Line - OUT

A A

HDA CODEC

ALC3600

4

480Mb/S

SPI BUS

SATA3.0 BUS

SATA2.0 BUS

High Definition Audio

TPM/TCM

23 mm x 22 mm

LPC BUS

SIO IT8772

PCIE Port4

PCIE Gen1 Interface 2. 5Gbps

REALTEK LAN

RTL8111G

RJ45

25M

133MHz

100MHz

96MHz

14.318MHz

32.768KHz

LPC BUS

FAN CNTL

3

32.7K

CPU 1X4 FAN

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

C

ROSA General-SFF

C

ROSA General-SFF

C

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

251Thursday, August 15, 2013

251Thursday, August 15, 2013

251Thursday, August 15, 2013

-1A

-1A

-1A

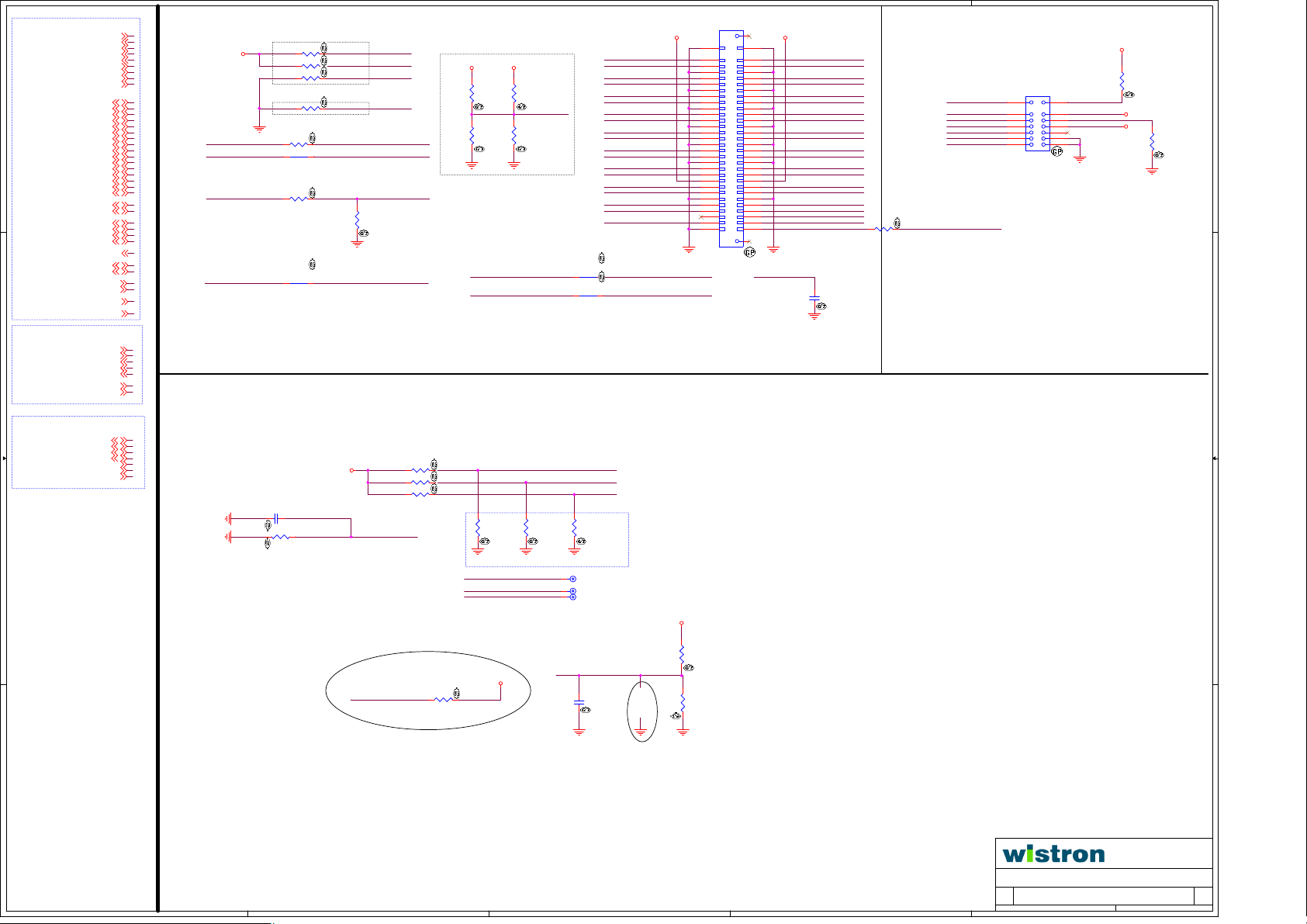

Page 3

5

4

3

2

1

CPU 2X2 POWER CONN

VCC12CPU

D D

Peak 18A

Continue 14A

PWM

NCP81102

NCP81161*3

3 Phase Design

SIR172DP*6

SIRA12DP*6

V_CPU_CORE

TDC=85A

Imax=112A

ATX 2X12 POWER CONN

V_SM

SB3V

LM358 AO4468

C C

+12V

VCC

10 A

14 A

N-MOSFETCOMP

V_1P05_PCH

TDC=6.2A

Imax=6.2A

1 Phase Design

VCC5A

1A

VCC3

19 A

-12V

0.2A

B B

SWITCH

N-MOSFET

P-MOSFET

SWITCH

N-MOSFET

P-MOSFET

SWITCH

N-MOSFET

P-MOSFET

P-MOSFET

DMP2130L-7

LDO

APL1085

LDO

APL5930

5V_DUAL

TDC= ?A

Imax= 13.3A

5VDUAL_USB_R

TDC= ?A

Imax=1A+3.6A

5VDUAL_USB_F

TDC= ?A

Imax= 1+1.8A

SB5V

TDC= ?A

Imax= 1.5A

V_3P3_A

TDC= 1.5A

Imax= 6A

V_1P5_PCH V_1P5_DAC_FB

Imax=0.35A

PWM

RT8120DGSP

RT8015AGQW

P-MOSFET SB3V

DMP2130L-7

TDC=?A

Imax=0.1A

AOD452AL*1

AOD472AL*1

V_1P05_MEPWM

TDC=?A

Imax=1A

TDC= 1.5A

Imax= 1.5A

V_SM

2 channel

TDC=?A APL5337

Imax=25A

LDO

BATTERY

SWITCH V_3P3_EPW

SWITCH V_3P3_PCIVAUX

N-MOSFET

P-MOSFET

SWITCH V_3P3_LAN

N-MOSFETTDC=?A

P-MOSFET

DIODE

BAS40C

TDC= ?AP-MOSFET

Imax= 0.016A

TDC= ?A

Imax= 1.5A

TDC= ?A

Imax= 0.218A

V_SM_VTT

TDC=1.1A

Imax=1.1A

V_3P0_BAT_VERG

TDC=6 uA

Imax=6 uA

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Power Delivery

Power Delivery

Power Delivery

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

C

ROSA General-SFF

C

ROSA General-SFF

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

351Thursday, August 15, 2013

351Thursday, August 15, 2013

351Thursday, August 15, 2013

-1A

-1A

-1A

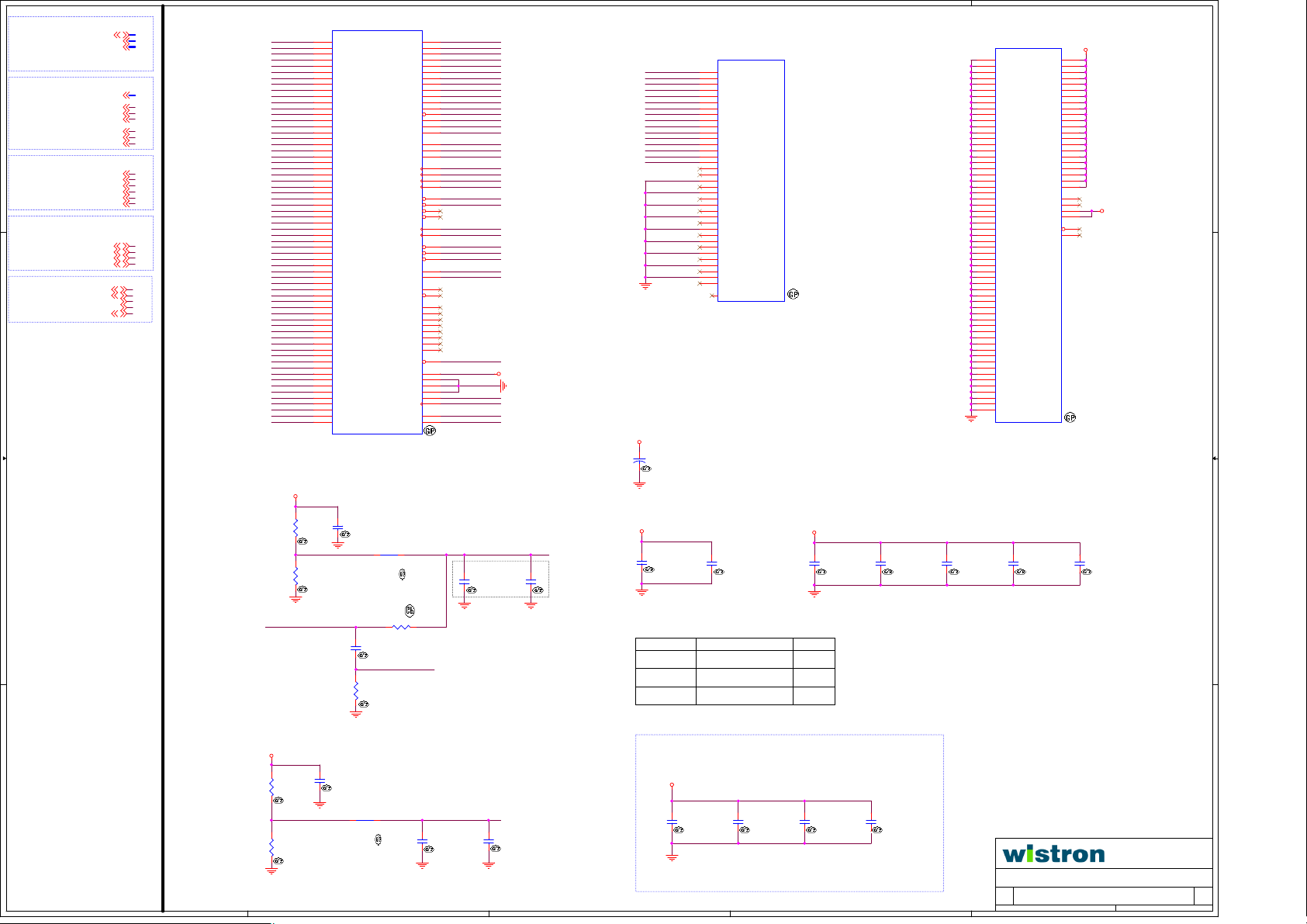

Page 4

5

4

3

2

1

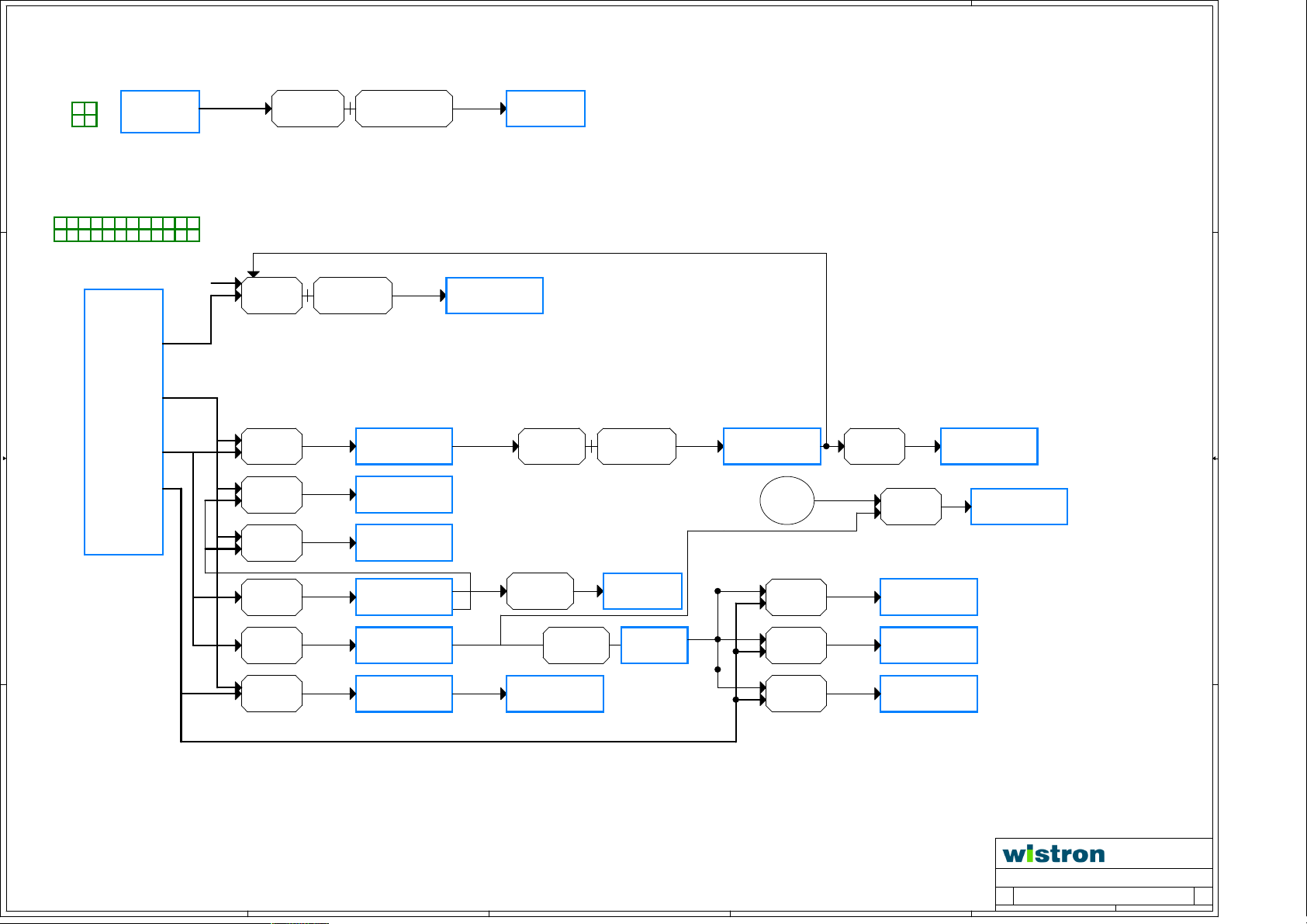

RESET / Power Good MAP

CPU-Haswell

D D

PWRGOOD

(9)

C C

(9)

ME POWER-GOOD

PCH_MEPWRGD

Power Botton

PWRBTN_N

RES

(1)

(7)

(2)

APWROK

PWRBTN#

SYS_RESET#

PCH

PROCPWRGD

DRAMPWRGD

SLP_S4#

SLP_S3#

PLTRST_PROC#

PLTRST#

B B

VR12.5

VR_RDY

(10)

SYS_PWROK

HD AUDIO

ALC3600

RESET#

(13)

HDA_RST#

AND

RSMRST#

PWROK

GPIO20

SM_DRAMPWROK

RESET*

(8) (8)

(8)

(3)

(4)

(1)

(2)

PANSWH#

PWRON#

SUSC#

SIO IT8772E

SUSB#

(11a)

(11b)

(2)

(3) IO_SMI_N

(7)

LRESET#

RSMRST#

PWRGD3

GP22

SM_DRAMRST*

PCIRST1#

PCIRST3#

PSON#

ATXPG

(12)

(12)

(6)

(8)

(9)

(2)

DDRIII Slots

D3_RESET#

CPU-XDP

LAN RT8111G

PERST#

Mini-PCIe

PERST#

PCI-E X1 Slot

PERST#

PCI-E X16 Slot

PERST#

TPM

PERST#

(5)

ATX Power

PSON

PWROK

PROCPWRGD

PWROK

A A

5

>1ms

4

3

PWRGD3

ATXPG

2

100~120ms

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

RESET / Power Good MAP

RESET / Power Good MAP

RESET / Power Good MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

C

ROSA General-SFF

C

ROSA General-SFF

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

451Thursday, August 15, 2013

451Thursday, August 15, 2013

451Thursday, August 15, 2013

-1A

-1A

-1A

Page 5

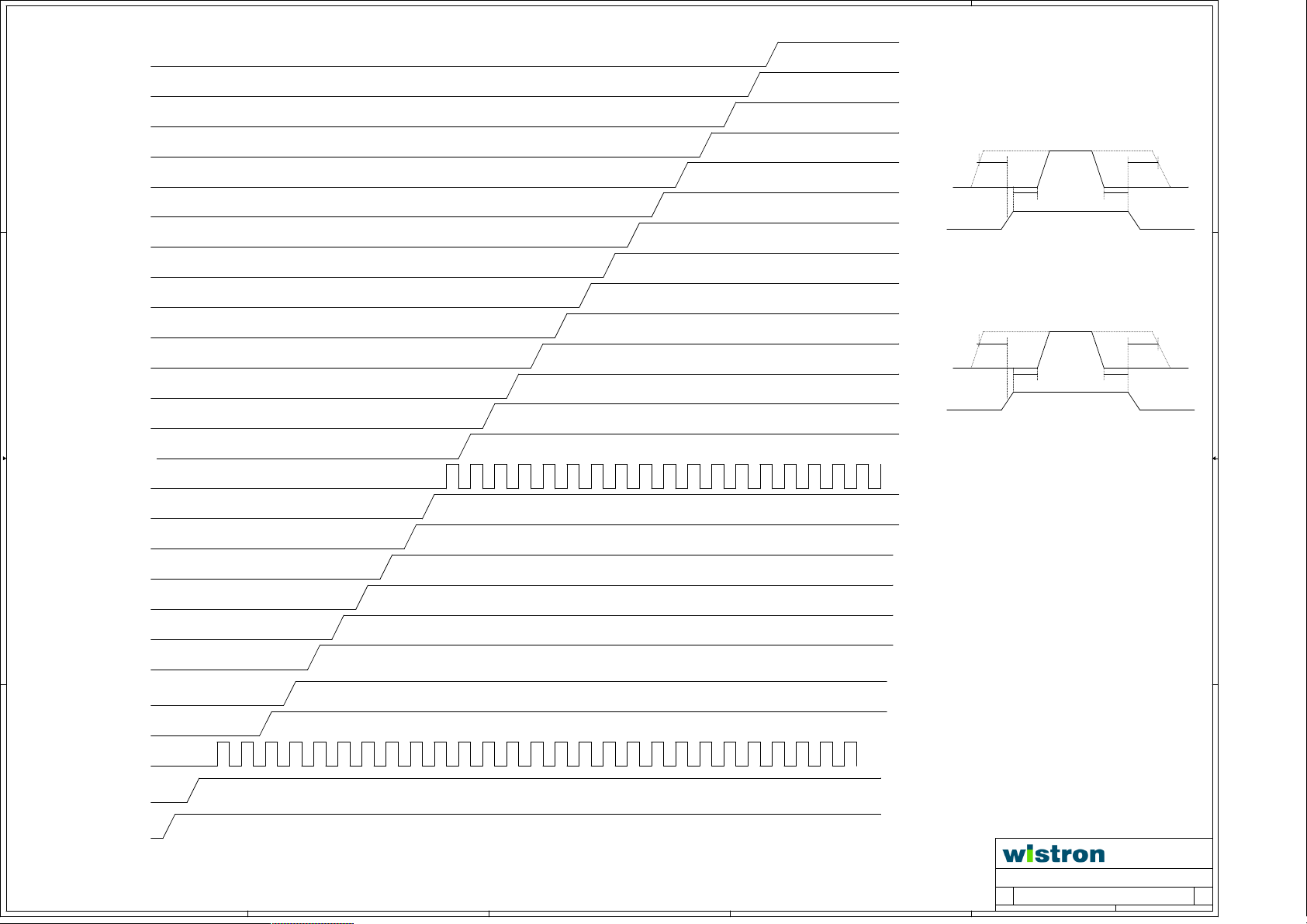

5

www.vinafix.vn

Intel PCH

CLKIN_GND0_N

CLKIN_GND0_P

Rs

4

3

2

1

D D

C C

B B

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

CLKOUT_DMI_N

CLKOUT_DMI_P

CLKOUT_DP_N

CLKOUT_DP_P

CLKOUT_PCIE0N

CLKOUT_PCIE0P

CLKOUT_PCIE1N

CLKOUT_PCIE1P

CLKOUT_PCIE2N

CLKOUT_PCIE2P

CLKOUT_PCIE3N

CLKOUT_PCIE3P

CLKOUT_PCIE4N

CLKOUT_PCIE4P

CLKOUT_PCIE5N

CLKOUT_PCIE5P

CLKOUT_PCIE6N

CLKOUT_PCIE6P

CLKOUT_PCIE7N

CLKOUT_PCIE7P

CLKOUT_PEG_A_N

CLKOUT_PEG_A_P

CLKOUT_PEG_B_N

CLKOUT_PEG_B_P

CLKOUT_33MHZ0

CLKOUT_33MHZ1

CLKOUT_33MHZ2

CLKIN_33MHZLOOPBACK

CLKOUT_33MHZ3

100MHz

100MHz

135MHz

100MHz

100MHz

100MHz

100MHz

Rs

Rs

Rs

Rs

CK_XDP/

CK_XDP#

CPU BCLK/

CPU BCLK#

SSC_DPLL_REF_CLK#

SSC_DPLL_REF_CLK

Realtek LAN

MINI PCIEX1

PCIEX1

PCIE_X16

LPC PORT80

TPM

SIO IT8772

25MHz

Intel

PCH

SMB_CLK_RESUME

SMB_DATA_RESUME

SMLICLK_PCH

SMLIDATA_PCH

MINI PCIEX1

PCIEX1

PCIEX16

SIO IT8772

SMB_CLK_MAIN

SMB_DATA_MAIN

DDR3

XDP CONN

CLKOUT_33MHZ4

CLKOUTFLEX0

CLKOUTFLEX1

XTAL25_OUT

XTAL25_IN

25MHz

RTCX1

RTCX2

A A

32.768KHz

CLKOUTFLEX2

CLKOUTFLEX3

REFCLK14IN

CLKIN_DOT_96N

CLKIN_DOT_96P

CLKIN_SATA_N

CLKIN_SATA_P

CLKIN_DMI_N

CLKIN_DMI_P

Note: .... is Reserve

Note: Rs is series resister

5

Rs

Rs

TPM

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Clock Diagram

Clock Diagram

Clock Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

C

ROSA General-SFF

C

ROSA General-SFF

C

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

551Thursday, August 15, 2013

551Thursday, August 15, 2013

551Thursday, August 15, 2013

-1A

-1A

-1A

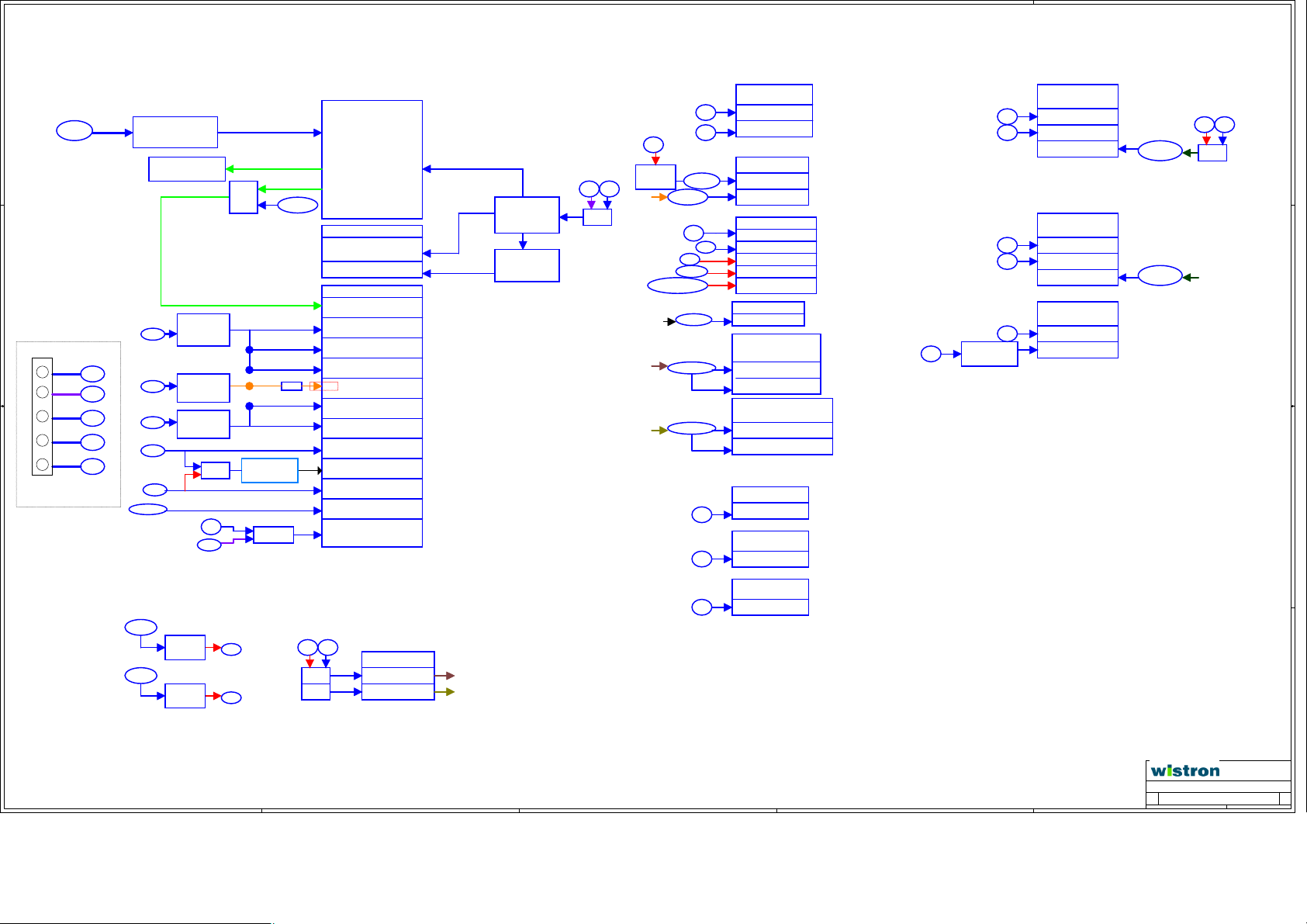

Page 6

5

POWER ON SEQUENCE

DMI Message

4

3

2

1

PLTRST

D D

H_PWRGD

H_DRAMPWRGD

PWRGD_3V

PCH_SYSPWROK

Sequencing Requirements between

PCH VCC3_3 and VCC Core Rail

3.3V

2.6V

<=25ms

0.6V

NO LIMIT

NO SLEW RATE

REQUIRENT

1.05V PCH

NO SLEW RATE

REQUIRENT

<=35ms

NO LIMIT

2.6V

PSPWRGD

V_CPU_CORE

V_1P5_PCH/

V_1P05_PCH

SLP_S3_N

V_SM

C C

SLP_S4_N

+12/VCC/VCC3

PS_ON_N

SIO_PSON*

Sequencing Requirements between

PCH VCC3_3 and VCC Core Rail

1.5V

1.35V

<=25ms

0.6V

NO LIMIT

NO SLEW RATE

REQUIRENT

1.05V PCH

NO SLEW RATE

REQUIRENT

<=35ms

NO LIMIT

1.35V

SLP_S3_N

SLP_S4_N

SUSCLK

SUSACK_N

SUS_WARNB

B B

RSMRST_SIO_N

SB5V/SB3V

SLP_SUSB

PS_ON_N

PCH_SIO_DPWROK

V_5P0_A/V_3P3_A

RTCCLK

A A

RTCRST#

VccRTC

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Power Sequence

Power Sequence

Power Sequence

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

C

ROSA General-SFF

C

ROSA General-SFF

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

651Thursday, August 15, 2013

651Thursday, August 15, 2013

651Thursday, August 15, 2013

-1A

-1A

-1A

Page 7

5

4

3

2

1

D D

VCC12CPU

C C

+12V

VCC5A

VCC

VCC3

-12V

POWER SUPPLY

B B

CPU Core Regulator(VRD 12 .5)

70A VR_TDC105A 0.5V-2.3V V_CPU_CORE

4-phase Switching

NCP81102

CPU XDP

V_CPU_VCCIO2PCH

1.05V 5A

V_1P05_PCH

V_SM

COMP LM358

1.05V 1A

SB5V

V_1P05_ME

COMP LM358

1.5V 0.35A

VCC3

V_1P5_PCH

APL5930KAI

VCC3

SB3V

V_3P3_A

Switch

BAT

VCC3A

V_CPU_VCCIO_RIGHT

V_3P3_EPW

TDC= ?A

Imax= 0.016A

DIODE BAT54C

VCCIO2PCH

V_1P05_PCH

Filter

Intel LGA1150

95A

HASWELL

VCCIO_OUT

1V 300mA

VCCIO2PCH

1V 30mA

DDR3 DIMM X2 & Termination

+1.5V

V_SM(S0,S1) 7A

V_SM(S3) 1.0A

+0.75V

V_SM_VTT(S0) 1.1A

Intel PCH Lynx P oint

External Suspend VR mode

1.05V

using INTVRMEN 1.12A

(VCC)

1.05V V_1P05_PCH 1.29A

(VCC)

1.05V

V_1P05_PCH 3.629A

(VCCIO)

1.05V

V_1P05_PCH 0.306A

(VCCCLK)

V_1P05_ME 0.67A1.05V

(VCCASW)

1.5V

V_1P5_PCH 0.179A

(VCCVRM)

V_1P5_PCH 0.07A

1.5V

(VCCADAC)

3.3V

VCC3 0.0133A

(VCCADAC3_3 )

3.3V V_3P3_EPW 0.022A

(VCCPSPI)

3.3V SB3V 0.261A

(VCCSUS3)

V_3P3_A 0.015A3.3V

(VCCDSW3_3)

V_3P0_BAT_VREG 1mA

(VCCRTC)

4.2A

CPU / DDR3

V_SM 1.5V 25A

1-phase Switching

NCP1589

DDR3 MEM_ VTT

V_SM_VTT

0.75V 1.1A Linear

APL533 6

VCC5A

Switch

VCC

SB3V

P-MOSFET

AO3413

V_3P3_LAN

V_1P05_LAN

BAT

SB3V

V_3P3_A

V_CPU_VCCIO_RIGHT 1.05V 1mA

V_3P3_EPW

5VDUAL_USB_F

5VDUAL_USB_R

VCC

VCC3

SB5V

VCC3

+3.0V

+3.3V

VCC3

+3.3V S3

+3.3V_A

SPI ROM(4MB+2MB)

+3.3V

USB(4 Front:2*USB2 .0

,2*USB3.0)

S0:

S3:

USB(6 Rear:4*US B3.0

,2*USB2.0)

S0:

S3:

+5V_VGA

3.3V

ALC662 VD

(NA mA)

5V

(NA mA)

3.3V

RTL8111G

70mA

3.3V

300mA

1.05V

NCT5532D

2.4µA

25mA

8mA

175mA

5VDUAL_USB_F

5VDUAL_USB_F

5VDUAL_USB_R

5VDUAL_USB_R

CRT

(1A fuse)

HDMI

(0.5 A fus e x 1)

(0.4A)

(4.6A)

(0.6A)

(2.8A)

VCC3

LDO

APL5930KAI

+12V

VCC3

+12V

VCC3

SB3V

PCIE X16 Slot

2.0A

+12V

1.0A

3.3V

0.38A

3.3Vaux

PCIE X1 Slot

0.5A

+12V

3.0A

3.3V

0.1A

3.3Vaux

MiniPCIe

0.75A

3.3V

0.38A

1.5V

V_3P3_PCIVAUX

V_3P3_PCIVAUX

SB3V VCC3

Switch

CPU Fans

+12V

200mA

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Power Map

Power Map

Power Map

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

D

ROSA General-SFF

D

ROSA General-SFF

D

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

751Thursday, August 15, 2013

751Thursday, August 15, 2013

751Thursday, August 15, 2013

+12V

V_5P0_A

P-MOSFET

AO3401

V_3P3_A

P-MOSFET

A A

AO3401

5

SB5V

SB3V

SB5V

Switch

Switch

VCC

USB

5VDUAL_USB_R

5VDUAL_USB_F

4

3

-1A

-1A

-1A

Page 8

5

D D

C C

4

3

2

1

TBD

B B

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

ROSA General-SFF

A

ROSA General-SFF

A

ROSA General-SFF

A

2

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

851Thursday, August 15, 2013

851Thursday, August 15, 2013

851Thursday, August 15, 2013

1

-1A

-1A

-1A

Page 9

5

D D

C C

4

3

2

1

TBD

B B

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

A A

Title

Title

Title

TBD

TBD

TBD

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

ROSA General-SFF

A

ROSA General-SFF

A

ROSA General-SFF

A

2

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

951Thursday, August 15, 2013

951Thursday, August 15, 2013

951Thursday, August 15, 2013

1

-1A

-1A

-1A

Page 10

5

CLOCK

CK_PE_100M_MCP_DN20

CK_PE_100M_MCP_DP20

CPU_VCORE

VCC_SENSE50

VSS_SENSE50

H_VIDSCK_VR50

H_VIDSOUT_VR50

H_VIDALERT_N_VR50

D D

XDP

C C

H_TDO14

H_TDI14

H_TCK14

H_TMS14

H_TRST_N14

H_PRDY_N14

H_PREQ_N14

XDP_DBRESET_N14

HSW_XDP_MBP_014

HSW_XDP_MBP_114

HSW_PCUDEBUG_014

HSW_PCUDEBUG_114

HSW_PCUDEBUG_214

HSW_PCUDEBUG_314

HSW_PCUDEBUG_414

HSW_PCUDEBUG_514

HSW_PCUDEBUG_614

HSW_PCUDEBUG_714

HSW_PCUDEBUG_814

HSW_PCUDEBUG_914

HSW_PCUDEBUG_1014

HSW_PCUDEBUG_1114

HSW_PCUDEBUG_1214

HSW_PCUDEBUG_1314

HSW_PCUDEBUG_1414

HSW_PCUDEBUG_1514

HSW_PCUSTB_0_DP14

HSW_PCUSTB_0_DN14

HSW_PCUSTB_1_DP14

HSW_PCUSTB_1_DN14

HSW_STRAP_1323

MINIMIZE STUB BETWEEN THESE AND RESISTORS AT SINAL PAGE

PLACE IN CRB AREA

H_VIDSCK_VR

H_VIDSOUT_VR H_VIDSOUT

H_VIDALERT_N_VR

R140

10KR2J-3-GP

1 2

1 2

R136 0R0402-PAD-1-GP

1 2

R129 0R0402-PAD-1-GP

1 2

R128 0R0402-PAD-1-GP

V_SM

H_PWRGD

12

C512

SCD1U16V2ZY-2GP

(R)

1 2

R2227 1K8R2F-GP

Place near CPU side

V_CPU_VCCIO_RIGHT

H_PROCHOT_N

1 2

R340

51R2F-2-GP

2012/12/15 Follow Intel PGD

1 2

R263 56R2J-4-GP

OTHER

VCCST13

XDP_PWR_DEBUG14

H_PWRGD14,19

FP_RST_DBR_N19

H_SKTOCC_N19,50

H_DRAMPWRGD19,46

CK_DPNS_R_DN20

CK_DPNS_R_DP20

H_PM_SYNC_021

H_PECI21,39

PLTRST_CPU_N14,21

H_PROCHOT_N50

H_THERMTRIP_N21

B B

H_THERMTRIP_N

V_1P05_PCH

1 2

R127 0R0402-PAD-1-GP

1 2

R159 150R2F-1-GP

12

R794 10KR2J-3-GP (R)

1 2

R806 0R2J-2-GP

(P)

4

H_VIDSCK

H_VIDALERT_N

CPU_THERMTRIP_N

PWR_DEBUG

PWR_DEBUGXDP_PWR_DEBUG

V_CPU_VCCIO_RIGHT

R424 75R2F-2-GP

R800 110R2F-GP

R482 90D9R2F-1-GP(R)

12

R2226

3K3R2F-2-GP

H_PROCHOT_R_N

V_1P05_PCH

2012/12/15 Follow Intel PGD

12

R411

1KR2J-1-GP

PLTRST_CPU_N

HSW_STRAP_13

(R)

3

1 2

1 2

1 2

H_VIDSCK

H_VIDSOUT

H_VIDALERT_N

H_DRAMPWRGD

1 2

R416 0R0402-PAD-1-GP

1 2

R843 1KR2J-1-GP

CLOSE TO CPU

DIMM_CA_CPU_VREF_A DIMM_CA_VREF_A

1 2

R516 44D2R2F-GP

1 2

R341 100R2J-2-GP (R)

1 2

R138 0R0402-PAD-1-GP

12

C567

SCD1U16V2ZY-2GP

(R)

Place near CPU side

1 2

R826 1KR2J-1-GP(R)

1 2

R827 1KR2J-1-GP(R)

1 2

R828 1KR2J-1-GP(R)

1 2

R829 1KR2J-1-GP(R)

1 2

R830 1KR2J-1-GP(R)

1 2

R831 1KR2J-1-GP(R)

1 2

R832 1KR2J-1-GP(R)

1 2

R833 1KR2J-1-GP(R)

1 2

R834 1KR2J-1-GP(R)

1 2

R835 1KR2J-1-GP(R)

1 2

R836 1KR2J-1-GP(R)

1 2

R837 1KR2J-1-GP(R)

1 2

R838 1KR2J-1-GP(R)

1 2

R839 1KR2J-1-GP(R)

1 2

R842 1KR2J-1-GP(R)

1 2

R844 1KR2J-1-GP(R)

1 2

R845 1KR2J-1-GP(R)

1 2

R848 1KR2J-1-GP(R)

1 2

R849 1KR2J-1-GP(R)

FP_RST_DBR_N

XDP_DBRESET_N

R804 49D9R2F-GP

12

R265 2R2F-GP

12

C3312

SCD022U16V2KX-3GP

DIMM_CA_CPU_VREF_RC

12

R793

24D9R2F-L-GP

Place near CPU side

CK_PE_100M_MCP_DN

CK_PE_100M_MCP_DP

H_VIDALERT_N_1

H_DRAMPWRGD_CPU

H_PWRGD

H_CPURST_N

H_PM_SYNC_0

H_PECI

TP_H_CATERR_N

1

TP166TPAD28

H_PROCHOT_R_N

CPU_THERMTRIP_N

H_SKTOCC_N

DIMM_CA_CPU_VREF_A

HSW_PCUDEBUG_0

HSW_PCUDEBUG_1

HSW_PCUDEBUG_2

HSW_PCUDEBUG_3

HSW_PCUDEBUG_4

HSW_PCUDEBUG_5

HSW_PCUDEBUG_6

HSW_PCUDEBUG_7

HSW_PCUDEBUG_8

HSW_PCUDEBUG_9

HSW_PCUDEBUG_10

HSW_PCUDEBUG_11

HSW_PCUDEBUG_12

HSW_PCUDEBUG_13

HSW_PCUDEBUG_14

HSW_PCUDEBUG_15

HSW_PCUSTB_0_DP

HSW_PCUSTB_0_DN

HSW_PCUSTB_1_DP

HSW_PCUSTB_1_DN

H_TCK

H_TDI

H_TDO

H_TMS

H_TRST_N

H_PRDY_N

H_PREQ_N

1 2

R264 0R0402-PAD-1-GP

TESTLOW_2

TP_RSVD_K8

1

TP140TPAD28

TP_RSVD_J10

1

TP141TPAD28

1 2

U27E

V4

BCLK#

V5

BCLK

C38

VIDSCLK

C37

VIDSOUT

B37

VIDALERT#

AK21

SM_DRAMPWROK

AB35

PWRGOOD

M39

RESET#

P36

PM_SYNC

N37

PECI

M36

CATERR#

K38

PROCHOT#

F37

THERMTRIP#

D38

SKTOCC#

AB38

SM_VREF

AA37

CFG0

Y38

CFG1

AA36

CFG2

W38

CFG3

V39

CFG4

U39

CFG5

U40

CFG6

V38

CFG7

T40

CFG8

Y35

CFG9

AA34

CFG10

V37

CFG11

Y34

CFG12

U38

CFG13

W34

CFG14

V35

CFG15

Y36

CFG17

Y37

CFG16

V36

CFG19

W36

CFG18

D39

TCK

F38

TDI

F39

TDO

E39

TMS

E37

TRST#

L39

PRDY#

L37

PREQ#

G40

DBR#

N5

TESTLO_N5

K8

RSVD_TP_K8

J10

RSVD_TP_J10

HASWE1NFU

(62.10040.A11)

DIMM_CA_VREF_B

Place near DIMM side

2

HASWELL

5 OF 10

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

RSVD_T35

RSVD_M38

TESTLO_P6

RSVD_K9

RSVD_H15

RSVD_J9

RSVD_H14

VCC_M8

RSVD_AV2

RSVD_TP_J16

RSVD_TP_H16

PWR_DEBUG

VSS

VSS

VSS

RSVD_TP_K13

RSVD_TP_J8

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

RSVD_AB36

RSVD_TP_AW2

RSVD_TP_AV1

RSVD_AC8

VCOMP_OUT

RSVD_U8

RSVD_AB33

RSVD_T8

RSVD_Y8

RSVD_M10

RSVD_L10

RSVD_M11

RSVD_L12

RSVD_W8

RSVD_R33

RSVD_P33

VCC_SENSE

VSS

VSS

VSS

VSS

VSS_SENSE

RSVD_N35

DPLL_REF_CLK#

DPLL_REF_CLK

CFG_RCOMP

DIMM_CA_VREF_A 15,17

DIMM_CA_VREF_B 15,17

G39

J39

G38

H37

H38

J38

K39

K37

T35

M38

P6

K9

H15

J9

H14

M8

AV2

J16

H16

N40

N39

V7

AB6

K13

J8

R1

P1

R2

AB36

AW2

AV1

AC8

P4

U8

AB33

T8

Y8

M10

L10

M11

L12

W8

R33

P33

E40

N33

J11

M9

J7

F40

N35

W6

W5

H40

HSW_XDP_MBP_0

HSW_XDP_MBP_1

TP_CPU_G38

TP_CPU_H37

TP_CPU_H38

TP_CPU_J38

TP_CPU_K39

TP_CPU_K37

TP_CPU_T35

TP_CPU_M38

TESTLOW_1

VCCST

TP_RSVD_H15

TP_RSVD_J9

TP_RSVD_H14

TP_RSVD_AV2

TP_RSVD_J16

TP_RSVD_H16

PWR_DEBUG

TP_RSVD_V7

TP_RSVD_AB6

TP_RSVD_K13

TP_RSVD_J8

DDR_RCOMP_0

DDR_RCOMP_1

DDR_RCOMP_2

TP_RSVD_AB36

TP_RSVD_AW2

TP_RSVD_AV1

TP_RSVD_AC8

TP_RSVD_U8

TP_RSVD_AB33

CPU_VSS_T8

TP_RSVD_Y8

TP_RSVD_M10

TP_RSVD_L10

TP_RSVD_M11

TP_RSVD_L12

TP_RSVD_W8

TP_RSVD_R33

TP_RSVD_P33

VCC_SENSE

VSS_SENSE

V_1P05_PECI_VCOM

CK_DPNS_R_DN

CK_DPNS_R_DP

TPEV_CFG_RCOMP

1

1

TP103

1

TP107

1

TP108

1

TP109

1

TP110

1

TP111

1

TP112

1

TP113

1 2

R798 49D9R2F-GP

1

TP136

1

TP137

1

TP138

V_CPU_CORE

1

TP139

1

TP134

1

TP135

1

TP161

1

TP167

1

TP130

1

TP131

1 2

R541 100R2F-L1-GP-U

1 2

R417 75R2F-2-GP

1 2

R796 100R2F-L1-GP-U

1

TP126

1

TP127

1

TP128

1

TP129

V_VCCIOA_LOAD

1

TP124

1

1

1

1

1

1

1

1

1

1

1 2

12

TP125

TP116

TP117

TP118

TP119

TP120

TP121

TP122

TP123

R799

49D9R2F-GP

(R)

TP133

R797

49D9R2F-GP

1 2

R1248 0R2J-2-GP

(R)

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

CPU uLGA 1150_1

CPU uLGA 1150_1

CPU uLGA 1150_1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

C

ROSA General-SFF

C

ROSA General-SFF

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

10 51Thursday, August 15, 2013

10 51Thursday, August 15, 2013

10 51Thursday, August 15, 2013

-1A

-1A

-1A

Page 11

5

4

3

2

1

PCIEX16

EXP_A_TX_DP[0..15]26

EXP_A_TX_DN[0..15]26

EXP_A_RX_DP[0..15]26

EXP_A_RX_DN[0..15]26

DMI

D D

C C

B B

DMI_IT_MR_DP[0..3]22

DMI_IT_MR_DN[0..3]22

DMI_MT_IR_DP[0..3]22

DMI_MT_IR_DN[0..3]22

FDI

HDMI

FDI_CSYNC22

FDI_INT22

FDI_TX_DN[0..1]22

FDI_TX_DP[0..1]22

CK_DP_DP20

CK_DP_DN20

DDSP_C_TX_DP_028

DDSP_C_TX_DN_028

DDSP_C_TX_DP_128

DDSP_C_TX_DN_128

DDSP_C_TX_DP_228

DDSP_C_TX_DN_228

DDSP_C_TX_DP_328

DDSP_C_TX_DN_328

1 2

V_VCCIOA_LOAD

V_VCCIOA_LOAD

R307 24D9R2F-L-GP

1 2

R805 24D9R2F-L-GP

TP80

TP77

TP76

TP35

TP36

TP78

TP79

1

1

1

1

FDI_CSYNC

FDI_INT

DP_COMP

CK_DP_DN

CK_DP_DP

DISP_UTIL_CPU

1

TP_DISP_K11

1

TP_DISP_J12

1

FDI_TX_DN0

FDI_TX_DP0

FDI_TX_DN1

FDI_TX_DP1

EXP_A_RX_DP0

EXP_A_RX_DN0

EXP_A_RX_DP1

EXP_A_RX_DN1

EXP_A_RX_DP2

EXP_A_RX_DN2

EXP_A_RX_DP3

EXP_A_RX_DN3

EXP_A_RX_DP4

EXP_A_RX_DN4

EXP_A_RX_DP5

EXP_A_RX_DN5

EXP_A_RX_DP6

EXP_A_RX_DN6

EXP_A_RX_DP7

EXP_A_RX_DN7

EXP_A_RX_DP8

EXP_A_RX_DN8

EXP_A_RX_DP9

EXP_A_RX_DN9

EXP_A_RX_DP10

EXP_A_RX_DN10

EXP_A_RX_DP11

EXP_A_RX_DN11

EXP_A_RX_DP12

EXP_A_RX_DN12

EXP_A_RX_DP13

EXP_A_RX_DN13

EXP_A_RX_DP14

EXP_A_RX_DN14

EXP_A_RX_DP15

EXP_A_RX_DN15

DMI_IT_MR_DP0

DMI_IT_MR_DN0

DMI_IT_MR_DP1

DMI_IT_MR_DN1

DMI_IT_MR_DP2

DMI_IT_MR_DN2

DMI_IT_MR_DP3

DMI_IT_MR_DN3

TP_PEG_D1

TP_PEG_C2

TP_PEG_B3

TP_PEG_A4

PEG_COMP

U27C

E15

F15

D14

E14

E13

F13

D12

E12

E11

F11

F10

G10

E9

F9

F8

G8

D3

D4

E4

E5

F5

F6

G4

G5

H5

H6

J4

J5

K5

K6

L4

L5

U3

T3

U1

V1

W2

V2

Y3

W3

D1

C2

B3

A4

P3

HASWE1NFU

(62.10040.A11)

U27D

D16

FDI_CSYNC

D18

FDI_INT

R4

DP_COMP

U5

SSC_DPLL_REF_CLK#

U6

SSC_DPLL_REF_CLK

E16

EDP_DISP_UTIL

K11

RSVD_TP_K11

J12

RSVD_TP_J12

B14

FDI0_TX0#0

A14

FDI0_TX00

C13

FDI0_TX0#1

B13

FDI0_TX01

HASWE1NFU

(62.10040.A11)

PEG_RX0

PEG_RX#0

PEG_RX1

PEG_RX#1

PEG_RX2

PEG_RX#2

PEG_RX3

PEG_RX#3

PEG_RX4

PEG_RX#4

PEG_RX5

PEG_RX#5

PEG_RX6

PEG_RX#6

PEG_RX7

PEG_RX#7

PEG_RX8

PEG_RX#8

PEG_RX9

PEG_RX#9

PEG_RX10

PEG_RX#10

PEG_RX11

PEG_RX#11

PEG_RX12

PEG_RX#12

PEG_RX13

PEG_RX#13

PEG_RX14

PEG_RX#14

PEG_RX15

PEG_RX#15

DMI_RX0

DMI_RX#0

DMI_RX1

DMI_RX#1

DMI_RX2

DMI_RX#2

DMI_RX3

DMI_RX#3

RSVD_TP_D1

RSVD_TP_C2

RSVD_TP_B3

RSVD_TP_A4

PEG_RCOMP

HASWELL

HASWELL

3 OF 10

PEG_TX0

PEG_TX#0

PEG_TX1

PEG_TX#1

PEG_TX2

PEG_TX#2

PEG_TX3

PEG_TX#3

PEG_TX4

PEG_TX#4

PEG_TX5

PEG_TX#5

PEG_TX6

PEG_TX#6

PEG_TX7

PEG_TX#7

PEG_TX8

PEG_TX#8

PEG_TX9

PEG_TX#9

PEG_TX10

PEG_TX#10

PEG_TX11

PEG_TX#11

PEG_TX12

PEG_TX#12

PEG_TX13

PEG_TX#13

PEG_TX14

PEG_TX#14

PEG_TX15

PEG_TX#15

DMI_TX0

DMI_TX#0

DMI_TX1

DMI_TX#1

DMI_TX2

DMI_TX#2

DMI_TX3

DMI_TX#3

A12

B12

B11

C11

C10

D10

B9

C9

C8

D8

B7

C7

A6

B6

B5

C5

E1

E2

F2

F3

G1

G2

H2

H3

J1

J2

K2

K3

M2

M3

L1

L2

AA4

AA5

AB3

AB4

AC5

AC4

AC1

AC2

4 OF 10

DDIB_TXB0

DDIB_TXB#0

DDIB_TXB1

DDIB_TXB#1

DDIB_TXB2

DDIB_TXB#2

DDIB_TXB3

DDIB_TXB#3

DDIC_TXC0

DDIC_TXC#0

DDIC_TXC1

DDIC_TXC#1

DDIC_TXC2

DDIC_TXC#2

DDIC_TXC3

DDIC_TXC#3

DDID_TXD0

DDID_TXD#0

DDID_TXD1

DDID_TXD#1

DDID_TXD2

DDID_TXD#2

DDID_TXD3

DDID_TXD#3

EXP_A_TX_DP0

EXP_A_TX_DN0

EXP_A_TX_DP1

EXP_A_TX_DN1

EXP_A_TX_DP2

EXP_A_TX_DN2

EXP_A_TX_DP3

EXP_A_TX_DN3

EXP_A_TX_DP4

EXP_A_TX_DN4

EXP_A_TX_DP5

EXP_A_TX_DN5

EXP_A_TX_DP6

EXP_A_TX_DN6

EXP_A_TX_DP7

EXP_A_TX_DN7

EXP_A_TX_DP8

EXP_A_TX_DN8

EXP_A_TX_DP9

EXP_A_TX_DN9

EXP_A_TX_DP10

EXP_A_TX_DN10

EXP_A_TX_DP11

EXP_A_TX_DN11

EXP_A_TX_DP12

EXP_A_TX_DN12

EXP_A_TX_DP13

EXP_A_TX_DN13

EXP_A_TX_DP14

EXP_A_TX_DN14

EXP_A_TX_DP15

EXP_A_TX_DN15

DMI_MT_IR_DP0

DMI_MT_IR_DN0

DMI_MT_IR_DP1

DMI_MT_IR_DN1

DMI_MT_IR_DP2

DMI_MT_IR_DN2

DMI_MT_IR_DP3

DMI_MT_IR_DN3

E17

F17

F18

G18

G19

H19

F20

G20

D19

E19

C20

D20

D21

E21

C22

D22

B15

C15

A16

B16

B17

C17

A18

B18

DDSP_C_TX_DP_0

DDSP_C_TX_DN_0

DDSP_C_TX_DP_1

DDSP_C_TX_DN_1

DDSP_C_TX_DP_2

DDSP_C_TX_DN_2

DDSP_C_TX_DP_3

DDSP_C_TX_DN_3

HDMI

SKT1

A A

Load Plate

(22.78003.021)

5

4

SKT2

Back Plate

(22.78006.031)

3

SKT3

BACK PLATE

(60.3EQ19.001)

SKT4

ILMCOVER

(42.3EQ28.002)

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

CPU uLGA 1150_2

CPU uLGA 1150_2

CPU uLGA 1150_2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

C

ROSA General-SFF

C

ROSA General-SFF

C

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

11 51Thursday, August 15, 2013

11 51Thursday, August 15, 2013

11 51Thursday, August 15, 2013

-1A

-1A

-1A

Page 12

5

DDR DATA

M_DATA_A[0..63]15

M_DATA_B[0..63]17

M_DQS_A_DP[0..7]15

M_DQS_A_DN[0..7]15

M_DQS_B_DP[0..7]17

M_DQS_B_DN[0..7]17

DDR CMD/ADD

D D

C C

B B

M_MAA_A[0..15]15

M_MAA_B[0..15]17

DDR CTRL

DDR CLOCK

CK_M_DDR0_A_DP15

CK_M_DDR0_A_DN15

CK_M_DDR1_A_DP15

CK_M_DDR1_A_DN15

CK_M_DDR0_B_DP17

CK_M_DDR0_B_DN17

CK_M_DDR1_B_DP17

CK_M_DDR1_B_DN17

DDR OTHERS

DDR3_DRAMRST_N15,17

DIMM_DQ_CPU_VREF_B17

DIMM_DQ_CPU_VREF_A15

Other

M_WE_A_N15

M_CAS_A_N15

M_RAS_A_N15

M_SBS_A015

M_SBS_A115

M_SBS_A215

M_WE_B_N17

M_CAS_B_N17

M_RAS_B_N17

M_SBS_B017

M_SBS_B117

M_SBS_B217

M_SCS_A_N015

M_SCS_A_N115

M_SCKE_A015

M_SCKE_A115

M_ODT_A015

M_ODT_A115

M_SCS_B_N017

M_SCS_B_N117

M_SCKE_B017

M_SCKE_B117

M_ODT_B017

M_ODT_B117

PWRGD_3V14,19,21,39

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A9

M_DATA_A13

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A8

M_DATA_A14

M_DATA_A15

M_DATA_A17

M_DATA_A21

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A16

M_DATA_A22

M_DATA_A23

M_DATA_A25

M_DATA_A29

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A24

M_DATA_A30

M_DATA_A31

M_DATA_A33

M_DATA_A37

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A32

M_DATA_A38

M_DATA_A39

M_DATA_A41

M_DATA_A45

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A40

M_DATA_A46

M_DATA_A47

M_DATA_A49

M_DATA_A53

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A48

M_DATA_A54

M_DATA_A55

M_DATA_A57

M_DATA_A61

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A56

M_DATA_A62

M_DATA_A63

M_DQS_A_DP0

M_DQS_A_DP1

M_DQS_A_DP2

M_DQS_A_DP3

M_DQS_A_DP4

M_DQS_A_DP5

M_DQS_A_DP6

M_DQS_A_DP7

M_DQS_A_DN0

M_DQS_A_DN1

M_DQS_A_DN2

M_DQS_A_DN3

M_DQS_A_DN4

M_DQS_A_DN5

M_DQS_A_DN6

M_DQS_A_DN7

AD38

AD39

AF38

AF39

AD37

AD40

AF37

AF40

AH40

AH39

AK38

AK39

AH37

AH38

AK37

AK40

AM40

AM39

AP38

AP39

AM37

AM38

AP37

AP40

AV37

AW37

AU35

AV35

AT37

AU37

AT35

AW35

AW6

AW4

AE39

AJ39

AN39

AV36

AV32

AE38

AJ38

AN38

AU36

AW5

AU32

AY6

AU6

AV4

AU4

AV6

AY4

AR1

AR4

AN3

AN4

AR2

AR3

AN2

AN1

AL1

AL4

AJ3

AJ4

AL2

AL3

AJ2

AJ1

AG1

AG4

AE3

AE4

AG2

AG3

AE2

AE1

AV5

AP3

AK3

AF3

AP2

AK2

AF2

U27A

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS8

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

SA_DQS#8

HASWE1NFU

(62.10040.A11)

4

HASWELL

1 OF 10

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_ODT0

SA_ODT1

SA_ODT2

SA_ODT3

SA_ECC_CB0

SA_ECC_CB1

SA_ECC_CB2

SA_ECC_CB3

SA_ECC_CB4

SA_ECC_CB5

SA_ECC_CB6

SA_ECC_CB7

SA_BS0

SA_BS1

SA_BS2

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_CS#2

SA_CS#3

SA_CK0

SA_CK#0

SA_CK1

SA_CK#1

SA_CK2

SA_CK#2

SA_CK3

SA_CK#3

RSVD_AW12

SA_RAS#

SA_WE#

RSVD_AV20

RSVD_AW27

SA_CAS#

SM_DRAMRST#

AU13

AV16

AU16

AW17

AU17

AW18

AV17

AT18

AU18

AT19

AW11

AV19

AU19

AY10

AT20

AU21

AW10

AY8

AW9

AU8

AW33

AV33

AU31

AV31

AT33

AU33

AT31

AW31

AV12

AY11

AT21

AV22

AT23

AU22

AU23

AU14

AV9

AU10

AW8

AY15

AY16

AW15

AV15

AV14

AW14

AW13

AY13

AW12

AU12

AU11

AV20

AW27

AU9

AK22

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_MAA_A15

M_ODT_A0

M_ODT_A1

M_SBS_A0

M_SBS_A1

M_SBS_A2

M_SCKE_A0

M_SCKE_A1

M_SCS_A_N0

M_SCS_A_N1

CK_M_DDR0_A_DP

CK_M_DDR0_A_DN

CK_M_DDR1_A_DP

CK_M_DDR1_A_DN

TP_RSVD_AW12

M_RAS_A_N

M_WE_A_N

TP_RSVD_AV20

TP_RSVD_AW27

M_CAS_A_N

DDR3_DRAMRST_N

12

C520

SCD1U10V2KX-4GP

(R)

1

TP34

1

1

3

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DATA_B8

M_DATA_B9

M_DATA_B10

M_DATA_B11

M_DATA_B12

M_DATA_B13

M_DATA_B14

M_DATA_B15

M_DATA_B17

M_DATA_B21

M_DATA_B19

M_DATA_B23

M_DATA_B20

M_DATA_B16

M_DATA_B18

M_DATA_B22

M_DATA_B25

M_DATA_B28

M_DATA_B27

M_DATA_B30

M_DATA_B24

M_DATA_B29

M_DATA_B26

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

M_DATA_B45

M_DATA_B41

M_DATA_B47

M_DATA_B43

M_DATA_B44

M_DATA_B40

M_DATA_B46

M_DATA_B42

M_DATA_B52

M_DATA_B53

M_DATA_B50

M_DATA_B55

M_DATA_B48

M_DATA_B49

M_DATA_B54

M_DATA_B51

M_DATA_B61

M_DATA_B60

M_DATA_B59

M_DATA_B63

M_DATA_B56

M_DATA_B57

M_DATA_B58

M_DATA_B62

M_DQS_B_DP0

M_DQS_B_DP1

M_DQS_B_DP2

M_DQS_B_DP3

M_DQS_B_DP4

M_DQS_B_DP5

M_DQS_B_DP6

M_DQS_B_DP7

M_DQS_B_DN0

TP32

TP33

M_DQS_B_DN1

M_DQS_B_DN2

M_DQS_B_DN3

M_DQS_B_DN4

M_DQS_B_DN5

M_DQS_B_DN6

M_DQS_B_DN7

AE34

AE35

AG35

AH35

AD34

AD35

AG34

AH34

AK31

AK34

AK35

AK32

AN34

AP34

AN31

AP31

AN35

AP35

AN32

AP32

AM29

AM28

AR29

AR28

AP29

AP28

AR12

AP12

AR13

AP13

AM13

AM12

AR10

AP10

AM10

AF35

AL33

AP33

AN28

AN12

AN25

AF34

AK33

AN33

AN29

AN13

AN26

AL34

AL35

AL31

AL32

AL29

AL28

AL13

AL12

AR9

AP9

AR6

AP6

AR7

AP7

AM9

AL9

AL6

AL7

AL10

AM6

AM7

AH6

AH7

AE6

AE7

AJ6

AJ7

AF6

AF7

AP8

AL8

AG7

AR8

AM8

AG6

U27B

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS8

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

SB_DQS#8

HASWE1NFU

(62.10040.A11)

HASWELL

2

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

2 OF 10

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_ODT0

SB_ODT1

SB_ODT2

SB_ODT3

SB_ECC_CB0

SB_ECC_CB1

SB_ECC_CB2

SB_ECC_CB3

SB_ECC_CB4

SB_ECC_CB5

SB_ECC_CB6

SB_ECC_CB7

SB_BS0

SB_BS1

SB_BS2

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_CS#2

SB_CS#3

SB_CK0

SB_CK#0

SB_CK1

SB_CK#1

SB_CK2

SB_CK#2

SB_CK3

SB_CK#3

SB_CAS#

RSVD_AL20

SB_RAS#

SB_WE#

AL19

AK23

AM22

AM23

AP23

AL23

AY24

AV25

AU26

AW25

AP18

AY25

AV26

AR15

AV27

AY28

AM17

AL16

AM16

AK15

AM26

AM25

AP25

AP26

AL26

AL25

AR26

AR25

AK17

AL18

AW28

AW29

AY29

AU28

AU29

AP17

AN15

AN17

AL15

AM20

AM21

AP22

AP21

AN20

AN21

AP19

AP20

AP16

AL20

AM18

AK16

AB39

AB40

M_MAA_B0

M_MAA_B1

M_MAA_B2

M_MAA_B3

M_MAA_B4

M_MAA_B5

M_MAA_B6

M_MAA_B7

M_MAA_B8

M_MAA_B9

M_MAA_B10

M_MAA_B11

M_MAA_B12

M_MAA_B13

M_MAA_B14

M_MAA_B15

M_ODT_B0

M_ODT_B1

M_SBS_B0

M_SBS_B1

M_SBS_B2

M_SCKE_B0

M_SCKE_B1

M_SCS_B_N0

M_SCS_B_N1

CK_M_DDR0_B_DP

CK_M_DDR0_B_DN

CK_M_DDR1_B_DP

CK_M_DDR1_B_DN

M_CAS_B_N

M_RAS_B_N

M_WE_B_N

DIMM_DQ_CPU_VREF_A

DIMM_DQ_CPU_VREF_B

1

U27H

PWRGD_3V

12

R2230

6K04R2F-GP

(R)

A A

5

12

4

R2231

2K67R2F-2-GP

(R)

TP148

TP149

TP150

TP151

TP152

TP153

TP154

TP155

TP164

TP160

TP162

TP163

TP156

TP157

TP158

TP159

TP_RSVD_AY18

1

TP_RSVD_AW24

1

TP_RSVD_AW23

1

TP_RSVD_AV29

1

TP_RSVD_AV24

1

TP_RSVD_AU39

1

TP_RSVD_AU27

1

TP_RSVD_AU1

1

TP_RSVD_AT40

1

TP_RSVD_AK20

1

VCCST_PWRGD

TP_RSVD_T34

1

TP_RSVD_R34

1

TP_RSVD_J40

1

TP_RSVD_J17

1

TP_RSVD_J15

1

TP_RSVD_H12

1

AY18

AW24

AW23

AV29

AV24

AU39

AU27

AT40

AK20

AU1

Y7

T34

R34

J40

J17

J15

H12

RSVD_AY18

RSVD_AW24

RSVD_AW23

RSVD_AV29

RSVD_AV24

RSVD_AU39

RSVD_AU27

RSVD_AU1

RSVD_AT40

RSVD_AK20

RSVD_Y7

RSVD_T34

RSVD_R34

RSVD_J40

RSVD_J17

RSVD_J15

RSVD_H12

HASWE1NFU

(62.10040.A11)

HASWELL

3

8 OF 10

RSVD_TP_K12

RSVD_TP_J13

RSVD_TP_P37

RSVD_TP_N38

RSVD_TP_R36

RSVD_TP_C39

RSVD_TP_N36

TP_RSVD_K12

K12

TP_RSVD_J13

J13

TP_RSVD_P37

P37

TP_RSVD_N38

N38

TP_RSVD_R36

R36

TP_RSVD_C39

C39

U35

VSS

P40

VSS

R38

VSS

T37

VSS

V34

VSS

R39

VSS

T38

VSS

U36

VSS

P39

VSS

T36

VSS

R37

VSS

J14

VSS

TP_CPU_N36

N36

1

TP142

1

TP143

1

TP144

1

TP145

1

TP146

1

TP147

<Variant Name>

<Variant Name>

<Variant Name>

1

TP165

Title

Title

Title

CPU uLGA 1150_3

CPU uLGA 1150_3

CPU uLGA 1150_3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

C

ROSA General-SFF

C

ROSA General-SFF

C

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

12 51Thursday, August 15, 2013

12 51Thursday, August 15, 2013

12 51Thursday, August 15, 2013

-1A

-1A

-1A

Page 13

5

Put R333 near PCH side for V_CPU_VCCIO2PCH

is for PCH power

1 2

R333 0R0402-PAD-1-GP

V_1P05_PCH

V_CPU_VCCIO2PCH

D D

VCCST10

V_CPU_VCCIO_RIGHT

C C

12

C187

SC4D7U6D3V3KX-GP

12

C141

SCD1U10V2KX-5GP

V_CPU_VCCIO_RIGHT

V_1P05_PCH

12

R200

0R0402-PAD-1-GP

12

C88

SC4D7U6D3V3KX-GP

1 2

R808

0R2J-2-GP

(R)

1 2

R807 0R2J-2-GP

(R)

V_CPU_CORE

V_CPU_CORE

VCCIO2PCHVCCST

PLACE CAPS AT TOP SOCKET EDGE

V_CPU_CORE

12

C397

B B

SC22U6D3V5MX-2GP

12

C270

SC22U6D3V5MX-2GP

12

C271

SC22U6D3V5MX-2GP

12

C500

SC22U6D3V5MX-2GP

P8

L40

AB8

L31

L18

L17

J33

A24

A25

A26

A27

A28

A29

A30

G33

B25

B27

B29

B31

J31

B33

G31

B35

C24

C25

C26

C27

C28

C29

C30

C32

C34

C35

D25

D27

D29

D31

E33

D33

E31

D35

E24

E25

E26

E27

E28

E29

E30

E32

E34

F23

F25

F27

F29

F31

E35

F33

F35

G22

G23

G24

G25

G26

G27

G28

G29

G30

G32

G34

G35

H23

H25

H27

H29

H31

L34

4

U27F

VCC

VCCIO_OUT

VCCIO2PCH

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

HASWE1NFU

(62.1004 0.A11)

HASWELL

6 OF 10

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

C31

C33

L16

L15

J35

H33

H35

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

J32

J34

K19

K21

K23

K25

K27

K29

K31

M13

K33

K35

L19

L20

L21

L22

L23

L24

L25

L26

L27

L28

L29

L30

L32

L33

M17

M15

M19

M21

M23

M25

M27

M29

M33

AJ12

AJ13

AJ15

AJ17

AJ20

AJ21

AJ24

AJ25

AJ28

AJ29

AJ9

AT17

AT22

AU15

AU20

AU24

AV10

AV11

AV13

AV18

AV23

AV8

AW16

AY12

AY14

AY9

V_CPU_CORE

V_SM

AA33

AA35

AA38

AB34

AB37

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

AD33

AD36

AE33

AE36

AE37

AE40

AG33

AG36

AG37

AG38

AG39

AG40

AH33

AH36

AF33

AF36

AJ11

AJ14

AJ16

AJ18

AJ19

AJ22

AJ23

AJ26

AJ27

AJ30

AJ31

AJ32

AJ33

A11

A13

A15

A17

A23

AA3

AA6

AA7

AA8

AB5

AB7

AC3

AC6

AC7

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AE5

AE8

AF1

AF4

AF5

AF8

AG5

AG8

AH1

AH2

AH3

AH4

AH5

AH8

U27I

A5

VSS

A7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

HASWE1NFU

(62.1004 0.A11)

3

HASWELL

9 OF 10

AJ5

VSS

AJ8

VSS

AJ34

VSS

AJ35

VSS

AJ36

VSS

AJ37

VSS

AJ40

VSS

AK1

VSS

AK4

VSS

AK5

VSS

AK6

VSS

AK7

VSS

AK8

VSS

AK9

VSS

AK10

VSS

AK11

VSS

AK12

VSS

AK13

VSS

AK14

VSS

AK18

VSS

AK19

VSS

AK24

VSS

AK25

VSS

AK26

VSS

AK27

VSS

AK28

VSS

AK29

VSS

AK30

VSS

AK36

VSS

AL5

VSS

AL11

VSS

AL14

VSS

AL17

VSS

AL21

VSS

AL22

VSS

AL24

VSS

AL27

VSS

AL30

VSS

AL36

VSS

AL37

VSS

AL38

VSS

AL39

VSS

AL40

VSS

AM1

VSS

AM2

VSS

AM3

VSS

AM4

VSS

AM5

VSS

AM11

VSS

AM14

VSS

AM15

VSS

AM19

VSS

AM24

VSS

AM27

VSS

AM30

VSS

AM31

VSS

AM32

VSS

AM33

VSS

AM34

VSS

AM35

VSS

AM36

VSS

AN5

VSS

AN6

VSS

AN7

VSS

AN8

VSS

AN9

VSS

AN10

VSS

AN11

VSS

AN14

VSS

AN16

VSS

AN18

VSS

AN19

VSS

AN22

VSS

AN23

VSS

AN24

VSS

AN27

VSS

AN30

VSS

AN36

VSS

AN37

VSS

AN40

VSS

AP1

VSS

AP11

AP14

AP15

AP24

AP27

AP30

AP36

AR11

AR14

AR16

AR17

AR18

AR19

AR20

AR21

AR22

AR23

AR24

AR27

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AR37

AR38

AR39

AR40

AT10

AT11

AT12

AT13

AT14

AT15

AT16

AT24

AT25

AT26

AT27

AT28

AT29

AT30

AT32

AT34

AT36

AT38

AT39

AU25

AU30

AU34

AU38

AV21

AV28

AV30

AV34

AV38

AW26

AW30

AP4

AP5

AR5

AT1

AT2

AT3

AT4

AT5

AT6

AT7

AT8

AT9

AU2

AU3

AU5

AU7

AV3

AV7

AW3

U27G

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

HASWE1NFU

(62.1004 0.A11)

HASWELL

2

7 OF 10

AW32

VSS

AW34

VSS

AW36

VSS

AW7

VSS

AY17

VSS

AY23

VSS

AY26

VSS

AY27

VSS

AY30

VSS

AY5

VSS

AY7

VSS

B24

VSS

B26

VSS

B28

VSS

B30

VSS

B34

VSS

B36

VSS

B4

VSS

B8

VSS

C4

VSS

C6

VSS

C12

VSS

C14

VSS

C16

VSS

C18

VSS

C19

VSS

C21

VSS

C23

VSS

C36

VSS

B10

VSS

B23

VSS

C3

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

D2

VSS

D23

VSS

D24

VSS

D26

VSS

D28

VSS

D30

VSS

D34

VSS

D36

VSS

D37

VSS

D5

VSS

D6

VSS

D7

VSS

E7

VSS

E8

VSS

E10

VSS

E18

VSS

E3

VSS

E20

VSS

E22

VSS

E23

VSS

E36

VSS

E38

VSS

B32

VSS

E6

VSS

F1

VSS

F32

VSS

F12

VSS

F14

VSS

F16

VSS

F19

VSS

F21

VSS

F22

VSS

F24

VSS

F26

VSS

F28

VSS

F30

VSS

F34

VSS

F36

VSS

F4

VSS

D32

VSS

F7

VSS

G9

VSS

G11

VSS

G3

G6

G7

G12

G13

G14

G15

G16

G17

G21

G36

G37

H1

H4

H7

H8

H9

H10

H11

H13

H17

H18

H20

H21

H22

H24

H26

H28

H30

H32

H34

H36

H39

J3

J6

J18

J19

J20

J36

J37

K1

K4

K7

K10

K14

K17

K18

K20

K22

K24

K26

K28

K30

K34

K36

K40

L3

L6

L7

L8

L9

L11

L13

L14

L35

L38

M1

M12

M14

M16

M18

M20

M22

M24

M26

M28

M30

M32

M34

M37

U27J

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

HASWE1NFU

(62.1004 0.A11)

HASWELL

VSS_NCTF_AU40

VSS_NCTF_AV39

VSS_NCTF_AW38

VSS_NCTF_AY3

VSS_NCTF_B38

VSS_NCTF_B39

VSS_NCTF_C40

VSS_NCTF_D40

NCTF TEST PIN: AU40,

AV39,AW38,AY3,B38,B39,C40,D40

10 OF 10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K15

K16

K32

L36

M4

M5

M6

M7

M35

M40

N1

N2

N3

N4

N6

N7

N8

N34

P2

P5

P7

P34

P35

P38

R3

R5

R6

R7

R8

R35

R40

T1

T2

T4

T5

T6

T7

T33

T39

U2

U4

U7

U33

U34

U37

V3

V6

V8

V33

V40

W1

W4

W7

W33

W35

W37

Y4

Y5

Y6

Y33

AU40

AV39

AW38

AY3

B38

B39

C40

D40

1

PLACE ALL 0805 CAPS INSIDE CPU SOCKET CAVITY

V_CPU_CORE

12

C564

SC22U6D3V5MX-2GP

A A

V_SM

12

C563

SC22U6D3V5MX-2GP

12

C503

SC22U6D3V5MX-2GP

12

C574

SC22U6D3V5MX-2GP

12

C552

SC22U6D3V5MX-2GP

12

C560

SC22U6D3V5MX-2GP

5

12

12

C387

SC22U6D3V5MX-2GP

C551

SC22U6D3V5MX-2GP

V_CPU_CORE

12

C548

SC22U6D3V5MX-2GP

12

C547

SC22U6D3V5MX-2GP

12

C391

SC22U6D3V5MX-2GP

(R)

12

12

12

C522

SC22U6D3V5MX-2GP

(R)

4

C573

SC22U6D3V5MX-2GP

C546

SC22U6D3V5MX-2GP

12

C504

SC22U6D3V5MX-2GP

(R)

12

C350

SC22U6D3V5MX-2GP

12

C542

SC22U6D3V5MX-2GP

12

12

12

C570

SC22U6D3V5MX-2GP

(R)

C501

SC22U6D3V5MX-2GP

C521

SC22U6D3V5MX-2GP

12

C562

SC22U6D3V5MX-2GP

12

12

(R)

C502

SC22U6D3V5MX-2GP

C561

SC22U6D3V5MX-2GP

12

C537

SC22U6D3V5MX-2GP

12

C549

SC22U6D3V5MX-2GP

3

12

C558

SC22U6D3V5MX-2GP

12

C550

SC22U6D3V5MX-2GP

CPU Power Capacitor Quantity

Net

Vcore

CAP AMOUNT

22uf 0805 22

V_SM 22uf 0805 4+5(R)

2

DEFENSIVE DESIGN PWR_DEBUG

2012/12/04 Ryan removed,

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

CPU uLGA 1150_4

CPU uLGA 1150_4

CPU uLGA 1150_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

ROSA General-SFF

ROSA General-SFF

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

-1A

-1A

13 51Thursd ay, Aug ust 15 , 201 3

13 51Thursd ay, Aug ust 15 , 201 3

1

13 51Thursd ay, Aug ust 15 , 201 3

-1A

Page 14

5

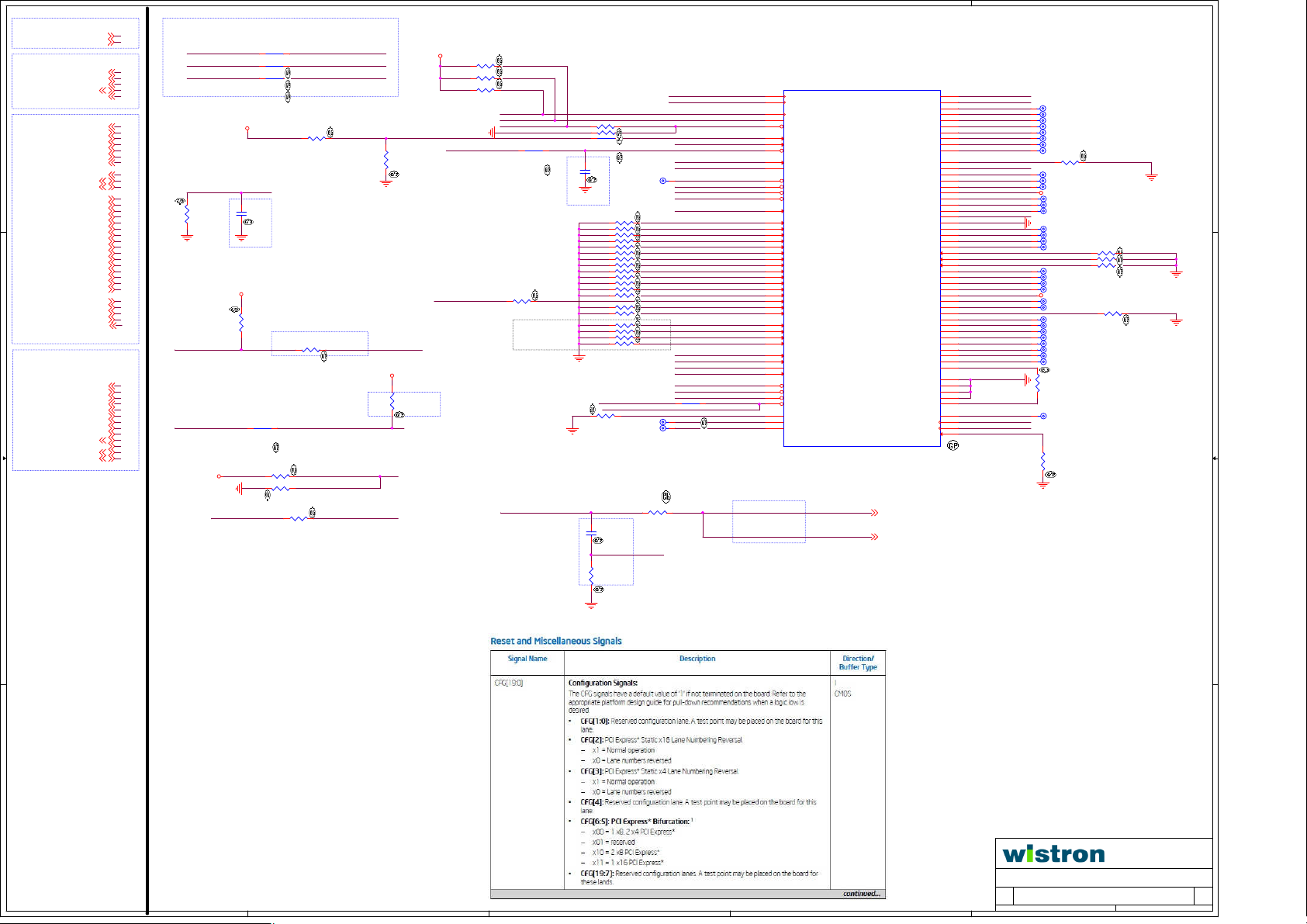

XDP for CPU

HSW_PCUDEBUG_010

HSW_PCUDEBUG_110

HSW_PCUDEBUG_210

D D

C C

HSW_PCUDEBUG_310

HSW_PCUDEBUG_410

HSW_PCUDEBUG_510

HSW_PCUDEBUG_610

HSW_PCUDEBUG_710

HSW_PCUDEBUG_810

HSW_PCUDEBUG_910

HSW_PCUDEBUG_1010

HSW_PCUDEBUG_1110

HSW_PCUDEBUG_1210

HSW_PCUDEBUG_1310

HSW_PCUDEBUG_1410

HSW_PCUDEBUG_1510

XDP for PCH

H_TDO10

H_TDI10

H_TMS10

H_TCK10

H_TRST_N10

H_PREQ_N10

H_PRDY_N10

XDP_DBRESET_N10

H_PWRGD10,19

HSW_XDP_MBP_010

HSW_XDP_MBP_110

HSW_PCUSTB_0_DP10

HSW_PCUSTB_0_DN10

HSW_PCUSTB_1_DP10

HSW_PCUSTB_1_DN10

XDP_PWR_DEBUG10

SMB_DATA_MAIN15,17,39

SMB_CLK_MAIN15,17,39

CK_100M_CPU_XDP_DN20

CK_100M_CPU_XDP_DP20

SW_ON_N19,39

PLTRST_CPU_N10,21

PCH_JTAG_RST_R19

PCH_JTAG_TDO19

PCH_JTAG_TDI19

PCH_JTAG_TMS19

PCH_JTAG_TCK19

VR_READY19,50

PWRGD_3V12,19,21,39

XDP for CPU

V_CPU_VCCIO_RIGHT

PLace Near CPU

PLTRST_CPU_N

H_PWRGD

SW_ON_N

R660 1KR2J-1-GP

(R)

R819 0R0402-PAD-1-GP

R519 1KR2J-1-GP

(R)

R637 0R0402-PAD-1-GP

XDP for PCH

PLace Near XDP CONN

1 2

R640 51R2F-2-GP(R)

1 2

R639 51R2F-2-GP(R)

1 2

R663 51R2F-2-GP

H_TCK TERMINATION PLACE

NEAR CPU WITHIN 1.1 INCH

1 2

R661 51R2F-2-GP

PLace Any where

1 2

1 2

1 2

1 2

LPC DEBUG PORT

L_AD019,39

L_AD119,39

L_AD219,39

L_AD319,39

L_FRAME_N19,39

CK_P_33M_LPCP8020

PCIRST3#39

12

C575 SCD1U16V2ZY-2GP

R816 51R2F-2-GP

(R)

12

4

H_TDI

H_TMS

H_TCK

H_TRST_N

H_RSTOUT_XDP_N

XDP_VR_READYVR_READY

V_1P05_PCH VCC3

12

R2216

51R2F-2-GP

12

(R)

R2217

825R2F-GP

PLace Near XDP CONN

XDP_PWRGD

12

R518

1KR2F-3-GP

(R)

XDP_PLTRST_N

Place R817, R764, R766, R812 close to PCH

Place R811, R818 close to PCH XDP connector side

1 2

SB3V

R811 200R2F-L-GP

1 2

R817 200R2F-L-GP

1 2

R766 200R2F-L-GP

PCH_JTAG_TCK

CK_100M_CPU_XDP_DN

CK_100M_CPU_XDP_DP

12

R818

100R2F-L1-GP-U

12

(R)

R2218

249R2F-GP

H_TDO

12

(R)

R2219

100R2F-L1-GP-U

R820 0R0402-PAD-1-GP

R821 0R0402-PAD-1-GP

12

R764

100R2F-L1-GP-U

1 2

1 2

PCH_JTAG_TDO

PCH_JTAG_TDI

PCH_JTAG_TMS

12

R812

100R2F-L1-GP-U

3

V_CPU_VCCIO_RIGHT V_CPU_VCCIO_RIGHT

H_PREQ_N

H_PRDY_N

HSW_PCUDEBUG_0

HSW_PCUDEBUG_1

HSW_PCUDEBUG_2

HSW_PCUDEBUG_3

HSW_XDP_MBP_0

HSW_XDP_MBP_1

HSW_PCUDEBUG_4

HSW_PCUDEBUG_5

HSW_PCUDEBUG_6

HSW_PCUDEBUG_7

XDP_PLTRST_N

XDP_PWR_DEBUG

XDP_VR_READY

SMB_DATA_MAIN

SMB_CLK_MAIN

H_TCK

CK_XDP_S_DN

CK_XDP_S_DP

XDPC1

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

(R)

SMC-CONN60A-GP

2

MH1

2

HSW_PCUSTB_0_DP

4

HSW_PCUSTB_0_DN

6

8

HSW_PCUDEBUG_8

10

HSW_PCUDEBUG_9

12

14

HSW_PCUDEBUG_10

16

HSW_PCUDEBUG_11

18

20

HSW_PCUSTB_1_DP

22

HSW_PCUSTB_1_DN

24

26

HSW_PCUDEBUG_12

28

HSW_PCUDEBUG_13

30

32

HSW_PCUDEBUG_14

34

HSW_PCUDEBUG_15

36

38

CK_XDP_S_DPXDP_PWRGD

40

CK_XDP_S_DN

42

44

H_RSTOUT_XDP_N

46

XDP_DBRESET_N

48

50

H_TDO

52

H_TRST_N

54

H_TDI

56

H_TMS

58

PRIVACY_MSR_EN_N HSW_PCUDEBUG_3

60

MH2

XDP_DBRESET_N

12

1 2

R867 1KR2J-1-GP

(R)

C576

SCD1U10V2KX-5GP

(R)

LPC DEBUG PORT

CK_P_33M_LPCP80

PCIRST3#

L_AD0

L_AD1

L_AD2

L_AD3

L_FRAME_N

LPC1

1

3

5

7

9

11

13

JWT-CONN14A-S3-GP

(R)

Pin height 2.3mm

2

4

6

8

10

12

14

INIT_3V

FWH_ID0

1

VCC3

12

R638

4K7R2J-2-GP

VCC3

VCC

12

R662

10KR2J-3-GP

(R)

B B

PWRGD_3V

1 2

R810 1KR2J-1-GP

(R)

PCH_JTAG_TDO

PCH_JTAG_TDI

PCH_JTAG_TMS

SB3V

1

1

1

TP87 TPAD28

TP105 TPAD28

TP104 TPAD28

12

C1672

SC1U10V2KX-1GP

(R)

PCH_JTAG_RST_R

SB3V

12

12

R712

10KR2J-3-GP

(R)

R765

20KR2F-L-GP

2012/12/15 delete reserve R815

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

XDP/80 PORT HEAD ER/APS

XDP/80 PORT HEAD ER/APS

XDP/80 PORT HEAD ER/APS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ROSA General-SFF

C

ROSA General-SFF

C

ROSA General-SFF

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

14 51Thursday, August 15, 2013

14 51Thursday, August 15, 2013

14 51Thursday, August 15, 2013

-1A

-1A

-1A

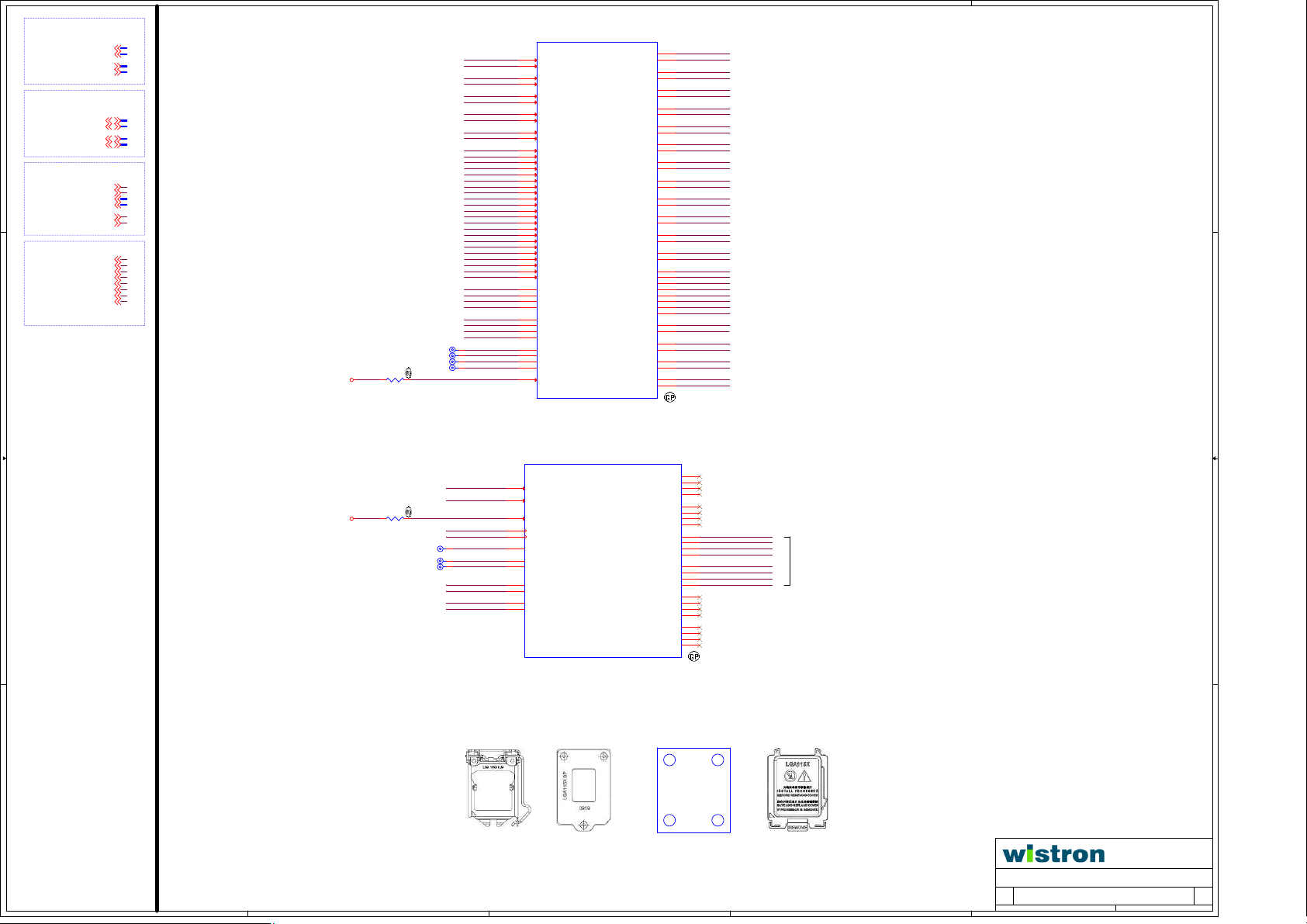

Page 15

5

DDR DATA

DDR CMD/ADD

D D

DDR CTRL

DDR CLOCK

DDR OTHERS

C C

M_DATA_A[0..63]12

M_DQS_A_DP[0..7]12

M_DQS_A_DN[0..7]12