DATEL ADS-CCD1201MM, ADS-CCD1201MC, ADS-BCCD1201 Datasheet

INNOVATION and EX C ELL E N C E

®

®

ADS-CCD1201

12-Bit, 1.2MHz, Sampling A/D’s

Optimized for CCD Applications

GENERAL DESCRIPTION

The functionally complete, easy-to-use ADS-CCD1201 is a

12-bit, 1.2MHz Sampling A/D Converter whose performance

and production testing have been optimized for use in

electronic imaging applications, particularly those employing

charge coupled devices (CCD’s) as their photodetectors. The

ADS-CCD1201 delivers the lowest noise (400µVrms) and the

best differential nonlinearity error (±0.35LSB max.) of any

commercially available 12-bit A/D in its speed class. It can

respond to full scale input steps (from empty to full well) with

less than a single count of error, and its input is immune to

overvoltages that may occur due to blooming.

Packaged in an industry-standard, 24-pin, ceramic DDIP, the

ADS-CCD1201 requires ±15V (or ±12V) and +5V supplies and

typically consumes 1.7 (1.4) Watts. The device is 100%

production tested for all critical performance parameters and is

fully specified over both the 0 to +70°C and –55 to +125°C

operating temperature ranges.

For those applications using correlated double sampling, the

ADS-CCD1201 can be supplied without its internal sample-

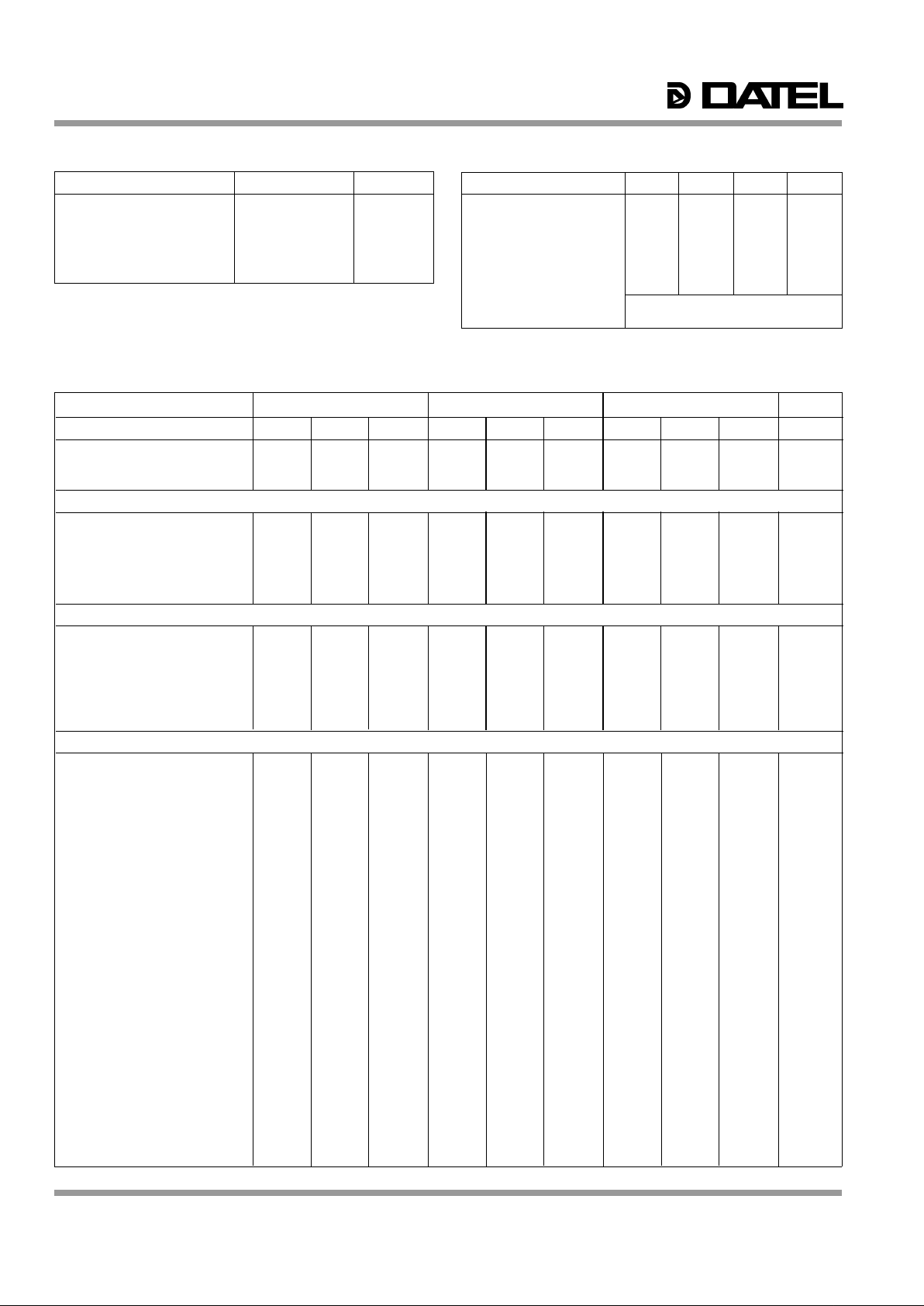

Figure 1. ADS-CCD1201 Functional Block Diagram

INPUT/OUTPUT CONNECTIONS

PIN FUNCTION PIN FUNCTION

1 BIT 12 (LSB) 24 –12V/–15V SUPPLY

2 BIT 11 23 GROUND

3 BIT 10 22 +12V/+15V SUPPLY

4 BIT 9 21 +10V REFERENCE OUT

5 BIT 8 20 ANALOG INPUT

6 BIT7 19 GROUND

7 BIT 6 18 NO CONNECT

8 BIT 5 17 NO CONNECT

9 BIT 4 16 START CONVERT

10 BIT 3 15 EOC

11 BIT 2 14 GROUND

12 BIT 1 (MSB) 13 +5V SUPPLY

• Unipolar input range (0 to +10V)

• 1.2MHz sampling rate

• 4096-to-1 dynamic range (72.2dB)

• Low noise, 400µVrms (1/6 of an LSB)

• Outstanding differential nonlinearity error (±0.35 LSB max.)

• Small, 24-pin ceramic DDIP

• Low power, 1.7 Watts

• Operates from ±12V or ±15V supplies

• Edge-triggered, no pipeline delay

FEATURES

hold amplifier. DATEL will also entertain discussions about

including the CDS circuit internal to the ADS-CCD1201. Please

contact us for more details.

DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1151 (U.S.A.) • Tel: (508) 339-3000 Fax: (508)339-6356 • For immediate assistance: (800) 233-2765

FLASH

ADC

REF

DAC

REGISTER

REGISTER

DIGITAL

CORRECTION

LOGIC

12 BIT 1 (MSB)

11 BIT 2

10 BIT 3

9 BIT 4

8 BIT 5

7 BIT 6

6 BIT 7

5 BIT 8

4 BIT 9

3 BIT 10

2 BIT 11

1 BIT 12 (LSB)

TIMING AND

CONTROL LOGIC

ANALOG INPUT 20

START CONVERT 16

EOC 15

13

+5V SUPPLY

17, 18

NO CONNECT

22

+12V/+15V SUPPLY

14, 19, 23

GROUND

24

–12V/–15V SUPPLY

S1

S2

S/H

BUFFER

–

+

+10V REFERENCE

21

ADS-CCD1201

®

®

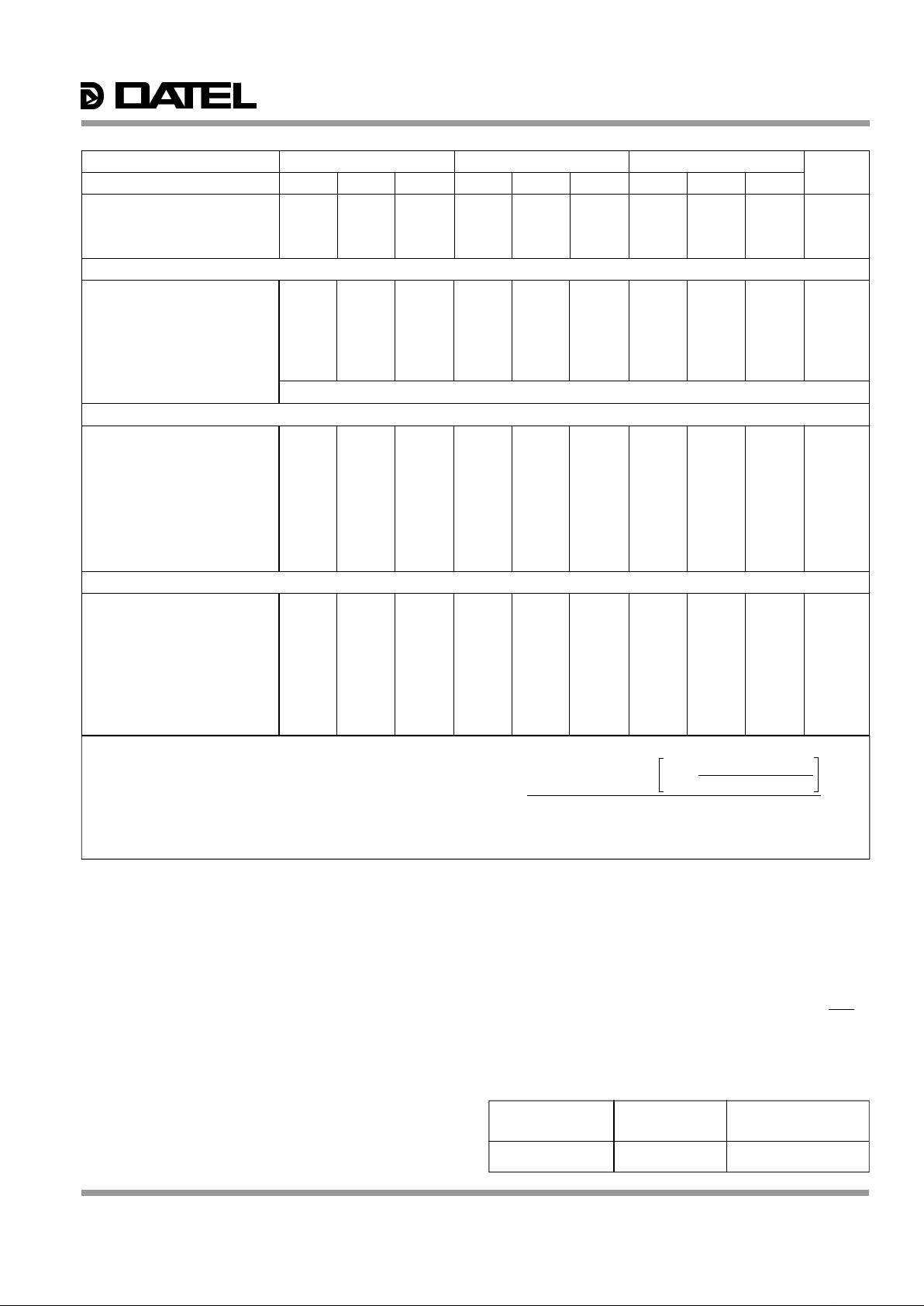

FUNCTIONAL SPECIFICATIONS

(TA = +25°C, ±Vcc = ±15V (or ±12V), +VDD = +5V, 1.2MHz sampling rate, and a minimum 1 minute warmup➀ unless otherwise specified.)

+25°C 0 to +70°C –55 to +125° C

ANALOG INPUT MIN. TYP. MAX. MIN. TYP. MAX. MIN. TYP. MAX. UNITS

Input Voltage Range ➁ — 0 to +10 — — 0 to +10 — — 0 to +10 — Volts

Input Resistance — 1 — — 1 — — 1 — kΩ

Input Capacitance — 7 15 — 7 15 — 7 15 pF

DIGITAL INPUTS

Logic Levels

Logic "1" +2.0 — — +2.0 — — +2.0 — — Volts

Logic "0" — — +0.8 — — +0.8 — — +0.8 Volts

Logic Loading "1" — — +20 — — +20 — — +20 µA

Logic Loading "0" — — –20 — — –20 — — –20 µA

Start Convert Positive Pulse Width ➂ — 100 — — 100 — — 100 — ns

STATIC PERFORMANCE

Resolution — 12 — — 12 — — 12 — Bits

Integral Nonlinearity (fin = 10kHz) — ±0.5 — — ±0.5 — — ±1 — LSB

Differential Nonlinearity (fin = 10kHz) — +0.25 ±0.35 — ±0.25 ±0.35 — ±0.35 ±0.75 LSB

Full Scale Absolute Accuracy — +0.1 ±0.3 — ±0.2 ±0.5 — ±0.3 ±0.5 %FSR

Offset Error (Tech Note 2) — ±0.05 ±0.15 — ±0.1 ±0.15 — ±0.15 ±0.4 %FSR

Gain Error (Tech Note 2) — ±0.1 ±0.3 — ±0.2 ±0.5 — ±0.3 ±0.5 %

No Missing Codes (fin = 10kHz) 12 — — 12 — — 12 — — Bits

DYNAMIC PERFORMANCE

Peak Harmonics (–0.5dB)

dc to 100kHz — –86 –80 — –86 –80 — –82 –76 dB

100kHz to 500kHz — –84 –78 — –84 –78 — –81 –75 dB

Total Harmonic Distortion (–0.5dB)

dc to 100kHz — –84 –79 — –84 –79 — –77 –71 dB

100kHz to 500kHz — –82 –77 — –82 –77 — –76 –70 dB

Signal-to-Noise Ratio

(w/o distortion, –0.5dB)

dc to 100kHz 72 73 — 72 73 — 70 72 — dB

100kHz to 500kHz 71 72 — 71 72 — 70 72 — dB

Signal-to-Noise Ratio ➃

(8 distortion, –0.5dB)

dc to 100kHz 71 73 — 71 73 — 68 71 — dB

100kHz to 500kHz 71 72 — 71 72 — 68 71 — dB

Two-tone Intermodulation Distortion

(fin = 100kHz, 240kHz

fs = 1.2MHz, –0.5dB) — –85 — — –84 — — –83 — dB

Noise — 400 — — 500 — — 700 — µVrms

Input Bandwidth (–3dB)

Small Signal (–20dB input) — 7.5 — — 7.5 — — 7.5 — MHz

Large Signal(–0.5dB input) — 6 — — 6 — — 6 — MHz

Feedthrough Rejection

(fin = 500kHz) — 84 — — 84 — — 84 — dB

Slew Rate — ±60 — — ±60 — — ±60 — V/µs

Aperture Delay Time — ±20 — — ±20 — — ±20 — ns

Aperture Uncertainty — 5 — — 5 — — 5 — ps rms

S/H Acquisition Time

( to ±0.01%FSR, 10V step) 360 400 440 360 400 440 360 400 440 ns

Overvoltage Recovery Time ➄ — 400 833 — 400 833 — 400 833 ns

A/D Conversion Rate 1.2 — — 1.2 — — 1.2 — — MHz

ABSOLUTE MAXIMUM RATINGS

PARAMETERS LIMITS UNITS

+12V/+15V Supply (Pin 22) 0 to +16 Volts

–12V/–15V Supply (Pin 24) 0 to –16 Volts

+5V Supply (Pin 13) 0 to +6 Volts

Digital Input (Pin 16) –0.3 to +V

DD +0.3 Volts

Analog Input (Pin 20) –4 to +17 Volts

Lead Temp. (10 seconds) +300 °C

PHYSICAL/ENVIRONMENTAL

PARAMETERS MIN. TYP. MAX. UNITS

Operating Temp. Range, Case

ADS-CCD1201MC 0 — +70 °C

ADS-CCD1201MM –55 — +125 °C

Thermal Impedance

θ

jc — 5 — °C/Watt

θ

ca — 24 — °C/Watt

Storage Temperature Range –65 – +150 °C

Package Type 24-pin, metal-sealed ceramic DDIP

Weight 0.42 ounces (12 grams)

2.

ADS-CCD1201

®

®

Footnotes:

➀ All power supplies must be on before applying a start convert pulse. All

supplies and the clock (START CONVERT) must be present during warmup

periods. The device must be continuously converting during this time. There is

a slight degradation in performance when using ±12V supplies.

➁ Contact DATEL for availability of other input voltage ranges.

➂ A 100ns wide start convert pulse is used for all production testing.

➃ Effective bits is equal to:

➄ This is the time required before the A/D output data is valid after

the analog input is back within the specified range.

+25°C 0 to +70°C –55 to +125°C

ANALOG OUTPUT MIN. TYP. MAX. MIN. TYP. MAX. MIN. TYP. MAX. UNITS

Internal Reference

Voltage +9.95 +10.0 +10.05 +9.95 +10.0 +10.05 +9.95 +10.0 +10.05 Volts

Drift — ±5 — — ±5 — — ±5 — ppm/ºC

External Current — — 1.5 — — 1.5 — — 1.5 mA

DIGITAL OUTPUTS

Logic Levels

Logic "1" +2.4 — — +2.4 — — +2.4 — — Volts

Logic "0" — — +0.4 — — +0.4 — — +0.4 Volts

Logic Loading “1" — — –4 — — –4 — — –4 mA

Logic Loading "0" — — +4 — — +4 — — +4 mA

Delay, Falling Edge of EOC

to Output Data Valid — — 35 — — 35 — — 35 ns

Output Coding Straight Binary

POWER REQUIREMENTS, ±15V

Power Supply Range

+15V Supply +14.5 +15.0 +15.5 +14.5 +15.0 +15.5 +14.5 +15.0 +15.5 Volts

–15V Supply –14.5 –15.0 –15.5 –14.5 –15.0 –15.5 –14.5 –15.0 –15.5 Volts

+5V Supply +4.75 +5.0 +5.25 +4.75 +5.0 +5.25 +4.75 +5.0 +5.25 Volts

Power Supply Current

+15V Supply — +50 +65 — +50 +65 — +50 +65 mA

–15V Supply — –40 –50 — –40 –50 — –40 –50 mA

+5V Supply — +70 +85 — +70 +85 — +70 +85 mA

Power Dissipation — 1.7 1.9 — 1.7 1.9 — 1.7 1.9 Watts

Power Supply Rejection — — ±0.01 — — ±0.01 — — ±0.01 %FSR/%V

POWER REQUIREMENTS, ±12V

Power Supply Range

+12V Supply +11.5 +12.0 +12.5 +11.5 +12.0 +12.5 +11.5 +12.0 +12.5 Volts

–12V Supply –11.5 –12.0 –12.5 –11.5 –12.0 –12.5 –11.5 –12.0 –12.5 Volts

+5V Supply +4.75 +5.0 +5.25 +4.75 +5.0 +5.25 +4.75 +5.0 +5.25 Volts

Power Supply Current

+12V Supply — +50 +65 — +50 +65 — +50 +65 mA

–12V Supply — –40 –48 — –40 –48 — –40 –48 mA

+5V Supply — +70 +80 — +70 +80 — +70 +80 mA

Power Dissipation — 1.4 1.6 — 1.4 1.6 — 1.4 1.6 Watts

Power Supply Rejection — — ±0.01 — — ±0.01 — — ±0.01 %FSR/%V

(SNR + Distortion) – 1.76 + 20 log

Full Scale Amplitude

Actual Input Amplitude

6.02

TECHNICAL NOTES

1. Obtaining fully specified performance from the ADS-CCD1201

requires careful attention to pc-card layout and power supply

decoupling. The device’s analog and digital ground systems are

connected to each other internally. For optimal performance, tie

all ground pins (14, 19, and 23) directly to a large analog

ground plane beneath the package.

Bypass all power supplies, as well as the REFERENCE

OUTPUT (pin 21), to ground with 4.7µF tantalum capacitors in

parallel with 0.1µF ceramic capacitors. Locate the bypass

capacitors as close to the unit as possible. If the user-installed

offset and gain adjusting circuit shown in Figure 2 is used, also

locate it as close to the ADS-CCD1201 as possible.

2. ADS-CCD1201 achieves its specified accuracies without

external calibration. If required, the device’s small initial offset

and gain errors can be reduced to zero using the input circuit of

Figure 2. When using this circuit, or any similar offset and gaincalibration hardware, make adjustments following warmup. To

avoid interaction, always adjust offset before gain.

3. When operating the ADS-CCD1201 from ±12V supplies, do not

drive external circuitry with the REFERENCE OUTPUT (pin 21).

The reference’s accuracy and drift specifications may not be

met, and loading the circuit may cause accuracy errors within

the converter.

4. A passive bandpass filter is used at the input of the A/D for all

production testing.

5. Applying a start pulse while a conversion is in progress (EOC =

logic "1") initiates a new and inaccurate conversion cycle. Data

for the interrupted and subsequent conversions will be invalid.

Input Voltage Zero Adjust Gain Adjust

Range +1/2 LSB +FS – 1 1/2 LSB

0 to +10V +1.2207mV +9.99634V

Table 1. Zero and Gain Adjust

3.

Loading...

Loading...