Page 1

X20C04

4K X20C04 512 x 8 Bit

Nonvolatile Static RAM

FEATURES

• High Reliability

—Endurance: 1,000,000 Nonvolatile Store

Operations

—Retention: 100 Years Minimum

• Power-on Recall

—E2PROM Data Automatically Recalled Into

SRAM Upon Power-up

• Lock Out Inadvertent Store Operations

• Low Power CMOS

—Standby: 250µA

• Infinite E

and Write Cycles

2

PROM Array Recall, and RAM Read

• Compatible with X2004

PIN CONFIGURATION

DESCRIPTION

The Xicor X20C04 is a 512 x 8 NOVRAM featuring a

static RAM overlaid bit-for-bit with a nonvolatile electrically erasable PROM (E2PROM). The X20C04 is fabricated with advanced CMOS floating gate technology to

achieve low power and wide power-supply margin. The

X20C04 features the JEDEC approved pinout for bytewide memories, compatible with industry standard RAMs,

ROMs, EPROMs, and E2PROMs.

The NOVRAM design allows data to be easily transferred from RAM to E2PROM (store) and E2PROM to

RAM (recall). The store operation is completed in 5ms or

less and the recall operation is completed in 5µs or less.

Xicor NOVRAMS are designed for unlimited write

operations to RAM, either from the host or recalls from

E2PROM, and a minimum 1,000,000 store operations to

the E2PROM. Data retention is specified to be greater

than 100 years.

I/O

I/O

I/O

V

NE

NC

A

A

A

A

A

A

A

A

SS

7

A

NCNENC

(TOP VIEW)

2

I/O1I/O

LCC

PLCC

X20C04

SS

NC

V

VCCWE

NC

29

28

27

26

25

24

23

22

21

I/O3I/O4I/O

3825 FHD F03

A

8

NC

NC

NC

OE

NC

CE

I/O

7

I/O

6

5

PLASTIC

CERDIP

1

2

3

7

4

6

5

5

6

4

7

3

2

1

0

0

1

2

8

9

10

11

12

13

14

X20C04

28

27

26

25

24

23

22

21

20

19

18

17

16

15

3825 FHD F02

V

WE

NC

A

NC

NC

OE

NC

CE

I/O

I/O

I/O

I/O

I/O

CC

8

4321323130

A

5

6

6

A

5

7

A

4

8

A

3

9

A

2

10

A

1

11

A

I/O

NC

0

12

13

0

14 15 16 17 18 19 20

7

6

5

4

3

©Xicor, Inc. 1992, 1995, 1996 Patents Pending Characteristics subject to change without notice

3825-2.8 7/31/97 T4/C0/D0 SH

1

Page 2

X20C04

PIN DESCRIPTIONS

Addresses (A0–A8)

The Address inputs select an 8-bit memory location

during a read or write operation.

Chip Enable (CE)

The Chip Enable input must be LOW to enable all read/

write operations. When CE is HIGH, power consumption

is reduced.

Output Enable (OE)

The Output Enable input controls the data output buffers

and is used to initiate read and recall operations. Output

Enable LOW disables a store operation regardless of

the state of CE, WE, or NE.

Data In/Data Out (I/O0–I/O7)

Data is written to or read from the X20C04 through the

I/O pins. The I/O pins are placed in the high impedance

state when either CE or OE is HIGH or when NE is LOW.

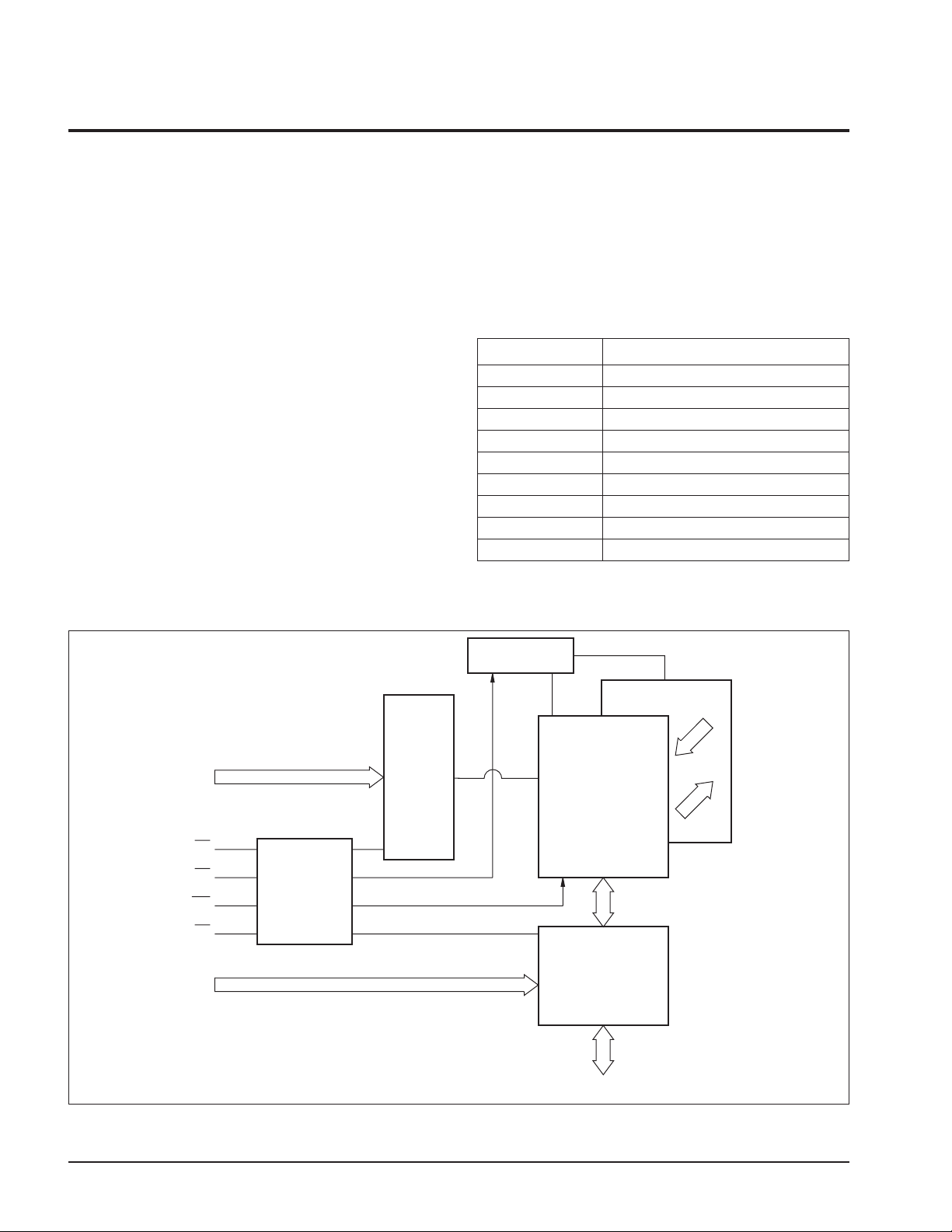

FUNCTIONAL DIAGRAM

Write Enable (WE)

The Write Enable input controls the writing of data to

both the static RAM and stores to the E2PROM.

Nonvolatile Enable (NE)

The Nonvolatile Enable input controls all accesses to

the E2PROM array (store and recall functions).

PIN NAMES

Symbol Description

A0–A

8

I/O0–I/O

7

Address Inputs

Data Input/Output

WE Write Enable

CE Chip Enable

OE Output Enable

NE Nonvolatile Enable

V

CC

V

SS

+5V

Ground

NC No Connect

3825 PGM T01

A3–A

A0–A

A7–A

CE

OE

WE

NE

VCC SENSE

EEPROM ARRA Y

6

CONTROL

LOGIC

2

8

ROW

SELECT

512 x 8

SRAM

ARRAY

COLUMN

SELECT

&

I/OS

I/O0–I/O

7

RECALL

STORE

3825 FHD F01

2

Page 3

X20C04

DEVICE OPERATION

The CE, OE, WE and NE inputs control the X20C04

operation. The X20C04 byte-wide NOVRAM uses a

2-line control architecture to eliminate bus contention in

a system environment. The I/O bus will be in a high

impedance state when either OE or CE is HIGH, or

when NE is LOW.

RAM Operations

RAM read and write operations are performed as they

would be with any static RAM. A read operation requires

CE and OE to be LOW with WE and NE HIGH. A write

operation requires CE and WE to be LOW with NE

HIGH. There is no limit to the number of read or write

operations performed to the RAM portion of the X20C04.

Nonvolatile Operations

With NE LOW, recall operation is performed in the same

manner as RAM read operation. A recall operation

causes the entire contents of the E2PROM to be written

into the RAM array. The time required for the operation

to complete is 5µs or less. A store operation causes the

entire contents of the RAM array to be stored in the

nonvolatile E2PROM. The time for the operation to

complete is 5ms or less.

Power-Up Recall

Upon power-up (VCC), the X20C04 performs an automatic array recall. When VCC minimum is reached, the

recall is initiated, regardless of the state of CE, OE, WE

and NE.

Write Protection

The X20C04 has five write protect features that are

employed to protect the contents of both the nonvolatile

memory and the RAM.

•VCC Sense—All functions are inhibited when VCC is

≤ 3.5V.

• A RAM write is required before a Store Cycle is

initiated.

• Write Inhibit—Holding either OE LOW, WE HIGH,

CE HIGH, or NE HIGH during power-up and power-

down will prevent an inadvertent store operation.

• Noise Protection—A combined WE, NE, OE and

CE pulse of less than 20ns will not initiate a Store

Cycle.

• Noise Protection—A combined WE, NE, OE and

CE pulse of less than 20ns will not initiate a recall

cycle.

SYMBOL TABLE

WAVEFORM

INPUTS

Must be

steady

May change

from LOW

to HIGH

May change

from HIGH

to LOW

Don’t Care:

Changes

Allowed

N/A

OUTPUTS

Will be

steady

Will change

from LOW

to HIGH

Will change

from HIGH

to LOW

Changing:

State Not

Known

Center Line

is High

Impedance

3

Page 4

X20C04

ABSOLUTE MAXIMUM RATINGS*

Temperature under Bias .................. –65°C to +135°C

Storage Temperature ....................... –65°C to +150°C

Voltage on any Pin with

Respect to V

.......................................

SS

–1V to +7V

D.C. Output Current ...........................................10mA

Lead Temperature (Soldering, 10 seconds)..... 300°C

*COMMENT

Stresses above those listed under “Absolute Maximum

Ratings” may cause permanent damage to the device.

This is a stress rating only and the functional operation of

the device at these or any other conditions above those

indicated in the operational sections of this specification is

not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

RECOMMENDED OPERATING CONDITIONS

Temperature Min. Max.

Commercial 0°C +70°C

Industrial –40°C +85°C

Military –55°C +125°C

3825 PGM T02.1

Supply Voltage Limits

X20C04 5V ±10%

3825 PGM T03

D.C. OPERATING CHARACTERISTICS (Over recommended operating conditions unless otherwise specified.)

Limits

Symbol Parameter Min. Max. Units Test Conditions

l

CC1

VCC Current (Active) 100 mA NE = WE = VIH, CE = OE = V

IL

Address Inputs = 0.4V/2.4V levels

@ f = 5MHz. All I/Os = Open

I

CC2

VCC Current During Store 10 mA All Inputs = V

IH

All I/Os = Open

I

SB1

VCC Standby Current 10 mA CE = V

IH

(TTL Input) All Other Inputs = VIH, All I/Os = Open

I

SB2

VCC Standby Current 250 µA All Inputs = V

CC

– 0.3V

(CMOS Input) All I/Os = Open

I

I

V

V

V

V

LI

LO

IL

IH

OL

OH

(1)

(1)

Input Leakage Current 10 µAVIN = VSS to V

Output Leakage Current 10 µAV

= VSS to VCC, CE = V

OUT

Input LOW Voltage –1 0.8 V

Input HIGH Voltage 2 V

+ 0.5 V

CC

Output LOW Voltage 0.4 V IOL = 2.1mA

Output HIGH Voltage 2.4 V IOH = –400µA

CC

IH

3825 PGM T04.3

POWER-UP TIMING

Symbol Parameter Max. Units

(2)

t

PUR

t

PUW

(2)

Power-Up to RAM Operation 100 µs

Power-Up to Nonvolatile Operation 5 ms

CAPACITANCE TA = +25°C, F = 1MHz, VCC = 5V.

Symbol Test Max. Units Conditions

(2)

C

I/O

(2)

C

IN

Notes: (1) VIL min. and VIH max. are for reference only and are not tested.

(2) This parameter is periodically sampled and not 100% tested.

Input/Output Capacitance 10 pF V

Input Capacitance 6 pF VIN = 0V

4

3825 PGM T05

= 0V

I/O

3825 PGM T06.1

Page 5

X20C04

ENDURANCE AND DATA RETENTION

Parameter Min. Units

Endurance 100,000 Data Changes Per Bit

Store Cycles 1,000,000 Store Cycles

Data Retention 100 Years

MODE SELECTION

CE WE NE OE Mode I/O Power

H X X X Not Selected Output High Z Standby

L H H L Read RAM Output Data Active

L L H H Write “1” RAM Input Data High Active

L L H H Write “0” RAM Input Data Low Active

L H L L Array Recall Output High Z Active

L L L H Nonvolatile Storing Output High Z Active

L H H H Output Disabled Output High Z Active

L L L L Not Allowed Output High Z Active

L H L H No Operation Output High Z Active

3825 PGM T07.1

3825 PGM T09.1

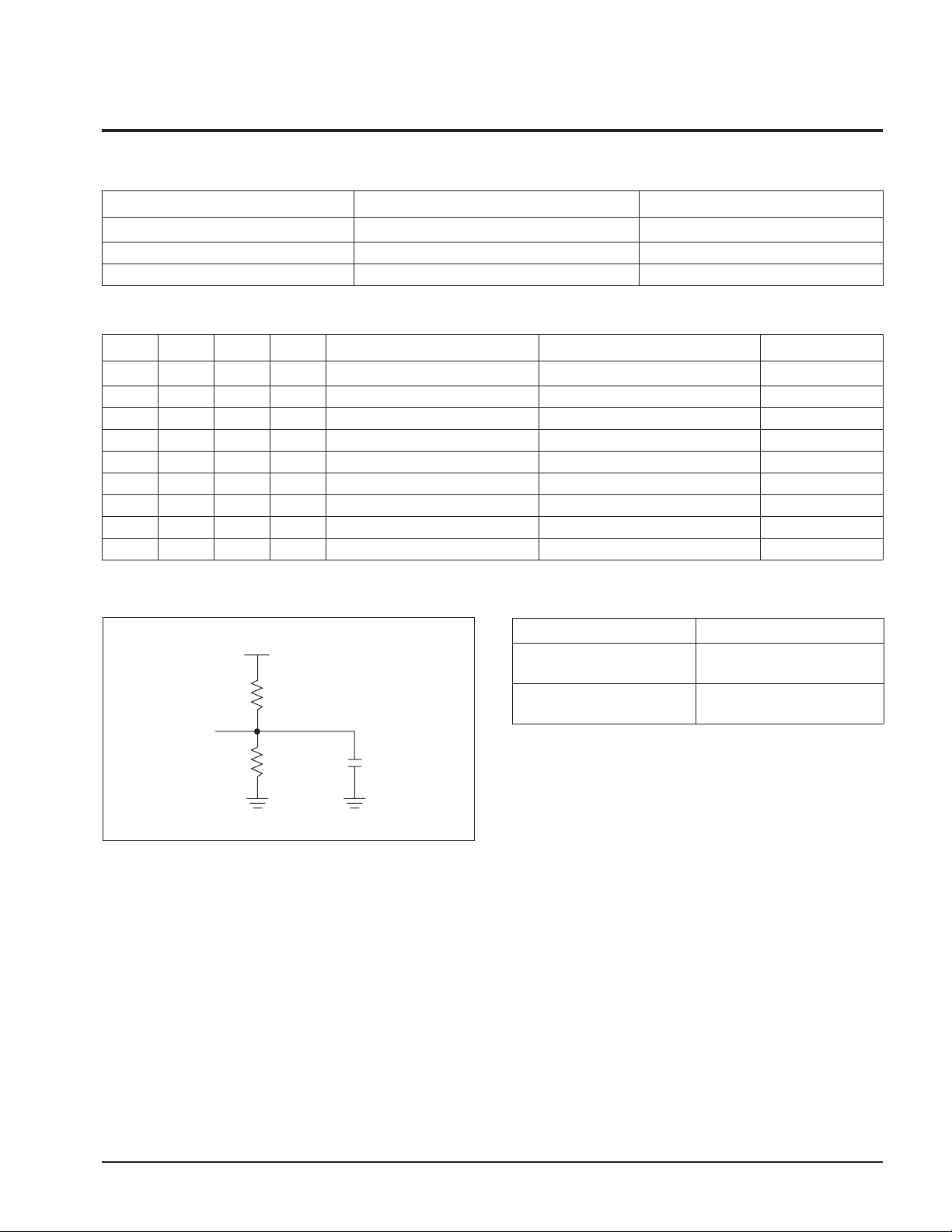

EQUIVALENT A.C. LOAD CIRCUIT A.C. CONDITIONS OF TEST

Input Pulse Levels 0V to 3V

5V

Input Rise and

Fall Times 10ns

1.92KΩ

Input and Output

Timing Levels 1.5V

OUTPUT

1.37KΩ

100pF

3825 FHD F04.1

3825 PGM T08.2

5

Page 6

X20C04

A.C. CHARACTERISTICS (Over the recommended operating conditions unless otherwise specified)

Read Cycle Limits

X20C04-15 X20C04-20 X20C04-25 X20C04

Symbol Parameter Min. Max. Min. Max. Min. Max. Min. Max. Units

t

RC

t

CE

t

AA

t

OE

(3)

t

LZ

(3)

t

OLZ

(3)

t

HZ

(3)

t

OHZ

t

OH

Read Cycle

ADDRESS

CE

OE

Read Cycle Time 150 200 250 300 ns

Chip Enable Access Time 150 200 250 300 ns

Address Access Time 150 200 250 300 ns

Output Enable Access Time 50 70 100 150 ns

Chip Enable to Output in Low Z 0 0 0 0 ns

Output Enable to Output in Low Z 0 0 0 0 ns

Chip Disable to Output in High Z 80 100 100 100 ns

Output Disable to Output in High Z 80 100 100 100 ns

Output Hold From Address Change 0 0 0 0 ns

3825 PGM T10

t

RC

t

CE

t

t

OE

OE

V

IH

WE

DATA I/O

Note: (3) tLZ min., tHZ, t

CL = 5pF from the point when CE or OE return HIGH (whichever occurs first) to the time when the outptus are no longer driven.

min., and t

OLZ

t

OLZ

t

LZ

DATA VALID

are periodically sampled and not 100% tested. tHZ max. and t

OHZ

6

t

t

OH

AA

t

HZ

DATA VALID

max. are measured, with

OHZ

t

OHZ

3825 FHD F05

Page 7

X20C04

Write Cycle Limits

X20C04-15 X20C04-20 X20C04-25 X20C04

Symbol Parameter Min. Max. Min. Max. Min. Max. Min. Max. Units

t

WC

t

CW

t

AS

t

WP

t

WR

t

DW

t

DH

(4)

t

WZ

(4)

t

OW

(4)

t

OZ

WE Controlled Write Cycle

Write Cycle Time 150 200 250 300 ns

Chip Enable to End of Write Input 150 200 250 300 ns

Address Setup Time 0 0 0 0 ns

Write Pulse Width 100 120 150 200 ns

Write Recovery Time 0 0 0 0 ns

Data Setup to End of Write 100 120 150 200 ns

Data Hold Time 0 0 0 0 ns

Write Enable to Output in High Z 80 100 100 100 ns

Output Active from End of Write 5 5 5 5 ns

Output Enable to Output in High Z 80 100 100 100 ns

3825 PGM T11

t

WC

ADDRESS

OE

t

CW

CE

t

AS

WE

t

OZ

DATA OUT

DATA IN

Note: (4) tWZ, tOW, and tOZ are periodically sampled and not 100% tested.

t

WP

t

DW

DATA VALID

t

DH

t

WR

t

OW

3825 FHD F06

7

Page 8

X20C04

CE Controlled Write Cycle

ADDRESS

t

WC

OE

CE

WE

DATA OUT

DATA IN

V

IH

t

CW

t

AS

t

WZ

t

WP

t

DW

DATA VALID

t

DH

t

WR

t

OW

3825 FHD F07.1

8

Page 9

X20C04

STORE CYCLE LIMITS

X20C04-15 X20C04-20 X20C04-25 X20C04

Symbol Parameter Min. Max. Min. Max. Min. Max. Min. Max. Units

t

STC

t

SP

t

NHZ

t

OEST

t

SOE

t

NS

Store Timing

NE

Store Cycle Time 5 5 5 5 ms

Store Pulse Width 100 120 150 200 ns

Nonvolatile Enable to 80 100 100 100 ns

Output in High Z

Output Enable From 10 10 10 10 ns

End of Store

OE Disable to Store 20 20 20 20 ns

Function

NE Setup Time from WE 0000ns

3825 PGM T09

t

STC

t

SP

t

SOE

t

OEST

OE

WE

t

NS

CE

t

NHZ

DATA I/O

V

CC

Note: (5) X20C04 VCC min. = 4.5V

The Store Pulse Width (tSP) is a minimum time that NE, WE and CE must be LOW simultaneously.

V

CC

MIN (5)

3825 FHD F15.1

9

Page 10

X20C04

ARRAY RECALL CYCLE LIMITS

X20C04-15 X20C04-20 X20C04-25 X20C04

Symbol Parameter Min. Max. Min. Max. Min. Max. Min. Max. Units

t

RCC

(6)

t

RCP

t

RWE

Array Recall Cycle

ADDRESS

NE

OE

Array Recall Cycle Time 5 5 5 5 µs

Recall Pulse Width to 0.1 1 0.12 1 0.15 1 0.2 1 µs

InitiateRecall

WE Setup Time to NE 0000ns

3825 PGM T13.1

t

RCC

t

RCP

WE

CE

DATA I/O

Note: (6) The Recall Pulse Width (t

NE and CE.

t

RWE

) is a minimum time that NE, OE and CE must be LOW simultaneously to insure data integrity,

RCP

3825 FHD F10

10

Page 11

X20C04

PACKAGING INFORMATION

28-LEAD HERMETIC DUAL IN-LINE PACKAGE TYPE D

1.490 (37.85) MAX.

0.610 (15.49)

0.500 (12.70)

SEATING

PLANE

0.150 (3.81) MIN.

PIN 1

0.200 (5.08)

0.125 (3.18)

0.110 (2.79)

0.090 (2.29)

TYP. 0.100 (2.54)

0.015 (0.38)

0.008 (0.20)

0.065 (1.65)

0.038 (0.97)

TYP. 0.055 (1.40)

0.620 (15.75)

0.590 (14.99)

TYP. 0.614 (15.60)

0.005 (0.127) MIN.

0.100 (2.54) MAX.

0.232 (5.90) MAX.

0.060 (1.52)

0.015 (0.38)

0.023 (0.58)

0.014 (0.36)

TYP. 0.018 (0.46)

0°

15°

NOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

11

3926 FHD F08

Page 12

X20C04

PACKAGING INFORMATION

PIN 1 INDEX

PIN 1

28-LEAD PLASTIC DUAL IN-LINE PACKAGE TYPE P

1.470 (37.34)

1.400 (35.56)

1.300 (33.02)

REF.

0.557 (14.15)

0.510 (12.95)

0.085 (2.16)

0.040 (1.02)

SEATING

PLANE

0.160 (4.06)

0.120 (3.05)

0.110 (2.79)

0.090 (2.29)

0.065 (1.65)

0.040 (1.02)

0.625 (15.88)

0.590 (14.99)

TYP. 0.010 (0.25)

0°

15°

NOTE:

1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

2. PACKAGE DIMENSIONS EXCLUDE MOLDING FLASH

0.160 (4.06)

0.125 (3.17)

0.030 (0.76)

0.015 (0.38)

0.022 (0.56)

0.014 (0.36)

12

3926 FHD F04

Page 13

X20C04

PACKAGING INFORMATION

32-PAD CERAMIC LEADLESS CHIP CARRIER PACKAGE TYPE E

0.015 (0.38)

0.003 (0.08)

0.300 (7.62)

PIN 1

BSC

0.150 (3.81) BSC

0.020 (0.51) x 45° REF.

0.095 (2.41)

0.075 (1.91)

0.022 (0.56)

0.006 (0.15)

DIA.

0.200 (5.08)

BSC

0.028 (0.71)

0.022 (0.56)

(32) PLCS.

0.015 (0.38)

MIN.

0.050 (1.27) BSC

0.458 (11.63)

0.442 (11.22)

0.458 (11.63)

––

0.055 (1.39)

0.045 (1.14)

TYP. (4) PLCS.

0.040 (1.02) x 45° REF.

TYP. (3) PLCS.

0.560 (14.22)

0.540 (13.71)

0.120 (3.05)

0.060 (1.52)

0.558 (14.17)

––

0.088 (2.24)

0.050 (1.27)

0.400 (10.16)

BSC

PIN 1 INDEX CORNER

NOTE:

1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

2. TOLERANCE: ±1% NLT ±0.005 (0.127)

13

3926 FHD F14

Page 14

X20C04

32-LEAD PLASTIC LEADED CHIP CARRIER PACKAGE TYPE J

0.420 (10.67)

0.050 (1.27) TYP.

0.021 (0.53)

0.013 (0.33)

TYP. 0.017 (0.43)0.045 (1.14) x 45°

0.495 (12.57)

0.485 (12.32)

TYP. 0.490 (12.45)

0.453 (11.51)

0.447 (11.35)

TYP. 0.450 (11.43)

0.300 (7.62)

REF.

0.050"

TYPICAL

0.510"

TYPICAL

0.400"

FOOTPRINT

SEATING PLANE

±0.004 LEAD

CO – PLANARITY

0.015 (0.38)

0.095 (2.41)

0.060 (1.52)

0.140 (3.56)

0.100 (2.45)

TYP. 0.136 (3.45)

0.048 (1.22)

0.042 (1.07)

0.300"

REF

0.410"

—

0.030" TYPICAL

32 PLACES

0.050"

TYPICAL

PIN 1

0.595 (15.11)

0.585 (14.86)

TYP. 0.590 (14.99)

0.553 (14.05)

0.547 (13.89)

TYP. 0.550 (13.97)

0.400

REF.

(10.16)

3° TYP.

NOTES:

1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

2. DIMENSIONS WITH NO TOLERANCE FOR REFERENCE ONLY

3926 FHD F13

14

Page 15

X20C04

ORDERING INFORMATION

X20C04 X X -X

Device

Access Time

–15 = 150ns

–20 = 200ns

–25 = 250ns

Blank = 300ns

Temperature Range

Blank = Commercial = 0°C to +70°C

I = Industrial = –40°C to +85°C

M = Military = –55°C to +125°C

MB = MIL-STD-833

Package

D = 28-Lead Cerdip

P = 28 Lead Plastic DIP

E = 32-Pad Ceramic LCC

J = 32-Lead PLCC

LIMITED WARRANTY

Devices sold by Xicor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Xicor, Inc. makes

no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described

devices from patent infringement. Xicor, Inc. makes no warranty of merchantability or fitness tor any purpose. Xicor, Inc. reserves the right to

discontinue production and change specifications and prices at any time and without notice.

Xicor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Xicor, Inc. product. No other circuits, patents,

licenses are implied.

US. PATENTS

Xicor products are covered by one or more of the following U.S. Patents: 4,263,664; 4,274,012; 4,300,212; 4,314,265; 4,326,134; 4,393,481;

4,404,475; 4,450,402; 4,486,769; 4,488,060; 4,520,461; 4,533,846; 4,599,706; 4,617,652; 4,668,932; 4,752,912; 4,829,482; 4,874,967; 4,883,976.

Foreign patents and additional patents pending.

LIFE RELATED POLICY

In situations where semiconductor component failure may endanger life, system designers using this product should design the system with

appropriate error detection and correction, redundancy and back-up features to prevent such an occurrence.

Xicor’s products are not authorized for use as critical components in life support devices or systems.

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life,

and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected

to result in a significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure

of the life support device or system, or to affect its satety or effectiveness.

15

Loading...

Loading...