Datasheet VSC7969YD2, VSC7969WD2B, VSC7969YD1, VSC7969WD2A, VSC7969WD1B Datasheet (VITESSE)

...Page 1

VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

VSC7969

3.125Gb/s Integrat ed Transim p eda nce

and Limiting Amplifier with Signal Detect

Features Applications

• Integrated TIA and Limiting Amplifier

• Low Power Consumption for SFF Applications

• TO Package-Compatible Layout

• On-Chip Signal Detect

• On-Chip Linear Photocurrent Monitor

• Single 3.3V Supply

• 5V Supply Operation via Wirebond Option

• Compatible with PIN or Avalanche Detectors

• Packages: 16-Pin TSSOP, TO-46, Bare Die

• 2.488Gb/s, 3.125Gb/s SONET OC-48/

SDH STM-16

• 2.125Gb/s Fibre Channel

• 2.5Gb/s or 3.125Gb/s Ethernet Applications with

8B/10B Overhead

• SFF Transceivers

General Description

The VSC7969 is a 3.125Gb/s transimpedance amplifier IC with a built-in limiting amplifier, a signal detect

feature and a photocurrent monitor. The VSC7969 does not require any external electrical components in the

construction of a high performance optical receiver such as for SONET/SDH applications. The analog output is

a differential sig nal with a min imum amplitude of 200mVp-p ( singl e-ended). The VSC7969 opera tes with a single power supply with a maximum power dissipation of 300mW. A PIN photodiode or APD can be connected

and separately biased to provide optimal performance.

The VSC7969 provides filt ered bias f or MSM and PIN phot odete ctors; appli cations u sing an APD ph otodetector must supply bias separately. The VSC7969 also provides a photocurrent monitor whose output is linearly

proportional to the input photocurrent.

The VSC7969 can operate from a single +3.3V supply or a +5V or -5.2V supply. The VSC7969 is offered

in die form and in a 16-pin plastic thin-shrink small outline package (TSSOP-16). A fully tested TO-46 outline

packaged receiver with a photodetector is also available.

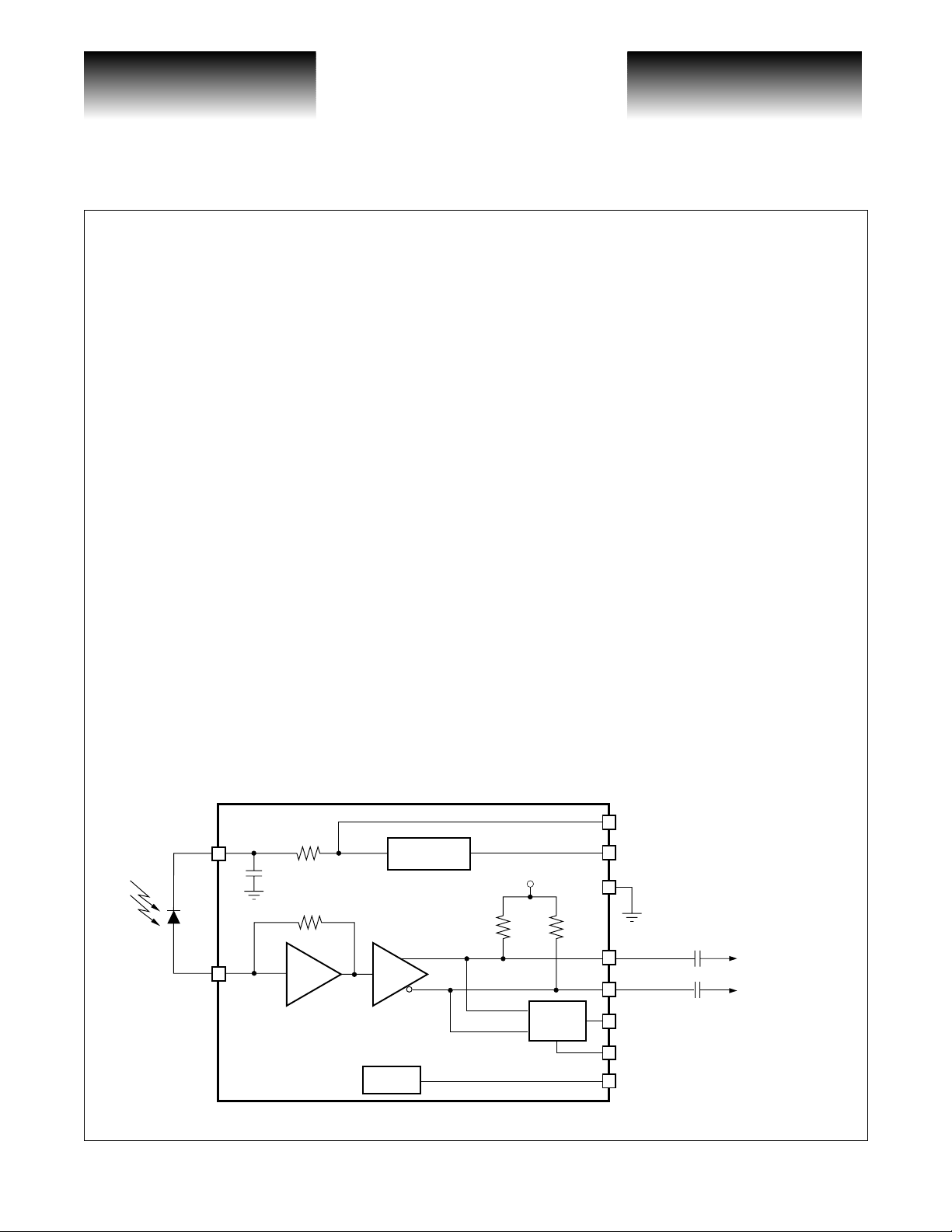

Block Diagram

Dual power supply pins are

VCCS

provided for +5V or +3.3V

Filter

In

VSC7969

G52355-0, Rev 2.0 Page 1

02/09/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

+3.3V +5V

Regulator

50Ω

Monitor

Internet: www.vitesse.com

+3.3V

50Ω

Signal

Detect

operation. Only one power

supply pin should be connected.

VCCD

GND

Outputs need to

be AC-coupled

VOUTP

VOUTN

SD_OUT

SD_ADJ

IMON

0.1µF

0.1µF

Page 2

VITESSE

SEMICONDUCTOR CORPORATION

3.125Gb/s Integrated Transimpedance

Advance Product Information

and Limiting Amplifier with Signal Detect

Electrical Characteristics

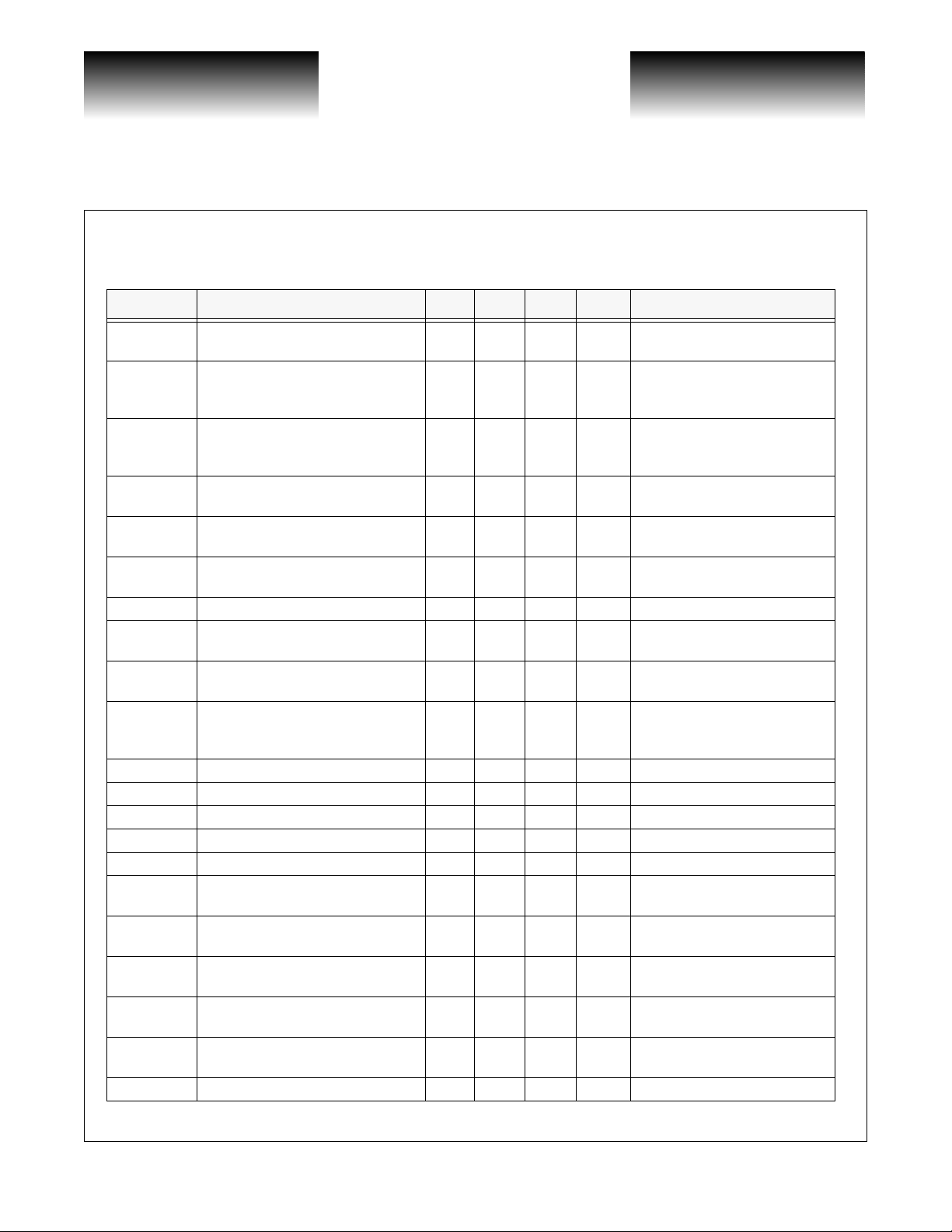

Table 1: AC Specifications

Symbol Parameter Min Typ Max Units Conditions

∆I

PH

I

PHS-AVG

I

PHS-PEAK

∆V

OUT-SE

∆V

OUT-DIFF

t

, t

R

F

(1)

Z

T

(1)

∆Z

T

BW Upper -3dB Bandwidth 2.2 2.5 3.0 GHz

F

L

Z

O

PSRR Power Supply Rejection Ratio TBD

I

NOISE

C

PD

SD

H

SD

A-OPEN

SD

D-OPEN

SD

A-SHORT

SD

D-SHORT

SD

HIGH

SD

LOW

Input Photocurrent Swing 2.2 mA

A verage Photocurrent Sensitivity 4 µA

Peak Input Photocurrent Sensitivity 8 µA

Single-Ended Ou tput Voltage

Amplitude

Differential Output Vo ltage Am plitude 400 500 600 mV

Rise and Fall Time 60 100 ps

Transimpedance Gain 20k 27k 40k Ω Differential measurement

Ripple in Passband Transimpedance 1 dB

Lower -3dB Cutoff Frequency 100 kHz

Output Impedance 50 Ω Single-ended

Input-Referred rms Noise Current 500 nA 30kHz to 2.5GHz

Photodetector Capacitance 0.4 0.6 0.8 pF Bias vo ltage on detector at 2.0V

Signal Detect Hysterisis 1 2 4 dB Electrical meas urement on SD pin

Signal Detect Assertion L evel 3 5 9 µA

Signal Detect Deasseration Level 1.0 2.2 3.0 µA

Signal Detect Asseration Level 6 10 18 µA

Signal Detect Deasseration Level 2.0 4.4 6.0 µA

Signal Detect HIGH Logic Level

Signal Detect LOW Logic Level 0.5 0.8 V

200 250 300 mV

V

CCS

- 0.3

Peak-to-peak AC current

amplitude

-23dBm average optical power

with a detector responsitivity of

0.8A/W.

-23dBm average optical power

with a detector responsitivity of

0.8A/W.

Single-ended peak-to-peak

measurement, I

Differential peak-to-peak

measurement, IIN >20µA.

At 2.2mAp-p input photocurrent

swing. 20% to 80%.

Modulation frequency between F

and BW

Referenced to 10MHz,

CPD = 0.6pF

Referenced to 10MHz, CPD =

0.6pF with no external

components

Average photocurrent with SD

open.

Average photocurrent with SD

open.

Average photocurrent with SD

shorted to ground.

Average photocurrent with SD

shorted to ground.

V

VSC7969

>20µA.

IN

L

Page 2 G52355-0, Rev 2.0

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

02/09/01

Page 3

VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

VSC7969

3.125Gb/s Integrat ed Transim p eda nce

and Limiting Amplifier with Signal Detect

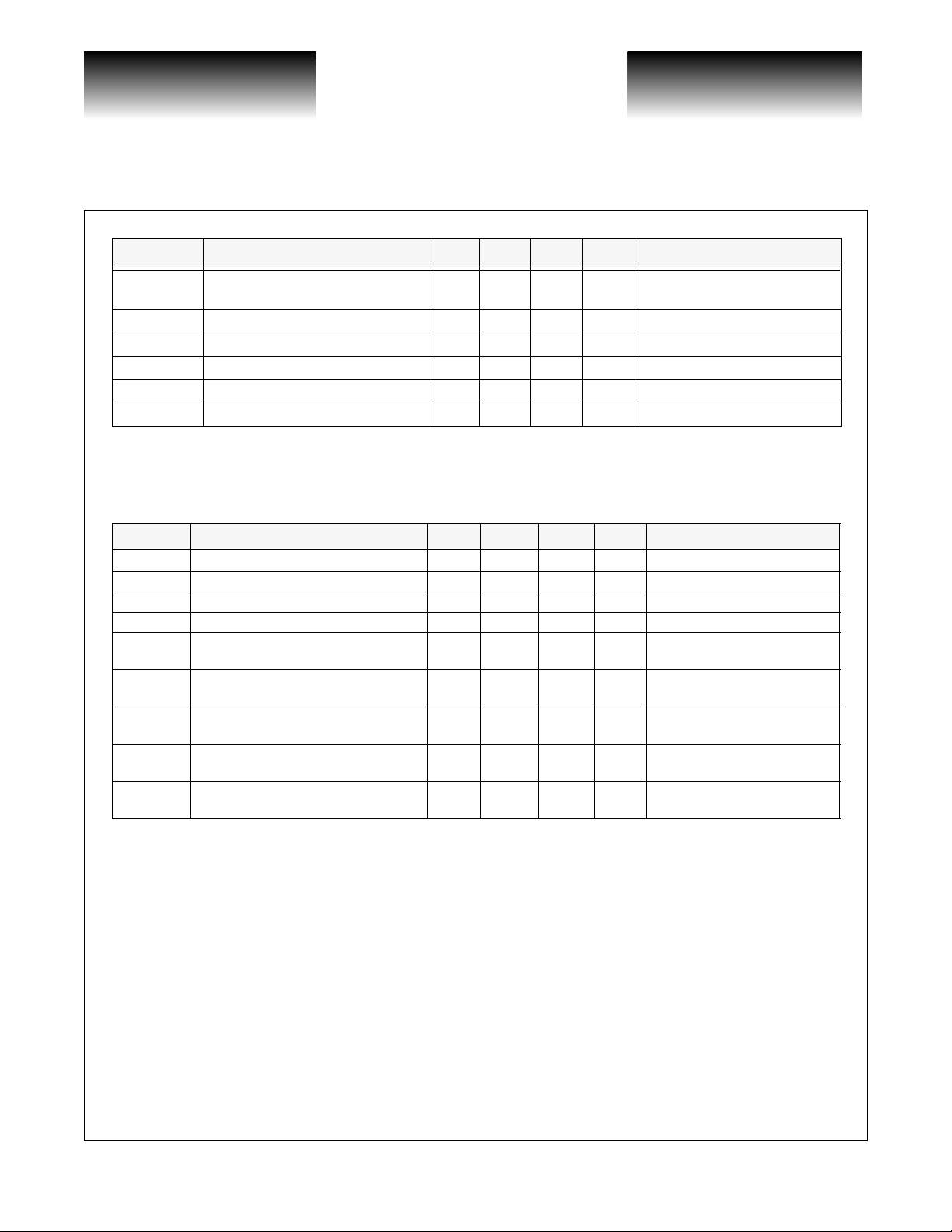

Symbol Parameter Min Typ Max Units Conditions

MON

DC Duty Cycle -5 +5 %

IMON

RANGE

IMON

OFFSET

R

J

D

J

NOTES: (1) The transimpedance gain is defined as ZT = (∆V

standard deviation of the edge of th e pat t ern, multiply the standard deviation by 14 to achieve the to ta l random jitter. (3) +K28.5

- K28.5 (00111110101100000101).

Slope of Linear Anal og Photocurrent

Monitor vs Input Optical Power

Photocurren t Monitor Lin earity Range 5 200 µA

Photocurrent Monitor Offset 0 1 0 µA

Random Jitter

Deterministic Jitter

(2)

(3)

OUT - DIFF

0.8 µA/µW

TBD ps Peak-to-peak

TBD ps Peak-to-peak

)/∆IPH. (2) Usi ng 111110000 0 patter n at 2.5 Gb/s to measur e the

0Ω to 2kΩ to V

responsitivity of 0.8A/W

Table 2: DC Specifications

Symbol Parameter Min Typ Max Units Conditions

GND Negative Supply Rail 0 V

V

CCS

V

CCD

ICC Power Supply Current 65 75 mA 3.3V

V

OUT-CM

V

ANODE

V

CATHODE

V

CAT-EXT

V

APD

Positive Supply Rail for 3.3V Operation 3.0 3.3 3.6 V

Positive Supply Rail for 5V Operation 4.5 5.0 5.5 V

-

V

Common-Mode Voltage on Output Pins

Internal DC Bias Voltage on Detector

Anode Contact

Interal DC Bias Voltage on Detector

Cathode Contact

External DC Bias Voltage Permissable

on Detector Cathode Contact

External DC Bias Voltage for Use with

Avalanche Photodetector

0.8 0.9 1.0 V

V

CCS

0.15V

CCS

125mV

-

3.3 10 V

60 V

V

CCS

Applicable to VOUTP and

VOUTN pins at 50Ω load.

V

with a detector

CC

Absolute Maximum Ratings

Power Supply Voltage (V

Power Supply Voltage (V

) ......................................................................................................................... 3.6V

CCS

)........................................................................................................................ 5.5V

CCD

(1)

(at TA = +25°C, unless otherwise specified)

Junction Temperature Range........................................................................................................-40°C to +125°C

Storage Temperature Range .........................................................................................................-40°C to +125°C

Relative Ambient Humidity .................................................................................................................85%/+85°C

NOTE: (1) CAUTION: Stresses listed under “Absolute Maximum Ratings” may be applied to devices one at a time without caus-

ing permanent damage. Functionality at or above the values listed is not implied. Exposure to these values for extended

periods may affect device reliability.

Recommended Operating Conditions

Positive Voltage Supply (V

Positive Voltage Supply (V

Negative Voltage Rail (GND) ............................................................................................................................ 0V

Ambient Temperature Range (T

G52355-0, Rev 2.0 Page 3

02/09/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

)......................................................................................................................3.3V

CCS

)......................................................................................................................5.0V

CCD

(1)

)

..............................................................................................-40°C to +85°C

A

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 4

VITESSE

SEMICONDUCTOR CORPORATION

3.125Gb/s Integrated Transimpedance

and Limiting Amplifier with Signal Detect

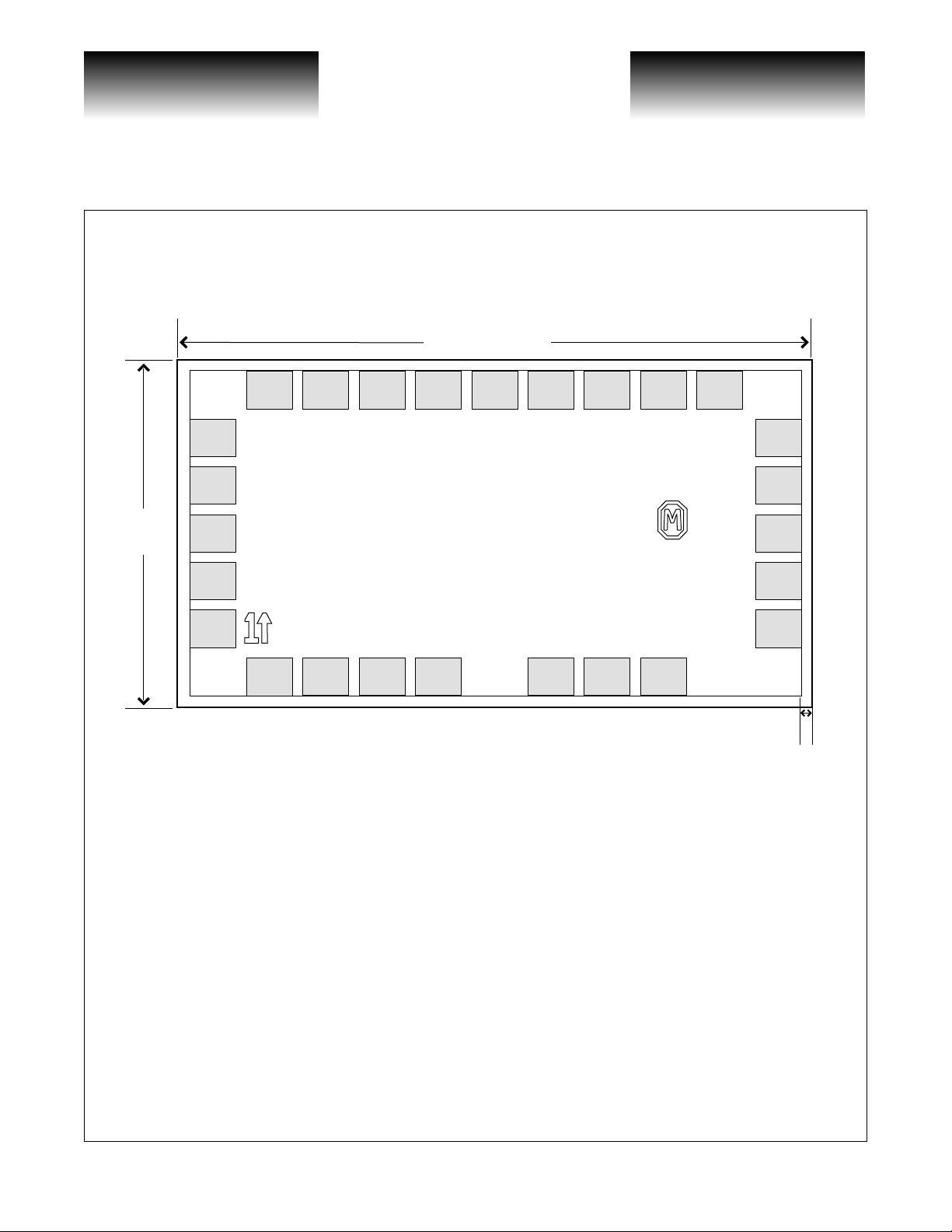

Bare Die Descriptions

Figure 1: Pad Assignments

1143µm

(45.0mil)

Pad 5

SD_ADJ

Pad 4

SD_TP

Pad 3

GND

Pad 2

BG_VREF

Pad 6

VOUTN

Pad 7

SD_OUT

Pad 8

GND

1467

Pad 9

VOUTN

VSC7969

µm (57.2mil)

Pad 10

GND

Advance Product Information

VSC7969

Pad 11

VOUTP

Pad 12

GND

Pad 13

IMON

Pad 14

VOUTP

Pad 15

GND

Pad 16

CSDN

Pad 17

CSDP

Pad 18

GND

Pad 1

GND

Pad 26

VCCD

Pad 25

VCCS

Pad 24

GND

Pad 23

IN

Die Size: 1143µm x 1453µm (45.0mil x 57.2mil)

Die Thickness: 279

µm (11.0mil)

Pad Size: 100µm x 100µm (3.9mil x 3.9mil)

Pad Passivation Opening: 86µm x 86µm (3.4mil x 3.4mil)

Scribe Size: 143µm (5.6mil)

Pad 22

FILTER

Pad 21

GND

Pad 20

GND

Pad 19

GND

143

µm

(5.6mil)

Page 4 G52355-0, Rev 2.0

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

02/09/01

Page 5

VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

VSC7969

3.125Gb/s Integrat ed Transim p eda nce

and Limiting Amplifier with Signal Detect

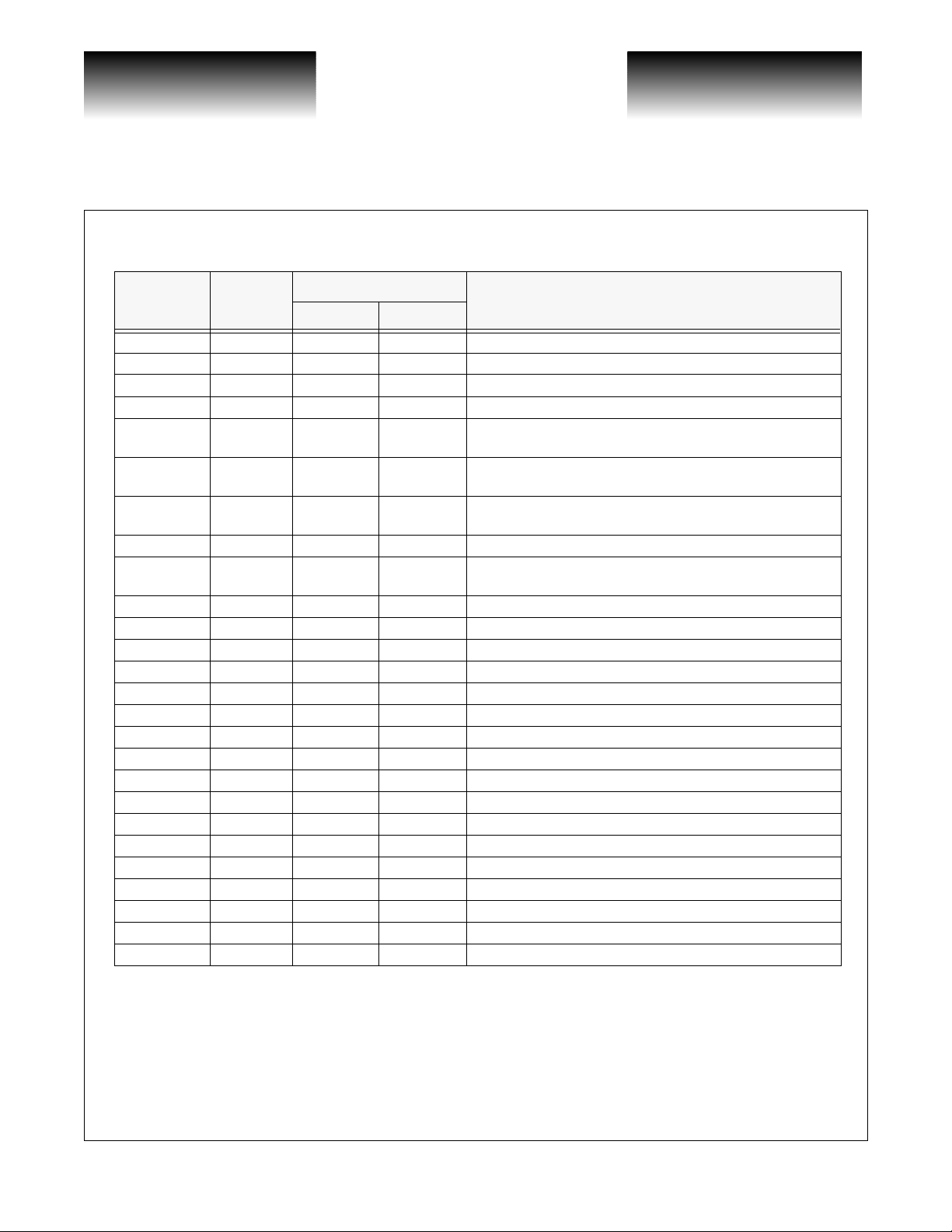

Table 3: Pad Coordinates

Signal

Name

GND 1 130 250 Negative power supply rail (typically 0V)

BG_VREF 2 130 375 Band Gap voltage reference 1.24V for testpoint, no connect

GND 3 130 500 Negative power supply rail (typically 0V)

SD_TP 4 130 625 Signal Detect test point, DO NOT CONNECT.

SD_ADJ 5 130 750

VOUTN 6 137 875

SD_OUT 7 280 875

GND 8 405 875 Negative power supply rail (typically 0V)

VOUTN 9 530 875

GND 10 655 875 Negative power supply rail (typ ically 0V)

VOUTP 11 780 875 Positive logic output (logic HIGH when photocurrent is HIGH)

GND 12 905 875 Negative power supply rail (typ ically 0V)

IMON 13 1030 875 Photocurrent Monitor

VOUTP 14 1173 875 Positive logic output (logic HIGH when photocurrent is HIGH)

GMD 15 1180 750 Negative power supply rail (typically 0V)

CSDN 16 1180 625 Test point for Signal Detect capacitor. DO NOT CONNECT.

CSDP 1 7 1180 500 Test point for Signal Detect capacitor. DO NOT CONNECT.

GND 18 1180 375 Negative power supply rail (typically 0V)

GND 19 1180 250 Negative power supply rail (typically 0V)

GND 20 1030 125 Negative power supply rail (typically 0V)

GND 21 905 125 Negative power supply rail (typ ically 0V)

FILTER 22 780 125 Photodetector cathode connection (filtered V

IN 23 530 125 Photodetector anode connection

GND 24 405 125 Negative power supply rail (typ ically 0V)

VCCS 25 280 125 Positive power supply rail for 3.3V operation

VCCD 26 137 125 Positive power supply rail for 5V operation

Pad

Number

Coordinates (µm)

X Y

Description

Signal Detect threshold adjustment (see Application am d Usage

section)

Complementary logic output (logi c LOW when photocurrent is

HIGH)

Signal detect output (logic HIGH when photocurrent exceeds

)

SD

A

Complementary logic output (logi c LOW when photocurrent is

HIGH)

)

CC

G52355-0, Rev 2.0 Page 5

02/09/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 6

VITESSE

SEMICONDUCTOR CORPORATION

3.125Gb/s Integrated Transimpedance

and Limiting Amplifier with Signal Detect

Package Pin Descriptions

Figure 2: Pin Diagram

VCC

GND

GND

IN

FILTER

GND

GND

GND

1

2

3

4

5

6

7

8

VSC7969

Advance Product Information

VSC7969

16

15

14

13

12

11

10

9

SD_ADJ

SD_OUT

GND

VOUTN

VOUTP

GND

GND

IMON

Table 4: Pin Identifications

Pin Name Pin No. Description

VCC 1 Power Supply

GND 2 Ground

GND 3 Ground

IN 4 Photodetec tor A no de Conn e ction

FILTER 5 Photodetector Cathode Connection (filtered V

GND 6 Ground

GND 7 Ground

GND 8 Ground

IMON 9 Photo cu r re nt Monitor

GND 10 Ground

GND 11 Ground

VOUTP 12 Positive Logic Output (logic HIGH when photocurrent is HIGH)

VOUTN 13 Complementary Logic Output (logic LOW when photocurren t is HIGH)

GND 14 Ground

SD_OUT 15 Signal Detect Output (logic HIGH when photocurrent exceeds SD

SD_ADJ 16 Signal Detect Threshold Adjustment (see Applications and Usage section)

CC

)

)

A

Page 6 G52355-0, Rev 2.0

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

02/09/01

Page 7

VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

VSC7969

Typical Operating Characteristics

Electrical Eye Diagram,

Input = 8µAp-p, 3.125Gb/s, PRBS 231-1

T

= º+25C, VCC = 3.3V

A

3.125Gb/s Integrat ed Transim p eda nce

and Limiting Amplifier with Signal Detect

Electrical Eye Diagram,

Input = 100µAp-p, 3.125Gb/s, PRBS 231-1

T

= º+25C, VCC = 3.3V

A

Bit Error Rate vs Input Level

BIT ERROR RATE vs INPUT LEVEL

1.00E-07

1.00E-08

1.00E-09

1.00E-10

1.00E-11

Bitt Eorr Rate (BER)

1.00E-12

1.00E-13

6.0 6.5 7.0 7.5

IN (I

) (µAp-p)

PD

G52355-0, Rev 2.0 Page 7

02/09/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

8.0 8.5

Internet: www.vitesse.com

250

200

150

(µA)

MON

100

I

50

0

0 50 100

IMON Characteristic,

0µA to 200µA Input

I

CHARACTERISTIC

MON

0µA to 200µA Input

IN (DC Current) (µA)

150 200

Page 8

VITESSE

SEMICONDUCTOR CORPORATION

3.125Gb/s Integrated Transimpedance

and Limiting Amplifier with Signal Detect

Advance Product Information

VSC7969

Circuit Description

The VSC7969 data path consists of several stages: transimpedance input stage, limiting amplifier, and output driver. The transimpedance amplifier accepts current from a photodetector connected to the input pad ‘IN’

and converts the input current to a differential output voltage. The signal then travels to the second stage limiting amplifier which p rovi des DC rest or at io n, el i min ati ng th e DC compo nent of t he in put si gnal . T he l i near p hotocurrent monitor and signal detect function is also provided by this stage. The final stage consists of an output

driver with a differential pair connected to V

ential transimpedance of the VSC7969 is typically 27k

ically 250mVp-p.

via 50Ω internal pull-up resistors. The overall effective differ-

CC

Ω. The limited output single-ended voltage swing is typ-

Design Guidelines

Power Supply

The VSC7969 is supplied by a single supply voltage; for +3.3V operation, the supply votlage should be

applied to only V

Data Outputs

The outputs of the VSC7969 need to be AC-coupled. This capacitor will determine the low frequency cutoff for the system, which is directly related to the receiver’s deterministic jitter. For ATM/SONET or other

applications using PRBS NRZ data, select a capacitor of at least 0.1µF or greater, which provides less than

32kHz low frequency cutoff. For Fibre Channel, Gigabit Ethernet, or other applications requiring 8B/10B data

coding, select a capacitor of at least 0.01µF or greater, which provides less than 320kHz low frequency cutoff.

The outputs can be used single-ended or differential. For best performance, differential operation is recommended. If single-ended operation is neces sary, the unused output should be AC-coupled and terminated wi th

an impedance equal to the load on the pin in use.

. For +5V operation, the supply voltage should be applied to only V

CCS

CCD

.

Page 8 G52355-0, Rev 2.0

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

02/09/01

Page 9

VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

VSC7969

Signal Detect

The signal detect feature of the VSC7969 provides a CMOS level output corresponding to the input current

level to the transimpedance amplifier. The assert and deassert levels of the signal detect pin can be adjusted by

placing an optional resistor from SD_ADJ to ground. The following tables show the two extremes at which the

signal detect pin will operate; open circuit and short-ciruit to ground.

Table 5: Signal Detect Function, SD_ADJ Open

Electrical

Min Typ Max Units

Assert 3 5 9 µA

Deassert 1 2.2 3 µA

Hysteresis 1 2 4 dB

With SD_ADJ (pin 16) shorted to ground, thresholds are 3dB higher, as shown in Table 6.

Table 6: Signal Detect Function, SD_ADJ Shorted to Ground

Electrical

3.125Gb/s Integrat ed Transim p eda nce

and Limiting Amplifier with Signal Detect

Min Typ Max Units

Assert 6 10 18 µA

Deassert 2 4.4 6 µA

Hysteresis 1 2 4 dB

Photodetector Current Monitor

The IMON pin provides a linear measurement of the average input current from the photodetector to the

transimpedance amplifier. For example, if 20µA is the average input current to the transimpedance amplifier,

the current through the IMON pin will be 20µA (see the typical operating curve “IMON Characte ristic, 0µA to

200µA). To use this feature, connect the IMON pin to V

used, the IMON pin can be left unconnected.

using a resistor less than 2kΩ. If this feature is not

CC

G52355-0, Rev 2.0 Page 9

02/09/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 10

VITESSE

SEMICONDUCTOR CORPORATION

3.125Gb/s Integrated Transimpedance

and Limiting Amplifier with Signal Detect

Application Information

IMON

Advance Product Information

VSC7969

VCC

VOUTP

GND

NOTES:

No external components required.

Unused output is AC-coupled and terminated to 50Ω.

Page 10 G52355-0, Rev 2.0

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

02/09/01

Page 11

VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

VSC7969

Package Information

TSSOP-16

3.125Gb/s Integrat ed Transim p eda nce

and Limiting Amplifier with Signal Detect

1. All dimensioning and tolerancing per ASME. Y14.5-1994

2. Controlling dimension: millimeter

3. This outline conforms to JEDEC Publication 95 Registration MS-026

G52355-0, Rev 2.0 Page 11

02/09/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 12

VITESSE

SEMICONDUCTOR CORPORATION

3.125Gb/s Integrated Transimpedance

and Limiting Amplifier with Signal Detect

TO-46 Ball Lens Package

TOP VIEW SIDE VIEW

Advance Product Information

VSC7969

1. Controlling dimenstion: millimeter

Reference Isometric

Page 12 G52355-0, Rev 2.0

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

02/09/01

Page 13

VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

VSC7969

TO-46 Flat Window Package

3.125Gb/s Integrat ed Transim p eda nce

and Limiting Amplifier with Signal Detect

TOP VIEW

1. Controlling dimension: millimeter

Reference Isometric

G52355-0, Rev 2.0 Page 13

02/09/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 14

VITESSE

SEMICONDUCTOR CORPORATION

3.125Gb/s Integrated Transimpedance

and Limiting Amplifier with Signal Detect

Ordering Informatio n

The order number for this product is formed by a combination of the device type and package type.

VSC7969

Device Type

3.125Gb/s Integrated Transimpedance

and Limiting Amplfier with Signal Detect

xx

Advance Product Information

VSC7969

Package

YD1: TSSOP-16, 3.3V Supply

YD2: TSSOP-16, 5V Supply

W: Dice Waffle Pack

WD1A: TO-46 Ball Lens, 3.3V Supply, VOUTN/VOUTP Outputs

WD1B: TO-46 Ball Lens, 3.3V Supply, VOUTN/IMON Outputs

WD2A: TO-46 Ball Lens, 5V Supply, VOUTN/VOUTP Outputs

WD2B: TO-46 Ball Lens, 5V Supply, VOUTN/IMON Outputs

Notice

Vitesse Semiconductor Corporation (“Vitesse”) provides this document for informational purposes only. This document contains pre-production

information about Vitesse products in their co ncep t, devel opme nt and/or te sting phase. All in forma tion in thi s docu ment, includ ing descriptions of

features, functions, performance, technical specifications and availability, is subject to change without notice at any time. Nothing contained in this

document shall be construed as extending any warranty or promise, express or implied, that any Vitesse product will be available as describe d or

will be suitable for or will accomplish any particular task.

Vitesse products are not intended for use in li fe support appliances, devic es o r systems. Use of a Vitesse product in such applications without written consent is prohibit ed.

Page 14 G52355-0, Rev 2.0

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

02/09/01

Loading...

Loading...