Page 1

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

VSC7940

Laser Diode Driver with Automatic Power Control

SONET/SDH 3.125Gb/s

Features Applications

• Power Supply: 5V ±5%

• DC-Coupled to Laser Diode

• Programmable Modulation Current: 5mA to 100mA

• Programmable Bias Current: 1mA to 100mA

• Enable/Disable Control

• Automatic Optical Average Power Control

• Modulation and Bias Current Monitors

• SONET/SDH at 622Mb/s, 1.244Gb/s,

2.488Gb/s, 3.125Gb/s

• Full-Speed Fibre Channel (1.062Gb/s)

General Description

The VSC7940 is a single 5V supply laser diode driver specially designed for SONET/SDH applications up

to 3.125Gb/s. External resistors set a wide range of bias and modulation currents for driving the laser. Data and

clock inputs accept differential PECL signals. The Automatic Power Control (APC) loop maintains a constant

average optical power over temperature and li fetime. The domi nant pole of t he APC loop can be c ontrol led with

an external capacitor. Other features include enable/disable control, programmable slow-start circuit to set laser

turn-on delay, and failure-monitor output to indicate when the APC loop is unable to maintain the average optical power. The VSC7940 is available in die form or in a 32-pin TQFP package.

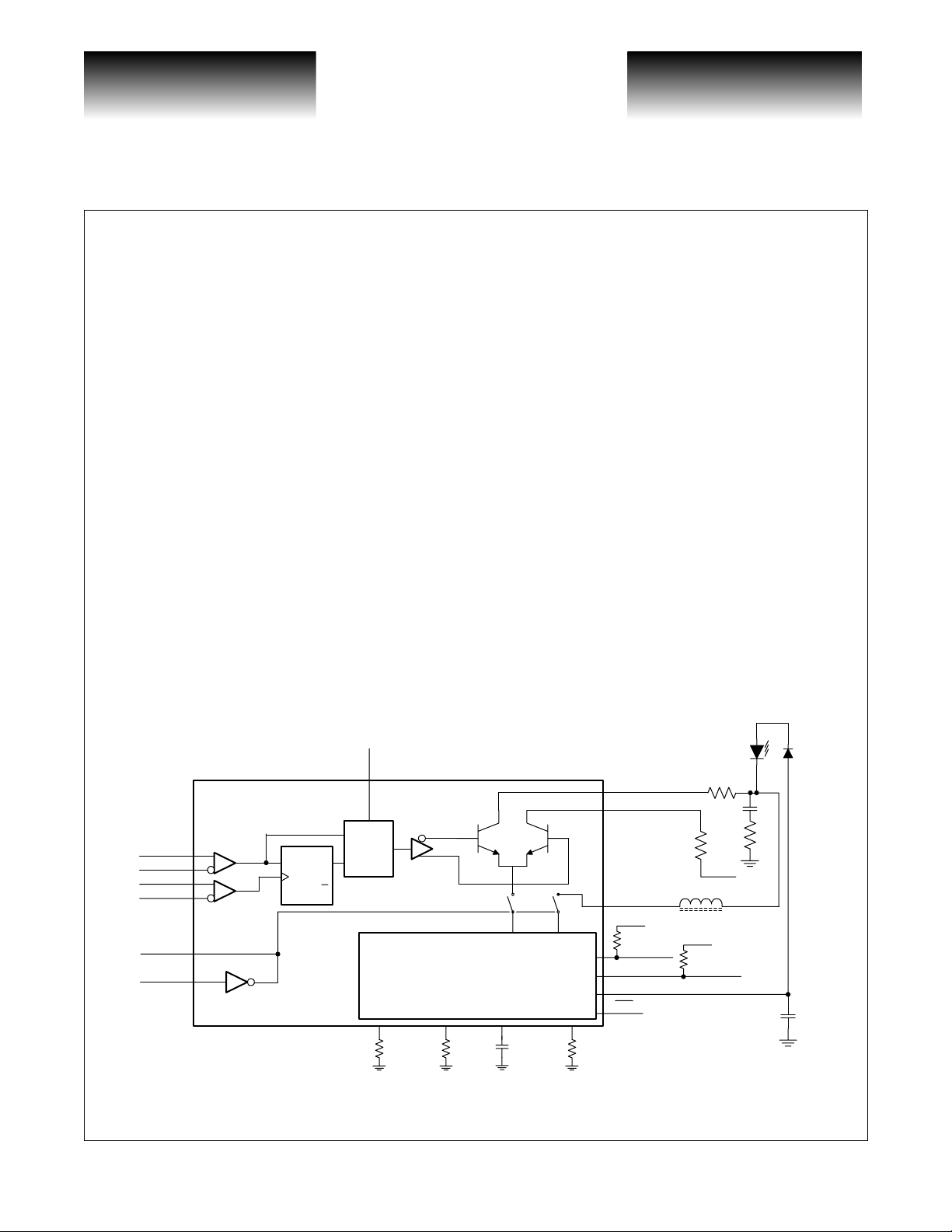

Block Diagram

DATA+

DATA-

CLK+

CLK-

ENABLE

DISABLE

D

SET

CLR

Q

Q

MODSET

MUX

LATCH

BIASMAX

APC

CAPC

APCSET

V

CC

MODMON

MD

FAIL

IOUT+

IOUT-

BIAS

V

V

CC

BIASMON

V

CC

C

F

R

F

CC

1nF

G52357-0, Rev 3.2 Page 1

05/11/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 2

VITESSE

SEMICONDUCTOR CORPORATION

SONET/SDH 3.125Gb/s

Preliminary Data Sheet

Laser Diode Driver with Automatic Power Control

Electrical Characteristics

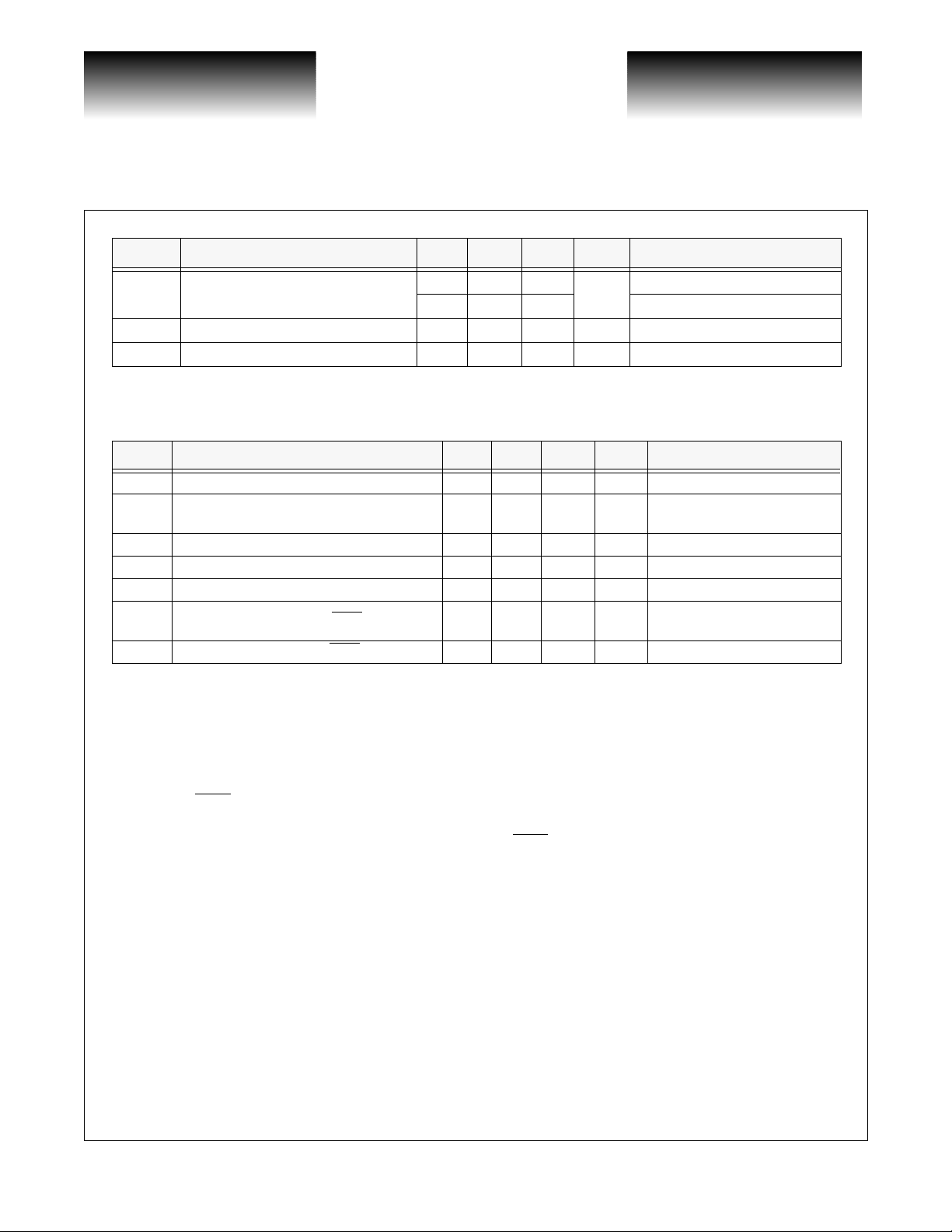

Table 1: AC Specifications

AC specifications are guaranteed by design an d characterization. Typical values are for 5V operation.

Symbol Parameter Min Typ Max Units Conditions

t

SU

t

H

t

R

t

F

PWD Pulse Width Distortion 10 50 ps See Notes 1, 2

CID

t

J

NOTES: (1) Measured with 622Mb/s 0-1 pattern , LATCH=high. (2) P WD = (wi der pulse - narrower pulse) / 2).

Input Latch Setup Time 100 ps LATCH=high

Input Latch Hold Time 100 ps LATCH=high

Enable/Start-up Delay 250 ns

Output Rise Time TBD TBD ps 20% to 80%

Output Fall Time TBD TBD ps 20% to 80%

Maximum Consecu tive Identical D igits 80 bits

MAX

Jitter Generation 7 20 ps

p-p

Jitter BW=12kHz to 20MHz,

0-1 pattern.

VSC7940

Table 2: DC Specifications

Symbol Parameter Min Typ Max Units Conditions

V

SS

I

CC

I

BIAS

I

BIAS-OFF

S

BIAS

VR

MD

I

MD

I

MOD

I

MOD-OFF

Power Supply Voltage 4.75 5.0 5.25 V

R

Power Supply Current TBD 45 mA

Bias Current Range 1 100 mA Voltage at BIAS pin=(VCC-1.6)

Bias Off Current 100 µA

Bias Current Stability

Bias Current Absolute Accuracy ±15 % Refers to part-to-part variation

Monitor Diode Reverse Bias Voltage 1.5 V

Monitor Diode Reverse Current Range 18 1000 µA

Monitor Diode Bias Setpoint Stability

Monitor Diode Bias Absolute Accuracy -15 15 % Refers to part-to-part variation

Modulation Current Range 5 100 mA

Modulation Off Current 200 µA

Modulation Current Absolute Accuracy ±15 % See Not e 2

-480 -50 480

230

900 APC open loop. I

90 IMD=18µA

ppm/°C

ppm/°C

R

I

BIAS

ENABLE=low or

DISABLE=high

APC open loop. I

IMD=1mA

ENABLE=low or

DISABLE=high

MODSET

BIASMAX

and I

=7.3kΩ

=4.8kΩ

excluded, VCC=5V

MOD

(1)

BIAS

BIAS

(2)

(2)

(1)

=100mA

=1mA

Page 2 G52357-0, Rev 3.2

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

05/11/01

Page 3

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

VSC7940

Laser Diode Driver with Automatic Power Control

SONET/SDH 3.125Gb/s

Symbol Parameter Min Typ Max Units Conditions

Modulation Current Stability

A

BIAS

A

MOD

NOTES: (1) Both I

BIASMON to I

MODMON to I

tion does not change with temperature.

BIAS

and I

-480 -50 480

250 I

Gain 37 I

BIAS

Gain 29 I

MON

will turn off if any of the current set pins are grounded. (2) Assume s l ase r di ode t o monitor diode transfer func-

MOD

ppm/°C

I

=60mA

MOD

=5mA

MOD

BIAS/IBIASMON

MOD/IMODMON

Table 3: PECL and TTL/CMOS Input/Output Specifications

Symbol Parameter Min Typ Max Units Conditions

V

ID

V

ICM

I

IN

V

IH

V

IL

Differential Input Voltag e 100 1600 mV

-

CC

1.49

VCC -

1.32

V

Common-Mode Input Voltage

Clock and Data Input Current -1 10 mA

TTL Input High Voltage (ENABLE, LATCH) 2.0 V

TTL Input Low Voltage (ENABLE, LATCH) 0.8 V

TTL Output High Voltage (FAIL

TTL Output Low Voltage (FAIL

)2.4

) 0.1 0.44 V Sinking 100µA

V

CC

0.3

VCC V

ID

V

CC

V PECL-compatible

/4

V Sourcing 50µA

(DATA+)-(DATA-)

p-p

Absolute Maximum Ratings

(1)

Power Supply Voltage (VCC).............................................................................................................-0.5V to +7V

Current into BIAS.....................................................................................................................-20mA to +150mA

Current into OUT+, OUT-...............................................................................................................................TBD

Current into MD.............................................................................................................................-5mA to +5mA

Current into FAIL

Voltage at DATA+, DATA-, CLK+, CLK-, ENABLE, LATCH.........................................-0.5V to (V

Voltage at APCFILT, MODSET, BIASMAX, APCSET, MD, FAIL

Voltage at OUT+, OUT- ..................................................................................................... -0.5V to (V

Voltage at BIAS.................................................................................................................. -0.5V to (V

Continuous Power Dissipation (T

......................................................................................................................... -10mA to 30mA

+ 0.5V)

CC

.............................................-0.5V to +3.0V

+ 1.5V)

CC

+ 0.5V)

CC

= +85°C, TQFP derate 20.8mW/°C above +85°C) .........................1350mW

A

Operating Junction Temperature Range...................................................................................... -55°C to +150°C

Storage Temperature Range ........................................................................................................ -65°C to +165°C

NOTE: (1) CAUTION: Stresses listed under “Absolute Maximum Ratings” may be applied to devices one at a time without caus-

ing permanent damage. Functionality at or above the values listed is not implied. Exposure to these values for extended

periods may affect device reliability.

Recommended Operating Conditions

Positive Voltage Rail (VCC)..............................................................................................................................+5V

Negative Voltage Rail (GND) ............................................................................................................................ 0V

Ambient Temperature Range (T

)..................................................................................................-40°C to +85°C

A

G52357-0, Rev 3.2 Page 3

05/11/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 4

VITESSE

SEMICONDUCTOR CORPORATION

SONET/SDH 3.125Gb/s

Laser Diode Driver with Automatic Power Control

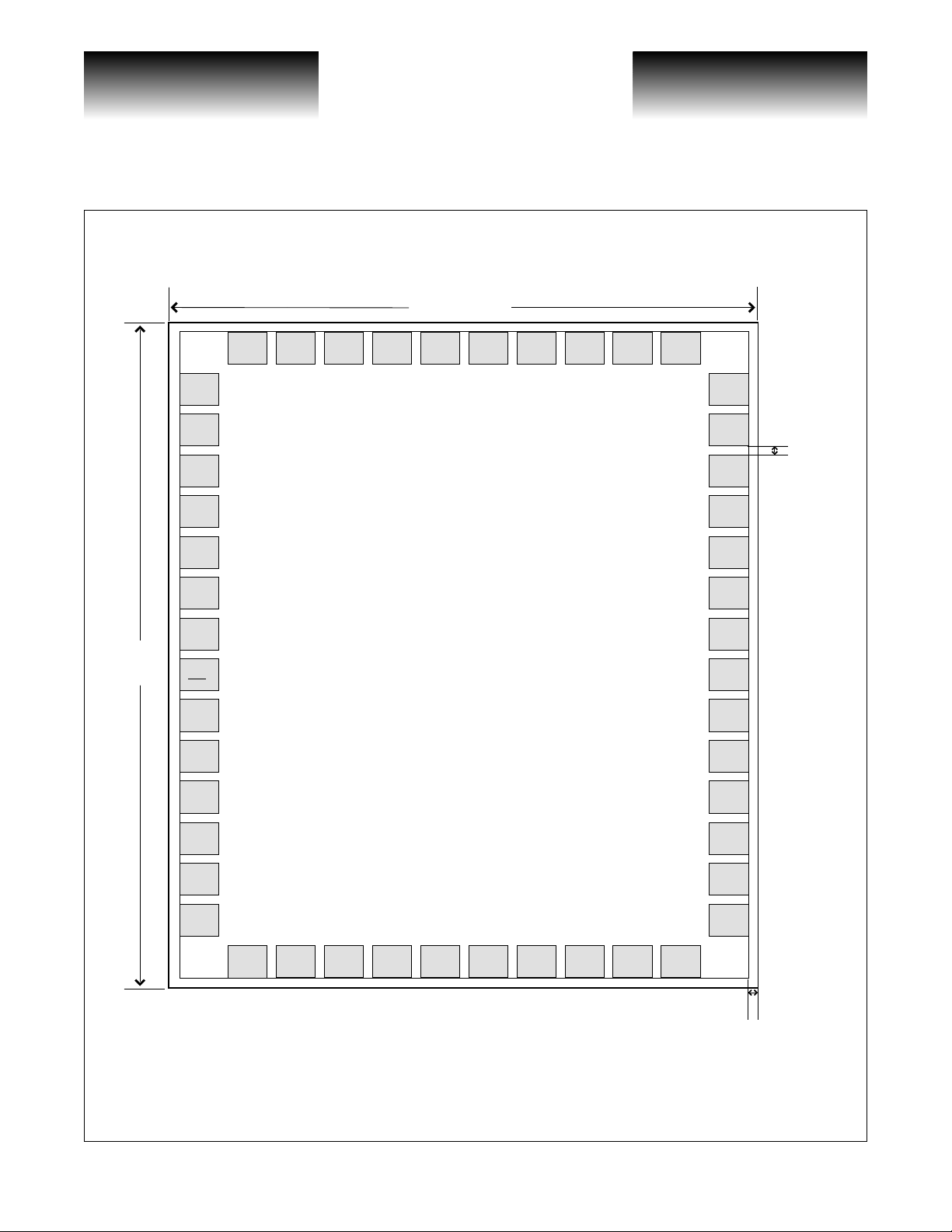

Bare Die Pad Descriptions

Figure 1: Pad Assignments

1773

µm (0.0698")

Pad 10

GND1

Pad 11

LATCH

Pad 12

ENABLE

Pad 13

DISABLE

Pad 14

GND1

Pad 15

BIASMON

Pad 9

VCC1

(Pin 8)

(Pin 9)

(Pin 10)

(Pin 11)

Pad 8

CLK-

Pad 7

CLK+

(Pin 5)

Pad 6

VCC1

Pad 5

GND1

Pad 4

VCC1

Pad 3

DATA-

Pad 2

DATA+

Preliminary Data Sheet

VSC7940

Pad 1

Pad 48

VCC1

GND1

(Pin 1)(Pin 2)(Pin 3)(Pin 4)(Pin 6)(Pin 7)

(Pin 32)

(Pin 31)

(Pin 30)

(Pin 29)

Pad 47

GND2

Pad 46

VCC2

Pad 45

BIASMAX

Pad 44

MODSET

Pad 43

GND2

Pad 42

APCSET

20

µm

(0.0008")

Pad 16

(Pin 12)

2233

µm

(0.0879")

MODMON

Pad 17

FAIL

Pad 18

GND4

Pad 19

PB_GND

Pad 20

APCFILT

Pad 21

GND4

Pad 22

VCC4

Pad 23

BIAS

(Pin 13)

(Pin 14)

(Pin 15)

(Pin 16)

(Pin 17)

Pad 24

PB_GND1

(Pin 18) (Pin 19) (Pin 20) (Pin 21) (Pin 22) (Pin 23) (Pin 24)

Pad 25

VCC4

Pad 26

DB_OUT+

Pad 27

OUT+

VSC7940

Pad 28

OUT-

Die Size: 1773µm x 2233µm (0.0698" x 0.0879")

Die Thickness: 625µm (0.0246")

Pad Pitch: 115µm (0.0045")

Pad to Pad Clearance: 20µm (0.0008")

Pad Passivation Opening: 95µm x 95µm (0.0037" x 0.0037")

Pad 29

DB_OUT-

Pad 30

VCC4

Pad 31

GND4

Pad 32

GND3

(Pin 28)

(Pin 27)

(Pin 26)

(Pin 25)

Pad 33

MD

Pad 41

RESERVED

Pad 40

GND2

Pad 39

PB_GND

Pad 38

GND3

Pad 37

PB_GND

Pad 36

CAPC

Pad 35

VCC3

Pad 34

GND3

(0.0030")

75

µm

Page 4 G52357-0, Rev 3.2

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

05/11/01

Page 5

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

VSC7940

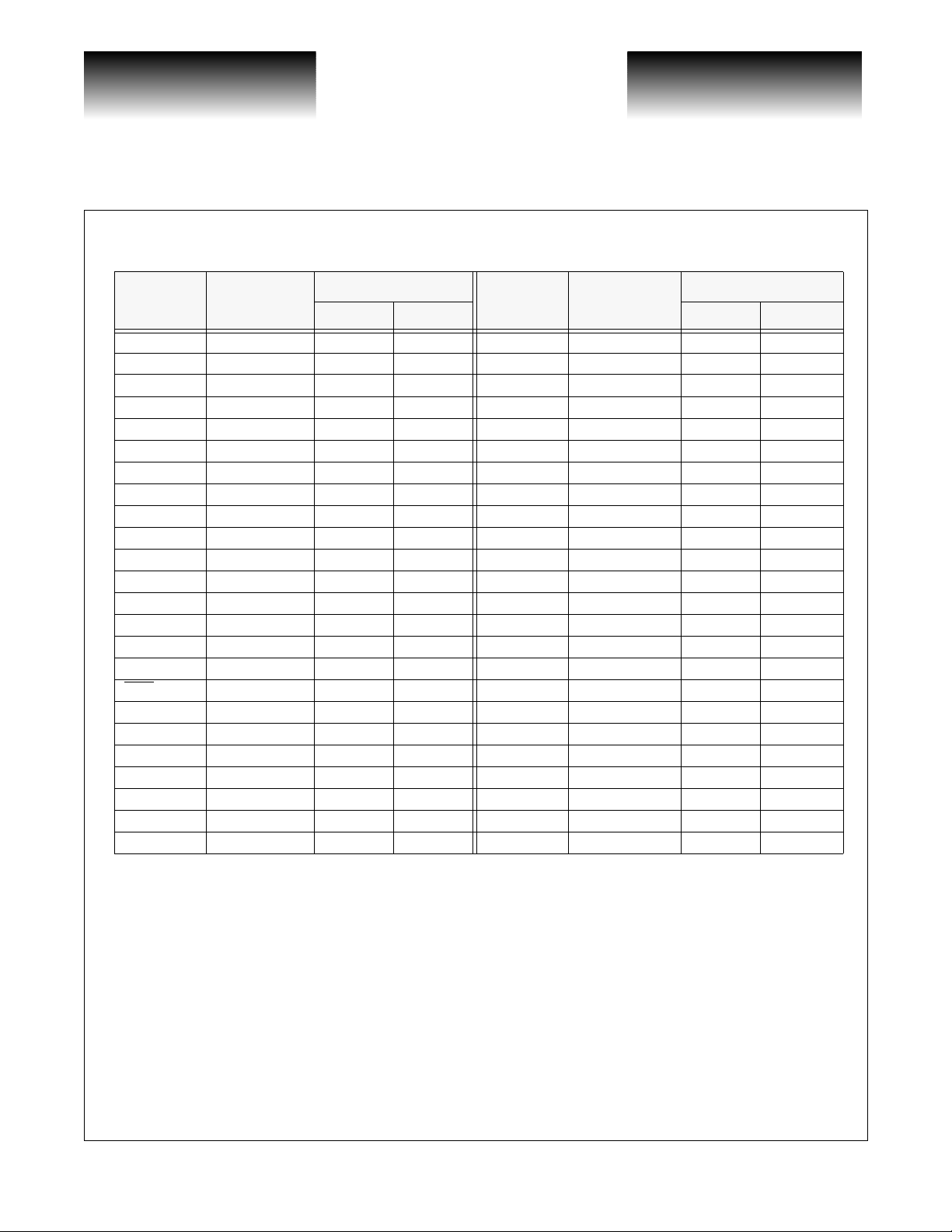

Table 4: Pad Coordinates

Signal

Name

VCC1 1 (Pin 1) 1211.025 1995.05 VCC4 25 (Pin 18 ) 406.025 80.95

DATA+ 2 (Pin 2) 1096.025 1995.05 DB_OUT+ 26 521.025 80.95

DATA- 3 (Pin 3) 981.025 1995.05 OUT+ 27 (Pin 19) 636.025 80.95

VCC1 4 (Pin 4) 866.025 1995.05 OUT– 28 (Pin 20) 751.025 80.95

GND1 5 751.025 1995.05 DB_OUT– 29 866.025 80.95

VCC1 6 636.025 1995.05 VCC4 30 (Pin 21) 981.025 80.95

CLK+ 7 (Pin 5) 521.025 1995.05 GND4 31 (Pin 22) 1096.025 80.95

CLK- 8 (Pin 6) 406.025 1995.05 GND3 32 (Pin 23) 1211.025 80.95

VCC1 9 (Pin 7) 291.025 1995.05 MD 33 (Pin 24) 1326.025 80.95

GND1 10 80.95 1784.975 GND3 34 1535.05 289.975

LATCH 11 (Pin 8) 80.95 1669.975 VCC3 35 (Pin 25) 1535.05 404.975

ENABLE 12 (Pin 9) 80.95 1554.975 CAPC 36 (Pin 26) 1535.05 519.975

DISABLE 1 3 (Pin 10) 80.95 1439.975 PB_GND 37 1535.05 634.975

GND1 14 80.95 1324.975 GND3 38 (Pin 27) 1535.05 749.975

BIASMON 15 ( Pin 11) 80.95 1209.975 PB_GND 39 1535.05 864.975

MODMON 16 (Pin 12) 8 0.95 109 4.975 GND2 40 1535.05 979.975

FAIL

GND4 18 80.95 864.975 APCSET 42 (Pin 29) 1535.05 1209.975

PB_GND 19 80.95 749.975 GND2 43 1535.05 1324.975

APCFILT 20 (Pin 14) 80.95 634.975 MODSET 44 (Pin 30) 1535.05 1439.975

GND4 21 (Pin 15) 80.95 519.975 BIASMAX 45 (Pin 31) 1535.05 1554.975

VCC4 22 (Pin 16) 80.95 404.975 VCC2 46 (Pin 32) 1535.05 1669.975

BIAS 23 (Pin 17) 80.95 289.975 GND2 47 1535.05 1784.975

PB_GND 24 291.025 80.95 GND1 48 1336.025 1995.05

Pad

No.

17 (Pin 13) 80.95 979.975 RESERVED 41 (Pin 28) 1535.05 1094.975

Coordinates (µm)

X Y X Y

Laser Diode Driver with Automatic Power Control

Signal

Name

Pad

SONET/SDH 3.125Gb/s

Coordinates (µm)

No.

G52357-0, Rev 3.2 Page 5

05/11/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 6

VITESSE

SEMICONDUCTOR CORPORATION

SONET/SDH 3.125Gb/s

Laser Diode Driver with Automatic Power Control

Package Pin Description

Figure 2: Pin Diagram

VCC

BIASMAX

MODSET

APCSET

32

31

30

29

VCC

DATA+

DATA-

VCC

CLK-

CLK+

VCC

LATCH

1

2

3

4

5

6

7

8

VSC7940

RESERVED

28

GND

27

CAPC

26

VCC

25

Preliminary Data Sheet

VSC7940

MD

24

GND

23

GND

22

VCC

21

OUT-

20

OUT+

19

VCC

18

BIAS

17

9

10

11

12

13

14

15

16

FAIL

ENABLE

DISABLE

BIASMON

Page 6 G52357-0, Rev 3.2

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

MODMON

APCFILT

GND

VCC

05/11/01

Page 7

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

VSC7940

Laser Diode Driver with Automatic Power Control

SONET/SDH 3.125Gb/s

Table 5: Pin Identifications

Pin Name Pin Number Description

GND

V

CC

DATA+ 2 Positive Data Input (PECL)

DATA- 3 Negative Data Input (PECL)

CLK+ 5 Positive Clock Input (PECL). Connect to V

CLK- 6 Negativ e Clock Input (PECL). Leave unconn ected if LATCH function is not used.

LATCH 8 Latch Input (TTL/CMOS). Connect to VCC for data retiming and GND for direct data.

ENABLE 9

DISABLE 10

BIASMON 11 Bias Current Monitor. Sink current source that is proportional to the laser bias current.

MODMON 12

FAIL 13 Output (TTL/CMOS). When low, indicates APC failure.

APCFILT 14 No effect on dev ice operation.

BIAS 17 Laser Bias Current Output

OUT+ 19 Positive Modulation-Current Output. I

OUT- 20 Negative Modulation-Current Output. I

MD 24

CAPC 26 Capacitor to GND sets dominant pole of the APC feed back loop.

RESERVED 28 Do not connect.

APCSET 29

MODSET 30 Connect resistor to GND to set desired modulation current.

BIASMAX 31

10, 15, 22,

23, 27

1, 4, 7, 16, 18,

21, 25, 32

Ground

Power Suppl y

if LATCH function is not used.

CC

Enable Input (TTL/CMOS). If used, connect DISABLE to GND. Connect to V

normal operation and GND to disable laser bias and modulation currents.

Disable Input (TTL/CMOS). If used, leave ENABLE pin floating. Connect to GND for

normal operation and V

Modulation Current Monitor. Sink current source that is proportional to the laser

modulation current.

Monitor Diode Input. Connect to monitor photodiode anode. Connect capacitor to GND to

filter high-speed AC monitor photocurrent.

Resistor to GND sets desired average optical power. If APC is not used, connect 100kΩ

resistor to GND.

Connect resistor to GND to set maximum bias current. The APC function can subtract from

this value, but cannot add to it.

to disable laser bias and modulation currents.

CC

flows when input data is high.

MOD

flows when input data is low.

MOD

CC

for

G52357-0, Rev 3.2 Page 7

05/11/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 8

VITESSE

SEMICONDUCTOR CORPORATION

SONET/SDH 3.125Gb/s

Laser Diode Driver with Automatic Power Control

Preliminary Data Sheet

VSC7940

Detailed Description

The VSC7940 is a high-speed l aser dri ver with Automatic Power Con trol. The device is desig ned to operate

up to 3.125Gb/s with a 5V supply. The data and clock inputs support PECL inputs as well as other inputs that

meet the common-mode voltage and differential voltage swing specifications. The differential pair output stage

is capable of sinking up to 100mA into the laser with ty pical rise and fall times of 60ps. The VSC79 40 is

designed to be DC-coupled . The k e y feat ures of the VSC7940 are its Automatic Power C ontr ol , l ow po wer supply current, and fast rise and fall times. The VSC7938 and VSC7939 are similar Vitesse laser drivers designed

for 60mA maximum output modula ti on cur rent s. T hese laser drivers may be powered from a 3.3V or 5V suppl y

and may be AC- or DC-couple d t o t he laser diode. The VSC7939 is available in the same 32-pin TQFP package

as the VSC7940. The VSC7938 is available in a 48-pin TQFP package.

Automatic Power Control

To ensure constant average optical power, the VSC7940 utilizes an Automatic Power Control (APC) loop.

A photodiode mounted in the laser package provides optical feedback to compensate for changes in average

laser output power due to changes that affect laser performance such as temperature and laser lifetime. The laser

bias current is adjusted by the APC loop according to the reference current set at APCSET by an external resistor. An external capacitor at CAPC controls the time constant for the APC feedback loop. The recommended

value for CAPC is 0.1

and guarantees stability. Because the APC loop noise is internally filtere d, APCFILT is not i nternal l y conn ect ed

and does not need to be connect ed to any external components. The device’s performance will not be affected if

a capacitor is connected to APCFILT. If the APC loop cannot adjust th e bias current to track th e desired monit or

current, FAIL

The device may be operated with or without APC. To utilize APC, a capacitor must be connected at CAPC

µF) and a resistor must be connected at APCSET to set the average optical power. For open-loop operation

(0.1

(no APC), a 10 0k

loop operation. In both mo des of o peratio n, resist ors to ground sho uld be p laced at BIASMAX and MODSET to

set the bias and modulation currents.

is set low.

µF. This value reduces pattern-dependent jitter associated with the APC feedback loop

Ω resistor should be connected between APCSET and GND. CAPC has no effect on open-

Data Retiming

The VSC7940 provides inpu ts for differential PECL cl ock signals for data ret iming to minim ize jitter at

high speeds. To incorporate this function, LATCH shou ld be connected to V

CLK+ should be connected to V

GND.

Short-Circuit Protection

If BIASMAX or MODSET are shorted to ground, the output mo dulation and bias currents will be turned

off.

Modulation and Bias Current Monitors

The VSC7940 provides monitoring of the modulation and bias currents vias BIASMON and MODMON.

These pins sink a current proportiona l to the actual modu lation and bias curren ts. MODMON sinks approximately 1/29th of the amount of modulation current and BIASMON sink approximately 1/37th of the amount of

the bias current. These pins should be tied through a pull-up resistor to V

that the voltage at MODMON is greater than V

1.6V.

Page 8 G52357-0, Rev 3.2

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

, CLK- should be left unconnected, and LATCH should be connected to

CC

- 1.0V and the voltage at BIASMON is greater than VCC -

CC

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

CC

. If this function is unused,

CC

. The resistors must be chosen such

05/11/01

Page 9

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

VSC7940

Enable/Disable

Laser Diode Driver with Automatic Power Control

SONET/SDH 3.125Gb/s

Two pins are provided to a llow either EN ABLE or DISABLE contr ol. If ENABLE is used, co nnect DISABLE to ground. Is DISABLE is used, leave ENABLE floating. Both modulation and bias currents are turned

off when ENABLE is low or DISABLE is high. Typically, ENABLE or DISABLE responds to within approximately 250ns.

Controlling the Modulation Current

The output modulation current may be determined from the following equation where P

peak optical power, P

is the average power, r

AVE

I

MOD

= P

A resistor at MODSET controls the output bias current. Graphs of I

is the extinction ratio, and η is the laser slope efficiency:

e

/ η= 2 * P

p-p

* (re-1) / (re+1) / η

AVE

MODSET

vs. R

MODSET

is the peak-to-

p-p

in Typical Operat-

ing Characteristics describe the relationship between the resistor at MODSET and the output modulation current at 25

°C. After determining the desired output modulation current, use the graph to determine the

appropriate resistor value at MODSET.

Controlling the Bias Current

A resistor at BIASMAX should be used to control the output bias current. Graphs of I

BIASMAX

vs. R

in Typical Operating Characte rist i cs describ e the relation ship between the resistor at BIASMAX and the out put

bias current at 25

°C. If the APC is not used, the appropriate resistor value at BIASMAX is determined by first

selecting the desired output bias current, and then using the graph to determine the appropriate resistor value at

BIASMAX. When using APC, BIASMAX sets the maximum allowed bias current. After determining the maximum end-of-life bias current at 85

°C for the laser, refer to the graph of I

BIASMAX

vs. R

BIASMAX

in Typical Oper-

ating Characteristics to select the appropriate resistor value.

BIASMAX

Controlling the APC Loop

To select the resistor at APCSET, use the graph of IMD vs. R

The graph relates the desired monitor current to the appropriate resistance value at APCSET. I

late from the desired optical average power, P

, and the laser-to-monitor transfer, ρ

AVE,

in Typical Operating Characteristics.

APCSET

MD

, for a specific laser

MON

may be calcu-

using the following equa tion:

Laser Diode Interface

I

MD

= P

AVE

* ρ

MON

An RC shunt network should be placed at the laser outpu t interface. Th e sum of the re sistor placed at the

output and the laser diode resistance should be 25

Ω resistor should be placed in series with the laser. For optimal performance, a bypass capacitor should be

20

Ω. For exam ple, if t he lase r diode ha s a resis tance of 5Ω, a

placed close to the laser anode.

A “snubber network” consisting of a capacitor C

minimize reflections from the laser (see Block Diagram). Suggested values for these components are 80

and resistor RF should be placed at the laser output to

F

Ω and

2pF, respectively, however, these values should be adjusted until an optical output waveform is obtained.

G52357-0, Rev 3.2 Page 9

05/11/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 10

VITESSE

SEMICONDUCTOR CORPORATION

SONET/SDH 3.125Gb/s

Laser Diode Driver with Automatic Power Control

Reducing Pattern-Dependent Jitter

Preliminary Data Sheet

VSC7940

Three design values significantly affect pattern-dependent jitter; the capacitor at CAPC, the pull-up inductor at the output (L

value for the capacitor at CAPC is 0.1

), and the AC-coupling c apaci t or at t he out put (CD). As previously stated, the recommended

P

µF. This results in a 10kHz loop bandwidth which makes the pattern-

dependent jitter from the APC loop negligible.

For 2.5Gb/s data rates, the recommended value for C

nated by L

. The variation in the peak vo ltage should be less that 12% of the average voltage over the maximum

P

is 0.056µF. The time constant at the output is domi-

D

consecutive identical digit (CID) period. The following equation approximates this time constant for a CID

period, t, of 100UI = 40ns:

τ

= -t / ln(1-12%) = 7.8t = LP / 25Ω

LP

Therefore, the inductor LP should be a 7.8µH SMD ferrite bead inductor for this case.

Input/Output Considerations

Although the VSC7940 is PECL-compatible, this is not required to drive the device. The inputs must only

meet the common-mode voltage and differential voltage swing specifications.

Power Consumption

The following equation provides the device supply current (IS) in terms of quiescent current (IQ), modulation current (I

), and bias current (I

MOD

BIAS

):

I

= 19mA + 0.4 * I

S

+ 0.16 * I

MOD

BIAS

This equation may be used to determine the estimated power dissipation:

P

= VCC * I

DIS

S

For example, if the device were operated at 5V with a 30mA modulation current and a 10mA bias current,

the supply current would be:

= 19mA + 0.4 * 30mA + 0.16 * 10mA = 33mA

I

S

This corresponds to a power dissipation of 5V * 33mA = 165mW.P

Page 10 G52357-0, Rev 3.2

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

05/11/01

Page 11

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

VSC7940

Typical Operating Characteristics

I

BIASMAX

vs. R

BIASMAX

T=25°C, VCC = 5V

SONET/SDH 3.125Gb/s

Laser Diode Driver with Automatic Power Control

I

vs. R

MOD

T=25°C VCC = 5V

MODSET

IMD vs. R

T=25°C, V

APCSET

= 5V

CC

,

G52357-0, Rev 3.2 Page 11

05/11/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 12

VITESSE

SEMICONDUCTOR CORPORATION

SONET/SDH 3.125Gb/s

Preliminary Data Sheet

Laser Diode Driver with Automatic Power Control

Applications Information

The following is a typical design example for the VSC7940 assuming 5V operation with APC.

Select a Laser

The Table 8 provides specifications for a typical communication-grade laser capable of operating at

2.5Gb/s.

Table 6: Typical Laser Characteristics

Symbol Parameter Value Units

λ Wavelength 1310 nm

P

AVE

I

th

ρ

MON

η Laser Slope Efficiency 0.4 mW/mA

T

C

Select Resistor for APCSET

The monitor diode current is estimated by IMD = P

vs. R

APCSET

Average Opti cal Output Power 6 mW

Threshold Current 6 mA

Laser to Monitor Transfer 0.04 mA/mW

Operating Temperature Range -40 to +85 °C

AVE

* ρ

= 6mW * 0.04mA/mW = 0.24mA. The IMD

MON

in Typical Operating Characteristics shows the resistor at APCSET should be 5kΩ.

VSC7940

Select Resistor for MODSET

T o ensure some minimum extinction ratio over temperature and lifetime, assume an optimal extinction ratio

of 20 (13dB) at 25

I

MOD

The graph of I

should be 8.5k

Select Resistor for BIASMAX

°C. The modulation current may be calculated from the following equation:

= P

/ η= 2 * P

p-p

MODSET

vs. R

* (re-1) / (re+1) / η = 2 * 6mA * (20-1) / (20 + 1) / 0.4 = 27.1mA

AVE

MODSET

in Typical Operating Characteristics shows the resistor for MODSET

Ω.

The maximum threshold current at +85°C and end of life must be determined. A graph of a typical laser’s

versus TC reveals a maximum threshold current of 30mA at 85°C. Therefore, the maxim um bias can be

I

th

approximated by:

The graph of I

should be 5k

Ω.

I

BIASMAX

BIASMAX

vs. R

= I

BIASMAX

TH-MAX

+ I

/ 2 = 30mA + 27.1mA / 2 = 43.6mA

MOD

in T ypi cal Operating Characteristics shows the resistor for BIASMAX

Page 12 G52357-0, Rev 3.2

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

05/11/01

Page 13

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

VSC7940

Select Resistors for MODMON and BIASMON

Assuming the modulation and bias currents never exceed 120mA, the following equations provide values

for the resistor at MODMON, R

Standard values for these values are R

MODMON would indicate a modulation current of:

Wire Bonding

For best performance, gold ball-bonding techniques are recommended. Wedge bonding is not recommended. For best performance and to minimize inductance keep wire bond lengths short.

MODMON

I

MOD

, and the resistor at BIASMON, R

R

MODMON

R

BIASMON

= 1.6V * 35 / 120mA = 467Ω

MODMON

= (5.2V - 4.8V) * 28 / 232mA = 48mA

Laser Diode Driver with Automatic Power Control

BIASMON

= 1V * 28 / 120mA = 233Ω

= 232Ω and R

BIASMON

SONET/SDH 3.125Gb/s

:

= 464Ω. A voltage of 4.8V at

PCB Layout Guidelines

Use high frequency PCB layout techniques with solid ground planes to minimize crosstalk and EMI. Keep

high speed traces as short as possible for signal integrity. The output traces to the laser diode must be short to

minimize inductance. Short output traces will provide best performance.

G52357-0, Rev 3.2 Page 13

05/11/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 14

VITESSE

SEMICONDUCTOR CORPORATION

SONET/SDH 3.125Gb/s

Laser Diode Driver with Automatic Power Control

Package Information - 32 Pin TQFP

Preliminary Data Sheet

VSC7940

1. All dimensioning and tolerancing conform to ANSI Y14.5-1982

2. Controlling dimension: millimeter

3. This outline conforms to JEDEC Publication 95 Registration MS-026

Page 14 G52357-0, Rev 3.2

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

05/11/01

Page 15

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

VSC7940

Ordering Informatio n

The order number for this product is formed by a combination of the device type and package type.

Device Type

SONET/SDH 3.125Gb/s

Laser Diode Driver with Automatic Power Control

VSC7940

SONET/SDH 3.125Gb/s

Laser Diode Driver with Automatic Power Control

xx

Package

RP: 32-Pin TQFP

W: Dice Waffle Pack

otice

itesse Semiconductor Corporation (“Vitesse”) provides this document for informational purposes only. This document contains pre-production information

bout Vitesse products in the ir co ncept, developm ent a nd/or tes tin g phase. Al l infor matio n in this docume nt, in cludi ng desc ripti ons of features, functions,

erformance, technica l s p ecifications and availability, is subject to chan g e wit h o ut n ot i ce at any time. Nothing contained in t his document shall be construed

s extending any warr anty or p romise , expr ess or impl ied, t hat a ny Vitesse prod uct will be a vaila ble as desc rib ed or wi ll be sui table for or will accomplish

ny particular task.

itesse products are not intended for use in life support appliances, devices or systems. Use of a Vitesse product in such applications without written consent

s prohibited.

G52357-0, Rev 3.2 Page 15

05/11/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 16

VITESSE

SEMICONDUCTOR CORPORATION

SONET/SDH 3.125Gb/s

Laser Diode Driver with Automatic Power Control

Preliminary Data Sheet

VSC7940

Page 16 G52357-0, Rev 3.2

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

05/11/01

Loading...

Loading...