Page 1

DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD75P3116

4-BIT SINGLE-CHIP MICROCONTROLLER

The µPD75P3116 replaces the µPD753108’s internal mask ROM with a one-time PROM, and features expanded ROM

capacity.

µ

Because the

development stage using the

Detailed information about functions is provided in the following User’s Manual. Be sure to read it before

designing:

PD75P3116 supports programming by users, it is suitable for use in evaluation of systems in the

µ

PD753104, 753106, or 753108, and for use in small-scale production.

µ

PD753108 User’s Manual : U10890E

FEATURES

Compatible with µPD753108

Memory capacity:

• PROM : 16384 x 8 bits

• RAM : 512 x 4 bits

Can be operated in same power supply voltage range as the mask version µPD753108

DD = 1.8 to 5.5 V

• V

On-chip LCD controller/driver

QTOPTM microcontroller

Remark QTOP microcontrollers are microcontrollers with on-chip one-time PROM that are totally supported by NEC.

The support include writing application programs, marking, screening, and verification.

ORDERING INFORMATION

Part Number Package

µ

PD75P3116GC-AB8 64-pin plastic QFP (14 x 14 mm, 0.8-mm pitch)

µ

PD75P3116GK-8A8 64-pin plastic QFP (12 x 12 mm, 0.65-mm pitch)

Caution This device does not provide an internal pull-up resistor connection function by means of mask

option.

Document No. U11369EJ2V0DS00 (2nd edition)

Date Published March 1997 N

Printed in Japan

The information in this document is subject to change without notice.

The mark shows major revised points.

©

1994

Page 2

µ

PD75P3116

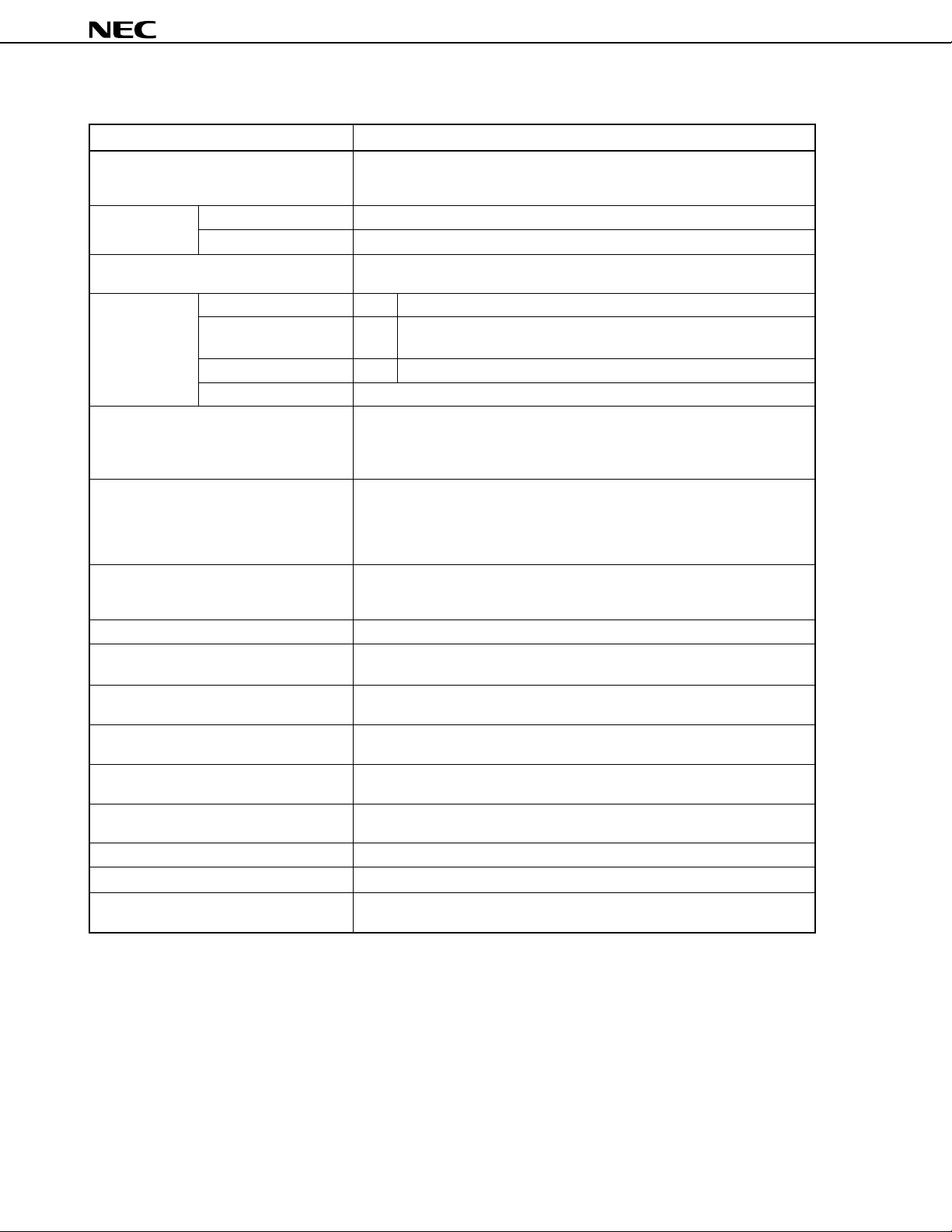

FUNCTION OUTLINE

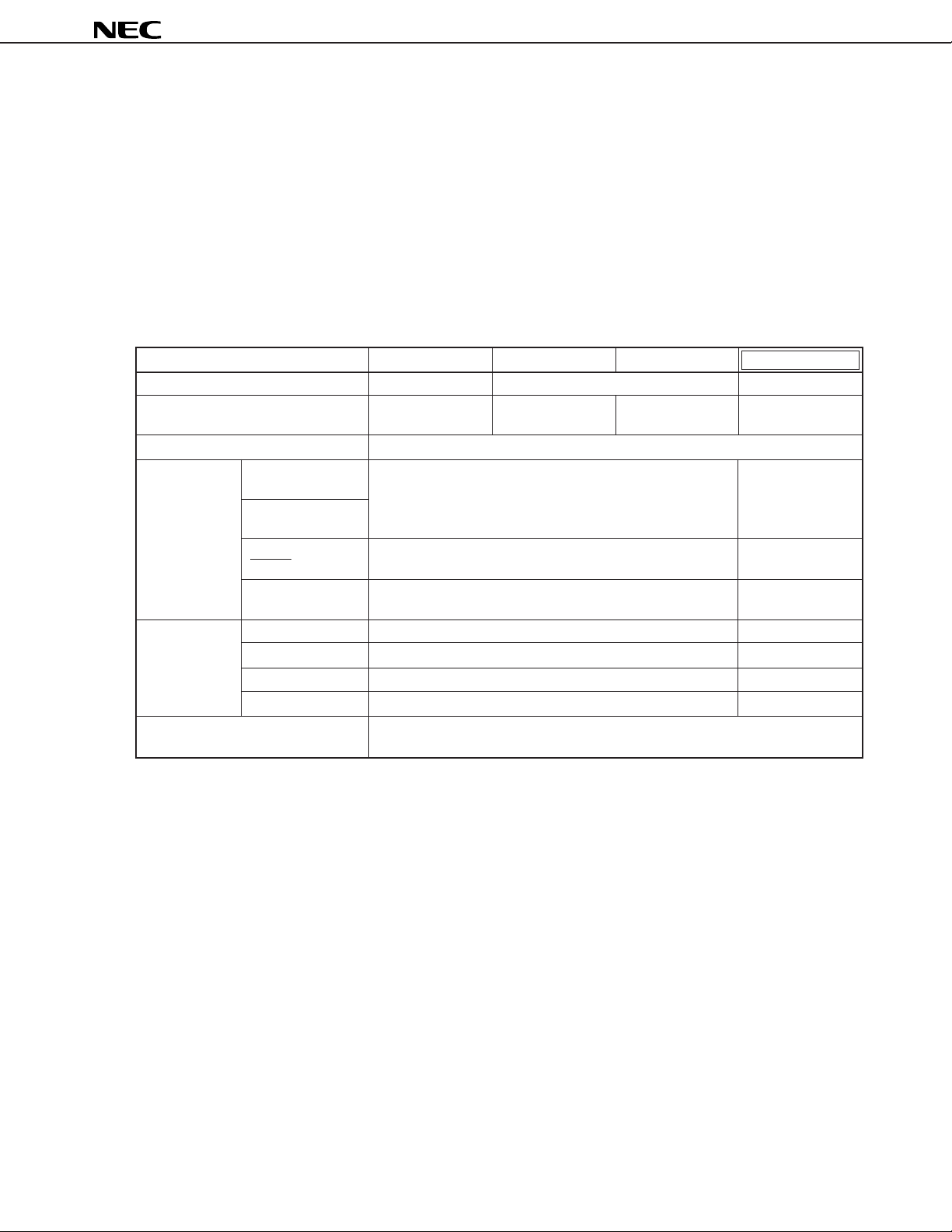

Item Function

Instruction execution time • 0.95, 1.91, 3.81, or 15.3 µs (main system clock: @ 4.19 MHz)

• 0.67, 1.33, 2.67, or 10.7 µs (main system clock: @ 6.0 MHz)

• 122 µs (subsystem clock: @ 32.768 kHz)

Internal memory PROM 16384 x 8 bits

RAM 512 x 4 bits

General-purpose register • 4-bit manipulation: 8 x 4 banks

• 8-bit manipulation: 4 x 4 banks

I/O ports CMOS input 8 Internal pull-up resistor connection can be specified by software: 7

CMOS I/O 20 Internal pull-up resistor connection can be specified by software: 12

Shared by segment pin: 8

N-ch open-drain I/O 4 13-V withstand voltage

Total 32

LCD controller/driver • Segment number selection: 16/20/24 segments (Switchable to CMOS I/O

ports in a batch of 4 pins, max. 8 pins)

• Display mode selection : static, 1/2 duty (1/2 bias), 1/3 duty (1/2 bias),

1/3 duty (1/3 bias), 1/4 duty (1/3 bias)

Timers 5 channels: • 8-bit timer/event counter : 3 channels

(Can be used as 16-bit timer/event counter, carrier generator,

and timer with gate)

• Basic interval timer/watchdog timer : 1 channel

• Watch timer : 1 channel

Serial interface • 3-wire serial I/O mode ··· MSB/LSB first switchable

• 2-wire serial I/O mode

• SBI mode

Bit sequential buffer (BSB) 16 bits

Clock output (PCL) Φ, 524, 262, and 65.5 kHz (main system clock: @ 4.19 MHz)

Φ, 750, 375, and 93.8 kHz (main system clock: @ 6.0 MHz)

Buzzer output (BUZ) • 2, 4, and 32 kHz (

• 2.93, 5.86, 46.9 kHz (main system clock: @ 6.0 MHz)

Vectored interrupts • External : 3

• Internal : 5

Test inputs • External : 1

• Internal : 1

System clock oscillation circuit • Ceramic/crystal oscillation circuit for main system clock

• Crystal oscillation circuit for subsystem clock

Standby function STOP/HALT mode

Power supply voltage V

Package • 64-pin plastic QFP (14 x 14 mm, 0.8-mm pitch)

DD = 1.8 to 5.5 V

• 64-pin plastic QFP (12 x 12 mm, 0.65-mm pitch)

main system clock: @ 4.19 MHz or subsystem clock: @ 32.768 kHz

)

2

Page 3

µ

PD75P3116

CONTENTS

1. PIN CONFIGURATION (Top View) .................................................................................................. 4

2. BLOCK DIAGRAM ............................................................................................................................ 5

3. PIN FUNCTIONS ............................................................................................................................... 6

3.1 Port Pins ................................................................................................................................................... 6

3.2 Non-port Pins ........................................................................................................................................... 8

3.3 Equivalent Circuits for Pins .................................................................................................................... 10

3.4 Recommended Connection of Unused Pins ......................................................................................... 12

4. Mk I AND Mk II MODE SELECTION FUNCTION ............................................................................. 13

4.1 Differences between Mk I Mode and Mk II Mode ................................................................................... 13

4.2 Setting of Stack Bank Selection (SBS) Register ................................................................................... 14

5. DIFFERENCES BETWEEN µPD75P3116 AND µPD753104, 753106, AND 753108 ...................... 15

6. MEMORY CONFIGURATION ........................................................................................................... 16

7. INSTRUCTION SET .......................................................................................................................... 18

8. ONE-TIME PROM (PROGRAM MEMORY) WRITE AND VERIFY ................................................... 27

8.1 Operation Modes for Program Memory Write/Verify ............................................................................ 27

8.2 Program Memory Write Procedure ......................................................................................................... 28

8.3 Program Memory Read Procedure ......................................................................................................... 29

8.4 One-time PROM Screening ..................................................................................................................... 30

9. ELECTRICAL SPECIFICATIONS ..................................................................................................... 31

10. CHARACTERISTIC CURVES (REFERENCE VALUES) .................................................................. 46

11. PACKAGE DRAWINGS ................................................................................................................... 48

12. RECOMMENDED SOLDERING CONDITIONS ................................................................................ 50

APPENDIX A. FUNCTION LIST OF µPD75308B, 753108, AND 75P3116 ........................................... 51

APPENDIX B. DEVELOPMENT TOOLS................................................................................................ 53

APPENDIX C. RELATED DOCUMENTS ............................................................................................... 57

3

Page 4

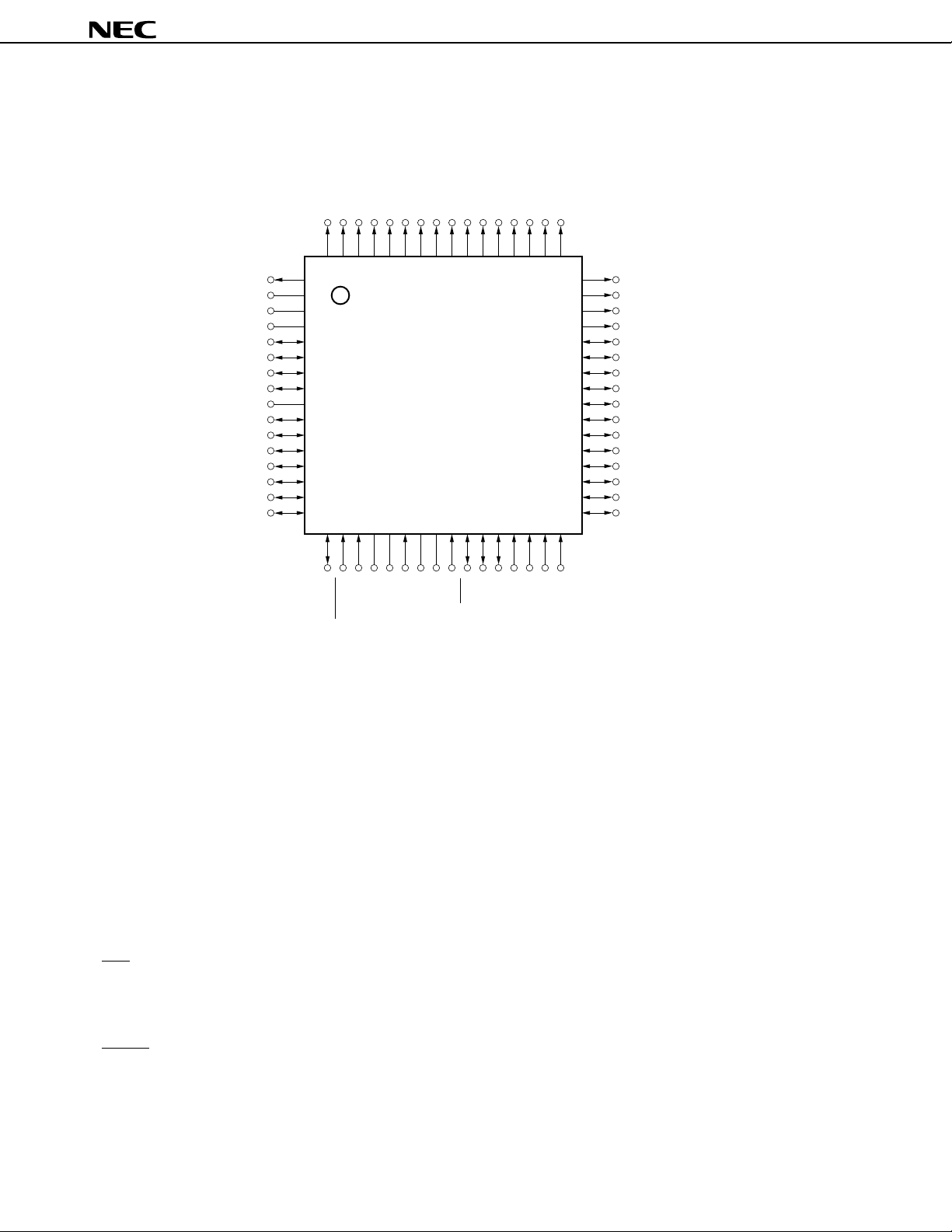

1. PIN CONFIGURATION (Top View)

• 64-pin plastic QFP (14 x 14 mm, 0.8-mm pitch) :µPD75P3116GC-AB8

µ

• 64-pin plastic QFP (12 x 12 mm, 0.65-mm pitch):

COM363COM262COM161COM060S059S158S257S356S455S554S653S752S851S950S1049S11

PD75P3116GK-8A8

µ

PD75P3116

64

BIAS

V

LC0

V

LC1

V

P30/LCDCL/MD0

P31/SYNC/MD1

P60/KR0/D0

P61/KR1/D1

P62/KR2/D2

LC2

P32/MD2

P33/MD3

Vss

P50/D4

P51/D5

P52/D6

P53/D7

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

Note Always connect the V

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

18

19

21

22X123X224

Note

XT120XT2

RESET

P63/KR3/D3

PP pin directly to VDD during normal operation.

VPP

25

26

VDD

P00/INT4

27

28

29

P01/SCK

P03/SI/SB1

P02/SO/SB0

33

30

31

32

P13/TI0

P10/INT0

P11/INT1

P12/INT2/TI1/TI2

S12

S13

S14

S15

P93/S16

P92/S17

P91/S18

P90/S19

P83/S20

P82/S21

P81/S22

P80/S23

P23/BUZ

P22/PCL/PTO2

P21/PTO1

P20/PTO0

PIN IDENTIFICATIONS

P00-P03 : Port0 COM0 to COM3 : Common Output 0 to 3

P10-P13 : Port1 V

LC0 to VLC2 : LCD Power Supply 0 to 2

P20-P23 : Port2 BIAS : LCD Power Supply Bias Control

P30-P33 : Port3 LCDCL : LCD Clock

P50-P53 : Port5 SYNC : LCD Synchronization

P60-P63 : Port6 TI0 to TI2 : Timer Input 0 to 2

P80-P83 : Port8 PTO0 to PTO2 : Programmable Timer Output 0 to 2

P90-P93 : Port9 BUZ : Buzzer Clock

KR0-KR3 : Key Return 0 to 3 PCL : Programmable Clock

SCK : Serial Clock INT0, 1, 4 : External Vectored Interrupt 0, 1, 4

SI : Serial Input INT2 : External Test Input 2

SO : Serial Output X1, X2 : Main System Clock Oscillation 1, 2

SB0, SB1 : Serial Data Bus 0, 1 XT1, XT2 : Subsystem Clock Oscillation 1, 2

RESET : Reset V

MD0 to MD3 : Mode Selection 0 to 3 V

PP : Programming Power Supply

DD : Positive Power Supply

D0 to D7 : Data Bus 0 to 7 Vss : Ground

S0 to S23 : Segment Output 0 to 23

4

Page 5

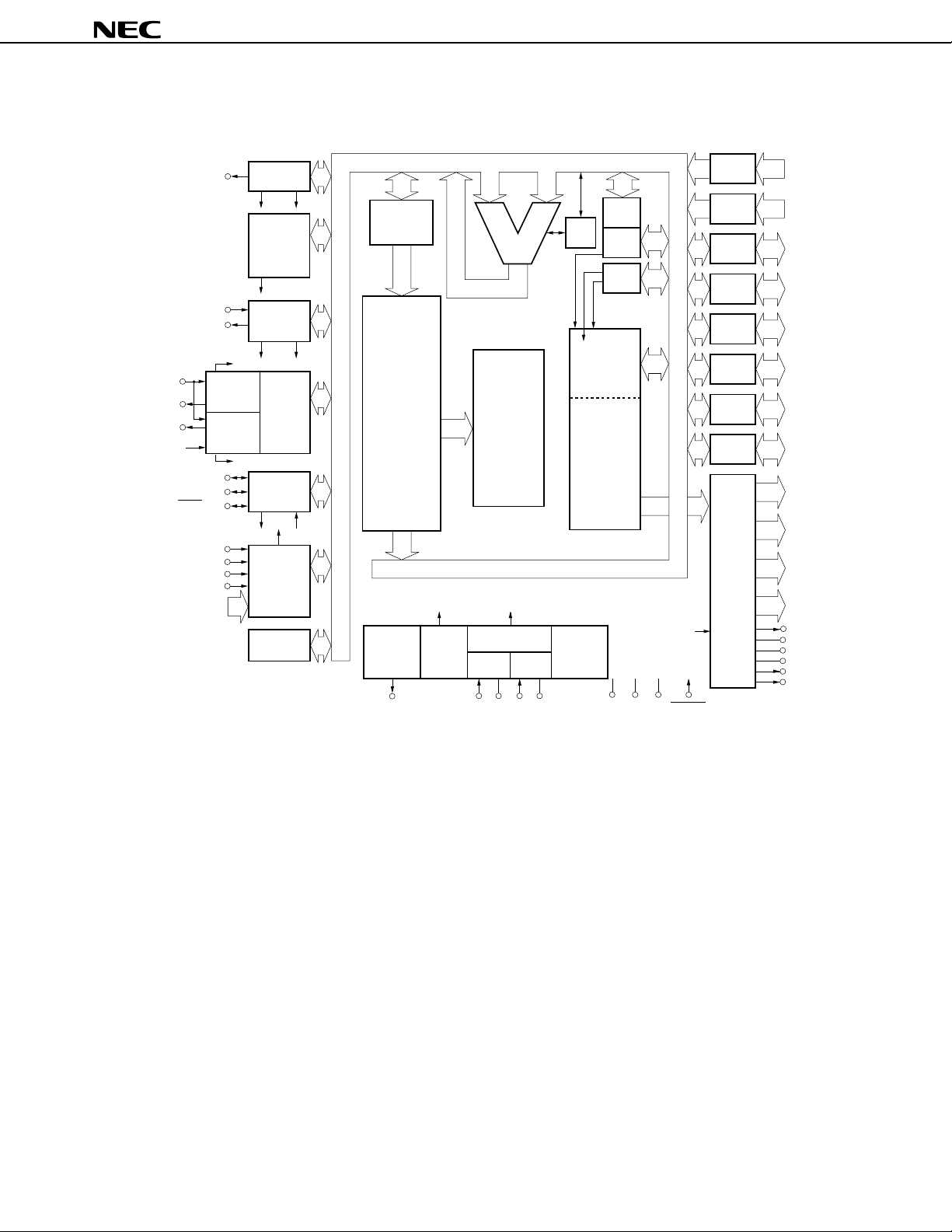

2. BLOCK DIAGRAM

µ

PD75P3116

BUZ/P23

PTO0/P20

TI1/TI2/

P12/INT2

PTO1/P21

PTO2/

PCL/P22

TOUT0

SI/SB1/P03

SO/SB0/P02

SCK/P01

INT0/P10

INT1/P11

INT4/P00

INT2/P12/TI1/TI2

P60/KR0 to

P63/KR3

TI0/P13

TIMER/EVENT

COUNTER #1

TIMER/EVENT

COUNTER #2

BASIC

INTERVAL

TIMER/

WATCHDOG

TIMER

TIMER/EVENT

COUNTER #0

INTT1

8-BIT

8-BIT

INTT2

CLOCKED

SERIAL

INTERFACE

INTERRUPT

CONTROL

4

BIT SEQ.

BUFFER (16)

WATCH

TIMER

INTW f

LCD

INTBT

8-BIT

INTT0 TOUT0

CASCADED

16-BIT

TIMER/

EVENT

COUNTER

INTCSI

TOUT0

INT1

PROGRAM

COUNTER (14)

PROGRAM

MEMORY

(PROM)

16384 x 8 BITS

CLOCK

OUTPUT

CONTROL

PCL/PTO2/P22

fx/2

CLOCK

DIVIDER

ALU

DECODE

AND

CONTROL

N

CPU CLOCK Φ

SYSTEM CLOCK

GENERATOR

MAIN SUB

X2X1 XT2XT1

CY

GENERAL

REG.

DATA

MEMORY

(RAM)

512 x 4 BITS

STAND BY

CONTROL

SP (8)

SBS

BANK

V

DD

PORT0 P00 to P03

PORT1 P10 to P13

PORT2

PORT3

PORT5

PORT6

PORT8 P80 to P83

PORT9 P90 to P93

f

LCD

V

PP

RESETVss

4

4

4

4

4

4

4

4

4

4

LCD

DRIVER

CONTROLLER/

P20 to P23

P30/MD0 to

P33/MD3

P50/D4 to

P53/D7

P60/D0 to

P63/D3

S0 to S1516

S16/P93 to

S19/P90

S20/P83 to

S23/P80

COM0 to COM34

BIAS

V

LC0

V

LC1

V

LC2

SYNC/P31

LCDCL/P30

5

Page 6

3. PIN FUNCTIONS

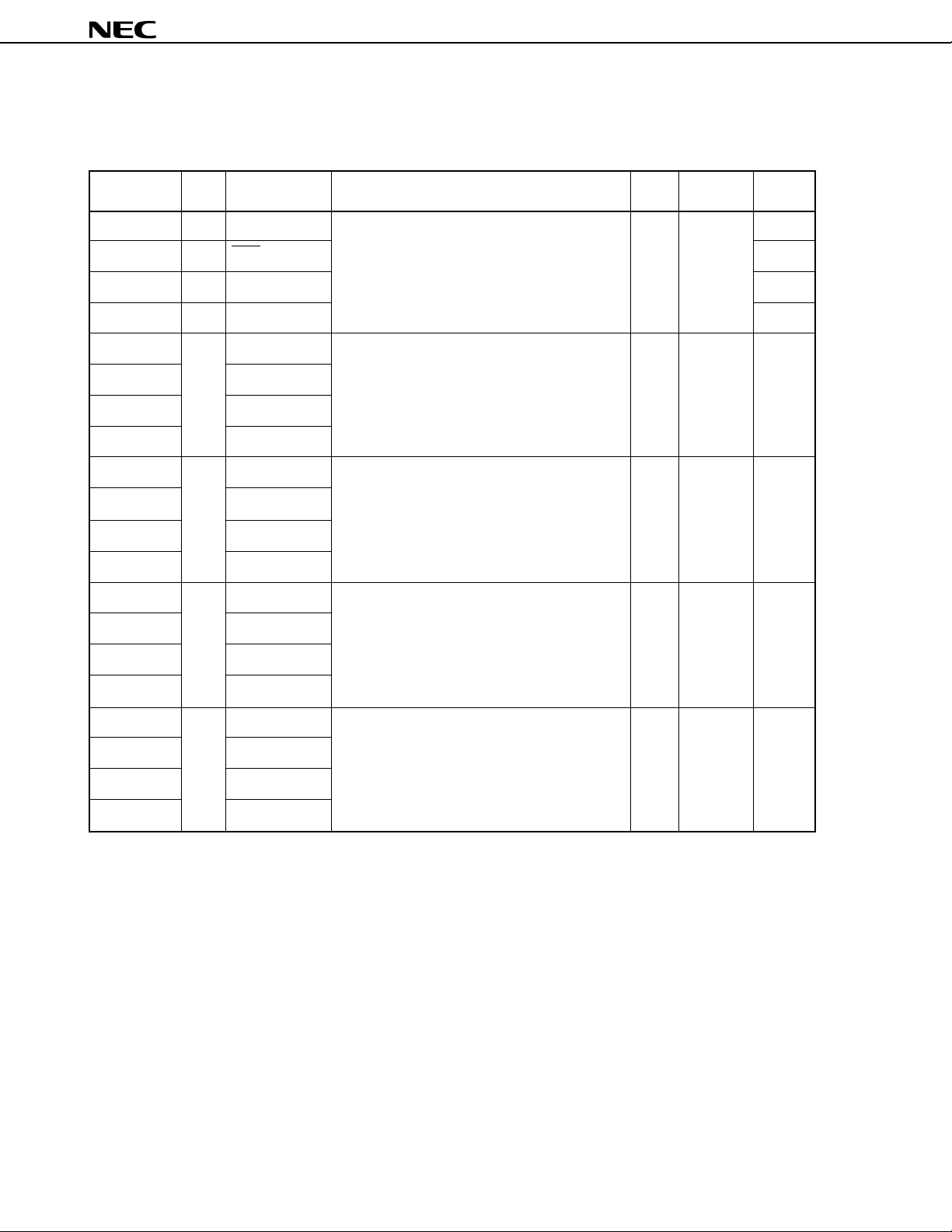

3.1 Port Pins (1/2)

µ

PD75P3116

Pin name I/O Alternate function Function 8-bit Status I/O circuit

I/O after reset type

P00 Input INT4 4-bit input port (PORT0) X Input <B>

P01 to P03 are 3-bit pins for which connection of

P01 I/O SCK an internal pull-up resistor can be specified by <F>-A

software.

P02 I/O SO/SB0 <F>-B

P03 I/O SI/SB1 <M>-C

P10 Input INT0 4-bit input port (PORT1) X Input <B>-C

Connection of an internal pull-up resistor can be

P11 INT1 specified by software in 4-bit units.

P10/INT0 can select noise elimination circuit.

P12 TI1/TI2/INT2

P13 TI0

P20 I/O PTO0 4-bit I/O port (PORT2) X Input E-B

Connection of an internal pull-up resistor

P21 PTO1 can be specified by software in 4-bit units.

P22 PCL/PTO2

P23 BUZ

P30 I/O LCDCL/MD0 Programmable 4-bit I/O port (PORT3) X Input E-B

Input and output in single-bit units can be specified.

P31 SYNC/MD1 When set for 4-bit units, connection of an internal

pull-up resistor can be specified by software.

P32 MD2

Note 1

P33 MD3

Note 2

P50

P51

P52

P53

Note 2

Note 2

Note 2

I/O D4 N-ch open-drain 4-bit I/O port (PORT5) X High M-E

When set to open-drain, voltage is 13 V. impedance

D5

D6

D7

Notes 1. Circuit types enclosed in brackets indicate Schmitt trigger input.

2. Low-level input leakage current increases when input instructions or bit manipulation instructions are executed.

6

Page 7

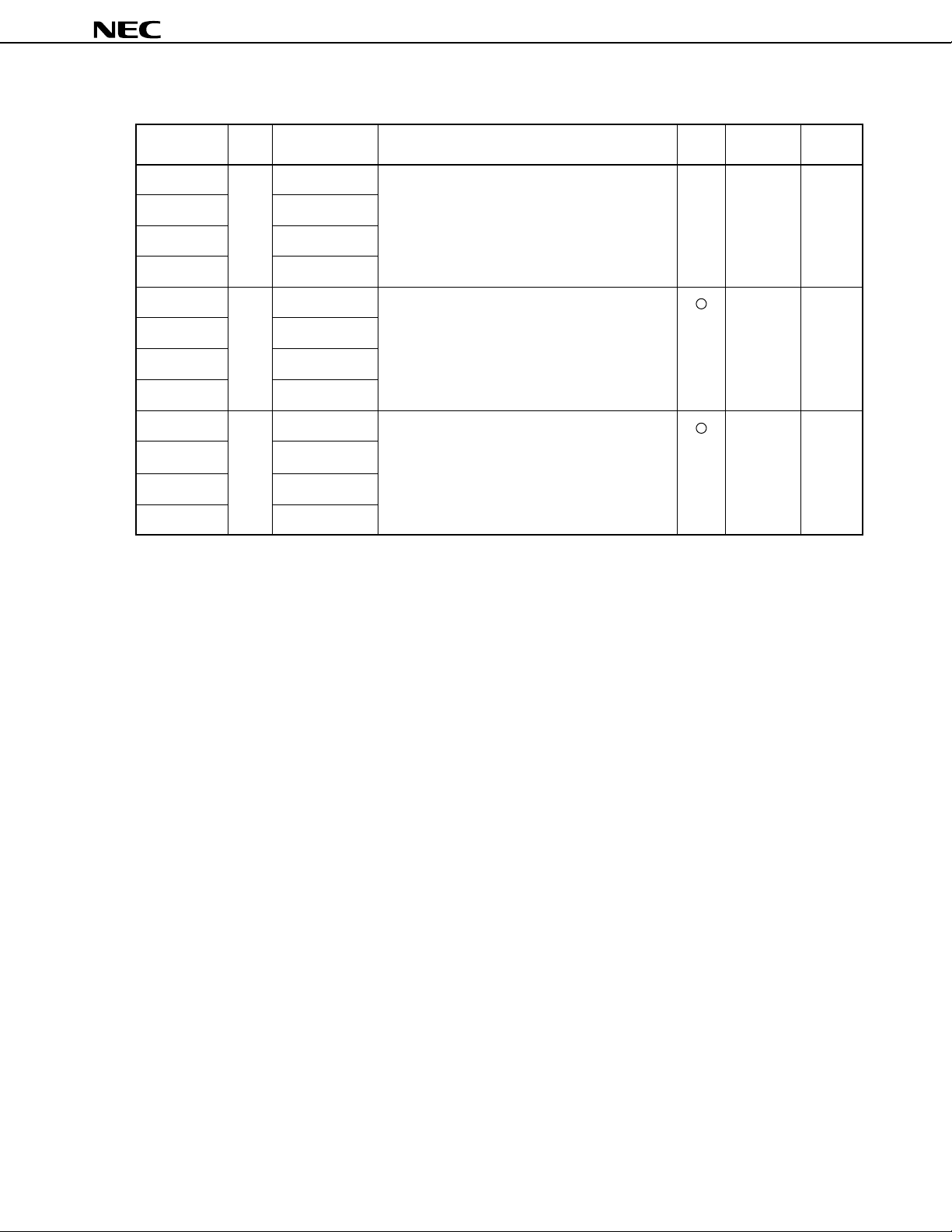

3.1 Port Pins (2/2)

µ

PD75P3116

Pin name I/O Alternate function Function 8-bit Status I/O circuit

I/O after reset type

P60 I/O KR0/D0 Programmable 4-bit I/O port (PORT6) X Input <F>-A

Input and output in single-bit units can be specified.

P61 KR1/D1 When set for 4-bit units, connection of an internal

pull-up resistor can be specified by software.

P62 KR2/D2

P63 KR3/D3

P80 I/O S23 4-bit I/O port (PORT8) Input H

When set for 4-bit units, connection of an internal

P81 S22 pull-up resistor can be specified by software

P82 S21

P83 S20

P90 I/O S19 Programmable 4-bit I/O port (PORT9) Input H

When set for 4-bit units, connection of an internal

P91 S18 pull-up resistor can be specified by software

P92 S17

P93 S16

Note 3

Note 3

.

.

Notes 1. Circuit types enclosed in brackets indicate Schmitt trigger input.

2. Low-level leak current increases when an input instruction or a bit manipulation instruction is performed.

3. Do not connect an internal pull-up resistor by software when used as the segment signal output.

Note 1

7

Page 8

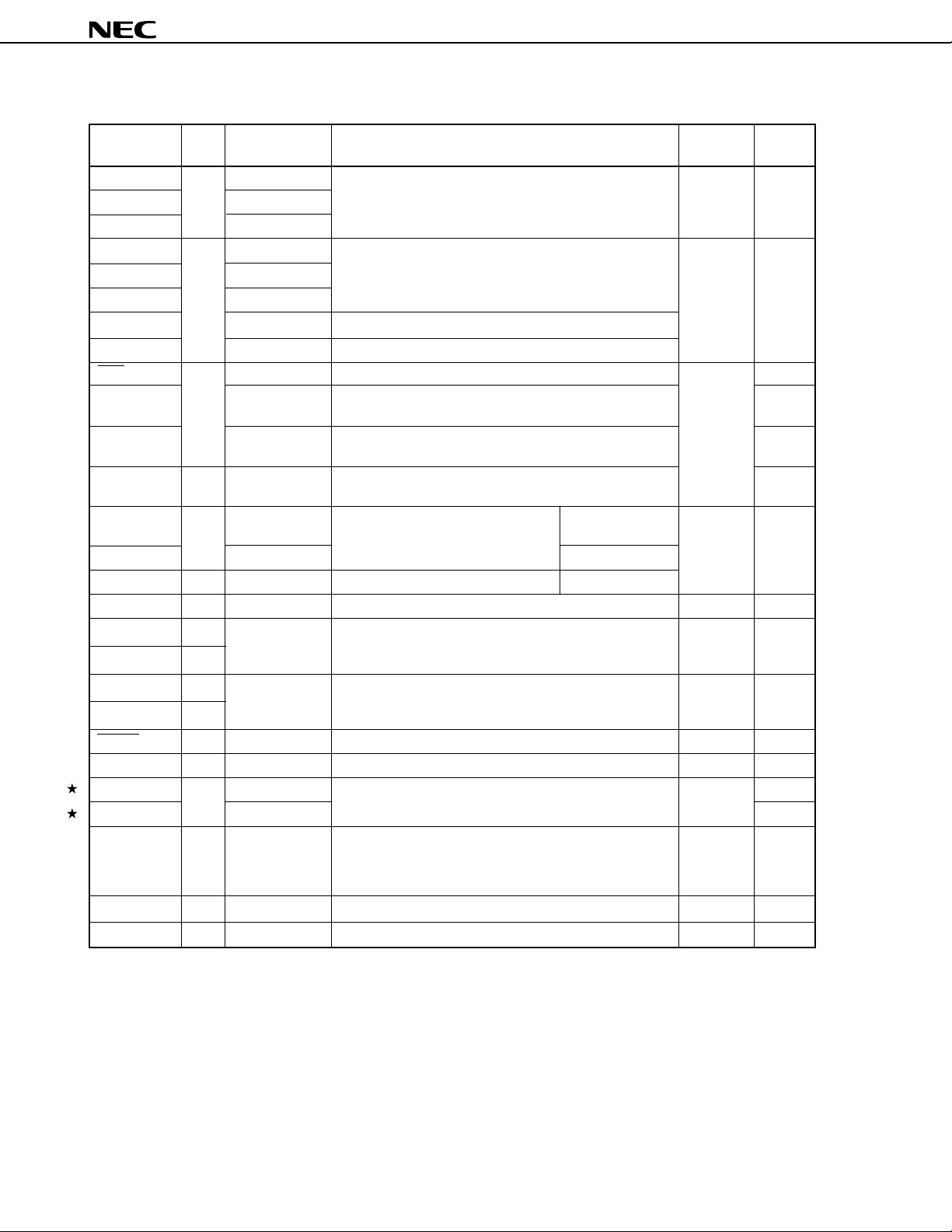

3.2 Non-port Pins (1/2)

µ

PD75P3116

Pin name I/O Alternate function Function Status I/O circuit

after reset type

TI0 Input P13 External event pulse input to timer/event counter Input <B>-C

TI1 P12/INT2/TI2

TI2 P12/INT2/TI1

PTO0 Output P20 Timer/event counter output Input E-B

PTO1 P21

PTO2 P22/PCL

PCL P22/PTO2 Clock output

BUZ P23 Frequency output (for buzzer or system clock trimming)

SCK I/O P01 Serial clock I/O Input <F>-A

SO/SB0 P02 Serial data output <F>-B

Serial data bus I/O

SI/SB1 P03 Serial data input <M>-C

Serial data bus I/O

INT4 Input P00 Edge detection vectored interrupt input <B>

(valid for detecting both rising and falling edges)

INT0 Input P10 Edge detection vectored interrupt input

(detection edge is selectable)

INT1 P11

INT2 Input P12/TI1/TI2 Rising edge detection testable input Asynch

KR0 to KR3 I/O P60 to P63 Parallel falling edge detection testable input Input <F>-A

X1 Input — Ceramic/crystal resonator connection for main system — —

X2 — and input inverted phase to X2.

XT1 Input — Crystal resonator connection for subsystem clock oscillation. — —

XT2 — phase to XT2. XT1 can be used as a 1-bit (test) input.

RESET Input — System reset input (low-level active) — <B>

MD0 to MD3 Input P30 to P33 Mode selection for program memory (PROM) write/verify Input E-B

D0 to D3 I/O

D4 to D7 P50 to P53 M-E

Note 2

V

PP

VDD — — Positive power supply — —

Vss — — Ground potential — —

P60/KR0 to P63/KR3

— — Programmable power supply voltage applied for program — —

INT0/P10 can select noise elimination circuit.

clock oscillation. If using an external clock, input signal to X1

If using an external clock, input signal to XT1 and input inverted

Data bus for program memory (PROM) write/verify Input <F>-A

memory (PROM) write/verify.

For normal operation, connect directly to VDD.

Apply +12.5 V for PROM write/verify.

With noise elimination

circuit/asynch is selectable

Asynch

Input <B>-C

Note 1

Notes 1. Circuit types enclosed in brackets indicate Schmitt trigger input.

2. The V

PP pin does not operate correctly when it is not connected to the VDD pin during normal operation.

8

Page 9

µ

PD75P3116

3.2 Non-port Pins (2/2)

Pin name I/O Alternate function Function Status I/O circuit

after reset type

S0 to S15

S16 to S19

S20 to S23

COM0 to COM3

VLC0 to VLC2 — — Power supply for driving LCD — —

BIAS Output — Output for external split resistor cut Note 2 —

LCDCL

Note 3

SYNC

Note 3

Output — Segment signal output Note 1 G-A

Output P93 to P90 Segment signal output Input H

Output P83 to P80 Segment signal output Input H

Output — Common signal output Note 1 G-B

I/O P30/MD0 Clock output for driving external expansion driver Input E-B

I/O P31/MD1 Clock output for synchronization of external expansion driver Input E-B

Notes 1. The VPP pin does not operate normally if it is not connected with VDD pin when normal operation.

2. The V

LCX (X = 0, 1, 2) shown below are selected as the input source for the display outputs.

S0 to S23: V

LC1, COM0 to COM2: VLC2, COM3: VLC0

3. When the split resistor is incorporated : Low level

When the split resistor is not incorporated : High impedance

4. These pins are provided for future system expansion. Currently, only P30 and P31 are used.

9

Page 10

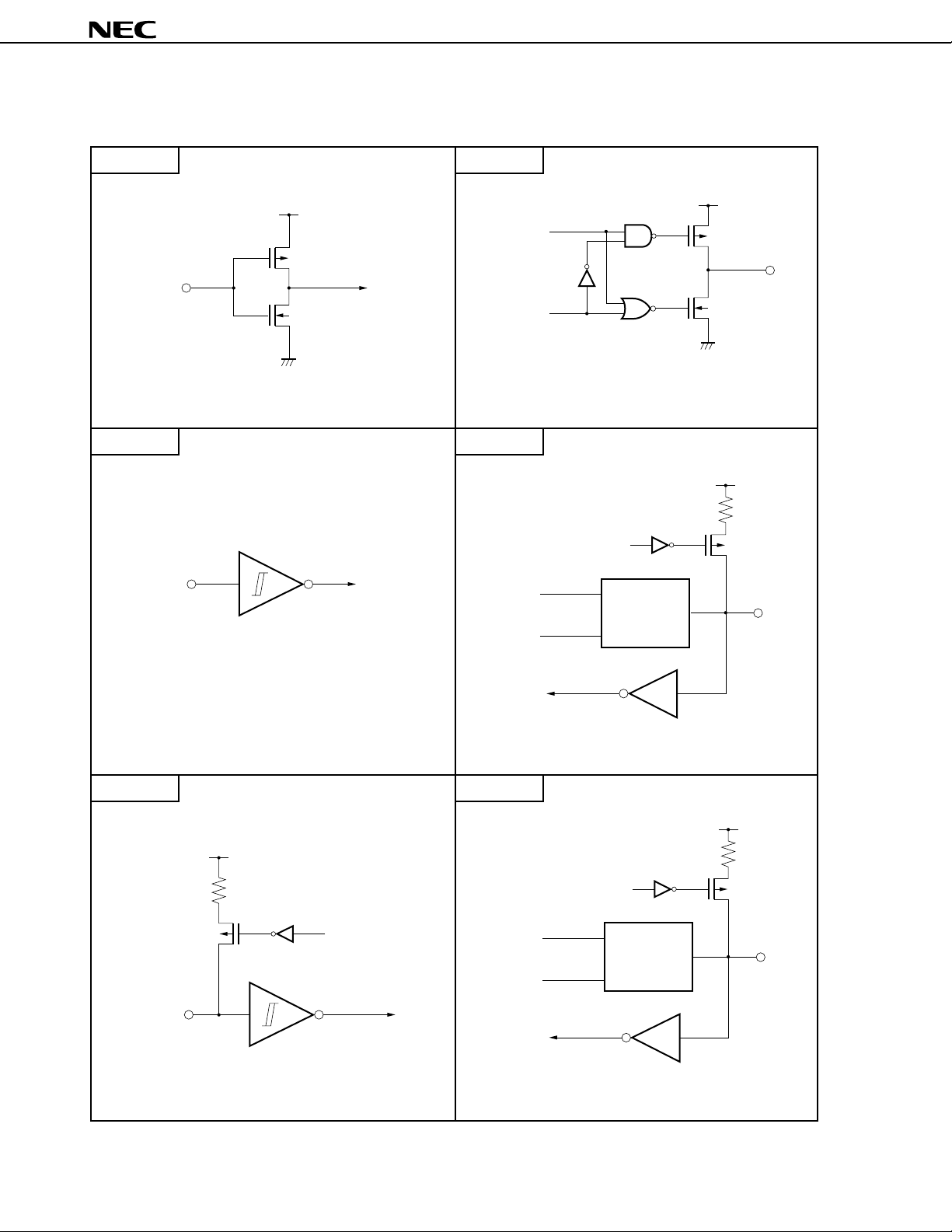

3.3 Equivalent Circuits for Pins

µ

The equivalent circuits for the

TYPE A TYPE D

PD75P3116’s pins are shown in abbreviated form below.

µ

PD75P3116

VDD

P-ch

IN

N-ch

CMOS standard input buffer

IN

VDD

Data

Output

disable

Push-pull output that can be set to high impedance output

(with both P-ch and N-ch OFF).

TYPE E-BTYPE B

P.U.R.

enable

Data

Type D

Output

disable

P-ch

N-ch

VDD

P.U.R.

P-ch

IN/OUT

OUT

Schmitt trigger input with hysteresis characteristics.

TYPE B-C TYPE F-A

VDD

P.U.R.

P-ch

IN

P.U.R. : Pull-Up Resistor

P.U.R.

enable

Output

disable

Data

Type A

P.U.R. : Pull-Up Resistor

P.U.R.

enable

Type D

Type B

P.U.R. : Pull-Up Resistor

VDD

P.U.R.

P-ch

IN/OUT

(Continued)

10

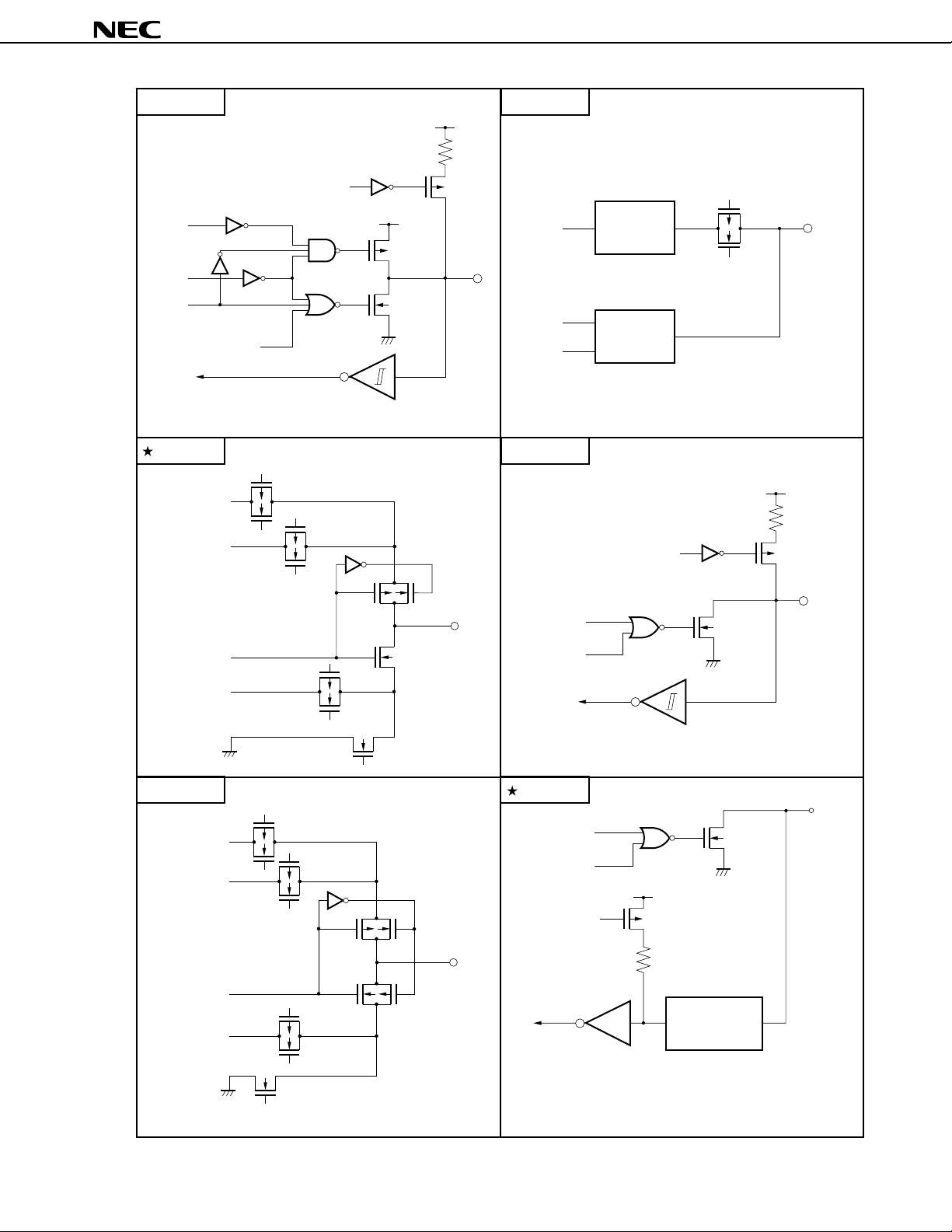

Page 11

TYPE F-B TYPE H

VDD

P.U.R.

µ

PD75P3116

(Continued)

Output

disable

(P)

Data

Output

disable

Output

disable

(N)

P.U.R. : Pull-Up Resistor

LC0

V

VLC1

SEG

data

V

LC2

P-ch

N-ch

P-ch

N-ch

P-ch

N-ch

P.U.R.

enable

VDD

P-ch

N-ch

N-chP-ch

N-ch

P-ch

IN/OUT

OUT

Output

disable

TYPE M-CTYPE G-A

SEG

data

Data

Output

disable

Data

Type G-A

Type E-B

P.U.R.

enable

N-ch

P-ch

N-ch

IN/OUT

VDD

P.U.R.

P-ch

IN/OUT

N-ch

TYPE G-B TYPE M-E

LC0

V

VLC1

COM

data

VLC2

P-ch

N-ch

N-ch

P-ch

N-ch

P-ch

N-ch

N-chP-ch

P-chN-ch

Input instruction

OUT

Data

Output

disable

Pull-up resistor that operates only when an input

Note

instruction is executed. (The current flows from

V

P.U.R. : Pull-Up Resistor

N-ch

(+13-V

withstand

Note

Voltage

controller

voltage)

(+13-V

withstand

voltage)

VDD

P-ch

P.U.R.

DD to a pin when the pin is at low level.)

IN/OUT

11

Page 12

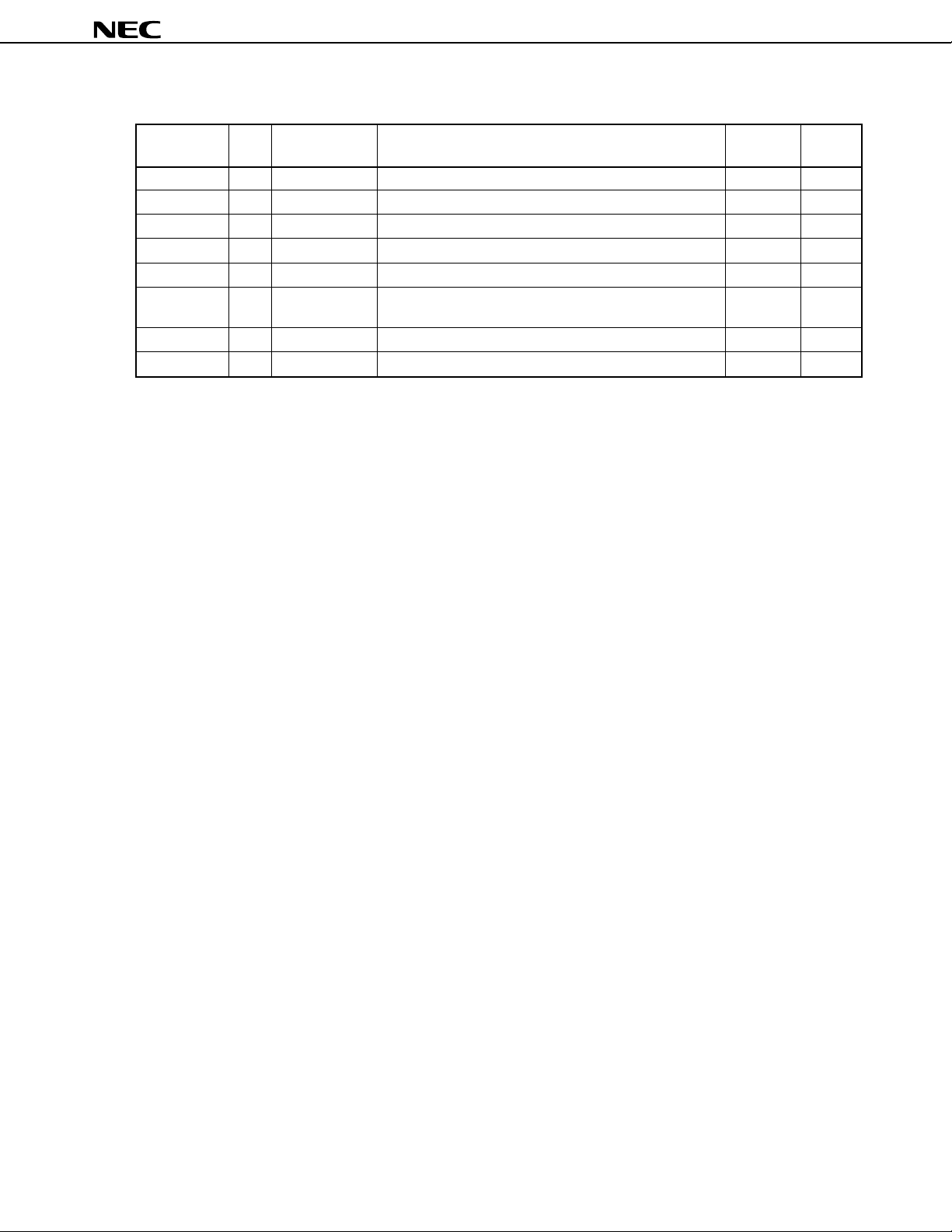

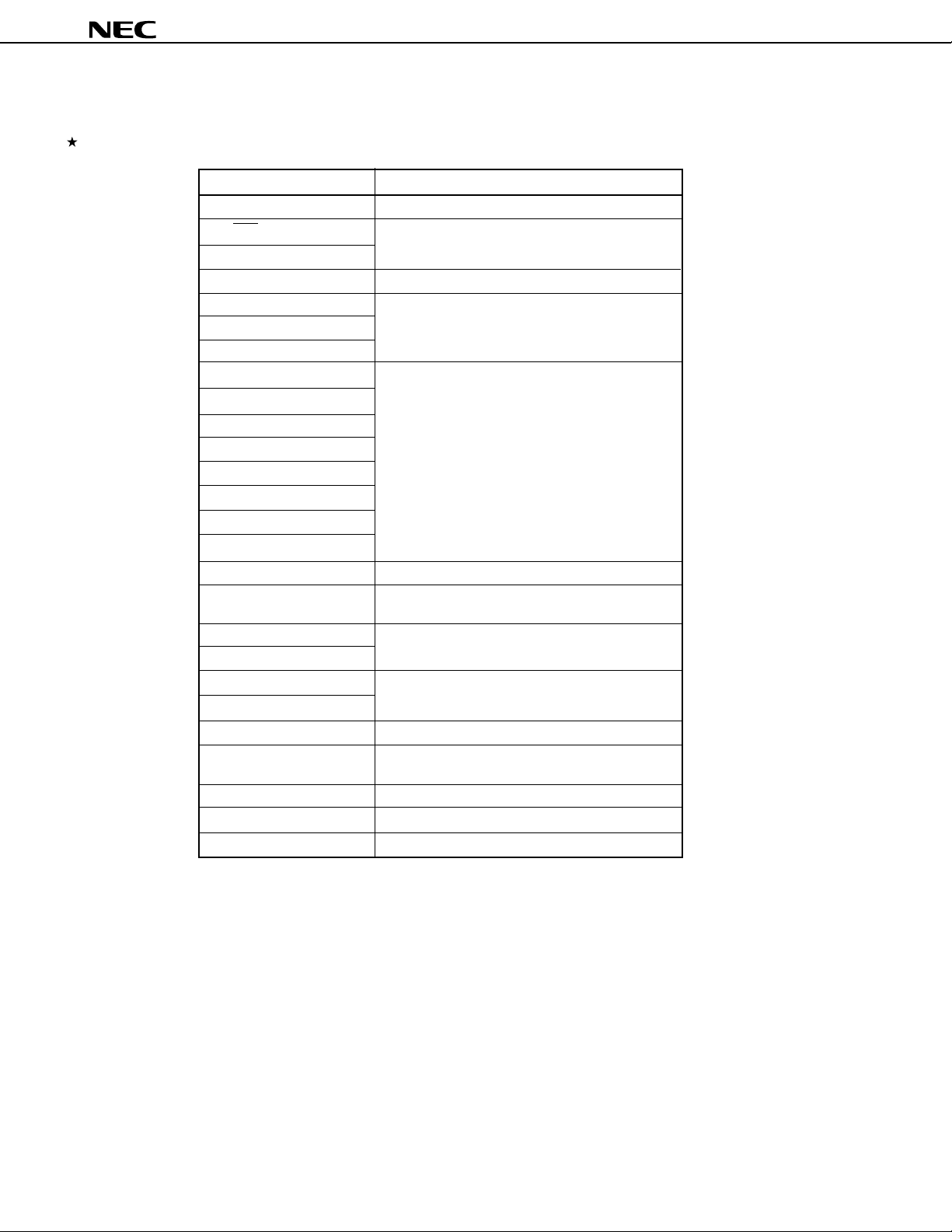

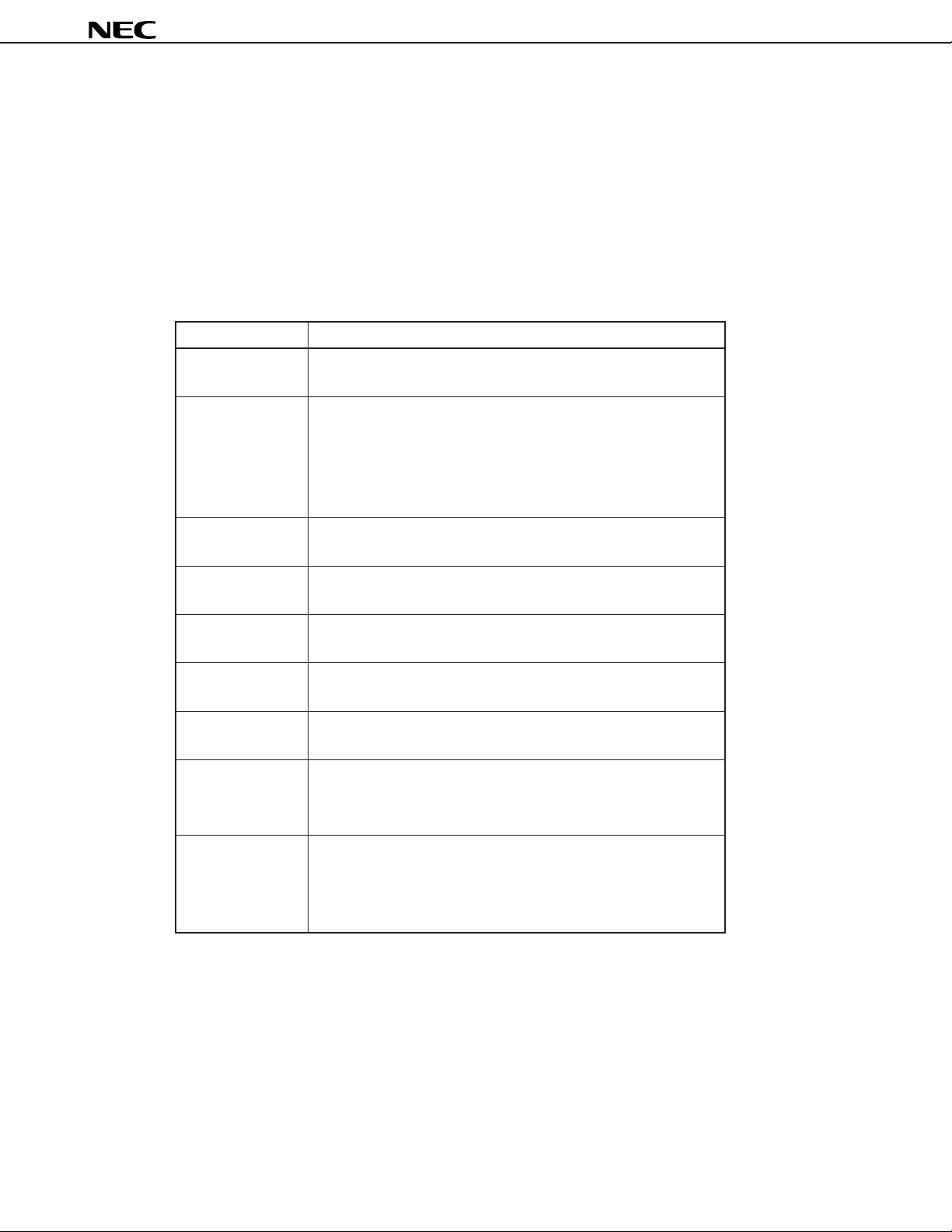

3.4 Recommended Connection of Unused Pins

Table 3-1. List of Unused Pin Connection

Pin Recommended connection

P00/INT4 Connect to Vss or VDD

P01/SCK Individually connect to Vss or VDD through a resistor.

P02/SO/SB0

P03/SI/SB1 Connect to Vss

P10/INT0 and P11/INT1 Connect to Vss or V

P12/TI1/TI2/INT2

P13/TI0

P20/PTO0 Input status : Individually connect to Vss or V

P21/PTO1 through a resistor

P22/PTO2/PCL Output status : Leave open

P23/BUZ

P30/LCDCL/MD0

P31/SYNC/MD1

P32/MD2

P33/MD3

P50/D4 to P53/D7 Connect to Vss

P60/KR0/D0 to P63/KR3/D3 Input status :

Output status : Leave open

S0 to S15 Leave open

COM0 to COM3

S16/P93 to S19/P90 Input status :

S20/P83 to S23/P80 Output status : Leave open

V

LC0 to VLC2 Connect to Vss

BIAS Connect to Vss only when neither of V

VLC2 is used. In other cases, leave open.

Note

XT1

Note

XT2

V

PP Always connect to VDD directly

Connect to Vss or VDD

Leave open

DD

DD

Individually connect to Vss or VDD through a resistor

Individually connect to Vss or VDD through a resistor

LC0, VLC1 and

µ

PD75P3116

12

Note In case the subsystem clock is not used, set SOS.0 = 1 (on-chip feedback

resistor not used).

Page 13

µ

PD75P3116

4. Mk I AND Mk II MODE SELECTION FUNCTION

Setting a stack bank selection (SBS) register for the µPD75P3116 enables the program memory to be switched between

µ

the Mk I mode and Mk II mode. This function is applicable when using the

753106, or 753108.

When the SBS bit 3 is set to 1 : sets the Mk I mode (supports the Mk I mode for the

When the SBS bit 3 is set to 0 : sets the Mk II mode (supports the Mk II mode for the

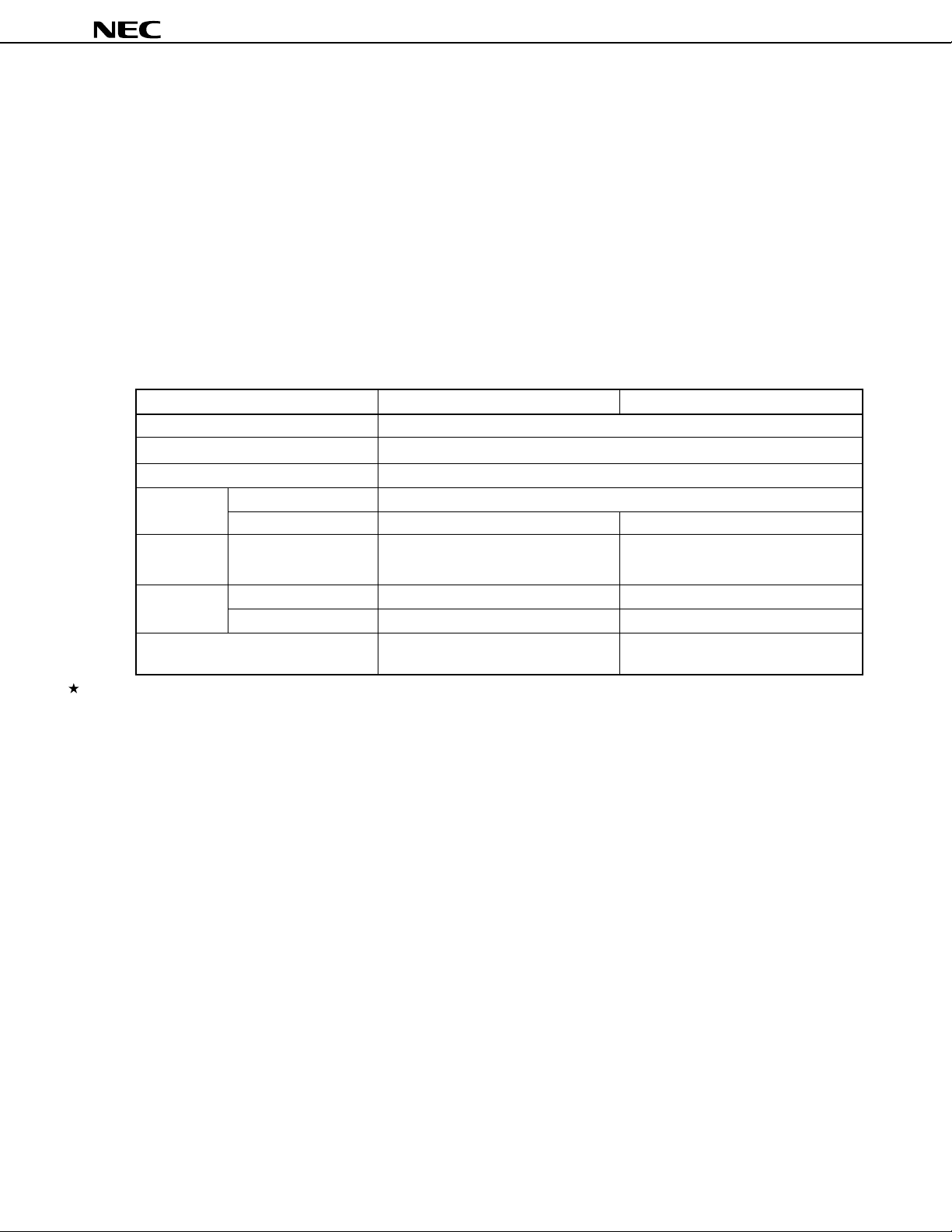

4.1 Differences between Mk I Mode and Mk II Mode Table 4-1 lists differences between the Mk I mode and the Mk II mode for the

Table 4-1. Differences between Mk I Mode and Mk II Mode

Item Mk I mode Mk II mode

Program counter PC

Program memory (bytes) 16384

Data memory (bits) 512 x 4

Stack Stack bank Selectable via memory banks 0, 1

No. of stack bytes 2 bytes 3 bytes

Instruction BRA !addr1 instruction Not available Available

CALLA !addr1 instruction

Instruction CALL !addr instruction 3 machine cycles 4 machine cycles

execution time CALLF !faddr instruction 2 machine cycles 3 machine cycles

Supported mask ROMs When set to Mk I mode: When set to Mk II mode:

13-0

µ

PD753104, 753106, and 753108

PD75P3116 to evaluate the µPD753104,

µ

PD753104, 753106, and 753108)

µ

PD753104, 753106, and 753108)

µ

PD75P3116.

µ

PD753104, 753106, and 753108

Caution The Mk II mode supports a program area exceeding 16 Kbytes for the 75X and 75XL Series. Therefore,

this mode is effective for enhancing software compatibility with products that have a program area of

more than 16 Kbytes.

With regard to the number of stack bytes during execution of subroutine call instructions, the usable

area increases by 1 byte per stack compared to the Mk I mode when the Mk II mode is selected.

However, when the CALL !addr and CALLF !faddr instructions are used, the machine cycle becomes

longer by 1 machine cycle. Therefore, if more emphasis is placed on RAM use efficiency and

processing performance than on software compatibility, the Mk I mode should be used.

13

Page 14

µ

PD75P3116

4.2 Setting of Stack Bank Selection (SBS) Register

Use the stack bank selection register to switch between the Mk I mode and Mk II mode. Figure 4-1 shows the format of

the stack bank selection register.

The stack bank selection register is set using a 4-bit memory manipulation instruction. When using the Mk I mode, be

Note

sure to initialize the stack bank selection register to 100XB

Note

be sure to initialize it to 000XB

.

at the beginning of the program. When using the Mk II mode,

Note Set the desired value for X.

Figure 4-1. Format of Stack Bank Selection Register

Address 3 2 1 0

SBS3 SBS2 SBS1 SBS0F84H

Symbol

SBS

Stack area specification

0

0

Memory bank 0

0

1

Memory bank 1

1

0

Setting prohibited

1

1

0 Be sure to enter “0” for bit 2.

Mode selection specification

01Mk II mode

Mk I mode

Caution SBS3 is set to “1” after RESET input, and consequently the CPU operates in the Mk I mode. When using

instructions for the Mk II mode, set SBS3 to “0” and set the Mk II mode before using the instructions.

14

Page 15

µ

PD75P3116

5. DIFFERENCES BETWEEN µPD75P3116 AND µPD753104, 753106, 753108

The µPD75P3116 replaces the internal mask ROM in the µPD753104, 753106, and 753108 with a one-time PROM and

features expanded ROM capacity. The µPD75P3116’s Mk I mode supports the Mk I mode in the µPD753104, 753106,

and 753108 and the µPD75P3116’s Mk II mode supports the Mk II mode in the µPD753104, 753106, and 753108.

µ

Table 5-1 lists differences among the

differences among these products before using them with PROMs for debugging or prototype testing of application

systems or, later, when using them with a mask ROM for full-scale production.

For details on the CPU functions and internal hardware, refer to the User’s Manual.

Table 5-1. Differences between

PD75P3116 and the µPD753104, 753106, and 753108. Be sure to check the

µ

PD75P3116 and µPD753104, 753106, and 753108

Item

Program counter 12 bits 13 bits 14 bits

Program memory (bytes) Mask ROM Mask ROM Mask ROM One-time PROM

Data memory (x 4 bits) 512

Mask options Pull-up resistor for Available Not available

PORT5 (On chip/not on chip can be specified.) (Not on chip)

Split resistor for

LCD driving power supply

Wait time after Available Not available

RESET (Selectable between 217/fX and 215/fX) (fixed to 215/fX)

Feedback resistor Available Not available

of subsystem clock (Use/not use can be selected.) (Enable)

Pin configuration Pin Nos. 5 to 8 P30 to P33

Pin Nos. 10 to 13 P50 to P53 P50/D4 to P53/D7

Pin Nos. 14 to 17 P60/KR0 to P63/KR3

Pin No. 21 IC VPP

Other Noise resistance and noise radiation may differ due to the different circuit sizes and mask

µ

PD753104

4096 6144 8192 16384

layouts.

µ

PD753106

µ

PD753108

µ

P30/MD0 to P33/MD3

P60/KR0/D0 to P63/KR3/D3

PD75P3116

Note 217/fX : 21.8 ms at 6.0-MHz operation, 31.3 ms at 4.19-MHz operation

215/fX : 5.46 ms at 6.0-MHz operation, 7.81 ms at 4.19-MHz operation

Note

Caution Noise resistance and noise radiation are different in PROM and mask ROMs. When changing from

PROM versions to mask ROM versions when switching from prototype development to full production,

be sure to fully evaluate the mask ROM version’s CS (not ES).

15

Page 16

6. MEMORY CONFIGURATION

765 0

MBE

RBE

0000H

0002H

0004H

0006H

0008H

000AH

000CH

MBE

MBE

MBE

MBE

MBE

MBE

Internal reset start address (upper 6 bits)

Internal reset start address (lower 8 bits)

RBE

INTBT/INT4 start address (upper 6 bits)

INTBT/INT4 start address (lower 8 bits)

RBE

INT0 start address (upper 6 bits)

INT0 start address (lower 8 bits)

RBE

INT1 start address (upper 6 bits)

INT1 start address (lower 8 bits)

RBE

INTCSI start address (upper 6 bits)

INTCSI start address (lower 8 bits)

RBE

INTT0 start address (upper 6 bits)

INTT0 start address (lower 8 bits)

RBE

INTT1/INTT2 start address (upper 6 bits)

INTT1/INTT2 start address (lower 8 bits)

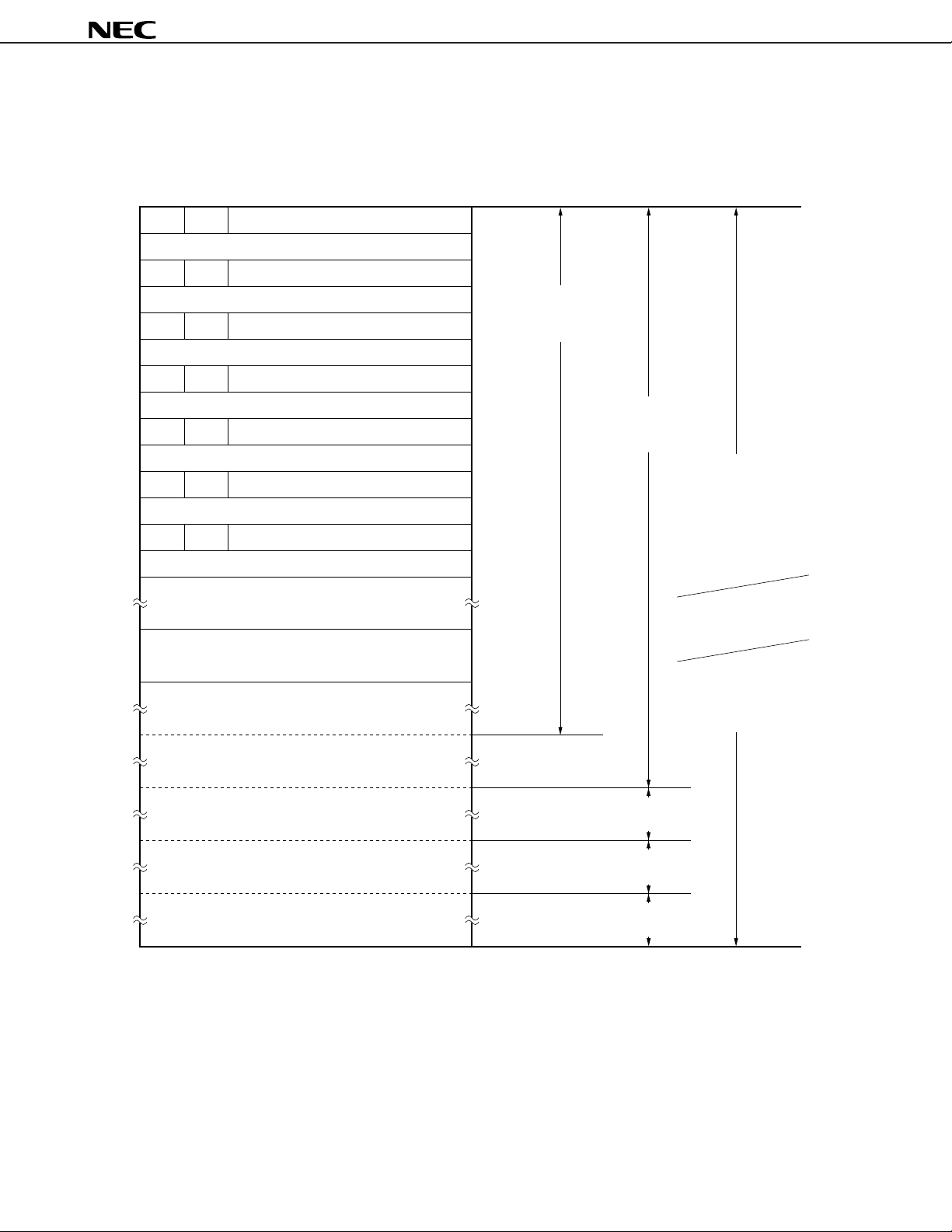

Figure 6-1. Program Memory Map

CALLF

!faddr instruction

entry address

BRCB

!caddr instruction

branch address

µ

PD75P3116

Branch addresses for

the following instructions

• BR !addr

• CALL !addr

• BRA !addr1

• CALLA !addr1

• BR BCDE

• BR BCXA

Note

Note

Branch/call

0020H

007FH

0080H

07FFH

0800H

0FFFH

1000H

1FFFH

2000H

2FFFH

3000H

3FFFH

Reference table for GETI instruction

BRCB

!caddr instruction

branch address

BRCB

!caddr instruction

branch address

BRCB

!caddr instruction

branch address

address

by GETI

BR $addr instruction

relative branch address

(–15 to –1,

+2 to +16)

Note Can be used only in the Mk II mode

Remark For instructions other than those noted above, the BR PCDE and BR PCXA instructions can be used to branch

to addresses with changes in the PC’s lower 8 bits only.

16

Page 17

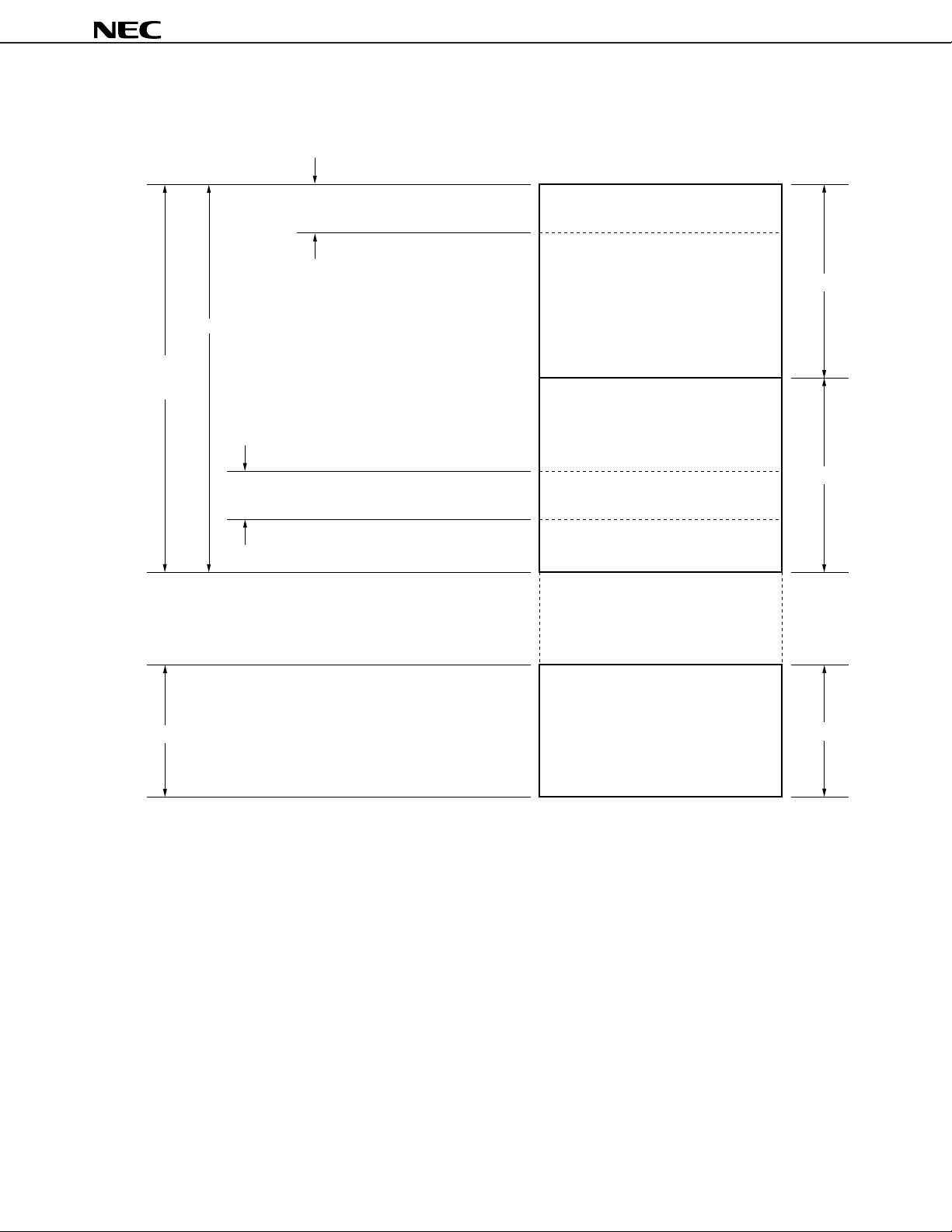

Figure 6-2. Data Memory Map

µ

PD75P3116

Data area

static RAM

(512 x 4)

Stack area

Note

Display data memory

General-purpose register area

000H

01FH

020H

0FFH

100H

1DFH

1E0H

1F7H

1F8H

1FFH

Data memory

(32 x 4)

256 x 4

(224 x 4)

256 x 4

(224 x 4)

(24 x 4)

(8 x 4)

Not incorporated

Memory bank

0

1

F80H

Peripheral hardware area

FFFH

Note Memory bank 0 or 1 can be selected as the stack area.

128 x 4

15

17

Page 18

µ

PD75P3116

7. INSTRUCTION SET

(1) Representation and coding formats for operands

In the instruction’s operand area, use the following coding format to describe operands corresponding to the instruction’s

operand representations (for further description, refer to the RA75X Assembler Package User’s Manual Language

(EEU-1363)). When there are several codes, select and use just one. Codes that consist of upper-case letters and + or

– symbols are key words that should be entered as they are.

For immediate data, enter an appropriate numerical value or label.

Enter register flag symbols as label descriptors instead of mem, fmem, pmem, bit, etc. (for further description, refer to the

User’s Manual). The number of labels that can be entered for fmem and pmem are restricted.

Representation Coding format

reg X, A, B, C, D, E, H, L

reg1 X, B, C, D, E, H, L

rp XA, BC, DE, HL

rp1 BC, DE, HL

rp2 BC, DE

rp’ XA, BC, DE, HL, XA’, BC’, DE’, HL’

rp’1 BC, DE, HL, XA’, BC’, DE’, HL’

rpa HL, HL+, HL–, DE, DL

rpa1 DE, DL

n4 4-bit immediate data or label

n8 8-bit immediate data or label

mem 8-bit immediate data or label

bit 2-bit immediate data or label

fmem FB0H to FBFH, FF0H to FFFH immediate data or label

pmem FC0H to FFFH immediate data or label

addr 0000H to 3FFFH immediate data or label

addr1 0000H to 3FFFH immediate data or label (Mk II mode only)

caddr 12-bit immediate data or label

faddr 11-bit immediate data or label

taddr 20H to 7FH immediate data (however, bit0 = 0) or label

PORTn PORT0 to PORT3, PORT5, PORT6, PORT8, PORT9

IEXXX IEBT, IECSI, IET0 to IET2, IE0 to IE2, IE4, IEW

RBn RB0 to RB3

MBn MB0, MB1, MB15

Note

18

Note When processing 8-bit data, only even-numbered addresses can be specified.

Page 19

(2) Operation legend

A : A register; 4-bit accumulator

B : B register

C : C register

D : D register

E : E register

H : H register

L : L register

X : X register

XA : Register pair (XA); 8-bit accumulator

BC : Register pair (BC)

DE : Register pair (DE)

HL : Register pair (HL)

XA’ : Expansion register pair (XA’)

BC’ : Expansion register pair (BC’)

DE’ : Expansion register pair (DE’)

HL’ : Expansion register pair (HL’)

PC : Program counter

SP : Stack pointer

CY : Carry flag; bit accumulator

PSW : Program status word

MBE : Memory bank enable flag

RBE : Register bank enable flag

PORTn : Port n (n = 0 to 3, 5, 6, 8, 9)

IME : Interrupt master enable flag

IPS : Interrupt priority selection register

IEXXX : Interrupt enable flag

RBS : Register bank selection register

MBS : Memory bank selection register

PCC : Processor clock control register

. : Delimiter for address and bit

(XX) : Addressed data with xx

XXH : Hexadecimal data

µ

PD75P3116

19

Page 20

(3) Description of symbols used in addressing area

MB = MBE • MBS

*1

MB = 0

*2

MBE = 0 :

*3

MBE = 1 :

MB = 15, fmem = FB0H to FBFH, FF0H to FFFH

*4

MB = 15, pmem = FC0H to FFFH

*5

addr = 0000H to 3FFFH

*6

addr, addr1 =*7(Current PC) –15 to (Current PC) –1

caddr =0000H to 0FFFH (PC

*8

MBS = 0, 1, 15

MB = 0 (000H to 07FH)

MB = 15 (F80H to FFFH)

MB = MBS

MBS = 0, 1, 15

(Current PC) +2 to (Current PC) +16

13,12

= 00B) or

1000H to 1FFFH (PC

2000H to 2FFFH (PC

3000H to 3FFFH (PC

13,12

13,12

13,12

= 01B) or

= 10B) or

= 11B)

µ

PD75P3116

Data memory

addressing

Program memory

addressing

faddr = 0000H to 07FFH

*9

taddr = 0020H to 007FH

*10

addr1 = 0000H to 3FFFH (Mk II mode only)

*11

Remarks 1. MB indicates access-enabled memory banks.

2. In area *2, MB = 0 for both MBE and MBS.

3. In areas *4 and *5, MB = 15 for both MBE and MBS.

4. Areas *6 to *11 indicate corresponding address-enabled areas.

(4) Description of machine cycles

S indicates the number of machine cycles required for skipping of skip-specified instructions. The value of S varies as

shown below.

• No skip .....................................................................S = 0

• Skipped instruction is 1-byte or 2-byte instruction....S = 1

Note

• Skipped instruction is 3-byte instruction

..............S = 2

Note 3-byte instructions: BR !addr, BRA !addr1, CALL !addr, and CALLA !addr1

Caution The GETI instruction is skipped for one machine cycle.

One machine cycle equals one cycle (= t

20

CY) of the CPU clock Φ. Use the PCC setting to select among four cycle times.

Page 21

µ

PD75P3116

Instruction Mnemonic Operand

group

Transfer MOV A, #n4 1 1 A<-n4 String-effect A

reg1, #n4 2 2 reg1<-n4

XA, #n8 2 2 XA<-n8 String-effect A

HL, #n8 2 2 HL<-n8 String-effect B

rp2, #n8 2 2 rp2<-n8

A, @HL 1 1 A<-(HL) *1

A, @HL+ 1 2+S A<-(HL), then L<-L+1 *1 L=0

A, @HL– 1 2+S A<-(HL), then L<-L–1 *1 L=FH

A, @rpa1 1 1 A<-(rpa1) *2

XA, @HL 2 2 XA<-(HL) *1

@HL, A 1 1 (HL)<-A *1

@HL, XA 2 2 (HL)<-XA *1

A, mem 2 2 A<-(mem) *3

XA, mem 2 2 XA<-(mem) *3

mem, A 2 2 (mem)<-A *3

mem, XA 2 2 (mem)<-XA *3

A, reg 2 2 A<-reg

XA, rp’ 2 2 XA<-rp’

reg1, A 2 2 reg1<-A

rp’1, XA 2 2 rp’1<-XA

XCH A, @HL 1 1 A<->(HL) *1

A, @HL+ 1 2+S A<->(HL), then L<-L+1 *1 L=0

A, @HL– 1 2+S A<->(HL), then L<-L–1 *1 L=FH

A, @rpa1 1 1 A<->(rpa1) *2

XA, @HL 2 2 XA<->(HL) *1

A, mem 2 2 A<->(mem) *3

XA, mem 2 2 XA<->(mem) *3

A, reg1 1 1 A<->reg1

XA, rp’ 2 2 XA<->rp’

Table MOVT XA, @PCDE 1 3 XA<-(PC13-8+DE)ROM

reference XA, @PCXA 1 3 XA<-(PC13-8+XA)ROM

XA, @BCDE

XA, @BCXA

No. of Machine

bytes cycle area

Note

1 3 XA<-(BCDE)ROM *6

Note

1 3 XA<-(BCXA)ROM *6

Operation

Addressing

Skip

condition

Note Only the lower 3 bits in the B register are valid.

21

Page 22

µ

PD75P3116

Instruction Mnemonic Operand

group

Bit transfer MOV1 CY, fmem.bit 2 2 CY<-(fmem.bit) *4

CY, pmem.@L 2 2 CY<-(pmem7-2+L3-2.bit(L1-0)) *5

CY, @H+mem.bit 2 2 CY<-(H+mem3-0.bit) *1

fmem.bit, CY 2 2 (fmem.bit)<-CY *4

pmem.@L, CY 2 2 (pmem7-2+L3-2.bit(L1-0))<-CY *5

@H+mem.bit, CY 2 2 (H+mem3-0.bit)<-CY *1

Arithmetic ADDS A, #n4 1 1+S A<-A+n4 carry

XA, #n8 2 2+S XA<-XA+n8 carry

A, @HL 1 1+S A<-A+(HL) *1 carry

XA, rp’ 2 2+S XA<-XA+rp’ carry

rp’1, XA 2 2+S rp’1<-rp’1+XA carry

ADDC A, @HL 1 1 A, CY<-A+(HL)+CY *1

XA, rp’ 2 2 XA, CY<-XA+rp’+CY

rp’1, XA 2 2 rp’1, CY<-rp’1+XA+CY

SUBS A, @HL 1 1+S A<-A–(HL) *1 borrow

XA, rp’ 2 2+S XA<-XA–rp’ borrow

rp’1, XA 2 2+S rp’1<-rp’1–XA borrow

SUBC A, @HL 1 1 A, CY<-A–(HL)–CY *1

XA, rp’ 2 2 XA, CY<-XA–rp’–CY

rp’1, XA 2 2 rp’1, CY<-rp’1–XA–CY

AND A, #n4 2 2 A<-A ^ n4

A, @HL 1 1 A<-A ^ (HL) *1

XA, rp’ 2 2 XA<-XA ^ rp’

rp’1, XA 2 2 rp’1<-rp’1 ^ XA

OR A, #n4 2 2 A<-A v n4

A, @HL 1 1 A<-A v (HL) *1

XA, rp’ 2 2 XA<-XA v rp’

rp’1, XA 2 2 rp’1<-rp’1 v XA

XOR A, #n4 2 2 A<-A v n4

A, @HL 1 1 A<-A v (HL) *1

XA, rp’ 2 2 XA<-XA v rp’

rp’1, XA 2 2 rp’1<-rp’1 v XA

Accumulator RORC A 1 1 CY<-A0, A3<-CY, An-1<-An

manipulation NOT A 2 2 A<-A

Increment/ INCS reg 1 1+S reg<-reg+1 reg=0

decrement rp1 1 1+S rp1<-rp1+1 rp1=00H

@HL 2 2+S (HL)<-(HL)+1 *1 (HL)=0

mem 2 2+S (mem)<-(mem)+1 *3 (mem)=0

DECS reg 1 1+S reg<-reg–1 reg=FH

rp’ 2 2+S rp’<-rp’–1 rp’=FFH

No. of Machine

bytes cycle area

Operation

Addressing

Skip

condition

22

Page 23

µ

PD75P3116

Instruction Mnemonic Operand

group

Comparison SKE reg, #n4 2 2+S Skip if reg=n4 reg=n4

@HL, #n4 2 2+S Skip if (HL)=n4 *1 (HL)=n4

A, @HL 1 1+S Skip if A=(HL) *1 A=(HL)

XA, @HL 2 2+S Skip if XA=(HL) *1 XA=(HL)

A, reg 2 2+S Skip if A=reg A=reg

XA, rp’ 2 2+S Skip if XA=rp’ XA=rp’

Carry flag SET1 CY 1 1 CY<-1

manipulation CLR1 CY 1 1 CY<-0

SKT CY 1 1+S Skip if CY=1 CY=1

NOT1 CY 1 1 CY<-CY

Memory bit SET1 mem.bit 2 2 (mem.bit)<-1 *3

manipulation fmem.bit 2 2 (fmem.bit)<-1 *4

pmem.@L 2 2 (pmem7-2+L3-2.bit(L1-0))<-1 *5

@H+mem.bit 2 2 (H+mem3-0.bit)<-1 *1

CLR1 mem.bit 2 2 (mem.bit)<-0 *3

fmem.bit 2 2 (fmem.bit)<-0 *4

pmem.@L 2 2 (pmem7-2+L3-2.bit(L1-0))<-0 *5

@H+mem.bit 2 2 (H+mem3-0.bit)<-0 *1

SKT mem.bit 2 2+S Skip if(mem.bit)=1 *3 (mem.bit)=1

fmem.bit 2 2+S Skip if(fmem.bit)=1 *4 (fmem.bit)=1

pmem.@L 2 2+S Skip if(pmem7-2+L3-2.bit(L1-0))=1 *5 (pmem.@L)=1

@H+mem.bit 2 2+S Skip if(H+mem3-0.bit)=1 *1

SKF mem.bit 2 2+S Skip if(mem.bit)=0 *3 (mem.bit)=0

fmem.bit 2 2+S Skip if(fmem.bit)=0 *4 (fmem.bit)=0

pmem.@L 2 2+S Skip if(pmem7-2+L3-2.bit(L1-0))=0 *5 (pmem.@L)=0

@H+mem.bit 2 2+S Skip if(H+mem3-0.bit)=0 *1

SKTCLR fmem.bit 2 2+S Skip if(fmem.bit)=1 and clear *4 (fmem.bit)=1

pmem.@L 2 2+S

@H+mem.bit 2 2+S Skip if(H+mem3-0.bit)=1 and clear *1

AND1 CY, fmem.bit 2 2 CY<-CY ^ (fmem.bit) *4

CY, pmem.@L 2 2 CY<-CY ^ (pmem7-2+L3-2.bit(L1-0)) *5

CY, @H+mem.bit 2 2 CY<-CY ^ (H+mem3-0.bit) *1

OR1 CY, fmem.bit 2 2 CY<-CY v (fmem.bit) *4

CY, pmem.@L 2 2 CY<-CY v (pmem7-2+L3-2.bit(L1-0)) *5

CY, @H+mem.bit 2 2 CY<-CY v (H+mem3-0.bit) *1

XOR1 CY, fmem.bit 2 2 CY<-CY v (fmem.bit) *4

CY, pmem.@L 2 2 CY<- CY v (pmem7-2+L3-2.bit(L1-0)) *5

CY, @H+mem.bit 2 2 CY<-CY v (H+mem3-0.bit) *1

No. of Machine

bytes cycle area

Skip if(pmem

Operation

7-2+L3-2

.bit(L

1-0

))=1 and clear

Addressing

*5 (pmem.@L)=1

condition

(@H+mem.bit)=1

(@H+mem.bit)=0

(@H+mem.bit)=1

Skip

23

Page 24

µ

PD75P3116

Instruction Mnemonic Operand

group

Branch BR

Note 1

BRA

BRCB !caddr 2 2 PC13-0<-PC13, 12+caddr11-0 *8

addr — — PC13-0<-addr *6

addr1 — — PC13-0<-addr1 *11

!addr 3 3 PC13-0<-addr *6

$addr 1 2 PC13-0<-addr *7

$addr1 1 2 PC13-0<-addr1

PCDE 2 3 PC13-0<-PC13-8+DE

PCXA 2 3 PC13-0<-PC13-8+XA

BCDE 2 3 PC13-0<-BCDE

BCXA 2 3 PC13-0<-BCXA

Note 1

!addr1 3 3 PC13-0<-addr1 *11

No. of Machine

bytes cycle area

Use the assembler to select the

most appropriate instruction

among the following.

• BR !addr

• BRCB !caddr

• BR $addr

Use the assembler to select

the most appropriate instruction

among the following.

• BRA !addr1

• BR !addr

• BRCB !caddr

• BR $addr1

Operation

Note 2

Note 2

Addressing

*6

*6

Skip

condition

Notes 1. The portion in a double box can be supported only in the Mk II mode. The others can be supported only in the

MK I mode.

2. The B register is valid only for the lower two bits.

24

Page 25

µ

PD75P3116

Instruction Mnemonic Operand

group

Subroutine CALLA

Note

!addr1 3 3

No. of Machine

Operation

bytes cycle area

(SP–6)(SP–3)(SP–4)<-PC11-0

stack control (SP–5)<-0, 0, PC13, 12

(SP–2)

<-X, X, MBE, RBE

PC13-0<-addr1, SP<-SP–6

Note

CALL

!addr 3 3 (SP–4)(SP–1)(SP–2)<-PC11-0 *6

(SP–3)<-MBE, RBE, PC13, 12

PC13-0<-addr, SP<-SP–4

4 (SP–6)(SP–3)(SP–4)<-PC11-0

(SP–5)<-0, 0, PC13, 12

(SP–2)<-X, X, MBE, RBE

PC13-0<-addr, SP<-SP–6

Note

CALLF

!faddr 2 2 (SP–4)(SP–1)(SP–2)<-PC11-0 *9

(SP–3)<-MBE, RBE, PC13, 12

PC13-0<-000+faddr, SP<-SP–4

3

(SP–6)(SP–3)(SP–4)<-PC11-0

(SP–5)<-0, 0, PC13, 12

(SP–2)<-X, X, MBE, RBE

PC13-0<-000+faddr, SP<-SP–6

Note

RET

1 3 MBE, RBE, PC13, 12<-(SP+1)

PC11-0<-(SP)(SP+3)(SP+2)

SP<-SP+4

X, X, MBE, RBE<-(SP+4)

PC11-0<-(SP)(SP+3)(SP+2)

0, 0, PC13, 12<-(SP+1)

SP<-SP+6

Note

RETS

1 3+S MBE, RBE, PC13, 12<-(SP+1) Unconditional

PC11-0<-(SP)(SP+3)(SP+2)

SP<-SP+4

then skip unconditionally

X, X, MBE, RBE<-(SP+4)

PC11-0<-(SP)(SP+3)(SP+2)

0, 0, PC13, 12<-(SP+1)

SP<-SP+6

then skip unconditionally

Note

RETI

1 3 MBE, RBE, PC13, 12<-(SP+1)

PC11-0<-(SP)(SP+3)(SP+2)

PSW<-(SP+4)(SP+5)

SP<-SP+6

0, 0, PC13, 12<-(SP+1)

PC11-0<-(SP)(SP+3)(SP+2)

PSW<-(SP+4)(SP+5), SP<-SP+6

Addressing

*11

Skip

condition

Note

The portion in a double box can be supported only in the Mk II mode. Other portions can be supported only in the Mk I mode.

25

Page 26

µ

PD75P3116

Instruction Mnemonic Operand

group

Subroutine PUSH rp 1 1 (SP–1)(SP–2)<-rp, SP<-SP–2

stack control BS 2 2

POP rp 1 1 rp<-(SP+1)(SP), SP<-SP+2

BS 2 2 MBS<-(SP+1), RBS<-(SP), SP<-SP+2

Interrupt EI 2 2 IME(IPS.3)<-1

control IEXXX 2 2 IEXXX<-1

DI 2 2 IME(IPS.3)<-0

IEXXX 2 2 IEXXX<-0

I/O IN

CPU control HALT 2 2 Set HALT Mode(PCC.2<-1)

Special SEL RBn 2 2 RBS<-n (n=0 to 3)

Note 1

OUT

STOP 2 2 Set STOP Mode(PCC.3<-1)

NOP 1 1 No Operation

GETI

A, PORTn 2 2 A<-PORTn

XA, PORTn 2 2 XA<-PORTn+1, PORTn(n=8)

Note 1

PORTn, A 2 2 PORTn<-A

PORTn, XA 2 2 PORTn+1, PORTn<-XA(n=8)

MBn 2 2 MBS<-n (n=0, 1, 15)

Note 2, 3

taddr 1 3 • When using TBR instruction *10

No. of Machine

bytes cycle area

(SP–1)<-MBS, (SP–2)<-RBS, SP<-SP–2

PC13-0<-(taddr)5-0+(taddr+1)

- - - - - - - - - - - - - - - - - - - - - - - - - - -

• When using TCALL instruction

(SP–4)(SP–1)(SP–2)<-PC11-0

(SP–3)<-MBE, RBE, PC13, 12

PC13-0<-(taddr)5-0+(taddr+1)

SP<-SP–4

- - - - - - - - - - - - - - - - - - - - - - - - - - -

• When using instruction other than Determined by

TBR or TCALL referenced

Execute (taddr)(taddr+1) instructions instruction

1 3 • When using TBR instruction *10

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

PC13-0<-(taddr)5-0+(taddr+1)

4 • When using TCALL instruction

(SP–6)(SP–3)(SP–4)<-PC11-0

(SP–5)<-0, 0, PC13, 12

(SP–2)<-X, X, MBE, RBE

PC13-0<-(taddr)5-0+(taddr+1)

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

3 • When using instruction other than Determined by

TBR or TCALL referenced

Execute (taddr)(taddr+1) instructions instruction

Operation

(n=0 to 3, 5, 6, 8, 9)

(n=2 to 3, 5, 6, 8, 9)

SP<-SP–6

Addressing

- - - - - - - - - - - -

- - - - - - - - - - - -

- - - - - - - - - - - -

- - - - - - - - - - - -

Skip

condition

Notes 1. Setting MBE=0 or MBE=1, MBS=15 is required during the execution of IN or OUT instruction.

2. TBR and TCALL instructions are assembler pseudo-instructions for the GETI instruction table definitions.

3. The portion in a double box can be supported only in the Mk II mode. Other portions can be supported only

in the Mk I mode.

26

Page 27

µ

PD75P3116

8. ONE-TIME PROM (PROGRAM MEMORY) WRITE AND VERIFY

The program memory contained in the µPD75P3116 is a 16384 x 8-bit one-time PROM that can be electrically written one

time only. The pins listed in the table below are used for this PROM’s write/verify operations. Clock input from the X1

pin is used instead of address input as a method for updating addresses.

Pin Function

VPP Pin where program voltage is applied during program memory

X1, X2 Clock input pins for address updating during program memory

MD0 to MD3 Operation mode selection pin for program memory write/verify

D0/P60 to D3/P63 8-bit data I/O pins for program memory write/verify

(lower 4 bits)

D4/P50 to D7/P53

(upper 4 bits)

VDD Pin where power supply voltage is applied. Applies 1.8 to 5.5

Caution Pins not used for program memory write/verify should be connected to Vss.

write/verify (usually VDD potential)

write/verify. Input the X1 pin’s inverted signal to the X2 pin.

V in normal operation mode and +6 V for program memory

write/verify.

8.1 Operation Modes for Program Memory Write/Verify

When +6 V is applied to the V

DD pin and +12.5 V to the VPP pin, the

µ

PD75P3116 enters the program memory write/verify

mode. The following operation modes can be specified by setting pins MD0 to MD3 as shown below.

Operation mode specification Operation mode

VPP VDD MD0 MD1 MD2 MD3

+12.5 V +6 V H L H L Zero-clear program memory address

L H H H Write mode

L L H H Verify mode

H X H H Program inhibit mode

X: L or H

27

Page 28

8.2 Program Memory Write Procedure

Program memory can be written at high speed using the following procedure.

(1) Pull down unused pins to Vss through resistors. Set the X1 pin low.

(2) Supply 5 V to the V

DD and VPP pins.

(3) Wait 10 µs.

(4) Select the program memory address zero-clear mode.

(5) Supply 6 V to V

DD and 12.5 V to VPP pins.

(6) Write data in the 1-ms write mode.

(7) Select the verify mode. If the data is written, go to (8) and if not, repeat (6) and (7).

(8) Additional write. (X: number of write operations from (6) and (7)) x 1 ms

(9) Apply four pulses to the X1 pin to increment the program memory address by one.

(10) Repeat (6) to (9) until the end address is reached.

(11) Select the program memory address zero-clear mode.

(12) Return the V

DD- and VPP-pin voltages to 5 V.

(13) Turn off the power.

The following figure shows steps (2) to (9).

µ

PD75P3116

V

V

PP

V

DD

D0/P60 to D3/P63

D4/P50 to D7/P53

MD1/P31

MD2/P32

V

VDD + 1

V

X1

MD0/P30

PP

DD

DD

X repetitions

Write Verify

Data input

Data

output

Additional

write

Data input

Address

increment

28

MD3/P33

Page 29

µ

PD75P3116

8.3 Program Memory Read Procedure

The µPD75P3116 can read program memory contents using the following procedure.

(1) Pull down unused pins to V

SS through resistors. Set the X1 pin low.

(2) Supply 5 V to the VDD and VPP pins.

(3) Wait 10 µs.

(4) Select the program memory address zero-clear mode.

(5) Supply 6 V to the V

DD and 12.5 to the VPP pins.

(6) Select the verify mode. Apply four pulses to the X1 pin. Every four clock pulses will output the data stored in one

address.

(7) Select the program memory address zero-clear mode.

(8) Return the V

DD- and VPP-pin voltages to 5V.

(9) Turn off the power.

The following figure shows steps (2) to (7).

V

V

PP

PP

V

DD

VDD + 1

V

DD

D0/P60 to D3/P63

D4/P50 to D7/P53

DD

V

X1

MD0/P30

MD1/P31

MD2/P32

MD3/P33

Data output Data output

“L”

29

Page 30

µ

PD75P3116

8.4 One-time PROM Screening

Due to its structure, the one-time PROM cannot be fully tested before shipment by NEC. Therefore, NEC recommends

that after the required data is written and the PROM is stored under the temperature and time conditions shown below,

the PROM should be verified via a screening.

Storage temperature Storage time

125˚C 24 hours

NEC offers QTOP microcontrollers for which one-time PROM writing, marking, screening, and verification are provided

at additional cost. For more detailed information, contact an NEC sales representative.

30

Page 31

µ

PD75P3116

9. ELECTRICAL SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS (TA = 25˚C)

Parameter Symbol Test Conditions Rating Unit

Power supply voltage V

PROM power supply VPP –0.3 to +13.5 V

voltage

Input voltage VI1 Except port 5 –0.3 to VDD +0.3 V

Output voltage VO –0.3 to VDD +0.3 V

Output current high I

Output current low IOL Per pin 30 mA

Operating ambient TA –40 to +85

temperature

Storage temperature T

DD –0.3 to +7.0 V

VI2 Port 5 (N-ch open drain) –0.3 to +14 V

OH Per pin –10 mA

Total of all pins –30 mA

Total of all pins 220 mA

Note

stg –65 to +150 ˚C

˚C

Note When LCD is driven in normal mode: TA = –10 to +85˚C

Caution If any of the parameters exceeds the absolute maximum ratings, even momentarily, the reliability

of the product may be impaired. The absolute maximum ratings are values that may physically

damage the products. Be sure to use the products within the ratings.

CAPACITANCE (T

Parameter Symbol Test Conditions MIN. TYP. MAX. Unit

Input capacitance CIN f = 1 MHz 15 pF

Output capacitance COUT Unmeasured pins returned to 0 V. 15 pF

I/O capacitance CIO 15 pF

A = 25˚C, VDD = 0 V)

31

Page 32

µ

PD75P3116

MAIN SYSTEM CLOCK OSCILLATOR CHARACTERISTICS (TA = –40 to +85°C, VDD = 1.8 to 5.5 V)

Resonator Recommended constant Parameter Test conditions MIN. TYP. MAX. Unit

Note 2

Ceramic Oscillation 1.0

X1

resonator frequency (fx)

C1

Crystal Oscillation 1.0

X1

resonator frequency (fx)

C1

X2

Note 1

C2

V

DD

X2

C2

DD

V

Oscillation After VDD reaches oscil- 4 ms

Note 1

Note 3

lation voltage range MIN.

stabilization time

Oscillation VDD = 4.5 to 5.5 V 10 ms

stabilization time

Note 3

External X1 input 1.0

clock frequency (fx)

X1

X2

Note 1

X1 input 83.3 500 ns

high-/low-level width

(tXH, tXL)

6.0

6.0

30

6.0

Note 2

Note 2

MHz

MHz

MHz

Notes 1. The oscillation frequency and X1 input frequency indicate characteristics of the oscillator only. For

the instruction execution time, refer to AC Characteristics.

2. When the power supply voltage is 1.8 V ≤ V

DD < 2.7 V and the oscillation frequency is 4.19 MHz < fx

≤ 6.0 MHz, setting the processor clock control register (PCC) to 0011 results in 1 machine cycle being

less than the required 0.95 µs. Therefore, set PCC to a value other than 0011.

3. The oscillation stabilization time is necessary for oscillation to stabilize after applying V

DD or releasing

the STOP mode.

Caution When using the main system clock oscillator, wiring in the area enclosed with the dotted line should

be carried out as follows to avoid an adverse effect from wiring capacitance.

• Wiring should be as short as possible.

• Wiring should not cross other signal lines.

• Wiring should not be placed close to a varying high current.

• The potential of the oscillator capacitor ground should be the same as V

DD.

• Do not ground to a ground pattern in which a high current flows.

• Do not fetch a signal from the oscillator.

32

Page 33

µ

PD75P3116

SUBSYSTEM CLOCK OSCILLATOR CHARACTERISTICS (TA = –40 to +85˚C, VDD = 1.8 to 5.5 V)

Resonator Recommended constant Parameter Test conditions MIN. TYP. MAX. Unit

Crystal Oscillation 32 32.768 35 kHz

XT1

resonator frequency (f

C3

XT2

R

C4

DD

V

Oscillation VDD = 4.5 to 5.5 V 1.0 2 s

stabilization time

XT)

Note 1

Note 2

10

External XT1 input frequency 32 100 kHz

clock (f

XT1

XT2

Note 1

XT)

XT1 input high-/low-level

515µs

width (tXTH, tXTL)

Notes 1. Indicates only oscillator characteristics. Refer to AC Characteristics for instruction execution time.

2. The oscillation stabilization time is necessary for oscillation to stabilize after applying V

DD.

Caution When using the subsystem clock oscillator, wiring in the area enclosed with the dotted line should

be carried out as follows to avoid an adverse effect from wiring capacitance.

• Wiring should be as short as possible.

• Wiring should not cross other signal lines.

• Wiring should not be placed close to a varying high current.

• The potential of the oscillator capacitor ground should be the same as V

DD.

• Do not ground to a ground pattern in which a high current flows.

• Do not fetch a signal from the oscillator.

The subsystem clock oscillator is designed as a low amplification circuit to provide low consumption

current, and is more liable to misoperation by noise than the main system clock oscillation circuit.

Special care should therefore be taken regarding the wiring method when the subsystem clock is

used.

33

Page 34

DC CHARACTERISTICS (TA = –40 to +85˚C, VDD = 1.8 to 5.5 V)

Parameter Symbol Test conditions MIN. TYP. MAX. Unit

µ

PD75P3116

Output current low I

OL Per pin 15 mA

Total of all pins 150 mA

Input voltage high VIH1 Ports 2, 3, 8, and 9 2.7 ≤ VDD ≤ 5.5 V 0.7VDD VDD V

1.8 ≤ VDD < 2.7 V 0.9VDD VDD V

VIH2 Ports 0, 1, 6, RESET 2.7 ≤ VDD ≤ 5.5 V 0.8V DD V DD V

DD < 2.7 V 0.9V DD VDD V

1.8 ≤ V

VIH3 Port 5 2.7 ≤ VDD ≤ 5.5 V 0.7VDD 13 V

(N-ch open-drain) 1.8 ≤ VDD < 2.7 V 0.9VDD 13 V

VIH4 X1, XT1

VDD – 0.1

VDD V

Input voltage low VIL1 Ports 2, 3, 5, 8, and 9 2.7 ≤ VDD ≤ 5.5 V 0 0.3VDD V

DD < 2.7 V 0 0.1VDD V

1.8 ≤ V

VIL2 Ports 0, 1, 6, RESET 2.7 ≤ VDD ≤ 5.5 V 0 0.2VDD V

1.8 ≤ VDD < 2.7 V 0 0.1VDD V

VIL3 X1, XT1 0 0.1 V

Output voltage high VOH

Output voltage low V

OL1

SCK, SO, Ports 2, 3, 6, 8, and 9 IOH = –1.0 mA

SCK, SO, Ports 2, 3, 5, 6, 8, and 9

IOL = 15 mA, 0.2 2.0 V

VDD =

4.5 to 5.5 V

VDD – 0.5

IOL = 1.6 mA 0.4 V

VOL2 SB0, SB1 When N-ch open-drain 0.2VDD V

pull-up resistor ≥ 1 kΩ

V

Input leakage I

LIH1 VIN = VDD Pins other than X1, XT1 3

current high ILIH2 X1, XT1 20

ILIH3 VIN = 13 V Port 5 (N-ch open-drain) 20

Input leakage ILIL1 VIN = 0 V Pins other than X1, XT1, and Port 5 –3

current low I LIL2 X1, XT1 –20

LIL3 Port 5 (N-ch open-drain) –3

I

µ

µ

µ

µ

µ

µ

When another instruction than input

instruction is executed

Port 5 (N-ch open-drain) –30

Output leakage ILOH1 VOUT = VDD

current high I

LOH2 VOUT = 13 V Port 5 (N-ch open-drain) 20

When input instruction VDD =

is executed VDD =

SCK, SO/SB0, SB1, Ports 2, 3, 6, 8, and 9

5.0 V

3.0 V

–10 –27

–3 –8

Output leakage ILOL VOUT = 0 V –3

µ

µ

µ

3

µ

µ

µ

current low

On-chip pull-up resistor RL VIN = 0 V Ports 0, 1, 2, 3, 6, 8, and 9 50 100 200 kΩ

(Excluding P00 pin)

A

A

A

A

A

A

A

A

A

A

A

A

34

Page 35

µ

PD75P3116

DC CHARACTERISTICS (TA = –40 to +85˚C, VDD = 1.8 to 5.5 V)

Parameter Symbol Test conditions MIN. TYP. MAX. Unit

LCD drive voltage V

VAC current

Note 1

LCD output voltage VODC lo = ±1.0 µAVLCD0 = VLCD 0 ±0.2 V

deviation

Note 2

(common) VLCD1 = VLCD x 2/3

LCD output voltage VODS lo = ±0.5 µAVLCD2 = VLCD x 1/3 0 ±0.2 V

deviation

Supply current

Note 2

(segment) 1.8 V ≤ VLCD ≤ VDD

Note 3

LCD VAC0 = 0 TA = –40 to +85°C 2.7 VDD V

A = –10 to +85°C 2.2 VDD V

T

VAC0 = 1 1.8 VDD V

IVAC VAC0 = 1, VDD = 2.0 V ± 10% 1 4

IDD1 6.00 MHz

Crystal oscillation

IDD2

C1 = C2 = 22 pF

Note 4

VDD = 5.0 V ± 10%

VDD = 3.0 V ± 10%

HALT mode VDD = 5.0 V ± 10% 0.7 2.0 mA

Note 5

Note 6

3.2 9.5 mA

0.55 1.6 mA

VDD = 3.0 V ± 10% 0.25 0.8 mA

IDD1 4.19 MHz

Crystal oscillation

IDD2

C1 = C2 = 22 pF

Note 4

VDD = 5.0 V ± 10%

VDD = 3.0 V ± 10%

HALT mode VDD = 5.0 V ± 10% 0.65 1.8 mA

Note 5

Note 6

2.5 7.5 mA

0.45 1.35 mA

VDD = 3.0 V ± 10% 0.22 0.7 mA

IDD3 32.768 kHz

Crystal oscillation

IDD4 HALT mode

Note 7

Low-voltage VDD = 3.0 V ± 10% 45 130

Note 8

mode

VDD = 2.0 V ± 10% 20 55

VDD = 3.0 V, TA = 25˚C

Low power

consumption

Note 9

mode

VDD = 3.0 V ± 10% 42 120

VDD = 3.0 V, TA = 25˚C

Low-

voltage

VDD = 3.0 V ± 10%

VDD = 2.0 V ± 10%

45 90

42 85

5.5 18

2.2 7

mode

IDD5 XT1 = 0 V

Note 8

Low

power

consumption mode

Note 10

VDD = 5.0 V ± 10% 0.05 10

Note 9

VDD = 3.0 V, TA = 25˚C

VDD = 3.0 V ± 10%

VDD = 3.0 V,

TA = 25˚C

5.5 12

4.0 12

4.0 8

STOP mode VDD = 3.0 V 0.02 5

± 10% TA = 25˚C 0.02 3

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

Notes 1. Set to VAC0 = 0 when the low power consumption mode and the stop mode are used. If VAC0 = 1

is set, the current increases for approx. 1 µA.

2. The voltage deviation is the difference from the output voltage corresponding to the ideal value of the

segment and common outputs (VLCDn; n = 0, 1, 2).

3. Not including currents flowing in on-chip pull-up resistors.

4. Including oscillation of the subsystem clock.

5. When the processor clock control register (PCC) is set to 0011 and the device is operated in the high-

speed mode.

6. When PCC is set to 0000 and the device is operated in the low-speed mode.

7. When the system clock control register (SCC) is set to 1001 and the device is operated on the

subsystem clock, with main system clock oscillation stopped.

8. When the sub-oscillation circuit control register (SOS) is set to 0000.

9. When SOS is set to 0010.

10. When SOS is set to 00×1 and the feedback resistor of the sub-oscillation circuit is not used.

35

Page 36

AC CHARACTERISTICS (TA = –40 to +85˚C, VDD = 1.8 to 5.5 V)

Parameter Symbol Test conditions MIN. TYP. MAX. Unit

µ

PD75P3116

CPU clock cycle t

Note 1

time

(Min. instruction execution

time = 1 machine cycle)

TI0, TI1, TI2 input fTI VDD = 2.7 to 5.5 V 0 1.0 MHz

frequency 0 275 kHz

TI0, TI1, TI2 input t

high-/low-level width 1.8

Interrupt input high-/

low-level width IM02 = 1 10

RESET low-level width tRSL 10

Notes 1. The cycle time (minimum instruction

execution time) of the CPU clock

(Φ) is determined by the oscillation

frequency of the connected

CY Operating on VDD = 2.7 to 5.5 V 0.67 64

main system clock 0.95 64

Operating on subsystem clock 114 122 125

TIH, tTIL VDD = 2.7 to 5.5 V 0.48

tINTH, tINTL

INT0 IM02 = 0 Note 2

INT1, 2, 4 10

KR0 to KR7 10

t

CY vs VDD

(At main system clock operation)

64

60

resonator (and external clock), the

system clock control register (SCC)

and the processor clock control

register (PCC). The figure at the

right indicates the cycle time t

CY

6

5

4

3

Guaranteed Operation

Range

versus supply voltage VDD

characteristic with the main system

clock operating.

CY or 128/fx is set by setting the

2. 2t

2

Cycle Time tCY [µs]

interrupt mode register (IM0).

1

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

36

0.5

10 23456

Supply Voltage VDD [V]

Page 37

µ

PD75P3116

SERIAL TRANSFER OPERATION

2-Wire and 3-Wire Serial I/O Mode (SCK...Internal clock output): (TA = –40 to +85˚C, VDD = 1.8 to 5.5 V)

Parameter Symbol Test conditions MIN. TYP. MAX. Unit

SCK cycle time tKCY1 VDD = 2.7 to 5.5 V 1300 ns

3800 ns

SCK high-/low-level t

KL1, tKH1 VDD = 2.7 to 5.5 V

width

Note 1

SI

setup time tSIK1 VDD = 2.7 to 5.5 V 150 ns

tKCY1/2–50

tKCY1/2–150

(to SCK↑) 500 ns

Note 1

SI

hold time tKSI1 VDD = 2.7 to 5.5 V 400 ns

(from SCK↑) 600 ns

Note 1

SCK↓→SO

delay time CL = 100 pF

output tKSO1 RL = 1 kΩ,VDD = 2.7 to 5.5 V 0 250 ns

Note 2

0 1000 ns

Notes 1. In 2-wire serial I/O mode, read this parameter as SB0 or SB1 instead.

L and CL are the load resistance and load capacitance of the SO output lines, respectively.

2. R

2-Wire and 3-Wire Serial I/O Mode (SCK...External clock input): (T

Parameter Symbol Test conditions MIN. TYP. MAX. Unit

SCK cycle time tKCY2 VDD = 2.7 to 5.5 V 800 ns

SCK high-/low-level tKL2, tKH2 VDD = 2.7 to 5.5 V 400 ns

width 1600 ns

Note 1

setup time tSIK2 VDD = 2.7 to 5.5 V 100 ns

SI

(to SCK↑) 150 ns

Note 1

SI

hold time tKSI2 VDD = 2.7 to 5.5 V 400 ns

(from SCK↑) 600 ns

Note 1

SCK↓→SO

delay time CL = 100 pF

output tKSO2 RL = 1 kΩ,VDD = 2.7 to 5.5 V 0 300 ns

Note 2

A = –40 to +85˚C, VDD = 1.8 to 5.5 V)

3200 ns

0 1000 ns

ns

ns

Notes 1. In 2-wire serial I/O mode, read this parameter as SB0 or SB1 instead.

L and CL are the load resistance and load capacitance of the SO output lines, respectively.

2. R

37

Page 38

SBI Mode (SCK...Internal clock output (master)): (TA = –40 to +85˚C, VDD = 1.8 to 5.5 V)

Parameter Symbol Test conditions MIN. TYP. MAX. Unit

µ

PD75P3116

SCK cycle time t

KCY3 VDD = 2.7 to 5.5 V 1300 ns

3800 ns

SCK high-/low-level tKL3, tKH3 VDD = 2.7 to 5.5 V

width

tKCY3/2–50

tKCY3/2–150

ns

ns

SB0, 1 setup time tSIK3 VDD = 2.7 to 5.5 V 150 ns

(to SCK↑) 500 ns

SB0, 1 hold time (from SCK↑)

tKSI3 tKCY3/2 ns

SCK↓→ SB0, 1 tKSO3 RL = 1 kΩ,VDD = 2.7 to 5.5 V 0 250 ns

output delay time CL = 100 pF

Note

0 1000 ns

SCK↑→ SB0, 1↓ tKSB tKCY3 ns

SB0, 1 ↓→SCK↓ t

SBK tKCY3 ns

SB0, 1 low-level width tSBL tKCY3 ns

SB0, 1 high-level width tSBH tKCY3 ns

Note RL and CL are the load resistance and load capacitance of the SB0 and SB1 output lines, respectively.

SBI Mode (SCK...External clock input (slave)): (T

Parameter Symbol Test conditions MIN. TYP. MAX. Unit

SCK cycle time tKCY4 VDD = 2.7 to 5.5 V 800 ns

SCK high-/low-level tKL4, tKH4 VDD = 2.7 to 5.5 V 400 ns

A = –40 to +85˚C, VDD = 1.8 to 5.5 V)

3200 ns

width 1600 ns

SB0, 1 setup time t

SIK4 VDD = 2.7 to 5.5 V 100 ns

(to SCK↑) 150 ns

SB0, 1 hold time (from SCK↑)

tKSI4 tKCY4/2 ns

SCK↓→SB0, 1 output tKSO4 RL = 1 kΩ,VDD = 2.7 to 5.5 V 0 300 ns

delay time C

L = 100 pF

Note

0 1000 ns

SCK↑→ SB0, 1↓ tKSB tKCY4 ns

SB0, 1↓→ SCK↓ t SBK tKCY4 ns

SB0, 1 low-level width tSBL tKCY4 ns

SB0, 1 high-level width tSBH tKCY4 ns

Note RL and CL are the load resistance and load capacitance of the SB0 and SB1 output lines, respectively.

38

Page 39

AC Timing Test Point (Excluding X1, XT1 Input)

µ

PD75P3116

Clock Timing

X1 Input

VIH (MIN.)

IL

(MAX.)

V

VOH (MIN.)

OL

(MAX.)

V

tXL

1/fX

1/fXT

tXH

V

IH

IL

V

V

OH

OL

V

(MIN.)

(MAX.)

(MIN.)

(MAX.)

V

DD–0.1 V

0.1 V

XT1 Input

TI0, TI1, TI2 Timing

TI0, TI1, TI2

tXTL

tXTH

V

DD–0.1 V

0.1 V

1/f

TI

t

TIL

t

TIH

39

Page 40

Serial Transfer Timing

3-wire serial I/O mode

SCK

tKCY1, 2

tKL1, 2 tKH1, 2

tSIK1, 2 tKSI1, 2

µ

PD75P3116

SI

SO

2-wire serial I/O mode

SCK

SB0, 1

tKSO1, 2

Input Data

tKL1, 2

tSIK1, 2

Output Data

tKCY1, 2

tKH1, 2

tKSI1, 2

40

tKSO1, 2

Page 41

Serial Transfer Timing

Bus release signal transfer

SCK

tKL3, 4

tKCY3, 4

tKH3, 4

µ

PD75P3116

SB0, 1

Command signal transfer

SCK

SB0, 1

tSBKtSBHtSBLtKSB

tKCY3, 4

tKL3, 4

tSBKtKSB

tKH3, 4

tSIK3, 4

tKSO3, 4

tSIK3, 4

tKSO3, 4

tKSI3, 4

tKSI3, 4

Interrupt input timing

INT0, 1, 2, 4

RESET input timing

tINTL tINTH

KR0 to 7

tRSL

RESET

41

Page 42

µ

DATA MEMORY STOP MODE LOW SUPPLY VOLTAGE DATA RETENTION CHARACTERISTICS

A = –40 to +85˚C)

(T

Parameter Symbol Test conditions MIN. TYP. MAX. Unit

PD75P3116

Release signal set time t

SREL 0

Oscillation stabilization tWAIT Release by RESET

wait time

Note 1

Release by interrupt request

215/f

Note 2

X

µ

ms

ms

s

Notes 1. The oscillation stabilization wait time is the time during which the CPU operation is stopped to prevent

unstable operation at the oscillation start.

2. Depends on the basic interval timer mode register (BTM) settings (See the table below).

BTM3 BTM2 BTM1 BTM0 Wait time

fx = at 4.19 MHz fx = at 6.0 MHz

—0002

—0112

—1012

—1112

20

/fx (approx. 250 ms) 220/fx (approx. 175 ms)

17

/fx (approx. 31.3 ms) 217/fx (approx. 21.8 ms)

15

/fx (approx. 7.81 ms) 215/fx (approx. 5.46 ms)

13

/fx (approx. 1.95 ms) 213/fx (approx. 1.37 ms)

42

Page 43

Data Retention Timing (STOP Mode Release by RESET)

Internal Reset Operation

HALT mode

STOP Mode

Data Retention Mode

V

DD

t

SREL

STOP Instruction Execution

RESET

t

WAIT

Data Retention Timing (Standby Release Signal: STOP Mode Release by Interrupt Signal)

µ

PD75P3116

Operating Mode

V

DD

STOP Instruction Execution

Standby Release Signal

(Interrupt Request)

STOP Mode

Data Retention Mode

t

SREL

HALT mode

t

WAIT

Operating Mode

43

Page 44

µ

PD75P3116

DC PROGRAMMING CHARACTERISTICS (TA = 25 ± 5˚C, VDD = 6.0 ± 0.25 V, VPP = 12.5 ± 0.3 V, VSS = 0 V)

Parameter Symbol Test conditions MIN. TYP. MAX. Unit

Input voltage high VIH1 Except X1 and X2 pins 0.7VDD V DD V

V

IH2 X1, X2 VDD–0.5 VDD V

Input voltage low VIL1 Except X1 and X2 pins 0 0.3VDD V

VIL2 X1, X2 0 0.4 V

Input leakage current I

LI VIN = VIL or VIH 10

µ

A

Output voltage high VOH I OH = –1 mA VDD–1.0 V

Output voltage low VOL IOL = 1.6 mA 0.4 V

V

DD power supply current IDD 30 mA

VPP power supply current IPP MD0 = V IL, MD1 = VIH 30 mA

Cautions 1. Avoid exceeding +13.5 V for VPP including the overshoot.

DD must be applied before VPP, and cut after VPP.

2. V

AC PROGRAMMING CHARACTERISTICS (T

A = 25 ±5˚C, VDD = 6.0 ±0.25 V, VPP = 12.5 ±0.3 V, VSS = 0 V)

Parameter Symbol Note 1 Test conditions MIN. TYP. MAX. Unit

Address setup time

Note 2

(to MD0↓)tAS t AS 2

MD1 setup time (to MD0↓)tM1S tOES 2

Data setup time (to MD0↓)tDS tDS 2

Address hold time

Data hold time (from MD0↑)t

Note 2

(from MD0↑)tAH tAH 2

DH tDH 2

MD0↑→data output float delay time tDF tDF 0 130 ns

VPP setup time (to MD3↑)tVPS tVPS 2

V

DD setup time (to MD3↑)tVDS tVCS 2

Initial program pulse width tPW tPW 0.95 1.0 1.05 ms

Additional program pulse width tOPW tOPW 0.95 21.0 ms

MD0 setup time (to MD1↑)tM0S tCES 2

MD0↓→data output delay time t

DV tDV MD0 = MD1 = VIL 1

MD1 hold time (from MD0↑)tM1H tOEH tM1H+tM1R ≥ 50 µs2

MD1 recovery time (from MD0↓)tM1R tOR 2

Program counter reset time t

PCR –10

X1 input high-/low-level width tXH, tXL – 0.125

X1 input frequency f X – 4.19 MHz

Initial mode set time t

I –2

MD3 setup time (to MD1↑)tM3S –2

MD3 hold time (from MD1↓)tM3H –2

MD3 setup time (to MD0↓)tM3SR –

Address

Address

Note 2

→data output delay time

Note 2

→data output hold time

tDAD tACC

tHAD tOH

MD3 hold time (from MD0↑)tM3HR –

MD3↓→data output float delay time t

DFR –

During program memory read

2

During program memory read

During program memory read

During program memory read

0 130 ns

2

During program memory read

2

2

Notes 1.Corresponding symbol of µPD27C256A

2.The internal address signal is incremented by 1 at the rising edge of the fourth X1 input and is not

connected to a pin.

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

44

Page 45

Program Memory Write Timing

t

VPS

V

PP

V

PP

V

DD

t

VDS

VDD+1

V

DD

V

DD

X1

D0/P60 to D3/P60

D4/P50 to D7/P53

MD0/P30

MD1/P31

MD2/P32

MD3/P33

t

I

t

PCR

t

M3S

Data input

t

DS

t

t

M1S

µ

PD75P3116

t

XH

t

Data output

t

DH

PW

t

M1H

t

DVtDF

t

M1R

t

M0S

Data input

t

DS

t

OPW

XL

t

DH

t

AH

t

AS

Data input

t

M3H

Program Memory Read Timing

tVPS

VPP

VPP

VDD

VDD+1

VDD

VDD

X1

D0/P60 to D3/P60

D4/P50 to D7/P53

tI

MD0/P30

MD1/P31

tPCR

MD2/P32

tVDS

tXH

tXL

tHAD

tDAD

Data output Data output

tDV

tM3HR

tDFR

MD3/P33

tM3SR

45

Page 46

10. CHARACTERISTIC CURVES (REFERENCE VALUES)

I

DD

vs VDD(Main System Clock: 6.0-MHz Crystal Resonator)

10

5.0

1.0

0.5

µ

PD75P3116

(T

A

= 25°C)

PCC = 0011

PCC = 0010

PCC = 0001

PCC = 0000

Main system clock

HALT mode + 32-kHz oscillation

(mA)

DD

0.1

Supply Current I

0.05

0.01

0.005

Subsystem clock operation

mode (SOS.1 = 0)

Main system clock STOP

mode + 32-kHz oscillation

(SOS.1 = 0) and

subsystem clock HALT mode

(SOS.1 = 0)

Main system clock STOP

mode + 32-kHz oscillation

(SOS.1 = 1) and subsystem

clock HALT mode (SOS.1 = 1)

XT1 XT2X1 X2

Crystal resonator

6.0 MHz

Crystal resonator

32.768 kHz

330 kΩ

22 pF 22 pF 22 pF 22 pF

46

V

V

0.001

012345678

DD

Supply Voltage V

(V)

DD

DD

Page 47

10

5.0

1.0

0.5

IDD vs VDD (Main System Clock: 4.19-MHz Crystal Resonator)

PCC = 0011

PCC = 0010

PCC = 0001

PCC = 0000

Main system clock

HALT mode + 32-kHz oscillation

µ

PD75P3116

(T

A = 25°C)

0.1

Supply Current IDD (mA)

0.05

0.01

0.005

22 pF 22 pF 22 pF 22 pF

0.001

012345678

Supply Voltage VDD (V)

Subsystem clock operation

mode (SOS.1 = 0)

Subsystem clock HALT mode

(SOS.1 = 0) and

main system clock STOP mode

+ 32-kHz oscillation (SOS.1 = 0)

Main system clock STOP

mode + 32-kHz oscillation

(SOS.1 = 1)

and subsystem

mode (SOS.1 = 1)

Crystal resonator

4.19 MHz

XT1 XT2X1 X2

clock HALT

Crystal resonator

32.768 kHz

VDDVDD

330 kΩ

47

Page 48

11. PACKAGE DRAWINGS

64 PIN PLASTIC QFP ( 14)

µ

PD75P3116

A

B

48

49

64

F

1

G

H

M

I

P

N

NOTE

Each lead centerline is located within 0.15

mm (0.006 inch) of its true position (T.P.) at

maximum material condition.

33

32

detail of lead end

C

D

S

Q

17

16

J

K

M

L

ITEM MILLIMETERS INCHES

A

B

C

D

F

G

H

I

J

K

L

M

N

17.6±0.4

14.0±0.2

14.0±0.2

17.6±0.4

1.0

1.0

0.35±0.10

0.15

0.8 (T.P.)

1.8±0.2

0.8±0.2

+0.10

0.15

–0.05

0.10