Datasheet UPD75108GF-XXX-3BE, UPD75108GF-A-XXX-3BE, UPD75108G-XXX-1B, UPD75108CW-XXX, UPD75108CW-A-XXX Datasheet (NEC)

...Page 1

DESCRIPTION

µ

PD75108 is a 4-bit single-chip microcomputer integrating timer/event counters, serial interface, and vector

interrupt function, in addition to a CPU, ROM, RAM, and I/O ports, on a single chip. Operating at high speeds,

the microcomputer allows data to be manipulated in units of 1, 4, or 8 bits. In addition, various bit manipulation

instructions are provided to reinforce I/O manipulation capability. Equipped with I/Os for interfacing with

peripheral circuits operating on a different supply voltage, outputs that can directly drive LEDs, and analog

inputs,

µ

PD75108 is suitable for controlling such systems as VTRs, acoustic products, button telephones, radio

communications equipment, and printers. A pin-compatible EPROM model is also available for evaluation of

system development and small-scale production of application systems.

Detailed functions are described in the following user’s manual. Be sure to read it for designing.

µ

PD751XX Series User’s Manual: IEM-922

FEATURES

• Internal memory

• Program memory (ROM)

: 8068 × 8 bits (µPD75108)

: 6016

×

8 bits (µPD75106)

: 4096

×

8 bits (µPD75104)

• Data memory (RAM)

: 512 × 4 bits (µPD75108)

: 320

×

4 bits (µPD75106, 75104)

• New architecture “75X series” rivaling 8-bit microcomputers

• 43 systematically organized instructions

• A wealth of bit manipulation instructions

• 8-bit data transfer, compare, operation, increment, and decrement instructions

• 1-byte relative branch instructions

• GETI instruction executing 2-/3-byte instruction with one byte

• High speed. Minimum instruction execution time: 0.95

µ

s (at 4.19 MHz), 5 V

• Power-saving, instruction time change function: 0.95

µ

s/1.91 µs/15.3 µs (at 4.19 MHz)

• I/O port pins as many as 58

• Three channels of 8-bit timers

• 8-bit serial interface

• Multiplexed vector interrupt function

• Model with PROM is available:

µ

PD75P108B (One-time PROM, EPROM)

NEC Corporation 1989

Document No. IC-2520B

(O. D. No. IC-6906B)

Date Published January 1994 P

Printed in Japan

DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD75104, 75106, 75108

4-BIT SINGLE-CHIP MICROCOMPUTER

The mark ★ shows major revised points.

The information in this document is subject to change without notice.

Unless there are differences among µPD75104, 75106, and 75108 functions, µPD75108 is treated as the

representative model throughout this manual.

Page 2

µ

PD75104, 75106, 75108

2

ORDERING INFORMATION

Part Number Package Quality Grade

µ

PD75104CW-xxx 64-pin plastic shrink DIP (750 mil) Standard

µ

PD75104GF-xxx-3BE 64-pin plastic QFP (14 × 20 mm) Standard

µ

PD75106CW-xxx 64-pin plastic shrink DIP (750 mil) Standard

µ

PD75106GF-xxx-3BE 64-pin plastic QFP (14 × 20 mm) Standard

µ

PD75108CW-xxx 64-pin plastic shrink DIP (750 mil) Standard

µ

PD75108GF-xxx-3BE 64-pin plastic QFP (14 × 20 mm) Standard

Remarks: xxx is ROM code number.

Please refer to “Quality Grade on NEC Semiconductor Devices” (Document Number IEI-1209) published by

NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

Page 3

µ

PD75104, 75106, 75108

3

FUNCTIONAL OUTLINE

Item Specifications

Number of Basic Instructions 43

Minimum Instruction Changeable in three steps: 0.95 µs, 1.91 µs, and 15.3 µs at 4.19 MHz

Execution Time

ROM 8064 × 8 bits (µPD75108), 6016 × 8 bits (µPD75106), 4096 × 8 bits (µPD75104)

RAM 512 × 4 bits (µPD75108), 320 × 4 bits (µPD75106, 75104)

General-Purpose Register 4 bits × 8 × 4 banks (memory mapped)

Three accumulators selectable according to the bit length of manipulated data:

• 1-bit accumulator (CY), 4-bit accumulator (A), and 8-bit accumulator (XA)

58 port pins

• CMOS input pins: 10

I/O Port

• CMOS I/O pins (can directly drive LEDs): 32

• Medium voltage N-ch open-drain I/O pins: 12

(can directly drive LEDs. Pull-up resistor can be connected to each bit)

• Comparator input pins (4-bit accuracy): 4

• 8-bit timer/event counter × 2

Timer/Counter

• 8-bit basic interval timer (can be used as watchdog timer)

• 8 bits

Serial Interface • LSB first/MSB first mode selectable

• Two transfer modes (transfer/reception and reception only modes)

Vector Interrupt External: 3, Internal: 4

Test Input External: 2

Standby • STOP and HALT modes

• Various bit manipulation instructions (set, reset, test, Boolean operation)

Instruction Set

• 8-bit data transfer, compare, operation, increment, and decrement

• 1-byte relative branch instructions

• GETI instruction constituting 2 or 3-byte instruction with 1 byte

• Power-ON reset circuit (mask option)

Others

• Bit manipulation memory (bit sequential buffer: 16 bits)

Package

• 64-pin plastic shrink DIP (750 mil)

• 64-pin plastic QFP (14 × 20 mm)

Internal Memory

Accumulator

Page 4

µ

PD75104, 75106, 75108

4

CONTENTS

1. PIN CONFIGURATION (TOP VIEW)............................................................................................... 6

2. BLOCK DIAGRAM ........................................................................................................................... 8

3. PIN FUNCTIONS.............................................................................................................................. 9

3.1 PORT PINS............................................................................................................................................. 9

3.2 PINS OTHER THAN PORTS ................................................................................................................. 10

3.3 PIN INPUT/OUTPUT CIRCUITS ........................................................................................................... 11

3.4 RECOMMENDED PROCESSING OF UNUSED PINS .......................................................................... 12

3.5 NOTES ON USING THE P00/INT4, AND RESET PINS ...................................................................... 13

4. MEMORY CONFIGURATION .......................................................................................................... 14

5. PERIPHERAL HARDWARE FUNCTIONS........................................................................................ 20

5.1 PORTS .................................................................................................................................................... 20

5.2 CLOCK GENERATOR CIRCUIT ............................................................................................................ 21

5.3 CLOCK OUTPUT CIRCUIT .................................................................................................................... 22

5.4 BASIC INTERVAL TIMER ..................................................................................................................... 23

5.5 TIMER/EVENT COUNTER ..................................................................................................................... 23

5.6 SERIAL INTERFACE .............................................................................................................................. 25

5.7 PROGRAMMABLE THRESHOLD PORT (ANALOG INPUT PORT) .................................................... 27

5.8 BIT SEQUENTIAL BUFFER .... 16 BITS ............................................................................................... 28

5.9 POWER-ON FLAG (MASK OPTION) .................................................................................................... 28

6. INTERRUPT FUNCTIONS................................................................................................................ 28

7. STANDBY FUNCTIONS .................................................................................................................. 30

8. RESET FUNCTION........................................................................................................................... 31

9. INSTRUCTION SET ......................................................................................................................... 34

Page 5

µ

PD75104, 75106, 75108

5

10. APPLICATION EXAMPLES .............................................................................................................. 43

10.1 VTR SYSTEM CONTROLLER ............................................................................................................... 43

10.2 VTR CAMERA ........................................................................................................................................ 43

10.3 COMPACT DISC PLAYER ..................................................................................................................... 44

10.4 AUTOMOBILE APPLICATIONS (TRIP COMPUTER)............................................................................ 44

10.5 PUSHBUTTON TELEPHONE ................................................................................................................ 45

10.6 DISPLAY PAGER ................................................................................................................................... 45

10.7 PLAIN PAPER COPIER (PPC) ............................................................................................................... 46

10.8 PRINTER CONTROLLER ....................................................................................................................... 46

11. MASK OPTION SELECTION ........................................................................................................... 47

12. ELECTRICAL SPECIFICATIONS ...................................................................................................... 48

13. CHARACTERISTIC DATA ................................................................................................................ 57

14. PACKAGE DRAWINGS ................................................................................................................... 62

15. RECOMMENDED SOLDERING CONDITIONS ............................................................................... 65

APPENDIX A. FUNCTIONAL DIFFERENCES AMONG PRODUCTS IN µPD751XX SERIES ......... 66

APPENDIX B. DEVELOPMENT TOOLS .............................................................................................. 67

APPENDIX C. RELATED DOCUMENTS .............................................................................................. 68

Page 6

µ

PD75104, 75106, 75108

6

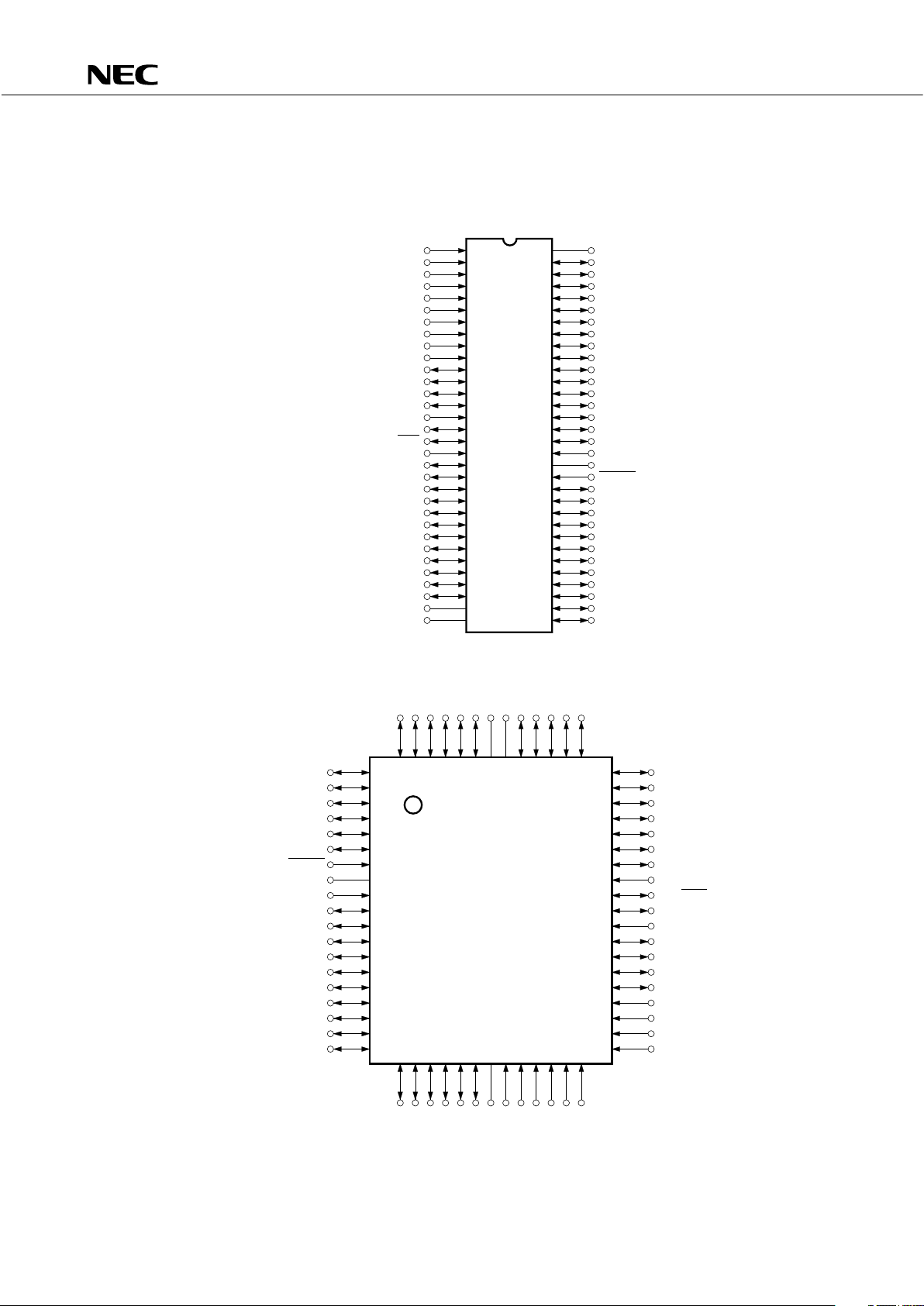

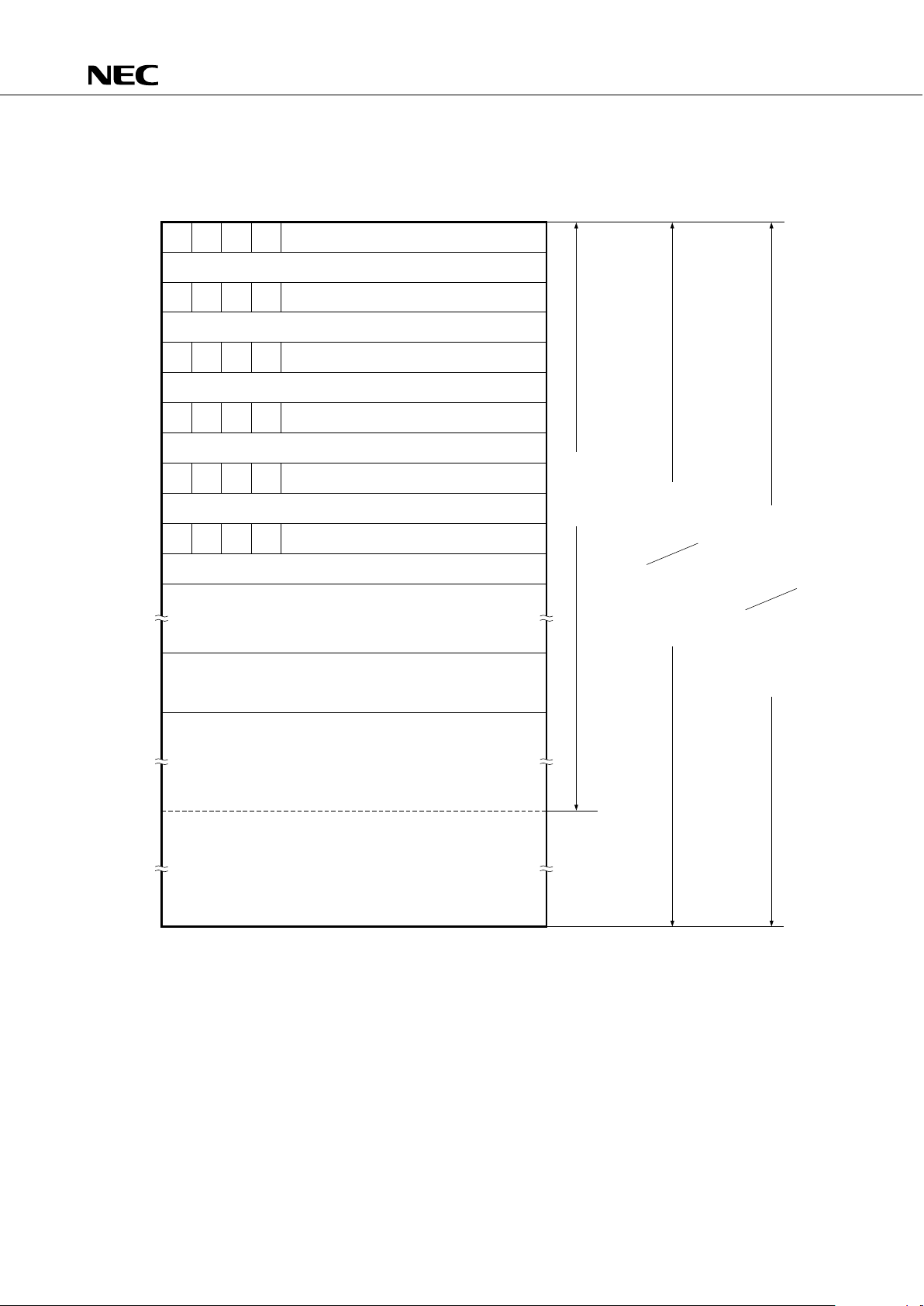

1. PIN CONFIGURATION (Top View)

• 64-Pin Plastic Shrink DIP (750 mil)

P13/INT3 1

V32

V64

33

SS

µ

PD75104CW-

PD75106CW-

PD75108CW-

×××

×××

×××

P12/INT2

P11/INT1

P10/INT0

PTH03

PTH02

PTH01

PTH00

TI0

TI1

P23

P22/PCL

2

3

4

5

6

7

8

9

10

11

12

P21 PTO1 13

P20 PTO0 14

P9063

P9162

P9261

P9360

P8059

P8158

P8257

P8356

P7055

P7154

P7253

P7352

P6051

P03/SI 15 P6150

P02/SO 16 P6249

P01/SCK 17 P6348

P00/INT4 18 X147

P123 19 X246

P122 20 RESET45

P121 21 P5044

P120 22 P5143

P133 23 P5242

P132 24 P5341

P131 25 P4040

P130 26 P4139

P143 27 P4238

P142 28 P4337

P141 29 P3036

P140 30 P3135

NC 31 P3234

DD

µ

µ

P33

51 P1311P41

64

P42

P43

P30

P31

P32

P33VNC

P140

P141

P142

P143

P130

63 62 61 60 59 58 57 56 55 54 53 52

DD

20 21 22 23 24 25 26 27 28 29 30 31 32

P81

P80

P93

P92

P91

P90

V

P13/INT3

P12/INT2

P11/INT1

P10/INT0

PTH03

PTH02

SS

µ

PD75104GF-

PD75106GF-

PD75108GF-

×××

×××

×××

µ

µ

-3BE

-3BE

-3BE

50 P1322P40

49 P1333P53

48 P1204P52

47 P1215P51

46 P1226P50

45 P1237RESET

44 P00/INT48X2

43 P01/SCK9X1

42 P02/SO10P63

41 P03/SI11P62

40 P20/PTO012P61

39 P21/PTO113P60

38 P22/PCL14P73

37 P2315P72

36 TI116P71

35 TI017P70

34 PTH0018P83

33 PTH0119P82

• 64-Pin Plastic QFP (14 × 20 mm)

Page 7

µ

PD75104, 75106, 75108

7

Pin names

P00-P03 : Port 0 SCK : Serial Clock Input/Output

P10-P13 : Port 1 SO : Serial Output

P20-P23 : Port 2 SI : Serial Input

P30-P33 : Port 3 PTO0, PTO1 : Timer Output

P40-P43 : Port 4 PCL : Clock Output

P50-P53 : Port 5 PTH00-PTH03 : Comparator Input

P60-P63 : Port 6

INT0, INT1, INT4 : External Vector Interrupt Input

P70-P73 : Port 7 INT2, INT3 : External Test Input

P80-P83 : Port 8 TI0, TI1 : Timer Input

P90-P93 : Port 9 X1, X2 : Clock Oscillation Pin

P120-P123 : Port 12 RESET : Reset Input

P130-P133 : Port 13 NC : No Connection

P140-P143 : Port 14

Page 8

µ

PD75104, 75106, 75108

8

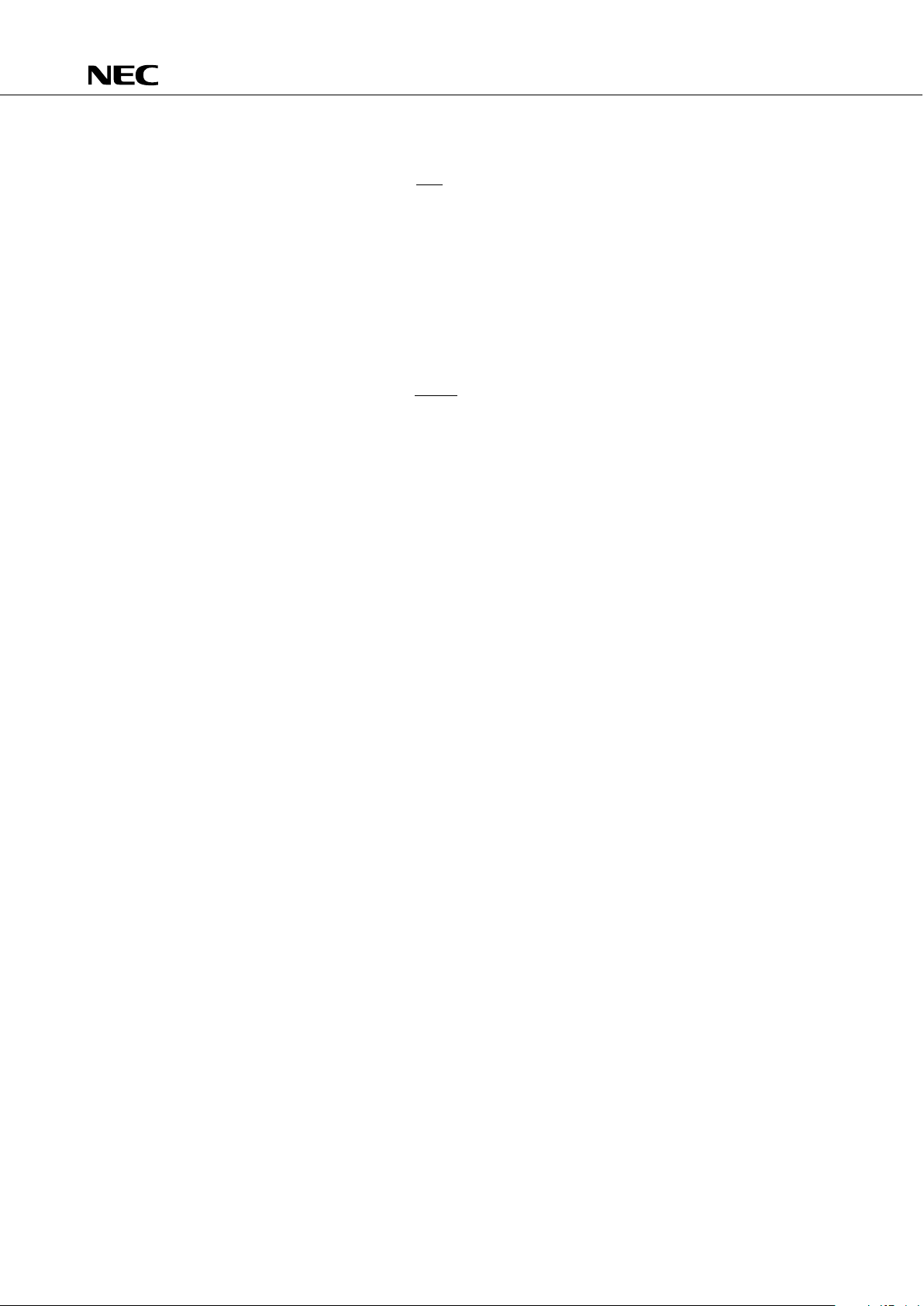

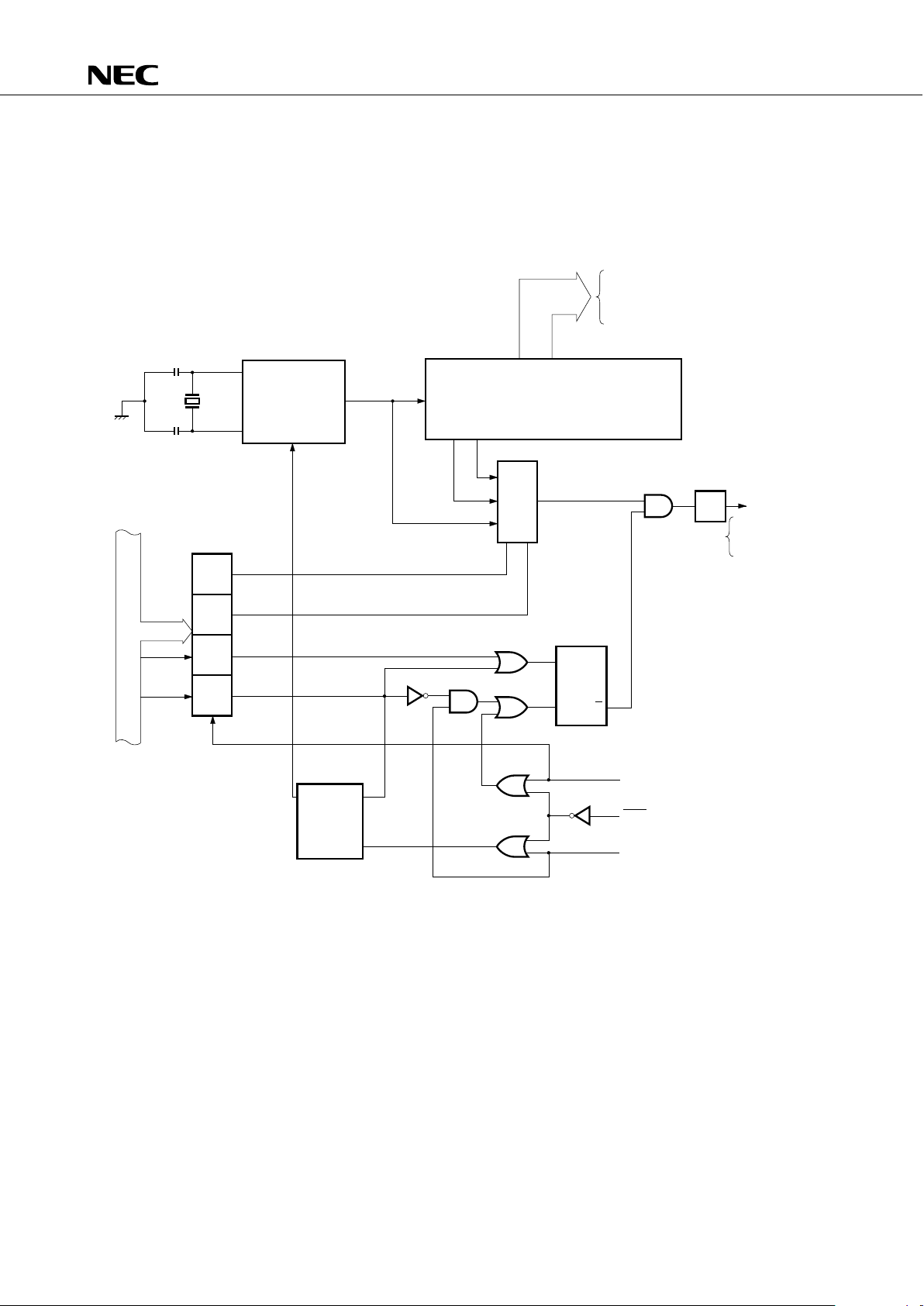

2. BLOCK DIAGRAM

TI0

PTO0/P20

BASIC

INTERVAL

TIMER

INTBT

PROGRAM

COUNTER*

ALU

CY SP (8)

BANK

GENERAL REG.

DECODE

AND

CONTROL

ROM

PROGRAM

MEMORY

8064 8BITS

: PD75108

6016 8BITS

: PD75106

4096 8BITS

: PD75104

µ

µ

µ

RAM

DATA MEMORY

512 4BITS

: PD75108

320 4BITS

: PD75106, 75104

×

×

×

×

×

µ

µ

f /2

XX

N

CPU CLOCK

Φ

PCL/P22 X1 X2 V

DDVSS

RESET

CLOCK

OUTPUT

CONTROL

CLOCK

DIVIDER

CLOCK

GENERATOR

STAND BY

CONTROL

TIMER/EVENT

COUNTER

#0

TIMER/EVENT

COUNTER

#1

SERIAL

INTERFACE

INTERRUPT

CONTROL

PROGRAMMABLE

THRESHOLD

PORT #0

TI1

PTO1/P21

SI/P03

SO/P02

SCK/P01

INT0/P10

INT1/P11

INT2/P12

INT3/P13

INT4/P00

PTH00-PTH03 4

4

4

4

4

4

4

4

4

4

4

4

4

4

BIT SEQ.

BUFFER (16)

PORT 0

P00 - P03

P10 - P13PORT 1

PORT 2

PORT 3

PORT 4

PORT 5

PORT 6

PORT 7

PORT 8

PORT 9

PORT 12

PORT 13

PORT 14

P20 - P23

P30 - P33

P40 - P43

P50 - P53

P60 - P63

P70 - P73

P80 - P83

P90 - P93

P120 - P123

P130 - P133

P140 - P143

*: 13 bits: PD75106, 75108

12 bits: PD75104

µ

µ

INTT0

INTT1

INTSIO

Page 9

µ

PD75104, 75106, 75108

9

3. PIN FUNCTIONS

3.1 PORT PINS

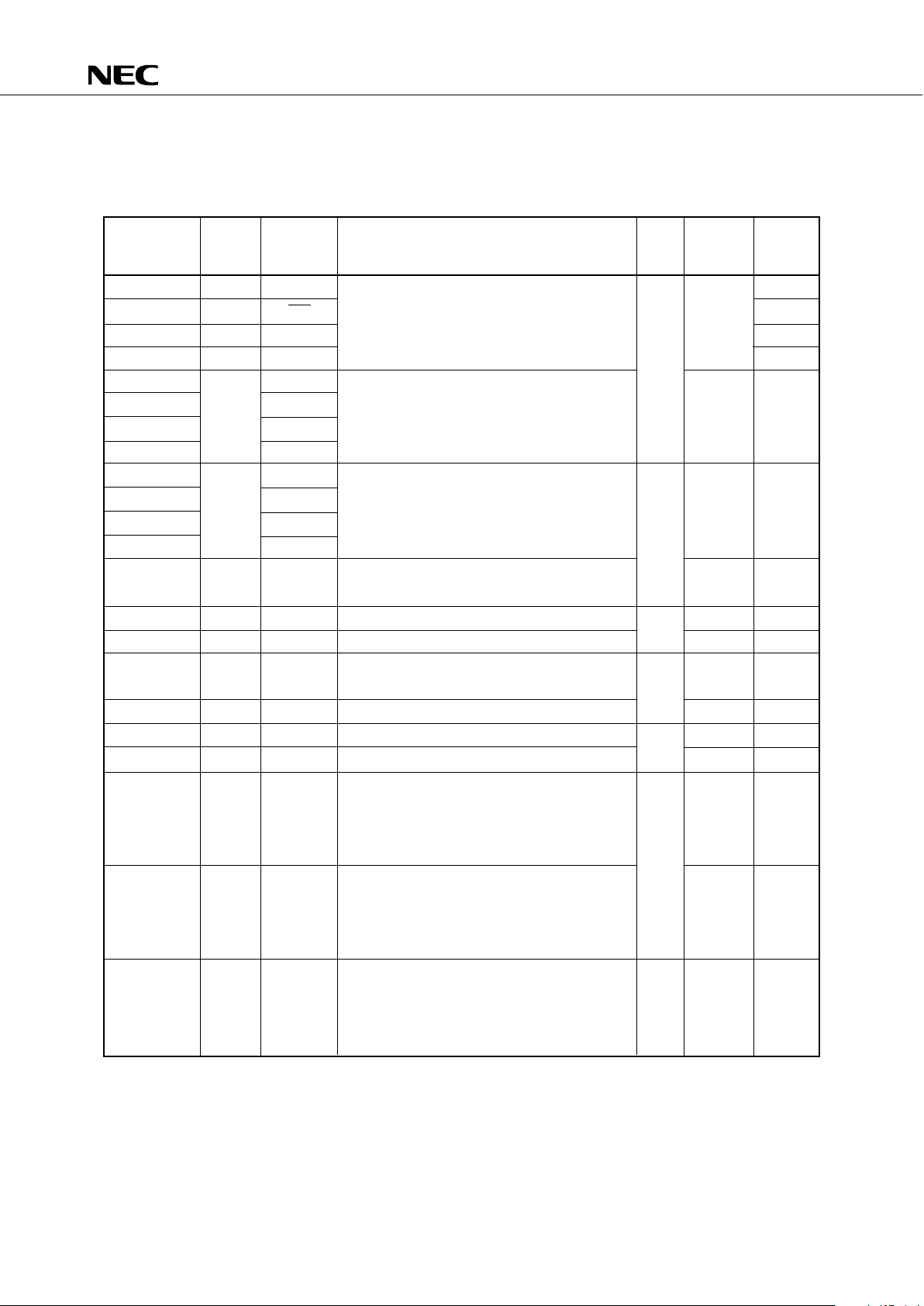

I/O

Pin Name I/O

Shared with:

Function At Reset Circuit

TYPE*

1

P00 Input INT4 B

P01 I/O SCK F

4-bit input port (PORT 0) Input

P02 I/O SO E

P03 Input SI B

x

P10 INT0

P11 INT1

Input 4-bit input port (PORT 1) Input B

P12 INT2

P13 INT3

P20*

3

PTO0

P21*

3

PTO1

I/O 4-bit I/O port (PORT 2) Input E

P22*

3

PCL

x

P23*

3

—

4-bit programmable I/O port (PORT 3)

P30-P33*

3

I/O — Input E

Can be specified for input or output bitwise.

P40-P43*

3

I/O — 4-bit I/O port (PORT 4) Input E

o

P50-P53*

3

I/O — 4-bit I/O port (PORT 5) Input E

4-bit programmable I/O port (PORT 6)

P60-P63*

3

I/O — Input E

Can be specified for input or output bitwise. o

P70-P73*

3

I/O 4-bit I/O port (PORT 7) Input E

P80-P83*

3

I/O — 4-bit I/O port (PORT 8) Input E

o

P90-P93*

3

I/O — 4-bit I/O port (PORT 9) Input E

4-bit N-ch open-drain I/O port (PORT 12)

Built-in pull-up resistors can be specified in bit

P120-P123*

3

I/O —

units by mask option.

Open-drain withstanding voltage: 12 V

o

4-bit N-ch open-drain I/O port (PORT 13)

Built-in pull-up resistors can be specified in bit

P130-P133*

3

I/O —

units by mask option.

Open-drain withstanding voltage: 12 V

4-bit N-ch open-drain I/O port (PORT 14)

Built-in pull-up resistors can be specified in bit

P140-P143*

3

I/O — – Input*

2

M

units by mask option.

Open-drain withstanding voltage: 12 V

*1: Circles indicate Schmitt trigger input pins.

2: With drain open: high impedance

With pull-up resistor connected: high level

3: Can directly drive LEDs.

8-Bit

I/O

Input*

2

M

Input*

2

M

Page 10

µ

PD75104, 75106, 75108

10

3.2 PINS OTHER THAN PORTS

I/O

Pin Name I/O

Shared with:

Function At Reset Circuit

TYPE*

1

PTH00-PTH03 Input — 4-bit variable threshold voltage analog input port — N

TI0 External event pulse inputs for timer/event counter.

Input — Also serves as edge-detected vector interrupt input. — B

TI1

1-bit input also possible.

PTO0 P20

I/O Outputs for timer/event counter Input E

PTO1 P21

SCK I/O P01 Serial clock I/O Input F

SO I/O P02 Serial data output Input E

SI Input P03 Serial data input Input B

Edge-detected vectored interrupt input (both rising and

INT4 Input P00 Input B

falling edges detected)

INT0 P10 Edge-detected vectored interrupt inputs (valid

Input Input B

INT1 P11 edge selectable)

INT2 P12

Input Edge-detected testable inputs (rising edge detected) Input B

INT3 P13

PCL I/O P22 Clock output Input E

Crystal/ceramic system clock oscillator connections.

X1, X2 — — Input external clock to X1, and signal in reverse phase — —

with X1 to X2.

RESET Input — System reset input (low level active type) — B

NC*

2

— — No Connection — —

VDD — — Positive power supply — —

VSS ——GND ——

*1: Circles indicate Schmitt trigger input pins.

2: Connect the NC pin directly to the V

DD pin when

µ

PD75P108B and a printed circuit board are shared.

Page 11

µ

PD75104, 75106, 75108

11

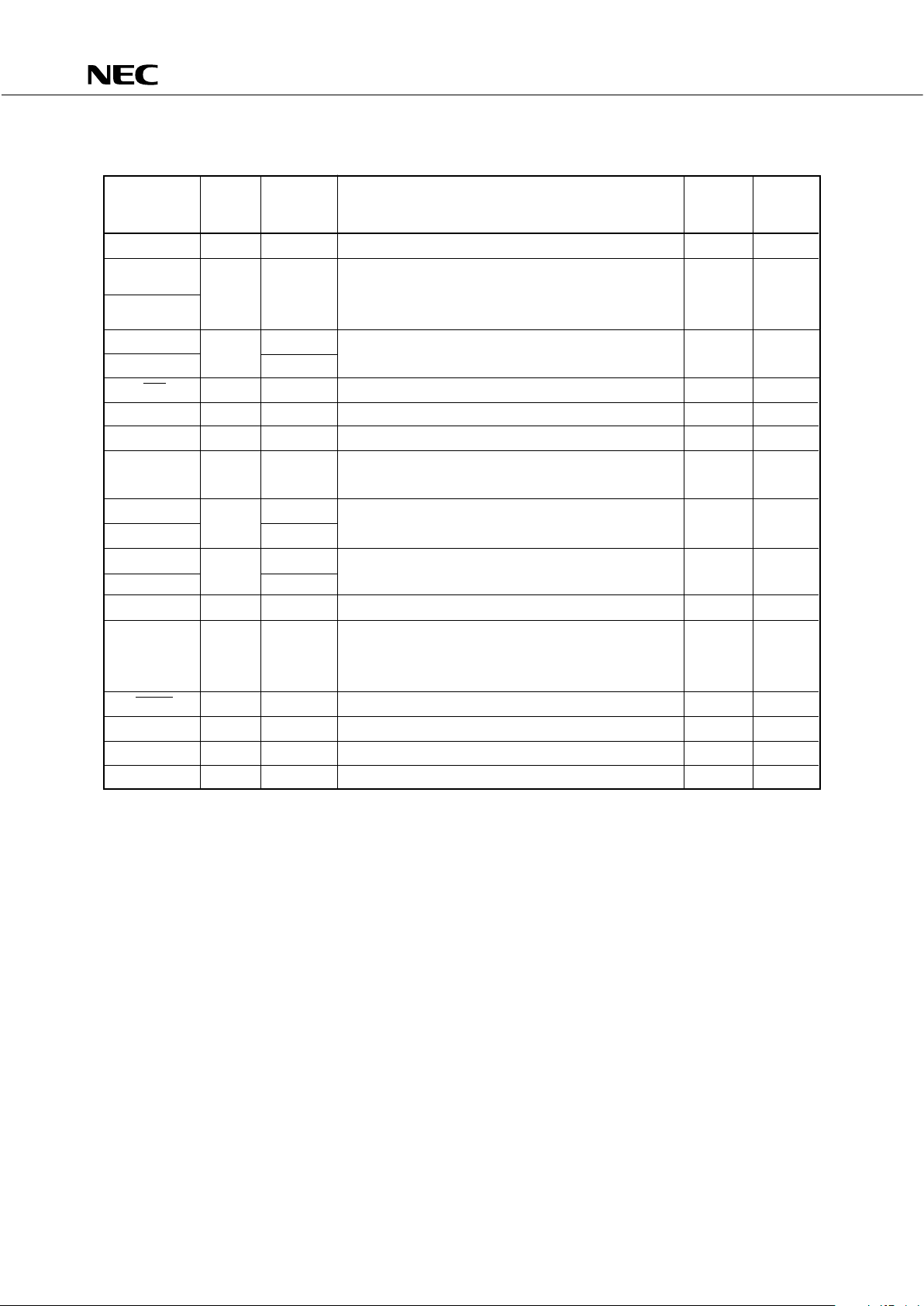

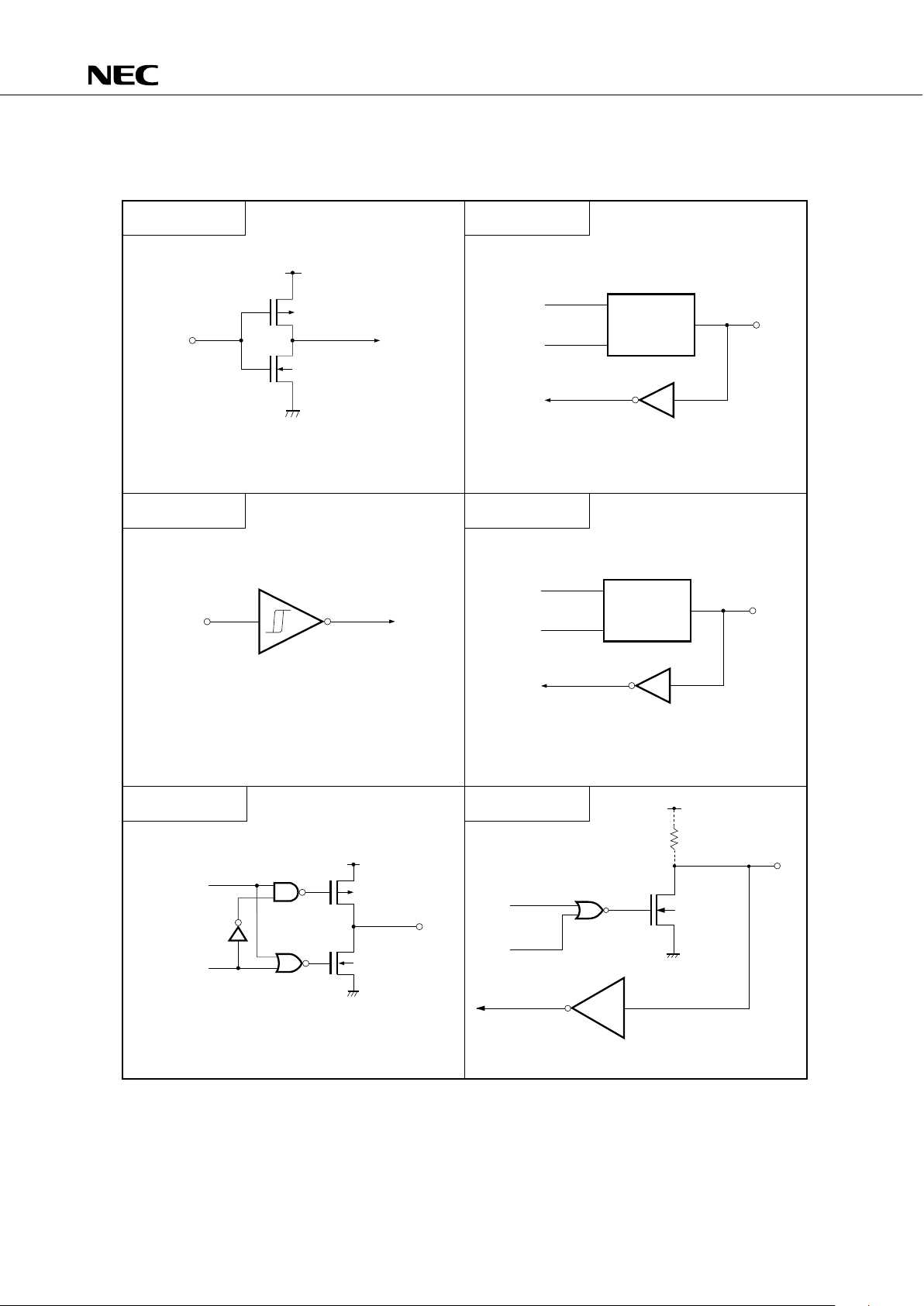

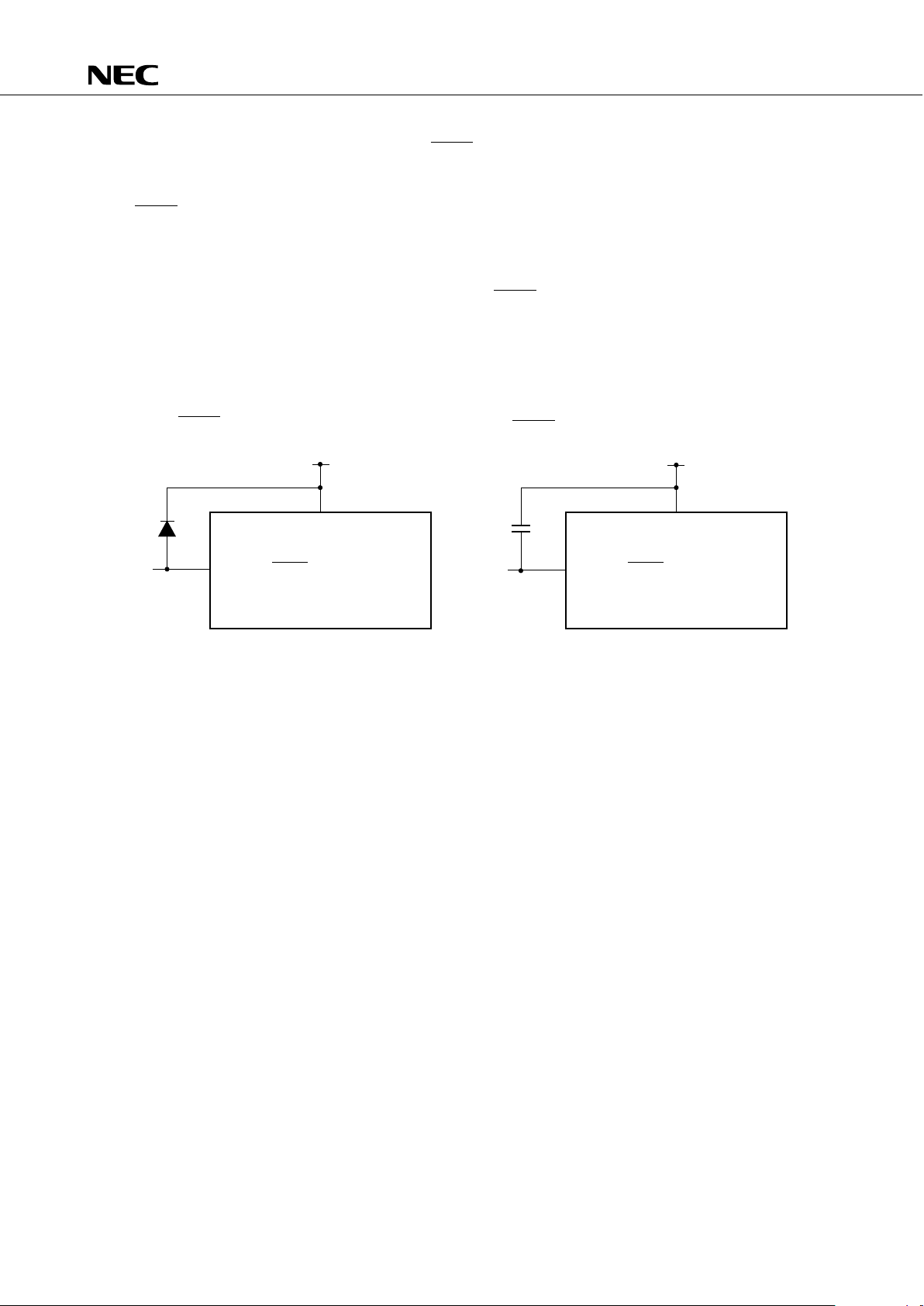

3.3 PIN INPUT/OUTPUT CIRCUITS

The following shows a simplified input/output circuit diagram for each pin of the

µ

PD75108.

TYPE A

TYPE E

TYPE B

TYPE F

IN

V

DD

Input buffer of CMOS standard

P–ch

N–ch

IN

Schmitt trigger input with hysteresis characteristics

data

output

disable

Type D

Type A

IN/OUT

TYPE D

TYPE M

data

output

disable

Type D

Type B

IN/OUT

data

output

disable

OUT

Push – pull output that can be set in a output

high– impedance state (both P –ch and N –ch are off)

V

DD

P-ch

N-ch

I/O circuit consisting of Type D push-pull output circuit

and Type A input buffer

I/O circuit consisting of Type D push-pull output and Type

B Schmitt trigger input

V

DD

P.U.R.

(mask option)

IN/OUT

data

output

disable

N-ch

(+12 V

withstand)

Medium-voltage input

buffer (+12 V withstand)

P.U.R.: Pull-Up Resistor

Page 12

µ

PD75104, 75106, 75108

12

TYPE N

IN +

–

Comparator

V (threshold voltage)

REF

3.4 RECOMMENDED PROCESSING OF UNUSED PINS

Pin Recommended connections

PTH00-PTH03

TI0 Connect to VSS or VDD

TI1

P00 Connect to VSS

P01-P03 Connect to VSS or VDD

P10-P13 Connect to VSS

P20-P23

P30-P33

P40-P43

P50-P53

P60-P63 Input: Connect to VSS or VDD

P70-P73

P80-P83 Output: Open

P90-P93

P120-P123

P130-P133

P140-P143

RESET*

1

Connect to VDD

NC*

2

Open

*1: Connect this pin to the VDD pin only when a power-ON reset circuit

is provided as a mask option.

2: Connect the NC pin to the V

DD pin when

µ

PD75P108 and a printed

circuit board are shared.

Page 13

µ

PD75104, 75106, 75108

13

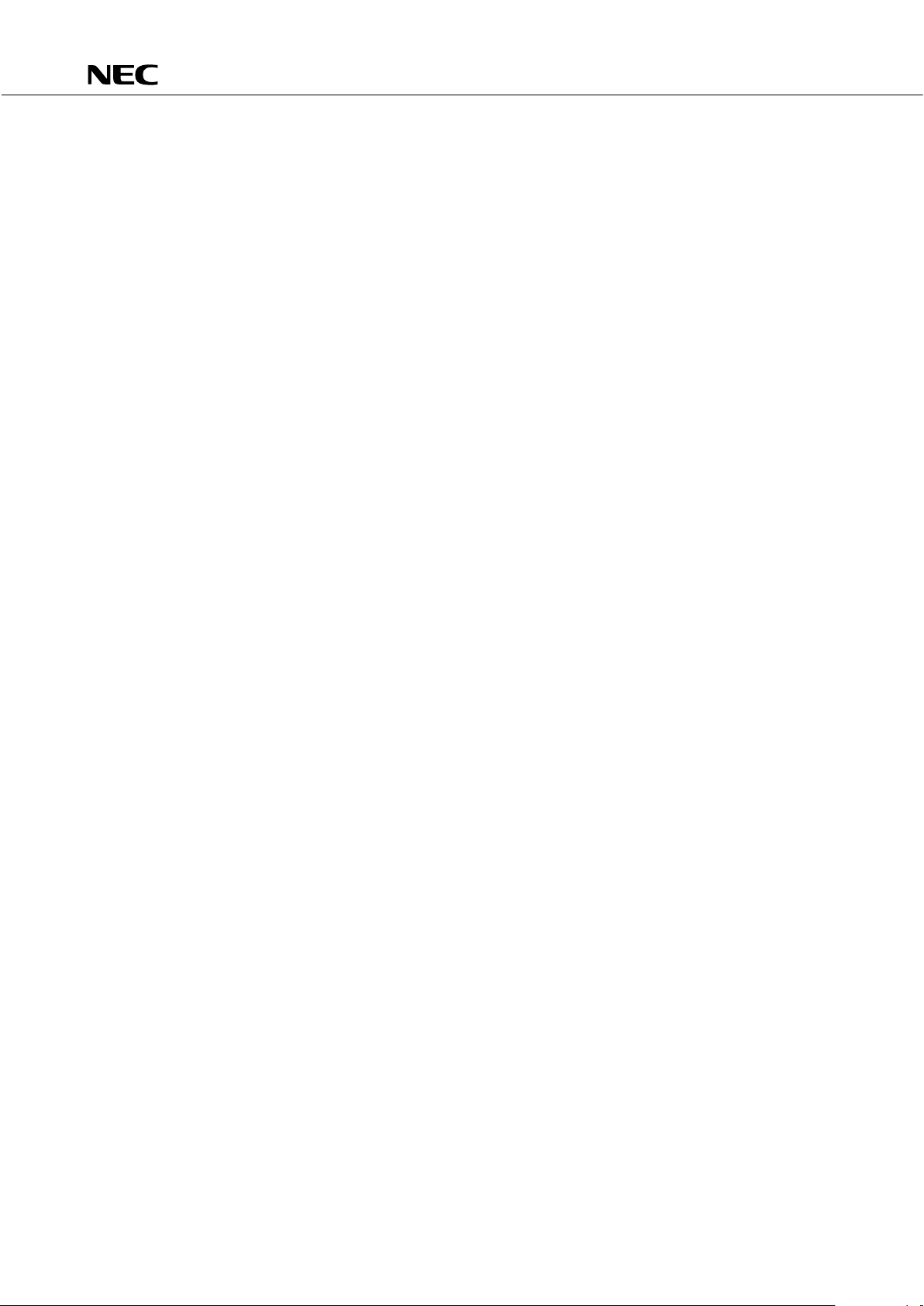

3.5 NOTES ON USING THE P00/INT4, AND RESET PINS

In addition to the functions described in Sections 3.1 and 3.2, an exclusive function for setting the test mode,

in which the internal fuctions of the

µ

PD75108 are tested (solely used for IC tests), is provided to the P00/INT4

and

RESET

pins.

If a voltage exceeding V

DD is applied to either of these pins, the

µ

PD75108 is put into test mode. Therefore,

even when the

µ

PD75108 is in normal operation, if noise exceeding the VDD is input into any of these pins, the

µ

PD75108 will enter the test mode, and this will cause problems for normal operation.

As an example, if the wiring to the P00/INT4 pin or the

RESET

pin is long, stray noise may be picked up

and the above montioned problem may occur.

Therefore, all wiring to these pins must be made short enough to not pick up stray noise. If noise cannot

be avoided, suppress the noise using a capacitor or diode as shown in the figure below.

• Connect a capacitor across P00/INT4 and

RESET

, and VDD.

• Connect a diode across P00/INT4 and

RESET

, and VDD.

VDD

VDD

P00/INT4, RESET

VDD

VDD

P00/INT4, RESET

Page 14

µ

PD75104, 75106, 75108

14

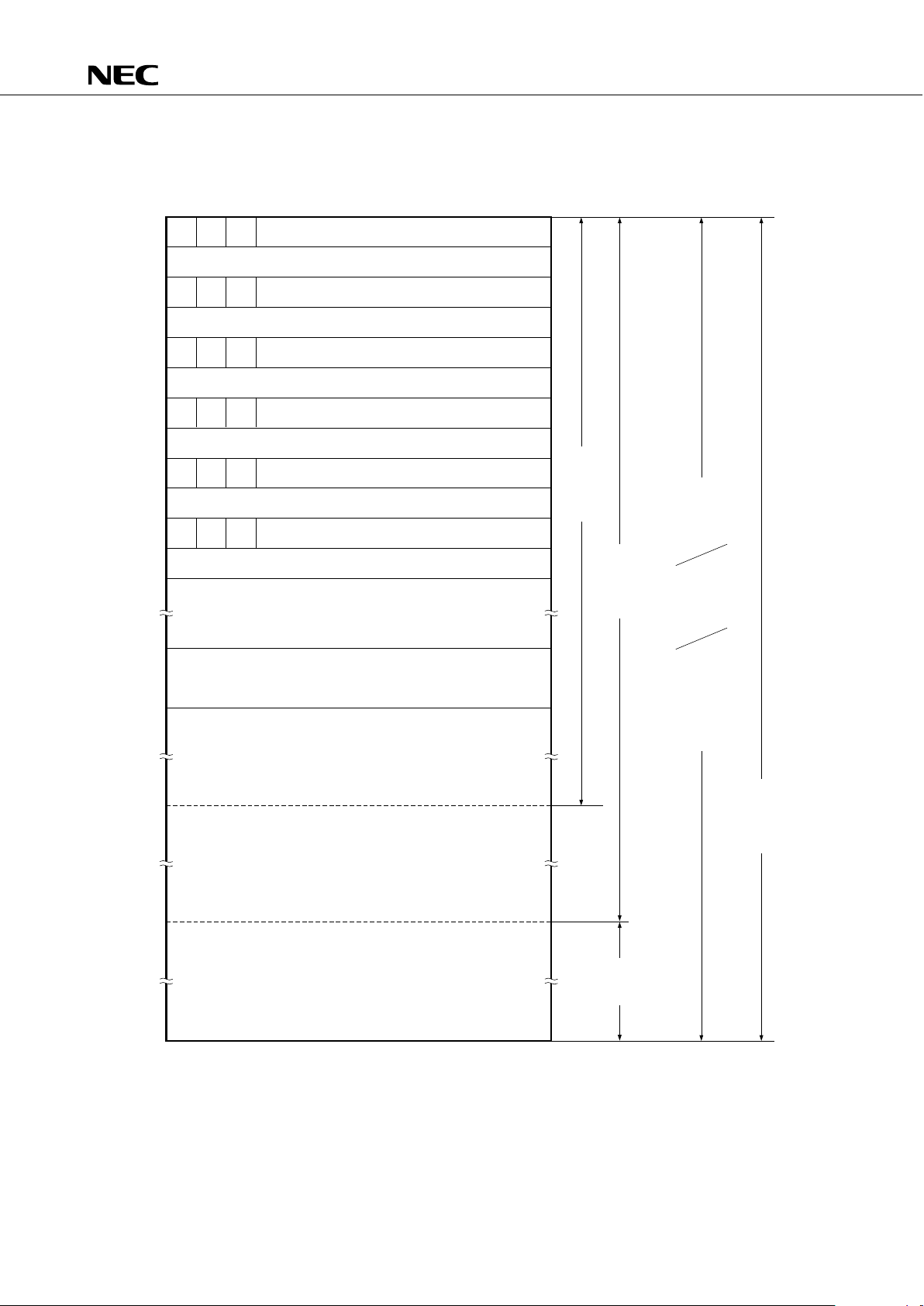

4. MEMORY CONFIGURATION

• Program memory (ROM) ... 8064 × 8 bits (0000H-1F7FH) : µPD75108

... 6016 × 8 bits (0000H-177FH) :

µ

PD75106

... 4096 × 8 bits (0000H-0FFFH) :

µ

PD75104

• 0000H, 0001H : Vector table to which address from which program is started is written after reset

• 0002H-000BH: Vector table to which address from which program is started is written after interrupt

• 0020H-007FH: Table area referenced by GETI instruction

• Data memory (RAM)

• Data area ....512 × 4 bits (000H–1FFH):

µ

PD75108

320 × 4 bits (000H-13FH) :

µ

PD75106, 75104

• Peripheral hardware area .... 128 × 4 bits (F80H–FFFH)

Page 15

µ

PD75104, 75106, 75108

15

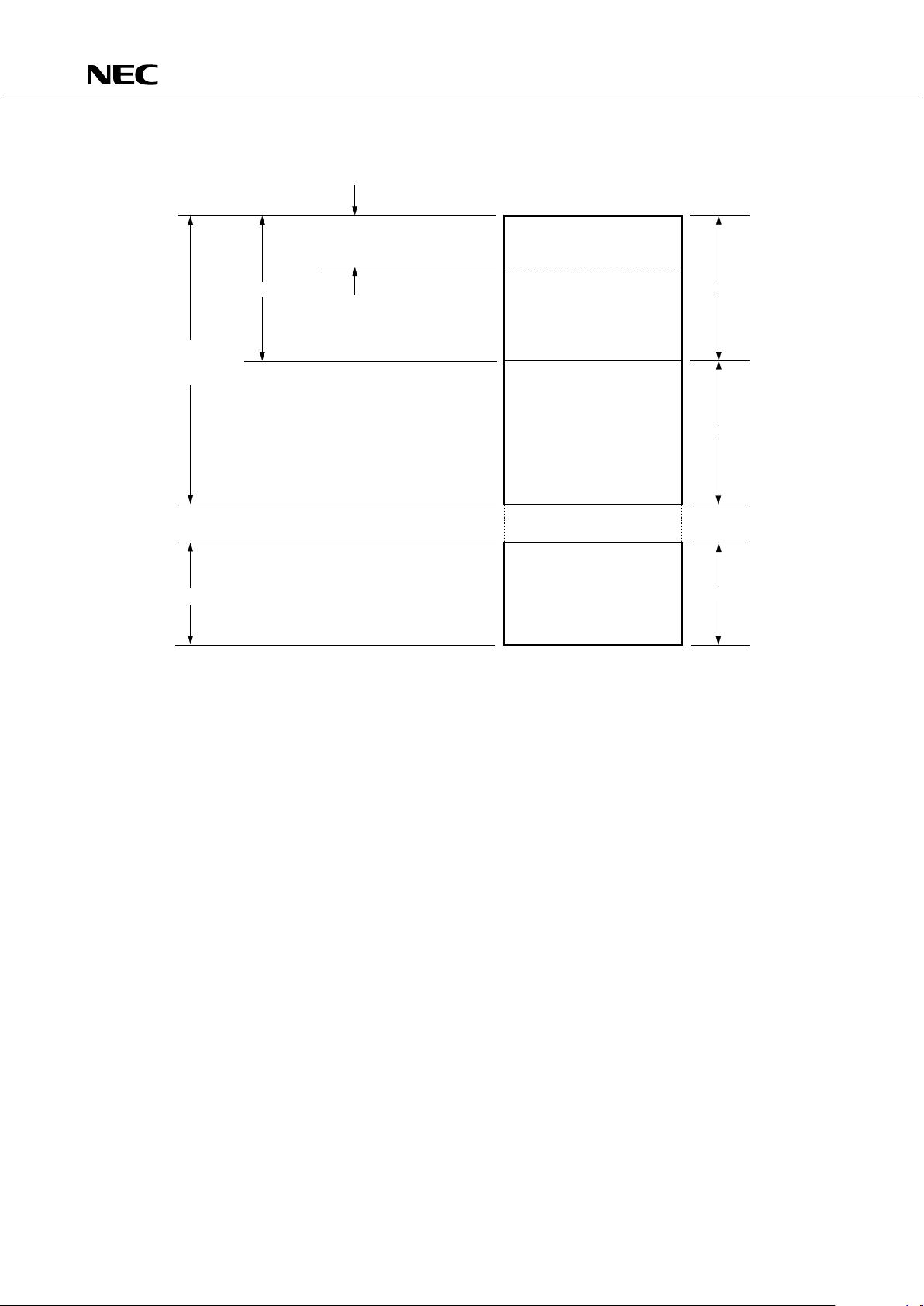

(a) µPD75108

765

MBE RBE 0

MBE RBE 0

MBE RBE 0

MBE RBE 0

MBE RBE 0

MBE RBE 0

Internal reset start address (upper 5 bits)

Internal reset start address (lower 8 bits)

INTBT/INT4 start address (upper 5 bits)

INTBT/INT4 start address (lower 8 bits)

INT0/INT1 start address (upper 5 bits)

INT0/INT1 start address (lower 8 bits)

INTSIO start address (upper 5 bits)

INTSIO start address (lower 8 bits)

INTT0 start address (upper 5 bits)

INTT0 start address (lower 8 bits)

INTT1 start address (upper 5 bits)

INTT1 start address (lower 8 bits)

0000H

0002H

0004H

0006H

0008H

000AH

0020H

007FH

0080H

07FFH

0800H

0FFFH

1000H

1F7FH

GETI instruction reference table

0

BRCB

! caddr

instruction

branch

address

CALLF

! faddr

instruction

entry

address

BR ! addr

instruction

branch address

CALL ! addr

instruction

subroutine

entry address

BR $addr

instruction

relational

branch address

(–15 to –1,

+2 to +16)

Branch destination

address and

subroutine entry

address for

GETI instruction

Address

BRCB ! caddr

instruction

branch address

Remarks: In addition to the above addresses, program can be branched to addresses specified by the PC

with the contents of its lower 8 bits changed by BR PCDE or BR PCXA instruction.

Fig. 4-1 Program Memory Map (1/3)

Page 16

µ

PD75104, 75106, 75108

16

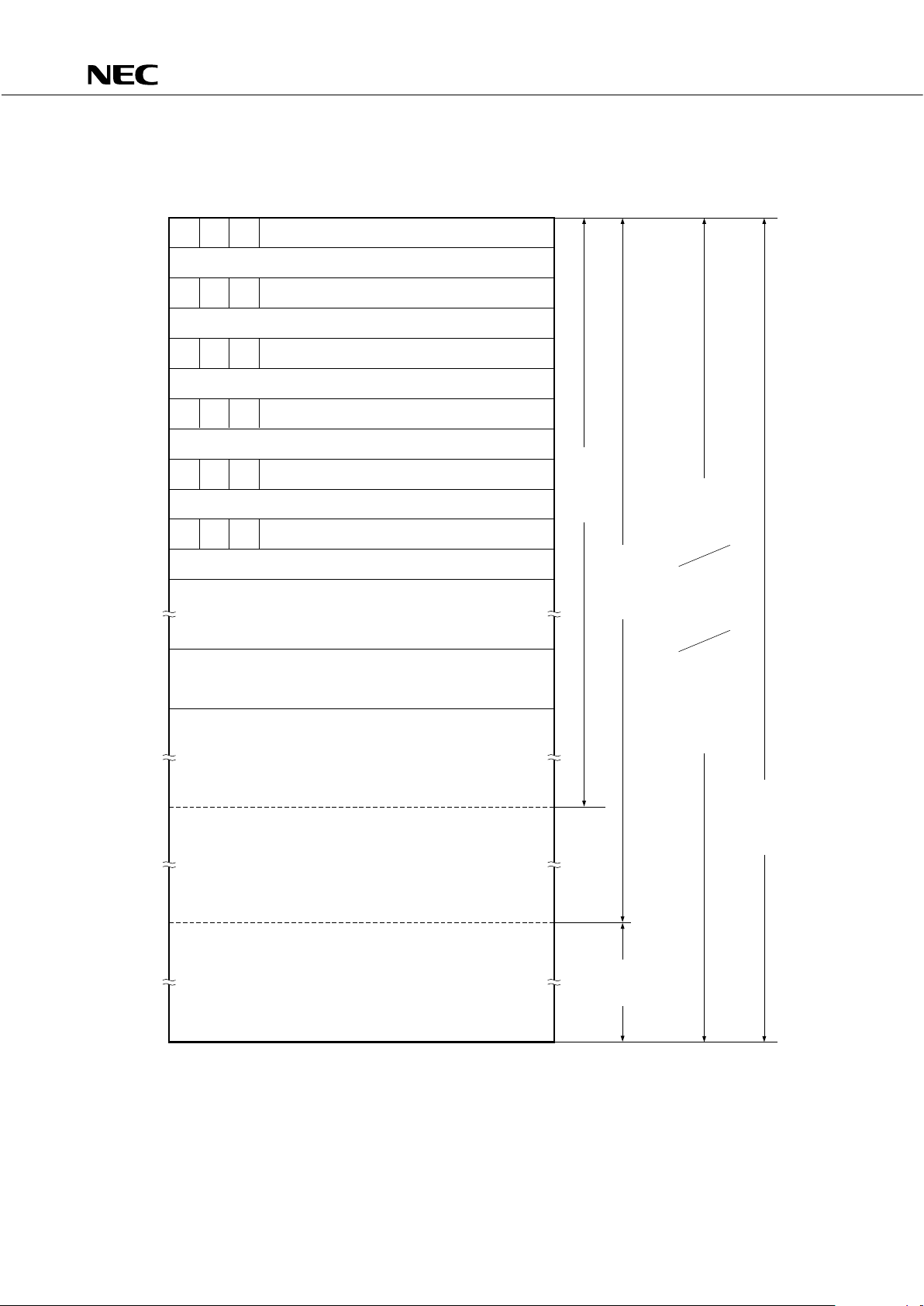

(b) µPD75106

Remarks: In addition to the above addresses, program can be branched to addresses specified by the PC

with the contents of its lower 8 bits changed by BR PCDE or BR PCXA instruction.

Fig. 4-1 Program Memory Map (2/3)

765

MBE RBE 0

MBE RBE 0

MBE RBE 0

MBE RBE 0

MBE RBE 0

MBE RBE 0

Internal reset start address (upper 5 bits)

Internal reset start address (lower 8 bits)

INTBT/INT4 start address (upper 5 bits)

INTBT/INT4 start address (lower 8 bits)

INT0/INT1 start address (upper 5 bits)

INT0/INT1 start address (lower 8 bits)

INTSIO start address (upper 5 bits)

INTSIO start address (lower 8 bits)

INTT0 start address (upper 5 bits)

INTT0 start address (lower 8 bits)

INTT1 start address (upper 5 bits)

INTT1 start address (lower 8 bits)

0000H

0002H

0004H

0006H

0008H

000AH

0020H

007FH

0080H

07FFH

0800H

0FFFH

1000H

177FH

GETI instruction reference table

0

BRCB

! caddr

instruction

branch

address

CALLF

! faddr

instruction

entry

address

BR ! addr

instruction

branch address

CALL ! addr

instruction

subroutine

entry address

BR $addr

instruction

relational

branch address

(–15 to +16)

Branch destination

address and

subroutine entry

address for

GETI instruction

Address

BRCB ! caddr

instruction

branch address

Page 17

µ

PD75104, 75106, 75108

17

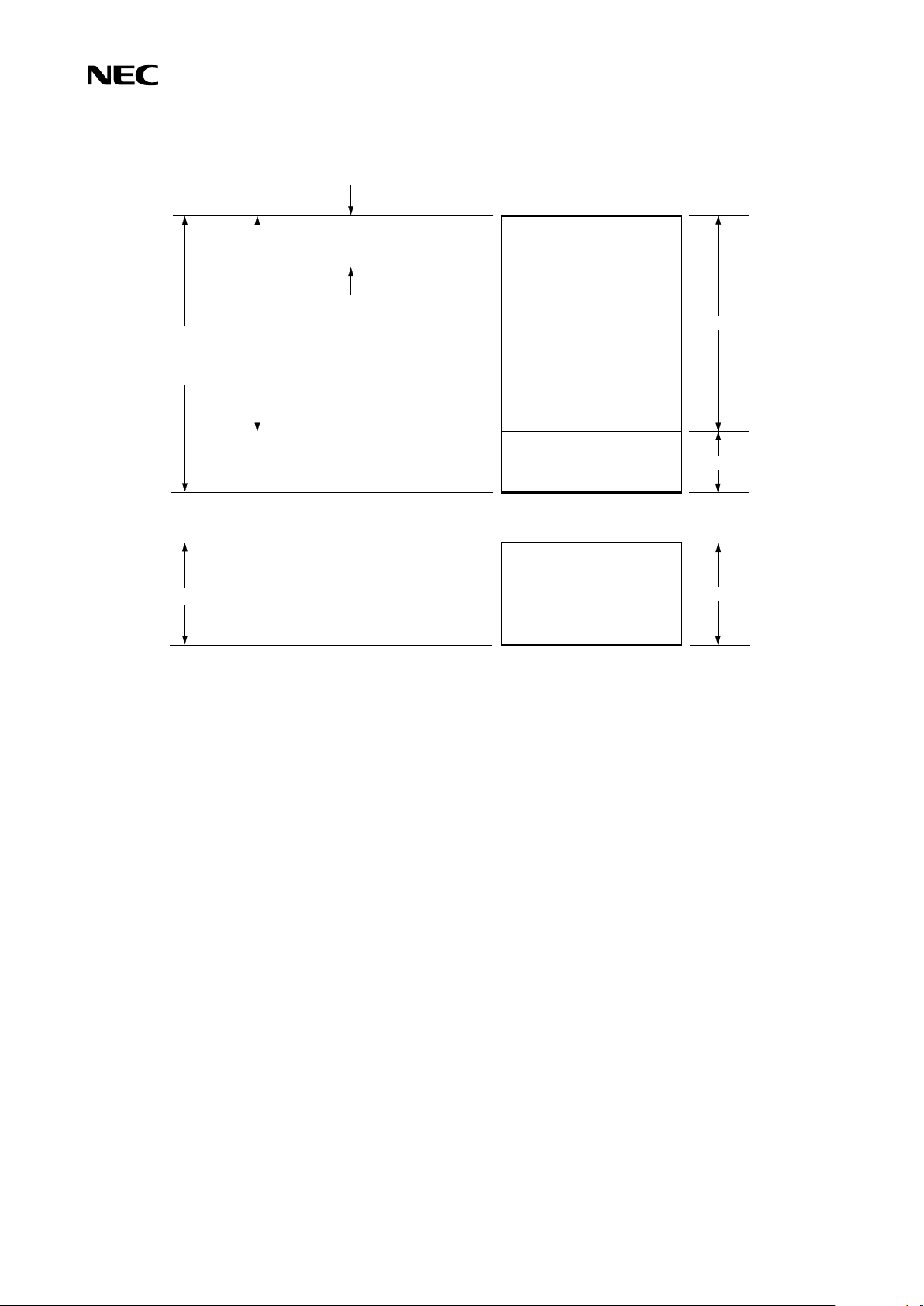

(c) µPD75106

765

MBE RBE 0

MBE RBE 0

MBE RBE 0

MBE RBE 0

MBE RBE 0

MBE RBE 0

Internal reset start address (upper 4 bits)

Internal reset start address (lower 8 bits)

INTBT/INT4 start address (upper 4 bits)

INTBT/INT4 start address (lower 8 bits)

INT0/INT1 start address (upper 4 bits)

INT0/INT1 start address (lower 8 bits)

INTSIO start address (upper 4 bits)

INTSIO start address (lower 8 bits)

INTT0 start address (upper 4 bits)

INTT0 start address (lower 8 bits)

INTT1 start address (upper 4 bits)

INTT1 start address (lower 8 bits)

000H

002H

004H

006H

008H

00AH

020H

07FH

080H

7FFH

800H

FFFH

GETI instruction reference table

0

CALLF

! faddr

instruction

entry

address

BRCB ! caddr

instruction

branch address

CALL ! addr

instruction

subroutine

entry address

Address

4

0

0

0

0

0

0

BR $addr

instruction

relational

branch address

(–15 to +16)

Branch destination

address and

subroutine entry

address for

GETI instruction

Remarks: In addition to the above addresses, program can be branched to addresses specified by the PC

with the contents of its lower 8 bits changed by BR PCDE or BR PCXA instruction.

Fig. 4-1 Program Memory Map (3/3)

Page 18

µ

PD75104, 75106, 75108

18

(a) µPD75108

000H

01FH

0FFH

100H

1FFH

F80H

FFFH

Data memory

Memory bank

(32 × 4)

256× 4

Not provided

128× 4

Bank 0

General-purpose

register area

Stack area

Data memory

Static RAM

(512× 4)

Peripheral hardware area

256× 4 Bank 1

Bank 15

Fig. 4-2 Data Memory Map(1/2)

Page 19

µ

PD75104, 75106, 75108

19

(b) µPD75106, 75104

000H

01FH

0FFH

100H

13FH

F80H

FFFH

Data memory

Memory bank

(32 × 4)

256× 4

Not provided

128× 4

Bank 0

General-purpose

register area

Stack area

General-

purpose

Static RAM

(320× 4)

Peripheral hardware area

64

× 4

Bank 1

Bank 15

Fig. 4-2 Data Memory Map(2/2)

Page 20

µ

PD75104, 75106, 75108

20

5. PERIPHERAL HARDWARE FUNCTIONS

5.1 PORTS

I/O ports are classified into the following 3 kinds:

• CMOS input (PORT0, 1) : 8

• CMOS input/output (PORT2, 3, 4, 5, 6, 7, 8, 9): 32

•

N-ch open-drain input/output (PORT12, 13, 14) :12

Total : 52

PORT0

PORT1

PORT3

PORT6

PORT2

PORT4

PORT5

PORT7

PORT8

PORT9

PORT12

PORT13

PORT14

Function

4-bit input

4-bit I/O*

4-bit I/O*

(N-ch open- drain.

12V)

Table 5-1 Port Function

Operation and Features

Can always be read or tested regardless of operation mode of shared pin

Can be set in input or output mode bitwise

Can be set in input or output mode in units of 4 bits.

Ports 4 and 5, 6 and 7, 8 and 9 can be used in pairs

to input or output 8-bit data

Can be set in input or output mode in units of 4 bits.

Ports 12 and 13 can be used in pairs to input or

output 8-bit data

Port

(Symbol)

Remarks

Shared with SI, SO, SCK, and

INT0 to 4 pins

—

Port 2 pins are shared with

PTO0, PTO1, and PCL pins

Each bit can be connected to

pull-up resistor by mask option

*: Can directly drive LED.

Page 21

µ

PD75104, 75106, 75108

21

5.2 CLOCK GENERATOR CIRCUIT

The clock generator circuit generates clocks to control CPU operation modes by supplying clocks to the CPU and

peripheral hardware. In addition, this circuit can change the instruction execution time.

• 0.95

µ

s/1.91 µs/15.3 µs (operating at 4.19 MHz)

· Basic interval timer (BT)

· Clock output circuit

· Timer/event counter

· Serial interface

f or

XX

f

X

1/2 1/16

1/8 to 1/4096

Frequency civider

X1

X2

System clock

generator

circuit

Oscillation

stops

Selector

1/4

Frequency

divider

· CPU

· Clock output

circuit

HALT F/F

S

RQ

PCC

PCC0

PCC1

PCC2

PCC3

4

Internal bus

HALT*

STOP*

Clears

PCC2,

PCC3

STOP F/F

Q

S

R

Wait release signal from BT

RES (internal reset) signal

Standby release signal from

interrupt control circuit

Φ

*: Execution of the instruction

Remarks 1: f

XX= Crystal/ceramic oscillator

2: f

X = External clock frequency

3: PCC: Processor clock control register

4: One clock cycle (t

CY) of Φ is one machine cycle of an instruction. For tCY, refer to AC

characteristics in 12. ELECTRICAL SPECIFICATIONS.

Fig. 5-1 Clock Generator Block Diagram

★

Page 22

µ

PD75104, 75106, 75108

22

5.3 CLOCK OUTPUT CIRCUIT

The clock output circuit outputs clock pulse from the P22/PCL pin. This clock output circuit is used to output

clock pulses to the remote control output, peripheral LSIs, etc.

• Clock output (PCL) : Φ, 524, 262 kHz (operating at 4.19 MHz)

Selector

Output

buffer

PCL/P22

Bit 2 of PMGBPORT2.2

Port 2 input/

output mode

specification

bit

P22 output

latch

Internal bus

CLOM3 CLOM2 CLOM1 CLOM0 CLOM

4

Φ

f

X

/2

3

fX/2

4

From the

clock

generator

X

X

Fig. 5-2 Clock Output Circuit Configuration

Page 23

µ

PD75104, 75106, 75108

23

5.4 BASIC INTERVAL TIMER

The basic interval timer has these functions:

• Interval timer operation which generates a reference time interrupt

• Watchdog timer application which detects a program runaway

• Selects the wait time for releasing the standby mode and counts the wait time

• Reads out the count value

Remarks

: *: Instruction execution

Fig. 5-3 Basic Interval Timer Configuration

From the

clock generator

f

X

/2

5

fX/2

7

fX/2

9

fX/2

12

MPX

Clear

Basic interval timer

(8-bit frequency divider circuit)

3

4

8

BT

Clear

Set

signal

BT

interrupt

request flag

IRQBT

Wait release signal

for standby release

Vector

interrupt

request

signal

Internal bus

BTM3 BTM2 BTM1 BTM0 BTM

SET1*

X

X

X

X

5.5 TIMER/EVENT COUNTER

µ

PD75108 contains two channels of timer/event counters.

These two channels are almost identical in terms of configuration and function except the count pulse (CP) that

can be selected and the function to supply clocks to the serial interface.

The functions of the timer/event counter include:

• Programmable interval timer operation

• Output of square wave at an arbitrary frequency to PTOn pin

• Event counter operation

• Input of TIn pin signal as external interrupt input signal

• Dividing TIn pin input by N to output to PTOn pin (frequency divider operation)

• Supply of serial shift clock to serial interface circuit (channel 0 only)

• Reading counting status

Page 24

µ

PD75104, 75106, 75108

24

Internal bus

888

Modulo register (8)TMn7 TMn6 TMn5 TMn4 TMn3 TMn2 TMn1 TMn0

TIn

Input buffer

TIn

MPX

CP

From

clock

generator

circuit

Timer operation start

SET1*

TMn TMODn

Tn

Clear

RES

Remarks:

Comparator (8)

Count register (8)

TOUT

F/F

Coincidence

TOFn

To

selector

TMn1 TMn0

Edge

detector

circuit

To

enable

flag

P2n

output

latch

Port 2

I/O

mode

TOEn TOn PORT2.n Bit 2 of PGMB

To serial

interface

(channel 0 only)

P2n/PTOn

Output

buffer

IRQTn set

signal

IRQTn clear

signal

Fig. 5-4 Timer/Event Counter Block Diagram (n = 0, 1)

* indicates the instruction execution.

8

8

Page 25

µ

PD75104, 75106, 75108

25

5.6 SERIAL INTERFACE

The

µ

PD75108 is equipped with clock 8-bit serial interface that operates in the following two modes:

• Operation stop mode

• Three-line serial I/O mode

Page 26

µ

PD75104, 75106, 75108

26

Internal bus

8

8

8

P03/SI

P02/SO

P01/SCK

SIO0

Shift register (8)

SIO7

SIO

QS

R

Clear

Serial clock

counter (3)

Overflow

MPX

*: "SET1" indicates execution of the instruction.

Φ

f /2

XX

4

f /2

XX

10

TOF0 (from timer channel 0)

Serial start

SIOM7 SIOM6 SIOM5 SIOM4 SIOM3 SIOM2 SIOM1 SIOM0

SET1*

SIOM

IRQSIO

set signal

IRQSIO

clear signal

Fig. 5-5 Serial Interface Block Diagram

Page 27

µ

PD75104, 75106, 75108

27

5.7 PROGRAMMABLE THRESHOLD PORT (ANALOG INPUT PORT)

µ

PD75108 is equipped with a 4-bit analog input port (consisting of PTH00 to PTH03 pins) whose threshold voltage

is programmable.

This programmable threshold port is configured as shown in Figure 5-6.

The threshold voltage (V

REF) can be changed in 16 steps (VDD × 0.5/16 – VDD × 15.5/16), and analog signals can be

directly input.

When V

REF is set to VDD × 7.5/16, the programmable threshold port can also be used as a digital signal input port.

Input buffer

PTH00

PTH01

PTH02

PTH03

+

–

+

–

+

–

+

–

V

DD

Internal bus

Programmable threshold port

input latch (4)

Operates

/stops

PTH0

8

4

MPX

PTHM7

PTHM6

PTHM5

PTHM4

PTHM3

PTHM2

PTHM1

PTHM0

PTHM

1

2

R

1

2

R

R

R

V

REF

Fig. 5-6 Programmable Threshold Port Configuration

Page 28

µ

PD75104, 75106, 75108

28

5.8 BIT SEQUENTIAL BUFFER .... 16 BITS

The bit sequential buffer is a data memory specifically provided for bit manipulation. With this buffer,

addresses and bit specifications can be sequentially up-dated in bit manipulation operation. Therefore, this

buffer is very useful for processing long data in bit units.

Remarks:

For the pmem.@L addressing, the specification bit is shifted according to the L register.

Fig. 5-7 Bit Sequential Buffer Format

5.9 POWER-ON FLAG (MASK OPTION)

The power-ON flag (PONF) is set to only when the power-ON reset circuit operates and power-ON reset signal

has been generated (see Fig. 8-1).

The PONF flag is mapped at bit 0 of memory space address FD1H, and can be manipulated by a bit manipulation

instruction. However, it cannot be set by the SET1 instruction.

6. INTERRUPT FUNCTIONS

The µPD75108 has 7 different interrupt sources and can perform multiplexed interrupt processing with

priority assigned.

In addition to that, the

µ

PD75108 is also provided with two types of edge detection testable inputs.

The interrupt control circuit of the

µ

PD75108 has these functions:

• Hardware controlled vector interrupt function which can control whether or not to accept an interrupt by

using the interrupt enable flag (IExxx) and interrupt master enable flag (IME).

• The interrupt start address can be arbitrarily set.

• Multiplexed interrupt function that can specify priority by the interrupt priority selector register (IPS).

• Interrupt request flag (IRQxxx) test function (an interrupt generation can be confirmed by means of

software).

• Standby mode release (Interrupts to be released can be selected by the interrupt enable flag).

Address bit

Symbol

L register

3210321032103210

L = F L = C L = B L = 8 L = 7 L = 4 L = 3 L = 0

BSB3 BSB2 BSB1 BSB0

DECS L

INCS L

FC3H FC2H FC1H FC0H

Page 29

µ

PD75104, 75106, 75108

29

Internal bus

22

IM1 IM0

IRQBT

INT4

/P00

INT0

/P10

INT1

/P11

INT2

/P12

INT

BT

INTSIO

INTT0

Both edge

detection

circuit

Edge

detection

circuit

Edge

detection

circuit

Rising edge

detection

circuit

Falling edge

detection

circuit

IRQ4

IRQ0

IRQ1

IRQSIO

IRQT0

IRQT1

IRQ2

Interrupt enable flag (IE )×××

IME

Decoder

IST

Priority control

circuit

Vector table

address

generator

Standby

release signal

Fig. 6-1 Interrupt Control Block Diagram

9

IRQ3

IPS

24

INTT1

INT3

/P13

Interrupt

request flag

Page 30

µ

PD75104, 75106, 75108

30

7. STANDBY FUNCTIONS

The µPD75108 has two different standby modes (STOP mode and HALT mode) to reduce the power

consumption of the microcomputer chip while waiting for program execution.

Table 7-1 Each Status in Standby Mode

Setting Instruction STOP instruction HALT instruction

Clock Generator

circuit

Basic Interval

Timer

Operates (sets IRQBT at reference

time intervals)

Operates only when input of external

SCK or output of TO0 is selected as

serial clock (where external TI0 is input

to timer/event counter 0)

Operates when serial clock other

than Φ is specified

Operates

Stops

Serial Interface

Clock output

STOP Mode

HALT Mode

Clock oscillation stops Only CPU clock Φ is stopped

Operation

Status

Timer/Event

Counter

circuit

Operates only when TIn pin input

signal is specified as count clock

Operates when clock other than CPU

clock Φ is used

Stops

CPU Stops

Release Signal Interrupt request signal enabled by interrupt enable flag, or RESET input

Stops

Page 31

µ

PD75104, 75106, 75108

31

8. RESET FUNCTION

The reset (

RES

) signal generator circuit is configured as shown in Figure 8-1.

RESET

SWB

SWA

Power-ON

reset

generator

circuit

Internal reset signal

(RES)

Power-ON

flag (PONF)

Execution of bit

manipulation

instruction*

Internal bus

*: PONF cannot be set to 1 by SET1 instruction.

Fig. 8-1 Reset Signal Generator Circuit

The Power-ON reset generator circuit generates an internal reset signal when the supply voltage rises. This pulse

can be used in three ways by specifying a mask option through SWA and SWB shown in Fig. 8-1. (Refer to 11. MASK

OPTION SELECTION.)

The reset operations performed by the Power-On reset circuit and the RESET input signal are illustrated in Figs.

8-2 and 8-3, respectively.

Supply voltage

0 V

Internal reset signal

(RES)

Wait*

(approx. 31.3 ms: 4.19 MHz)

HALT mode Operation mode

Internal reset operation

*: The wait time does not include the time required after the

RES

signal has been generated until the

oscillation starts.

Fig. 8-2 Reset by Power-ON Reset Circuit

Page 32

µ

PD75104, 75106, 75108

32

Wait*

(31.3 ms: 4.19 MHz)

HALT mode Operation mode

Operation mode

or standby mode

RESET input

Internal reset operation

*: The wait time does not include the time required after the

RES

signal has been generated until the

oscillation starts.

Fig. 8-3 Reset by RESET Signal

The status of each internal hardware device after the reset operation has been performed is shown in Table 8-

1.

Page 33

µ

PD75104, 75106, 75108

33

Table 8-1 Hardware Device Status After Reset

RESET input during Power-ON Reset or RESET

standby mode Input during Operation

Lower 4 bits of program Lower 4 bits of program

memory address 000H are memory address 000H are

Program Counter (PC) set to PC12-8,*1 and set to PC12-8,*1 and

contents of address 001H contents of address 001H

are set to PC7-0. are set to PC7-0.

Carry Flag (CY) Retained Undefined

Skip Flags (SK0-SK2) 0 0

PSW Interrupt Status Flags (IST0, 1) 0 0

Bit 6 of program memory Bit 6 of program memory

Bank Enable Flags (MBE, RBE)

address 000H is set in address 000H is set in

RBE, and bit 7 is set in RBE, and bit 7 is set in

MBE. MBE.

Stack Pointer (SP) Undefined Undefined

Data Memory (RAM) Retained*

2

Undefined

General-Purpose Registers (X,A,H,L,D,E,B,C) Retained Undefined

Bank Selector Registers (MBS, RBS) 0, 0 0, 0

Counter (BT) Undefined Undefined

Mode Register (BTM) 0 0

Counter (Tn) 0 0

Modulo Register (TMODn) FFH FFH

Mode Register (TMn) 0 0

TOEn, TOFn 0, 0 0, 0

Serial Interface

Shift Register (SIO) Retained Undefined

Mode Register (SIOM) 0 0

Processor Clock Control Register 0 0

(PCC)

Clock Output Mode Register 0 0

(CLOM)

Interrupt Request Rlags Reset (0) Reset (0)

(IRQxxx)

Interrupt Enable Flags (IExxx) 0 0

Interrupt

Priority Selector Register (IPS) 0 0

INT0, 1 Mode Registers 0, 0 0, 0

(IM0, IM1)

Output Buffer OFF OFF

Digital Port

Output Latch Cleared (0) Cleared (0)

I/O Mode Registers 0 0

(PMGA, PMGB, PMGC)

PTH00-PTH03 Input Latches Undefined Undefined

Analog Port

Mode Register (PTHM) 0 0

Power-ON Flag (PONF) Retained 1 or undefined*

2

Bit Sequential Buffer (BSB0-BSB3) 0 0

*1: PC11-8 for µPD75104

2: Power-ON reset: 1

RESET

input during operation: undefined

Note: Data at data memory addresses 0F8H to 0FDH become undefined when the

RESET

signal has been input.

Hardware

Basic interval timer

Timer/Event Counter

(n = 0, 1)

Clock Generator Circuit,

Clock Output Circuit

Page 34

µ

PD75104, 75106, 75108

34

9. INSTRUCTION SET

(1) Operand representation and description

Describe one or more operands in the operand field of each instruction according to the operand

representation and description methods of the instruction (for details, refer to RA75X Assembler Package

User's Manual - Language (EEU-730)). With some instructions, only one operand should be selected from

several operands. The uppercase characters, +, and – are keywords and must be described as is.

Describe an appropriate numeric value or label as immediate data.

The symbols in the register and flag symbols can be described as labels in the places of mem, fmem,

pmem, and bit (for details, refer to

µ

PD751XX Series User‘s Manual (IEM-922)). However, fmem and pmem

restricts the label that can be described.

Representation Description

reg X, A, B, C, D, E, H, L

reg1 X, B, C, D, E, H, L

rp XA, BC, DE, HL

rp1 BC, DE, HL

rp2 BC, DE

rp' XA, BC, DE, HL, XA', BC', DE', HL'

rp'1 BC, DE, HL, XA', BC', DE', HL'

rpa HL, HL+, HL–, DE, DL

rpa1 DE, DL

n4 4-bit immediate data or label

n8 8-bit immediate data or label

mem 8-bit immediate data or label*

bit 2-bit immediate data or label

fmem FB0H to FBFH,FF0H to FFFH immediate data or label

pmem FC0H to FFFH immediate data or label

µ

PD75104 0000H to 0FFFH immediate data or label

addr

µ

PD75106 0000H to 177FH immediate data or label

µ

PD75108 0000H to 1F7FH immediate data or label

caddr 12-bit immediate data or label

faddr 11-bit immediate data or label

taddr 20H to 7FH immediate data (where bit0 = 0) or label

PORTn PORT0 - PORT9, PORT12 - PORT14

IExxx IEBT, IESIO, IET0, IET1, IE0 - IE4

RBn RB0 - RB3

MBn MB0, MB1, MB15

*: Only even address can be described as mem for 8-bit data processing.

Page 35

µ

PD75104, 75106, 75108

35

(2) Legend of operation field

A : A register; 4-bit accumulator

B : B register; 4-bit accumulator

C : C register; 4-bit accumulator

D : D register; 4-bit accumulator

E : E register; 4-bit accumulator

H : H register; 4-bit accumulator

L : L register; 4-bit accumulator

X : X register; 4-bit accumulator

XA : Register pair (XA); 8-bit accumulator

BC : Register pair (BC); 8-bit accumulator

DE : Register pair (DE); 8-bit accumulator

HL : Register pair (HL); 8-bit accumulator

XA' : Expansion register pair (XA')

BC' : Expansion register pair (BC')

DE' : Expansion register pair (DE')

HL' : Expansion register pair (HL')

PC : Program counter

SP : Stack pointer

CY : Carry flag; or bit accumulator

PSW : Program status word

MBE : Memory bank enable flag

RBE : Register bank enable flag

PORTn : Port n (n = 0 - 9, 12 - 14)

IME : Interrupt mask enable flag

IPS : Interrupt priority selection register

IExxx : Interrupt enable flag

RBS : Register bank selection register

MBS : Memory bank selection register

PCC : Processor clock control register

.

: Delimiter of address and bit

(xx) : Contents addressed by xx

xxH : Hexadecimal data

Page 36

µ

PD75104, 75106, 75108

36

(4) Machine cycle field

In this field, S indicates the number of machine cycles required when an instruction having a skip

function skips. The value of S varies as follows:

• When no instruction is skipped ........................................................................ S = 0

• When 1-byte or 2-byte instruction is skipped................................................. S = 1

• When 3-byte instruction (BR ! adder or CALL ! adder) is skipped .............. S = 2

Note

: The GETI instruction is skipped in one machine cycle.

One machine cycle equals to one cycle of the CPU clock Φ, (= tCY), and can be changed in three steps

depending on the setting of the processor clock control register (PCC).

(3) Symbols in addressing area field

*1 MB = MBE . MBS

(MBS = 0, 1, 15)

*2 MB = 0

*3 MBE = 0 : MB = 0 (00H-7FH) Data memory

MB = 15 (80H-FFH) addressing

MBE = 1 : MB = MBS (MBS = 0, 1, 15)

*4 MB = 15, fmem = FB0H-FBFH,

FF0H-FFFH

*5 MB = 15, pmem = FC0H-FFFH

*6

µ

PD75104 addr = 0000H-0FFFH

µ

PD75106 addr = 0000H-177FH

µ

PD75108 addr = 0000H-1F7FH

*7 addr = (Current PC) – 15 to (Current PC) – 1

(Current PC) + 2 to (Current PC) + 16 Program memory

*8

µ

PD75104 caddr = 0000H-0FFFH (PC11 = 0) addressing

µ

PD75106 caddr = 0000H-0FFFH (PC12 = 0) or 1000H-177FH (PC12 = 1)

µ

PD75108 caddr = 0000H-0FFFH (PC12 = 0) or 1000H-1F7FH (PC12 = 1)

*9 faddr = 000H-7FFH

*10 taddr = 020H-07FH

Remarks • MB indicates memory bank that can be accessed.

• In *2, MB = 0 regardless of MBE and MBS.

• In *4 and *5, MB = 15 regardless of MBE and MBS.

• *6 to *10 indicate areas that can be addressed.

Page 37

µ

PD75104, 75106, 75108

37

Ma-

Instruc- Mne-

Operand Bytes

chine

Operation

Addressing Skip

tions monics Cyc- Area Conditions

les

Transfer MOV A, #n4 1 1 A ← n4 String effect A

reg1, #n4 2 2 reg1 ← n4

XA, #n8 2 2 XA ← n8 String effect A

HL, #n8 2 2 HL ← n8 String effect B

rp2, #n8 2 2 rp2 ← n8

A, @HL 1 1 A ← (HL) *1

A, @HL+ 1 2+S A ← (HL), then L ← L+1 *1 L = 0

A, @HL– 1 2+S A ← (HL), then L ← L–1 *1 L = FH

A, @rpa1 1 1 A ← (rpa1) *2

XA, @HL 2 2 XA ← (HL) *1

@HL, A 1 1 (HL) ← A*1

@HL, XA 2 2 (HL) ← XA *1

A,mem 2 2 A ← (mem) *3

XA, mem 2 2 XA ← (mem) *3

mem, A 2 2 (mem) ← A*3

mem, XA 2 2 (mem) ← XA *3

A, reg 2 2 A ← reg

XA, rp' 2 2 XA ← rp'

reg1, A 2 2 reg1 ← A

rp'1, XA 2 2 rp'1 ← XA

XCH A, @HL 1 1 A ↔ (HL) *1

A, @HL+ 1 2+S A ↔ (HL), then L ← L+1 *1 L = 0

A, @HL– 1 2+S A ↔ (HL), then L ← L–1 *1 L = FH

A, @rpa1 1 1 A ↔ (rpa1) *2

XA, @HL 2 2 XA ↔ (HL) *1

A, mem 2 2 A ↔ (mem) *3

XA, mem 2 2 XA ↔ (mem) *3

A, reg1 1 1 A ↔ reg1

XA, rp' 2 2 XA ↔ rp'

MOVT XA, @PCDE 1 3 •µPD75104

XA ← (PC11-8+DE)ROM

•µPD75106, 75108

XA ← (PC12-8+DE)ROM

XA, @PCXA 1 3 •µPD75104

XA ← (PC11-8+XA)ROM

•µPD75106, 75108

XA ← (PC12-8+XA)ROM

Table

Reference

Page 38

µ

PD75104, 75106, 75108

38

Ma-

Instruc- Mne-

Operand Bytes

chine

Operation

Addressing Skip

tions monics Cyc- Area Conditions

les

Bit MOV1 CY,fmem.bit 2 2 CY ← (fmem.bit) *4

transfer CY,pmem.@L 2 2 CY ← (pmem7-2+L3-2.bit(L1-0)) *5

CY,@H+mem. 2 2 CY ← (H+mem3-0.bit) *1

bit

fmem.bit,CY 2 2 (fmem.bit) ← CY *4

pmem.@L,CY 2 2 (pmem7-2+L3-2.bit(L1-0)) ← CY *5

@H+mem.bit, 2 2 (H+mem3-0.bit) ← CY *1

CY

Arith- ADDS A, #n4 1 1+S A ← A+n4 carry

metic XA, #n8 2 2+S XA ← XA+n8 carry

opera- A, @HL 1 1+S A ← A+(HL) *1 carry

tion XA, rp’ 2 2+S XA ← XA+rp’ carry

rp’1, XA 2 2+S rp’1 ← rp’1+XA carry

ADDC A, @HL 1 1 A, CY ← A+(HL)+CY *1

XA, rp’ 2 2 XA, CY ← XA+rp’+CY

rp’1, XA 2 2 rp’1,CY ← rp’1+XA+CY

SUBS A, @HL 1 1+S A ← A-(HL). *1 borrow

XA, rp’ 2 2+S XA ← XA-rp’ borrow

rp’1, XA 2 2+S rp’1 ← rp’1-XA borrow

SUBC A, @HL 1 1 A, CY ← A-(HL)-CY *1

XA, rp’ 2 2 XA, CY ← XA-rp’-CY

rp’1, XA 2 2 rp’1,CY ← rp’1-XA-CY

AND A, #n4 2 2 A ← A ∧ n4

A, @HL 1 1 A ← A ∧ (HL) *1

XA, rp’ 2 2 XA ← XA ∧ rp’

rp’1, XA 2 2 rp’1 ← rp’1 ∧ XA

OR A, #n4 2 2 A ← A ∨ n4

A, @HL 1 1 A ← A ∨ (HL) *1

XA, rp’ 2 2 XA ← XA ∨ rp’

rp’1, XA 2 2 rp’1 ← rp’1 ∨ XA

XOR A, #n4 2 2 A ← A ∨ n4

A, @HL 1 1 A ← A ∨ (HL) *1

XA, rp’ 2 2 XA ← XA ∨ rp’

rp’1, XA 2 2 rp’1 ← rp’1 ∨ XA

RORC A 1 1 CY ← A0, A3 ← CY, An-1 ← An

NOT A 2 2 A ← A

Incre- INCS reg 1 1+S reg ← reg+1 reg = 0

ment/ rp1 1 1+S rp1 ← rp1+1 rp1 = 00H

decre- @HL 2 2+S (HL) ← (HL)+1 *1 (HL) = 0

ment mem 2 2+S (mem) ← (mem)+1 *3 (mem) = 0

DECS reg 1 1+S reg ← reg-1 reg = FH

rp’ 2 2+S rp’ ← rp’-1 rp’ = FFH

Accumulator

Manipulation

Page 39

µ

PD75104, 75106, 75108

39

Ma-

Instruc- Mne-

Operand Bytes

chine

Operation

Addressing Skip

tions monics Cyc- Area Conditions

les

Com- SKE reg, #n4 2 2+S Skip if reg = n4 reg = n4

pare @HL, #n4 2 2+S Skip if (HL) = n4 *1 (HL) = n4

A, @HL 1 1+S Skip if A = (HL) *1 A = (HL)

XA, @HL 2 2+S Skip if XA = (HL) *1 XA = (HL)

A, reg 2 2+S Skip if A = reg A = reg

XA, rp’ 2 2+S Skip if XA = rp’ XA = rp’

Carry SET1 CY 1 1 CY ← 1

flag CLR1 CY 1 1 CY ← 0

Manipu- SKT CY 1 1+S Skip if CY = 1 CY = 1

lation NOT1 CY 1 1 CY ← CY

Memory/ SET1 mem.bit 2 2 (mem.bit) ← 1 *3

Bit fmem.bit 2 2 (fmem.bit) ← 1 *4

Manipu- pmem.@L 2 2 (pmem7-2 + L3-2.bit(L1-0)) ← 1*5

lation @H+mem.bit 2 2 (H + mem3-0.bit) ← 1*1

CLR1 mem.bit 2 2 (mem.bit) ← 0 *3

fmem.bit 2 2 (fmem.bit) ← 0 *4

pmem.@L 2 2 (pmem7-2 + L3-2.bit(L1-0)) ← 0*5

@H+mem.bit 2 2 (H+mem3-0.bit) ← 0*1

SKT mem.bit 2 2+S Skip if (mem.bit) = 1 *3 (mem.bit) = 1

fmem.bit 2 2+S Skip if (fmem.bit) = 1 *4 (fmem.bit) = 1

pmem.@L 2 2+S

Skip if (pmem7-2+L3-2.bit (L1-0)) = 1

*5 (pmem.@L) = 1

@H+mem.bit 2 2+S Skip if (H + mem3-0.bit) = 1 *1

(@H+mem.bit) = 1

SKF mem.bit 2 2+S Skip if (mem.bit) = 0 *3 (mem.bit) = 0

fmem.bit 2 2+S Skip if (fmem.bit) = 0 *4 (fmem.bit) = 0

pmem.@L 2 2+S

Skip if (pmem7-2 +L3-2.bit (L1-0)) = 0

*5 (pmem.@L) = 0

@H+mem.bit 2 2+S Skip if (H + mem3-0.bit) = 0 *1

(@H+mem.bit) = 0

SKTCLR

fmem.bit 2 2+S Skip if (fmem.bit) = 1 and clear *4 (fmem.bit) = 1

pmem.@L 2 2+S Skip if (pmem7-2+L3-2.bit *5 (pmem.@L) = 1

(L1-0)) = 1 and clear

@H+mem.bit 2 2+S

Skip if (H+mem3-0.bit) = 1 and clear

*1

(@H+mem.bit) = 1

AND1 CY,fmem.bit 2 2 CY ← CY ∧ (fmem.bit) *4

CY,pmem.@L 2 2

CY ← CY ∧ (pmem7-2+L3-2.bit(L1-0))

*5

CY,@H+mem.bit

2 2 CY

←

CY ∧ (H+mem3-0.bit) *1

OR1 CY,fmem.bit 2 2 CY

←

CY ∨ (fmem.bit) *4

CY,pmem.@L 2 2

CY ← CY ∨ (pmem7-2+L3-2.bit (L1-0))

*5

CY,@H+mem.bit

2 2 CY

←

CY ∨ (H+mem3-0.bit) *1

XOR1 CY,fmem.bit 2 2 CY

←

CY ∨ (fmem.bit) *4

CY,pmem.@L 2 2

CY ← CY

∨

(pmem7-2+L3-2.bit (L1-0))

*5

CY,@H+mem.bit

2 2 CY

←

CY ∨ (H+mem3-0.bit) *1

Page 40

µ

PD75104, 75106, 75108

40

Ma-

Instruc- Mne-

Operand Bytes

chine

Operation

Addressing Skip

tions monics Cyc- Area Conditions

les

Branch BR addr — — • µPD75104 *6

PC11-0 ← addr

The most suitable instruction

is selectable from among

BRCB ! caddr, and BR $ addr

depending on the assembler.

• µPD75106, 75108

PC12-0 ← addr

The most suitable instruction

is selectable from among BR

! addr, BRCB ! caddr, and BR

$ addr depending on the

assembler.

! addr 3 3 • µPD75106, 75108 *6

PC12-0 ← addr

$ addr 1 2 • µPD75104 *7

PC11-0 ← addr

• µPD75106, 75108

PC12-0 ← addr

BRCB ! caddr 2 2 • µPD75104 *8

PC11-0 ← caddr11-0

• µPD75106, 75108

PC12-0 ← PC12 + caddr11-0

BR PCDE 2 3 • µPD75104

PC11-0 ← PC11-8 + DE

• µPD75106, 75108

PC12-0 ← PC12-8 + DE

PCXA 2 3 • µPD75104

PC11-0 ← PC11-8 + XA

• µPD75106, 75108

PC12-0 ← PC12-8 + XA

Subrou- CALL ! addr 3 3 • µPD75104 *6

tine/ (SP-4)(SP-1)(SP-2) ← PC11-0

Stack (SP-3) ← MBE, RBE, 0, 0

Control PC11-0 ← addr, SP ← SP-4

• µPD75106, 75108

(SP-4)(SP-1)(SP-2) ← PC11-0

(SP-3) ← MBE, RBE, 0, PC12

PC12-0 ← addr, SP ← SP-4

Page 41

µ

PD75104, 75106, 75108

41

Ma-

Instruc- Mne-

Operand Bytes

chine

Operation

Addressing Skip

tions monics Cyc- Area Conditions

les

CALLF ! faddr 2 2 • µPD75104 *9

(SP-4)(SP-1)(SP-2) ← PC11-0

(SP-3) ← MBE, RBE, 0, 0

PC11-0 ←0, faddr, SP ← SP-4

• µPD75106, 75108

(SP-4)(SP-1)(SP-2) ← PC11-0

(SP-3) ← MBE, RBE, 0, PC12

PC12-0 ← 00, faddr, SP ← SP-4

RET 1 3 • µPD75104

MBE, RBE, x, x ← (SP+1)

PC11-0 ← (SP)(SP+3)(SP+2)

SP ← SP+4

• µPD75106, 75108

MBE, RBE, x, PC12 ← (SP+1)

PC11-0 ← (SP)(SP+3)(SP+2)

SP ← SP+4

RETS 1 3+S • µPD75104 Unconditioned

MBE, RBE, x, x ← (SP+1)

PC11-0 ← (SP)(SP+3)(SP+2)

SP ← SP+4,

then skip unconditionally

• µPD75106, 75108

MBE, RBE, x, PC12 ← (SP+1)

PC11-0 ← (SP)(SP+3)(SP+2)

SP ← SP+4,

then skip unconditionally

RETI 1 3 • µPD75104

MBE, RBE, x, x ← (SP+1)

PC11-0 ← (SP)(SP+3)(SP+2)

PSW ← (SP+4)(SP+5), SP ← SP+6

• µPD75106, 75108

MBE, RBE, x, PC12 ← (SP+1)

PC11-0 ← (SP)(SP+3)(SP+2)

PSW ← (SP+4)(SP+5), SP ← SP+6

PUSH rp 1 1 (SP-1)(SP-2) ← rp, SP ← SP-2

BS 2 2 (SP-1) ← MBS, (SP-2) ← RBS,

SP ← SP-2

POP rp 1 1 rp ← (SP+1)(SP), SP ← SP+2

BS 2 2 MBS ← (SP+1), RBS ← (SP),

SP ← SP+2

Subroutine/

Stack

Control

(Cont‘d)

Page 42

µ

PD75104, 75106, 75108

42

Ma-

Instruc- Mne-

Operand Bytes

chine

Operation

Addressing Skip

tions monics Cyc- Area Conditions

les

Inter- EI 2 2 IME (IPS.3) ← 1

rupt IExxx 2 2 IExxx ← 1

Control DI 2 2 IME (IPS.3) ← 0

IExxx 2 2 IExxx ← 0

I/O IN* A, PORTn 2 2 A ← PORTn (n = 0-9, 12-14)

XA, PORTn 2 2

XA

←

PORTn+1,PORTn

(n = 4, 6, 8, 12)

OUT* PORTn, A 2 2 PORTn ← A (n = 2-9, 12-14)

PORTn, XA 2 2 PORTn+1, PORTn ← XA(n = 4, 6, 8, 12)

CPU HALT 2 2 Set HALT Mode (PCC.2 ← 1)

Control STOP 2 2 Set STOP Mode (PCC.3 ← 1)

NOP 1 1 No Operation

Special SEL RBn 2 2 RBS ← n (n = 0-3)

MBn 2 2 MBS ← n (n = 0, 1, 15)

GETI taddr 1 3 • µPD75104 *10

• Where TBR instruction,

PC11-0 ← (taddr)3-0+(taddr+1)

• Where TCALL instruction,

(SP-4)(SP-1)(SP-2) ← PC11-0

(SP-3) ← MBE, RBE, 0, 0

PC11-0 ← (taddr)3-0+(taddr+1)

SP ← SP-4

• Except for TBR and TCALL Depends on

instructions, referenced

Instruction execution of instruction

(taddr)(taddr+1)

• µPD75106, 75108

• Where TBR instruction,

PC12-0 ← (taddr)4-0+(taddr+1)

• Where TCALL instruction,

(SP-4)(SP-1)(SP-2) ← PC11-0

(SP-3) ← MBE, RBE, 0, PC12

PC12-0 ← (taddr)4-0+(taddr+1)

SP ← SP-4

• Except for TBR and TCALL Depends on

instructions, referenced

Instruction execution of instruction

(taddr)(taddr+1)

*: When executing the IN/OUT instruction, MBE = 0, or MBE = 1, and MBS = 15.

Remarks: TBR and TCALL instructions are assembler instructions for GETI instruction table definition.

.........................................................

.........................................................

......................................................... .............................

......................................................... .............................

★

Page 43

µ

PD75104, 75106, 75108

43

10. APPLICATION EXAMPLES

10.1 VTR SYSTEM CONTROLLER

PD75108

µ

Remote

controller

signal

receiver

Operation

mode LED

indicator

Servo

system

control

circuit

Motor

driver

circuit,

etc.

Highcurrent

output

System

controller/

tape counter/

remote controller/

remaining tape

computation

INT

INT

Comparator

input

INT

Audio video system

control circuit

12 V

SIO

Key

matrix

Take-up reel pulse

Supply reel pulse

Sensor circuit

Exposure sensor

Tape start/end

sensor

On-screen

display

controller

PD752

timer/tuner/OSD

µ

××

PWM output

MNOS

PD6252

PD6253

PD6254

µ

µ

µ

TunerFIP

10.2 VTR CAMERA

PD75108

µ

Operation

mode LED

indicator

Servo

system

control

circuit

INT

Motor

plunger

driver

circuit,

etc.

System control/

editing

function

INT

Key matrix

(including

message

input)

Reel pulse

Battery sensor

Sensor circuit

Exposure sensor

Tape start/end

sensor

Powerdown

detector

On-screen

display

controller

12 V

Audio video system

control circuit

Comparator

input

Highcurrent

output

Page 44

µ

PD75104, 75106, 75108

44

10.3 COMPACT DISC PLAYER

PD75108

µ

SIO

INT

Servo

control

IC

Loading

control

circuit

Remote

controller

signal

receiver

Highcurrent

output

Key

matrix

LED

indication

10.4 AUTOMOBILE APPLICATIONS (TRIP COMPUTER)

PD75108

µ

SIO

INT0

INT1

TI

TO

Vehicle speed

detection

Number of

revolutions

detection

Fuel

comsumption

Key position

Gear position

Key input

Mode select

Numerical

input

Buzzer

Display

driver

PD6300

PD6323

PD6332

µ

µ

µ

Clock

Alarm

Average

speed

Arrival

time, etc.

Page 45

µ

PD75104, 75106, 75108

45

10.5 PUSHBUTTON TELEPHONE

Filter

PD75108

µ

Comparator

input

SIO

INT

TO

Code ROM

Piezoelectric

buzzer

Switch

RAM

PD4464

µ

LED indicator

Battery

check

LCD indicator

LCD controller/

driver

PD7228/7229

µ

Highcurrent

output

Hook switch

To main

equipment

LED

indicator

Key

matrix

Data

receiver

circuit

Data

transmitter

circuit

TO

PD75108

µ

Filter

SIO

PD7228G

µ

LCD

controller/

driver

LCD indicator

Microphone

Speaker

Transmitter/

receiver

MPX

Highcurrent

output

Transmitter/

receiver/

speaker

selector

Communication

circuit

Speaker

amplifier

Microphone

amplifier

Call sound

10.6 DISPLAY PAGER

Page 46

µ

PD75104, 75106, 75108

46

10.7 PLAIN PAPER COPIER (PPC)

PD75108

µ

TO

Comparator

input

Motor/relay

driver

circuit

Switch

Piezoelectric

buzzer

12 V

Highcurrent

output

LED indicator

Key matrix

Sensor circuit,

heater

temperature, toner

drum pressure, etc.

10.8 PRINTER CONTROLLER

PD75108

µ

Host machine

PD0 to PD7

STRB

BUSY

TxD

INT

SI

TO

12 V

High

current

Key matrix

LED

Motor

driver

control

circuit

Dot

matrix

head

driver

circuit

Piezoelectric

buzzer

Page 47

µ

PD75104, 75106, 75108

47

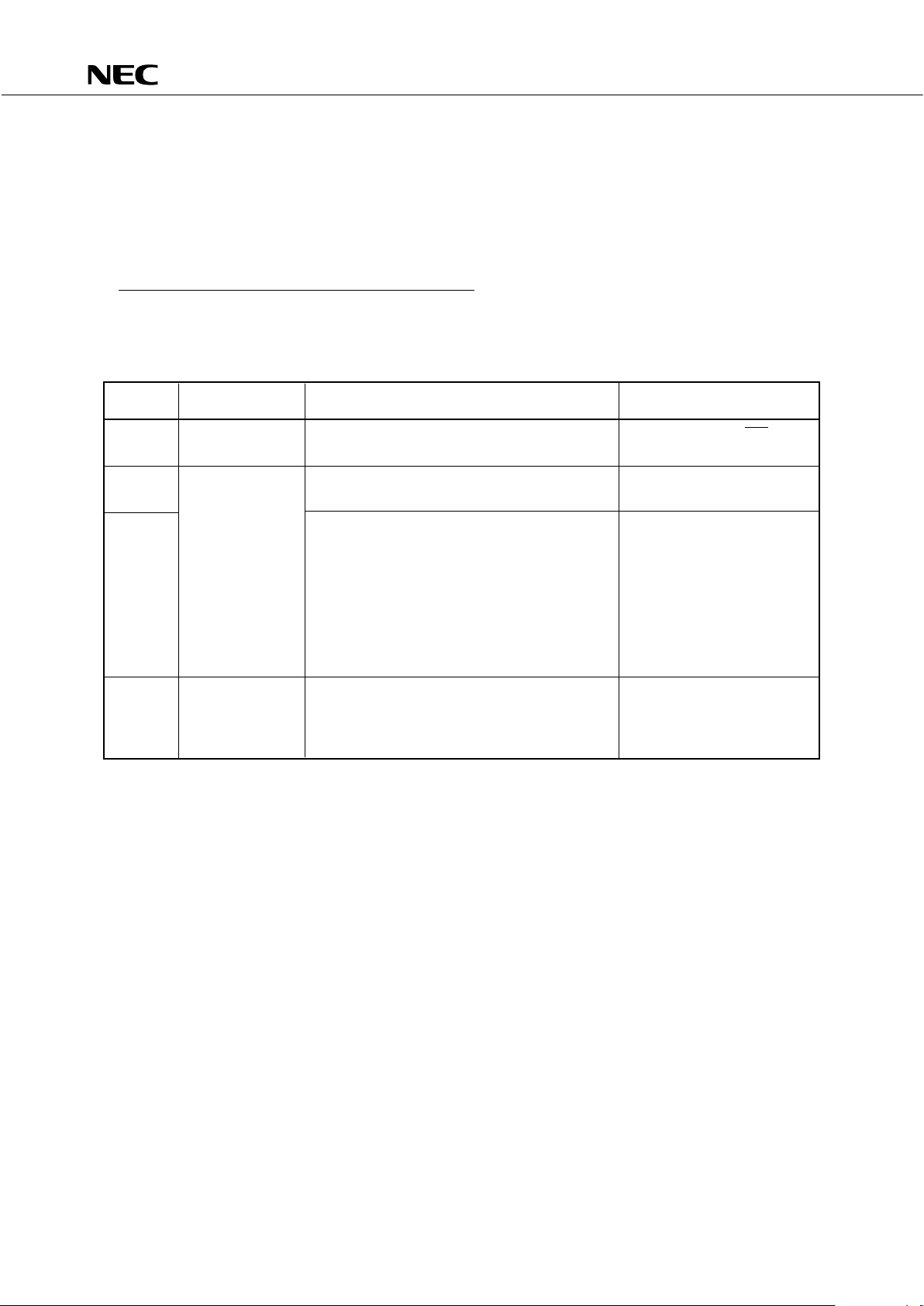

11. MASK OPTION SELECTION

µ

PD75108 has the following mask options. Options to be built in can be selected.

(1) Pin

Pin Mask Option

P120 - P123

P130 - P133 Pull-down resistor can be built in bitwise.

P140 - P143

(2) Power-ON reset generation circuit, power-ON flag (PONF)

One from the following three ways can be selected.

Switching Selection

Power-On Reset Power-On Flag Internal Reset Signal

(Refer to Fig. 8-1.)

Generation Circuit (PONF) (RES)

SWA SWB

ON ON Provided Provided Generates automatically

ON OFF Provided Provided Not generates autoamtically

OFF OFF Not provided Not provided —

Page 48

µ

PD75104, 75106, 75108

48

12. ELECTRICAL SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS (Ta = 25°C)

Parameter Symbol Conditions Ratings Unit

Supply Voltage VDD -0.3 to +7.0 V

VI1 Other than ports 12, 13, 14 -0.3 to VDD+0.3 V

Input Voltage VI2*1Ports 12 to 14 w/pull-up -0.3 to VDD+0.3

V

resistor

Open drain -0.3 to +13 V

Output Voltage VO -0.3 to VDD+0.3 V

High-Level Output IOH 1 pin -15 mA

Current

All pins -30 mA

Low-Level Output IOL*21 pin Peak 30 mA

Current rms 15 mA

Total of ports 0, 2 to 4, 12 to 14 Peak 100 mA

rms 60 mA

Total of ports 5 to 9 Peak 100 mA

rms 60 mA

Operating Temperature Topt -40 to +85 °C

Storage Temperature Tstg -65 to +150 °C

*1: The power supply impedance (pull-up resistance) must be 50 kΩ or higher when a voltage higher than

10 V is applied to ports 12, 13, and 14.

2: rms = Peak value x √Duty

Page 49

µ

PD75104, 75106, 75108

49

OSCILLATOR CIRCUIT CHARACTERISTICS

(T

a = -40 to +85°C, VDD = 2.7 to 6.0 V)

Oscillator

Recommended

Item Conditions MIN. TYP. MAX. Unit

Constants

Ceramic Oscillation VDD = Oscillation

2.0 5.0 MHz

frequency(fXX)*

1

voltage range

Oscillation stabiliza- After VDD come to

tion time*

2

MIN. of oscillation

voltage range

4ms

Crystal Oscillation

2.0 4.19 5.0 MHz

frequency (fXX)*

1

Oscillation stabiliza- VDD = 4.5 to 6.0 V 10 ms

tion time*

2

30 ms

External Clock X1 input frequency

2.0 5.0 MHz

(fX)*

1

X1 input high-,

low-level widths

(tXH, tXL) 100 250 ns

*1: The oscillation frequency and X1 input frequency are indicated only to express the characteristics

of the oscillator circuit. For instruction execution time, refer to AC Characteristics.

2: Time required for oscillation to stabilize after V

DD has come to MIN. of oscillation volrage range

or the STOP mode has been released.

3: When the oscillation frequency is 4.19 MHz < fx ≤ 5.0 MHz, do not select PCC = 0011 as the

instruction execution time: otherwise, one machine cycle is set to less than 0.95

µ

s, falling short

of the rated minimum value of 0.95

µ

s.

Note: When using the oscillation circuit of the system clock, wire the portion enclosed in dotted line

in the figures as follows to avoid adverse influences on the wiring capacity:

• Keep the wiring length as short as possible.

• Do not cross the wiring over the other signal lines. Also, do not route the wiring in the vicinity

of lines through which a high alternating current flows.

• Always keep the ground point of the capacitor of the osccillator circuit at the same potential

as V

SS. Do not connect the ground pattern through which a high current flows.

• Do not extract signals from the oscillation circuit.

X1 X2

C1 C2

X1 X2

C1 C2

X1 X2

PD74HCU04

µ

*

3

*

3

*

3

★

★

Page 50

µ

PD75104, 75106, 75108

50

RECOMMENDED OSCILLATOR CIRCUITS CONSTANTS

RECOMMENDED CERAMIC OSCILLATORS

External Oscillation

Manufacturer Product Name

Capacitance (pF) Voltage Range (V)

C1 C2 MIN. MAX.

CSA 2.00MG 30 30 2.7 6.0

Murata Mfg. CSA 4.19MG 30 30 3.0 6.0

Co., Ltd. CSA 4.19MGU 30 30 2.7 6.0

CST 4.19T Provided Provided 3.0 6.0

KBR-2.0MS 100 100 3.0 6.0

Kyoto Ceramic KBR-4.0MS 33 33 3.0 6.0

Co., Ltd. KBR-4.19MS 33 33 3.0 6.0

KBR-4.9152M 33 33 3.0 6.0

RECOMMENDED CRYSTAL OSCILLATOR

External Oscillation

Manufacturer Product Name

Capacitance (pF) Voltage Range (V)

C1 C2 MIN. MAX.

Kinseki HC-49/U 22 22 2.7 6.0

Page 51

µ

PD75104, 75106, 75108

51

DC CHARACTERISTICS (Ta = -40 to +85°C, VDD = 2.7 to 6.0 V)

Item Symbol Conditions MIN. TYP. MAX. Unit

VIH1 Other than below 0.7VDD VDD V

High-Level VIH2 Ports 0, 1, TI0, 1, RESET 0.8 VDD VDD V

Input Voltage Pull-up resistor 0.7 VDD VDD V

Open drain 0.7 VDD 12 V

VIH4 X1, X2 VDD-0.5 VDD V

VIL1 Other than below 0 0.3 VDD V

Low-Level Input Voltage VIL2 Ports 0, 1, TI0, 1, RESET 0 0.2 VDD V

VIL3 X1, X2 0 0.4 V

VDD = 4.5 to 6.0 V,IOH = -1 mA VDD-1.0 V

IOH = -100 µAVDD-0.5 V

VDD = Ports 0, 2 to 9, IOL = 15 mA 0.35 2.0 V

4.5 to 6.0 V Ports 12 to 14, IOL = 10 mA 0.35 2.0 V

VDD = 4.5 to 6.0 V, IOL = 1.6 mA 0.4 V

IOL = 400 µA 0.5 V

ILIH1 Other than below 3

µ

A

ILIH2 X1,X2 20

µ

A

ILIH3 VIN = 12 V Ports 12 to 14 (open drain) 20

µ

A

Low-Level ILIL1 Other than X1, X2 –3

µ

A

Input Leakage Current ILIL2 X1, X2 –20

µ

A

High-Level ILOH1 VOUT = VDD Other than below 3

µ

A

Output Leakage Current ILOH2 VOUT = 12 V Ports 12 to 14 (open drain) 20

µ

A

Low-Level Output ILOL VOUT = 0 V –3

µ

A

Leakage Current

VDD = 5 V±10% 15 40 70 kΩ

10 80 kΩ

4.19MHz VDD = 5 V± 10%*

2

39mA

crystal VDD = 3 V±10%*

3

0.55 1.5 mA

Supply Current*

1

oscillator HALT VDD = 5 V±10% 600 1800

µ

A

C1 = C2 = 22pF mode VDD = 3±10% 200 600

µ

A

IDD3 STOP mode, VDD = 3 V± 10% 0.1 10

µ

A

*1: The current flowing into the internal pull-up resistor, power-ON reset circuit (mask option), and comparator

circuit is not included.

2: When the high-speed mode is set by setting the processor clock control register (PCC) to 0011.

3: When the low-speed mode is set by setting the PCC to 0000.

Low-Level Output Voltage VOL

High-Level Output Voltage VOH

VIN = VDD

VIN = 0 V

High-Level Input Leakage

Current

Internal Pull-Up Resistor*1RL Ports 12 to 14

IDD1

IDD2

VIH3 Ports 12 to 14

Page 52

µ

PD75104, 75106, 75108

52

CAPACITANCE (Ta = 25°C, VDD = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Input Capacitance CIN f = 1 MHz 15 pF

Output Capacitance COUT Pins other than thosemeasured are at 0 V 15 pF

Input/Output CIO 15 pF

Capacitance

COMPARATOR CHARACTERISTICS (Ta = -40 to +85°C, VDD = 4.5 to 6.0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Comparison Accuracy VACOMP ±100 mV

Threshold Voltage VTH 0VDD V

PTH Input voltage VIPTH 0VDD V

Comparator circuit PTHM7 is set to “1” 1 mA

current dissipation

POWER-ON RESET CIRCUIT CHARACTERISTICS (MASK OPTION) (Ta = -40 to +85°C)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Power-On Reset

High-Level VDDH 4.5 6.0 V

Operating Voltage

Power-On Reset

Low-Level VDDL 0 0.2 V

Operating Voltage

Supply Voltage tr 10 *

1

µ

s

Rise Time

Supply Voltage toff 1s

Off Time

Power-On Reset Circuit IDDPR VDD = 5 V± 10% 10 100

µ

A

Current Dissipation*

2

VDD = 2.5 V 2 20

µ

A

*1: 217/fXX (31.3 ms at fXX = 4.19 MHz)

2: Current flowing when power-ON reset circuit or power-ON Flag is incorporeated.

Note: Apply power gradually and smoothly.

V

DD

V

DDH

V

DDL

t

off

t

r

Page 53

µ

PD75104, 75106, 75108

53

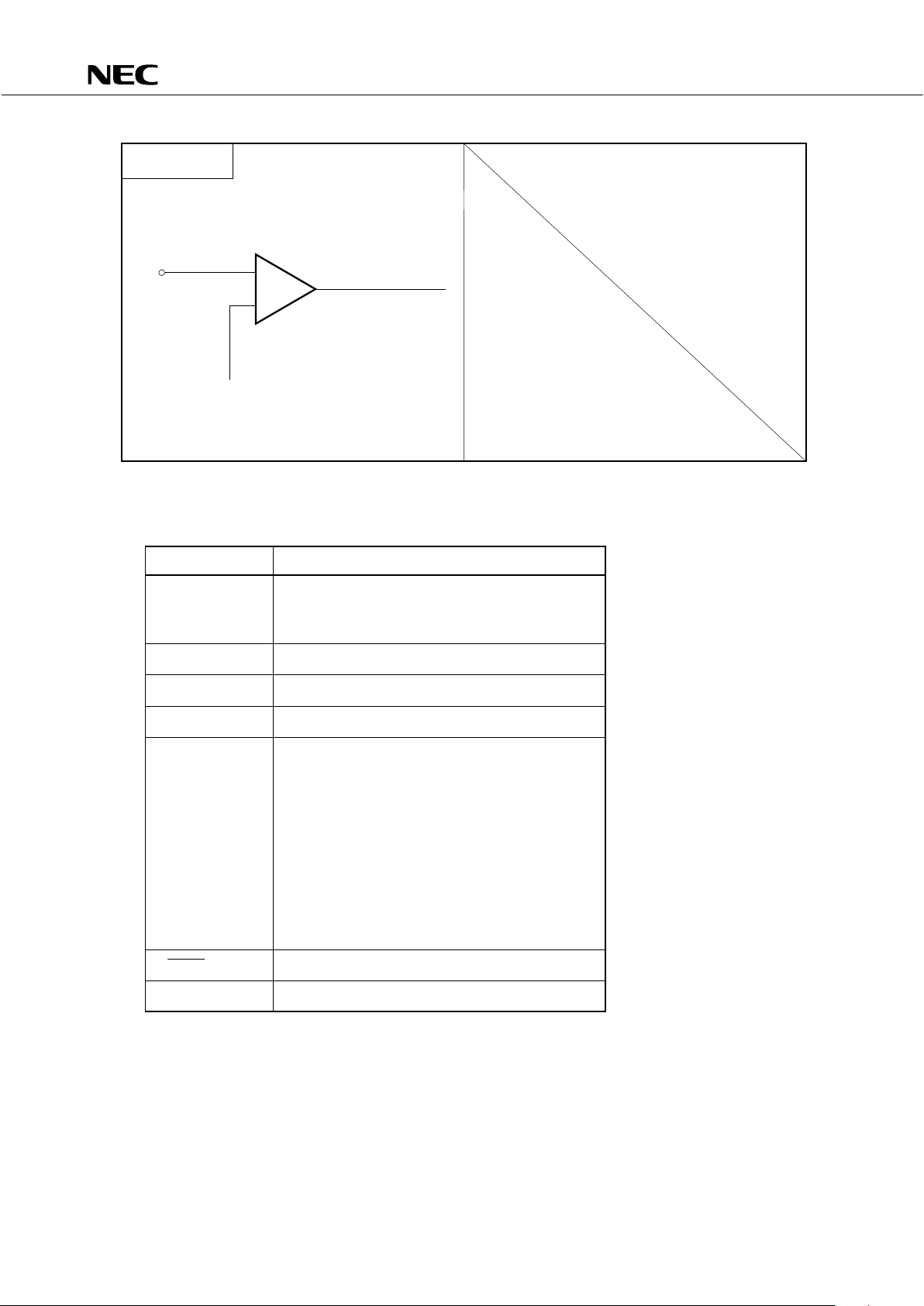

AC CHARACTERISTICS (Ta = -40 to +85°C, VDD = 2.7 to 6.0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

VDD = 4.5 to 6.0 V 0.95 32

µ

s

3.8 32

µ

s

VDD = 4.5 to 6.0 V 0 1 MHz

0 275 kHz

tTIH,VDD = 4.5 to 6.0 V 0.48

µ

s

t

TIL

1.8

µ

s

VDD = 4.5 to 6.0 V Input 0.8

µ

s

Output 0.95

µ

s

Input 3.2

µ

s

Output 3.8

µ

s

VDD = 4.5 to 6.0 V Input 0.4

µ

s

Output tKCY/2-50 ns

Input 1.6

µ

s

Output

tKCY/2-150

ns

SI Setup Time tSIK 100 ns

(vs. SCK↑)

SI Hold Time tKSI 400 ns

(vs. SCK↑)

VDD = 4.5 to 6.0 V 300 ns

1000 ns

INT0 to 4 tINTH,

5

µ

s

High-/Low-Level Width tINTL

RESET Low-Level Width tRSL 5

µ

s

*: The cycle time of the CPU clock (Φ) is

determined by the input frequency of

the ceramic or crystal oscillator circuit

and the set value of the processor clock

control register. The t

CY vs. VDD charac-

teristics are as shown on the right.

0123 456

0.5

1

2

3

4

5

6

V

DD

[V]

t

CY

[ s]

tCY vs. V

DD

µ

32

40

Operation

guaranteed

range

7

CPU Clock Cycle Time*

(Minimum Instruction

Execution Time = 1

Machine Cycle)

tCY

TI0, TI1 Input Frequency fTI

TI0, TI1 Input High-/

Low-Level Width

SCK Cycle Time tKCY

SCK High-/Low-Level

Width

tKH,

tKL

SCK ↓→ SO Output

delay Time

tKSO

Page 54

µ

PD75104, 75106, 75108

54

AC TIMING MEASURING POINTS (excluding Ports 0, 1, TI0, TI1, X1, X2, and RESET)

CLOCK TIMING

TI TIMING

Measuring

points

0.7 V

DD

0.3 V

DD

0.7 V

DD

0.3 V

DD

X1 input

V

DD

–0.5

0.4

t

XL

t

XH

1/f

X

0.8

TI0, TI1

t

TIL

t

TIH

1/f

TI

0.2

V

DD

V

DD

Page 55

µ

PD75104, 75106, 75108

55

SERIAL TRANSFER TIMING