Page 1

Evaluation Board User Guide

UG-366

VIN

12 V

06388-016

One Technology Way • P. O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

Evaluation Board for PWM, Step-Down DC-to-DC Controller with

Margining and Tracking

INTRODUCTION

This data sheet describes the design, operation, and test of the

ADP1822 standard evaluation board. In all tests, the board is

operated from an input voltage range of 9 V to 15 V, and

generates up to 10 A at V

fixed at 300 kHz.

GENERAL DESCRIPTION

The ADP1822 is a versatile and inexpensive synchronous buck

PWM controller. The converter power input voltage range is

1 V to 24 V, while the ADP1822 controller is specified from

3.0 V to 5.5 V. The ADP1822 free-running frequency is logicselectable at either 300 kHz or 600 kHz. Alternatively, it can be

synchronized to an external clock at any frequency between

300 kHz and 1.2 MHz. The internal gate drivers control an all

N-channel power stage to regulate a converter output voltage as

low as 0.6 V with up to 20 A load current.

The regulated output of the ADP1822 can track another power

supply and be dynamically adjusted up or down with the

margining control inputs of the controller.

= 1.8 V. The switching frequency is

OUT

The ADP1822 includes an adjustable soft start to limit input

inrush current and to facilitate sequencing. It provides currentlimit and short-circuit protection, and a power-good logic output.

The ADP1822 is well suited for a wide range of power

applications, such as DSP and processor core power in

telecommunications, medical imaging, high performance

servers, and industrial applications.

SPECIFICATIONS

Table 1. Evaluation Board Specifications

Description Parameter

V

1.8 V

OUT

Frequency 300 kHz

Maximum I

Current Limit 15 A

High and Low Voltage Margining 5%

10 A

OUT

PLEASE SEE THE LAST PAGE FOR AN IMPORTANT

WARNING AND LEGAL TERMS AND CONDITIONS.

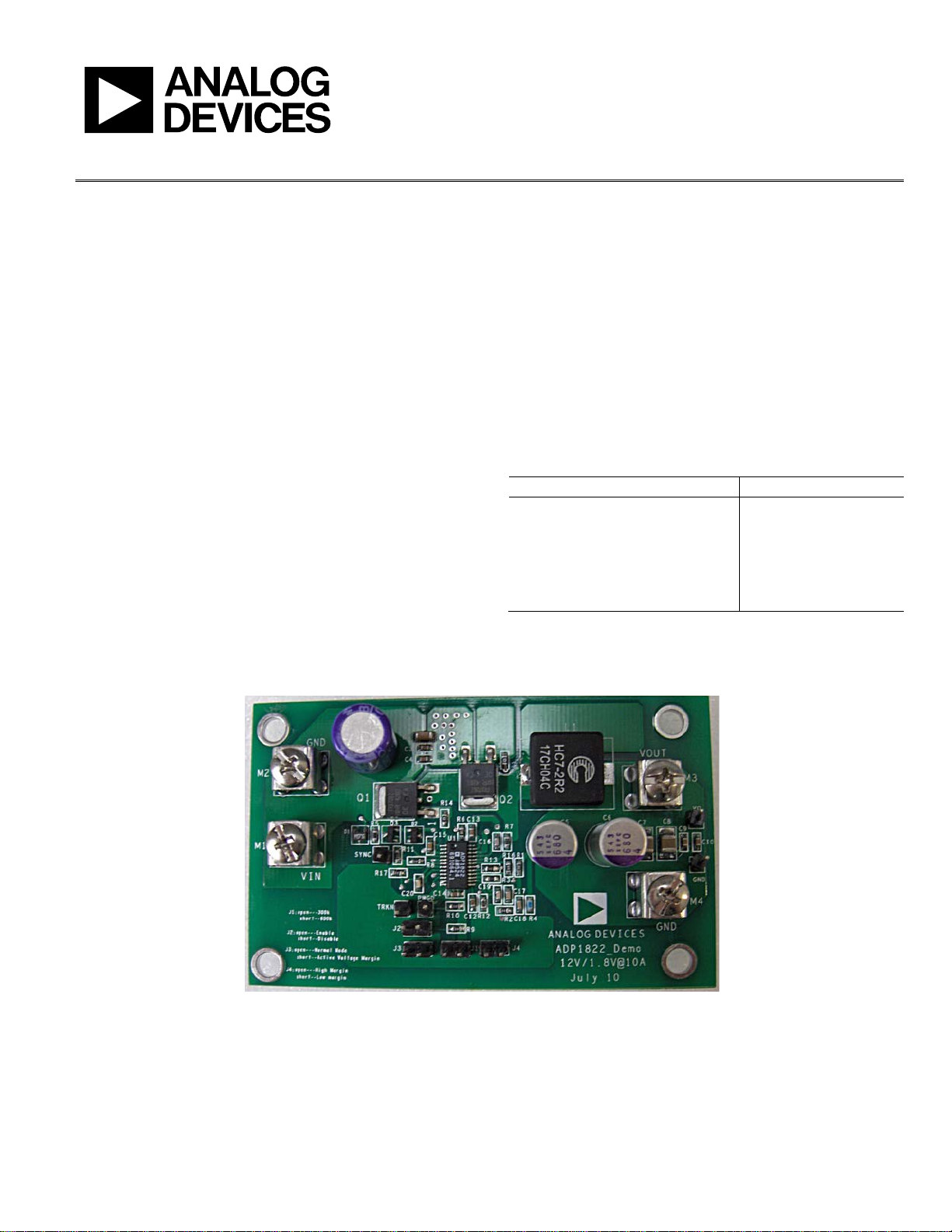

Figure 1. ADP1822 Evaluation Board (ADP1822-EVALZ)

Rev. A | Page 1 of 16

Page 2

UG-366 Evaluation Board User Guide

TABLE OF CONTENTS

Introduction ...................................................................................... 1

General Description ......................................................................... 1

Specifications ..................................................................................... 1

Revision History ............................................................................... 2

Test Instructions ............................................................................... 3

Component Selection ....................................................................... 4

Input Capacitor ............................................................................. 4

Output Inductor ........................................................................... 4

Output Capacitor .......................................................................... 4

MOSFET Selection ....................................................................... 4

Output Voltage .............................................................................. 5

Current Limit Set Resistor ........................................................... 5

REVISION HISTORY

12/11—Rev. 0 to Rev. A

Updated Format .................................................................. Universal

Changed EVAL-ADP1822 to ADP1822-E VAL .............. Universal

11/06—Revision 0: Initial Version

Setting the Soft Start .....................................................................5

Output Voltage Tracking ..............................................................5

Output Voltage Margining ...........................................................6

Control Loop Design and Equations ..............................................7

Power Stage Transfer Function ....................................................7

Control Circuit and Transfer Function ......................................7

Overall Loop Gain .........................................................................8

Test Results and Major Waveforms .................................................9

PCB Layout Guidelines .................................................................. 11

Evaluation Board Schematic and Layout..................................... 12

Ordering Information .................................................................... 14

Bill of Materials ........................................................................... 14

Rev. A | Page 2 of 16

Page 3

Evaluation Board User Guide UG-366

TEST INSTRUCTIONS

Test instructions:

1. Make sure that Jumper 2 is open. Power on the board

(output voltage is at 1.8 V).

2. If Jumper 1 is shorted, replace the inductor to another

value to fit 600 kHz operation.

3. If Jumper 3 is shorted, the output high margining is at

1.89 V. If Jumper 4 is open, the output low margining is at

1.71 V.

4. Verify the output voltage tracking features when

connecting the external generator to the TRKN point.

5. Use the PWGD point for monitoring operation behavior.

Table 2. Jumper and Connector Descriptions

Name Description

M1 VIN

M2 GND In

M3 VIN

M4 GND Out

Jumper 1 Open: 300 kHz

Short: 600 kHz

Jumper 2 Open: enable the board

Short: disable the board

Jumper 3 Open: output voltage normal mode.

Short: active voltage margin

Jumper 4 Open: high margin

Short: low margin

Table 3. Margining Description

MAR MSEL Voltage Margin

Low (Jumper 3

open)

High (Jumper 3

shorted)

High (Jumper 3

shorted)

X None

High (Jumper 4

open)

Low (Jumper 4

shorted)

High margin (FB

connected to MUP)

Low margin (FB

connected to MDN)

Default

Status

Open

Open

Open

Open

Rev. A | Page 3 of 16

Page 4

UG-366 Evaluation Board User Guide

)1( D

f

KI

V

L

SWCR

OUT

OUT

−=

+∆=∆

OUT

SW

L

OUT

Cf

ESRIV

8

1

up

OUT

OUT

min1OUT,

VV

LI

C

∆

∆

=

2

2

down

UTO

IN

OUT

min2OUT,

VVV

LI

C

∆−

∆

=

)(2

2

12

2

L

COUT

II∆

=

DSON

L

UTO

lowC

R

I

IDP

∆

+−=

12

)1(

2

2

,

SWGGG

fQVP =

2

)(

SW

FRLIN

T

fttIV

P+=

COMPONENT SELECTION

INPUT CAPACITOR

In continuous mode, the source current of the high-side

MOSFET is a square wave of duty cycle V

OUT/VIN

. To prevent

large voltage transients, use a low ESR input capacitor sized for

the maximum rms current. The maximum rms capacitor

current is given by I

√D(1 − D)

L

OUTPUT INDUCTOR

In high switching applications, if the inductor is too big, the

dI/dt is too low and cannot respond to load changes quickly. If

the inductor is too small, the output ripple would be high.

Therefore, if good transient response is needed, smaller

inductors and larger capacitors are better, within the constraint

of the maximum allowed ripple current in the capacitor and the

maximum dissipation of the core (core temperature).

The output inductor can be chosen according to the following

equation:

(1)

where:

is the output voltage.

V

OUT

I

is the rated output current.

OUT

K

is the ratio of current ripple, ΔIL/IO.

CR

f

is the switching frequency.

SW

D is the duty cycle

Generally, K

should be chosen around 20% ~ 40%.

cr

OUTPUT CAPACITOR

The selection of C

capacitance. The output voltage ripple can be approximated as

is determined by the ESR and the

OUT

(4)

where:

is the step load.

ΔI

OUT

ΔV

is the output voltage overshoot when the load is

up

stepped down.

ΔV

is the output voltage overshoot when the load is

down

stepped up.

V

is the input voltage.

IN

C

is the minimum capacitance according to the overshoot

OUT,min1

voltage ΔV

C

OUT,min2

voltage ΔV

Select an output capacitance that is greater than both C

and C

up.

is the minimum capacitance according to the overshoot

down.

OU T, min1

.

OU T, min2

Make sure that the ripple current rating of the output capacitors

is greater than the following current:

(5)

MOSFET SELECTION

The choice of MOSFET directly affects the dc-to-dc converter

performance. The MOSFET must have low on resistance

(R

) to reduce the conduction loss, and low gate charge to

DSON

reduce switching loss.

For the low-side (synchronous) MOSFET, the dominant loss is

the conduction loss. It can be calculated as

(6)

(2)

Generally, the voltage ripple caused by the capacitance or ESR

depends on the capacitor chosen.

ESR affects the output voltage ripple; thus, an MLCC capacitor

is recommended because of its low ESR.

During a load transient on the output, the amount of

capacitance needed is determined by the maximum energy

stored in the inductor. The capacitance must be sufficient to

absorb the change in inductor current when a high current to

low current transition occurs and to supply the load when a low

current to high current transition occurs.

(3)

The gate charge loss is approximated by the following equation:

where:

V

G

Q

G

The high-side (switching) MOSFET has to be able to handle

conduction loss and switching loss. The high-side MOSFET

switching loss is approximated by the equation

where t

Rev. A | Page 4 of 16

(7)

is the driver voltage.

is the MOSFET total gate charge.

(8)

and tF are the rise and fall times of the MOSFET.

R

Page 5

Evaluation Board User Guide UG-366

G

SPG

GD

GS

R

R

VV

Q

Q

t

−

+

=

2

G

SP

GD

GS

F

R

V

Q

Q

t+=

2

m

UTO

TH

SP

g

I

VV +≈

DSON

L

OUT

highC

R

I

IDP

∆

+=

12

2

2

,

6.0

6.0−

=

OUT

V

RR 21

( )

lowDSON

L

L

lowDSON

CSLCSL

CSL

R

I

IRRIV

__

2

∆

+−+=

CSL

lowDSON

L

CSL

I

R

I

I

R

_

2

∆

+

=

limit

kΩ100

8.0

6.0

1ln ×

−−

=

SS

SS

t

C

tR and tF can be calculated using

and

where:

and Q

Q

GS

R

is the gate resistance

G

V

is approximated using

SP

are provided in the MOSFET data sheet.

GD

In normal operation, the direction of current flow through the

low-side FET causes a negative voltage to appear on its drain.

This voltage is V = IR, where I is the instantaneous FET current

and R is its R

. A +42 μA current source at the ADP1822

DSON

CSL pin causes a fixed voltage drop in the current sense resistor

that is connected from the CSL pin to the drain of the low-side

FET. This current through the current limit set resistor produces

a voltage in the opposite direction, thus raising (in the positive

direction) the potential at the CSL pin. The resulting net voltage

on the CSL pin is compared with ground. During normal

operation, the CSL pin stays above ground potential. The

overcurrent protection circuitry is triggered when increased

FET current produces increased negative voltage on the lowside MOSFET drain, thus causing the voltage on the CSL pin to

go negative with respect to ground.

Therefore, the resistor R

can be calculated from the following

CSL

equation:

where g

is the MOSFET transconductance.

m

The high-side MOSFET conduction loss can be calculated as

(9)

OUTPUT VOLTAGE

The regulation threshold at the FB pin is 0.6 V, and t he

maximum input bias current is 100 nA. This bias current can

introduce significant error if the divider impedance is too high.

In order to get the best accuracy, the bottom resistor, R2, should

be no higher than 50 kΩ. On the other hand, very low values of

R2 will dissipate excess power. For R2, a 1% resistor with a value

between 1 kΩ and 10 kΩ is recommended.

The upper divider is then set using the following formula (it

should also be a 1% type):

(10)

CURRENT LIMIT SET RESISTOR

The voltage on the CSL pin can be calculated by the following

formula:

(11)

where:

is the voltage on the CSL pin.

V

CSL

I

is the current out from the CSL pin, I

CSL

R

is the current limited resistor.

CSL

R

I

ΔI

is the conduction resistor of the lower side MOSFET.

DSON_low

is the output current.

L

is the output current ripple.

L

= 42 μA.

CSL

(12)

SETTING THE SOFT START

The soft start characteristic is set by the capacitor connected

from SS to GND. The ADP1822 charges C

internal resistor. The soft start period (t

V

= 0.6 V.

CSS

to 0.8 V through an

SS

) is achieved when

SS

(13)

where 100 kΩ is the internal resistor.

OUTPUT VOLTAGE TRACKING

The ADP1822 features an internal comparator that forces the

output voltage to track an external voltage at startup, which

prevents the output voltage from exceeding the tracking voltage.

The comparator turns off the high-side switch if the positive

tracking (TRKP) input voltage exceeds the negative tracking

(TRKN) input voltage. Connect TRKP to the output voltage and

drive TRKN with the voltage to be tracked. If the voltage at

TRKN is below the regulation voltage, the output voltage at

TRKN is below the regulation voltage, and the output voltage is

limited to the voltage at TRKN. If the voltage at TRKN is above

the regulation voltage, the output voltage regulates the desired

voltage set by the voltage divider.

Rev. A | Page 5 of 16

Page 6

UG-366 Evaluation Board User Guide

OUTPUT VOLTAGE MARGINING

The ADP1822 features output voltage margining. MSEL is the

margin select input. Drive MSEL high to activate the voltage

margining feature. Drive MSEL low to regulate the output

voltage to the nominal value. If not used, connect MSEL to

GND. MAR is the margin control input. MAR is used with

MSEL to control output voltage margining. MAR chooses

between high voltage and low voltage margining when MSEL is

driven high. If not used, connect MAR to GND.

The internal switches from FB are connected to MUP and

MSEL terminals to determine the high and low margining. The

high voltage is margined by switching a resistor from FB to

GND, and the low voltage is margined by switching a resistor

from FB to the output voltage.

Table 4. Voltage Margining Control

MAR MSEL Voltage Margin

Low X None

High High High margin (FB connected to MUP)

High Low Low margin (FB connected to MDN)

Rev. A | Page 6 of 16

Page 7

Evaluation Board User Guide UG-366

)(

)(

)(

sD

sV

sG

OUT

VD

=

2

2

1

1

1

)(

OO

C

L

IN

VD

s

Q

s

sCR

R

R

V

sG

ω

+

ω

+

××+

×

+

=

LC

RR

RR

C

L

O

+

+

=ω

O

L

C

C

L

L

R

CRR

CRR

R

L

R

R

Q

ω

⋅

+×++

+

=

1

)(

1

π

+

π

+

π

+

π

+

=

21

21

2

1

2

1

2

1

2

1

)(

PP

ZZ

EA

f

s

f

s

f

s

f

s

ksG

1R

3R

k −=

R3C17

f

Z

π=2

1

1

18C2R1R

f

Z

)(2

1

2

+π

=

C19C17

C19C17

R

f

P

+

⋅

π=32

1

1

R4C18

f

P

π=2

1

2

L1

R8

C20

R9

HIGH SIDE

DRIVER

LOW SIDE

DRIVER

OUT

OUT

C21

C22

R11

R

C

C1

RL1

R10

COMP

06388-002

V

OUT

V

IN

V

FB

V

REF

R3

C17

C19

R1R4

C18

R2

OUT

06388-003

V

COMP

V

REF

V

OUT

CONTROL LOOP DESIGN AND EQUATIONS

Figure 2 is a simplified schematic diagram of the overall control loop.

Figure 2. Control Loop

POWER STAGE TRANSFER FUNCTION

The power stage transfer function of the ADP1822 is given by

the following equation:

(14)

(15)

where:

is the ESR of the output capacitor.

R

C

R

is the series resistance of output inductor.

L

CONTROL CIRCUIT AND TRANSFER FUNCTION

Refer to the compensation circuit shown in Figure 3.

The equation for the compensation transfer function is

(16)

where:

The switching frequency is 300 kHz. For best performance, set

the crossover frequency to about 1/10 of switching frequency,

f

, or around 60 kHz. Lower crossover frequencies cause poor

SW

dynamic response, while higher crossover frequencies can cause

instability. The best performance usually results from the

highest possible crossover frequency that allows adequate gain

and phase margins. A phase margin in the range of 40° to 60° is

recommended.

Figure 3. Compensation Circuit

Rev. A | Page 7 of 16

Page 8

UG-366 Evaluation Board User Guide

RAMP

EA

VD

V

sGsG

sT

)()()(×

=

OVERALL LOOP GAIN

The transfer function for the overall control loop can be written as

(17)

where V

the ADP1822 controller.

is the PWM peak ramp voltage (typically 1.25 V) of

RAMP

Use the following guidelines to select the compensation

components:

1. Set the loop gain cross frequency f

place the cross frequency f

2. Cancel ESR zero f

Z

C

by compensator pole fP1.

3. Place the high frequency pole f

. A good choice is to

C

at fSW/10 for fast response.

to achieve maximum

P2

attenuation of switching ripple and high frequency noise.

4. Place two compensator zeros nearby at the power stage

resonant frequency f

place f

between fO and fC.

Z2

. Typically, place fZ1 below fO and

O

5. Check the phase margin to ensure good regulation

performance.

Rev. A | Page 8 of 16

Page 9

Evaluation Board User Guide UG-366

06388-004

CH1 20.0V M4.00µs A CH1 1.20mV

T 42.80%

1

T

Δ: 16.8mV

@: –7.60mV

90

85

80

75

70

EFFICIENCY (%)

0 2 4 6 8 10 12

IO (A)

06388-006

95

VIN = 9V

V

IN

= 15V

V

IN

= 12V

3

06388-008

CH1 1.00V

CH3 1.00V

M20.0ms A CH3 1.86V

T 72.60%

Δ: 1.32mV

@: 1.78mV

T

1

06388-005

CH1 20.0mV M4.00µs A CH1 1.20mV

1

T 42.80%

Δ: 20.0mV

@: –9.20mV

T

3

06388-007

CH1 20.0mV M200µs A CH3 5.20A

1

T 405.200µs

T

Δ: 62.8mV

@: –32.8mV

CH3 5.00A Ω

4

2

06388-009

CH3 2.00V

CH2 2.00V M4.00ms A CH3 1.56V

T 29.80%

Δ: 1.76V

@: 4.44V

T

3

CH4 100mV

TEST RESULTS AND MAJOR WAVEFORMS

Figure 4. Output Voltage Ripple, Without Load,

Channel 1: Output Voltage

Figure 5. Efficiency vs. Load Current

Figure 7. Output Voltage Ripple,10 A,

Channel 1: Output Voltage

Figure 8. Load Transient Response,

Channel 1: Output Voltage (AC-Coupled), Channel 3: Output Current

Figure 6. Output Tracking,

Channel 1: Output Voltage, Channel 3: Tracking Input

Figure 9. Output Voltage with Margin Up and Margin Down,

Channel 2: MAR Pin (Blue Trace), Channel 3: MSEL Pin (Pink Trace), Channel

4: Output Voltage

Rev. A | Page 9 of 16

Page 10

UG-366 Evaluation Board User Guide

4

2

06388-010

CH3 2.00V

CH2 2.00V M1.00ms A CH2 1.56V

T 29.80%

T

Δ: 1.76V

@: 4.44V

CH4 100mV

3

PHASE (Degrees)

10 100 1k 10k 100k 1M

FREQUENCY

(Hz)

GAIN (dB)

80

60

40

20

0

–20

–40

–60

140

120

100

80

60

40

20

0

06388-012

100

GAIN

PHASE

06388-011

CH3 2.00V

CH2 2.00V M1.00ms A CH2 1.56V

T 31.40%

T

Δ: 1.76V

@: 4.44V

CH4 100mV

4

2

3

Figure 10. Output Voltage Margin Down,

Channel 2: MAR Pin, Channel 3: MSEL Pin, Channel 4: Output Voltage

Figure 11. Control Loop,

Cross Frequency: 35.4 kHz, Phase Margin: 63.1°

Figure 12. Output Voltage Margin Up,

Channel 2: MAR Pin, Channel 3: MSEL Pin, Channel 4: Output Voltage

Rev. A | Page 10 of 16

Page 11

Evaluation Board User Guide UG-366

PCB LAYOUT GUIDELINES

1. Use separate analog and power ground planes. Connect the

analog circuitry to analog ground. Connect the power

circuitry to power ground.

2. To keep the inductance down, the traces from the high-

side MOSFET and the low-side MOSFET to the DH and

DL pins of the ADP1822, respectively, need to be relatively

short and wide.

3. Place the source of Q1 and the drain of Q2 very close to

each other to minimize inductance. Use a wide copper

trace for this connection. However, too much copper area

on this switch node can increase capacitive-coupled

common-mode noise.

4. Place ceramic input decoupling capacitors (C2, C3, and

C4) close to the Q1 drain and the Q2 source.

5. Place C13 and C14 close to the V

6. The compensation components should also be placed as

close as possible to the FB pin.

7. Connect the trace connecting R7 should be directly to the

drain of Q2 to ensure an ideal Kelvin connection,.

pin of the IC.

IN

Rev. A | Page 11 of 16

Page 12

UG-366 Evaluation Board User Guide

NC

PVCC

DL

PGND

CSL

VCC

MUP

MDN

BST

DH

SW

SYNC

FREQ

MAR

TRKN

TRKP

ADP1822

1

2

3

4

5

6

7

8

24

23

21

20

19

15

14

13

DH

SW

SYNC

1

PWGD

1

U1

SW

06388-001

V

IN

DGND AGND PGND

Q2

IRFR3711Z

DH

SW

DL

M1

CON4

4

3

2

1

M2

CON4

4

3

2

1

LOW_S

M3

CON4

1

2

3

4

CON4

1

2

3

4

M4

C1

180µF

20V

C2

10µF

16V

C3

1µF

25V

C4

1µF

25V

R14

0Ω, 1%

R15

0Ω, 1%

Q1

IRFR3711Z

L1

2.2µH, 5. 5mΩ

C5

680µF

4V

C6

680µF

4V

C7

22µF

10V

C8

22µF

10V

C9

1µF

10V

C10

1µF

10V

V

OUT

Q3

MMBT2222

R5

1.2kΩ

1%

D1

BZX84C5V6

C13

1µF

16V

R10

10kΩ

1%

SHDN

PWGD

DGND

GND

9

10

11

12

DGND AGND

C12

22nF

16V

16

R12

133kΩ

1%

AGNDAGND

DGND

J4

17

18

D2

BAT54

C15

0.1µF

16V

22

DL

R6

10Ω

1%

C14

1µF

16V

R16

10Ω

5%

AGND

R17

10kΩ

5%

J3

R9

10kΩ

1%

J1

J2

R8

10kΩ

1%

R11

10kΩ

1%

C16

2.2pF

16V

R7

3kΩ

1%

R13

246kΩ

1%

R3

82kΩ

1%

C17

1nF

16V

C19

18pF

AGND

R2

10kΩ

1%

R1

20kΩ

1%

R4

2.7kΩ

1%

C18

1.8nF

16V

V

OUT

V

OUT

C20

1nF

16V

TRKN

1

MSEL

COMP

FB

SS

J1:

J2:

J3:

J4:

OPEN = 300kHz

SHORT = 600kHz

OPEN = ENABLE

SHORT = DIS ABLE

OPEN = HIG H M ARGIN

SHORT = LOW MARGIN

OPEN = ACTIVE VOLTAGE MARGIN

SHORT = NO M ARGIN

06388-013

EVALUATION BOARD SCHEMATIC AND LAYOUT

Figure 13. Typical Application Schematic Diagram

Figure 14. Top Layer

Rev. A | Page 12 of 16

Page 13

Evaluation Board User Guide UG-366

06388-014

06388-015

Figure 15. Bottom Layer

Figure 16. Silkscreen Top

Rev. A | Page 13 of 16

Page 14

UG-366 Evaluation Board User Guide

34

Jumper

Any

Any

J1, J2, J3, J4

4

ORDERING INFORMATION

BILL OF MATERIALS

Table 5. Bill of Materials for ADP1822 Typical Application Circuit (12 V to 1.8 V @ 10 A, fSW = 300 kHz)

Item Description Manufacturer Part No. Designator Qty

1 Capacitor, OS-CON, 180 μF, 20 V, 20 mΩ,

11 mm × 10 mm × 5 mm

2 Capacitor, Ceramic, 10 μF, 25 V, X5R,1206 Murata GRM31CR61E106KA12 C2 1

3 Capacitor, Ceramic, 1 μF, 25 V, X5R, 0603 Murata GRM188R61E105KA12 C3, C4 2

4 Capacitor, Ceramic, 1 μF, 16 V, X5R, 0603 Murata GRM185R61C105KE44 C9, C10 2

5 Capacitor, OS-CON, 680 μF, 4 V, 7 mΩ,

13 mm × 8 mm × 3.5 mm

6 Capacitor, Ceramic, 22 μF, 10 V, X5R, 1210 Murata GRM32NR61A226KE19 C7, C8 2

7 Capacitor, Ceramic, 22 nF, 16 V, X7R, 0603 Vishay or equivalent VJ0603Y233KXXA C12 1

8 Capacitor, Ceramic, 1 μF, 16 V, X5R, 0603 Murata GRM188R61C105KA93 C13, C14 2

9 Capacitor, Ceramic, 0.1 μF, 16 V, X7R, 0603 Vishay or equivalent VJ0603Y104MXQ C15 1

10 Capacitor, Ceramic, 2.2 pF, 16 V, NPO, 0603 Vishay or equivalent VJ0603Y2R2KXXA C16 1

11 Capacitor, Ceramic, 1 nF, 16 V, X7R, 0603 Vishay or equivalent VJ0603Y102KXXA C17, C20 2

12 Capacitor, Ceramic, 1.8 nF, 16 V, X7R, 0603 Vishay or equivalent VJ0603Y182KXXA C18 1

13 Capacitor, Ceramic, 18 pF, NPO, 0603 Vishay or equivalent VJ0603Y180KXXA C19 1

15 Diode, Zener, 5.6 V, SOT-23 FairChild BZX84C5V6LT1 D1 1

16 Diode, Schottky, 30 V, SOT-23 FairChild BAT54 D2 1

17 Inductor, 2.2 μH, 5.2 mΩ, 13 A (rms) Cooper Bussmann HC7-2R2 L1 1

18 N MOSFET, 30 V, 61 A, 6.5 mΩ, D-PAK, 17 nC IR IRFR3709ZPBF Q1,Q2 2

19 Transistor, BJT-NPN, 40 V, SOT-23 ON Semiconductor MMBT2222 Q3 1

20 Resistor, 20 kΩ, 1/10 W, 1%, 0603 Vishay or equivalent CRCW06032002F R1 1

21 Resistor, 10 kΩ, 1/10 W, 1%, 0603 Vishay or equivalent CRCW06031002F R2, R8, R9, R10,

22 Resistor, 82 kΩ, 1/10 W, 1%, 0603 Vishay or equivalent CRCW06038202F R3 1

23 Resistor, 2.7 kΩ, 1/10 W, 1%, 0603 Vishay or equivalent CRCW06032701F R4 1

24 Resistor, 1.2 kΩ, 1/10 W, 1%, 0603 Vishay or equivalent CRCW06031201F R5 1

25 Resistor, 10 Ω, 1/10 W, 1%, 0603 Vishay or equivalent CRCW060310R0F R6 1

26 Resistor, 3 kΩ, 1/10 W, 1%, 0603 Vishay or equivalent CRCW06033001F R7 1

27 Resistor, 133 kΩ, 1/10 W, 1%, 0603 Vishay or equivalent CRCW06031334F R12 1

28 Resistor, 246 kΩ, 1/10 W, 1%, 0603 Vishay or equivalent CRCW06032464F R13 1

29 Resistor, 0 Ω, 1/10 W, 1%, 0603 Vishay or equivalent CRCW06030R0F R14, R15 2

30 Resistor, 10 kΩ, 1/10 W, 5%, 0603 Vishay or equivalent CRCW06031002J R16, R17 2

32 Input and Output Terminal Keystone Electronics CAT.NO.8191 M1, M2, M3, M4 4

33 Tes t Point Any Any PWGD, SYNC,

Sanyo 20SP180M C1 1

Sanyo 4SEPC680M C5, C6 2

5

R11

5

TRKN, VOUT, GND

35 IC— 20 A Step Down DC-to-DC Controller

Analog Devices ADP1822 U1 1

with Tracking and Margining

Rev. A | Page 14 of 16

Page 15

Evaluation Board User Guide UG-366

NOTES

Rev. A | Page 15 of 16

Page 16

UG-366 Evaluation Board User Guide

LY. Customer understands and agrees that the Evaluation Board is provided

SORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER’S POSSESSION OR USE OF

in accordance with the substantive laws of the Commonwealth of

NOTES

ESD Caution

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection

circuitry, damage may occur on devices subjected to high e nergy ESD. Therefore, proper ESD precaution s should be taken to avoid performance degradation or loss of functionality.

Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the “Evaluation Board”), you are agreeing to be bound by the terms and conditions

set forth below (“Agreement”) unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale s hall govern. Do not use the Evaluation Board until you

have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you (“Customer”) and Analog Devices, I nc.

(“ADI”), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. S ubject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal,

temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ON

for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Further more, the license granted is expressly made subject to the following additional

limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluati on Board. As used herein, the term

“Third Party” includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including

ownership of t he Evaluation Board, are res erved by ADI. CONFIDENTIA LITY. This Agreement and the Evaluation Board shall all be considered the confidential and p roprietary information of ADI. Customer may

not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to

promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any

occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board.

Modifications to the Evaluation Board must comply with applicable law, including but not limited to the Ro HS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice

to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED “AS IS” AND ADI MAKES NO

WARRANTIES OR REP RESENTATI ONS OF ANY KIN D WITH RESPECT TO IT. ADI S PECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDO RSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED

TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL

PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICEN

THE EVALUATION BOARD, INCLUD ING BUT NOT LIMITED TO LOST PROFITS, DE LAY COSTS, LABOR COSTS OR LOSS OF GOO DWILL. ADI’S TOTAL LIABILIT Y FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE

AMOUNT OF ONE HUNDRED US DOLLARS ($100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable

United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed

Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in t he state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby

submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the Internation al Sale of Goods shall not apply to this Agreement an d is expressly disclai med.

©2006–2011 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

UG06388-0-12/11(A)

Rev. A | Page 16 of 16

Loading...

Loading...