Page 1

2998

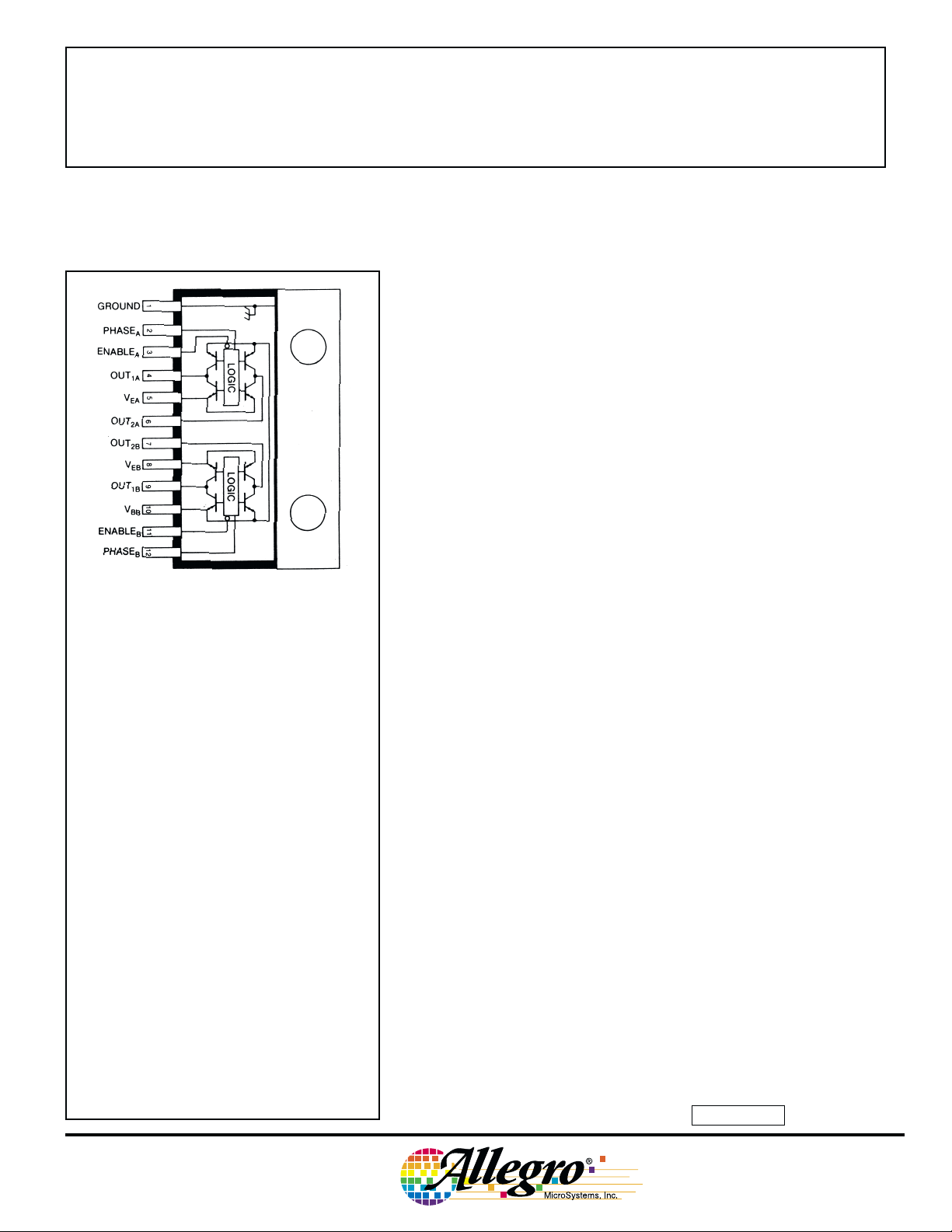

DUAL FULL-BRIDGE

MOTOR DRIVER

As an interface between low-level logic and solenoids, dc (brush)

motors, or stepper motors, the UDN2998W dual full-bridge driver will

operate inductive loads up to 50 V with continuous output currents of

up to 2 A per bridge or peak (start-up) currents to 3 A. The control

inputs are compatible with TTL, DTL, and 5 V CMOS logic. Except

for a common supply voltage and thermal shutdown, the two drivers in

each package are completely independent.

For external PWM control, an Output Enable for each bridge

circuit is provided and the sink driver emitters are pinned out for

connection to external current-sensing resistors. The chopper drive

mode is characterized by low power dissipation levels and maximum

efficiency. A PHASE input to each bridge determines load-current

direction.

Data Sheet

29319.6B†

Dwg. No. W-106

ABSOLUTE MAXIMUM RATINGS

at T

≤ +150°C

J

Supply Voltage, VBB.......................... 50 V

Output Current, I

(peak) ........................................... ±3 A

Sink Driver Emitter Voltage, VE...... 1.5 V

Logic Input Voltage Range,

V

or V

PHASE

Package Power Dissipation,

PD....................................... See Graph

Operating Temperature Range,

TA.............................. -20°C to +85°C

Storage Temperature Range,

TS............................. -55°C to +150°C

NOTE: Output current rating may be limited

by chopping frequency, ambient temperature, air flow, or heat sinking. Under any set

of conditions, do not exceed the specified

current rating or a junction temperature of

+150°C.

(continuous) ..... ±2 A

OUT

....... -0.3 V to 15 V

ENABLE

Extensive circuit protection is provided on-chip. Both groundclamp and flyback diodes for each bridge are provided. A thermal

shutdown circuit disables the load drive if chip temperature rating

(package power dissipation) is exceeded. Internally-generated delays

provide crossover-current protection.

The UDN2998W is packaged in a 12-pin single in-line power-tab

package for high power capabilities. Driving either of the bridges at

the full 2 A dc rating requires the use of an external heat sink. The tab

is at ground potential and needs no insulation.

FEATURES

■ ±3 A Peak Output Current

■ Output Voltage to 50 V

■ Integral Output Suppression Diodes

■ Output Current Sensing

■ TTL/CMOS Compatible Inputs

■ Internal Thermal Shutdown Circuitry

■ Crossover-Current Protected

■ Automotive Capable

Always order by complete part number: UDN2998W .

Page 2

2998

DUAL FULL-BRIDGE

MOTOR DRIVER

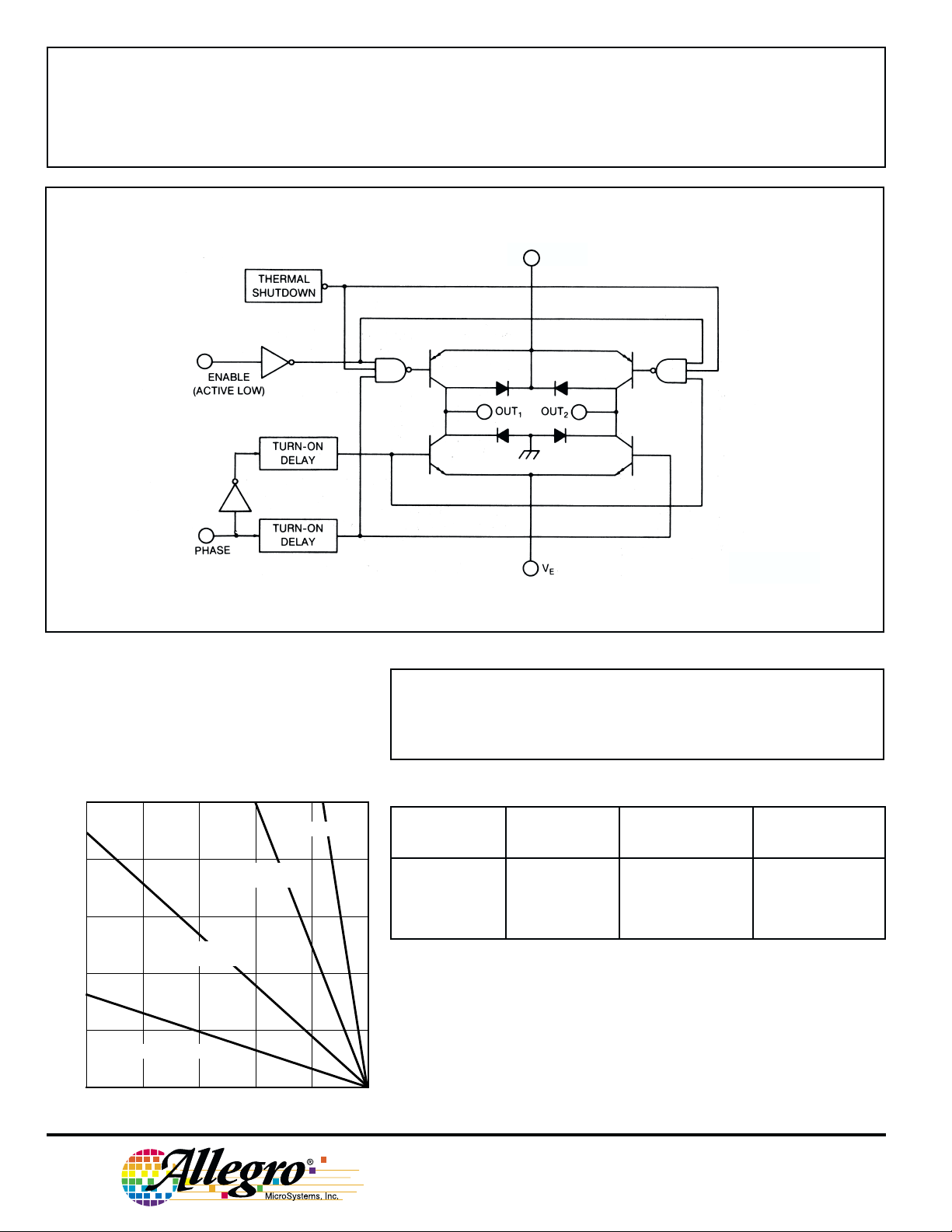

FUNCTIONAL BLOCK DIAGRAM

(ONE OF TWO DRIVERS)

BB

Dwg. No. W-107A

To maintain isolation between integrated circuit components and to

provide for normal transistor operation, the ground tab must be

connected to the most negative point in the external circuit.

10

R = 2.0°C/W

θJT

8

6

12°C/W HEAT SINK

4

2

FREE AIR, R = 38°C/W

3.0°C/W HEAT SINK

R = 14°C/W

θJA

θJA

R = 5.0°C/W

θJA

ENABLE PHASE

INPUT INPUT OUTPUT 1 OUTPUT 2

Low High High Low

Low Low Low High

High High Open Low

High Low Low Open

TRUTH TABLE

0

ALLOWABLE PACKAGE POWER DISSIPATION IN WATTS

25

50 75 100 125 150

TEMPERATURE IN °C

Dwg. GP-012B

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Copyright © 1985, 2000 Allegro MicroSystems, Inc.

Page 3

2998

DUAL FULL-BRIDGE

MOTOR DRIVER

ELECTRICAL CHARACTERISTICS at TA = +25°C, TJ ≤ +150°C, VBB = 50 V

Limits

Characteristic Symbol Test Conditions Min. Typ. Max. Units

Output Drivers

Operating Voltage Range V

Output Leakage Current I

Output Saturation Voltage V

Output Sustaining Voltage V

Source Driver Rise Time t

Source Driver Fall Time t

Deadtime t

Clamp Diode Leakage Current I

Clamp Diode Forward Voltage V

Supply Current I

Control Logic (PHASE or ENABLE)

Logic lnput Voltage V

V

Logic Input Current I

I

Turn-On Delay Time t

Turn-Off Delay Time t

NOTES:1. Each driver is tested separately.

2. Test is performed with V

= 0.8 V and then repeated for V

PHASE

3. Negative current is defined as coming out of (sourcing) the specified device pin.

BB

CEX

CE(SAT)

CE(sus)

r

f

d

R

F

BB

IN(0)

IN(1)

IN(0)

IN(1)

pd0

pd1

10 — 50 V

V

= 50 V, V

OUT

V

= 0, V

OUT

I

= 1 A, Sink Driver — 1.2 1.4 V

OUT

I

= 2 A, Sink Driver — 1.7 1.9 V

OUT

I

= -1 A, Source Driver — 1.7 1.9 V

OUT

I

= -2 A, Source Driver — 2.0 2.2 V

OUT

I

= ±2 A, L = 3.5 mH, Note 2 50 — — V

OUT

I

= -2 A — 500 — ns

OUT

I

= -2 A — 750 — ns

OUT

I

= ±2 A — 2.5 — µs

OUT

ENABLE

= 2.0 V, Note 2 — <5.0 50 µA

ENABLE

= 2.0 V, Note 2 — <-5.0 -50 µA

VR = 50 V — <5.0 50 µA

IF = 2 A — 1.5 2.0 V

V

ENABLE(1)

= V

ENABLE(2)

= 0.8 V — 30 35 mA

— — 0.8 V

2.0 — — V

V

PHASE

V

PHASE

or V

or V

= 0.8 V — -5.0 -25 µA

ENABLE

= 2.0 V — <1.0 10 µ A

ENABLE

ENABLE Input to Source Drivers — 0.4 1.0 µs

ENABLE Input to Source Drivers — 2.0 4.0 µs

= 2.0 V.

PHASE

www.allegromicro.com

Page 4

2998

DUAL FULL-BRIDGE

MOTOR DRIVER

V

ENABLE

V

PHASE

+

I

OUT

–

INPUT

INPUT

t

pd

t

d

90%

t

90%

pd

0%

t

d

t

r

t

f

Dwg. WM-001

Dwg. WM-001

TYPICAL APPLICATION

2-PHASE BIPOLAR STEPPER MOTOR DRIVE

(Chopper Mode)

+5V

A

0

+5V

B

0

Dwg. No. A-12,454

Dwg. EP-025

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Page 5

Dimensions in Inches

(controlling dimensions)

2998

DUAL FULL-BRIDGE

MOTOR DRIVER

INDEX

AREA

0.065

0.035

0.020

1.260

1.240

0.775

0.765

0.245

0.225

0.180

0.155

MAX

0.055

0.045

ø

0.145

0.140

0.135

0.570

0.365

1

0.030

0.020

12

0.100

±0.010

0.540

0.290

0.023

0.018

MIN

0.100

0.080

0.070

Dwg. MP-007 in

www.allegromicro.com

NOTES: 1. Lead thickness is measured at seating plane or below.

2. Lead spacing tolerance is non-cumulative.

3. Exact body and lead configuration at vendor’s option within limits shown.

4. Lead gauge plane is 0.030” below seating plane.

5. Supplied in standard sticks/tubes of 15 devices.

Page 6

2998

DUAL FULL-BRIDGE

MOTOR DRIVER

Dimensions in Millimeters

(for reference only)

INDEX

AREA

1.65

0.89

0.51

1

32.00

31.49

19.69

19.45

0.76

0.51

12

6.22

5.71

3.56

9.27

2.54

±0.254

3.94

3.68

4.57

MAX

ø

14.48

13.71

7.36

MIN

0.59

0.45

1.40

1.14

3.43

2.54

2.03

1.77

Dwg. MP-007 mm

NOTES: 1. Lead thickness is measured at seating plane or below.

The products described here are manufactured under one or more

U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to

time, such departures from the detail specifications as may be required

to permit improvements in the performance, reliability, or

manufacturability of its products. Before placing an order, the user is

cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components

in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and

reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of

third parties which may result from its use.

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

2. Lead spacing tolerance is non-cumulative.

3. Exact body and lead configuration at vendor’s option within limits shown.

4. Lead gauge plane is 0.762 mm below seating plane.

5. Supplied in standard sticks/tubes of 15 devices.

Loading...

Loading...