Page 1

TICPAL22V10Z-25C, TICPAL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

• 24-Pin Advanced CMOS PLD

• Virtually Zero Standby Power

• Propagation Delay Time:

I, I/O to I/O in the Turbo Mode

-25C . . . 25 ns Max

-30I . . . 30 ns Max

I, I/O to I/O in the Zero-Power Mode

-25C . . . 35 ns Max

-30I . . . 40 ns Max

CLK to Q

-25C . . . 15 ns Max

-30I . . . 20 ns Max

• Variable Product Term Distribution Allows

More Complex Functions to Be

Implemented

• Each Output Is User-Programmable for

Registered or Combinatorial Operation,

Polarity, and Output Enable Control

• Extra Terms Provide Logical Synchronous

Set and Asynchronous Reset Capability

• Preload Capability on All Registered

Outputs Allow for Improved Device Testing

• UV Light Erasable Cell Technology Allows

for:

Reconfigurable Logic

Reprogrammable Cells

Full Factory Testing for High

Programming Yield

• Programmable Design Security Bit

Prevents Copying of Logic Stored in Device

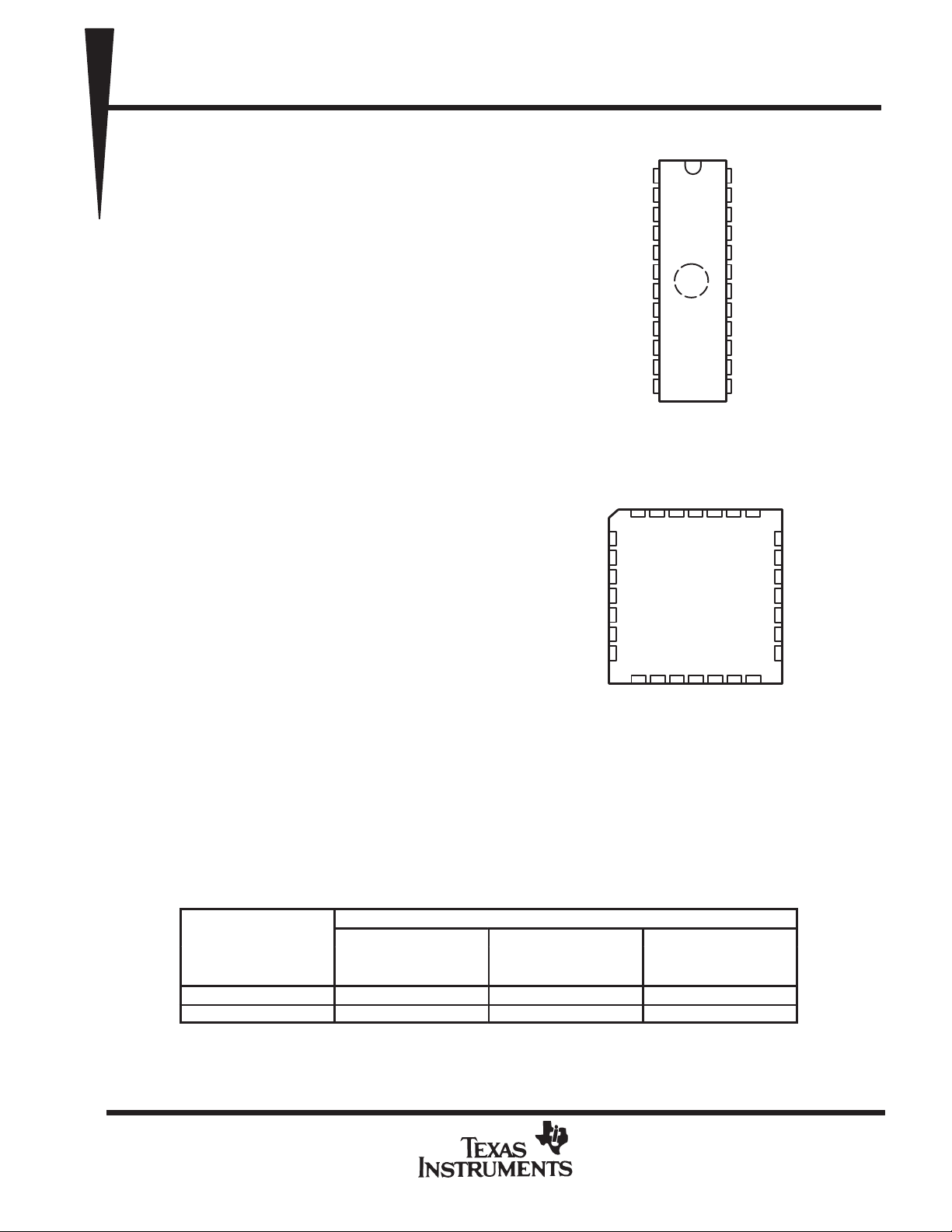

JTL AND NT PACKAGE

(TOP VIEW)

NC

24

23

22

21

20

19

18

17

16

15

14

13

V

I

CC

V

CC

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I

I/O/Q

25

24

23

22

21

20

19

I/O/Q

I/O/Q

CLK/I

GND

I

I

I

NC

I

I

I

1

I

2

I

3

I

4

I

5

I

6

I

7

I

8

I

9

I

10

I

11

12

FN PACKAGE

(TOP VIEW)

I

I

CLK/INCI/O/Q

3212827

426

5

6

7

8

9

10

11

12 13

14 15 16 1718

I

I

GND

– No internal connection

NC

Pin assignments in operating mode

I/O/Q

I/O/Q

I/O/Q

NC

I/O/Q

I/O/Q

I/O/Q

• Package Options Include Plastic

Dual-In-Line and Clip Carrier [for

One-Time-Programmable (OTP) Devices]

and Ceramic Dual-In-Line Windowed

Package

.

T

A

RANGE

0°C to 75°C TICPAL22V10Z-25CJTL TICPAL22V10Z-25CNT TICPAL22V10Z-25CFN

–40°C to 85°C NA TICPAL22V10Z-30INT TICPAL22V10Z-30IFN

These devices are covered by U.S. Patent 4,410,987.

EPIC is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

CERAMIC WINDOWED

DUAL-IN-LINE

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

AVAILABLE OPTIONS

(JTL)

PACKAGE TYPE

PLASTIC

DUAL-IN-LINE

(NT)

PLASTIC

CHIP CARRIER

(FN)

Copyright 1992, Texas Instruments Incorporated

1

Page 2

TICPAL22V10Z-25C, TICPAL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

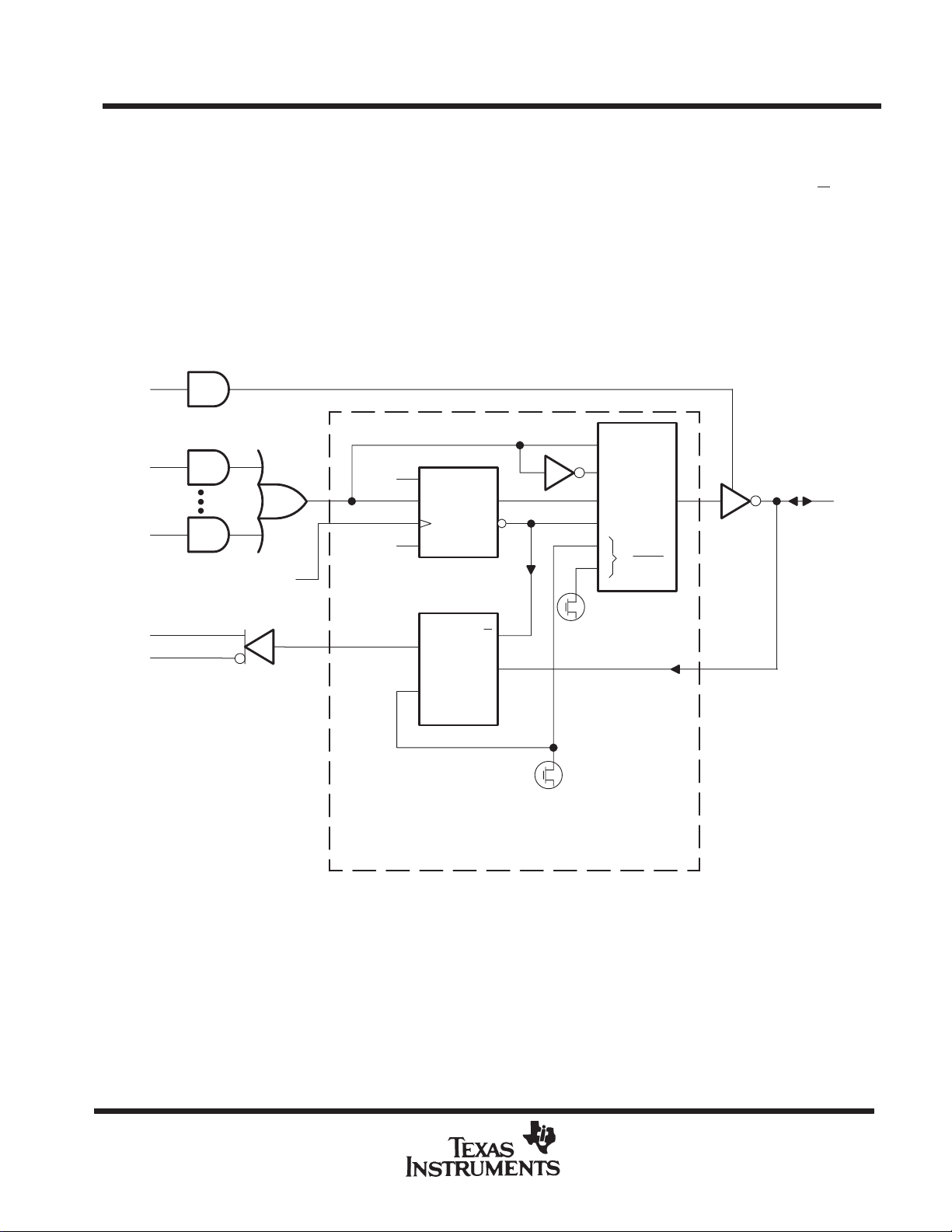

description

The CMOS PLD devices feature variable product terms, flexible outputs, and virtually zero standby power. It

combines TI’s EPIC (Enhanced Processed Implanted CMOS) process with ultraviolet-light-erasable EPROM

technology. Each output has an output logic macrocell (OLM) configuration allowing for user definition of the

output type. This device provides reliable, low-power substitutes for numerous high-performance TTL PLDs with

gate complexities between 300 and 800 gates.

The TICPAL22V10Z has 12 dedicated inputs and 10 user-definable outputs. Individual outputs can be

programmed as registered or combinational and inverting or noninverting as shown in the OLM diagram. These

ten outputs are enabled through the use of individual product terms

The variable product-term distribution on this device removes rigid limitation to a maximum of eight product

terms per output. This technique allocates from 8 to 16 logical product terms to each output for an average of

12 product terms per output. The variable allocation of product terms allows for far more complex functions to

be implemented in this device than in previously available devices.

With features such as the programmable OLMs and the variable product-term distribution, the TICP AL22V10Z

offers quick design and development of custom LSI functions. Since each of the ten output pins may be

individually configured as inputs on either a temporary or permanent basis, functions requiring up to 21 inputs

and a single output or down to 12 inputs and 10 outputs can be implemented with this device.

Design complexity is enhanced by the addition of synchronous set and asynchronous reset product terms.

These functions are common to all registers. When the synchronous set product term is a logic 1, the output

registers are loaded with a logic 1 on the next low-to-high clock transition. When the asynchronous reset product

term is a logic 1, the output registers are loaded with a logic 0 independently of the clock. The output logic level

after set or reset will depend on the polarity selected during programming.

Output registers of this device can be preloaded to any desired state during testing, thus allowing for full logical

verification during product testing.

The TICP AL22V10Z has internal electrostatic discharge (ESD) protection circuits and has been classified with

a 2000-V ESD rating tested under MIL-STD-883C, Method 3015.6. However, care should be exercised in

handling these devices, as exposure to ESD may result in a degradation of the device parametric performance.

The floating-gate programmable cells allow the devices to be fully programmed and tested before assembly to

assure high field programming yield and functionality . They are then erased by ultraviolet light before packaging.

The TICPAL22V10Z-25C is characterized for operation from 0°C to 75°C. The TICPAL22V10Z-30I is

characterized for operation from –40°C to 85°C.

design security

The ’PAL22V10Z contains a programmable design security cell. Programming this cell will disable the read

verify and programming circuitry protecting the design from being copied. The security cell is usually

programmed after the design is finalized and released to production. A secured device will verify as if every

location in the device is programmed. Because programming is accomplished by storing an invisible charge

instead of opening a metal link, the ’22V10Z cannot be copied by visual inspection. Once a secured device is

fully erased, it can be reprogrammed to any desired configuration.

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 3

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

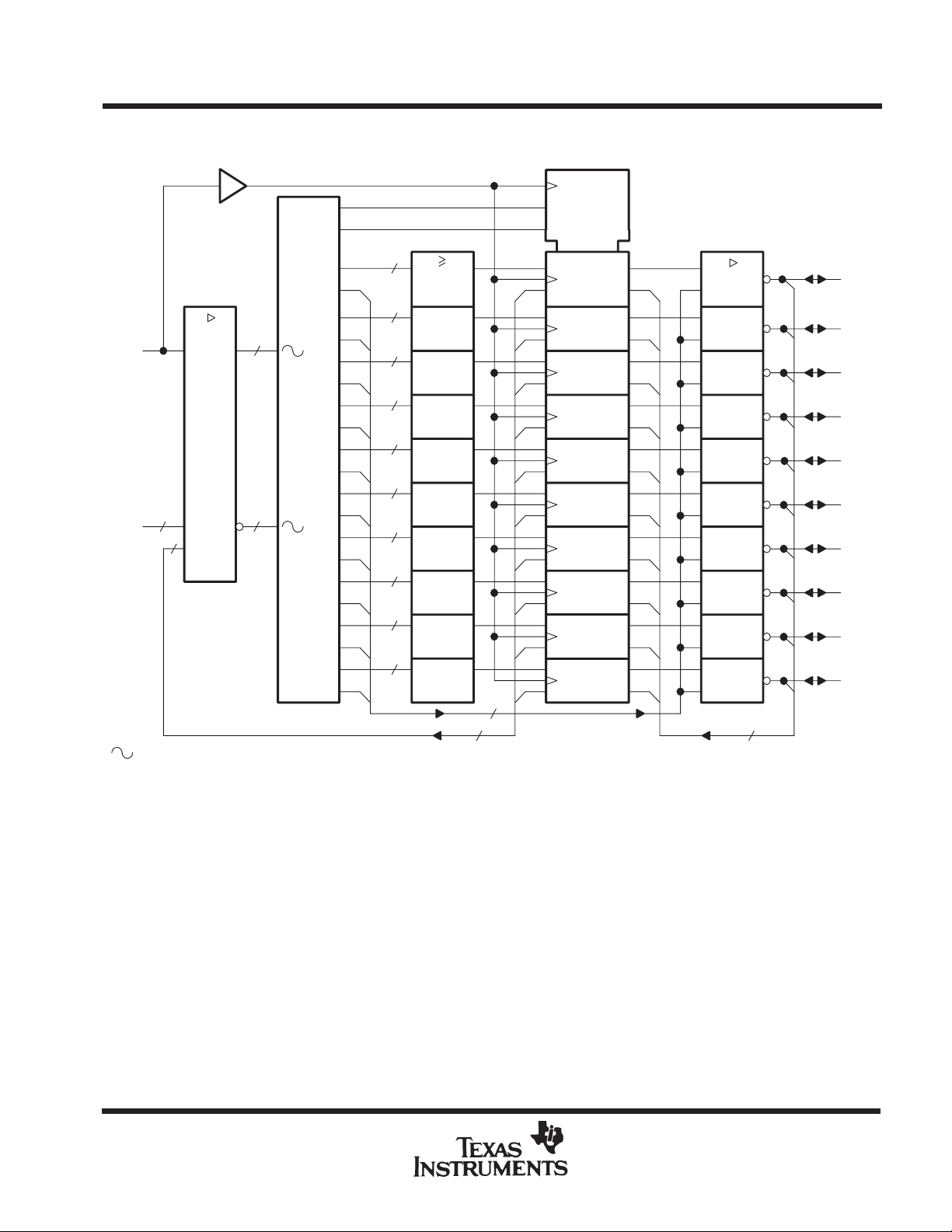

functional block diagram (positive logic)

TICPAL22V10Z-25C, TICPAL22V10Z-30I

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

CLK/I

C1

1S

R

Output

Logic

Macrocell

EN

EN

EN

EN

EN

EN

EN

EN

EN

EN

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

10

10

12

14

16

16

14

12

10

Set

Reset

8

8

1

10

10

&

44 x 132

22

11

I

10

22

denotes programmable cell inputs

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

Page 4

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

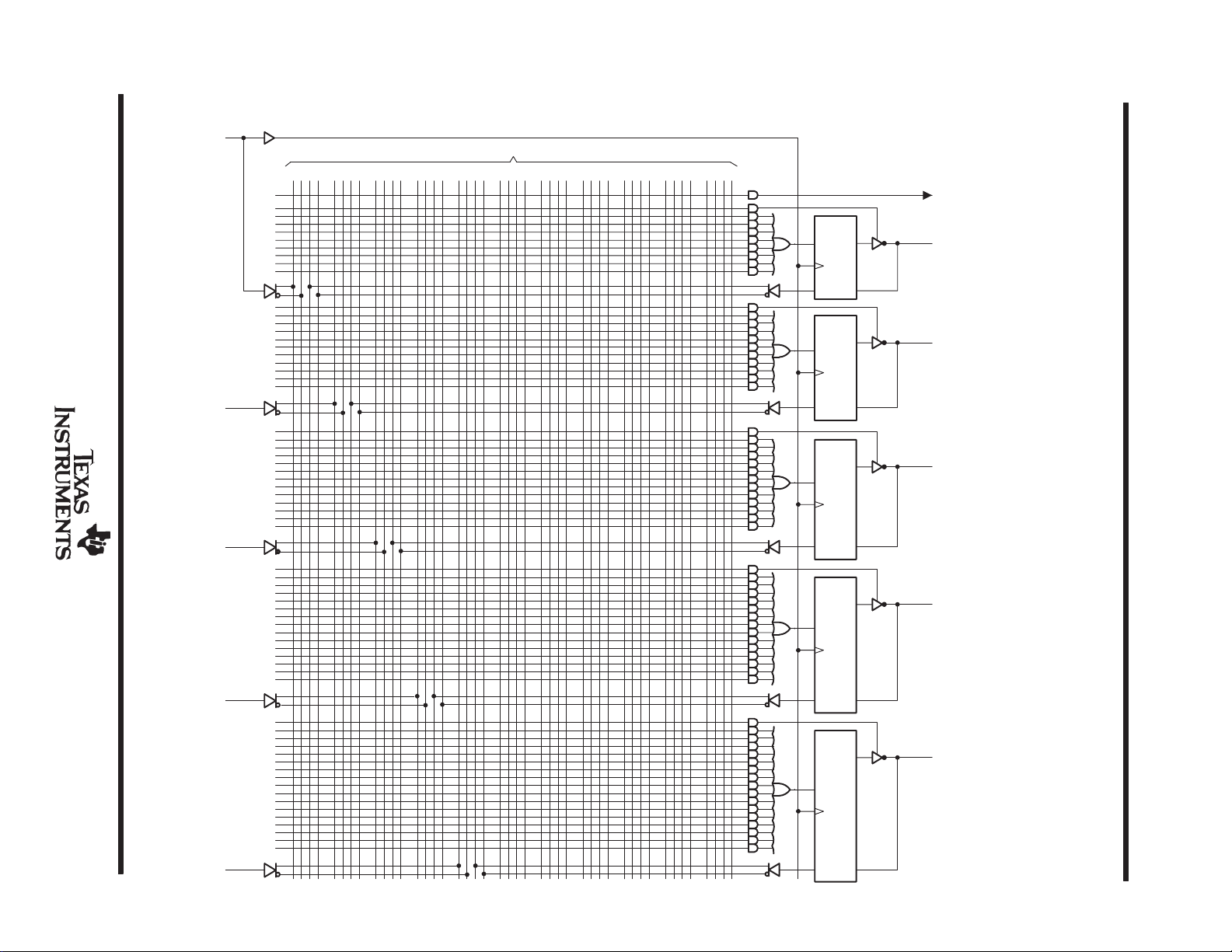

logic diagram (positive logic)

1

CLK/I

First

Cell

Numbers

2

I

3

I

0 481216 20 24 28

0

396

440

880

924

1452

1496

Increment

32 36 40

MACRO

CELL

P = 5808

R = 5809

MACRO

CELL

P = 5810

R = 5811

MACRO

CELL

P = 5812

R = 5813

MACRO

CELL

Asynchronous Reset

(to all registers)

23

I/O/Q

22

I/O/Q

21

I/O/Q

20

I/O/Q

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

TICPAL22V10Z-25C, TICPAL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

2112

4

I

2156

2860

5

I

P = 5814

R = 5815

MACRO

CELL

P = 5816

R = 5817

19

I/O/Q

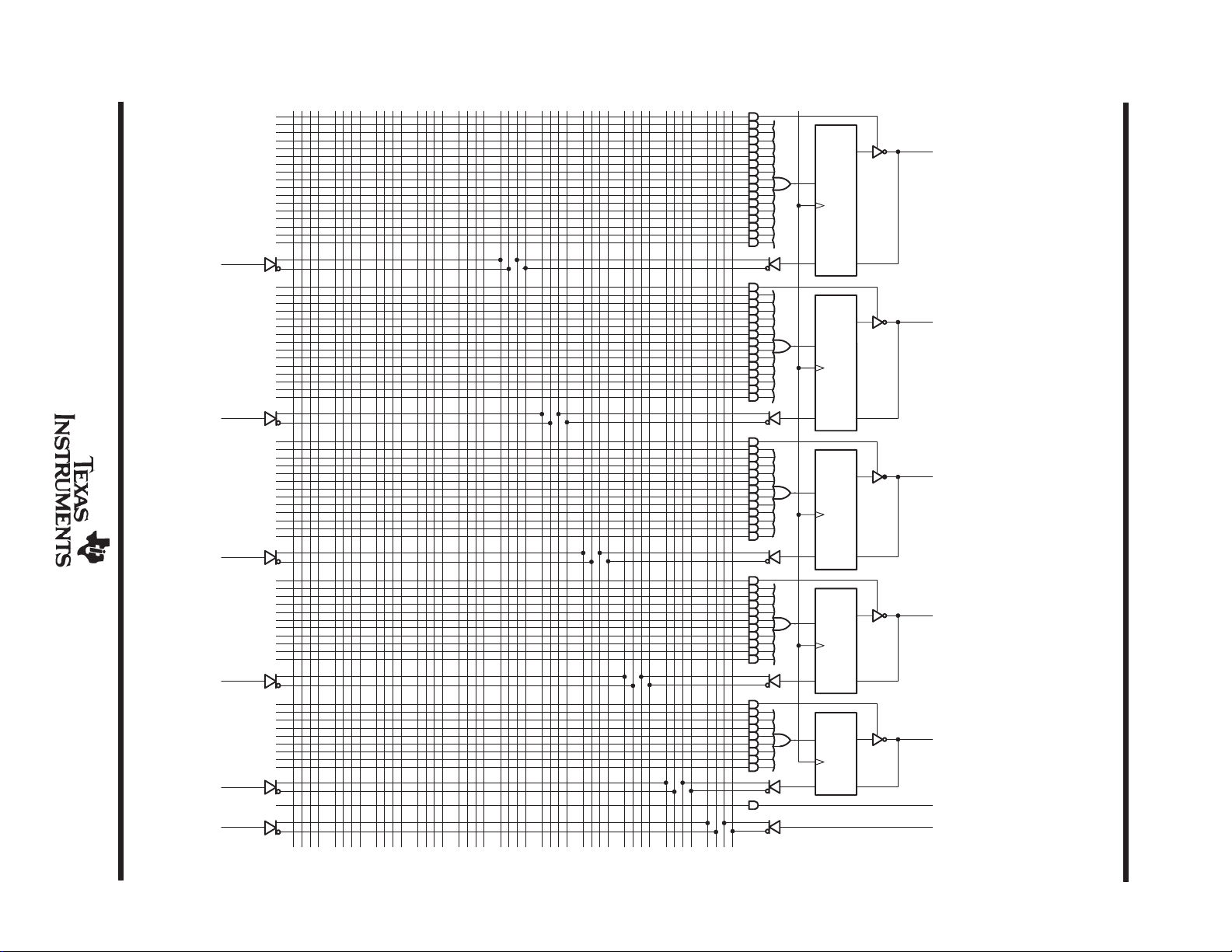

Page 5

2904

MACRO

CELL

3608

6

I

3652

P = 5818

R = 5819

MACRO

CELL

18

17

I/O/Q

I/O/Q

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

4268

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

7

I

4312

4840

8

I

4884

5324

9

I

5368

5720

10

I

5764

11

I

P = 5820

R = 5821

MACRO

CELL

P = 5822

R = 5823

MACRO

CELL

P = 5824

R = 5825

MACRO

CELL

P = 5826

R = 5827

16

I/O/Q

15

I/O/Q

14

I/O/Q

Synchronous Set

(to all registers)

13

I

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

TICPAL22V10Z-25C, TICPAL22V10Z-30I

5

Inside each MACROCELL the (P) cell is the polarity cell and the (R) cell is the register cell.

Programmable Cell Number = First Cell Number + Increment

Page 6

TICPAL22V10Z-25C, TICPAL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

output logic macrocell (OLM) description

A great amount of architectural flexibility is provided by the user-configurable macrocell output options. The

macrocell consists of a D-type flip-flop and two select multiplexers. The D-type flip-flop operates like a standard

TTL D-type flip-flop. The input data is latched on the low-to-high transition of the clock input. The Q and Q outputs

are made available to the output select multiplexer. The asynchronous reset and synchronous set controls are

available in all flip-flops.

The select multiplexers are controlled by programmable cells. The combination of these programmable cells

will determine which macrocell functions are implemented. It is this user control of the architectural structure

that provides the generic flexibility of this device.

output logic macrocell diagram

From Clock Buffer

Output Logic Macrocell

AR

SS

AR = asynchronous reset

SS = synchronous set

R

1D

C1

1S

MUX

1

1

G1

S1

S0

MUX

2

3

0

1

0

1

G

3

0

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 7

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

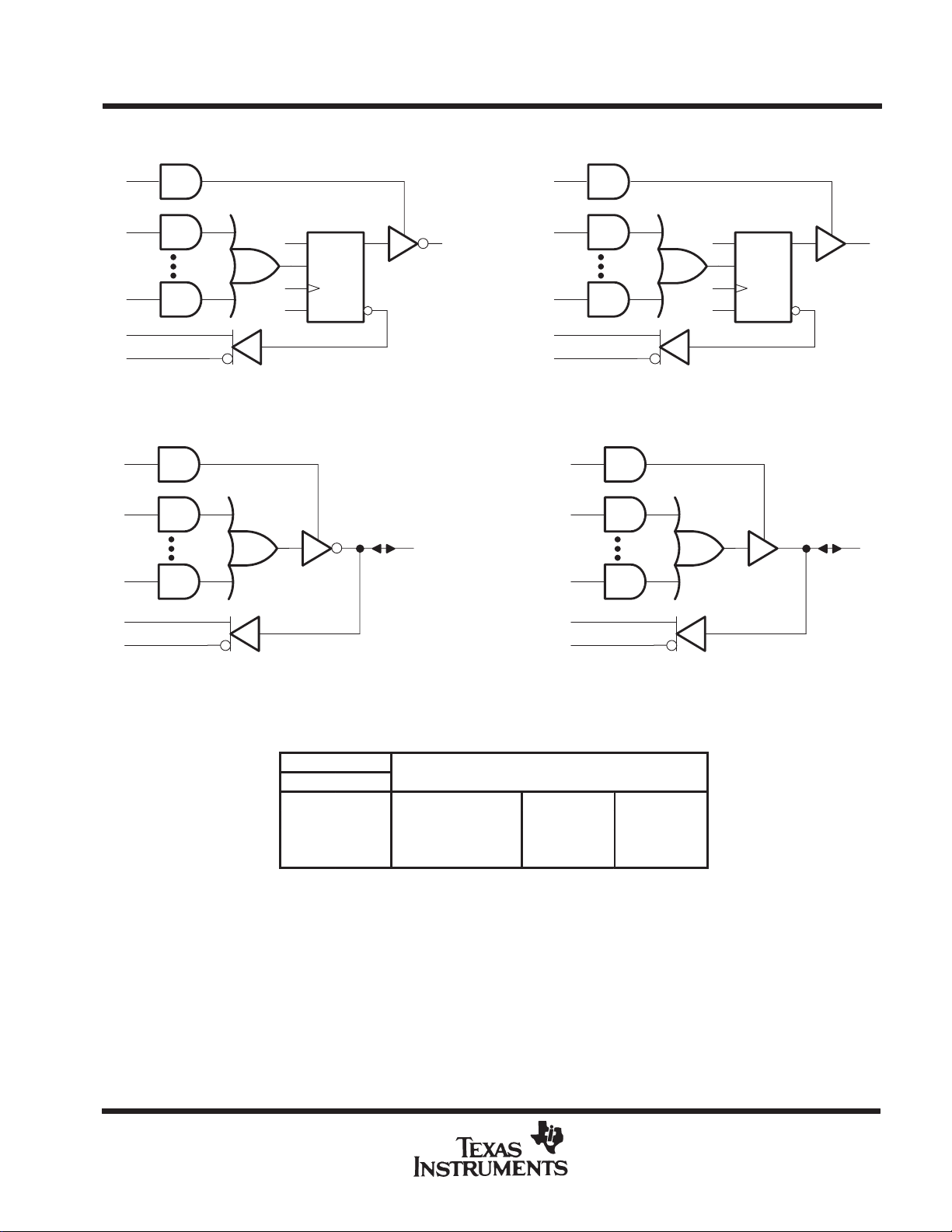

output logic macrocell options (see Figure 1)

TICPAL22V10Z-25C, TICPAL22V10Z-30I

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

R

1D

C1

1S

REGISTER FEEDBACK, REGISTERED, ACTIVE-LOW OUTPUT REGISTER FEEDBACK, REGISTERED, ACTIVE-HIGH OUTPUT

I/O FEEDBACK, COMBINATIONAL, ACTIVE-LOW OUTPUT I/O FEEDBACK, COMBINATIONAL, ACTIVE-HIGH OUTPUT

S1 = 0

S0 = 0

S1 = 1

S0 = 0

R

1D

1S

C1

S1 = 0

S0 = 1

S1 = 1

S0 = 1

MACROCELL FEEDBACK AND OUTPUT FUNCTION TABLE

CELL SELECT

S1 S0

0 0 Register feedback Registered Active low

0 1 Register feedback Registered Active high

1 0 I/O feedback Combinational Active low

1 1 I/O feedback Combinational Active high

0 = erased cell, 1 = programmed cell

S1 and S0 are select-function cells as shown in the output logic macrocell

diagram.

FEEDBACK AND OUTPUT CONFIGURATION

Figure 1. Resultant Macrocell Feedback and Output Logic After Programming

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

7

Page 8

TICP AL22V10Z-25C

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, VCC –0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, VI (see Note 1) –0.5 V to VCC+0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input clamp current, IIK (VI < 0 or V

Output clamp current, I

(VO < 0 or V

OK

> VCC) ± 20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I

> VCC) ± 20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

O

Continuous output current, IO (VO = 0 to VCC) ± 40 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 in) from case for 10 seconds: FN or NT package 260°C. . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 in) from case for 10 seconds: JTL package 300°C. . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range 0°C to 75°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: These ratings apply except for programming pins during a programming cycle or during a preload cycle.

recommended operating conditions

MIN NOM MAX UNIT

V

V

V

I

I

t

t

t

t

T

OH

OL

w

su

su

h

Supply voltage 4.75 5 5.25 V

CC

High-level input voltage 2 V

IH

Low-level input voltage 0.8 V

IL

High-level output current

Low-level output current mA

Pulse duration Clock low 10 ns

Setup time, turbo mode Asynchronous reset inactive 20 ns

Setup time, zero-power mode Asynchronous reset inactive 30 ns

Hold time Input or feedback 0 ns

Operating free-air temperature 0 75 °C

A

Driving TTL –3.2

Driving CMOS –4

Driving TTL 16

Driving CMOS 4

Clock high 10

Asynchronous reset 20

Input or feedback 17

Synchronous preset inactive 20

Input or feedback 25

Synchronous preset inactive 30

mA

†

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 9

TICPAL22V10Z-25C

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

electrical characteristics over recommended operating free-air temperature range

PARAMETER TEST CONDITION MIN TYP†MAX UNIT

V

OH

V

OL

I

OZH

I

OZL

I

IH

I

IL

I

O

I

CC

C

i

‡

§

I 6

I/O 10

VCC = 4.75 V, IOH = –3.2 mA for TTL 4 4.8

VCC = 4.75 V, IOH = –4 mA for CMOS 3.86 4.7

VCC = 4.75 V, IOL = 16 mA for TTL 0.25 0.5

VCC = 4.75 V, IOL = 4 mA for CMOS 0.07 0.4

VCC = 5.25 V, VO = 2.7 V 0.01 10 µA

VCC = 5.25 V, VO = 0.5 V –0.01 –10 µA

VCC = 5.25 V, VI = 5.25 V 0.01 10 µA

VCC = 5.25 V, VI = 0.5 V –0.01 –10 µA

VCC = 5.25 V, VO = 0.5 V –30 –45 –90 mA

VCC = 5.25 V,

Outputs open,

VI = 2 V, f = 1 MHz

VI = 0 or VCC,

Zero-power mode

10 100 µA

switching characteristics over recommended ranges of supply voltage and operating free-air

temperature (unless otherwise noted) (see Figure 3)

PARAMETER

¶

f

max

t

pd

t

pd

t

pd

t

en

t

dis

†

All typical values are at VCC = 5 V, TA = 25°C.

‡

Not more than one output should be shorted at a time, and the duration of the short circuit should not exceed one second. VO is set at 0.5 V to

avoid test problems caused by test equipment ground degradation.

§

Disabled outputs are tied to GND or VCC.

¶

f

max

Without feedback 50 66

With feedback 31.2 55

Turbo mode 16 25

Zero-power mode 21 35

Turbo mode 18 30

Zero-power mode 23 40

Turbo mode 15 25

Zero-power mode 20 35

Turbo mode 15 25

Zero-power mode 17 35

(with feedback) =

tsu)

1

tpd(CLK to Q)

FROM

(INPUT)

I, I/O O, I/O

Asynchronous

RESET

CLK↑ Q 10 15 ns

I, I/O

I, I/O

; f

(without feedback) =

max

tw(high))tw(low)

TO

(OUTPUT)

Q

I, Q, I/O

I, Q, I/O

1

MIN TYP†MAX UNIT

V

V

pF

MHz

ns

ns

ns

ns

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

9

Page 10

TICP AL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, VCC –0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, VI (see Note 1) –0.5 V to VCC+0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input clamp current, IIK (VI < 0 or V

Output clamp current, I

(VO < 0 or V

OK

> VCC) ± 20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I

> VCC) ± 20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

O

Continuous output current, IO (VO = 0 to VCC) ± 40 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 in) from case for 10 seconds: FN or NT package 260°C. . . . . . . . . . . . . . . .

Operating free-air temperature range –40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: These ratings apply except for programming pins during a programming cycle or during a preload cycle.

recommended operating conditions

MIN NOM MAX UNIT

V

V

V

I

I

t

t

t

t

T

OH

OL

w

su

su

h

Supply voltage 4.5 5 5.5 V

CC

High-level input voltage 2 V

IH

Low-level input voltage 0.8 V

IL

High-level output current

Low-level output current mA

Pulse duration Clock low 12 ns

Setup time, turbo mode Asynchronous reset inactive 25 ns

Setup time, zero-power mode Asynchronous reset inactive 35 ns

Hold time Input or feedback 0 ns

Operating free-air temperature –40 85 °C

A

Driving TTL –3.2

Driving CMOS –4

Driving TTL 16

Driving CMOS 4

Clock high 12

Asynchronous reset 30

Input or feedback 22

Synchronous preset inactive 25

Input or feedback 30

Synchronous preset inactive 35

mA

†

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 11

TICPAL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

electrical characteristics over recommended operating free-air temperature range

PARAMETER TEST CONDITION MIN TYP†MAX UNIT

V

OH

V

OL

I

OZH

I

OZL

I

IH

I

IL

I

O

I

CC

C

i

‡

§

I 6

I/O 10

VCC = 4.5 V, IOH = –3.2 mA for TTL 4 4.8

VCC = 4.5 V, IOH = –4 mA for CMOS 3.86 4.7

VCC = 4.5 V, IOL = 16 mA for TTL 0.25 0.5

VCC = 4.5 V, IOL = 4 mA for CMOS 0.07 0.4

VCC = 5.5 V, VO = 2.7 V 0.01 10 µA

VCC = 5.5 V, VO = 0.5 V –0.01 –10 µA

VCC = 5.5 V, VI = 5.5 V 0.01 10 µA

VCC = 5.5 V, VI = 0.5 V –0.01 –10 µA

VCC = 5.5 V, VO = 0.5 V –30 –45 –90 mA

VCC = 5.5 V,

Outputs open,

VI = 2 V, f = 1 MHz

VI = 0 or VCC,

Zero-power mode

10 100 µA

switching characteristics over recommended ranges of supply voltage and operating free-air

temperature (unless otherwise noted) (see Figure 3)

PARAMETER

¶

f

max

t

pd

t

pd

t

pd

t

en

t

dis

†

All typical values are at VCC = 5 V, TA = 25°C.

‡

Not more than one output should be shorted at a time, and the duration of the short circuit should not exceed one second. VO is set at 0.5 V to

avoid test problems caused by test equipment ground degradation.

§

Disabled outputs are tied to GND or VCC.

¶

f

max

Without feedback 41.6 66

With feedback 23.8 55

Turbo mode 16 30

Zero-power mode 21 40

Turbo mode 18 35

Zero-power mode 23 45

Turbo mode 15 30

Zero-power mode 20 40

Turbo mode 15 30

Zero-power mode 17 40

(with feedback) =

tsu)

1

tpd(CLK to Q)

FROM

(INPUT)

I, I/O O, I/O

Asynchronous

RESET

CLK↑ Q 10 20 ns

I, I/O

I, I/O

; f

(without feedback) =

max

tw(high))tw(low)

TO

(OUTPUT)

Q

I, Q, I/O

I, Q, I/O

1

MIN TYP†MAX UNIT

V

V

pF

MHz

ns

ns

ns

ns

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

11

Page 12

TICPAL22V10Z-25C, TICPAL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

preload procedure for registered outputs (see Notes 2 and 3)

The output registers can be preloaded to any desired state during device testing. This permits any state to be

tested without having to setup through the entire state-machine sequence. Each register is preloaded

individually by following the steps given below. The output level depends on the polarity selected during

programming.

Step 1. With VCC at 5 V and pin 1 at VIL, raise pin 8 to V

Step 2. Apply either V

or VIH to the output corresponding to the register to be preloaded.

IL

IHH

.

Step 3. Pulse pin 1, clocking in preload data.

Step 4. Remove output voltage, then lower pin 8 to V

. Preload can be verified by observing the voltage level

IL

at the output pin.

V

V

V

V

V

V

IHH

IL

IH

IL

OH

OL

Pin 8

t

t

d

CLK/I

Registered I/O Input Output

su

t

w

t

d

V

IH

V

IL

Figure 2. Preload Waveforms

NOTES: 2. Pin numbers shown are for the JTL and NT packages only. If chip-carrier socket adapter is not used, pin numbers must be changed

accordingly.

3.

t

= t

d

=

tw = 100 ns to 1000 ns. V

su

= 10.25 V to 10.75 V.

IHH

programming information

Texas Instruments programmable logic devices can be programmed using widely available software and

inexpensive device programmers.

Complete programming specifications, algorithms, and the latest information on hardware, software, and

firmware are available upon request. Information on programmers capable of programming T exas Instruments

programmable logic is also available, upon request, from the nearest TI field sales office, local authorized TI

distributor, or by calling Texas Instruments at (214) 997-5666.

12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 13

TICPAL22V10Z-25C, TICPAL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

PARAMETER MEASUREMENT INFORMATION

5 V

(see Note D)

S1

300 Ω

From Output

Under Test

Test

Point

CLK

t

Data

Input

Input

t

pd

In-Phase

Output

t

pd

Out-of-Phase

Output

(see Note D)

PROPAGATION DELAY TIMES

1.5 V

su

1.5 V

VOLTAGE WAVEFORMS

SETUP AND HOLD TIMES

1.5 V 1.5 V

1.5 V

1.5 V 1.5 V

VOLTAGE WAVEFORMS

(see Note A)

t

h

1.5 V

t

pd

1.5 V

t

pd

V

V

V

V

C

L

LOAD CIRCUIT FOR

3-STATE OUTPUTS

3 V

0

3 V

0

(see Note B)

3 V

0

OH

OL

OH

OL

390 Ω

High-Level

Pulse

Low-Level

Pulse

Output

Control

(low-level

enabling)

Waveform 1

S1 Closed

(see Note C)

Waveform 2

S1 Open

(see Note C)

1.5 V 1.5 V

t

w

1.5 V 1.5 V

VOLTAGE WAVEFORMS

PULSE DURATIONS

1.5 V 1.5 V

t

en

t

en

t

1.5 V

1.5 V

t

dis

dis

3 V

0

3 V

0

(see Note B)

3 V

0

(see Note B)

≈ 3.3 V

VOL + 0.5 V

V

OL

V

OH

VOH – 0.5 V

≈ 0 V

ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS

NOTES: A. CL includes probe and jig capacitance and is 50 pF for tpd and ten, 5 pF for t

B. All input pulses have the following characteristics: PRR ≤ 1 MHz, Zo = 50 Ω, tr = tf = 2 ns, duty cycle = 50%.

C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2

is for an output with internal conditions such that the output is high except when disabled by the output control.

D. When measuring propagation delay times of 3-state outputs, switch S1 is closed.

E. Equivalent loads may be used for testing.

Figure 3. Load Circuit and Voltage Waveforms

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

VOLTAGE WAVEFORMS

.

dis

13

Page 14

TICPAL22V10Z-25C, TICPAL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

special design features

True CMOS Outputs: Each TICPAL22V10Z output is designed with a P-channel pull-up transistor and an

N-channel pull-down transistor, a true CMOS output with rail-to-rail output switching. This provides direct

interface to CMOS logic, memory, or ASIC devices without the need for a pull-up resistor. The CMOS output

has 16-mA drive capability , which makes the TICPAL22V10Z an ideal substitute for bipolar PLDs. The electrical

characteristics of this device show the output under both CMOS and TTL conditions.

Simultaneous Switching: High-performance CMOS devices often have output glitches on nonswitched

outputs when a large number of outputs are switched simultaneously. This glitch is commonly referred to as

(low-level output voltage). Ground bounce is

”ground bounce” and is most noticeable on outputs held at V

caused by the voltage drop across the inductance in the package lead when current is switched (dv α I x di/dt).

One solution is to restrict the number of outputs that can switch simultaneously . Another solution is to change

the device pinout such that the ground is located on a low-inductance package pin. TI opted for a third option

in order to maintain pinout compatibility and eliminate functional constraints. This option controls the output

transistor turn-on characteristics and puts a limit on the instantaneous current available to the load, much like

the I

resistor in a TTL circuit.

OS

Wake-Up Features: The TICP AL22V10Z employs input signal transition detection techniques to power up the

device from the standby-power mode. The transition detector monitors all inputs, I/Os, and feedback paths.

Whenever a transition is sensed, the detector activates the power-up mode. The device will remain in the

power-up mode until the detector senses that the inputs and outputs have been static for about 40 ns; thereafter,

the device returns to the standby mode.

OL

T urbo Mode or Zero-Power Mode: When the turbo cell is programmed, the device will be set to the power-up

mode. Therefore, the delay associated with its transition detection and power up will be eliminated. This is how

the faster propagation delays and shorter setup times are obtained in the turbo mode. The turbo mode and the

associated speed increase can be effectively simulated with the turbo cell erased, if a series of adjacent input,

I/O, or feedback edges occur with an interval of about 25 ns or less between these adjacent edges. Under these

conditions, the TICPAL22V10Z will never have the opportunity to power down due to the frequency of the

adjacent edges.

Power Up: The TICP AL22V10Z device configuration bits (power mode, and macrocell configuration) are read

at the first input transition after a monotonic power up. When completed, the TICP AL22V10Z is in its designed

configuration. The use of an initializing device reset is necessary in applications where registered feedback is

used to ensure the TICPAL22V10Z is in a known state at the beginning of system operation.

Power Dissipation: Power dissipation of the TICP AL22V10Z is defined by three contributing factors, and the

total power dissipation is the sum of all three.

Standby Power: The product of V

and the standby ICC. The standby current is the reverse current

CC

through the diodes that are reversed biased. This current is very small, and for circuits that remain in static

condition for a long time, this low amount of current can become a major performance advantage.

Dynamic Power: The product of VCC and the dynamic current. This dynamic current flows through the

device only when the transistors are switching from one logic level to the other. The total dynamic current

for the TICPAL22V10Z is dependent upon the users’ configuration of the device and the operating

frequency. Output loading can be a source of additional power dissipation.

Interface Power: The product of I

(interface) and VCC. The total interface power is dependent on the

CC

number of inputs at the TTL VOH level. The interface power can be eliminated by the addition of a pull-up

resistor.

14

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 15

TICPAL22V10Z-25C, TICPAL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

Even though power dissipation is a function of the user’s device configuration and the operating frequency, the

TICPAL22V10Z is a lower powered solution than either the quarter-powered or half-powered bipolar devices.

The virtually zero standby power feature makes the TICPAL22V10Z the device of choice for low-duty-cycle

applications.

programming and erasability

Programming of the TICPAL22V10Z is achieved through floating-gate avalanche injection techniques. The

charge trapped on the floating gate remains after power has been removed, allowing for the nonvolatility of the

programmed data. The charge can be removed by exposure to light with wavelengths of less than 400 nm

(4000 Å). The recommended erasure wavelength is 253.7 nm (2537 Å), with erasure time of 60 to 90 minutes,

using a light source with a power rating of 12000 µW/cm

The TICP AL22V10Z is designed for programming endurance of 1000 write/erase cycles with a data retention

of ten years. T o guarantee maximum data retention, the window on the device should be covered by an opaque

label. The fluorescent light in a room can erase a unit in three years or, in the case of a direct sunlight, erasure

can be complete in one week.

2

placed within 2.5 cm (one inch) of the device.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

15

Page 16

TICPAL22V10Z-25C, TICPAL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

TYPICAL CHARACTERISTICS

OUTPUT CURRENT

vs

OUTPUT VOLTAGE

400

VCC = 5 V

TA = 25°C

200

I

100

70

40

–I

20

10

7

– Output Current – mA

O

I

4

2

0123 5

OH

VO – Output Voltage – V

OL

4

Figure 4

1.4

= 25 °C

1.3

A

T

1.2

= 5 V,V

CC

V

1.1

1

0.9

0.8

CL = 50 pF

f

Duty Cycle = 50%

0.7

Normalized Supply Current at

–50 –25 0

NORMALIZED SUPPLY CURRENT

vs

FREE-AIR TEMPERATURE

(10-BIT COUNTER)

= 23.8 MHz

clock

25 50 75

TA – Free-Air Temperature – °C

Figure 5

VCC = 4.5 V

VCC = 4.75 V

VCC = 5 V

VCC = 5.25 V

VCC = 5.5 V

100

CLOCK FREQUENCY

100

VCC = 5 V

TA = 25°C

CL = 50 pF

Duty cycle = 50%

80

60

40

– Supply Current – mA

CC

I

20

Turbo Bit off

0

100 1 k 10 k 100 k

f

clock

SUPPLY CURRENT

vs

(10-BIT COUNTER)

Turbo Bit on

1 M 10 M

– Clock Frequency – Hz

Figure 6

100 M

NORMALIZED PROPAGATION DELAY TIME

1.15

= 5 V

CC

1.05

0.95

Normalized Propagation Delay Time at

CLK to Q and Turbo Mode

1.1

1

TA = 25 °C

CL = 50 pF

R1 = 300 Ω

R2 = 390 Ω

0.9

4.5 5

vs

SUPPLY VOLTAGE

Zero-Power Mode

4.75

VCC – Supply Voltage – V

Figure 7

5.25

5.5

16

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 17

TICPAL22V10Z-25C, TICPAL22V10Z-30I

EPIC CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007C – D3323, SEPTEMBER 1989 – REVISED FEBRUARY 1992

TYPICAL CHARACTERISTICS

CHANGE IN

NORMALIZED PROPAGATION DELAY TIME

vs

FREE-AIR TEMPERATURE

1.2

VCC = 5 V

CL = 50 pF

= 25 °C

A

T

R1 = 300 Ω

R2 = 390 Ω

1.1

30

25

20

PROPAGATION DELAY TIME

vs

LOAD CAPACITANCE

VCC = 5 V

TA = 25 °C

R1 = 300 Ω

R2 = 390 Ω

1

0.9

Normalized Propagation Delay Time at

0.8

–50 –25 0

= CLK to Q

= Zero-Power Mode

= Turbo Mode

25 50 75

TA – Free-Air Temperature –°C

Figure 8

PROPAGATION DELAY TIME

NUMBER OF OUTOUTS SWITCHING

1.5

VCC = 5 V

TA = 25 °C

CL = 50 pF

R1 = 300 Ω

R2 = 390 Ω

Registered Macrocell

1

100

CHANGE IN

vs

15

10

5

Change in Propagation Delay Time – ns

0

0 100 200 300 400 500

CL – Load Capacitance – pF

Figure 9

t

PHL

t

PLH

600 700 800

0.5

Change in Propagation Delay Time – ns

0

1234567

Number of Outputs Switching

Figure 10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

t

PHL

t

PLH

8910

17

Page 18

Page 19

TI Worldwide

Sales Offices

ALABAMA: Huntsville: 4960 Corporate Drive,

Suite 150, Huntsville, AL 35805, (205) 837-7530.

ARIZONA: Phoenix: 8825 N. 23rd Avenue, Suite 100,

Phoenix, AZ 85021, (602) 995-1007.

CALIFORNIA: Irvine: 1920 Main Street, Suite 900,

Irvine, CA 92714, (714) 660-1200;

San Diego: 5625 Ruffin Road, Suite 100,

San Diego, CA 92123, (619) 278-9600;

Santa Clara: 5353 Betsy Ross Drive,

Santa Clara, CA 95054, (408) 980-9000;

Woodland Hills: 21550 Oxnard Street, Suite 700,

Woodland Hills, CA 91367, (818) 704-8100.

COLORADO: Aurora: 1400 S. Potomac Street, Suite 101,

Aurora, CO 80012, (303) 368-8000.

CONNECTICUT: W allingford: 9 Barnes Industrial Park

So., Wallingford, CT 06492, (203) 269-0074.

FLORIDA: Altamonte Springs: 370 S. North Lake

Boulevard, Suite 1008, Altamonte Springs, FL 32701,

(407) 260-2116;

Fort Lauderdale: 2950 N.W. 62nd Street,

Suite 100, Fort Lauderdale, FL 33309,

(305) 973-8502; Tampa: 4803 George Road, Suite 390,

Tampa, FL 33634-6234, (813) 885-7588.

GEORGIA: Norcross: 5515 Spalding Drive,

Norcross, GA 30092-2560, (404) 662-7967.

ILLINOIS: Arlington Heights: 515 West Algonquin,

Arlington Heights, IL 60005, (708) 640-6925.

INDIANA: Carmel: 550 Congressional Drive, Suite 100,

Carmel, IN 46032, (317) 573-6400;

Fort Wayne: 103 Airport North Office Park,

Fort Wayne, IN 46825, (219) 489-4697.

KANSAS: Overland Park: 7300 College Boulevard,

Lighton Plaza, Suite 150, Overland Park, KS 66210,

(913) 451-4511.

MARYLAND: Columbia: 8815 Centre Park Drive,

Suite 100, Columbia, MD 21045, (410) 964-2003.

MASSACHUSETTS: Waltham: Bay Colony Corporate

Center 950 Winter Street, Suite 2800, Waltham, MA 02154,

(617) 895-9100.

MICHIGAN: Farmington Hills: 33737 W. 12 Mile Road,

Farmington Hills, MI 48018, (313) 553-1581.

MINNESOTA: Eden Prairie: 11000 W. 78th Street,

Suite 100, Eden Prairie, MN 55344, (612) 828-9300.

MISSOURI: St. Louis: 12412 Powerscourt Drive,

Suite 125, St. Louis, MO 63131, (314) 821-8400.

NEW JERSEY: Iselin: Metropolitan Corporate Plaza, 485

Bldg E. U.S. 1 South, Iselin, NJ 08830, (908) 750-1050.

NEW MEXICO: Albuquerque: 2709 J. Pan American

Freeway, N.E., Albuquerque, NM 87101, (505) 345-2555.

NEW YORK: East Syracuse: 6365 Collamer Drive,

East Syracuse, NY 13057, (315) 463-9291;

Fishkill: 300 Westage Business Center, Suite 140,

Fishkill, NY 12524, (914) 897-2900;

Melville: 48 South Service Road, Suite 100, Melville, NY

11747, (516) 454-6601;

Pittsford: 2851 Clover Street, Pittsford, NY 14534,

(716) 385-6770.

NORTH CAROLINA: Charlotte: 8 Woodlawn Green,

Suite 100, Charlotte, NC 28217, (704) 527-0930;

Raleigh: 2809 Highwoods Boulevard, Suite 100,

Raleigh, NC 27625, (919) 876-2725.

OHIO: Beachwood: 23775 Commerce Park Road,

Beachwood, OH 44122-5875, (216) 765-7258;

Beavercreek: 4200 Colonel Glenn Highway, Suite 600,

Beavercreek, OH 45431, (513) 427-6200.

OREGON: Beaverton: 6700 S.W. 105th Street,

Suite 110, Beaverton, OR 97005, (503) 643-6758.

PENNSYLVANIA: Blue Bell: 670 Sentry Parkway,

Suite 200, Blue Bell, PA 19422, (215) 825-9500.

PUERTO RICO: Hato Rey: 615 Mercantile Plaza Building,

Suite 505, Hato Rey, PR 00919, (809) 753-8700.

TEXAS: Austin: 12501 Research Boulevard,

Austin, TX 78759, (512) 250-6769;

Dallas: 7839 Churchill Way, Dallas, TX 75251,

(214) 917-1264;

Houston: 9301 Southwest Freeway, Commerce Park, Suite

360, Houston, TX 77074, (713) 778-6592;

Midland: FM 1788 & I-20, Midland, TX 79711-0448,

(915) 561-7137.

UTAH: Salt Lake City: 2180 South 1300 East, Sute 335,

Salt Lake City, UT 54106, (801) 466-8972.

WISCONSIN: Waukesha: 20825 Swenson Drive,

Suite 900, Waukesha WI 53186, (414) 798-1001.

CANADA: Nepean: 301 Moodie Drive, Suite 102, Mallom

Center, Nepean, Ontario, Canada K2H 9C4,

(613) 726-1970;

Richmond Hill: 280 Centre Street East, Richmond Hill,

Ontario, Canada L4C 1B1, (416) 884-9181;

St. Laurent: 9460 Trans Canada Highway, St. Laurent,

Quebec, Canada H4S 1R7, (514) 335-8392.

AUSTRALIA (& NEW ZEALAND): T exas Instruments

Australia Ltd., 6-10 Talavera Road, North Ryde (Sydney),

New South Wales, Australia 2113, 2-878-9000; 14th Floor,

380 Street, Kilda Road, Melbourne, Victoria, Australia 3004,

3-696-1211; 171 Philip Highway, Elizabeth, South Australia

5112, 8 255-2066.

BELGIUM: Texas Instruments Belgium S.A./N.V.,

Avenue Jules Bordetlaan 11, 1140 Brussels, Belgium,

(02) 242 30 80.

BRAZIL: Texas Instruments Electronicos do Brasil Ltda.,

Av. Eng. Luiz Carlos Berrini 1461-11o andar, 04571,

Sao Paulo, SP, Brazil, 11-535–5133.

DENMARK: Texas Instruments A/S, Borupvang 2D,

2750 Ballerup, Denmark, (44) 68 74 00.

FINLAND: Texas Instruments OY, Ahertajantle 3,

P.O. Box 86, 02321 Espoo, Finland, (0) 802 6517.

FRANCE: Texas Instruments France, 8-10 Avenue

Morane-Saulnier, B.P. 67, 78141 Velizy Villacoublay Cedex,

France, (1) 30 70 1003.

GERMANY: Texas Instruments Deutschland GmbH.,

Haggertystrasse 1, 8050 Freising, (08161) 80-0;

Kurfurstendamm 195-196, 1000 Berlin 15, (030) 8 82 73 65;

Dusseldorfer Strasse 40, 6236 Eschborn 1, (06196) 80 70;

Kirchhorster Strasse 2, 3000 Hannover 51, (0511) 64 68-0;

Maybachstrasse II, 7302 Ostfildern 2 (Nellingen),

(0711) 3403257; Gildehofcenter, Hollestrasses 3, 4300

Essen 1, (0201) 24 25-0.

HOLLAND: Texas Instruments Holland B.V., Hogehilweg

19, Postbus 12995, 1100 AZ Amsterdam-Zuidoost, Holland,

(020) 5602911.

HONG KONG: T exas Instruments Hong Kong Ltd., 8th

Floor, World Shipping Center, 7 Canton Road, Kowloon,

Hong Kong, 737-0338.

HUNGARY: Texas Instruments Representation, Budaorsi

ut.42, 1112 Budapest, Hungary, (1) 1 66 66 17.

IRELAND: Texas Instruments Ireland Ltd., 7/8 Harcourt

Street, Dublin 2, Ireland, (01) 755233.

ITALY: Texas Instruments Italia S.p.A., Centro Direzionale

Colleoni, Palazzo Perseo-Via Paracelso 12, 20041 Agrate

Brianza (Mi), Italy, (039) 63221; Via Castello della Magliana,

38, 00148 Roma, Italy (06) 6572651; Via Amendola, 17,

40100 Bologna, Italy (051) 554004.

JAPAN: Texas Instruments Japan Ltd., Aoyama Fuji

Building 3-6-12 Kita-Aoyama Minato-ku, Tokyo, Japan 107,

03-498-2111; MS Shibaura Building 9F, 4-13-23 Shibaura,

Minato-ku, Tokyo, Japan 108, 03-769-8700; Nissho-iwai

Building 5F, 2-5-8 Imabashi, Chuou-ku, Osaka, Japan 541,

06-204-1881; Dai-ni Toyota Building Nishi-kan 7F, 4-10-27

Meieki, Nakamura-ku, Nagoya, Japan 450, 052-583-8691;

Kanazawa Oyama-cho Daiichi Seimei Building 6F, 3-10

Oyama-cho, Kanazawa, Ishikawa, Japan 920,

0762-23-5471; Matsumoto Showa Building 6F, 1-2-11

Fukashi, Matsumoto, Nagano, Japan 390, 0263-33-1060;

Daiichi Olympic Tachikawa Building 6F, 1-25-12,

Akebono-cho, Tachikawa, Tokyo, Japan 190,

0425-27-6760; Yokohama Business Park East Tower 10F,

134 Goudo-cho Hodogaya-ku, Yokohama-shi, Kanagawa,

Japan 240, 045-338-1220; Nihon Seimei Kyoto Yasaka

Building 5F, 843-2, Higashi Shiokohji-cho, Higashi-iru,

Nishinotoh-in, Shiokohji-dori, Shimogyo-ku, Kyoto, Japan

600, 075-341-7713; Sumitomo Seimei Kumagaya Building

8F, 2-44 Yayoi, Kumagaya, Saitama, Japan 360,

0485-22-2440; 2597-1, Aza Harudai, Oaza Yasaka, Kitsuki,

Oita, Japan 873, 09786-3-3211.

KOREA: Texas Instruments Korea Ltd., 28th Floor, Trade

Tower, 159, Samsung-Dong, Kangnam-ku Seoul, Korea, 2

551-2800.

MALAYSIA: Texas Instruments Malaysia, Sdn. Bhd., Asia

Pacific, Lot 36.1 #Box 93, Menara Maybank, 100 Jalan Tun

Perak, 50050 Kuala Llumpur, Malaysia, 2306001.

MEXICO: Texas Instruments de Mexico S.A., de C.V.,

Alfonso Reyes 115, Col. Hipodromo Condesa, Mexico, D.F.,

Mexico 06170, 5-515-6081.

NORWAY: Texas Instruments Norge A/S, P.B. 106, Refstad

(Sinsenveien 53), 0513 Oslo 5, Norway, (02) 155 090.

PEOPLE’S REPUBLIC OF CHINA: Texas Instruments

China Inc., Beijing Representative Office, 7-05 CITIC

Building, 19 Jianguomenwai Dajie, Beijing, China,

500-2255, Ext. 3750.

PHILIPPINES: Texas Instruments Asia Ltd.,

Philippines Branch, 14th Floor, Ba-Lepanto Building,

Paseo de Roxas, Makati, Metro Manila, Philippines,

2-8176031.

PORTUGAL: Texas Instruments Equipamento Electronico

(Portugal) Ltda., Ing. Frederico Ulricho, 2650 Moreira Da

Maia, 4470 Maia, Portugal (2) 948 1003.

SINGAPORE (& INDIA, INDONESIA, MALAYSIA,

THAILAND): Texas Instruments Singapore (PTE) Ltd.,

Asia Pacific, 101 Thomson Road, #23-01,

United Square, Singapore 1130, 3508100.

SPAIN: Texas Instruments Espana S.A., c/Gobelas 43,

Urbanizasion, La Florida, 28023, Madrid, Spain, (1) 372

8051; c/Diputacion, 279-3-5, 08007 Barcelona, Spain, (3)

317 91 80.

SWEDEN: Texas Instruments International Trade

Corporation (Sverigefilialen), Isafjordsgaton, Box 30, S-164

93 Kista, Sweden, (08) 752 58 00.

SWITZERLAND: Texas Instruments Switzerland AG,

Riedstrasse 6, C8953 Dietikon, Switzerland,

(01) 744 2811.

TAIWAN: Texas Instruments Taiwan Limited, Taipei

Branch, 10th Floor Bank Tower, 205 Tung Hwa N. Road,

Taipei, Taiwan, 10592 Republic of China, 2-7139311.

TURKEY: Texas Instruments, DSEG MidEast Regional

Marketing Office, Karum Center, Suite 442, Iran Caddesi

21, 06680 Kavaklldere, Ankara, Turkey, 4-468-0155.

UNITED KINGDOM: T exas Instruments Ltd., Manton Lane,

Bedford, England, MK41 7PA, (0234) 270 111.

TI Authorized

North American

Distributors

Alliance Electronics, Inc. (military product only)

Almac/Arrow

Anthem Electronics

Arrow/Schweber

Future Electronics (Canada)

GRS Electronics Co., Inc. *

Hall-Mark Electronics

Marshall Industries

Newark Electronics *

Wyle Laboratories

Zeus Components

Rochester Electronics, Inc. (obsolete product only)

*Not authorized for TI military products

1992 T exas Instruments Incorporated

B0892

Page 20

TI North

American Sales

Offices

ALABAMA: Huntsville: (205) 837-7530

ARIZONA: Phoenix: (602) 995-1007

CALIFORNIA: Irvine: (714) 660-1200

San Diego: (619) 278-9600

Santa Clara: (408) 980-9000

Woodland Hills: (818) 704-8100

COLORADO: Aurora: (303) 368-8000

CONNECTICUT: W allingford: (203) 269-0074

FLORIDA: Altamonte Springs: (407) 260-2116

Fort Lauderdale: (305) 973-8502

Tampa: (813) 885-7588

GEORGIA: Norcross: (404) 662-7967

ILLINOIS: Arlington Heights: (708) 640-3000

INDIANA: Carmel: (317) 573-6400

Fort Wayne: (219) 489-4697

KANSAS: Overland Park: (913) 451-4511

MARYLAND: Columbia: (410) 964-2003

MASSACHUSETTS: Waltham: (617) 895-9100

MICHIGAN: Farmington Hills: (313) 553-1581

MINNESOTA: Eden Prairie: (612) 828-9300

MISSOURI: St. Louis: (314) 821-8400

NEW JERSEY: Iselin: (908) 750-1050

NEW MEXICO: Albuquerque: (505) 345-2555

NEW YORK: East Syracuse: (315) 463-9291

Fishkill: (914) 897-2900

Melville: (516) 454-6600

Pittsford: (716) 385-6770

NORTH CAROLINA: Charlotte: (704) 527-0930

Raleigh: (919) 876-2725

OHIO: Beachwood: (216) 765-7258

Beavercreek: (513) 427-6200

OREGON: Beaverton: (503) 643-6758

PENNSYLVANIA: Blue Bell: (215) 825-9500

PUERTO RICO: Hato Rey: (809) 753-8700

TEXAS: Austin: (512) 250-6769

Dallas: (214) 917-1264

Houston: (713) 778-6592

Midland: (915) 561-7137

UTAH: Salt Lake CIty: (801) 466-8972

WISCONSIN: Waukesha: (414) 798-1001

CANADA: Nepean: (613) 726-1970

Richmond Hill: (416) 884-9181

St. Laurent: (514) 335-8392

TI Regional

Technology

Centers

CALIFORNIA: Irvine: (714) 660-8140

Santa Clara: (408) 748-2222

GEORGIA: Norcross: (404) 662-7945

ILLINOIS: Arlington Heights: (708) 640-2909

INDIANA: Indianapolis: (317) 573-6400

MASSACHUSETTS: Waltham: (617) 895-9196

MEXICO: Mexico City: 491-70834

MINNESOTA: Minneapolis: (612) 828-9300

TEXAS: Dallas: (214) 917-3881

CANADA: Nepean: (613) 726-1970

TI Authorized

North American

Distributors

Alliance Electronics, Inc. (military product only)

Almac/Arrow

Anthem Electronics

Arrow/Schweber

Future Electronics (Canada)

GRS Electronics Co., Inc.

Hall-Mark Electronics

Marshall Industries

Newark Electronics

Rochester Electronics, Inc.

(obsolete product only (508) 462-9332)

Wyle Laboratories

Zeus Components

TI Distributors

ALABAMA: Arrow/Schweber (205) 837-6955; Hall-Mark

(205) 837-8700; Marshall (205) 881-9235.

ARIZONA: Anthem (602) 966-6600; Arrow/Schweber (602)

437-0750; Hall-Mark (602) 431-0030; Marshall (602)

496-0290; Wyle (602) 437-2088.

CALIFORNIA: Los Angeles/Orange County: Anthem

(818) 775-1333, (714) 768-4444; Arrow/Schweber (818)

380-9686, (714) 838-5422; Hall-Mark (818) 773-4500, (714)

727-6000; Marshall (818) 878-7000, (714) 458-5301; Wyle

(818) 880-9000, (714) 863-9953; Zeus (714) 921-9000,

(818) 889-3838;

Sacramento: Anthem (916) 624-9744; Hall-Mark (916)

624-9781; Marshall (916) 635-9700; Wyle (916) 638-5282;

San Diego: Anthem (619) 453-9005; Arrow/Schweber

(619) 565-4800; Hall-Mark (619) 268-1201; Marshall (619)

578-9600; Wyle (619) 565-9171; Zeus (619) 277-9681.

San Francisco Bay Area: Anthem (408) 453-1200;

Arrow/Schweber (408) 441-9700, (510) 490-9477;

Hall-Mark (408) 432-4000; Marshall (408) 942-4600;

Wyle (408) 727-2500; Zeus (408) 629-4789.

COLORADO: Anthem (303) 790-4500; Arrow/Schweber

(303) 799-0258; Hall-Mark (303) 790-1662; Marshall (303)

451-8383; Wyle (303) 457-9953.

CONNECTICUT: Anthem (203) 575-1575; Arrow/Schweber

(203) 265-7741; Hall-Mark (203) 271-2844; Marshall (203)

265-3822.

FLORIDA:Fort Lauderdale:Arrow/Schweber (305)

429-8200; Halll-Mark (305) 971-9280; Marshall (305)

977-4880.

Orlando: Arrow/Schweber (407) 333-9300; Hall-Mark (407)

830-5855; Marshall (407) 767-8585; Zeus (407) 788-9100.

Tampa: Hall-Mark (813) 541-7440; Marshall (813)

573-1399.

GEORGIA: Arrow/Schweber (404) 497-1300; Hall-Mark

(404) 623-4400; Marshall (404) 923-5750.

ILLINOIS: Anthem (708) 884-0200; Arrow/Schweber (708)

250-0500; Hall-Mark (312) 860-3800; Marshall (708)

490-0155; Newark (312)784-5100.

INDIANA: Arrow/Schweber (317) 299-2071; Hall-Mark

(317) 872-8875; Marshall (317) 297-0483.

IOWA: Arrow/Schweber (319) 395-7230.

KANSAS: Arrow/Schweber (913) 541-9542; Hall-Mark

(913) 888-4747; Marshall (913) 492-3121.

MARYLAND: Anthem (301) 995-6640; Arrow/Schweber

(301) 596-7800; Hall-Mark (301) 988-9800; Marshall (301)

622-1118; Zeus (301) 997-1118.

MASSACHUSETTS: Anthem (508) 657-5170;

Arrow/Schweber (508) 658-0900; Hall-Mark (508)

667-0902; Marshall (508) 658-0810; Wyle (617) 272-7300;

Zeus (617) 246-8200.

MICHIGAN: Detroit: Arrow/Schweber (313) 462-2290;

Hall-Mark (313) 416-5800; Marshall (313) 525-5850;

Newark (313) 967-0600.

MINNESOTA: Anthem (612) 944-5454; Arrow/Schweber

(612) 941-5280; Hall-Mark (612) 881-2600; Marshall (612)

559-2211.

MISSOURI: Arrow/Schweber (314) 567-6888; Hall-Mark

(314) 291-5350; Marshall (314) 291-4650.

NEW JERSEY: Anthem (201) 227-7960; Arrow/Schweber

(201) 227-7880, (609) 596-8000; Hall-Mark (201) 515-3000,

(609) 235-1900; Marshall (201) 882-0320, (609) 234-9100.

NEW MEXICO: Alliance (505) 292-3360.

NEW YORK: Long Island: Anthem (516) 864-6600;

Arrow/Schweber (516) 231-1000; Hall-Mark (516)

737-0600; Marshall (516) 273-2424; Zeus (914) 937-7400.

Rochester: Arrow/Schweber (716) 427-0300; Hall-Mark

(716) 425-3300; Marshall (716) 235-7620.

Syracuse: Marshall (607) 785-2345.

NORTH CAROLINA: Arrow/Schweber (919) 876-3132;

Hall-Mark (919) 872-0712; Marshall (919) 878-9882.

OHIO: Cleveland: Arrow/Schweber (216) 248-3990;

Hall-Mark (216) 349-4632; Marshall (216) 248-1788.

Columbus: Hall-Mark (614) 888-3313.

Dayton: Arrow/Schweber (513) 435-5563; Marshall (513)

898-4480; Zeus (513) 293-6162.

OKLAHOMA: Arrow/Schweber (918) 252-7537; Hall-Mark

(918) 254-6110.

OREGON: Almac/Arrow (503) 629-8090; Anthem (503)

643-1114; Marshall (503) 644-5050; Wyle (503) 643-7900.

PENNSYLVANIA: Anthem (215) 443-5150;

Arrow/Schweber (215) 928-1800; GRS (215) 922-7037;

(609) 964-8560; Marshall (412) 788-0441.

TEXAS: Austin: Arrow/Schweber (512) 835-4180;

Hall-Mark (512) 258-8848; Marshall (512) 837-1991; Wyle

(512) 345-8853;

Dallas: Anthem (214) 238-7100; Arrow/Schweber (214)

380-6464; Hall-Mark (214) 553-4300; Marshall (214)

233-5200; Wyle (214) 235-9953; Zeus (214) 783-7010;

Houston: Arrow/Schweber (713) 530-4700; Hall-Mark

(713) 781-6100; Marshall (713) 467-1666; Wyle (713)

879-9953.

UTAH: Anthem (801) 973-8555; Arrow/Schweber (801)

973-6913; Marshall (801) 973-2288; Wyle (801) 974-9953.

WASHINGTON: Almac/Arrow (206) 643-9992, Anthem

(206) 483-1700; Marshall (206) 486-5747; Wyle (206)

881-1150.

WISCONSIN: Arrow/Schweber (414) 792-0150; Hall-Mark

(414) 797-7844; Marshall (414) 797-8400.

CANADA: Calgary: Future (403) 235-5325;

Edmonton: Future (403) 438-2858;

Montreal: Arrow/Schweber (514) 421-7411; Future (514)

694-7710; Marshall (514) 694-8142

Ottawa: Arrow/Schweber (613) 226-6903; Future (613)

820-8313.

Quebec: Future (418) 897-6666.

Toronto: Arrow/Schweber (416) 670-7769;

Future (416) 612-9200; Marshall (416) 458-8046.

Vancouver: Arrow/Schweber (604) 421-2333;

Future (604) 294-1166.

TI Die Processors

Chip Supply (407) 298-7100

Elmo Semiconductor (818) 768-7400

Minco T echnology Labs (512) 834-2022

Customer

Response Center

TOLL FREE: (800) 336-5236

OUTSIDE USA: (214) 995-6611

(8:00 a.m. – 5:00 p.m. CST)

1992 T exas Instruments Incorporated

D0892

SRPS007C

Page 21

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERTAIN APPLICA TIONS USING SEMICONDUCT OR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICA TIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

Loading...

Loading...