Page 1

● 8 A RMS, 70 A Peak

● Glass Passivated Wafer

● 400 V to 800 V Off-State Voltage

● Max I

of 50 mA (Quadrants 1 - 3)

GT

MT1

MT2

TIC226 SERIES

SILICON TRIACS

APRIL 1971 - REVISED MARCH 1997Copyright © 1997, Power Innovations Limited, UK

TO-220 PACKAGE

(TOP VIEW)

1

2

G

3

Pin 2 is in electrical contact with the mounting base.

absolute maximum ratings over operating case temperature (unless otherwise noted)

RATING SYMBOL VALUE UNIT

TIC226D

Repetitive peak off-state voltage (see Note 1)

TIC226M

TIC226S

V

DRM

TIC226N

Full-cycle RMS on-state current at (or below) 85°C case temperature (see Note 2) I

Peak on-state surge current full-sine-wave (see Note 3) I

Peak on-state surge current half-sine-wave (see Note 4) I

Peak gate current I

Peak gate power dissipation at (or below) 85°C case temperature (pulse width

≤ 200 µs) P

Average gate power dissipation at (or below) 85°C case temperature (see Note 5) P

Operating case temperature range T

Storage temperature range T

Lead temperature 1.6 mm from case for 10 seconds T

T(RMS)

TSM

TSM

GM

GM

G(AV)

C

stg

L

NOTES: 1. These values apply bidirectionally for any value of resistance between the gate and Main Terminal 1.

2. This value applies for 50-Hz full-sine-wave operation with resistive load. Above 85°C derate linearly to 110°C case temperature at

the rate of 320 mA/°C.

3. This value applies for one 50-Hz full-sine-wave when the device is operating at (or below) the rated value of on-state current.

Surge may be repeated after the device has returned to original thermal equilibrium. During the surge, gate control may be lost.

4. This value applies for one 50-Hz half-sine-wave when the device is operating at (or below) the rated value of on-state current.

Surge may be repeated after the device has returned to original thermal equilibrium. During the surge, gate control may be lost.

5. This value applies for a maximum averaging time of 20 ms.

400

600

700

800

70 A

80 A

±1 A

2.2 W

0.9 W

-40 to +110 °C

-40 to +125 °C

230 °C

MDC2ACA

V

8 A

electrical characteristics at 25°C case temperature (unless otherwise noted)

PARAMETER TEST CONDITIONS

I

DRM

I

GTM

V

GTM

Repetitive peak

off-state current

Peak gate trigger

current

Peak gate trigger

voltage

= rated V

V

D

V

supply

V

supply

V

supply

V

supply

V

supply

V

supply

V

supply

V

supply

DRM

= +12 V†

= +12 V†

= -12 V†

= -12 V†

= +12 V†

= +12 V†

= -12 V†

= -12 V†

IG = 0 TC = 110°C ±2 mA

R

= 10 Ω

L

RL = 10 Ω

RL = 10 Ω

RL = 10 Ω

R

= 10 Ω

L

RL = 10 Ω

RL = 10 Ω

RL = 10 Ω

t

t

t

t

t

t

t

t

p(g)

p(g)

p(g)

p(g)

p(g)

p(g)

p(g)

p(g)

> 20 µs

> 20 µs

> 20 µs

> 20 µs

> 20 µs

> 20 µs

> 20 µs

> 20 µs

† All voltages are with respect to Main Terminal 1.

PRODUCT INFORMATION

Information is current as of publication date. Products conform to specifications in accordance

with the terms of Power Innovations standard warranty. Production processing does not

necessarily include testing of all parameters.

MIN TYP MAX

2

50

-12

-50

-9

-50

20

0.7

-0.8

-0.8

0.9

2

-2

-2

2

UNIT

mA

V

1

Page 2

TIC226 SERIES

I

- Gate Trigger Current - mA

SILICON TRIACS

APRIL 1971 - REVISED MARCH 1997

electrical characteristics at 25°C case temperature (unless otherwise noted) (continued)

PARAMETER TEST CONDITIONS

V

TM

I

H

I

L

dv/dt

dv/dt

Peak on-state voltage ITM = ±12 A IG = 50 mA (see Note 6) ±1.6 ±2.1 V

Holding current

Latching current

Critical rate of rise of

off-state voltage

Critical rise of commu-

(c)

tation voltage

V

V

V

V

V

V

supply

supply

supply

supply

DRM

DRM

= +12 V†

= -12 V†

= +12 V†

= -12 V†

= Rated V

= Rated V

I

= 0

G

= 0

I

G

(see Note 7)

DRMIG

DRMITRM

= 0 TC = 110°C ±100 V/µs

= ±12 A TC = 85°C ±5 V/µs

† All voltages are with respect to Main Terminal 1.

NOTES: 6. This parameter must be measured using pulse techniques, t

the current carrying contacts are located within 3.2 mm from the device body.

7. The triacs are triggered by a 15-V (open-circuit amplitude) pulse supplied by a generator with the following characteristics:

= 100 Ω, t

R

G

= 20 µs, tr = ≤ 15 ns, f = 1 kHz.

p(g)

thermal characteristics

PARAMETER MIN TYP MAX UNIT

R

R

Junction to case thermal resistance 1.8 °C/W

θJC

Junction to free air thermal resistance 62.5 °C/W

θJA

MIN TYP MAX

Init’ I

Init’ I

= 100 mA

TM

= -100 mA

TM

5

-9

-30

-50

= ≤ 1 ms, duty cycle ≤ 2 %. Voltage-sensing contacts separate from

p

30

50

UNIT

mA

mA

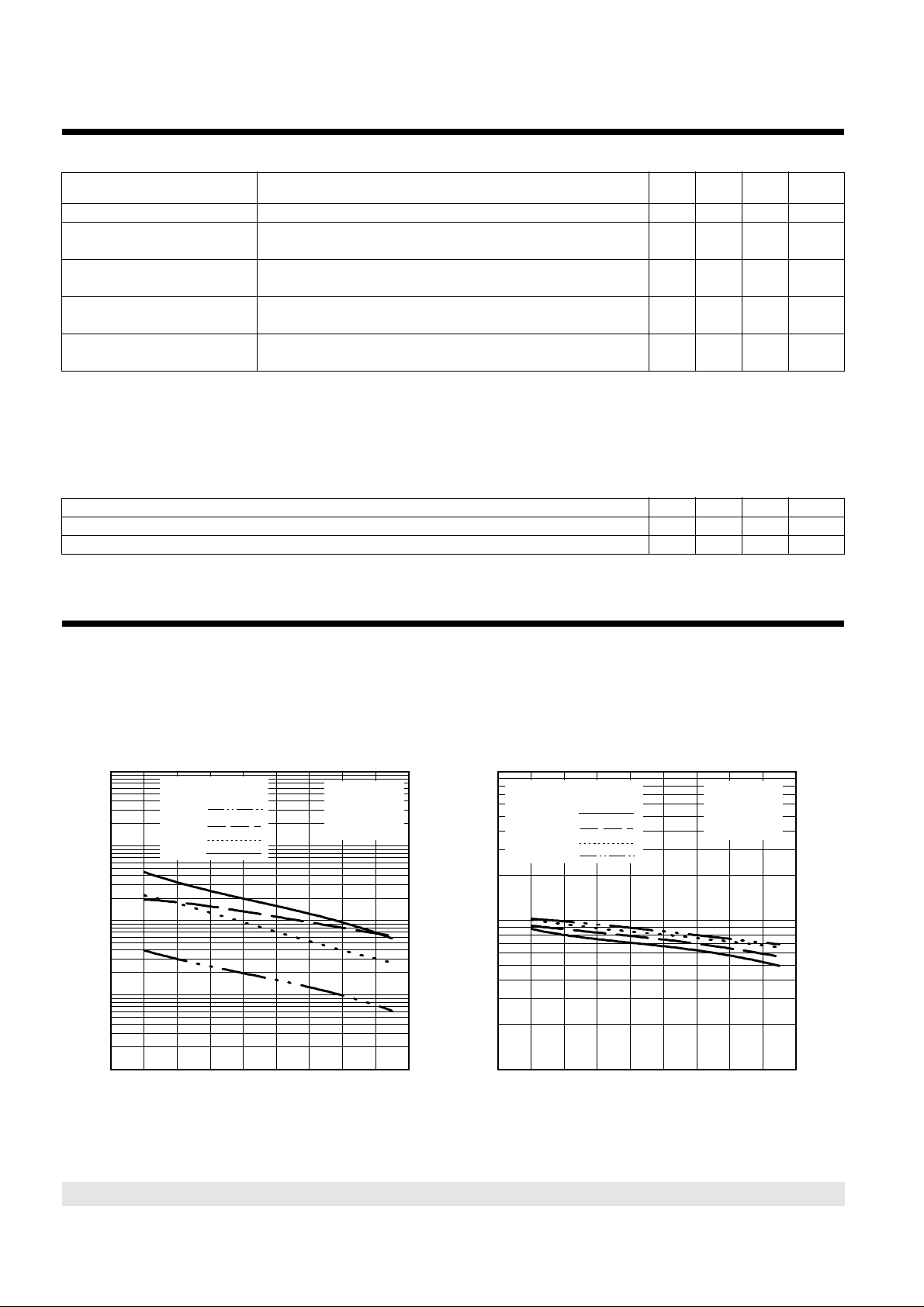

TYPICAL CHARACTERISTICS

GATE TRIGGER CURRENT

vs

CASE TEMPERATURE

1000

V

supply IGTM

+ +

+ -

100

- -

- +

10

GT

1

0·1

-60 -40 -20 0 20 40 60 80 100 120

TC - Case Temperature - °C

Figure 1. Figure 2.

VAA = ± 12 V

RL = 10 ΩΩ

t

= 20 µs

p(g)

TC01AA

GATE TRIGGER VOLTAGE

vs

CASE TEMPERATURE

10

V

supply IGTM

+ +

+ -

- -

- +

1

- Gate Trigger Voltage - V

GT

V

0·1

-60 -40 -20 0 20 40 60 80 100 120

TC - Case Temperature - °C

VAA = ± 12 V

RL = 10 ΩΩ

t

= 20 µs

p(g)

TC01AB

PRODUCT INFORMATION

2

Page 3

TYPICAL CHARACTERISTICS

V

- Gate Forward Voltage - V

I

- Latching Current - mA

TIC226 SERIES

SILICON TRIACS

APRIL 1971 - REVISED MARCH 1997

HOLDING CURRENT

vs

CASE TEMPERATURE

1000

V

supply

+

-

100

10

- Holding Current - mA

H

I

1

0·1

-60 -40 -20 0 20 40 60 80 100 120

TC - Case Temperature - °C

VAA = ± 12 V

IG = 0

Initiating ITM = 100 mA

Figure 3. Figure 4.

TC01AD

GATE FORWARD VOLTAGE

vs

GATE FORWARD CURRENT

10

1

0·1

GF

IA = 0

TC = 25 °C

QUADRANT 1

0·01

0·0001 0·001 0·01 0·1 1

IGF - Gate Forward Current - A

TC01AC

LATCHING CURRENT

vs

CASE TEMPERATURE

1000

V

supply IGTM

+ +

+ -

- -

- +

100

10

L

1

-60 -40 -20 0 20 40 60 80 100 120

TC - Case Temperature - °C

VAA = ± 12 V

Figure 5. Figure 6.

TC01AE

SURGE ON-STATE CURRENT

vs

CYCLES OF CURRENT DURATION

100

TC ≤≤ 85 °C

No Prior Device Conduction

10

Gate Control Guaranteed

- Peak Full-Sine-Wave Current - A

TSM

I

1

1 10 100 1000

Consecutive 50-Hz Half-Sine-Wave Cycles

TI01AA

PRODUCT INFORMATION

3

Page 4

TIC226 SERIES

PMC2AA

SILICON TRIACS

APRIL 1971 - REVISED MARCH 1997

TYPICAL CHARACTERISTICS

MAX RMS ON-STATE CURRENT

vs

CASE TEMPERATURE

10

9

8

7

6

5

4

3

- Maximum On-State Current - A

2

T(RMS)

I

1

0

0 25 50 75 100 125 150

TC - Case Temperature - °C

Figure 7. Figure 8.

TI01AB

MAX AVERAGE POWER DISSIPATED

vs

RMS ON-STATE CURRENT

32

TJ = 110 °C

28

Conduction Angle = 360 °

Above 8 A rms

24

See I

Figure

TSM

20

16

12

8

- Maximum Average Power Dissipated - W

4

(av)

P

0

0 2 4 6 8 10 12 14 16

I

- RMS On-State Current - A

T(RMS)

TI01AC

PARAMETER MEASUREMENT INFORMATION

V

AC

V

L1

I

MT2

50 Hz

C1

DUT

R1

V

MT2

R

G

See

Note A

I

G

NOTE A: The gate-current pulse is furnished by a trigger circuit which presents essentially an open circuit between pulses. The pulse is timed

so that the off-state-voltage duration is approximately 800 µs.

AC

I

MT2

V

MT2

I

G

Figure 9.

I

TRM

V

DRM

10%

dv/dt

63%

PRODUCT INFORMATION

4

Page 5

TIC226 SERIES

Version 1, 18.0 mm. Version 2, 17.6 mm.

SILICON TRIACS

APRIL 1971 - REVISED MARCH 1997

MECHANICAL DATA

TO-220

3-pin plastic flange-mount package

This single-in-line package consists of a circuit mounted on a lead frame and encapsulated within a plastic

compound. The compound will withstand soldering temperature with no deformation, and circuit performance

characteristics will remain stable when operated in high humidity conditions. Leads require no additional

cleaning or processing when used in soldered assembly.

TO220

3,96

ø

3,71

see Note B

see Note C

0,97

0,61

10,4

10,0

1 2 3

1,70

1,07

2,74

2,34

5,28

4,88

2,95

2,54

6,1

3,5

4,70

4,20

1,32

1,23

6,6

6,0

15,90

14,55

14,1

12,7

0,64

0,41

2,90

2,40

NOTES: A. The centre pin is in electrical contact with the mounting tab.

B. Mounting tab corner profile according to package version.

C. Typical fixing hole centre stand off height according to package version.

PRODUCT INFORMATION

VERSION 2 VERSION 1

ALL LINEAR DIMENSIONS IN MILLIMETERS

MDXXBE

5

Page 6

TIC226 SERIES

SILICON TRIACS

APRIL 1971 - REVISED MARCH 1997

IMPORTANT NOTICE

Power Innovations Limited (PI) reserves the right to make changes to its products or to discontinue any

semiconductor product or service without notice, and advises its customers to verify, before placing orders, that the

information being relied on is current.

PI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with PI's standard warranty. Testing and other quality control techniques are utilized to the extent PI

deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except as mandated by government requirements.

PI accepts no liability for applications assistance, customer product design, software performance, or infringement

of patents or services described herein. Nor is any license, either express or implied, granted under any patent

right, copyright, design right, or other intellectual property right of PI covering or relating to any combination,

machine, or process in which such semiconductor products or services might be or are used.

PI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE

SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS.

Copyright © 1997, Power Innovations Limited

PRODUCT INFORMATION

6

Loading...

Loading...