Page 1

INTEGRATED CIRCUITS

DATA SH EET

TDA9802

Multistandard VIF-PLL

demodulator and FM-PLL detector

Preliminary specification

File under Integrated Circuits, IC02

November 1992

Page 2

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator

TDA9802

and FM-PLL detector

FEATURES

• Suitable for negative and positive vision modulation

• Gain controlled 3-stage IF amplifier; suitable for VIF

frequencies up to 60 MHz

• True synchronous demodulation with active carrier

regeneration (ultra-linear demodulation, good

intermodulation figures, reduced harmonics and

excellent pulse response)

• Peak sync AGC for negative modulation, e.g. B/G

standard

• Peak white AGC for positive modulation, e.g. L standard

• Video amplifier to match sound trap and sound filter

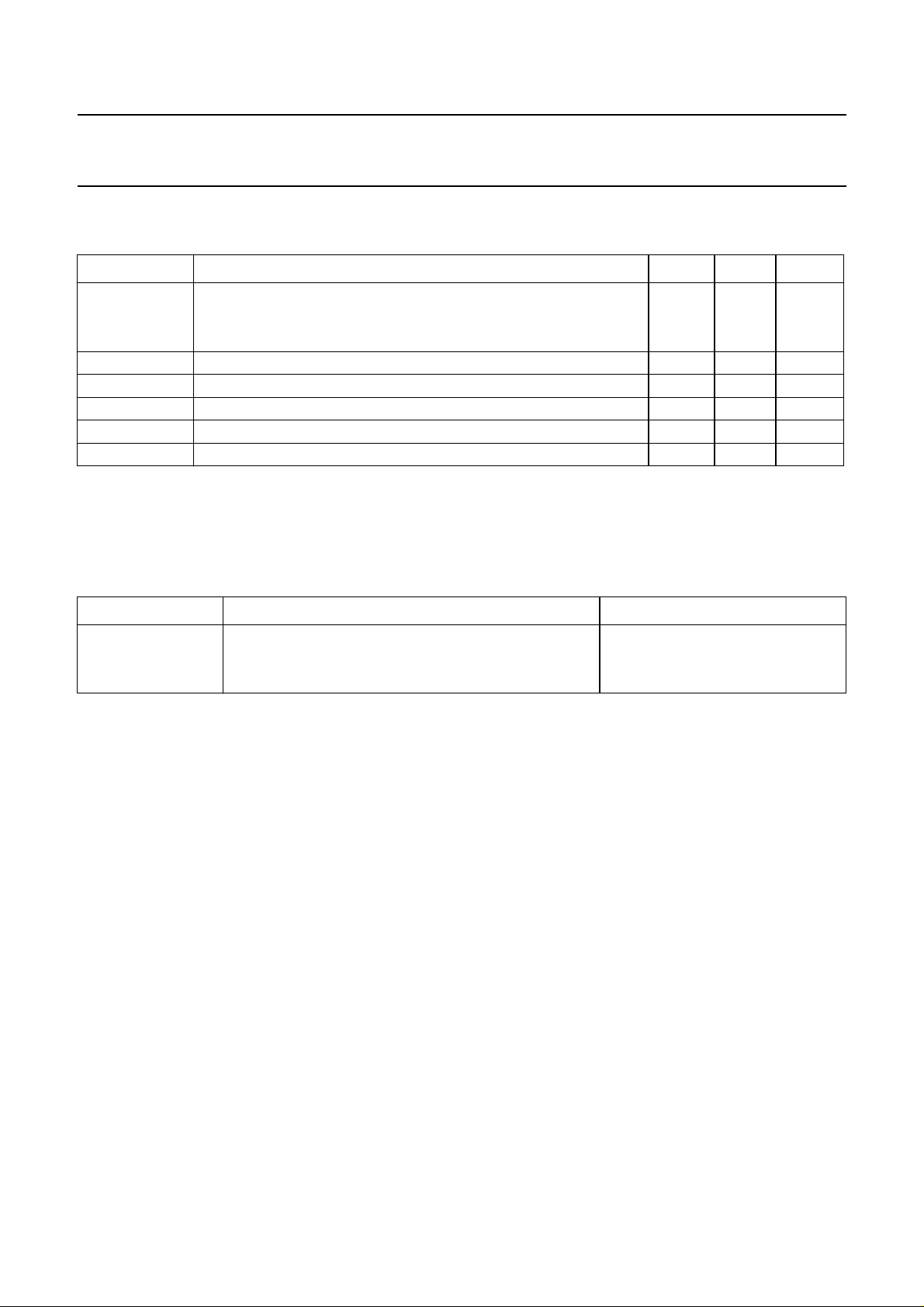

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

P

I

P

V

iIF

positive supply voltage (pin 20) 4.5 5 8.8 V

supply current 51 60 69 mA

vision IF input signal sensitivity (RMS value, pins 1 and 2) − 50 90 µV

maximum vision IF input signal (RMS value, pins 1 and 2) 70 150 − mV

G

v

V

o CVBS

IF gain control range 64 70 73 dB

CVBS output signal on pin 7 (peak-to-peak value) 1.7 2.0 2.3 V

B −3 dB video bandwidth on pin 7 6 8 − MHz

S/N (W) signal-to-noise ratio weighted; for video 56 59 − dB

α

α

α

V

1.1

3.3

H

oAF

intermodulation attenuation 56 62 − dB

suppression of harmonics in video signal 35 40 − dB

maximum AF output signal for THD < 1.5% (RMS value,

pin 9)

T

amb

operating ambient temperature range 0 − +70 °C

• AGC output voltage for tuner; adjustable take-over point

(TOP)

• AFC detector without extra reference circuit

• Alignment-free FM-PLL detector with high linearity

• Stabilizer circuit for ripple rejection and to achieve

constant output signals

• 5 to 8 V positive supply voltage range, low power

consumption (300 mW at +5 V supply voltage)

GENERAL DESCRIPTION

The TDA9802 is a monolithic integrated circuit for vision

and sound IF signal processing in multistandard TV and

VTR sets.

56 62 − dB

0.8 −−V

ORDERING INFORMATION

EXTENDED

TYPE NUMBER

PINS PIN POSITION MATERIAL CODE

TDA9802 20 DIL plastic SOT146(1)

TDA9802T 20 mini-pack plastic SOT163A(2)

Note

1. SOT146-1; 1996 November 19.

2. SOT163-1; 1996 November 19.

November 1992 2

PACKAGE

Page 3

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

TDA9802

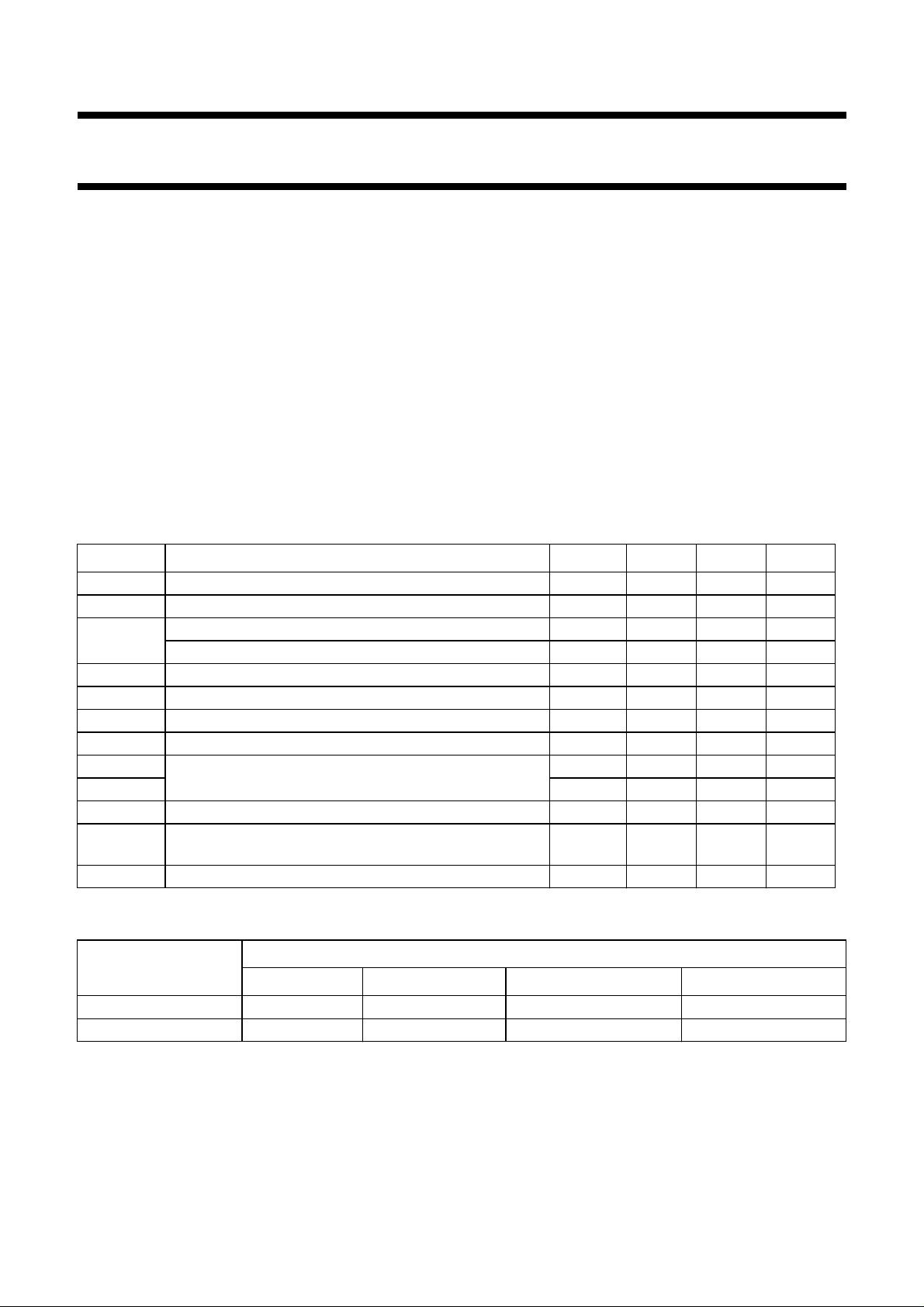

Fig.1 Block diagram.

November 1992 3

Page 4

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

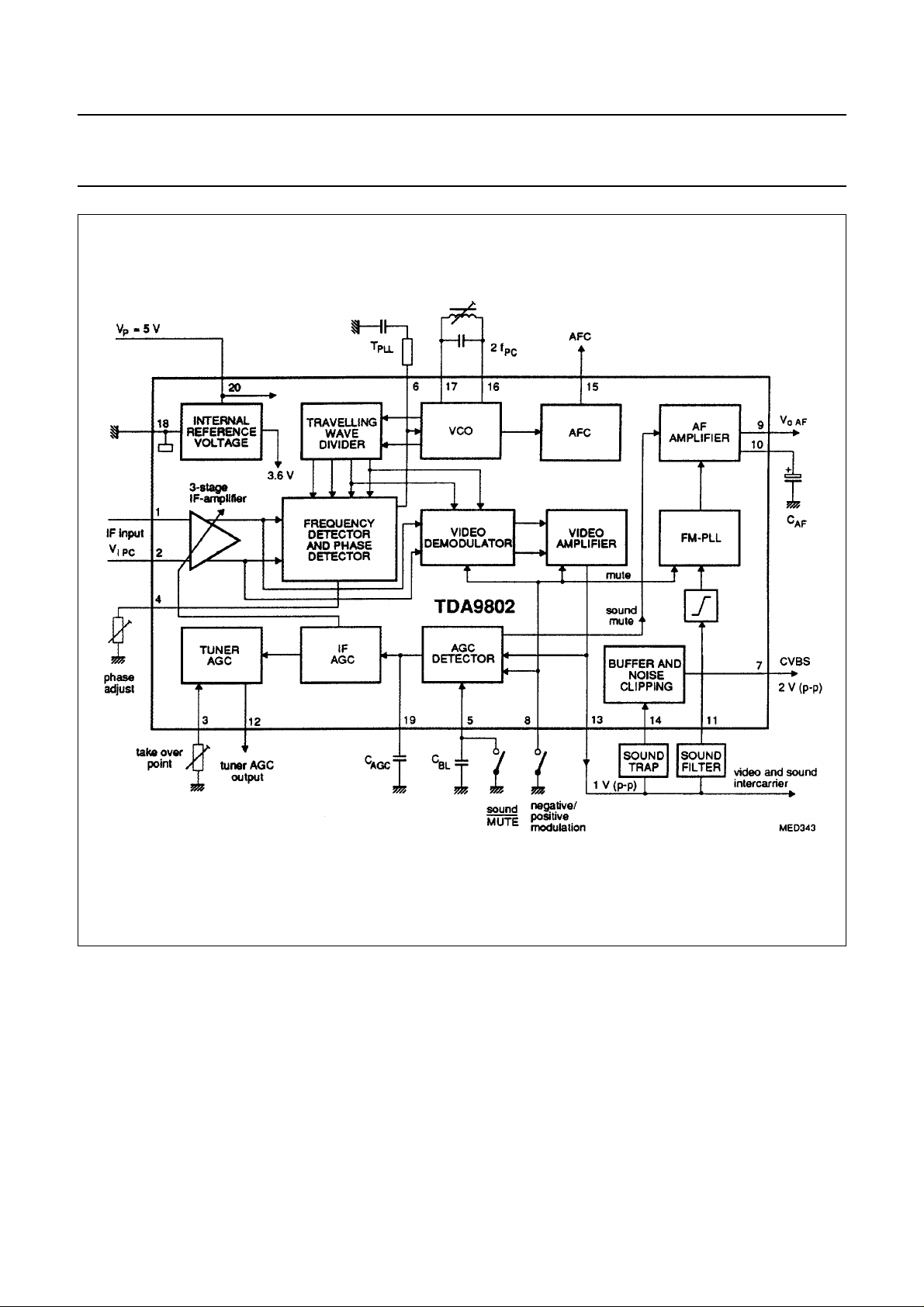

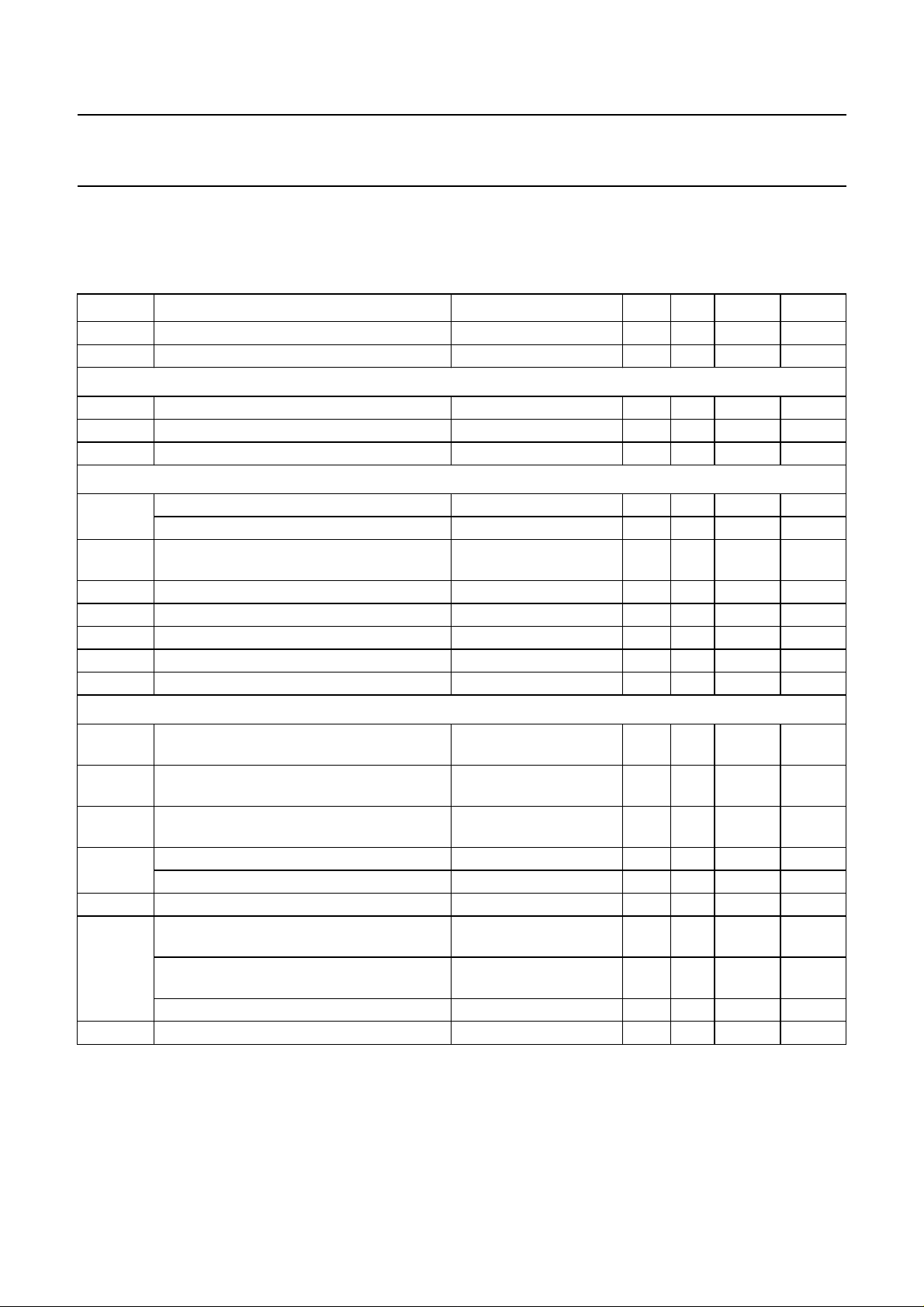

PINNING

SYMBOL PIN DESCRIPTION

V

iIF

TADJ 3 tuner AGC take-over adjust (TOP)

φADJ 4 phase detector adjust

C

BL

T

PLL

V

o CVBS

STD 8 standard switch (negative = HIGH,

V

oAF

C

AF

V

iIC

TAGC 12 tuner AGC output

V

o VID

V

i VID

AFC 15 automatic frequency control output

VCO1 16 VCO reference circuit for 2 f

VCO2 17

GND 18 ground (0 V)

C

AGC

V

P

1 vision IF differential input signal

2

5 black level capacitor, mute switch input

6 PLL time constant of phase detector

7 CVBS (positive) output signal

positive = LOW)

9 audio frequency output signal

10 decoupling capacitor of audio frequency amplifier

11 sound intercarrier input signal

13 video and sound intercarrier output signal

14 video input signal to buffer amplifier

PC

19 AGC capacitor

20 positive supply voltage

TDA9802

Fig.2 Pin configuration.

November 1992 4

Page 5

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

FUNCTIONAL DESCRIPTION

Vision IF input

The vision IF amplifier consists of three AC-coupled

differential amplifier stages; each stage comprises a

controlled feedback network by means of emitter

degeneration.

IF and tuner AGC

The automatic control voltage to maintain the video output

signal at a constant level is generated according to the

transmission standard. For negative modulation the

peak-sync level is detected, for positive modulation the

peak white level is detected. The AGC detector charges

and discharges the capacitor on pin 19 to set the IF gain

and the tuner gain. The standard is switched by the voltage

on pin 8. To reduce the response time for positive

modulation (which needs a very long time constant) a

black level detector (CBL) increases the AGC capacitor

discharge current for low-level video signals.

The AGC capacitor voltage is transferred to an internal IF

control signal, and is fed to the tuner AGC to generate the

tuner AGC output current on pin 12 (open-collector

output). The tuner AGC voltage take over point is adjusted

on pin 3. This allows the tuner and the IF SAW filter to be

matched to achieve the optimum IF input level.

Frequency detector, phase detector and video demodulator

The IF amplifier output signal is fed to a frequency detector

and to a phase detector. The frequency detector is

operational before lock-in. A DC current is generated

which is proportional to the frequency difference between

the input frequency and the VCO frequency. After lock-in,

the frequency detector and the phase detector generate a

DC current proportional to the phase difference between

VCO and input signals. The control signal for the VCO is

provided by the phase detector. The video demodulator is

a linear multiplier, designed for low distortion and wide

bandwidth. The vision IF input signal is multiplied by the

in-phase component of the VCO output. The demodulated

output signal is fed via an integrated low-pass filter

(f

= 12 MHz) to the video amplifier for suppression of the

g

carrier harmonics. The polarity of the video signal is

switched in the demodulator stage according to the TV

standard.

TDA9802

VCO and travelling wave divider

The VCO operates with a symmetrically-connected

reference LC-circuit, operating at double vision carrier

frequency. Frequency control is performed by an internal

varicap diode. The voltage to set the VCO frequency to the

actual frequency of double vision carrier frequency, is also

amplified and converted for the AFC output current.

The VCO signal is divided-by-two in a travelling wave

divider, which generates two differential output signals

with 90 degree phase difference independent of

frequency.

Video amplifier, buffer and noise clipping

The video amplifier is a wide bandwidth operational

amplifier with internal feedback. Dependent on

transmission standard, a level shifter provides the same

sync level for positive as for negative modulation. A

nominal positive modulated video signal of 1 V (p-p) is

present on the composite video output (pin 13).

The input impedance of the 7 dB wideband buffer amplifier

(with internal feedback) is suitable for ceramic sound trap

filters.

The CVBS output (pin 7) provides a positive video signal

of 2 V (p-p). Noise clipping is provided internally.

Sound demodulation

The FM sound intercarrier signal is fed to pin 11 and

through a limiter amplifier before it is demodulated. This

achieves high sensitivity and high AM suppression. The

limiter amplifier consists of seven internal AC-coupled

stages, minimizing the DC offset.

The FM-PLL demodulator consists of an RC-oscillator,

loop filter and phase detector. The oscillator frequency is

locked on the FM intercarrier signal from the limiter

amplifier.

As a result of this locking, the RC-oscillator is

frequency-modulated. The modulating signal voltage (AF

signal) is used to control the oscillator frequency. By this,

the FM-PLL operates as an FM demodulator.

The audio frequency amplifier with internal feedback is

designed for high gain and high common mode rejection.

The low-level AF signal output from the FM-PLL

demodulator is amplified and buffered in a low-ohmic

audio signal output stage (pin 9). An external decoupling

capacitor on pin 10 removes the DC voltage from the audio

amplifier input.

November 1992 5

Page 6

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

TDA9802

FM-PLL detector

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC134)

SYMBOL PARAMETER MIN. MAX. UNIT

V

P

V

I

t

s max

V

12

T

stg

V

ESD

Notes to the Limiting Values

1. Supply current I

2. Equivalent to discharging a 200 pF capacitor through a 0 Ω series resistor (negative and positive voltage).

THERMAL RESISTANCE

supply voltage (pin 20) for a maximum chip temperature (note 1)

SOT146 at + 120 °C 0 8.8 V

SO163A at + 100 °C 0 5.5 V

voltage on pins 1, 2, 7, 8, 11, 13, 14, 15 and 19 0 V

P

short-circuit time − 10 s

tuner AGC output voltage − 13.2 V

storage temperature range −25 +150 °C

electrostatic handling for all pins (note 2) −±300 V

= 69 mA at T

P

amb

= +70 °C.

V

SYMBOL PARAMETER THERMAL RESISTANCE

R

th j-a

from junction to ambient in free air

SOT146 73 K/W

SOT163A 85 K/W

November 1992 6

Page 7

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

TDA9802

FM-PLL detector

CHARACTERISTICS

=5V; T

V

P

(sync level at B/G; peak-white level at L); video modulation DSB; residual carrier: B/G = 10%, L = 3%; video signal in

accordance with CCIR line 17; measurements taken in Fig.3 unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

P

I

P

Standard switch input (pin 8)

V

IH

V

IL

I

IL

Vision IF input (pins 1 and 2)

V

i

∆V

i

G

IF

B −3 dB IF bandwidth upper cut-off frequency 70 100 − MHz

R

i

C

i

V

1, 2

True synchronous video demodulator

f

VCO

∆f

VCO

V

o ref

∆f

PC

t

acqu

V

iIF

I

loop

= +25 °C; fPC= 38.9 MHz; fSC= 33.4 MHz with VPC/VSC= 13 dB (B/G); V

amb

= 10 mV RMS value

iIF

supply voltage range (pin 20) see note 1 4.5 5 8.8 V

supply current 51 60 69 mA

input voltage for negative modulation see note 2 1.5 − V

P

input voltage for positive modulation 0 − 0.8 V

LOW level input current V8=0V −−300 −360 µA

B/G standard

input signal sensitivity (RMS value) −1 dB video at output − 50 90 µV

maximum input signal (RMS value) +1 dB video at output 70 150 − mV

IF amplitude difference between picture and

within AGC range − 0.7 1 dB

sound carrier

IF gain control range see Fig.4 64 70 73 dB

input resistance 1.7 2.2 2.7 kΩ

input capacitance 1.2 1.7 2.5 pF

DC input voltage 3.0 3.4 3.8 V

see note 3

maximum oscillator frequency for carrier

f=2f

PC

125 130 − MHz

regeneration

oscillator drift (free running) as a function of

temperature

oscillator swing at pins 16 and 17

see note 4;

∆T = 0 to+70 °C

−−±1300 10

tbn 120 tbn mV

(RMS value)

vision carrier capture range (negative) 1.5 2 − MHz

vision carrier capture range (positive) 1.5 2 − MHz

acquisition time see note 5; BL = 60 kHz −−30 ms

IF input signal sensitivity (RMS value, pins 1

and 2)

for PLL still locked see note 6;

− 70 100 µV

maximum IF gain

for C/N = 10 dB see note 7 − 100 140 µV

FPLL loop offset current at pin 6 see note 8 −−±4.5 µA

V

−6

November 1992 7

Page 8

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

TDA9802

FM-PLL detector

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Composite video amplifier (pin 13)

V

V

0 vid

13

output signal (peak-to-peak value) see Fig.7 0.9 1.0 1.1 V

sync level B/G and L 1.4 1.5 1.6 V

zero carrier level B/G 2.5 2.6 2.7 V

upper video clipping level V

lower video clipping level − 0.3 0.4 V

V

R

I

int13

I

13

0FM

13

IF intercarrier level (RMS value) sound carrier on;

output resistance −−10 Ω

internal bias current for emitter follower DC 1.8 2.5 − mA

maximum output sink current DC and AC 1.4 tbn − mA

maximum output source current 2.0 tbn − mA

B −3 dB video bandwidth C13< 50 pF; RL> 1kΩ 710− MHz

α

H

suppression of video signal harmonics see note 10;

RR ripple rejection on pin 13 see Fig.9 32 35 − dB

sound carrier off

L 1.37 1.47 1.57 V

−

VP−

P

1.1

− V

1.0

tbn 140 tbn mV

see note 9

35 40 − dB

C13< 50 pF; RL> 1kΩ

CVBS buffer amplifier and noise clipper (pins 7 and 14)

R

14

C

14

V

14

G

v

V

o CVBS

input resistance 2.6 3.3 4.0 kΩ

input capacitance 1.4 2 3.0 pF

DC voltage at input pin 14 not connected 1.5 1.8 2.1 V

voltage gain see note 11 6 7 7.5 dB

CVBS output signal on pin 7 (peak-to-peak

value)

sound carrier off;

see Fig.3

1.7 2.0 2.3 V

CVBS output level upper video clipping tbn 4.0 − V

lower video clipping − 1.0 tbn V

sync level 1.25 1.35 1.45 V

R

I

I

7

int7

7

output resistance −−10 Ω

internal bias current for emitter follower DC 1.8 2.5 − mA

maximum output sink current DC and AC 1.4 tbn − mA

maximum output source current 2.4 tbn − mA

B −3 dB video bandwidth C7< 20 pF; RL> 1kΩ 811− MHz

November 1992 8

Page 9

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

TDA9802

FM-PLL detector

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Measurements from IF input to CVBS output (pin 7) 330 Ω between pins 13 and 14, sound carrier off

V

o CVBS

CVBS output signal on pin 7 (peak-to-peak

value)

∆V

o

deviation of CVBS output signal at B/G 50 dB gain control −−0.5 dB

30 dB gain control −−0.1 dB

black level tilt B/G standard;

see note 12

vertical tilt for worst case in L standard vision carrier modulated

by test line (VITS) only;

see note 12

∆G differential gain − 25 %

∆ϕ differential phase − 1 3 deg

B −3 dB video bandwidth C

< 20 pF; RL> 1kΩ 68− MHz

L

S/N(W) signal-to-noise ratio; weighted see Fig.5 and note 13 56 59 − dB

α

1.1

α

3.3

α

C

intermodulation at ‘blue’ see Fig.6 and note 14;

intermodulation at ‘yellow’ 58 64 − dB

f = 1.1 MHz

intermodulation at ‘blue’ see Fig.6 and note 14;

intermodulation at ‘yellow’ 57 63 − dB

f = 3.3 MHz

residual vision carrier (RMS value) fundamental wave − 110 mV

harmonics − 110 mV

α

H

suppression of video signal harmonics see note 10 35 40 − dB

RR ripple rejection on pin 7 see Fig.9 25 28 − dB

1.7 2.0 2.3 V

−−1%

−−1.5 %

56 62 − dB

56 62 − dB

AGC detector (pin 19)

t

resp

response to an increasing amplitude step of

50 dB in input signal

response to a decreasing amplitude step of

50 dB in input signal

I

19

charging current B/G and L; see note 12 0.85 1.1 1.35 mA

additional charging current L in case of missing

discharging current B/G 17 22 27 µA

V

19

V

13

AGC voltage see Fig.4

threshold voltage level see Fig.7

for additional charging current L 1.9 1.95 2.0 V

for fast L mode L 1.6 1.65 1.7 V

B/G and L − 110 ms

B/G − 50 100 ms

L − 100 150 ms

2.0 2.7 3.5 µA

VITS pulses and no

white video content

normal mode L 0.24 0.33 0.42 µA

fast mode L 31 44 57 µA

maximum gain 0 tbn − V

minimum gain − tbn VP− 0.7 V

November 1992 9

Page 10

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

TDA9802

FM-PLL detector

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Tuner AGC (pin 12)

V

i

IF input signal for minimum starting point of

tuner take over (RMS value)

IF input signal for maximum starting point of

tuner take over (RMS value)

V

12

allowable voltage from external source −−13.2 V

saturation voltage I

∆V

12

I

12

∆G

IF

variation of take over point by temperature ∆T = 0 to +50 °C − 13 dB

sink current see Fig.4

IF slip by automatic gain control tuner gain current from

AFC circuit (pin 15)

S control steepness ∆I

∆f

V

IF

15

frequency variation by temperature ∆T = 0 to +70 °C;

output voltage upper limit see Fig.8 VP−

/∆f see note 16 0.6 0.72 0.84 µA/kHz

15

output voltage lower limit − 0.3 0.5 V

I

15

output current source 160 200 240 µA

output current sink 160 200 240 µA

∆I

15

residual video modulation current

(peak-to-peak value)

Sound mute switch (pin 5)

V

V

I

IL

α

∆V

IL

IH

mute

5

input voltage for MUTE-ON 0 − 0.8 V

input voltage for MUTE-OFF 1.5 − V

LOW level input current V5=0V −−300 −360 µA

audio attenuation V5=0V 70 80 − dB

DC offset voltage at switching (plop) switching to MUTE-ON − 100 500 mV

FM sound limiter amplifier (pin 11)

V

iFM

input signal (RMS value, pin 11) CCIR468-4

for S/N = 40 dB see Fig.11 − 200 300 µV

for AM suppression α

= 40 dB AM: f = 1 kHz; m = 0.3 − 1 − mV

AM

maximum input signal handling (RMS value) 200 −− mV

R

11

input resistance 480 600 720 Ω

B −3 dB IF frequency response of sound IF lower and upper

V

11

DC voltage 2.3 2.6 2.9 V

input at pins 1 and 2;

R

=22kΩ

TOP

input at pins 1 and 2;

R

=0Ω

TOP

= 1.7 mA −−0.2 V

12

−−5mV

50 −− mV

no tuner gain reduction − 0.1 0.3 µA

maximum tuner gain

1.7 2.0 2.6 mA

reduction

− 68 dB

20 to 80%

see Fig.8 and note 15

−−±1300 10

see note 4

VP−

− V

0.5

0.3

B/G and L − 20 30 µA

see note 17

P

V

FM 5.5 MHz

3.5 − 10 MHz

cut-off frequency

−6

November 1992 10

Page 11

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

TDA9802

FM-PLL detector

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

FM−PLL sound demodulator and AF output (pin 9)

f

iFM

catching range of PLL 4 − 7 MHz

holding range of PLL 3.5 − 8 MHz

t

acqu

∆f

AF

V

10

V

oAF

acquisition time −−4 µs

frequency deviation THD < 1.5%;

DC voltage at decoupling capacitor voltage dependent on

AF output signal (RMS value, pin 9) ∆fAF= ±27 kHz;

maximum output signal handling THD < 1.5% 0.8 −− V

∆V

o

R

9

R

L

V

9

temperature drift of AF output signal ∆T = 0 to+70 °C − 0.2 0.5 dB

output resistance − 100 −Ω

load resistance (pin 9) 2.2 −− kΩ

DC voltage 1.6 2.0 2.4 V

B −3 dB audio frequency bandwidth 95 120 − kHz

THD total harmonic distortion − 0.1 0.5 %

S/N (W) signal-to-noise ratio, weighted CCIR468-4; see Fig.11 50 55 − dB

V

SC

residual sound carrier and harmonics (RMS

value)

α

AM

AM suppression see Fig.10;

RR ripple rejection on pin 9 see Fig.9 26 30 − dB

see note 18

−−±50 kHz

see note 19

1.2 − 2.2 V

VCO frequency;

see note 20

280 350 420 mV

see Fig.11

−−75 mV

46 50 − dB

AM: f = 1 kHz; m = 0.3

Measurements from IF input to audio output (pin 9)

S/N (W) weighted signal-to-noise ratio referred to

560 Ω between pins 13 and 11

CCIR468-4; with offset alignment on pin 4

54% FM modulation

6 kHz sinusoidal waveform black-to-white 39 46 − dB

black level sync only 39 48 − dB

white picture 39 46 − dB

November 1992 11

Page 12

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

TDA9802

FM-PLL detector

Notes to the characteristics

1. Typical values of video and sound parameters are decreased at VP= 4.5 V.

2. The input voltage for negative modulation has to be V8> 1.5 V, or pin 8 open-circuit.

3. Loop bandwidth BL = 60 kHz (natural frequency fn= 15 kHz; damping factor d = 2 calculated with grey level and

FPLL input signal level).

Resonance circuit of VCO: Qo> 50; C

4. The oscillator drift is related to the picture carrier frequency (at external temperature-compensated LC-circuit).

5. V

= 10 mV (RMS value); ∆f = 1 MHz (VCO frequency offset related to picture carrier frequency); white picture

iIF

video modulation.

6. V

for 0.9 V CVBS (peak-to-peak value) at composite video output pin 13; PLL is still locked.

iIF

7. Transformer at IF input (Fig.3). The C/N ratio at IF input for ‘lock-in’ is defined as the vision IF input signal (sync level,

RMS value) in relation to a superimposed, 5 MHz band-limited white noise signal (RMS value); video modulation:

white picture.

8. Offset current measured between pin 6 and half of supply voltage (V = 2.5 V) under the following conditions: no input

signal at IF input (pins 1 and 2) and IF-amplifier gain at minimum (V19=VP), pin 4 (phase adjust) open-circuit.

9. The intercarrier output signal is superimposed to the video signal at pin 13 and can be calculated by the following

formula:

V

20

13 interc.

log

------------------------------------------

pp–()

1V p p–()

V

iSC

----------- V

iPC

with

V

iSC

dB sound to picture carrier ratio at IF input (pins 1 and 2) in dB=

----------- V

iPC

and

±2 dB = tolerance of intercarrier output amplitude V

10. Measurements taken with SAW filter G1956; modulation: VSB, f

11. The 7 dB buffer gain accounts for 1 dB loss in the sound trap. Buffer output signal is typical 2 V (p-p). If no sound

trap is applied a 330 Ω resistor must be connected from output to input (from pin 13 to pin 14).

12. The leakage current of the AGC capacitor has to be < 1µA in B/G mode (< 30 nA in L mode) to avoid larger tilt.

13. S/N is the ratio of black-to-white amplitude to the black level noise voltage (RMS value, pin 7). B = 5 MHz weighted

in accordance with CCIR-567 at a source impedance of 50 Ω.

14. α

= 20 log (Voat 4.4 MHz / Vo at 1.1 MHz) + 3.6 dB; α

1.1

α

= 20 log (Voat 4.4 MHz / Vo at 3.3 MHz); α

3.3

15. To match the AFC output signal to different tuning systems a current source output is provided (Fig.8).

16. Depending on the radio ∆C/Coof the LC resonance circuit of VCO

(Qo> 50; Co=C

int+Cext

; C

ext

= 8.2 pF; C

17. No mute state is also valid for pin not connected. For switching on the L-standard no external load is allowed at pin

5 except capacitor CBL.

18. A 5.5 MHz signal for second IF with 10 mV (RMS value) input level, f

FM modulation of audio reference is fed directly to pin 11. Audio measurements are taken at 50 µs de-emphasis.

19. To allow higher frequency deviation, the resistor Rxon pin 10 (see Fig.12) has to be increased to a value which does

not exceed the AF output signal of nominally 0.35 V for THD = 0.1% (Rx= 4.7 kΩ provides −6 dB amplification).

20. The leakage current of the 2.2 µF capacitor is < 100 nA.

dB 6.9 dB 2 dB±+=

= 8.2 pF; C

ext

≈ 8.5 pF).

int

≈ 8.5 pF (loop voltage about 2.7 V).

int

o FM.

> 0.5 MHz, loop bandwidth BL = 60 kHz.

video

value at 1.1 MHz related to black/white signal

1.1

value at 3.3 MHz related to colour carrier.

3.3

= 1 kHz and frequency deviation with 54%

mod

November 1992 12

Page 13

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

TDA9802

Fig.3 Test circuit.

November 1992 13

Page 14

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

70

handbook, full pagewidth

60

G

IF

(dB)

50

40

30

20

10

0

−10

0

1234

(2) (3) (4)

(1)

TDA9802

MED332

V19 (V)

5

I

12

(mA)

0

0.2

0.6

1.0

1.4

1.8

2.0

80

handbook, halfpage

S/N

(dB)

60

40

20

0

−60 −40 −20 20

0.06 0.6 6 60060

Fig.4 IF AGC (dashed) and tuner AGC as a function of take over point adjustment.

MED333

0

V

10

V

i IF(rms)

i IF(rms)

(dB)

(mV)

handbook, halfpage

−13.2 dB

−24 dB

SC CC PC SC CC PC

SC = sound carrier level ; with respect to TOP sync level.

CC = chrominance carrier level ; with respect to TOP sync level.

PC = picture carrier level ; with respect to TOP sync level.

Sound shelf attenuation: 17 dB.

−3.2 dB

−13.2 dB

−24 dB

BLUE YELLOW

−10 dB

MED334

Fig.5 Typical signal-to-noise ratio as a function of

IF input signal.

November 1992 14

Fig.6 Input conditions for intermodulation

measurements.

Page 15

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

Fig.7 Video signal levels on output pin 13.

TDA9802

Fig.8 Measurement conditions and typical AFC characteristic.

Fig.9 Ripple rejection condition.

November 1992 15

Page 16

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

α

(dB)

−100

AM

−20

−40

−60

−80

0

−1

10

1

Fig.10 Typical AM suppression of FM sound demodulator.

handbook, full pagewidth

10 10

TDA9802

MED338

2

V

(mV)

i IC

3

10

handbook, full pagewidth

370

V

o AF

(mV RMS)

360

350

340

330

−1

10

(1)

(2)

11010

2

Vi FM (mV)

Fig.11 Typical AF output signal and signal-to-noise ratio.

MED339

S/N (W)

3

10

60

(dB)

50

40

30

20

November 1992 16

Page 17

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

TDA9802

(1) depends on tuner

Fig.12 Application circuit.

November 1992 17

Page 18

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

TDA9802

(1) depends on TOP

Fig.13 Front end level diagram.

November 1992 18

Page 19

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

TDA9802

November 1992 19

Fig.14 Internal circuits.

Page 20

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

PACKAGE OUTLINE

DIP20: plastic dual in-line package; 20 leads (300 mil)

D

seating plane

L

Z

20

e

b

TDA9802

SOT146-1

M

E

A

2

A

A

1

w M

b

1

11

c

(e )

1

M

H

pin 1 index

1

0 5 10 mm

scale

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

A

A

A

UNIT

inches

Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

max.

mm

OUTLINE

VERSION

SOT146-1

1 2

min.

max.

1.73

1.30

0.068

0.051

IEC JEDEC EIAJ

b

b

1

0.53

0.38

0.021

0.015

0.36

0.23

0.014

0.009

REFERENCES

cD E e M

(1) (1)

26.92

26.54

1.060

1.045

SC603

6.40

6.22

0.25

0.24

E

10

(1)

M

e

L

1

3.60

8.25

3.05

7.80

0.14

0.32

0.12

0.31

EUROPEAN

PROJECTION

H

E

10.0

0.2542.54 7.62

8.3

0.39

0.010.10 0.30

0.33

ISSUE DATE

w

92-11-17

95-05-24

Z

max.

2.04.2 0.51 3.2

0.0780.17 0.020 0.13

November 1992 20

Page 21

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

SO20: plastic small outline package; 20 leads; body width 7.5 mm

D

c

y

Z

20

11

TDA9802

SOT163-1

E

H

E

A

X

v M

A

pin 1 index

1

e

0 5 10 mm

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

mm

A

max.

2.65

0.10

A

1

0.30

0.10

0.012

0.004

A

2

2.45

2.25

0.096

0.089

A

0.25

0.01

b

0.49

0.36

p

cD

0.32

0.23

0.013

0.009

3

0.019

0.014

UNIT

inches

Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

10

w M

b

p

scale

(1)E(1) (1)

13.0

12.6

0.51

0.49

eHELLpQ

7.6

1.27

7.4

0.30

0.050

0.29

10.65

10.00

0.419

0.394

Q

A

2

A

1

1.4

0.055

1.1

0.4

0.043

0.016

detail X

1.1

1.0

0.043

0.039

(A )

L

p

L

0.25

0.01

A

3

θ

0.25 0.1

0.01

ywv θ

Z

0.9

0.4

8

0.004

0.035

0.016

0

o

o

OUTLINE

VERSION

SOT163-1

IEC JEDEC EIAJ

075E04 MS-013AC

REFERENCES

November 1992 21

EUROPEAN

PROJECTION

ISSUE DATE

95-01-24

97-05-22

Page 22

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

FM-PLL detector

SOLDERING

Introduction

There is no soldering method that is ideal for all IC

packages. Wave soldering is often preferred when

through-hole and surface mounted components are mixed

on one printed-circuit board. However, wave soldering is

not always suitable for surface mounted ICs, or for

printed-circuits with high population densities. In these

situations reflow soldering is often used.

This text gives a very brief insight to a complex technology.

A more in-depth account of soldering ICs can be found in

“IC Package Databook”

our

DIP

SOLDERING BY DIPPING OR BY WAVE

The maximum permissible temperature of the solder is

260 °C; solder at this temperature must not be in contact

with the joint for more than 5 seconds. The total contact

time of successive solder waves must not exceed

5 seconds.

The device may be mounted up to the seating plane, but

the temperature of the plastic body must not exceed the

specified maximum storage temperature (T

printed-circuit board has been pre-heated, forced cooling

may be necessary immediately after soldering to keep the

temperature within the permissible limit.

R

EPAIRING SOLDERED JOINTS

Apply a low voltage soldering iron (less than 24 V) to the

lead(s) of the package, below the seating plane or not

more than 2 mm above it. If the temperature of the

soldering iron bit is less than 300 °C it may remain in

contact for up to 10 seconds. If the bit temperature is

between 300 and 400 °C, contact may be up to 5 seconds.

SO

REFLOW SOLDERING

Reflow soldering techniques are suitable for all SO

packages.

(order code 9398 652 90011).

). If the

stg max

TDA9802

Several techniques exist for reflowing; for example,

thermal conduction by heated belt. Dwell times vary

between 50 and 300 seconds depending on heating

method. Typical reflow temperatures range from

215 to 250 °C.

Preheating is necessary to dry the paste and evaporate

the binding agent. Preheating duration: 45 minutes at

45 °C.

AVE SOLDERING

W

Wave soldering techniques can be used for all SO

packages if the following conditions are observed:

• A double-wave (a turbulent wave with high upward

pressure followed by a smooth laminar wave) soldering

technique should be used.

• The longitudinal axis of the package footprint must be

parallel to the solder flow.

• The package footprint must incorporate solder thieves at

the downstream end.

During placement and before soldering, the package must

be fixed with a droplet of adhesive. The adhesive can be

applied by screen printing, pin transfer or syringe

dispensing. The package can be soldered after the

adhesive is cured.

Maximum permissible solder temperature is 260 °C, and

maximum duration of package immersion in solder is

10 seconds, if cooled to less than 150 °C within

6 seconds. Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal

of corrosive residues in most applications.

EPAIRING SOLDERED JOINTS

R

Fix the component by first soldering two diagonally-

opposite end leads. Use only a low voltage soldering iron

(less than 24 V) applied to the flat part of the lead. Contact

time must be limited to 10 seconds at up to 300 °C. When

using a dedicated tool, all other leads can be soldered in

one operation within 2 to 5 seconds between

270 and 320 °C.

Reflow soldering requires solder paste (a suspension of

fine solder particles, flux and binding agent) to be applied

to the printed-circuit board by screen printing, stencilling or

pressure-syringe dispensing before package placement.

November 1992 22

Page 23

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL demodulator and

TDA9802

FM-PLL detector

DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or

more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation

of the device at these or at any other conditions above those given in the Characteristics sections of the specification

is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these

products can reasonably be expected to result in personal injury. Philips customers using or selling these products for

use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such

improper use or sale.

November 1992 23

Loading...

Loading...