Page 1

INTEGRATED CIRCUITS

DATA SH EET

TDA9150B

Programmable deflection controller

Preliminary specification

File under Integrated Circuits, IC02

Philips Semiconductors

July 1994

Page 2

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

FEATURES

General

• 6.75, 13.5 and 27 MHz clock frequency

• Few external components

• Synchronous logic

2

• I

C-bus controlled

• Easy interfacing

• Low power

• ESD protection

• Flash detection with restart

• Two-level sandcastle pulse.

Vertical deflection

Horizontal deflection

• Phase 2 loop with low jitter

• Internal loop filter

• Dual slicer horizontal flyback input

2

• Soft start by I

C-bus

• Over voltage protection/detection with selection and

status bit.

• Self adaptive 16-bit precision vertical scan

• DC coupled deflection to prevent picture bounce

• Programmable fixed compression to 75%

• S-correction can be preset

• S-correction setting independent of the field frequency

• Differential output for high DC stability

• Current source outputs for high EMC immunity

• Programmable de-interlace phase.

East-West correction

• DC coupled EW correction to prevent picture bounce

• 2nd and 4th order geometry correction can be preset

• Trapezium correction

• Geometry correction settings are independent of field

frequency

• Self adaptive Bult generator prevents ringing of the

horizontal deflection

• Current source output for high EMC immunity.

ORDERING INFORMATION

EHT correction

• Input selection between aquadag or EHT bleeder

• Internal filter.

GENERAL DESCRIPTION

The TDA9150B is a programmable deflection controller

contained in a 20-pin DIP package and constructed using

BIMOS technology. This high performance

synchronization and DC deflection processor has been

especially designed for use in both digital and analog

based TV receivers and monitors, and serves horizontal

and vertical deflection functions for all TV standards. The

TDA9150B uses a line-locked clock at 6.75, 13.5 or

27 MHz, depending on the line frequency and application,

and requires only a few external components. The device

is self-adaptive for a number of functions and is fully

2

programmable via the I

C-bus.

TYPE NUMBER

PINS PIN POSITION MATERIAL CODE

TDA9150B 20 DIP plastic SOT146-1

July 1994 2

PACKAGE

Page 3

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

CC

I

CC

P

tot

T

amb

Inputs

V

14

V

13

V

12

V

5

V

18

V

17

V

PSL

V

1

V

3

V

9

Outputs

V

20

I

11−I10(M)

V

10,11

I

6(M)

V

6

SANDCASTLE OUTPUT LEVELS (DSC)

V

2

V

2

V

2

HORIZONTAL OFF-CENTRE SHIFT (OFCS)

V

19

supply voltage 7.2 8.0 8.8 V

supply current f

= 6.75 MHz − 27 − mA

clk

total power dissipation − 220 − mW

operating ambient temperature −25 − +70 °C

line-locked clock (LLC) logic level − TTL −

horizontal sync (HA) logic level − TTL −

vertical sync (VA) logic level − TTL −

line-locked clock select (LLCS)

note 1 − CMOS 5 V −

logic level

serial clock (SCL) logic level − CMOS 5 V −

serial data input (SDA) logic level − CMOS 5 V −

horizontal flyback (HFB) phase

slicing level

horizontal flyback (HFB) blanking

FBL = logic 0 − 3.9 − V

FBL = logic 1 − 1.3 − V

− 100 − mV

slicing level

over voltage protection (PROT)

− 3.9 − V

level

EHT flash detection level − 1.5 − V

horizontal output (HOUT) voltage

I20 = 10 mA −− 0.5 V

(open drain)

vertical differential (VOUT

output current (peak value)

A, B

)

vertical amplitude = 100%;

I8 = −120 µA; note 2

440 475 510 µA

vertical output voltage 0 − 3.9 V

EW (EWOUT) total output current

I8 = −120 µA −− 930 µA

(peak value)

EW (EWOUT) output voltage 1.0 − 5.5 V

base voltage level − 0.5 − V

horizontal and vertical blanking

− 2.5 − V

voltage level

video clamping voltage level − 4.5 − V

output voltage I19 = 2 mA 0 − V

CC

V

Notes

1. Hard wired to ground or V

is highly recommended.

CC

2. DAC values: vertical amplitude = 31; EHT = 0; SHIFT = 3; SCOR = 0.

July 1994 3

Page 4

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

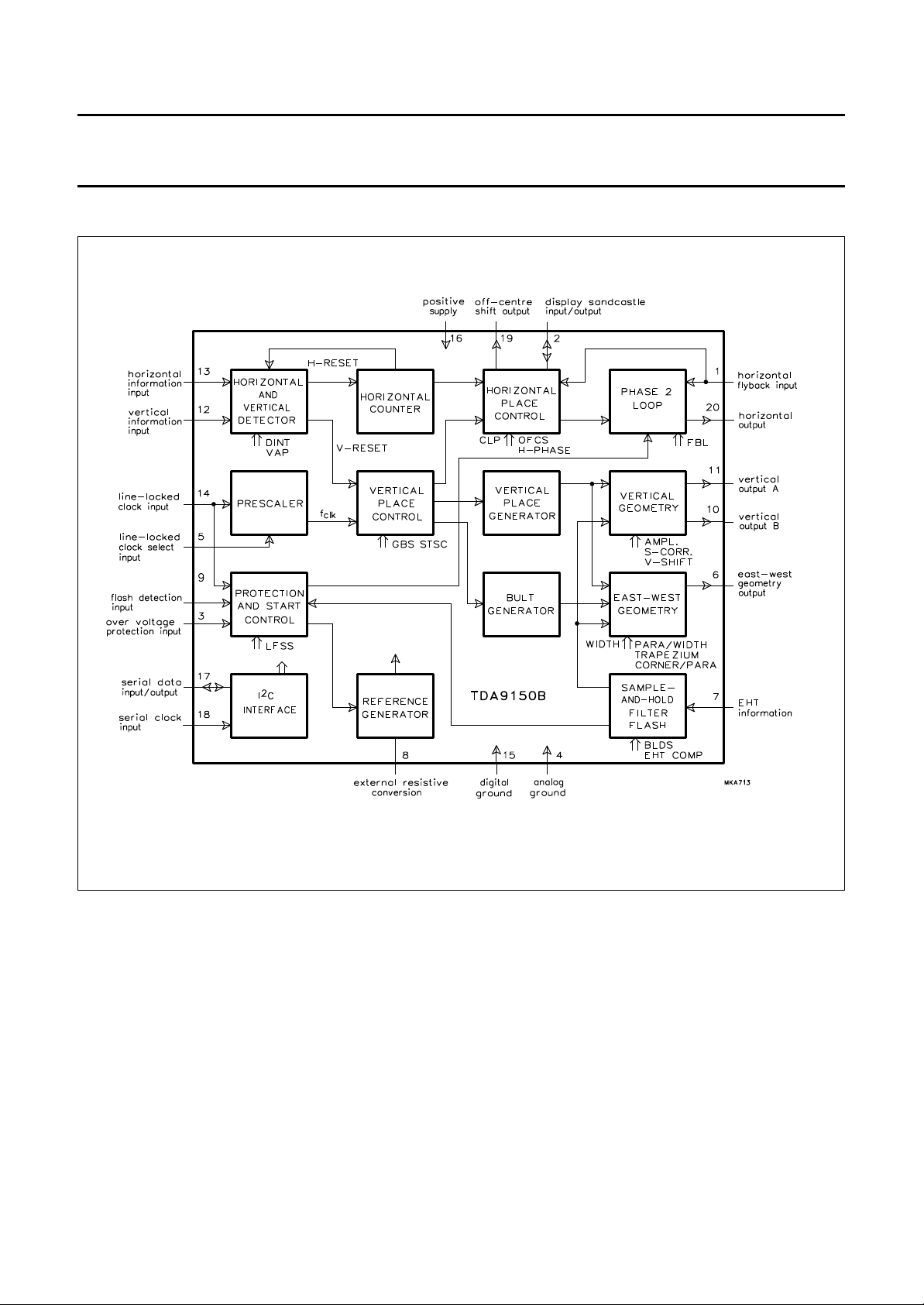

BLOCK DIAGRAM

Fig.1 Block diagram.

July 1994 4

Page 5

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

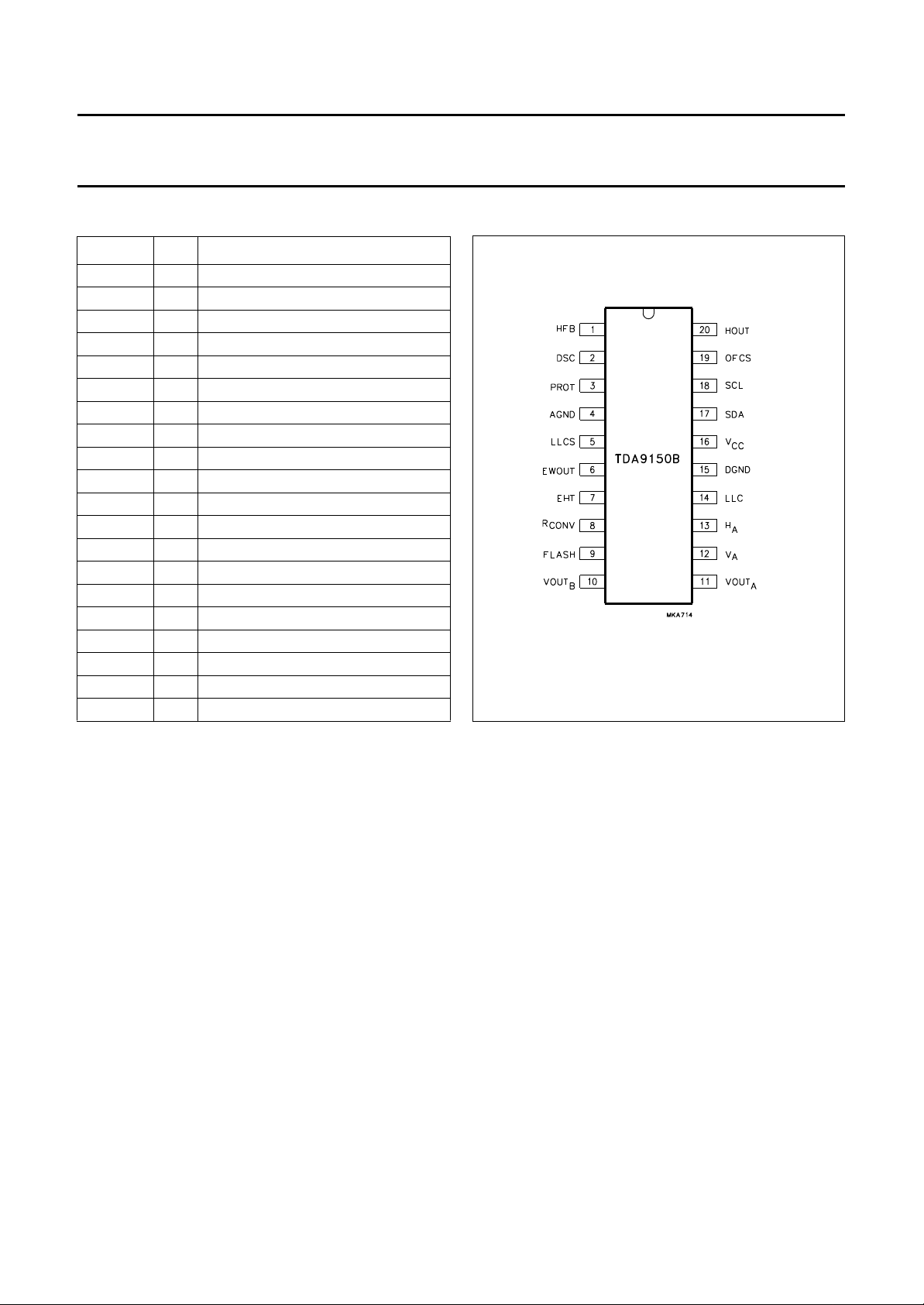

PINNING

SYMBOL PIN DESCRIPTION

HFB 1 horizontal flyback input

DSC 2 display sandcastle input/output

PROT 3 over voltage protection input

AGND 4 analog ground

LLCS 5 line-locked clock selection input

EWOUT 6 east-west geometry output

EHT 7 EHT compensation

R

CONV

FLASH 9 flash detection input

VOUT

B

VOUT

A

V

A

H

A

LLC 14 line-locked clock input

DGND 15 digital ground

V

CC

SDA 17 serial data input/output

SCL 18 serial clock input

OFCS 19 off-centre shift output

HOUT 20 horizontal output

8 external resistive conversion

10 vertical output B

11 vertical output A

12 vertical information input

13 horizontal information input

16 supply input (+8 V)

Fig.2 Pin configuration.

FUNCTIONAL DESCRIPTION

Input signals (pins 12, 13, 14, 17 and 18)

The TDA9150B requires three signals for minimum

operation (apart from the supply). These signals are the

line-locked clock (LLC) and the two I

2

C-bus signals (SDA

and SCL). Without the LLC the device will not operate

because the internal synchronous logic uses the LLC as

the system clock.

I2C-bus transmissions are required to enable the device to

perform its required tasks. Once started the IC will use the

HA and/or VA inputs for synchronization. If the LLC is not

present the outputs will be switched off and all operations

discarded (if the LLC is not present the line drive will be

inhibited within 2 µs, the EW output current will drop to

zero and the vertical output current will drop to 20% of the

adjusted value within 100 µs). The SDA and SCL inputs

meet the I

2

C-bus specification, the other three inputs are

TTL compatible.

The LLC frequency can be divided-by-two internally by

connecting LLCS (pin 5) to ground thereby enabling the

prescaler.

The LLC timing is given in the Chapter “Characteristics”.

July 1994 5

Page 6

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

I2C-bus commands

Slave address: 8C HEX = 1000110X BIN

READ MODE

The format of the status byte is: PON PROT 000000

Where:

PON is the status bit for power-on reset (POR) and after

power failure:

• Logic 1:

– after the first POR and after power failure; also set to

1 after a severe voltage dip that may have disturbed

the various settings

– POR 1 to 0 transition, VCC = 6.25 V (typ.)

– POR 0 to 1 transition, VCC = 5.75 V (typ.)

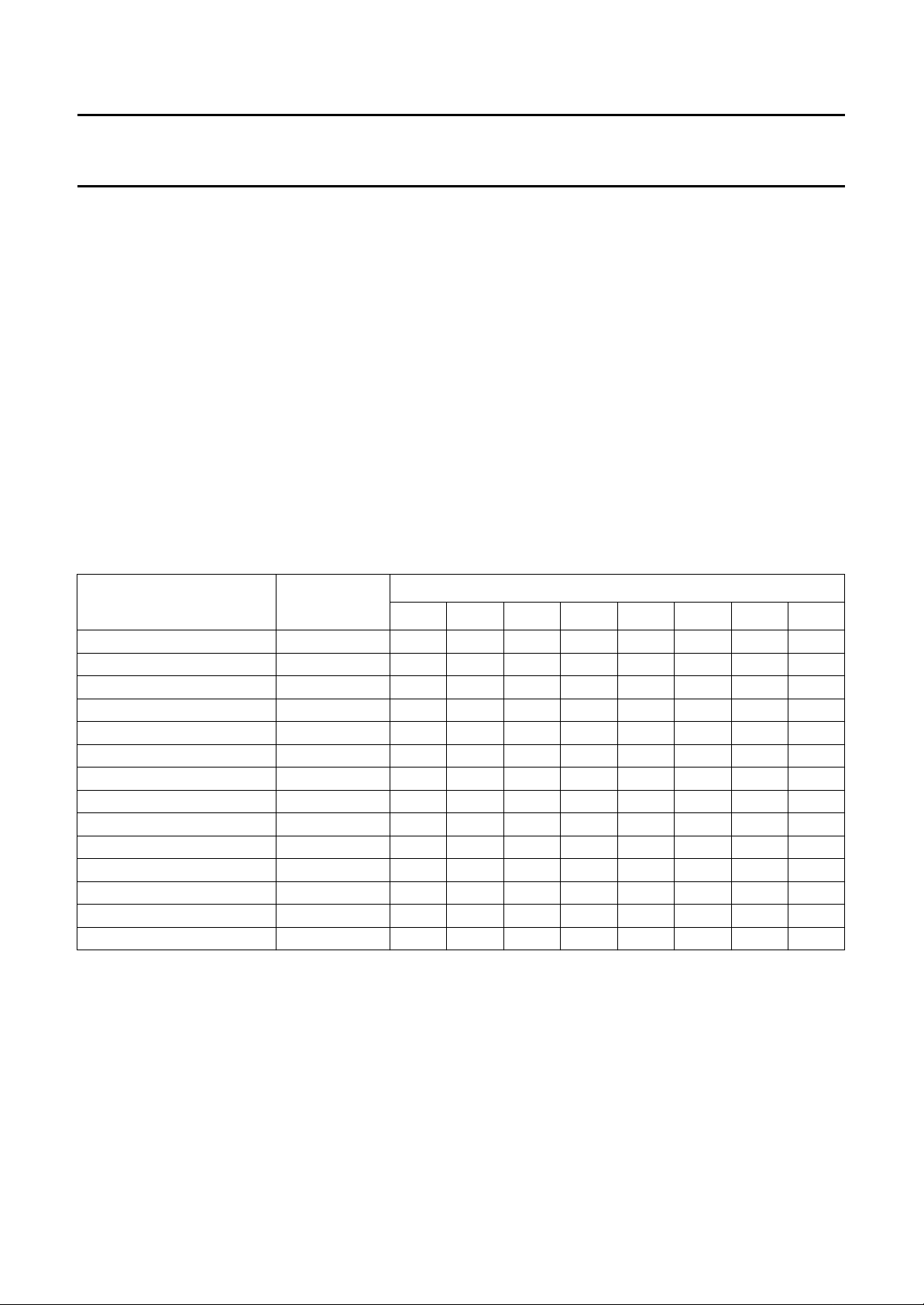

Table 1 Write mode with auto increment; subaddress and data byte format.

FUNCTION SUBADDRESS

Vertical amplitude 00 X

Vertical S-correction 01 X X A5 A4 A3 A2 A1 A0

Vertical start scan 02 X X A5 A4 A3 A2 A1 A0

Vertical off-centre shift 03 X note 2 note 2 note 2 X A2 A1 A0

EW trapezium correction 03 X A6 A5 A4 X note2 note2 note2

EW width/width ratio 04 X X A5 A4 A3 A2 A1 A0

EW parabola/width ratio 05 X X A5 A4 A3 A2 A1 A0

EW corner/parabola ratio 06 X X A5 A4 A3 A2 A1 A0

EHT compensation 07 X X A5 A4 A3 A2 A1 A0

Horizontal phase 08 X X A5 A4 A3 A2 A1 A0

Horizontal off-centre shift 09 X X A5 A4 A3 A2 A1 A0

Clamp shift 0A X XXXXA2A1A0

Control 1 0B MS WS FBL VAP BLDS LFSS DINT GBS

Control 2 0F X X X VPR CPR DIP PRD CSU

D7 D6 D5 D4 D3 D2 D1 D0

(1)

• Logic 0:

– after a successful read of the status byte.

PROT is the over voltage detection for the scaled EHT

input:

• Logic 1:

– if the scaled EHT rises above the reference value of

3.9 V

• Logic 0:

– after a successful read of the status byte and EHT

<3.9 V.

Remark: a read action is considered successful when an

End Of Data signal has been detected (i.e. no master

acknowledge).

DATA BYTE

X A5A4A3A2A1A0

Notes

1. X = don’t care.

2. Data bit used in another function.

July 1994 6

Page 7

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

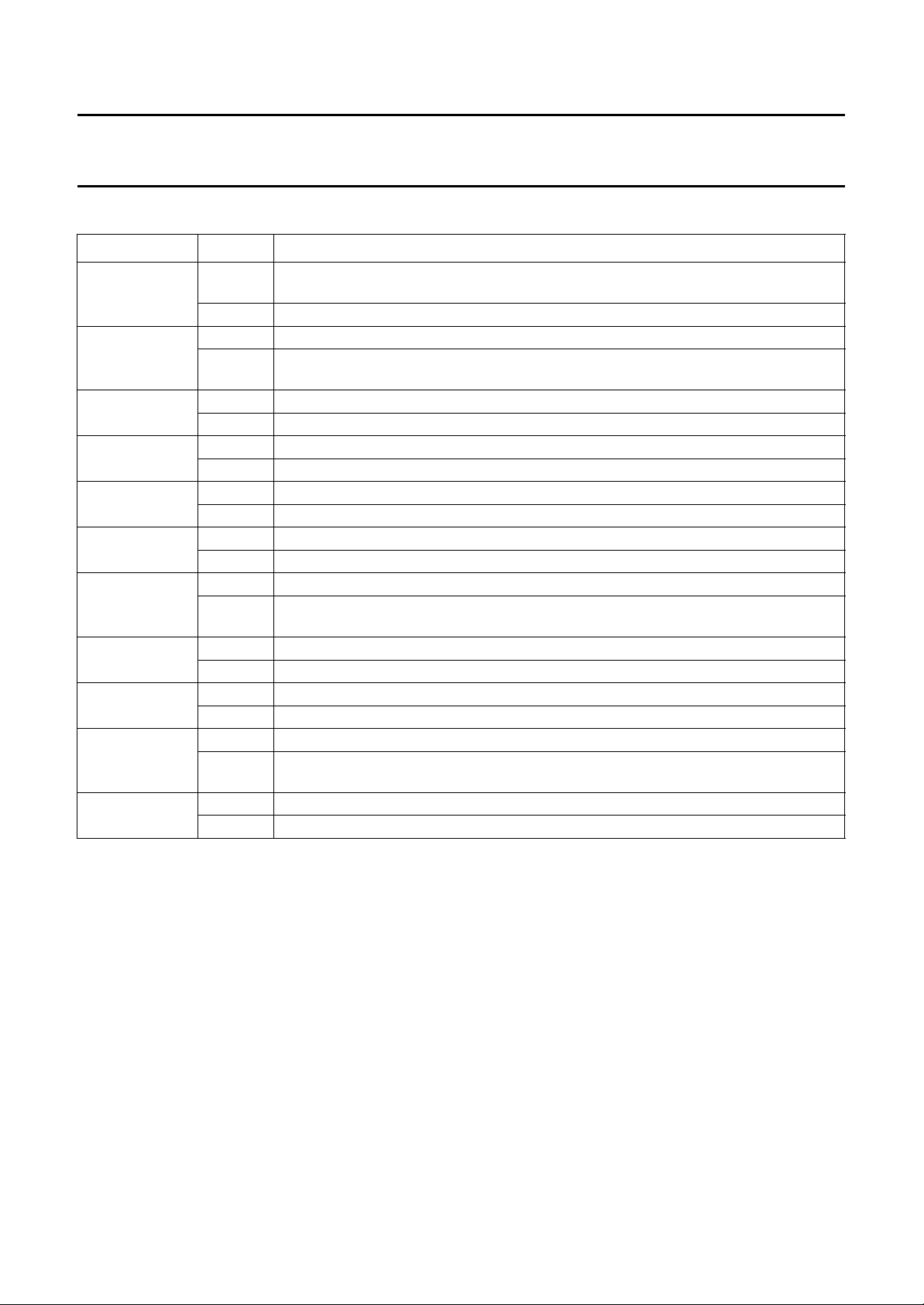

Table 2 Control bits.

CONTROL BIT LOGIC FUNCTION

LFSS 0 Line stop: EW output current becomes zero and the vertical output current is reduced

to 20% of the adjusted value. LFSS becomes logic 0 after a HIGH on PON.

1 Line start enabled: the soft start mechanism is now activated.

DINT 0 De-interlace on: the V

1 De-interlace off: the V

edge is used as vertical reset.

BLDS 0 Aquadag selected.

1 Bleeder selected.

GBS 0 Becomes logic 0 after power-on.

1 Guard band 48/12 lines.

VAP 0 Positive V

1 Negative V

edge detection.

A

edge detection.

A

FBL 0 Horizontal flyback slicing level = 3.9 V.

1 Horizontal flyback slicing level = 1.3 V.

CSU 0 No clamping suppression, standard mode of operation.

1 Clamping suppression in wait, stop and protection modes

(used in systems with e.g. TDA4680/81).

PRD 0 No defeat of HOUT, the over voltage information is only written in the PROT status bit.

1 HOUT is defeated and status bit PROT is set when over voltage is detected.

DIP 0 V

1V

is sampled 42 clock pulses after the leading edge of HA.

A

is sampled 258 clock pulses after the leading edge of HA.

A

CPR 0 Nominal amplitude.

1 Compression to 75% of adjusted amplitude, used for display of 16 : 9 standard pictures

on 4 : 3 displays.

VPR 0 Nominal amplitude (100%) during wait, stop and clipping.

1 Amplitude reduced to 20% during wait, stop and clipping.

pulse is sampled at a position selected with control bit DIP.

A

pulse is sampled with the system clock and the detected rising

A

July 1994 7

Page 8

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

Table 3 Explanation of control bits shown in Table 2.

CONTROL BITS DESCRIPTION

LFSS line frame start/stop

DINT de-interlace

BLDS bleeder mode selection

GBS guard band selection

VAP polarity of V

FBL flyback slicing level

CSU clamping suppression mode

PRD protection/detection mode

DIP de-interlace phase

CPR compression on/off

VPR vertical power reduction mode

Table 4 Clock frequency control bit (pin 5; note 1).

edge detection

A

CONTROL BIT LOGIC FUNCTION

LLCS 0 prescaler on: the internal clock frequency f

1 prescaler off (default by internal pull-up resistor): the internal clock frequency f

clk

=1⁄2f

LLC

clk

= f

LLC

Note

1. Switching of the prescaler is only allowed when LFSS is LOW. It is highly recommended to hard wire LLCS to ground

. Active switching may damage the output power transistor due to the changing HOUT pulse. This may cause

or V

CC

very high currents and large flyback pulses. The permitted combinations of LLC and the prescaler are shown in

Table 5.

Table 5 Line duration with prescaler.

LLC (MHz) ON (µs) OFF (µs)

6.75 note 1 64

13.5 64 32

27 32 note 1

Note

1. Combination not allowed.

July 1994 8

Page 9

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

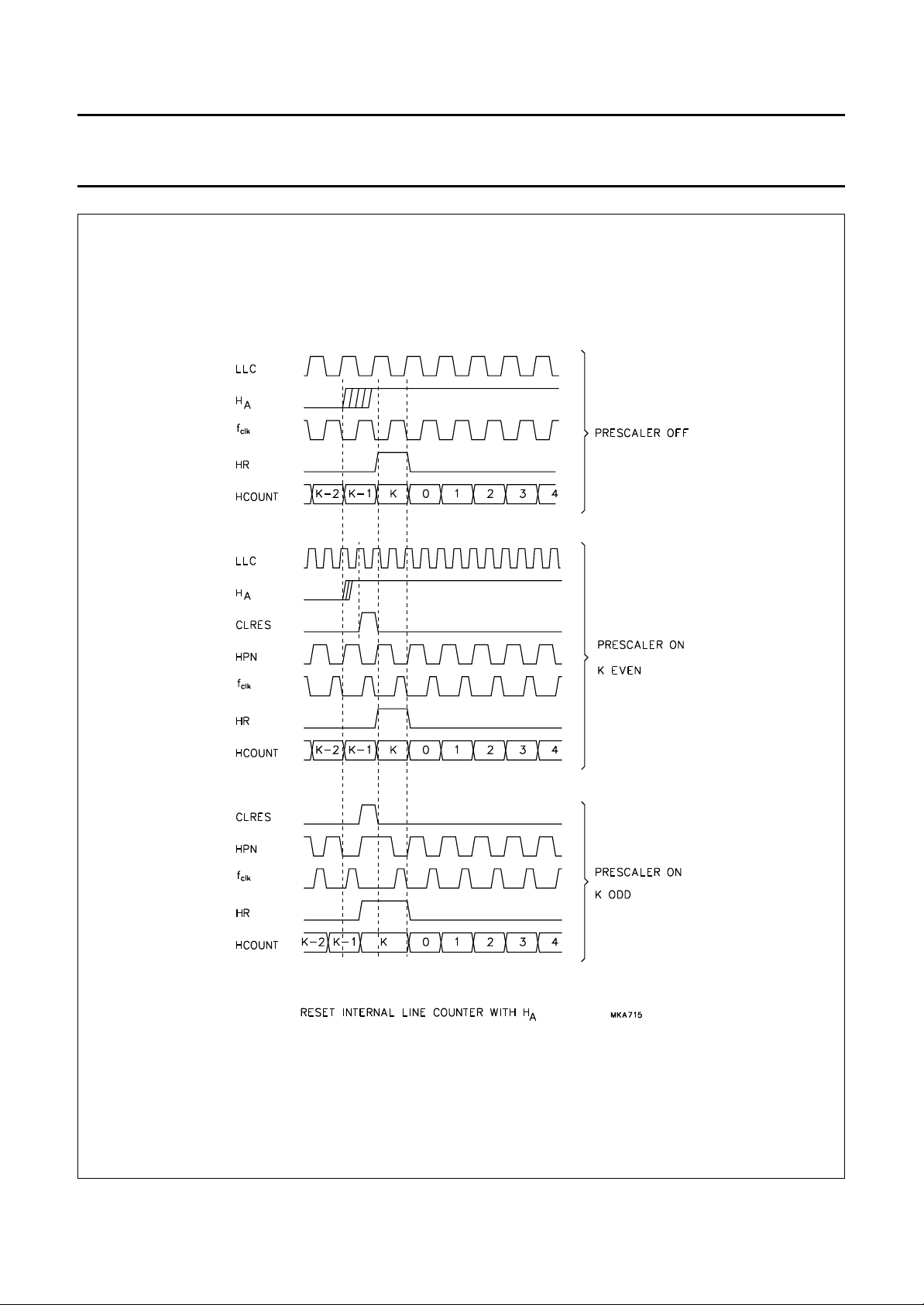

Fig.3 Timing relations between LLC, HA and line counter.

July 1994 9

Page 10

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

Horizontal part (pins 1, 2, 13, 19 and 20)

S

YNCHRONIZATION PULSE

The HA input (pin 13) is a TTL-compatible CMOS input.

Pulses on this input have to fulfil the timing requirements

as illustrated in Fig.6. For correct detection the minimum

pulse width for both the HIGH and LOW periods is 2

internal clock periods.

F

LYBACK INPUT PULSE

The HFB input (pin 1) is a CMOS input. The delay of the

centre of the flyback pulse to the leading edge of the H

A

pulse can be set via the I2C-bus with the horizontal phase

byte (subaddress 08), as illustrated in Fig.7. The

resolution is 6-bit.

UTPUT PULSE

O

The HOUT pulse (pin 20) is an open-drain NMOS output.

The duty factor for this output is typically52⁄

48

(conducting/non-conducting) during normal operation. A

soft start causes the duty factor to increase linearly from 5

to 52% over a minimum period of 2000 lines in 2000 steps.

FF-CENTRE SHIFT

O

The OFCS output (pin 19) is a push-pull CMOS output

which is driven by a pulse-width modulated DAC.

By using a suitable interface, the output signal can be used

for off-centre shift correction in the horizontal output stage.

This correction is required for HDTV tubes with a 16 × 9

aspect ratio and is useful for high performance flat square

tubes to obtain the required horizontal linearity. For

applications where off-centre correction is not required,

the output can be used as an auxiliary DAC. The OFCS

signal is phase-locked with the line frequency. The

off-centre shift can be set via the I2C-bus, subaddress 09,

with a 6-bit resolution as illustrated in Fig.8.

S

ANDCASTLE

The DSC input/output (pin 2) acts as a sandcastle

generating output and a guard sensing input. As an output

it provides 2 levels (apart from the base level), one for the

horizontal and vertical blanking and the other for the video

clamping. As an input it acts as a current sensor during the

vertical blanking interval for guard detection.

LAMPING PULSE

C

The clamping pulse width is 21 internal clock periods. The

shift, with respect to HA can be varied from 35 to 49 clock

periods in 7 steps via the I2C-bus, clamp shift byte

subaddress 0A, as illustrated in Fig.9. It is possible to

suppress the clamping pulse during wait, stop and

protection modes with control bit CSU. This will avoid

unwanted reset of the TDA4680/81 (only used in those

circuits).

H

ORIZONTAL BLANKING

The start of the horizontal blanking pulse is minimum 38

and maximum 41 clock periods before the centre of the

flyback pulse, depending on the f

clk/fH

ratio K in

accordance with 41 − (432 − K).

Stop of the horizontal blanking pulse is determined by the

trailing edge of the HFB pulse at the horizontal blanking

slicing level crossing as illustrated in Fig.10.

ERTICAL BLANKING

V

The vertical blanking pulse starts two internal clock pulses

after the rising edge of the VA pulse. During this interval a

small guard pulse, generated during flyback by the vertical

power output stage, must be inserted. Stop vertical

blanking is effected at the end of the blanking interval only

when the guard pulse is present (see Section “Vertical

guard”).

The start scan setting determines the end of vertical

blanking with a 6-bit resolution in steps of one line via the

I2C-bus subaddress 02 (see Figs 11 and 12).

ERTICAL GUARD

V

In the vertical blanking interval a small unblanking pulse is

inserted. This pulse must be filled-in by a blanking pulse or

guard pulse from the vertical power output stage which

was generated during the flyback period. In this condition

the sandcastle output acts as guard detection input and

requires a minimum 800 µA input current. This current is

sensed during the unblanking period. Vertical blanking is

only stopped at the end of the blanking interval when the

inserted pulse is present. In this way the picture tube is

protected against damage in the event of missing or

malfunctioning vertical deflection (see Figs 11 and 12).

July 1994 10

Page 11

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

Vertical part (pins 6, 8, 10, 11 and 12)

S

YNCHRONIZATION PULSE

The VA input (pin 12) is a TTL-compatible CMOS input.

Pulses at this input have to fulfil the timing requirements as

illustrated in Fig.6. For correct detection the minimum

pulse width for both the HIGH and LOW period is 2 internal

clock periods. For further requirements on minimum pulse

width see also Section “De-interlace”.

ERTICAL PLACE GENERATOR

V

With control bit CPR a compress to 75% of the adjusted

values is possible in all modes of operation. This control bit

is used to display 16 : 9 standard pictures on 4 : 3

displays. No new adjustment of other corrections, such as

corner and S-correction, is required.

With control bit VPR a reduction of the current during

clipping, wait and stop modes to 20% of the nominal value

can be selected, which will reduce the dissipation in the

vertical drive circuits.

The vertical start-scan data (subaddress 02) determines

the vertical placement in the total range of 64 × 432 clock

periods in 63 steps. The maximum number of

synchronized lines per scan is 910 with an equivalent field

frequency of 17.2 or 34.4 Hz for fH = 15625 or 31250 Hz

respectively.

The minimum number of synchronized lines per scan is

200 with an equivalent field frequency of 78 or 156 Hz for

fH= 15 625 or 31250 Hz respectively.

D

E-INTERLACE

With de-interlace on (DINT = logic 0), the VA pulse is

sampled with LLC at a position supplied by control bit DIP

(de-interlace phase).

When DIP = logic 0 sampling takes place 42 clock pulses

after the leading edge of HA (T = T

× 42/432).

line

When DIP = logic 1 sampling takes place 258 clock pulses

after the leading edge of HA (T = T

× 258/432).

line

The distance between the two selectable sampling points

is (T

× (258 − 42)/432) which is exactly half a line, thus

line

de-interlace is possible in two directions.

The duration of the V

pulse must, therefore, be sufficient

A

to enable the HA pulse to caught, in this event an active

time of minimum of half a line (see Fig.13 which has an

integration time of T

×1⁄4 for the VA pulse).

line

With de-interlace off, the VA pulse is sampled with the

system clock. The leading edge is detected and used as

the vertical reset. Selection of the positive or negative

leading edge is achieved by the control bit VAP.

ERTICAL GEOMETRY PROCESSING

V

The vertical geometry processing is DC-coupled and

therefore independent of field frequency. The external

resistive conversion (R

) at pin 8 sets the reference

CONV

current for both the vertical and EW geometry processing.

A useful range is 100 to 150 µA, the recommended value

is 120 µA.

If the VA pulse is not present, the number of lines per scan

will increase to 910.2. If the LLC is not present the vertical

blanking will start within 2 µs.

Amplitude control is automatic, with a settling time of 1 to

2 new fields and an accuracy of either 16/12 or 48/12 lines

depending on the value of the GBS bit.

Differences in the number of lines per field, as can occur in

TXT or in multi-head VTR, will not affect the amplitude

setting providing the differences are less than the value

selected with GBS. This is called amplitude control

guardband. The difference sequence and the difference

sequence length are not important.

July 1994 11

VERTICAL OUTPUTS

The vertical outputs VOUTA and VOUTB on pins 10 and 11

together form a differential current output. The vertical

amplitude can be varied over the range 80 to 120% in

63 steps via the I2C-bus (subaddress 00). Vertical

S-correction is also applied to these outputs and can be

set from 0 to 16% by subaddress 01 with a 6-bit resolution.

The vertical off-centre shift (OFCS) shifts the vertical

deflection current zero crossing with respect to the EW

parabola bottom. The control range is −1.5 to +1.5%

(±1⁄8× I8) in 7 steps set by the least significant nibble at

subaddress 03.

Page 12

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

EW GEOMETRY PROCESSING

The EW geometry processing is DC coupled and therefore

independent of field frequency. R

sets the reference

CONV

current for both the vertical and EW geometry processing.

The EW output is an ESD-protected single-ended current

output.

The EW width/width ratio can be set from 100 to 80% in

63 steps via subaddress 04 and the EW parabola/width

ratio from 0 to 20% via subaddress 05. The EW

corner/EW parabola ratio has a control range of−40 to 0%

in 63 steps via subaddress 06.

The EW trapezium correction can be set from

−1.5 to +1.5% in 7 steps via the most significant nibble at

subaddress 03.

BULT GENERATOR

The Bult generator makes the EW waveform continuous

(see Fig.20).

Protection input (pin 3)

The protection input (PROT) is a CMOS input.

The input voltage must be EHT scaled and has the

following characteristics:

Two modes of protection are available with the aid of

control bit PRD.

• With PRD = logic 1 the protection mode is selected,

HOUT will be defeated and the PROT bit in the status

word is set if the input voltage is above 3.9 V. Thus the

deflection stops and EW output current is zero, while the

vertical output current is reduced to 20% of the adjusted

value. A new start of the circuit is I

2

C-bus controlled with

the user software.

• With PRD = logic 0 the detection mode is selected,

HOUT will not be defeated and the over voltage

information is only written in the PROT status bit and can

be read by the I2C-bus.

Flash detection/protection input (pin 9)

The FLASH input is a CMOS input with an internal pull-up

current of approximately 8 µA.

When a negative-going edge crosses the 0.75 V level a

restart will be executed with a soft start of approximately

2000 lines, such as in the soft-start mode. When the

function is not used pin 9 can be connected to ground, V

CC

or left open-circuit, the internal pull-up current source will

prevent any problems. However a hard wired connection

to VCC or ground is recommended when the function is not

used.

EHT compensation (pin 7)

The EHT input is a CMOS input.

The EHT compensation input permits scan amplitude

modulation should the EHT supply not be perfect. For

correct tracking of the vertical and horizontal deflection the

gain of the EW output stage, provided by the ratio

R

CONV-EW/RCONV

, must be1⁄16V

scan

× V

(see Fig.14).

ref

The input for EHT compensation can be derived from an

EHT bleeder or from the picture tubes aquadag

(subaddress 0B, bit BLDS).

EHT compensation can be set via subaddress 07 in

63 steps allowing a scan modulation range from

−10 to +9.7%.

All further actions, such as a write of the LFSS bit, are

achieved by the I2C-bus. They depend on the

configuration used and are defined by user software.

July 1994 12

Page 13

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

INTERNAL CIRCUITRY

MBD863

300 Ω

300 Ω

12 11

300 Ω

13

300 Ω

300 Ω

141516

9 10

7 8

handbook, full pagewidth

TDA9150B

300 Ω

5 6

300 Ω

17

Fig.4 Internal circuitry.

181920

300 Ω

July 1994 13

300 Ω

3 4

300 Ω

1 2

Page 14

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

APPLICATION INFORMATION

vertical

deflection coil

33 V

10

EW-OUT

C110

11

100 nF

12

MBD864

13

IE5

123

IE5

R113 R117

1

2

3

4

5

6

R113

TDA8350

7

LV

330 Ω

8

9

3 kΩ

R105

flash detection input

9

10

12

11

45 V (vert)

3.3 kΩ

R75

100 Ω

3

18

C105

R99

R76

100 µF

R107

82 kΩ

diode

Zener

handbook, full pagewidth

Fig.5 Application diagram.

DSC

R84

2

19

15 kΩ

R85

3.3 kΩ

HFB

1

20

R77

1 kΩ

23 V (peak)

OFCS

HOUT

nF

100

C105

100 µF

16 V (vert)

CC

6

TDA9150B

15

C95 C89

V

( 8 V)

C97

5

16

22 µF 100 nF

100 nF

4

17

100 Ω

EHT

R87

39 kΩ

8

13

R88

4.7 kΩ

7

14

A

A

V

H

LLC

V

CC

( 8 V)

SDA

July 1994 14

SCL

V

CC

( 8 V)

Page 15

Philips Semiconductors Preliminary specification

NNNNNNN

NNNNNNN

Programmable deflection controller TDA9150B

TIMING DIAGRAMS

Fig.6 Timing requirements for LLC, HA and VA.

Fig.7 Horizontal phase and HOUT control range.

July 1994 15

Page 16

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

Fig.8 OFCS duty factor.

Fig.9 DSC clamping pulse.

July 1994 16

Page 17

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

Fig.10 DSC line blanking.

Fig.11 DCS vertical blanking with unblanking.

July 1994 17

Page 18

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

Vertical blanking LOW period: during scan, during unblanking.

Vertical blanking HIGH period (2.5 V): during STSC.

Vertical blanking continuously HIGH: POR = logic 1, LFSS = logic 0, no guard detected.

Fig.12 DSC with guard interval; start scan = 24.

July 1994 18

Page 19

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

I = start VA for DINT = logic 1.

D = start VA for DINT = logic 0.

Fig.13 De-interlace timing.

Fig.14 Explanation of R

July 1994 19

CONV-EW/RCONV

ratio.

Page 20

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

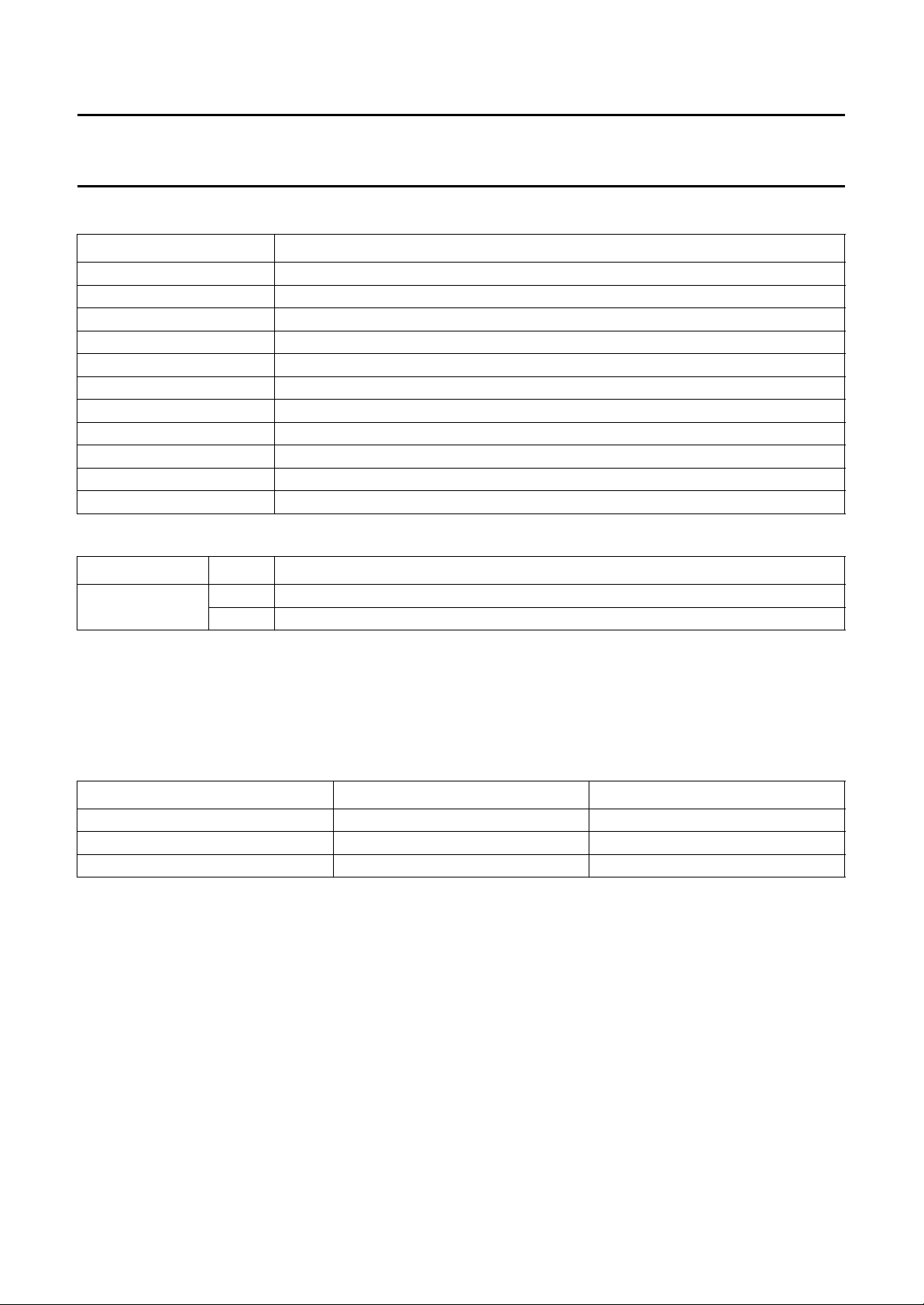

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC134).

SYMBOL PARAMETER MIN. MAX. UNIT

V

CC

I

CC

P

tot

T

stg

T

amb

V

supply

I

I/O

V

ESD

Note

1. Equivalent to discharging a 100 pF capacitor via a 1.5 kΩ series resistor.

supply voltage −0.5 8.8 V

supply current −10 +50 mA

total power dissipation − 500 mW

storage temperature −65 +150 °C

operating ambient temperature −25 +70 °C

voltage supplied to pins 1 to 3, 5 to 14 and 17 to 20 −0.5 VCC+ 0.5 V

current in or out of any pin except pins 4, 15 and 16 −20 +20 mA

electrostatic handling for all pins (note 1) −±2000 V

THERMAL CHARACTERISTICS

SYMBOL PARAMETER VALUE UNIT

R

th j-a

thermal resistance from junction to ambient in free air 70 K/W

July 1994 20

Page 21

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

CHARACTERISTICS

V

= 8V;T

CC

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supply

V

CC

I

CC

P

tot

V

por

SDA and SCL (pins 17 and 18)

V

17

V

IL

V

IH

I

IL

I

IH

V

OL

V

18

V

IL

V

IH

I

IL

I

IH

Line-locked clock and line-locked clock select (pins 14 and 5)

V

IL

V

IH

I

14

t

r

t

f

δ

0

δ

1

TIMING (PRESCALER ON;f

f

LLC

K line-locked clock frequency ratio

= 25 °C; DGND = AGND = 0 V; unless otherwise specified.

amb

supply voltage 7.2 8.0 8.8 V

supply current note 1;

f

= 6.75 MHz

clk

− 27 − mA

total power dissipation − 220 − mW

power-on reset POR 1-to-0

− 6.25 7.0 V

transition

POR 0-to-1

5.0 5.75 − V

transition

SDA input voltage 0 − 5.5 V

LOW level input voltage (pin 17) −−1.5 V

HIGH level input voltage (pin 17) 3.5 −− V

LOW level input current (pin 17) V17 = V

HIGH level input current (pin 17) V17 = V

SSD

CC

−−−10 µA

−−10 µA

LOW level output voltage (pin 17) IIL = 3 mA −−0.4 V

SCL input voltage 0 − 5.5 V

LOW level input voltage (pin 18) −−1.5 V

HIGH level input voltage (pin 18) 3.5 −− V

LOW level input current (pin 18) V18 = V

HIGH level input current (pin 18) V18 = V

SSD

CC

−−−10 µA

−−10 µA

LOW level input voltage (pin 14) −−0.8 V

HIGH level input voltage (pin 14) 2.0 −− V

input current V14 = <5.5 V −10 − +10 µA

rise time 0 −

fall time 0 −

duty factor LLCS = logic 0;

40 50 60 %

1

⁄2t

LLC

1

⁄2t

LLC

at 1.4 V; note 2

duty factor LLCS = logic 1;

25 50 75 %

at 1.4 V; note 2

clk

=1⁄2f

WHERE f

LLC

= INTERNAL CLOCK)

clk

line-locked clock frequency 12.4 − 29.2 MHz

H locked 856 864 865

between f

line-locked clock frequency ratio

between f

LLC

clk

and f

and f

H

H unlocked − 866 −

H locked 428 432 432.5

H

H unlocked − 433 −

July 1994 21

Page 22

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

TIMING (PRESCALER OFF;f

f

LLC

line-locked clock frequency 6.2 − 15.5 MHz

K line-locked clock frequency ratio

between f

line-locked clock frequency ratio

between f

V

5

V

IL

V

IH

I

IL

I

IH

LLCS input voltage 0 − 8.8 V

LOW level input voltage (pin 5) −−1.5 V

HIGH level input voltage (pin 5) 3.5 −− V

LOW level input current (pin 5) V5 = V

HIGH level input current (pin 5) V5 = V

LLC

clk

clk

and f

and f

=f

LLC

H

H

WHERE f

= INTERNAL CLOCK)

clk

H locked 428 432 432

H unlocked − 433 −

H locked 428 432 432

H unlocked − 433 −

SSD

CC

−−−150 µA

−−100 µA

Horizontal part

I

NPUT SIGNALS

HA (pin 13)

V

IL

V

IH

I

13

t

r

t

f

t

WH

t

WL

LOW level input voltage −−0.8 V

HIGH level input voltage 2.0 −− V

input current V13 = 5.5 V −10 − +10 µA

rise time 0 −

fall time 0 −

pulse width HIGH 2 × t

pulse width LOW 2 × t

clk

clk

−−

−−

1

⁄2t

LLC

1

⁄2t

LLC

HFB (pin 1)

V

PSL

phase slicing level FBL = logic 0 3.7 3.9 4.1 V

FBL = logic 1 1.1 1.3 1.5 V

V

I

1

blank

blanking slicing level 0 0.1 0.2 V

input current −10 − +10 µA

Horizontal phase (delay centre flyback pulse to leading edge of HA; where N = horizontal phase data)

CR control range 0 N × t

clk

N + (432 − K)

× t

clk

number of steps − 63 −

OUTPUT SIGNALS

ns

ns

HOUT (pin 20)

V

20

V

OL

I

20

output voltage I20 = 0 0 − V

CC

LOW level output voltage I20 = 10 mA −−0.5 V

input current output off −10 − +10 µA

δ duty factor normal operation 51 52 53 %

July 1994 22

V

Page 23

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Soft start (duty factor controlled line drive)

t

W

CR control range 5 − 53 %

t

ss

Switch-off time to the centre of the flyback pulse

CR control range note 3 0 − 160 −

Φ control sensitivity (loop gain) 400 1000 −µs/µs

k correction factor note 4 − 0.5 −

σ sigma value of phase jitter note 5 − 750 − ps

PSRR power supply rejection ratio −−10 ns/V

Horizontal off-centre shift (pin 19; N = off-centre shift data)

V

19

V

OL

V

OH

δ

(max)

δ duty factor N ≥54 − 1 − %

ANDCASTLE (PIN 2)

S

initial pulse width soft start −−5%

soft start time 1500 − 3000 lines

(432 − K)

× t

clk

output voltage 0 − V

CC

V

LOW level output voltage I19 = 2 mA −−0.5 V

HIGH level output voltage I19 = −2mA VCC−0.5 −− V

maximum duty factor N <54 1/K (8N + 1)/K 425/K %

number of steps − 54 −

DSC output voltage

V

V

clamp

blank

video clamping voltage 4.0 4.5 5.0 V

horizontal and vertical blanking

voltage level

V

I

t

t

base

2

r

f

base voltage level 0 0.5 1.0 V

output current guard not detected −1.0 − +0.35 mA

rise time − 60 − ns

fall time − 60 − ns

Clamping pulse (N = clamp pulse shift data)

t

W

t

clamp

clamping pulse width − 21 × t

clamp pulse shift w.r.t H

A

number of steps − 7 −

t

start

start of horizontal blanking before

middle of flyback pulse

2.0 2.5 3.0 V

guard detected 0.8 − 2.5 mA

−

clk

35 (2N + 35)

× t

clk

38 41 −

49

41

(432 − K)

× t

clk

July 1994 23

Page 24

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Vertical blanking width (N = vertical start-scan data)

CR control range 1 × 432t

K = 432 1 − 64 lines

number of steps − 63 −

Guard detection (N = vertical start-scan data)

t

start

t

stop

start interval w.r.t V

stop interval w.r.t V

A

A

no wait {48(N+1) +2}

× t

clk

no wait {96(N+1) +2}

× t

clk

Vertical section

(N + 1)

clk

× 432t

clk

−−

−−

64 × 432t

clk

INPUT SIGNALS (PIN 12; V

V

IL

V

IH

I

12

t

r

t

f

t

WH

t

WL

t

WH

t

WL

LOW level input voltage −−0.8 V

HIGH level input voltage 2.0 −− V

input current V12<5.5 V −10 − +10 µA

rise time 0 −

fall time 0 −

pulse width HIGH 2 × t

pulse width LOW 2 × t

pulse width HIGH de-interlace mode 0.5 × t

pulse width LOW de-interlace mode 0.5 × t

)

A

clk

clk

line

line

−−

−−

−−

−−

Vertical place generator (N = vertical start-scan data)

CR control range 1 × 432t

clk

(N + 1)

× 432t

clk

K = 432 1 − 64 lines

number of steps − 63 −

L

max

maximum number of

− 910 − lines/

synchronized lines per scan

f

eq

equivalent field frequency at 910

lines/scan

L

min

minimum number of

fH = 15625 Hz − 17.2 − Hz

= 31250 Hz − 34.4 − Hz

f

H

− 200 − lines/

synchronized lines per scan

f

eq

equivalent field frequency at 200

lines/scan

fH = 15625 Hz − 78 − Hz

= 31250 Hz − 156 − Hz

f

H

CA amplitude control − automatic −

CA

g

amplitude control guardband GBS = logic 0 − 16/12 − lines

GBS = logic 1 − 48/12 − lines

settling time 1 1.5 2 new

1

⁄2t

LLC

1

⁄2t

LLC

64 × 432t

clk

scan

scan

fields

July 1994 24

Page 25

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Vertical geometry processing

∆I

(M)

D/∆T drift over temperature range −−10

1

⁄

(I10+I11) vertical output signal bias current I8 = −120 µA 275 325 375 µA

2

I

os

OS/∆T offset over temperature range −−10

V

10

V

11

CMRR common mode rejection ratio −−1 %/V

LE linearity error adjacent blocks;

Vertical amplitude (N = vertical amplitude data)

CR control range note 9 81 − 119 %

Vertical S-correction (N = S-correction data)

CR control range note 9 0 − 15 %

Vertical shift

CR control range −1⁄8I

vertical differential output current

between VOUTA and VOUT

B

VA = 100%; note 6;

I8= −120 µA

440 475 510 µA

(peak value)

amplitude error due to

−4

−−2%

−1

K

S-correction setting

vertical output offset current note 7 −−1%

−4

−1

K

vertical output voltage (pin 10) 0 − 3.9 V

vertical output voltage (pin 11) 0 − 3.9 V

−−2.0 %

note 8

non-adjacent

−−3.0 %

blocks; note 8

number of steps − 63 −

number of steps − 63 −

8

− +1⁄8I

8

µA

number of steps − 7 −

EW output (pin 6)

V

6

I

6

output voltage note 10 1.0 − 5.5 V

output current I8 = −120 µA;

15 − 930 µA

note 11

RR output ripple rejection − 0.15 1 %/V

D/∆T output drift over temperature

−−5.10

−4

K

range

EW WIDTH/WIDTH RATIO

CR control range note 9 100 − 81 %

I

eq

equivalent output current 15 − 440 µA

number of steps − 63 −

July 1994 25

−1

Page 26

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

EW PARABOLA/WIDTH RATIO

CR control range note 9 1 − 19 %

I

eq

CORNER/EW PARABOLA RATIO

EW

CR control range notes 9 and 12 40 − 0%

I

eq

TRAPEZIUM CORRECTION

EW

equivalent output current width = 100% 10 − 430 µA

width = 80% 10 − 345 µA

number of steps − 63 −

equivalent output current width = 100% 0 − 200 µA

width = 80% 0 − 160 µA

number of steps − 63 −

EW trapezium/width ratio note 9 −1.5 − +1.5 %

number of steps − 7 −

EHT input (pin 7)

V

ref

V

I

V

I

m

scan

m

GC

reference voltage BLDS = logic 1 − 3.9 − V

− V

ref

input voltage w.r.t V

input voltage w.r.t V

ref

CC

BLDS = logic 0 − V

CC

BLDS = logic 1 −20 0 +20 %

BLDS = logic 0 0 −−2V

scan modulation −10 0 +9.7 %

modulation gain control 0 − 1

number of steps − 63 −

I

I

R

V

I

8

CONV

O

input current −100 − +100 nA

input (pin 8)

output voltage I8 = −120 µA 3.7 3.9 4.1 V

current range −100 −120 −150 µA

PROT input (pin 3)

V

I

V

3

I

I

input voltage 0 − V

CC

voltage detection level 3.7 3.9 4.1 V

input current −10 − +10 µA

FLASH detection input (pin 9)

V

I

V

9

input voltage 0 − V

CC

voltage detection level falling edge 0.5 0.75 1.0 V

H detection level hysteresis 0.3 0.5 0.8 V

I

9

detection pull-up current −4 −8 −16 µA

V

V

V

July 1994 26

Page 27

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

Notes to the characteristics

1. For all other frequencies the expected supply current will be as shown in Table 6 (f

f

is the internal clock frequency applied to pin 14).

LLC

2. When the prescaler is on, one in two LLC HIGH periods is omitted.

3. For 16 kHz operation the minimum value of the control range is 5.7 µs. With1⁄2tFB = 5.7 µs the minimum storage time

is 0 and the maximum is 18 µs.

For 32 kHz operation the minimum value of the control range is 0 µs. With1⁄2tFB = 2.85 µs the minimum storage time

is 0 and the maximum is 9 µs.

4. The k factor is defined as the amount of correction of a phase step. Thus with k = 0.5 a 50% correction of the error

takes place each line. The resulting step response now becomes kn, with n the line number after the step.

5. The sigma value (σ) of the jitter with respect to LLC at fH = 32 kHz and a storage time of 5 µs.

Measurement ofσ is carried out during 200 lines in the active scan, the resulting peak-to-peak value is approximately

6σ. The visible jitter on the screen will be higher than the peak-to-peak jitter, depending on the deflection stage.

6. DAC values: vertical amplitude = 31; EHT = 0; SHIFT = 3; SCOR = 0.

7. Value is a percentage of I10− I11.

8. The linearity error is measured without S-correction and based on the same measurement principle as used for the

screen. Measuring method: divide the output signal I10− I11 into 22 equal parts, ranging from 1 to 22 inclusive.

Measure the value of two succeeding parts called one block starting with part 2 and 3 (block 1) and ending with part

20 and 21 (block 10). Thus part 1 and 22 are unused.

is the internal clock frequency,

clk

aka

–

k1+()

Linearity error for adjacent blocks =

Linearity error for non-adjacent blocks =

Where a = amplitude, a

= amplitude block k and a

k

----------------------------- a

avg

a

maxamin

----------------------------- a

–

avg

= average amplitude.

avg

9. Minimum available range.

10. Selection of test mode.

When the EW output is pulled above V

− 0.5 V a special test mode is entered in which the prescaler and the clock

CC

detector are disabled.

11. DAC values: vertical amplitude = 31; EHT = 0; WIDTH = 0.

12. The value of −40% (typically 46%) corresponds with data 3F (hexadecimal) and implies maximum 4th order

compensation.

Table 6 Supply current with prescaler on/off.

LLC (MHz) ON (mA) OFF (mA)

6.75 note 1 27

13.5 27 38

27 42 note 1

Note

1. Combination not allowed.

July 1994 27

Page 28

Philips Semiconductors Preliminary specification

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

Programmable deflection controller TDA9150B

TEST AND APPLICATION INFORMATION

I11− I10.

Fig.15 Control range amplitude.

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

Fig.16 Control range S-correction.

July 1994 28

Page 29

Philips Semiconductors Preliminary specification

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

BBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBBB

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

BBBBBBBBBBBBBBBBBBBBBBBBBBB

Programmable deflection controller TDA9150B

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

Fig.17 Control range EW parabola/width ratio.

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

Fig.18 Control range EW corner/EW parabola ratio.

July 1994 29

Page 30

Philips Semiconductors Preliminary specification

BBBBBBBBBBBBBBBBBBBBBBBBBBB

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

BBBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBB

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

BBBBBBBBBBBBBBBBBBBBBBBBB

Programmable deflection controller TDA9150B

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBBBB

Fig.19 Control range EW width.

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

July 1994 30

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

BBBBBBBBBBBBBBBBBBBBBBBB

Fig.20 The BULT makes the EW waveform continuous.

Page 31

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

PACKAGE OUTLINE

seating plane

3.60

3.05

2.0

max

26.92

26.54

3.2

4.2

max

max

0.51

min

2.54

(9x)

20

1

0.53

max

1.73 max

0.254

M

11

6.40

6.22

10

0.38 max

8.25

7.80

7.62

10.0

8.3

MSA258

Dimensions in mm.

Fig.21 Plastic dual in-line package; 20 leads (300 mil); DIP20, SOT146-1.

SOLDERING

Plastic dual in-line packages

B

Y DIP OR WAVE

The maximum permissible temperature of the solder is

260 °C; this temperature must not be in contact with the

joint for more than 5 s. The total contact time of successive

solder waves must not exceed 5 s.

The device may be mounted up to the seating plane, but

the temperature of the plastic body must not exceed the

specified storage maximum. If the printed-circuit board has

been pre-heated, forced cooling may be necessary

immediately after soldering to keep the temperature within

the permissible limit.

July 1994 31

R

EPAIRING SOLDERED JOINTS

Apply a low voltage soldering iron below the seating plane

(or not more than 2 mm above it). If its temperature is

below 300 °C, it must not be in contact for more than 10 s;

if between 300 and 400 °C, for not more than 5 s.

Page 32

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or

more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation

of the device at these or at any other conditions above those given in the Characteristics sections of the specification

is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these

products can reasonably be expected to result in personal injury. Philips customers using or selling these products for

use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such

improper use or sale.

PURCHASE OF PHILIPS I2C COMPONENTS

Purchase of Philips I

components in the I2C system provided the system conforms to the I2C specification defined by

Philips. This specification can be ordered using the code 9398 393 40011.

2

C components conveys a license under the Philips’ I2C patent to use the

July 1994 32

Page 33

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

NOTES

July 1994 33

Page 34

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

NOTES

July 1994 34

Page 35

Philips Semiconductors Preliminary specification

Programmable deflection controller TDA9150B

NOTES

July 1994 35

Page 36

Philips Semiconductors – a worldwide company

Argentina: IEROD, Av. Juramento 1992 - 14.b, (1428)

BUENOS AIRES, Tel. (541)786 7633, Fax. (541)786 9367

Australia: 34 Waterloo Road, NORTH RYDE, NSW 2113,

Tel. (02)805 4455, Fax. (02)805 4466

Austria: Triester Str. 64, A-1101 WIEN, P.O. Box 213,

Tel. (01)60 101-1236, Fax. (01)60 101-1211

Belgium: Postbus 90050, 5600 PB EINDHOVEN, The Netherlands,

Tel. (31)40 783 749, Fax. (31)40 788 399

Brazil: Rua do Rocio 220 - 5

CEP: 04552-903-SÃO PAULO-SP, Brazil.

P.O. Box 7383 (01064-970).

Tel. (011)821-2333, Fax. (011)829-1849

Canada: PHILIPS SEMICONDUCTORS/COMPONENTS:

Tel. (800) 234-7381, Fax. (708) 296-8556

Chile: Av. Santa Maria 0760, SANTIAGO,

Tel. (02)773 816, Fax. (02)777 6730

Colombia: IPRELENSO LTDA, Carrera 21 No. 56-17,

77621 BOGOTA, Tel. (571)249 7624/(571)217 4609,

Fax. (571)217 4549

Denmark: Prags Boulevard 80, PB 1919, DK-2300 COPENHAGEN S,

Tel. (032)88 2636, Fax. (031)57 1949

Finland: Sinikalliontie 3, FIN-02630 ESPOO,

Tel. (9)0-50261, Fax. (9)0-520971

France: 4 Rue du Port-aux-Vins, BP317,

92156 SURESNES Cedex,

Tel. (01)4099 6161, Fax. (01)4099 6427

Germany: PHILIPS COMPONENTS UB der Philips G.m.b.H.,

P.O. Box 10 63 23, 20043 HAMBURG,

Tel. (040)3296-0, Fax. (040)3296 213.

Greece: No. 15, 25th March Street, GR 17778 TAVROS,

Tel. (01)4894 339/4894 911, Fax. (01)4814 240

Hong Kong: PHILIPS HONG KONG Ltd., Components Div.,

6/F Philips Ind. Bldg., 24-28 Kung Yip St., KWAI CHUNG, N.T.,

Tel. (852)424 5121, Fax. (852)428 6729

India: Philips INDIA Ltd, Components Dept,

Shivsagar Estate, A Block ,

Dr. Annie Besant Rd. Worli, Bombay 400 018

Tel. (022)4938 541, Fax. (022)4938 722

Indonesia: Philips House, Jalan H.R. Rasuna Said Kav. 3-4,

P.O. Box 4252, JAKARTA 12950,

Tel. (021)5201 122, Fax. (021)5205 189

Ireland: Newstead, Clonskeagh, DUBLIN 14,

Tel. (01)640 000, Fax. (01)640 200

Italy: PHILIPS COMPONENTS S.r.l.,

Viale F. Testi, 327, 20162 MILANO,

Tel. (02)6752.3302, Fax. (02)6752 3300.

Japan: Philips Bldg13-37, Kohnan 2-chome, Minato-ku, TOKYO 108,

Tel. (03)3740 5028, Fax. (03)3740 0580

Korea: (Republic of) Philips House, 260-199 Itaewon-dong,

Yongsan-ku, SEOUL, Tel. (02)794-5011, Fax. (02)798-8022

Malaysia: No. 76 Jalan Universiti, 46200 PETALING JAYA,

SELANGOR, Tel. (03)750 5214, Fax. (03)757 4880

Mexico: Philips Components, 5900 Gateway East, Suite 200,

EL PASO, TX 79905, Tel. 9-5(800)234-7381, Fax. (708)296-8556

Netherlands: Postbus 90050, 5600 PB EINDHOVEN, Bldg. VB

Tel. (040)783749, Fax. (040)788399

New Zealand: 2 Wagener Place, C.P.O. Box 1041, AUCKLAND,

Tel. (09)849-4160, Fax. (09)849-7811

Norway: Box 1, Manglerud 0612, OSLO,

Tel. (022)74 8000, Fax. (022)74 8341

th

floor, Suite 51,

Pakistan: Philips Electrical Industries of Pakistan Ltd.,

Exchange Bldg. ST-2/A, Block 9, KDA Scheme 5, Clifton,

KARACHI 75600, Tel. (021)587 4641-49,

Fax. (021)577035/5874546.

Philippines: PHILIPS SEMICONDUCTORS PHILIPPINES Inc,

106 Valero St. Salcedo Village, P.O. Box 2108 MCC, MAKATI,

Metro MANILA, Tel. (02)810 0161, Fax. (02)817 3474

Portugal: PHILIPS PORTUGUESA, S.A.,

Rua dr. António Loureiro Borges 5, Arquiparque - Miraflores,

Apartado 300, 2795 LINDA-A-VELHA,

Tel. (01)14163160/4163333, Fax. (01)14163174/4163366.

Singapore: Lorong 1, Toa Payoh, SINGAPORE 1231,

Tel. (65)350 2000, Fax. (65)251 6500

South Africa: S.A. PHILIPS Pty Ltd., Components Division,

195-215 Main Road Martindale, 2092 JOHANNESBURG,

P.O. Box 7430 Johannesburg 2000,

Tel. (011)470-5911, Fax. (011)470-5494.

Spain: Balmes 22, 08007 BARCELONA,

Tel. (03)301 6312, Fax. (03)301 42 43

Sweden: Kottbygatan 7, Akalla. S-164 85 STOCKHOLM,

Tel. (0)8-632 2000, Fax. (0)8-632 2745

Switzerland: Allmendstrasse 140, CH-8027 ZÜRICH,

Tel. (01)488 2211, Fax. (01)481 77 30

Taiwan: PHILIPS TAIWAN Ltd., 23-30F, 66, Chung Hsiao West

Road, Sec. 1. Taipeh, Taiwan ROC, P.O. Box 22978,

TAIPEI 100, Tel. (02)388 7666, Fax. (02)382 4382.

Thailand: PHILIPS ELECTRONICS (THAILAND) Ltd.,

209/2 Sanpavuth-Bangna Road Prakanong,

Bangkok 10260, THAILAND,

Tel. (662)398-0141, Fax. (662)398-3319.

Turkey:Talatpasa Cad. No. 5, 80640 GÜLTEPE/ISTANBUL,

Tel. (0212)279 2770, Fax. (0212)269 3094

United Kingdom: Philips Semiconductors LTD.,

276 Bath road, Hayes, MIDDLESEX UB3 5BX,

Tel. (081)73050000, Fax. (081)7548421

United States:811 East Arques Avenue, SUNNYVALE,

CA 94088-3409, Tel. (800)234-7381, Fax. (708)296-8556

Uruguay: Coronel Mora 433, MONTEVIDEO,

Tel. (02)70-4044, Fax. (02)92 0601

For all other countries apply to: Philips Semiconductors,

International Marketing and Sales, Building BE-p,

P.O. Box 218, 5600 MD, EINDHOVEN, The Netherlands,

Telex 35000 phtcnl, Fax. +31-40-724825

SCD33 © Philips Electronics N.V. 1994

All rights are reserved. Reproduction in whole or in part is prohibited without the

prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation

or contract, is believed to be accurate and reliable and may be changed without

notice. No liability will be accepted by the publisher for any consequence of its

use. Publication thereof does not convey nor imply any license under patent- or

other industrial or intellectual property rights.

Printed in The Netherlands

533061/1500/01/pp36 Date of release: July 1994

Document order number: 9397 737 80011

Philips Semiconductors

Loading...

Loading...