Page 1

TDA9109/N

LOW-COST DEFLECTIONPROCESSOR

FOR MULTISYNC MONITORS

June 1998

SHRINK32

(Plastic Package)

ORDER CODE : TDA9109/N

HORIZONTAL

.

SELF-ADAPTATIVE

.

DUALPLLCONCEPT

.

150kHzMAXIMUM FREQUENCY

.

X-RAYPROTECTIONINPUT

.

I2C CONTROLS : H-POSITION, FREQUENCY

GENERATORFOR BURN-IN MODE

VERTICAL

.

VERTICALRAMP GENERATOR

.

50 TO165Hz AGC LOOP

.

GEOMETRYTRACKINGWITHVPOS& VAMP

.

I2C CONTROLS:

VAMP, VPOS, S-CORR, C-CORR

.

DC BREATHING COMPENSATION

I

2

C GEOMETRYCORRECTIONS

.

VERTICALPARABOLAGENERATOR

(Pincushion,Keystone)

.

HORIZONTALDYNAMICPHASE

(SidePin Balance& Parallelogram)

.

HORIZONTALAND VERTICALDYNAMIC FOCUS (Horizontal Focus Amplitude, Horizontal

FocusSymmetry,VerticalFocus Amplitude)

GENERAL

.

SYNCPROCESSOR

.

12V SUPPLYVOLTAGE

.

8V REFERENCEVOLTAGE

.

HOR.& VERT. LOCK/UNLOCK OUTPUTS

.

READ/WRITEI2C INTERFACE

.

VERTICALMOIRE

.

B+REGULATOR

- INTERNAL PWM GENERATOR FOR B+

CURRENT MODE STEP-UP CONVERTER

- S WITCHABL E TO STEP-DOWN CONVERTER

-I

2

CADJUSTABLEB+REFERENCE VOLTAGE

- OUTPUT PULSES SYNCHRONIZED ON

HORIZONTALFREQUENCY

- INTERNALMAX. CURRENT LIMITATION

.

COMPARED WITH THE TDA9109,

THE TDA9109/NHAS:

-NOI

2

C FREE RUNNING FREQUENCY AD-

JUSTMENT

- FIXED HORIZONTALDUTY CYCLE (48%)

- INCREASEDMAX.STORAGETIME OF THE

HORIZONTALSCANNING TRANSISTOR

DESCRIPTION

The TDA9109/N is a monolithic integrated circuit

assembledin32-pinshrinkdual in lineplasticpackage.ThisIC controlsall thefunctionsrelatedtothe

horizontal and vertical deflection in multimode or

multi-frequencycomputerdisplaymonitors.

The internal sync processor, combined with the

very powerful geometrycorrection block makethe

TDA9109/N suitable for very high performance

monitors,using very few externalcomponents.

Thehorizontaljitter levelisverylow.Itisparticularly

well suited forhigh-end 15” and 17” monitors.

Combined with the ST7275Microcontroller family,

TDA9206 (Video preamplifier) and STV942x (OnScreen Display controller) the TDA9109/N allows

fullyI

2

Cbus controlled computer display monitors

to be built with a reduced number of external

components.

1/32

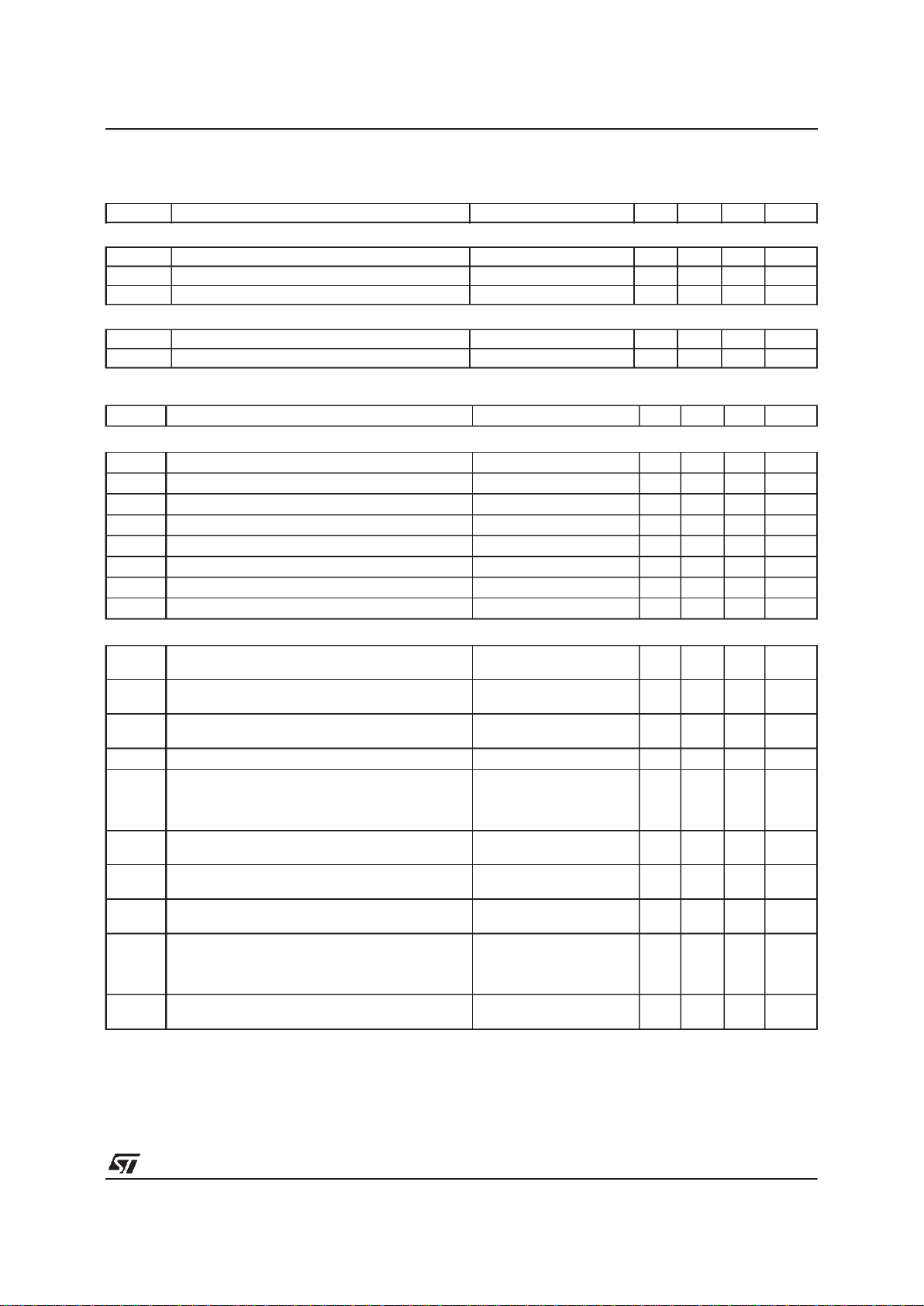

Page 2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

22

23

24

25

26

21

20

19

18

17

5V

SDA

SCL

V

CC

GND

HOUT

XRAY

EWOUT

VOUT

VCAP

V

REF

VAGCCAP

VGND

BREATH

B+GNDI

SENSE

REGIN

COMP

HREF

HFLY

HGND

FOCUS-OUT

HFOCUSCAP

HPOSITION

PLL1F

R0

C0

PLL2C

HLOCKOUT

H/HVIN

VSYNCIN

32

31

30

29

28

27

BOUT

9109N-01.EPS

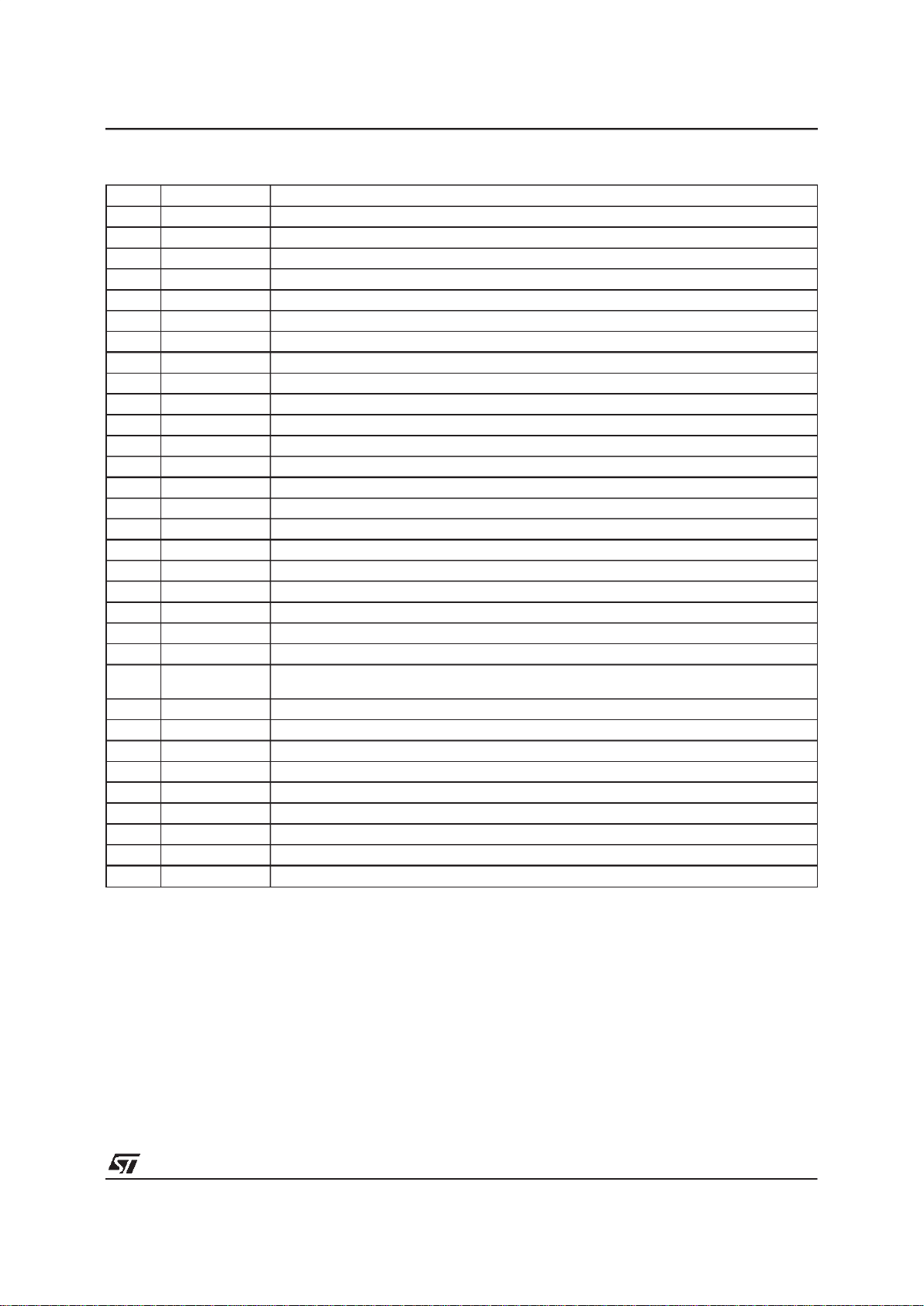

PIN CONNECTIONS

TDA9109/N

2/32

Page 3

PIN CONNECTIONS

Pin Name Function

1 H/HVIN TTL compatible Horizontal sync Input (separate or composite)

2 VSYNCIN TTL compatible Vertical sync Input (for separated H&V)

3 HLOCKOUT First PLL Lock/Unlock Output (0V unlocked - 5V locked)

4 PLL2C Second PLL LoopFilter

5 C0 Horizontal Oscillator Capacitor

6 R0 Horizontal Oscillator Resistor

7 PLL1F First PLL Loop Filter

8 HPOSITION HorizontalPosition Filter (capacitor to be connected to HGND)

9 HFOCUSCAP Horizontal Dynamic Focus Oscillator Capacitor

10 FOCUSOUT Mixed Horizontal and Vertical Dynamic Focus Output

11 HGND Horizontal Section Ground

12 HFLY Horizontal Flyback Input (positivepolarity)

13 HREF Horizontal Section ReferenceVoltage (to be filtered)

14 COMP B+ Error Amplifier Output for frequency compensation and gain setting

15 REGIN Regulation Input of B+ control loop

16 I

SENSE

Sensing ofexternal B+ switching transistor current, or switch for step-down converter

17 B+GND Ground (related toB+ reference adjustment)

18 BREATH DC Breathing Input Control (compensation of vertical amplitude against EHV variation)

19 VGND Vertical Section Ground

20 VAGCCAP Memory Capacitor for Automatic Gain Control Loop in Vertical Ramp Generator

21 V

REF

Vertical Section Reference Voltage (to be filtered)

22 VCAP Vertical Sawtooth Generator Capacitor

23 VOUT Vertical Ramp Output(withfrequencyindependantamplitude and S or C Correctionsif any).

It is mixed with vertical position voltage and vertical moiré.

24 EWOUT Pin Cushion - E/W Correction Parabola Output

26 HOUT Horizontal Drive Output (internal transistor, open collector)

25 XRAY X-RAY protection input (with internal latch function)

27 GND General Ground (referenced to V

CC

)

28 BOUT B+ PWMRegulator Output

29 V

CC

Supply Voltage (12V typ)

30 SCL I

2

C Clock Input

31 SDA I

2

C Data Input

32 5V Supply Voltage (5V typ.)

9109N-01.TBL

TDA9109/N

3/32

Page 4

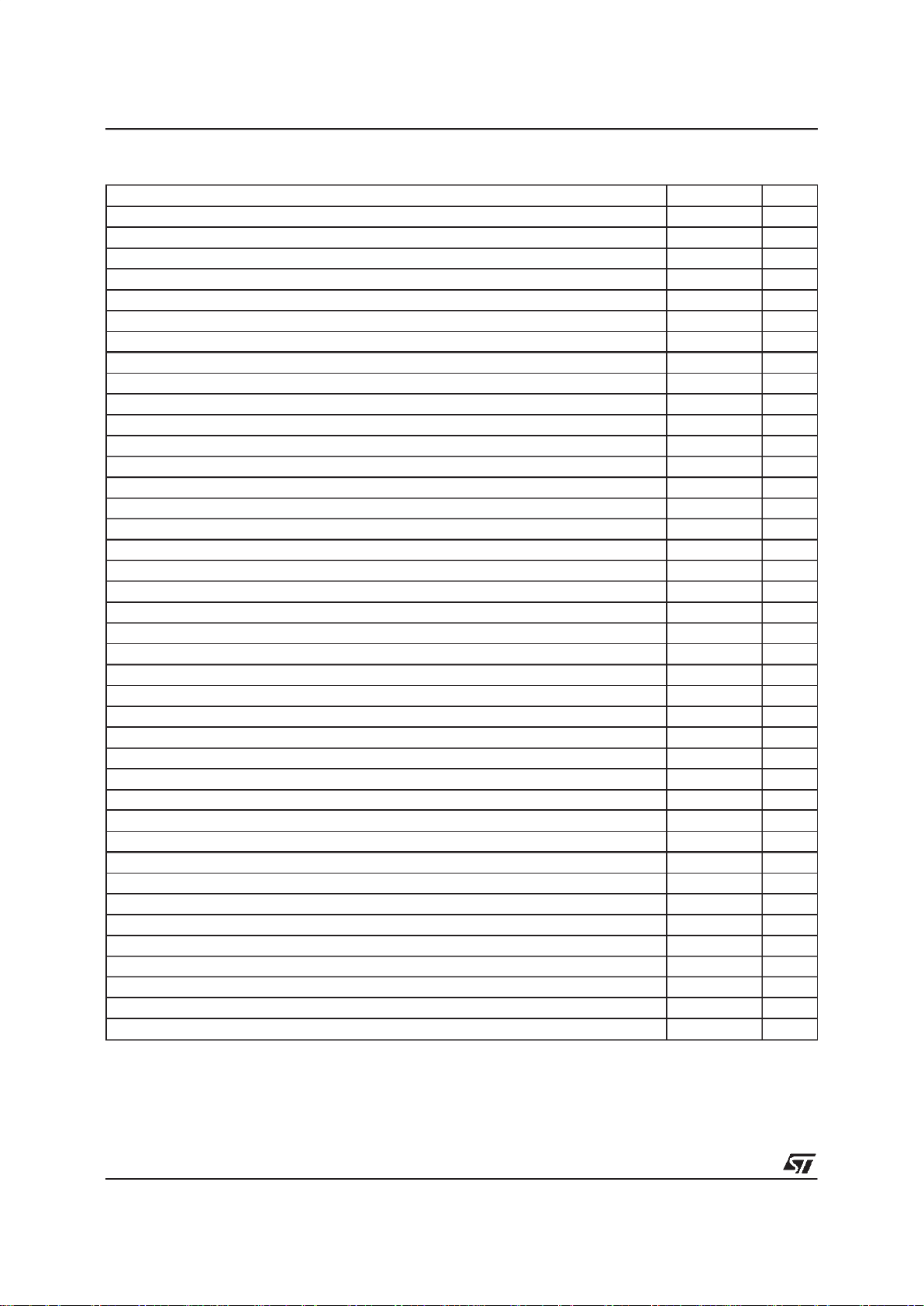

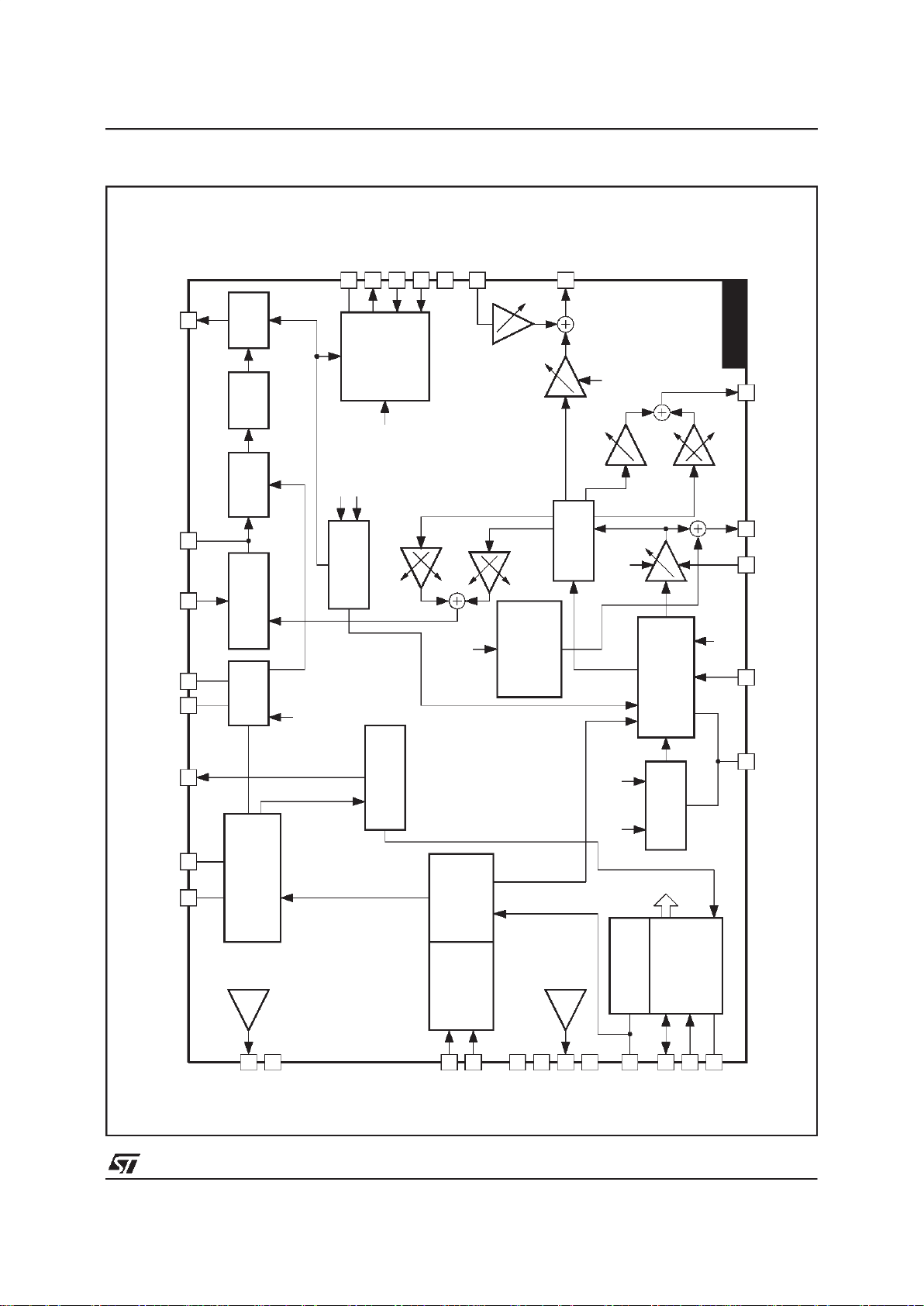

QUICK REFERENCE DATA

Parameter Value Unit

Horizontal Frequency 15 to 150 kHz

Autosynch Frequency (for given R0 and C0) 1 to 4.5 f0

æ Horizontal Sync Polarity Input YES

Polarity Detection (on bothHorizontal and Vertical Sections) YES

TTL Composite Sync YES

Lock/Unlock Identification (on both Horizontal 1st PLL and Vertical Section) YES

I

2

C Control for H-Position

±

10 %

XRAY Protection YES

Fixed I

2

C Horizontal Duty Cycle 48 %

I

2

C Free Running Frequency Adjustment NO

Stand-by Function YES

Dual Polarity H-Drive Outputs NO

Supply Voltage Monitoring YES

PLL1 Inhibition Possibility NO

Blanking Outputs NO

Vertical Frequency 35 to 200 Hz

Vertical Autosync (for 150nF on Pin 22 and 470nF on Pin 20) 50 to 165 Hz

Vertical S-Correction YES

Vertical C-Correction YES

Vertical Amplitude Adjustment YES

DC Breathing Control on VerticalAmplitude YES

Vertical Position Adjustment YES

East/West (E/W) Parabola Output (also known as Pin Cushion Output) YES

E/W Correction Amplitude Adjustment YES

Keystone Adjustment YES

Internal Dynamic Horizontal Phase Control YES

Side Pin Balance Amplitude Adjustment YES

Parallelogram Adjustment YES

Tracking of Geometric Corrections with Vertical Amplitude and Position YES

Reference Voltage (both on Horizontal and Vertical) YES

Dynamic Focus (both Horizontal and Vertical) YES

I

2

C Horizontal Dynamic Focus Amplitude Adjustment YES

I

2

C Horizontal Dynamic Focus Symmetry Adjustment YES

I

2

C Vertical Dynamic Focus Amplitude Adjustment YES

Detection of Input Sync Type (biased from 5V alone) YES

Vertical Moiré Output YES

I

2

C Controlled V-Moiré Amplitude YES

Frequency Generator for Burn-in YES

Fast I

2

C Read/Write 400 kHz

B+ Regulation adjustable by I

2

C YES

9109N-02.TBL

TDA9109/N

4/32

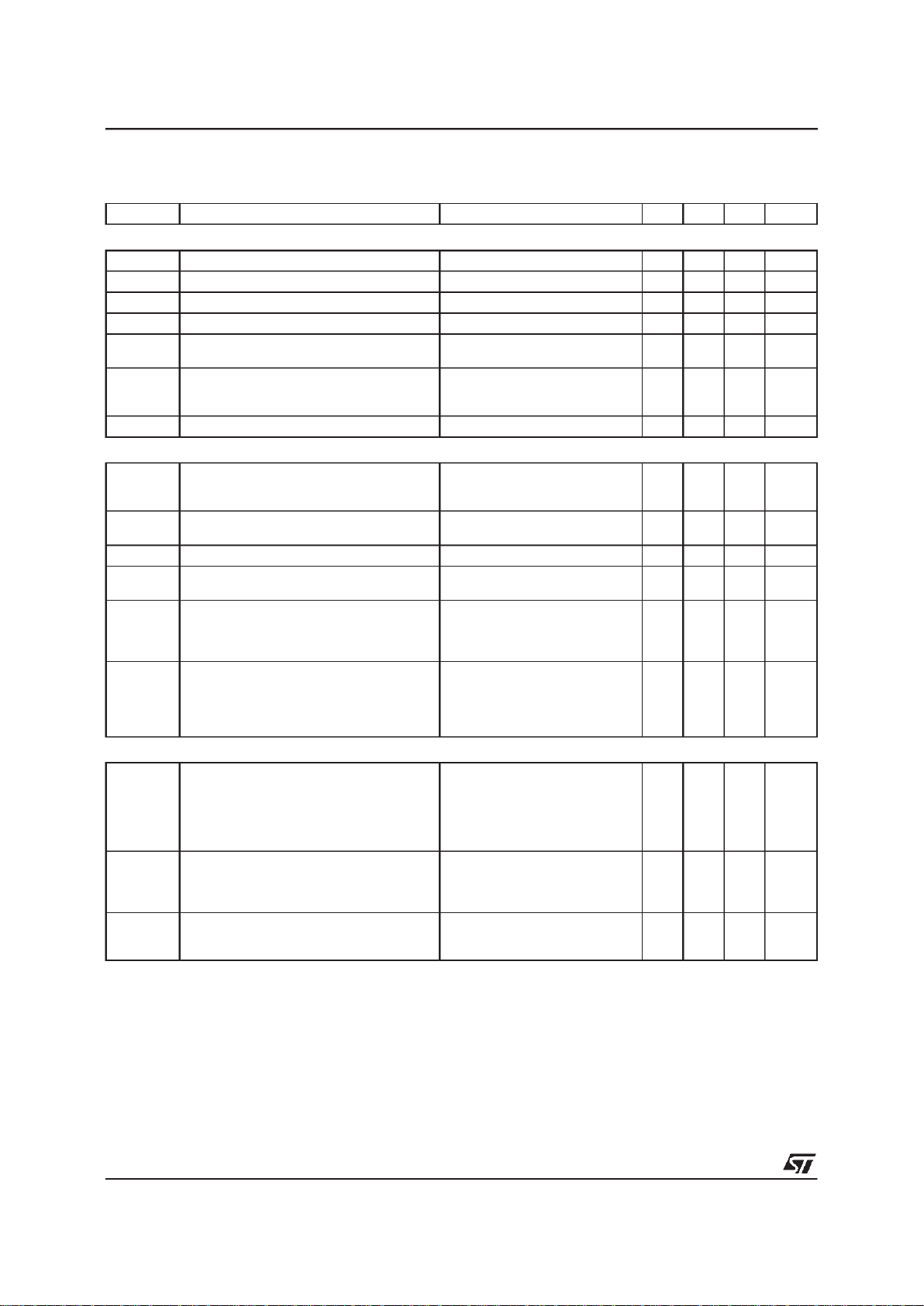

Page 5

V

REF

4

131211

5

9

3

1

67 26

2

Amp & Symmetry

2 x 5 bits

HFOCUSCAP

HREF

HGND

SYNC

PROCESSOR

SYNC INPUT

SELECT

(1 bit)

B+

CONTROLLER

LOCK/UNLOCK

IDENTIFICATION

PHASE

COMPARATOR

PHASE

SHIFTER

H-DUTY

(48%)

HOUT

BUFFER

VCO

Forced

Frequency

2 bits

VAMP

7 bits

21

22 23

30

192432

31

27

V

REF

VGND

5V

SDA

SCL

GND

V

REF

S AND C

CORRECTION

VERTICAL

OSCILLATOR

RAMP GENERATOR

GEOMETRY

TRACKING

6 bits 6 bits

Keyst.

6 bits

E/W

7 bits

TDA9109/N

PLL1F

HLOCKOUT

HPOSITION

R0

C0

HFLY

PLL2C

HOUT

V

CAP

V

AGCCAP

V

OUT

VSYNCIN

H/HVIN

EWOUT

X

2

X

2

X

25

29

XRAY

V

CC

RESET

GENERATOR

I

2

C INTERFACE

VPOS

7 bits

20

VAMPVDF

6 bits

10 FOCUS

Parallelogram

6 bits

Spin Bal

6 bits

X

2

X

2

VSYNC

SAFETY

PROCESSOR

XRAY

V

CC

17

BGND

16

I

SENSE

15 REGIN

28 B+OUT

14 COMP

B+ Adjust

7 bits

18

BREATH

PHASE/FREQUENCY

COMPARATOR

H-PHASE(7 bits)

8

VERTICAL

MOIRE

CANCEL

5 BITS+ON/OFF

9109N-02.EPS

BLOCKDIAGRAM

TDA9109/N

5/32

Page 6

ABSOLUTE MAXIMUMRATINGS

Symbol Parameter Value Unit

V

CC

Supply Voltage (Pin 29) 13.5 V

V

DD

Supply Voltage (Pin 32) 5.7 V

V

IN

Max Voltage on Pin 4

Pin 9

Pin 5

Pins 6, 7, 8, 14, 15, 16, 20, 22

Pin 10, 18, 23, 24, 25, 26,28

Pins 1, 2, 3, 30, 31

4.0

5.5

6.4

8.0

V

CC

V

DD

V

V

V

V

V

V

VESD

ESD susceptibility Human Body Model,100pF Dischargethrough 1.5kΩ

EIAJ Norm,200pF Discharge through 0Ω

2

300

kV

V

T

stg

Storage Temperature -40, +150

o

C

T

j

Junction Temperature +150

o

C

T

oper

Operating Temperature 0, +70

o

C

9109N-03.TBL

THERMAL DATA

Symbol Parameter Value Unit

R

th (j-a)

Junction-Ambient Thermal Resistance Max. 65

o

C/W

9109N-04.TBL

SYNC PROCESSOR

OperatingConditions (V

DD

=5V,T

amb

=25oC)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

HsVR Voltage on H/HVIN Input Pin 1 0 5 V

MinD Minimum Horizontal Input Pulses Duration Pin 1 0.7 µs

Mduty Maximum Horizontal Input Signal Duty Cycle Pin 1 25 %

VsVR Voltage on VSYNCIN Pin2 0 5 V

VSW Minimum Vertical Sync Pulse Width Pin 2 5 µs

VSmD Maximum Vertical SyncInput Duty Cycle Pin 2 15 %

VextM Maximum Vertical Sync Widthon TTLH/Vcomposite Pin 1 750

µ

s

I

HLOCKOUT

Sink and Source Current Pin3 250 µA

ElectricalCharacteristics(VDD=5V,T

amb

=25oC)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

VINTH Horizontal and Vertical Input Logic Level

(Pins 1, 2)

Low Level

High Level 2.2

0.8 V

V

RIN Horizontal and Vertical Pull-Up Resistor Pins 1, 2 200 k

Ω

TfrOut Fall and Rise Time, Output CMOS Buffer Pin 3, C

OUT

= 20pF 200 ns

VHlock Horizontal1st PLLLock OutputStatus (Pin 3) Locked, I

LOCKOUT

= -250µA

Unlocked, I

LOCKOUT

= +250µA 4.405

0.5 V

V

VoutT Extracted Vsync Integration Time (% of T

H

)

on H/V Composite (see Note 1)

C0 = 820pF 26 35 %

Note 1 : THisthe horizontal period.

I2C READ/WRITE (see Note 2)

ElectricalCharacteristics(V

DD

=5V,T

amb

=25oC)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

2

C PROCESSOR

Fscl Maximum Clock Frequency Pin 30 400 kHz

Tlow Low period of the SCLClock Pin30 1.3

µ

s

Thigh High period of the SCL Clock Pin30 0.6

µ

s

Vinth SDA and SCL Input Threshold Pins 30,31 2.2 V

VACK Acknowledge Output Voltage on SDA input with 3mA Pin 31 0.4 V

Note 2 : See also I2C Table Control and I2C Sub Address Control.

9109N-05.TBL

TDA9109/N

6/32

Page 7

HORIZONTAL SECTION

OperatingConditions

Symbol Parameter Test Conditions Min. Typ. Max. Unit

VCO

R

0(Min.)

Minimum Oscillator Resistor Pin 6 6 k

Ω

C

0(Min.)

Minimum Oscillator Capacitor Pin 5 390 pF

F

(Max.)

Maximum Oscillator Frequency 150 kHz

OUTPUT SECTION

I12m Maximum Input Peak Current Pin 12 5 mA

HOI Horizontal Drive Output Maximum Current Pin 26, Sunk current 30 mA

ElectricalCharacteristics(VCC=12V,T

amb

=25oC)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

SUPPLY AND REFERENCE VOLTAGES

V

CC

Supply Voltage Pin 29 10.8 12 13.2 V

V

DD

Supply Voltage Pin 32 4.5 5 5.5 V

I

CC

Supply Current Pin 29 50 mA

I

DD

Supply Current Pin 32 5 mA

V

REF-H

Horizontal Reference Voltage Pin 13, I = -2mA 7.4 8 8.6 V

V

REF-V

Vertical Reference Voltage Pin 21, I = -2mA 7.4 8 8.6 V

I

REF-H

Max. Sourced Current on V

REF-H

Pin 13 5 mA

I

REF-V

Max. Sourced Current on V

REF-V

Pin 21 5 mA

1st PLL SECTION

HpolT Delay Time for detecting polarity change

(see Note 3)

Pin 1 0.75 ms

V

VCO

VCO Control Voltage (Pin 7) V

REF-H

=8V f

0

fH(Max.)

1.3

6.2

V

V

Vcog VCO Gain (Pin 7) R

0

= 6.49kΩ,C0= 820pF,

dF/dV = 1/11R

0C0

17.1 kHz/V

Hph Horizontal Phase Adjustment(see Note 4) % of Horizontal Period ±10 %

Vbmin

Vbtyp

Vbmax

HorizontalPhaseSetting Value (Pin8) (seeNote4)

Minimum Value

Typical Value

Maximum Value

Sub-Address 01

Byte x1111111

Byte x1000000

Byte x0000000

2.8

3.4

4.0

V

V

V

IPll1U

IPll1L

PLL1 Filter Current Charge PLL1is Unlocked

PLL1 is Locked

±140

±1

µA

mA

f

0

Free Running Frequency R0= 6.49kΩ,C0= 820pF,

f

0

= 0.97/8R0C

0

22.8 kHz

df0/dT Free RunningFrequency Thermal Drift

(No drift on external components) (see Note 5)

-150 ppm/C

CR PLL1 Capture Range (see Note 6) R

0

= 6.49kΩ,C0= 820pF,

from f

0

+0.5kHz to 4.5f

0

fH(Min.)

f

H

(Max.) 90

25 kHz

kHz

FF Forced Frequency FF1 Byte 11xxxxxx

FF2 Byte 10xxxxxx

Sub-Address 02 2f0

3f0

Notes: 3. This delay is mandatory to avoid a wrong detection of polarity change in the case of a composite sync.

4. See Figure 10 for explanation of referencephase.

5. These parameters are not tested on each unit. They are measured during our internal qualification.

6. This PLL capturerange may be obtained only if f0is adjusted (for instanceby adjusting R0) . If not, more marginmust be provided

between f

H

(Min.) and f0, to cope withthe components spread.

9109N-05.TBL

TDA9109/N

7/32

Page 8

HORIZONTAL SECTION (continued)

ElectricalCharacteristics(V

CC

=12V,T

amb

=25oC) (continued)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

2nd PLL SECTION AND HORIZONTAL OUTPUT SECTION

FBth Flyback Input Threshold Voltage (Pin 12) 0.65 0.75 V

Hjit Horizontal Jitter At 31.4kHz 70 ppm

HD Horizontal Drive OutputDuty-Cycle Pin 26, see Note 7 48 %

XRAYth X-RAY Protection Input ThresholdVoltage Pin 25, see Note 8 8 V

Vphi2 Internal Clamping Levels on 2nd PLL

Loop Filter (Pin 4)

Low Level

High Level

1.6

4.0

V

V

VSCinh Threshold Voltage to Stop H-Out,V-Out,

B-Out and Reset XRAY

when V

CC

< VSCinh (see Note 8)

Pin 29 7.5 V

HDvd Horizontal Drive Output (low level) Pin 26, I

OUT

= 30mA 0.4 V

HORIZONTAL DYNAMIC FOCUS FUNCTION

HDFst HorizontalDynamic FocusSawtooth

MinimumLevel

MaximumLevel

Pin 9, capacitor on

HFOCUSCAP and C0 = 820pF,

T

H

=20µs

2

4.7

V

V

HDFdis Horizontal Dynamic Focus Sawtooth

Discharge Width

Start by HFLY center 400 ns

HDFDC Bottom DC Output Level R

LOAD

= 10kΩ, Pin10 2 V

TDHDF DC Output VoltageThermal Drift

(see Note 5)

200 ppm/C

HDFamp Horizontal Dynamic Focus Amplitude

Min Byte xxx11111

Typ Byte xxx10000

Max Byte xxx00000

Sub-Address 03, Pin 10,

f

H

= 50kHz, Symmetry Typ. 1

1.5

3

V

PP

V

PP

V

PP

HDFKeyst Horizontal Dynamic Focus Symmetry

Min A/B Byte xxx11111

Typ Byte xxx10000

Max A/B Byte xxx00000

Sub-Address 04, f

H

= 50kHz,

Typ. Amp

B/A

A/B

A/B

223.5

1.0

3.5

VERTICAL DYNAMIC FOCUS FUNCTION (positiveparabola)

AMPVDF Vertical Dynamic Focus Parabola (added

to horizontal)Amplitude with VAMP and

VPOS Typical

Min. Byte 000000

Typ. Byte 100000

Max. Byte 111111

Sub-Address 0F

0

0.5

1

V

PP

V

PP

V

PP

VDFAMP Parabola Amplitude Function of VAMP

(tracking between VAMP and VDF) with

VPOS Typ. (see Figure 1 andNote 9)

Sub-Address 05

Byte 10000000

Byte 11000000

Byte 11111111

0.6

1

1.5

V

PP

V

PP

V

PP

VHDFKeyt Parabola Asymetry Function of VPOS

Control(tracking between VPOS andVDF)

with VAMP Max.

Sub-Address 06

Byte x0000000

Byte x1111111

0.52

0.52

V

PP

V

PP

Notes: 5. These parameters are not tested on each unit.They are measured during our internalqualification.

7. Duty Cycle is the ratio between the output transistor OFF time and the period. The power transistor is controlled OFF when the

output transistor is OFF.

8. See Figure 14.

9. S and C correction are inhibited so the output sawtooth has a linearshape.

9109N-05.TBL

TDA9109/N

8/32

Page 9

VERTICALSECTION

OperatingConditions

Symbol Parameter Test Conditions Min. Typ. Max. Unit

OUTPUTS SECTION

VEWM Maximum E/W OutputVoltage Pin 24 6.5 V

VEWm Minimum E/W Output Voltage Pin 24 1.8 V

R

LOAD

Minimum Load for less than 1% VerticalAmplitude Drift Pin 20 65 M

Ω

ElectricalCharacteristics(VCC=12V,T

amb

=25oC)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

VERTICAL RAMP SECTION

VRB Voltage at Ramp Bottom Point V

REF-V

= 8V, Pin 22 2 V

VRT Voltage at Ramp Top Point (with Sync) V

REF-V

= 8V, Pin 22 5 V

VRTF Voltage at Ramp Top Point (without Sync) Pin 22 VRT-0.1 V

VSTD Vertical Sawtooth Discharge Time Pin 22, C

22

= 150nF 70 µs

VFRF Vertical Free RunningFrequency

(see Note 10)

C

OSC (Pin 22)

= 150nF

Measured on Pin22

100 Hz

ASFR AUTO-SYNC Frequency (see Note 11) C

22

= 150nF ±5% 50 165 Hz

RAFD Ramp Amplitude Drift Versus Frequency at

Maximum Vertical Amplitude (see Note 5)

C

22

= 150nF

50Hz < f and f < 165Hz

200 ppm/Hz

Rlin Ramp Linearity on Pin 22 (see Note 10) 2.5V < V

27

and V27< 4.5V 0.5 %

VPOS Vertical Position Adjustment Voltage

(Pin 23 - VOUT mean value)

Sub Address 06

Byte x0000000

Byte x1000000

Byte x1111111 3.65

3.2

3.5

3.8

3.3 V

V

V

VOR Vertical Output Voltage

(peak-to-peak on Pin 23)

Sub Address 05

Byte x0000000

Byte x1000000

Byte x1111111 3.5

2.25

3

3.75

2.5 V

V

V

VOI Vertical Output Maximum Current (Pin 23) ±5mA

dVS Max Vertical S-Correction Amplitude

(see Note 12)

x0xxxxxx inhibitsS-CORR

x1111111 givesmax S-CORR

Sub Address 07

∆V/V

PP

at TV/4

∆V/V

PP

at 3TV/4

-4

+4

%

%

Ccorr Vertical C-Corr Amplitude

x0xxxxxx inhibits C-CORR

Sub Address 08

∆V/V

PP

@ TV/2

Byte x1000000

Byte x1100000

Byte x1111111

-3

0

3

%

%

%

Notes: 5. These parameters are not testedon each unit. They are measured during our internal qualification.

10. With Register 07 at Byte x0xxxxxx (S correctionis inhibited) and withRegister 08 at Bytex0xxxxxx (C correction is inhibited),the

sawtooth has a linear shape.

11. This is the frequencyrangefor which thevertical oscillatorwill automaticallysynchronize,using a single capacitorvalue on Pin22

and with a constant ramp amplitude.

12. TV is thevertical period.

9109N-05.TBL

TDA9109/N

9/32

Page 10

VERTICALSECTION(continued)

ElectricalCharacteristics(V

CC

=12V,T

amb

=25oC) (continued)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

East/West (E/W) FUNCTION

EW

DC

DC Output Voltage with Typ. VPOS and Keystone

inhibited

Pin 24, see Figure 2 2.5 V

TDEW

DC

DC Output Voltage Thermal Drift See Note 13 100 ppm/C

EWpara Parabola Amplitude with Max. VAMP, Typ. VPOS,

Keystone inhibited

Subaddress 0A

Byte 11111111

Byte 11000000

Byte 10000000

2.5

1.25

0

V

PP

V

PP

V

PP

EWtrack Parabola Amplitude Function of VAMP Control

(tracking between VAMPandE/W) with Typ. VPOS,

Typ. E/W Amplitude and Keystone inhibited(see

Note 10)

Subaddress 05

Byte 10000000

Byte 11000000

Byte 11111111

0.45

0.8

1.25

V

PP

V

PP

V

PP

KeyAdj Keystone Adjustment Capability with Typ. VPOS,

E/W inhibited and Max. Vertical Amplitude

(see Note 10 and Figure 4)

Subaddress 09

Byte 1x000000

Byte 1x111111

1

1

V

PP

V

PP

KeyTrack Intrinsic Keystone Function of VPOS Control

(tracking between VPOS and E/W) with Max. E/W

Amplitude and Max.VerticalAmplitude (see Note 13)

A/B Ratio

B/A Ratio

Subaddress 06

Byte x0000000

Byte x1111111

0.52

0.52

INTERNAL DYNAMIC HORIZONTAL PHASE CONTROL

SPBpara Side Pin Balance Parabola Amplitude(Figure 3)with

Max. VAMP, Typ.VPOSand Parallelograminhibited

(see Notes 10 & 14)

Subaddress 0D

Byte x1111111

Byte x1000000

+1.4

-1.4

%T

H

%T

H

SPBtrack Side Pin Balance Parabola Amplitude function of

VAMP Control (tracking between VAMP and SPB)

with Max. SPB, Typ. VPOS and Parallelogram

inhibited (see Notes 10 & 14)

Subaddress 05

Byte 10000000

Byte 11000000

Byte 11111111

0.5

0.9

1.4

%T

H

%T

H

%T

H

ParAdj Parallelogram Adjustment Capabilit y wit h

Max. VAMP, T yp. VPOS and Max. SPB

(see Notes 10 & 14)

Subaddress 0E

Byte x1111111

Byte x1000000

+1.4

-1.4

%T

H

%T

H

Partrack Intrinsic Parallelogram Function of VPOS Control

(t racki ng between VPOS and DHP C) with

Max. VAMP, Max. SPB and Parallelogram inhibited

(see Notes 10 & 14)

A/B Ratio

B/A Ratio

Subaddress 06

Byte x0000000

Byte x1111111

0.52

0.52

VERTICAL MOIRE

VMOIRE Vertical Moiré(measured on VOUT : Pin 23) Subaddress 0C

Byte 01x11111 6 mV

BREATHING COMPENSATION

BRRANG DC Breathing Control Range (see Note 15) V18 1 12 V

BRADj Vertical Output Variation versus DC Breathing

Control (Pin 23)

V

18

≥ V

REF-V

V18=4V

0

-10

%

%

Notes: 10. With Register 07 at Byte x0xxxxxx (S correction is inhibited)and with Register 08at Byte x0xxxxxx (C correction is inhibited),the

sawtooth has a linear shape.

13. These parameters are not tested on each unit. They are measured during our internal qualification.

14. T

H

is the horizontal period.

15. When not used the DC breathingcontrol pin must be connected to 12V.

9109N-05.TBL

TDA9109/N

10/32

Page 11

B+SECTION

OperatingConditions

Symbol Parameter Test conditions Min. Typ. Max. Unit

FeedRes Minimum Feedback Resistor Resistor between Pins 15 and 14 5 kΩ

ElectricalCharacteristics(VCC=12V,T

amb

=25oC)

Symbol Parameter Test conditions Min. Typ. Max. Unit

OLG Error Amplifier Open Loop Gain At lowfrequency (see Note 16) 85 dB

UGBW Unity Gain Bandwidth (see Note 16) 6 MHz

IRI Regulation Input Bias Current Current sourced by Pin 15 (PNP base) 0.2

µ

A

EAOI Error Amplifier Output Current Current sourced by Pin 14

Current sunk by Pin 14

0.52mA

mA

CSG Current Sense InputVoltage Gain Pin 16 3

MCEth Max Current Sense InputThreshold

Voltage

Pin 16 1.2 V

ISI Current Sense InputBias Current Current sunk by Pin 16 (NPN base) 1

µ

A

Tonmax Maximum ON Time of the external

power transistor

% of Horizontal period,

f

0

= 27kHz (see Note 17)

100 %

B+OSV B+ Output Saturation Voltage V

28

with I28= 10mA 0.25 V

IV

REF

Internal Reference Voltage Onerroramp (+) inputforSubaddress0B

Byte 1000000

4.8 V

V

REFADJ

Internal Reference Voltage

Adjustment Range

Byte 1111111

Byte 0000000

+20

-20

%

%

PWMSEL Threshold for step-up/step-down

selection

Pin 16 6 V

t

FB+

Fall Time Pin 28 100 ns

Notes: 16. These parameters are not tested on each unit. They are measured during our internal qualification procedure which includes

characterization on batches coming from corners of our processes and also temperature characterization.

17. The external power transistor is OFF during 400ns of the HFOCUSCAPdischarge.

9109N-05.TBL

HDF

DC

A

B

VDF

AMP

9109N-03.EPS

Figure1 : VerticalDynamic Focus Function

DHPC

DC

A

B

SPB

PARA

9109N-05.EPS

Figure3 : Dynamic Horizontal Phase Control

Output

EW

DC

A

B

EW

PARA

9109N-04.EPS

Figure 2 : E/WOutput

Keyadj

9109N-06.EPS

Figure 4 : KeystoneEffect on E/W Output

(PCCInhibited)

TDA9109/N

11/32

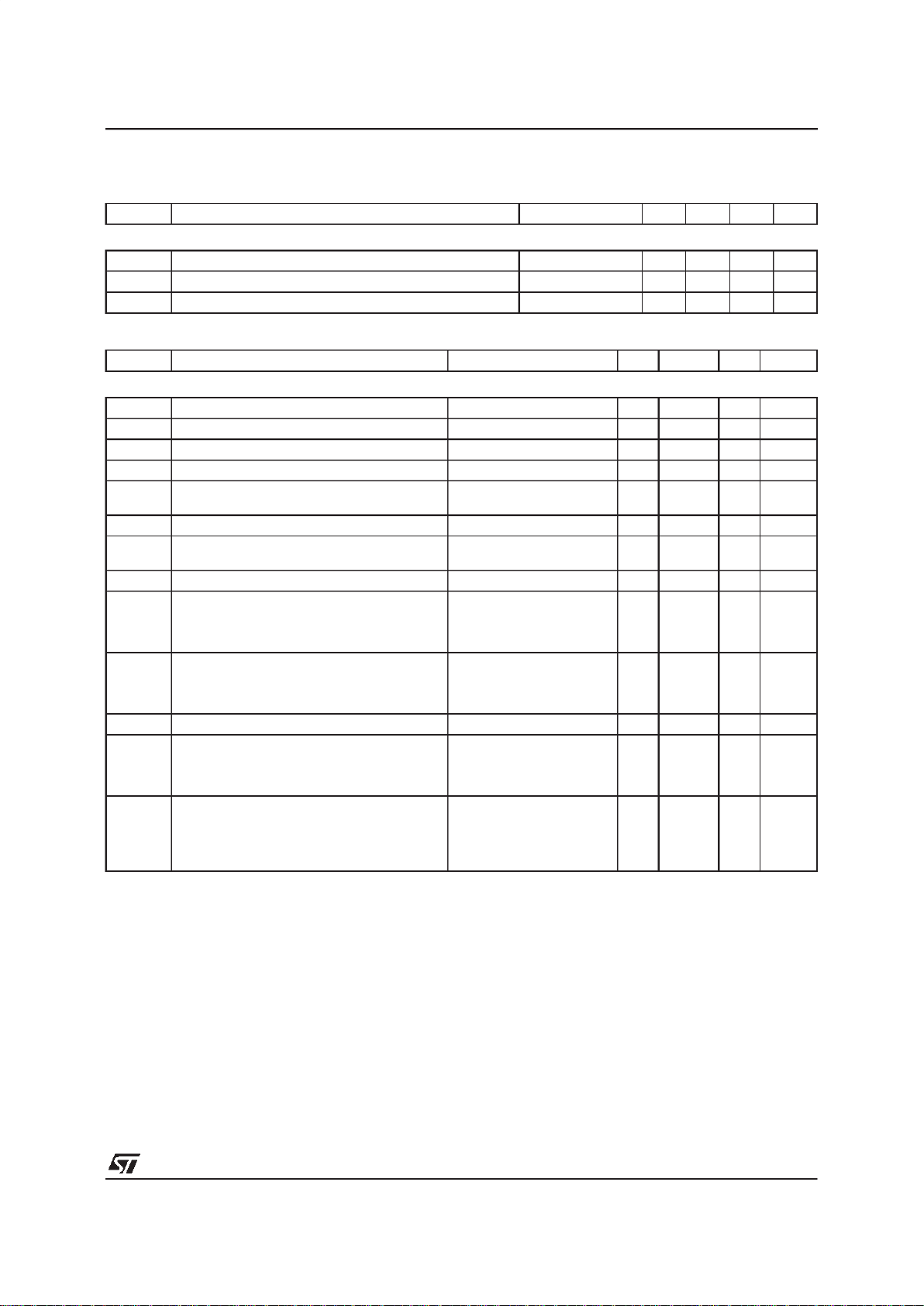

Page 12

TYPICALVERTICAL OUTPUTWAVEFORMS

Function

Sub

Address

Pin Byte Specification Effect on Screen

Vertical Size 05 23

10000000

11111111

Vertical

Position

DC

Control

06 23

x0000000

x1000000

x1111111

V

OUTDC

= 3.2V

V

OUTDC

= 3.5V

V

OUTDC

= 3.8V

Vertical

S

Linearity

07 23

0xxxxxxx

Inhibited

1x111111

Vertical

C

Linearity

08 23

1x000000

1x111111

9109N-06.TBL/ 9109N-07.EPSTO 9109N-13.EPS

2.25V

3.75V

V

OUTDC

V

OUTDC

V

PP

∆V

∆V

V

PP

=4%

V

PP

∆V

∆V

V

PP

=3%

∆V

V

PP

∆V

V

PP

=3%

TDA9109/N

12/32

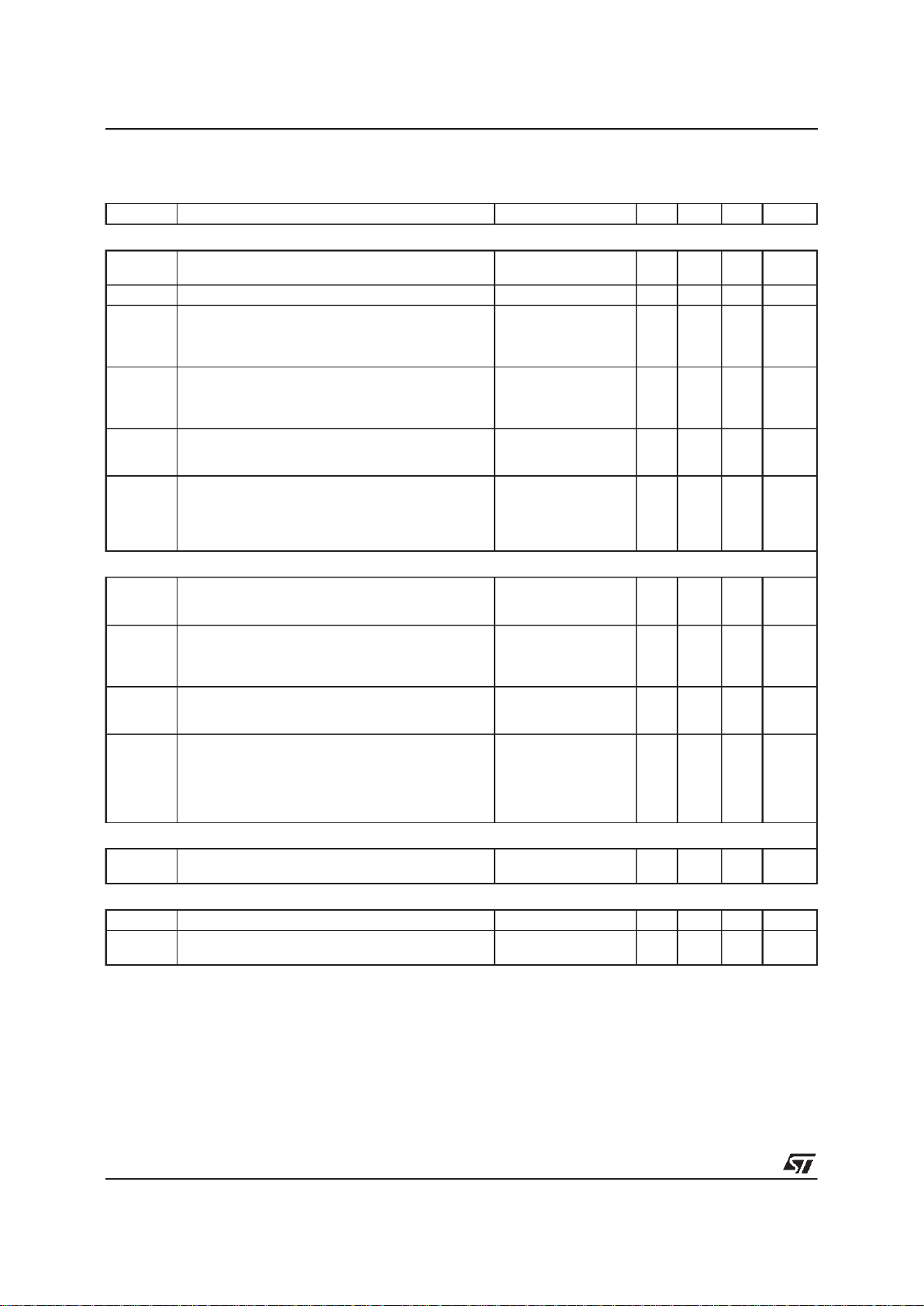

Page 13

GEOMETRY OUTPUT WAVEFORMS

Function

Sub

Address

Pin Byte Specification Effect on Screen

Horizontal

Dynamic

Focus with :

Amplitude 03 10

Horizontal

Dynamic

Focus with :

Symmetry

04 10

Keystone

(Trapezoid)

Control

09 24

E/W

Inhibited

1x000000

1x111111

E/W

(Pin Cushion)

Control

0A 24

Keystone

Inhibited

10000000

11111111

Parrallelogram

Control

0E Internal

SPB

Inhibited

1x000000

1x111111

Side Pin

Balance

Control

0D Internal

Parallelogram

Inhibited

1x000000

1x111111

Vertical

Dynamic

Focus

with Horizontal

0F 10

9109N-07.TBL / 9109N-14.EPSTO 9109N-24.EPS

2.5V

2.5V

1.0V

1.0V

0V

2.5V

2.5V

1.4% T

H

3.7V

3.7V

1.4% T

H

1.4% T

H

3.7V

1.4% T

H

3.7V

2V

T

V

T

H

Flyback

T

H

Flyback

TDA9109/N

13/32

Page 14

I2C BUSADDRESS TABLE

Slave Address (8C) : WriteMode

SubAddressDefinition

D8 D7 D6 D5 D4 D3 D2 D1

0 0 0 0 0 0 0 0 0 Horizontal Drive Selection

1 0 0 0 0 0 0 0 1 Horizontal Position

2 0 0 0 0 0 0 1 0 Forced Frequency

3 0 0 0 0 0 0 1 1 Sync Priority / Horizontal Focus Amplitude

4 0 0 0 0 0 1 0 0 Refresh / Horizontal Focus Keystone

5 0 0 0 0 0 1 0 1 Vertical Ramp Amplitude

6 0 0 0 0 0 1 1 0 Vertical Position Adjustment

7 0 0 0 0 0 1 1 1 S Correction

8 0 0 0 0 1 0 0 0 C Correction

9 0 0 0 0 1 0 0 1 E/W Keystone

A 0 0 0 0 1 0 1 0 E/W Amplitude

B 0 0 0 0 1 0 1 1 B+ Reference Adjustment

C 0 0 0 0 1 1 0 0 Vertical Moiré

D 0 0 0 0 1 1 0 1 Side Pin Balance

E 0 0 0 0 1 1 1 0 Parallelogram

F 0 0 0 0 1 1 1 1 Vertical Dynamic FocusAmplitude

Slave Address (8D) : ReadMode

No sub addressneeded.

TDA9109/N

14/32

Page 15

D8 D7 D6 D5 D4 D3 D2 D1

WRITE MODE

00

HDrive

0, off

[1], on

01

Xray

1, reset

[0]

Horizontal Phase Adjustment

[1] [0] [0] [0] [0] [0] [0]

02

Forced Frequency

1, on

[0], off

1, f0 x 2

[0], f0 x 3

03

Sync

0, Comp

[1], Sep

Horizontal Focus Amplitude

[1] [0] [0] [0] [0]

04

Detect

Refresh

[0], off

Horizontal Focus Keystone

[1] [0] [0] [0] [0]

05

Vramp

0, off

[1], on

Vertical Ramp Amplitude Adjustment

[1] [0] [0] [0] [0] [0] [0]

06

Vertical Position Adjustment

[1] [0] [0] [0] [0] [0] [0]

07

S Select

1, on

[0]

S Correction

[1] [0] [0] [0] [0] [0]

08

C Select

1, on

[0]

C Correction

[1] [0] [0] [0] [0] [0]

09

E/W Key

0, off

[1]

E/W Keystone

[1] [0] [0] [0] [0] [0]

0A

E/W Sel

0, off

[1]

E/W Amplitude

[1] [0] [0] [0] [0] [0] [0]

0B

Test H

1, on

[0], off

B+ Reference Adjustment

[1]

[0] [0] [0] [0] [0] [0]

0C

Test V

1, on

[0], off

Moiré

1, on

[0]

Vertical Moiré

[0] [0] [0] [0] [0]

0D

SPB Sel

0, off

[1]

Side Pin Balance

[1] [0] [0] [0] [0] [0]

0E

Parallelo

0, off

[1]

Parallelogram

[1] [0] [0] [0] [0] [0]

0F

Vertical Dynamic Focus Amplitude

[1] [0] [0] [0] [0] [0]

READ MODE

Hlock

0, on

[1], no

Vlock

0, on

[1], no

Xray

1, on

[0], off

Polarity Detection Sync Detection

H/V pol

[1], negative

V pol

[1], negative

Vext det

[0], no det

H/V det

[0], no det

V det

[0], no det

[] initial value

Datais transferredwith verticalsawtooth retrace.

Werecommend to set the unspecifiedbit to [0]in orderto assurethe compatibilitywith future devices.

I

2

C BUSADDRESS TABLE (continued)

TDA9109/N

15/32

Page 16

OPERATING DESCRIPTION

I - GENERALCONSIDERATIONS

I.1 - Power Supply

The typical values of the power supply voltages

V

CC

and VDDare 12V and 5V respectively. Opti-

mum operation is obtained for V

CC

between 10.8

and 13.2V and V

DD

between4.5 and 5.5V.

Inordertoavoiderraticoperationof thecircuitduring

the transient phaseof V

CC

switchingon, or off, the

value of V

CC

is monitored : if VCCis less than

7.5Vtyp., theoutputsof the circuitareinhibited.

Similarly, before V

DD

reaches4V, all theI2Cregister

areresetto theirdefaultvalue(see I

2

CControlTable).

Inorder to have very good power supply rejection,

the circuit is internally supplied by several voltage

references(typ. value : 8V). Two of these voltage

references are externally accessible, one for the

vertical and one for the horizontal part. They can

be used to bias external circuitry (if I

LOAD

is less

than5mA). Itis necessarytofilter the voltagereferencesby externalcapacitorsconnectedto ground,

inorderto minimize thenoiseandconsequentlythe

”jitter”on verticaland horizontaloutputsignals.

I.2 - I

2

C Control

TDA9109/N belongs to the I

2

C controlled device

family. Instead of being controlled by DC voltages

ondedicatedcontrolpins, each adjustmentcan be

donevia the I

2

C Interface.

TheI

2

C busis a serial buswith a clock and a data

input.Thegeneralfunctionandthebusprotocolare

specifiedin the Philips-bus data sheets.

Theinterface(DataandClock)is a comparatorwith

hysteresis;the thresholds(less then2.2V on rising

edge, more than 0.8V on falling edge with 5V

supply)are TTL-compatible.Spikes of up to 50ns

arefilteredby anintegratorandthemaximumclock

speedis limited to 400kHz.

The data line (SDA) can be used bidirectionally.

In read-mode the IC sends reply information

(1 byte) to themicro-processor.

The bus protocol prescribes a full-byte transmission in all cases. The first byte after the start

condition is used to transmit the IC-address

(hexa8C for write, 8D forread).

I.3 - Write Mode

In write mode the second byte sent contains the

subaddress of the selected function to adjust (or

controlstoaffect)and thethirdbytethe corresponding data byte. It is possible to send more than one

data byteto the IC. If afterthe thirdbyte no stop or

start condition is detected, the circuit increments

automaticallyby onethemomentarysubaddressin

the subaddress counter (auto-increment mode).

So it ispossible totransmitimmediatelythe following data bytes without sending the IC address or

subaddress.Thiscan be usefulto reinitializeall the

controls very quickly (flash manner). This procedure can be finished by a stop condition.

Thecircuithas 14adjustmentcapabilities:1 forthe

horizontal part, 4 for the vertical, 2 for the E/W

correction,2 for thedynamichorizontalphase control,1 for the Moiré option, 3 for the horizontal and

the vertical dynamic focus and 1 for the B+ reference adjustment.

17 bits are also dedicated to several controls

(ON/OFF, Horizontal Forced Frequency,Sync Priority, DetectionRefresh and XRAYreset).

I.4 - Read Mode

During the read mode the second byte transmits

the reply information.

The reply byte contains the horizontaland vertical

lock/unlockstatus,the XRAY activationstatusand,

the horizontalandvertical polaritydetection.It also

containsthe sync detection statuswhichis usedby

the MCU toassign the sync priority.

Astopconditionalwaysstopsallthe activitiesofthe

bus decoderand switchesto high impedanceboth

the data and clock line (SDAand SCL).

See I

2

C subaddressand control tables.

I.5 - Sync Processor

TheinternalsyncprocessorallowstheTDA9109/N

to accept :

- separated horizontal & vertical TTL-compatible

sync signal,

- composite horizontal & vertical TTL-compatible

sync signal.

TDA9109/N

16/32

Page 17

OPERATING DESCRIPTION (continued)

I.6 - Sync IdentificationStatus

The MCU can read (address read mode : 8D) the

statusregister via theI

2

C bus, and then select the

sync priority dependingon this status.

Among other data this registerindicates the pres-

ence of sync pulses on H/HVIN, VSYNCIN and

(when 12V is supplied) whether a Vext has been

extractedfrom H/HVIN.Bothhorizontalandvertical

sync are detected even if only 5V is supplied.

In order to choosethe right sync prioritythe MCU

may proceed as follows(see I

2

C AddressTable):

- refresh the statusregister,

- wait at least for 20ms (Max. verticalperiod),

- read this status register.

Syncpriority choice should be :

Vext

det

H/V

detVdet

Sync priority

Subaddress

03 (D8)

Comment

Sync type

No Yes Yes 1 Separated H & V

Yes Yes No 0 Composite TTL H&V

Ofcourse,whenthechoiceis made,wecanrefresh

the sync detections and verify that the extracted

Vsyncis presentand thatnosynctypechangehas

occured. The sync processor also gives sync polarityinformation.

I.7 - IC status

TheIC caninformtheMCUaboutthe1st horizontal

PLLand vertical section status (locked or not) and

aboutthe XRAYprotection(activated or not).

Resetting the XRAY internal latch can be done

either by decreasing the V

CC

supply or directly

resettingit viathe I

2

C interface.

I.8 - Sync Inputs

Both H/HVIN and VSYNCIN inputs are TTL compatible triggers with hysterisis to avoid erratic detection. Both inputs include a pull up resistor

connectedto V

DD

.

I.9 - Sync ProcessorOutput

The sync processor indicates on the HLOCKOUT

Pin whether 1st PLL is locked to an incoming

horizontal sync. HLOCKOUT is a TTL compatible

CMOS output. Its level goes to high when locked.

Inthe sametimethe D8 bit of the statusregisteris

setto 0.

This information is mainly used to trigger safety

procedures(like reducing B+ value) as soon as a

changeis delectedon the incoming sync.

II - HORIZONTALPART

II.1 - Internal Input Conditions

Adigital signal (horizontalsync pulse or TTL composite)issentbythe syncprocessorto thehorizontal input. It may be positive or negative (see

Figure5).

9109N-25.EPS

Figure 5

Using internal integration, both signals are recognized if Z/T < 25%. Synchronizationoccurs on the

leadingedge of the internal syncsignal. The minimumvalue of Z is 0.7µs.

Another integration is able to extract the vertical

pulsefromcompositesyncifthedutycycleishigher

than25% (typicallyd = 35%) (see Figure 6).

dd

C

TRAMEXT

9109N-26.EPS

Figure 6

Thelastfeatureperformedistheremovalof equalizationpulsesto avoidparasiticpulsesonthe phase

comparator(which would be disturbed by missing

or extraneouspulses).

TDA9109/N

17/32

Page 18

II.2 - PLL1

The PLL1 consists of a phase comparator, an

external filter and a voltage-controlled oscillator

(VCO). The phase comparator is a ”phase frequency” type designedin CMOS technology.This

kind of phase detector avoids locking on wrong

frequencies. It is followed by a ”charge pump”,

composedof two current sources : sunk and sourced (typically I = 1mAwhen locked and I = 140µA

whenunlocked).Thisdifferencebetweenlock/unlock

allowssmooth catchingof the horizontal frequency

by PLL1. This effect is reinforced by an internal

original slow down system when PLL1 is locked,

avoiding the horizontal frequency changing too

quickly. The dynamic behaviourof PLL1 is fixed by

anexternalfilterwhichintegratesthe currentofthe

charge pump. A ”CRC” filter is generally used

(seeFigure 7).

The PLL1 is internally inhibited during extracted

vertical sync (if any) to avoid taking in account

missingpulses or wrong pulses on phase comparator.The inhibition is done by a switch located

between the charge pump and the filter (see Fig-

7

PLL1F

1µF

4.7µF

1.8kΩ

9109N-27.EPS

Figure 7

OPERATING DESCRIPTION (continued)

ure 8). The VCO uses an external RC network.It

delivers a linear sawtooth obtained by the charge

and the discharge of the capacitor, with a current

proportionalto the currentin theresistor.The typical thresholdsof the sawtooth are 1.6V and6.4V.

The control voltageofthe VCO is between 1.33V

and 6V (see Figure 9). The theorical frequency

range of this VCO is in the ratio of 1 to 4.5.

The effective frequency range has to be smaller

(1 to 4.2) due to clamp intervention on the filter

lowest value.

6

7

Loop

Filter

R0

1.6V

6.4V

5

C0

6.4V

1.6V

0 0.875T

HTH

RS

FLIP FLOP

(1.3V < V < 6V)

7

I

0

2

4

I

0

I

0

9109N-29.EPS

Figure9 : Detailsof VCO

LOCKDET

COMP1

INPUT

INTERFACE

H/HVIN

High

CHARGE

PUMP

Low

PLL

INHIBITION

VCO

765

PLL1F R0 C0

PHASE

ADJUST

E2

I

2

C

HPOS

Adj.

OSC

Tramext

Tramext

I

2

C

Forced

Frequency

Lock/Unlock

Status

8

HPOSITION

1

9109N-28.EPS

Figure8 : BlockDiagram

TDA9109/N

18/32

Page 19

OPERATING DESCRIPTION (continued)

Thesyncfrequencymustalwaysbe higherthanthe

freerunningfrequency.For example,when usinga

sync range between 24kHz and 100kHz, the suggestedfree running frequencyis23kHz.

This can be obtained only by adjusting f

0

(for in-

stance,making R

0

adjustable).If no adjustment is

possible, more margin must be provided to cope

withthe componentsspread : ±8% for the IC, ±1%

forR

0

,±2 or5% for C0, leadingto±11%or 14%on

f

0

. The same percentage of frequency range will

lostat upperend of the range.

Another feature is the capability for the MCU to

force the horizontal frequency through I

2

C to 2xf0

or 3xf0 (for burn-in mode or safety requirements).

Inthiscase,theinhibitionswitch isopened,leaving

PLL1 free, but the voltage on PLL1 filter is forced

to 2.66V(for 2xf0) or 4.0V (for 3xf0).

PLL1ensuresthe coincidencebetweenthe leading

edge of the sync signal and a phase reference

obtained by comparison between the sawtooth of

the VCO and an internal DC voltage which is I

2

C

adjustablebetween 2.8Vand4.0V (corresponding

to±10%)(see Figure 10).

TheTDA9109/Nalsoincludesa Lock/Unlockidentification block which senses in real time whether

PLL1 is locked or not on the incoming horizontal

sync signal. The resulting information is available

on HLOCKOUT(see Sync Processor).

When PLL1 is unlocked, it forces HLOCKOUT to

high level.

The lock/unlock information is also available

throughthe I

2

C read.

H Osc

Sawtooth

Phase REF1

H Synchro

1.6V

Vb

6.4V

2.8V < Vb < 4.0V

7/8T

H

1/8T

H

Phase REF1is obtainedby comparisonbetweenthesawtoothand

a DC voltage adjustable between 2.8V and 4.0V. The PLL1 ensures the exact coincidence between the signal phase REF and

HSYNC. A ± T

H

/10 phase adjustment is possible.

9109N-30.EPS

Figure10 : PLL1Timing Diagram

II.3 - PLL2

PLL2 ensures a constant position of the shaped

flyback signal in comparison with the sawtooth of

theVCO,takinginto accountthe saturationtimeTs

(seeFigure 11).

H Osc

Sawtooth

H Drive

1.6V

4.0V

6.4V

7/8T

H

1/8T

H

Ts

Duty Cycle

Internally

Shaped

Flyback

Flyback

The duty cycle of H-drive is fixed (48%).

9109N-31.EPS

Figure 11 : PLL2 Timing Diagram

The phase comparator of PLL2 (phase type comparator) is followed by a charge pump (typical

output current : 0.5mA).

The flyback input consists of an NPN transistor.

This input must be current driven. The maximum

recommendedinputcurrentis 5mA(seeFigure12).

The dutycycle is fixed (48%).

The maximum storage time (TsMax.) is (0.44T

H

-

T

FLY

/2). Typically, T

FLY/TH

is around 20% which

meansthat Tsmax is around 34% of T

H

.

20kΩ

Q1

GND 0V

12

HFLY

400Ω

9109N-32.EPS

Figure 12 : FlybackInput Electrical Diagram

TDA9109/N

19/32

Page 20

OPERATING DESCRIPTION (continued)

H-DRIVE26

V

CC

9109N-33.EPS

Figure13

II.4 - Output Section

The H-drive signal is sent to the output through a

shapingstagewhich also controlsthe H-driveduty

cycle (I

2

C adjustable) (see Figure 11). In order to

secure the scanning power part operation, the

output is inhibitedin the followingcases:

- when V

CC

or VDDare too low,

- when the XRAYprotection is activated,

- during the Horizontalflyback,

- when the HDrive I

2

C bit control is off.

The output stage consists of a NPN bipolar

tran s is t or. O n l y th e collect or is accessib le

(see Figure 13).

This output stage is intended for ”reverse” base

control, where setting the output NPN in off-state

will control the power scanning transistor in offstate(see ApplicationDiagram).

BOUT

HORIZONTAL

OUTPUT

INHIBITION

VERTICAL

OUTPUT

INHIBITION

S

R

Q

HorizontalFlyback

0.7V

XRAYProtection

VCCChecking

V

CC

VCCoffor I2CReset

XRAY

VSCinh

I2C Drive on/off

I2C Rampon/off

9109N-34.EPS

Figure14 : SafetyFunctions BlockDiagram

The maximum output current is 30mA, and the

correspondingvoltage drop of theoutput V

CEsat

is

0.4VMax.

Obviouslythe powerscanningtransistorcannotbe

directlydrivenbytheintegratedcircuit.Aninterface

hasto beadded betweenthe circuitand the power

transistoreitherof bipolaror MOS type.

II.5 - X-RAYProtection

TheX-Ray protectionis activatedby applicationof

a high level on the X-Ray input (8V on Pin 25).

It inhibits the H-Drive and B+ outputs.

Thisprotection islatched; it maybe reset either by

V

CC

switch off or byI2C (seeFigure 14).

II.6 - Horizontaland VerticalDynamic Focus

The TDA9109/N delivers a horizontal parabola

whichis addedon a verticalparabolawaveform on

Pin 10. This horizontal parabola comes from a

sawtooth in phase with flyback pulse middle.This

sawtoothis present on Pin 9 where the horizontal

focuscapacitorshouldbethesameas C0to obtain

the correct amplitude (from 2 to 4.7V typically).

Symmetry and amplitude are I

2

C adjustable

(see Figure 15). The vertical dynamic focus is

trackedwithVPOSand VAMP.Its amplitudecan be

adjusted.Itis alsoaffectedby S andC corrections.

This positive signal once amplified is to be sent to

the CRT focusing grids.

TDA9109/N

20/32

Page 21

OPERATING DESCRIPTION (continued)

Horizontal Flyback

Internal Trigged

Horizontal Flyback

Horizontal Focus

Cap Sawtooth

Horizontal Dynamic

Focus Parabola

Output

4.7V

2V

2V

400ns

9109N-35.EPS

Figure15

III - VERTICALPART

III.1- Function

Whenthe synchronizationpulse isnot present, an

internal current source sets the free running frequency.For an external capacitor,C

OSC

= 150nF,

the typical free running frequencyis 100Hz.

The typical free running frequency can be calcu-

lated by :

f

0

(Hz)=

1.5⋅10

−5

⋅

1

C

OSC

A negative or positive TTL level pulse applied on

Pin2 (VSYNC)as wellasa TTLcompositesyncon

Pin 1 can synchronize the ramp in the range

[fmin,fmax].Thisfrequencyrange dependson the

external capacitor con nected on Pin 22.

A 150nF (±5%) capacitor is recommended for

50Hzto 165Hzapplications.

The typical maximum and minimum frequency,at

25

o

C and without any correction (S correction or

C correction),can be calculatedby :

f

(Max.)

= 2.5 x f0and f

(Min.)

= 0.33 x f

0

If S or C corrections are applied, these values are

slightyaffected.

If a synchronization pulse is applied, the internal

oscillator is synchonized immediately but its amplitude changes. An internal correction then adjusts it in less thanhalf a second.The top valueof

theramp(Pin22)is sampledonthe AGC capacitor

(Pin 20) at each clock pulse and a transconductance amplifier modifies thecharge current of the

capacitor in such a way to make the amplitude

again constant.

ThereadstatusregisterprovidestheverticalLockUnlockand the vertical sync polarity information.

Werecommend the use of an AGC capacitor with

low leakage current. A value lower than 100nA is

mandatory.

A good stability of the internal closed loop is

reached by a 470nF ± 5% capacitor value on

Pin 20 (VAGC).

III.2 - I

2

C ControlAdjustments

S and C correction shapes can then be added

to this ramp. These frequency independent S

and C corrections are generated internally.

Their amplitudes are adjustable by theirrespective I

2

C registers. They can also be inhibited by

their select bits.

Finally, the amplitude of this S and C corrected

ramp can be adjusted by the vertical ramp amplitude control register.

The adjustedramp is availableon Pin23 (V

OUT

)to

drive an external powerstage.

The gain of this stage can be adjusted (±25%)

depending on its register value.

The mean value of this ramp is driven by its own

I

2

C register (vertical position). Its value is

VPOS = 7/16 ⋅ V

REF-V

± 300mV.

Usually VOUTis sent through a resistive divider to

the inverting input of the booster. Since VPOS

derives from V

REF-V

, the bias voltage sent to the

non-invertinginput of the boostershould also derive from V

REF-V

tooptimize theaccuracy (see Ap-

plication Diagram).

III.3 - VerticalMoiré

By using the vertical moiré, VPOS can be modulatedfromframeto frame.Thisfunctionis intended

to cancelthe fringeswhich appearwhen lineto line

intervalis veryclose to the CRTvertical pitch.

The amplitude of the modulation is controlled by

register VMOIRE on sub-address 0C and can be

switched-offvia the control bit D7.

TDA9109/N

21/32

Page 22

OPERATING DESCRIPTION (continued)

23

VOUT

18 BREATH

VERT_AMP

SUB05/7bits

VMOIRE

SUB0C/5bits

VPOSITION

SUB06/7bits

22

20

SYNCHRO OSCILLATOR

2

OSC

CAP

DISCH.

VSYNCIN

POLARITY

SAMPLING

SAMPLING

CAPACITANCE

Vlow

Sawth.

Disch.

REF

TRANSCONDUCTANCE

AMPLIFIERCHARGE CURRENT

VS_AMP

SUB07/6bits

COR_C

SUB08/6bits

S CORRECTION

C CORRECTION

9109N-36.EPS

Figure16 : AGCLoop Block Diagram

III.4- Basic Equations

Infirstapproximation,the amplitudeoftheramp on

Pin23 (VOUT)is :

V

OUT

-VPOS = (V

OSC-VDCMID

)⋅(1 + 0.25(V

AMP

))

with:

-V

DCMID

= 7/16 ⋅ V

REF

(middle value of the ramp

on Pin22, typically 3.5V)

-V

OSC=V22

(rampwith fixed amplitude)

-V

AMP

= -1for minimumvertical amplitude register

value and +1 formaximum

- VPOSis calculatedby :VPOS= V

DCMID

+ 0.3V

P

with VPequals -1 for minimum vertical position

registervalue and+1 for maximum

Thecurrent available on Pin 22 is :

I

OSC

=

3

8

⋅ V

REF

⋅ C

OSC

⋅ f

with: C

OSC

: capacitorconnected on Pin 22 and

f : synchronizationfrequency.

III.5- GeometricCorrections

Theprinciple is representedin Figure17.

Startingfromthe verticalramp, a parabola-shaped

currentis generatedforE/Wcorrection(alsoknown

as Pin Cushion correction), dynamic horizontal

phase controlcorrection, and vertical dynamic Focus correction.

The parabola generator is made by an analog

multiplier, the outputcurrent of which is equal to :

DI = k⋅(V

OUT-VDCMID

)

2

where VOUT is the vertical output ramp (typicallybetween 2 and 5V) and V

DCMID

is 3.5V (for

V

REF-V

=8V).

The VOUT sawtooth is typically centeredon 3.5V.

By changing the vertical position, the sawtooth

shiftsby±0.3V.

Inordertohave good screengeometryforanyend

useradjustment, the TDA9109/N hasthe ”geometry tracking” feature, which allows generation of a

dissymetric parabola depending on the vertical

position.

Due to thelarge output stage voltage range (E/W,

Keystone), the combination of tracking function

with maximum vertical amplitude, maximum or

minimum vertical position and maximum gain on

the DAC control may lead to the output stage

saturation. This must be avoided by limiting the

outputvoltagewithapropriateI2Cregistersvalues.

TDA9109/N

22/32

Page 23

OPERATING DESCRIPTION (continued)

FortheE/Wpart and thedynamichorizontal phase

controlpart, a sawtooth-shapeddifferentialcurrent

in the following form is generated:

DI’= k’ ⋅ (V

OUT-VDCMID

)

Then ∆I and ∆I’ are added and converted into

voltagefor the E/W part.

Each of the two E/W components or the two dynamichorizontalphase control onesmay be inhibitedby theirown I

2

C selectbit.

The E/W parabola is available on Pin 24 via an

emitter follower output stage which has to be biased by an external resistor (10kΩto ground).

Sincestable in temperature,the device can be DC

coupledwith an external circuitry.

The vertical dynamic focus is combined with the

horizontalfocus on Pin 10.

The dynamichorizontal phase control drivesinternally the H-position, moving the HFLYposition on

the horizontalsawtooth in the range of ± 1.4% T

H

both for side pin balance and parallelogram.

EW Output

EW Amp

Keystone

Sidepin Amp

Parallelogram

DynamicFocus

Sidepin Balance

OutputCurrent

To Horizontal

Phase

V

DCMID

(3.5V)

2

Vertical Ramp VOUT

V.Focus

Amp

HORIZONTAL

DYNAMICFOCUS

Parabola

Generator

V

DCMID

(3.5V)

V

DCMID

(3.5V)

23

24

10

9109N-37.EPS

Figure17 : GeometricCorrections Principle

III.6- E/W

EWOUT= 2.5V + K1 (V

OUT-VDCMID

) + K2 (V

OUT-VDCMID

)

2

K1is adjustableby thekeystoneI2C register

K2is adjustableby theE/W amplitude I

2

C register

III.7- DynamicHorizontalPhase Control

I

OUT

=K3(V

OUT-VDCMID

) + K4 (V

OUT-VDCMID

)

2

K3is adjustableby theparallelogramI2C register

K4is adjustableby theside pin balance I

2

C register

TDA9109/N

23/32

Page 24

IV- DC/DC CONVERTER PART

OPERATING DESCRIPTION (continued)

This unit controls the switch-mode DC/DC converter. It converts a DC constant voltage into the

B+ voltage (roughly proportional to the horizontal

frequency)necessary for thehorizontal scanning.

This DC/DC converter can be configuredeither in

step-uporstep-down mode. In bothcases it operates very similarly to the well known UC3842.

IV.1- Step-upMode

OperatingDescription

- ThepowerMOS isswitched-onduringtheflyback

(at the beginning of the positive slope of the

horizontal focus sawtooth).

- The power MOS is switched-offwhen its current

reachesa predeterminedvalue.Forthispurpose,

a sense resistor is inserted in its source. The

voltage on this resistoris sentto Pin16(I

SENSE

).

- The feedback(com i ngeitherfrom the EHV or from

theflyback )is dividedtoa voltage clo s eto 4.8Vand

compar edto theinter nal4.8Vrefer ence(I

VREF

).The

differenceisamplif i edby anerroramplifi er,theoutput

ofwhichcontrolsthepowerMOSswitch-offcurrent.

MainFeatures

- Switching synchronized on the horizontal frequency,

- B+ voltage always higher than the DC source,

- Currentlimited on a pulse-by-pulsebasis.

IV.2- Step-down Mode

In step-down mode, the Isense information is not

usedanymoreandthereforenot sentto the Pin16.

This mode is selected by connectingthis Pin16 to

a DC voltage higher than6V (for example V

REF-V

).

OperatingDescription

- The powerMOSis switched-onas forthestep-up

mode.

- The feedbackto theerroramplifier is done as for

the step-up mode.

- T he power MOS is switched-off whe n the

HFOCUSCAP voltage get higher than the error

amplifier output voltage.

Main Features

- Switching synchronized on the horizontal frequency,

- B+ voltage always lower than the DC source,

- No currentlimitation.

IV.3- Step-up and Step-downModeComparison

In step-down mode the control signal is inverted

compared with the step-upmode.

The reason for this is the following:

- In step-upmode, the switch is a N-channelMOS

referencedto ground and made conductive by a

high level on its gate.

- In step-down,a high-side switch is necessary.It

can be either a P-or a N-channel MOS.

- ForaP-channelMOS,thegateiscontr olleddire ctly

fromPin28throughacapacitor(thisallow stospare

aTransformer).Inthiscase,anegative-goingpulse

isneededtomaketheMOSconductive.Therefore

itis necessar yto inver tthecontrolsignal.

- For a N-channelMOS,a transformeris needed

to control the gate. The polarity of the transformer can be easily adapted to the negativegoingcontrol pulse.

161415

V

B+

L

+

8V

6V

C4

C3

C2

1/3

Σ

C1

Horizontal Dynamic

Focus Sawtooth

down

up

S

R

Q

HDF Disc

400ns

down

up

Inhibit SMPS

28

12V

Command step-up/down

BOUT

I

SENSE

COMPREGIN

95dB

A

± I

adjust

DAC

7bits

I2C

TDA9109/N

1MΩ

22kΩ

1.2V

1.2V

4.8V ±20%

8V

9109N-38.EPS

Figure18 : DC/DCConverter

TDA9109/N

24/32

Page 25

INTERNAL SCHEMATICS

Pins 1 -2

H/HVIN

VSYNCIN

20k

Ω

200

Ω

5V

9109N-39.EPS

Figure19

5V

3

HLOCKOUT

9109N-40.EPS

Figure20

4

13

12V

PLL2C

HREF

9109N-41.EPS

Figure21

5

13

12V

C0

HREF

9109N-42.EPS

Figure22

6

13 13

12V

HREF HREF

R0

9109N-43.EPS

Figure23

7PLL1F

9109N-44.EPS

Figure24

TDA9109/N

25/32

Page 26

INTERNAL SCHEMATICS (continued)

8

12V

HREF

HPOSITION

9109N-45.EPS

Figure25

9

13

12V

HREF

HFOCUS

CAP

9109N-46.EPS

Figure26

10HFOCUS

12V

12V

9109N-47.EPS

Figure27

12

13

12V

HREF

HFLY

9109N-48.EPS

Figure28

14

COMP

9109N-49.EPS

Figure29

15REGIN

12V

9109N-50.EPS

Figure30

TDA9109/N

26/32

Page 27

INTERNAL SCHEMATICS (continued)

16

12V

I

SENSE

9109N-51.EPS

Figure31

18BREATH

12V

9109N-52.EPS

Figure32

20

12V

VAGCCAP

9109N-53.EPS

Figure33

22VCAP

12V

9109N-54.EPS

Figure 34

23

12V

VOUT

9109N-55.EPS

Figure35

24EWOUT

12V

9109N-56.EPS

Figure36

TDA9109/N

27/32

Page 28

INTERNAL SCHEMATICS (continued)

25

12V

XRAY

9109N-57.EPS

Figure37

HOUT-BOUT

Pins 26-28

12V

9109N-58.EPS

Figure 38

12V

Pins 30-31

SDA - SCL

9109N-59.EPS

Figure39

TDA9109/N

28/32

Page 29

APPLICATION DIAGRAMS

TP17

J12

TP13

J11

TP10

TP16

123456789101112

242322212019181716151413

PWM0

PWM1

FBLK

VSYNC

HSYNC

V

DD

PXCK

CKOUT

XTALOUT

XTALIN

PWM2

PWM3PWM4

PWM5

PWM6

PWM7

SCL

SDA

RST

GNDRGBTEST

IC3 - STV9422

X1

8MHz

C37

33pF

C38

33pF

C43

47µF

L2

22µH

+5V

R30

10kΩ

R43

10kΩ

C42

1µF

TILT

J13

C45

10µF

J16 J15

432

1

J14

+5V

R39

4.7kΩ

R29

4.7kΩ

R42

100Ω

R41

100Ω

C39

22pF

C40

22pF

SCL

SDA

12345678

910111216 15 14 13

GND

QA

IA

IA

CDA

TA2

TA1V

CC

TB1

TB2

CDBIBIBQBQB

ICC1

MC14528

QA

CC3

47pF

PC1

47kΩ

+12V

+12V

+12V

CC4

47pF

+12V

PC2

47kΩ

CC1

100nF

CC2

10µF

R35

10kΩ

R10

10kΩ

C25

33pF

HOUT

R8

10kΩ

C22

33pF

J8

HFLY

Q1

BC557Q2BC557

R15

1kΩ

R17

270kΩ

R37

27kΩ

+12V

R31

27kΩ

R19

270kΩ

R38

2.2Ω

3W

C11 220pF

R18

39kΩ

R33

4.7kΩ

R9

470Ω

R34

1kΩ

J1

E/W

C36

1µF

Q3

TIP122

E/W POWER STAGE

TP4 TP3

1

7

5

4

6

2

3

IC1

TDA8172

C10

470µF

C8

100nF

-12V

C1

220nFR31.5Ω

R5

5.6kΩ

R11

220Ω

0.5W

R4

1Ω

0.5W

C4

100nF

R2

5.6kΩ

R40

36kΩ

C10

100µF

35V

D1

1n4001

C14

470µFC9100nF

TP6

TP7

3

2

1

J18

V YOKE

J6

J3

J2

+12V

-12V

R1

12kΩ

C41

470pF

VERTICAL DEFLECTION STAGE

1

2

3

4

5

6

7

8

9

10

11

12

16

15

14

13

C13 10nF

R36 1.8kΩC31 4.7µF

C17 1µF

24

23

22

21

20

19

18

17

26

25

32

31

30

29

28

27

H/HVIN

VSYNCIN

HLOCKOUT SCL

PLL2C

C0 B+OUT

R0 GGND

PLL1F HOUTCOL

HPOSITION XRAYIN

HFOCUSC EWOUT

FOCUS VOUT

HGND VCAP

HFLY VREF

HREF VAGCCAP

COMP VGND

REGIN BREATH

I

SENSE

BGND

IC4

TDA9109/N

TP1

+12VV

CC

C5

100µF

C6

100nF

C49

100nF

HOUT

R53

1kΩ

C48

10µF

C3

47µF

C2

100nF

C12

150nF

C15

470nF

+12V

R52

3.9kΩ

+12V

Q4

BC557

Q5

BC547

R58

10Ω

L3

22µH

C50

10µF

C7 22nF

C28

820pF 5%

R23

6.49kΩ 1%

C34

820pF 5%

C16

C33

100nF

C27

47µF

HREF

L4

47µH

R24

10kΩ

R25

1kΩ

J9

DYN

FOCUS

C47

100pF

R50

1MΩ

C46

1nF

C51

100nF

R57

82kΩ

JP1

R51

1kΩ

B+OUT

GND

I

SENSE

REGIN

3

2

1

J19

4

CON4

R49

22kΩ

+5V

C30

100µF

C32

100nF

L1

22µH

+5V

SDA

+5V

R56

560Ω

D2

1N4148

J17

HOUT

C60

100nF

R74

10kΩ

R77

15kΩ

P1

10kΩ

+12V

R73

1MΩ

R76

47kΩ

R75

10kΩTP8

EHT

COMP

R7 10kΩ

R45 33kΩ

TP14

()

*

()*Optional

9109N-60.EPS

Figure40 : DemonstrationBoard

TDA9109/N

29/32

Page 30

APPLICATION DIAGRAMS (continued)

9109N-61.EPS

Figure41 : PCBLayout

TDA9109/N

30/32

Page 31

APPLICATION DIAGRAMS (continued)

9109N-62.EPS

Figure42 : ComponentsLayout

TDA9109/N

31/32

Page 32

PMSDIP32.EPS

PACKAGE MECHANICAL DATA

32 PINS - PLASTICSHRINK DIP

Dimensions

Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 3.556 3.759 5.080 0.140 0.148 0.200

A1 0.508 0.020

A2 3.048 3.556 4.572 0.120 0.140 0.180

B 0.356 0.457 0.584 0.014 0.018 0.023

B1 0.762 1.016 1.397 0.030 0.040 0.055

C 0.203 0.254 0.356 0.008 0.010 0.014

D 27.43 27.94 28.45 1.080 1.100 1.120

E 9.906 10.41 11.05 0.390 0.410 0.435

E1 7.620 8.890 9.398 0.300 0.350 0.370

e 1.778 0.070

eA 10.16 0.400

eB 12.70 0.500

L 2.540 3.048 3.810 0.100 0.120 0.150

SDIP32.TBL

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from

its use. No licence is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications

mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information

previouslysupplied.STMicroelectronicsproducts are notauthorized foruse ascriticalcomp onentsin lifesupportdevicesor systems

without express written approval of STMicroelectronics.

The ST logo is a trademark of STMicroelectronics

1998 STMicroelectronics - All Rights Reserved

Purchase of I

2

C Components of STMicroelectronics, conveys a license under the Philips I2C Patent.

Rights to use these components in a I

2

C system,is granted provided that the system conforms to

the I

2

C Standard Specifications as defined by Philips.

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy- Japan - Korea - Malaysia - Malta - Morocco- The Netherlands

Singapore - Spain - Sweden - Switzerland- Taiwan- Thailand - United Kingdom - U.S.A.

TDA9109/N

32/32

Loading...

Loading...