Datasheet T15N1024A-55D, T15N1024A-100PI, T15N1024A-100P, T15N1024A-100HI, T15N1024A-100CI Datasheet (Taiwan Memory Technology)

...Page 1

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 1 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

SRAM

128K X 8 LOW POWER

CMOS STATIC RAM

FEATURES

• Low-power consumption

- Active: 40mA at 55ns (Max.)

- CMOS Stand-by: 10uA (Max.)

• 55/70/100 ns access time

• Equal access and cycle time

• Single +2.4V to 3.6V Power Supply

• TTL compatible , Tri-state output

• Common I/O capability

• Automatic power-down when deselected

• Available in 32-pin SOP ,TSOP-I(8x20mm),

TSOP-I(8x13.4mm) ,48-pin CSP packages

•

Operating temperature :

Commercial : 0 ~ +70 °C

Industrial : -40 ~ +85 °C

PART NUMBER EXAMPLES

PART NO.

PACKAGE

CODE

Operating

Temperature

T15N1024A-55D

T15N1024A-70H

T15N1024A-100P

T15N1024A-100C

D=SOP

H=TSOP-I(8x20)

P=TSOP-I(8x13.4)

C=CSP

0 ~ +70 °C

T15N1024A-55DI

T15N1024A-70HI

T15N1024A-100PI

T15N1024A-100CI

D=SOP

H=TSOP-I(8x20)

P=TSOP-I(8x13.4)

C=CSP

-40 ~ +85 °C

GENERAL DESCRIPTION

The T15N1024A is a very Low Power CMOS

Static RAM organized as 131,072 words by 8 bits.

That operates on a wide voltage range from 2.4V

to 3.6V power supply, Fabricated using high

performance CMOS technology, Inputs and

three-state outputs are TTL compatible and allow

for direct interfacing with common system bus

structures. Data retention is guaranteed at a power

supply voltage as low as 1.5V.

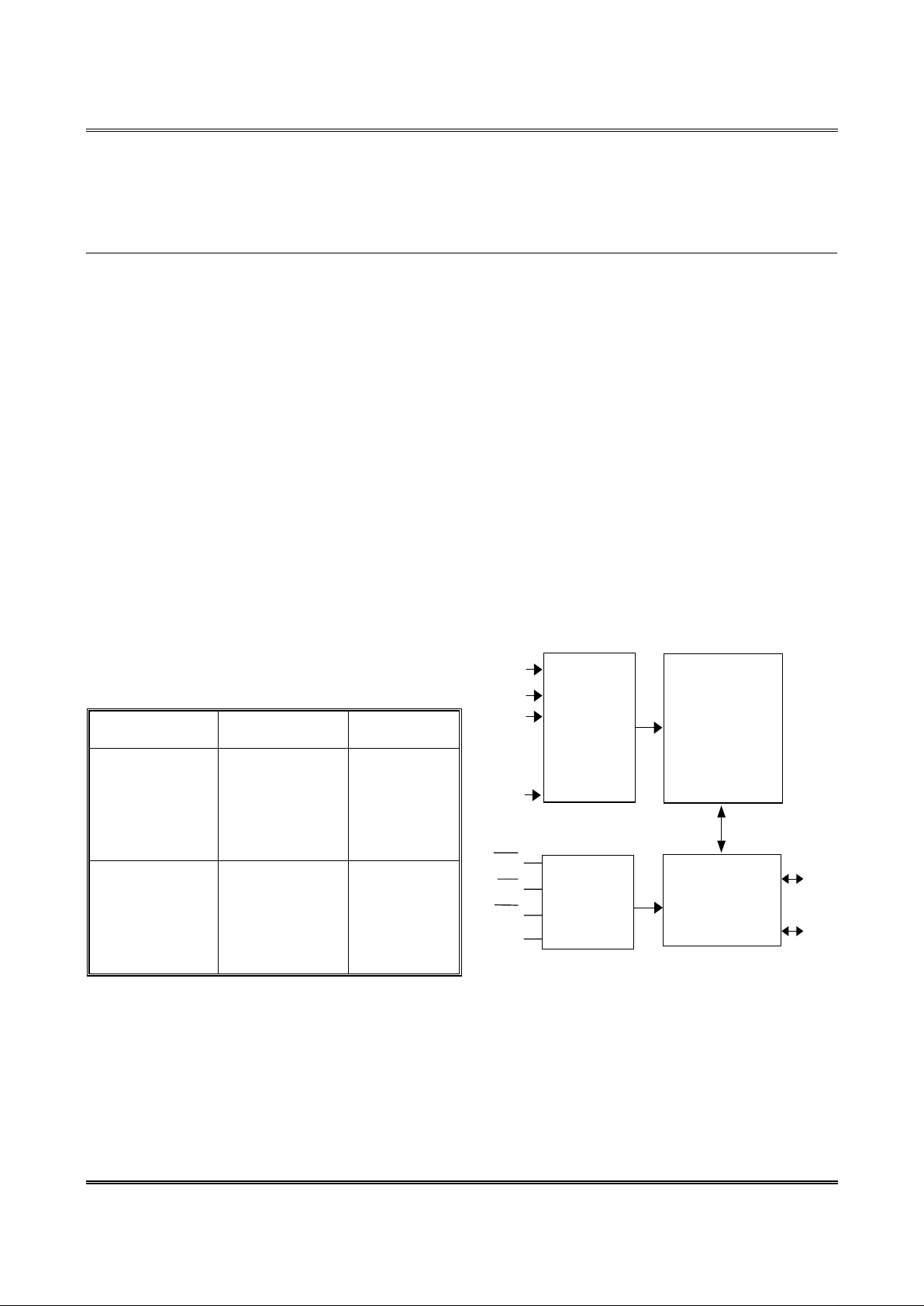

BLOCK DIAGRAM

DECODER

A0

A16

I/O8

Vcc

.

.

.

.

.

.

DATA I/O

CORE

ARRAY

Vss

I/O1

WE

OE

CE1

CONTROL

CIRCUIT

CE2

Page 2

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 2 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

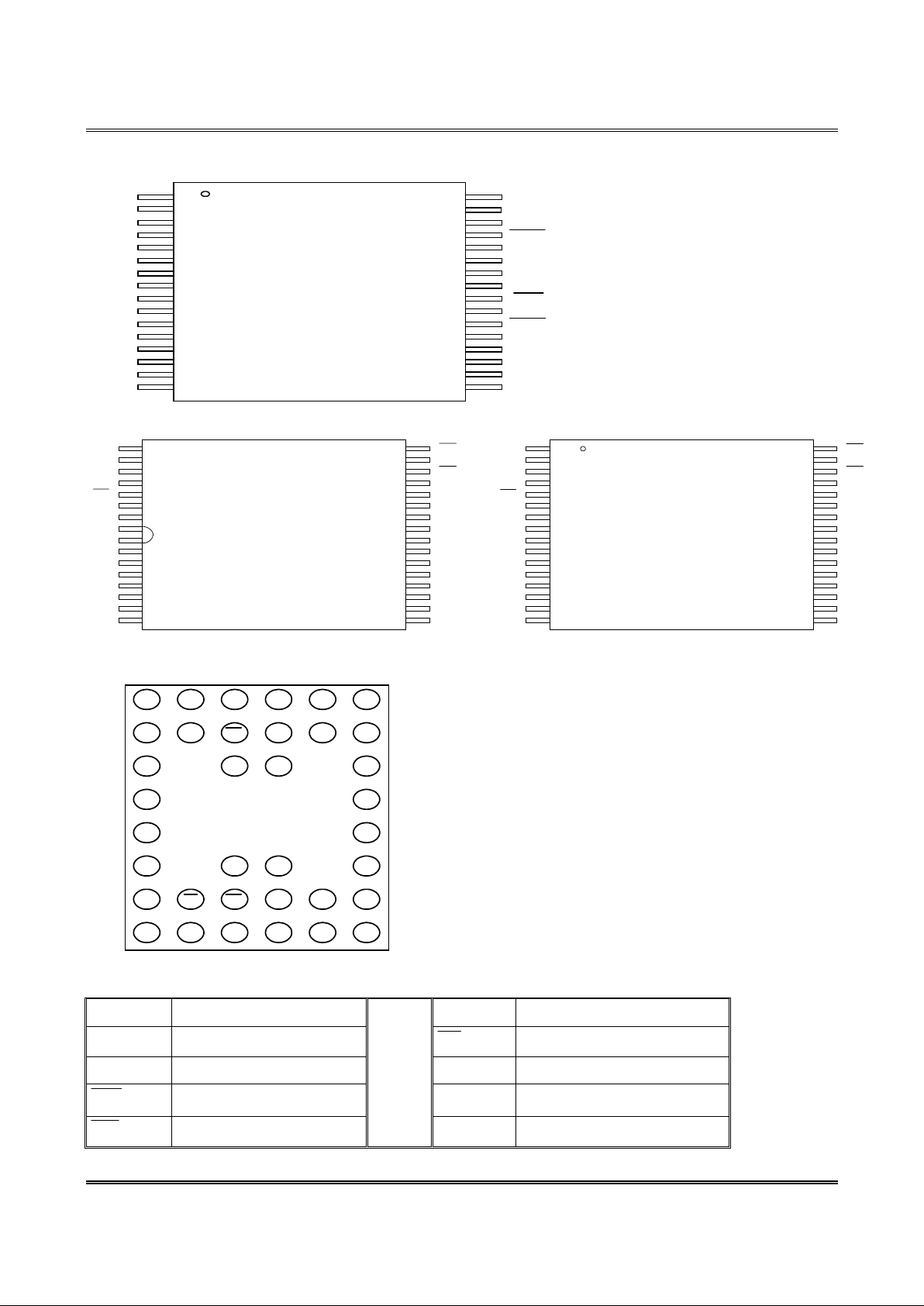

PIN CONFIGURATIONS

SOP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

NC

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O1

I/O2

I/O3

VSS

VDD

A15

CE2

WE

A13

A8

A9

A11

OE

A10

CE1

I/O8

I/O7

I/O6

I/O5

I/O4

TSOP-I

(8x20mm)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

A11

A9

A8

A13

WE

CE2

A15

VDD

NC

A16

A14

A12

A7

A6

A5

A4

OE

A10

CE1

I/O8

I/O7

I/O6

I/O5

I/O4

VSS

I/O3

I/O2

I/O1

A0

A1

A2

A3

TSOP-I

(8x13.4mm)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

A11

A9

A8

A13

WE

CE2

A15

VDD

NC

A16

A14

A12

A7

A6

A5

A4

OE

A10

CE1

I/O8

I/O7

I/O6

I/O5

I/O4

VSS

I/O3

I/O2

I/O1

A0

A1

A2

A3

A0 A1

I/O5

VDD

VSS

I/O6

I/O7

I/O8

A9 A10

NCOENC

CE1 A16

A11 A12

A15

A13 A14

I/O4

I/O3

A5

A8

VDD

VSS

A2

I/O2

I/O1

CE2 A3 A6

A7A4WE

NC

A

654321

H

G

F

E

D

C

B

48-CSP

TOP VIEW

PIN DESCRIPTIONS

SYMBOL DESCRIPTIONS SYMBOL DESCRIPTIONS

A0 ~ A16 Address inputs

OE

Output enable input

I/O0~I/O8 Data inputs/outputs VDD Power supply

CE1

,

CE2

Chip enable VSS Ground

WE

Write enable input

NC No connection

Page 3

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 3 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

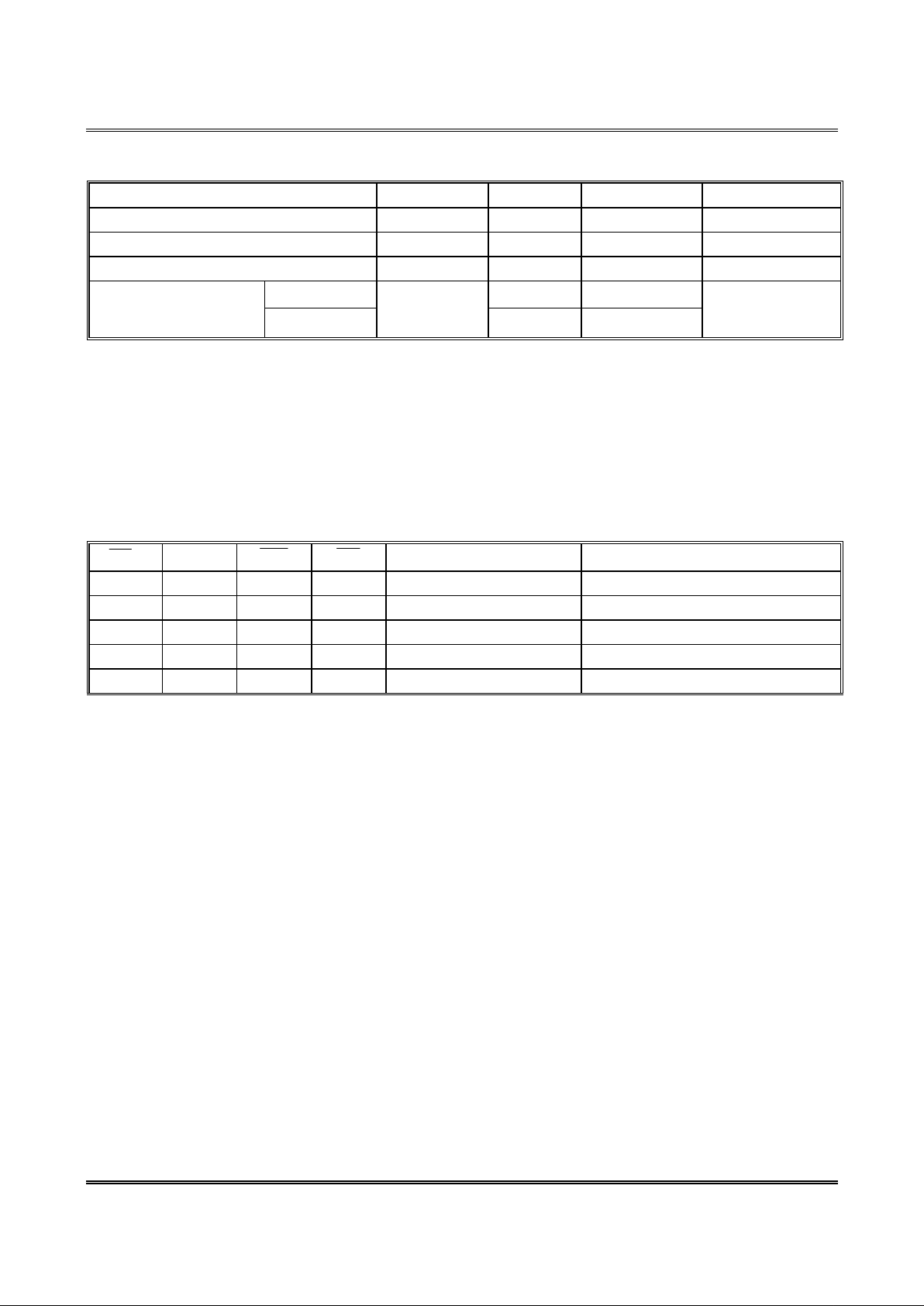

ABSOLUTE MAXIMUM RATINGS*

PARAMETER SYM MIN. MAX. UNIT

Voltage on Any Pin Relative to Gnd VR -0.5 +4.6 V V

Power Dissipation

P

D

- 0.7 W

Storage Temperature

T

STG

-55 +150 °C

commercial 0 +70

Operating

Temperature

industrial

Ta

-40 +85

°C

*Note: Stresses greater than those listed above Absolute Maximum Ratings may cause permanent damage to

the device. This is a stress rating only and function operation of the device at these or any other

conditions outside those indicated in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect reliability.

TRUTH TABLE

CE 1

CE2

WE

OE

DATA MODE

H X X X High-Z

Standby

X L X X High-Z

Standby

L H H L Data Out Active, Read

L H H H High-Z Active, Output Disable

L H L X Data In Active, Write

*Note: X = Don’t Care, L = Low, H = High

Page 4

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 4 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

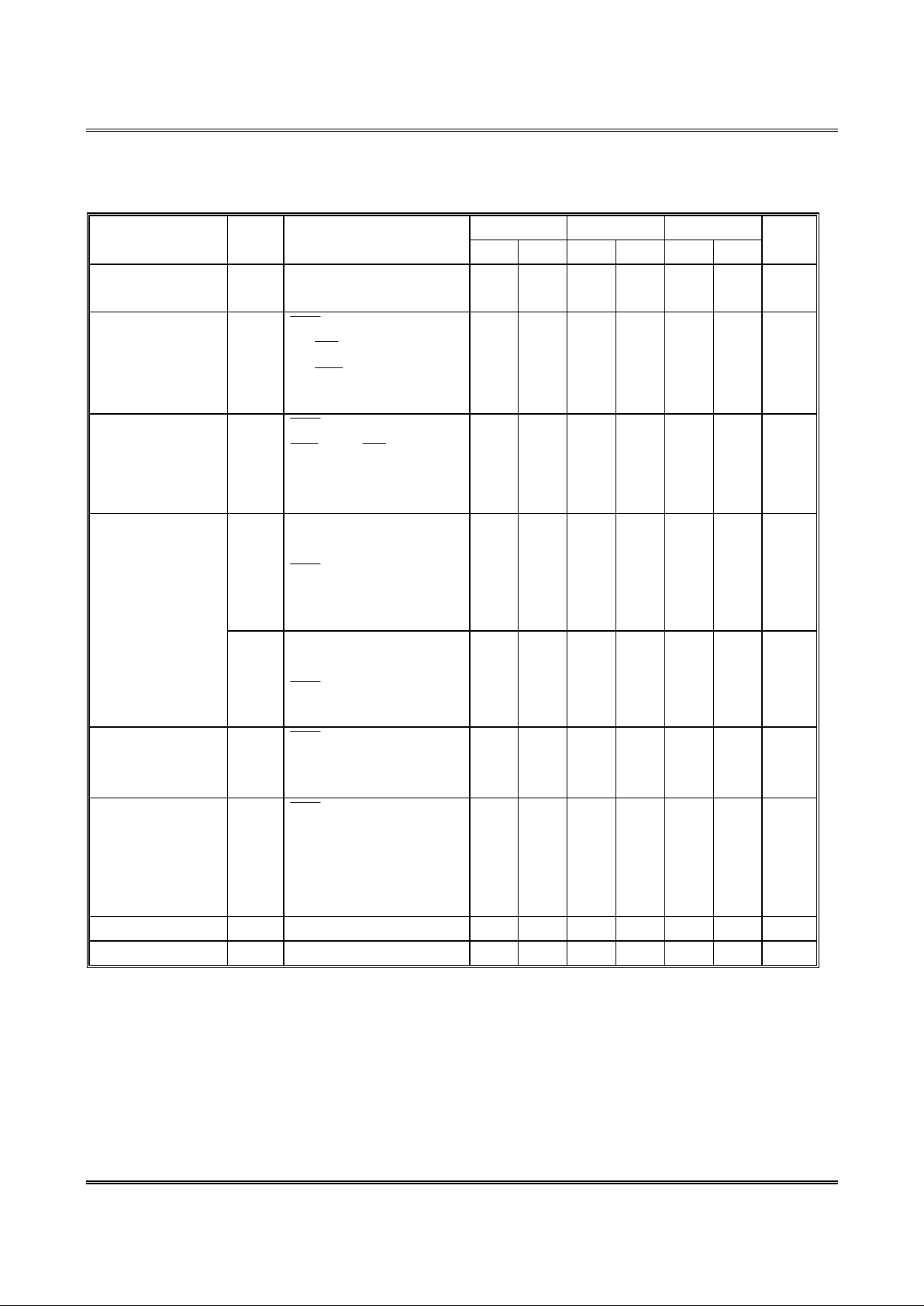

OPERATING CHARACTERISTICS

(Vcc = 2.4 to 3.6V, Gnd = 0V, Ta =

0 ~ +70 °C

/-40°C to 85°C)

-55 -70 -100

PARAMETER SYM. TEST CONDITIONS

Min Max Min Max Min Max

UNIT

Input Leakage

Current

I

LI

Vcc = Max,

V

IN

= Gnd to Vcc

- 1 - 1 - 1 uA

Output Leakage

Current

I

LO

CE1

= VIH or CE2= VIL

or

OE

= VIH

or

WE

= VIL

V

OUT

= Gnd to Vcc

- 1 - 1 - 1 uA

Operating Power

Supply Current

I

CC

CE1

= VIL,CE2= V

IH,

WE

=V

IH,

OE

= V

IH ,

V

IN

= VIH or V

IL,

I

OUT

=0mA

- 2 - 2 - 2 mA

I

CC1

Cycle time=1us,

100% duty, I

OUT

=0mA,

CE1

≤ 0.2V,

CE2 ≥ V

CC

-0.2V,

V

IN

≤ 0.2V

- 3 - 3 - 3 mA

Average Operating

Current

I

CC2

Cycle time=min,

100% duty, I

OUT

=0mA,

CE1

= VIL,CE2= V

IH ,

V

IN

= VIH or VIL

- 40 - 35 - 25 mA

Standby Power

Supply Current

(TTL Level)

I

SB

CE1

=VIH

CE2= V

IL

- 0.5 - 0.5 - 0.5 mA

Standby Power

Supply Current

(CMOS Level)

I

SB1

CE1

≥ Vcc-0.2V,

CE2 ≥ V

CC

-0.2V

or CE2 ≤ 0.2V

V

IN

≤ 0.2V or

V

IN

≥ Vcc-0.2V

- 10 - 10 - 10

u

A

Output Low Voltage

V

OL

I

OL

= 1.0mA

- 0.4 - 0.4 - 0.4 V

Output High Voltage

V

OH

I

OH

= -0.5 mA

2.1 - 2.1 - 2.1 - V

Page 5

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 5 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

RECOMMENDED OPERATING CONDITIONS

(Ta =

0 ~ +70 °C

/-40°C to 85°C**)

PARAMETER SYM MIN MAX UNIT

Vcc 2.4 3.6 V

Supply Voltage

Gnd 0.0 0.0 V

V

IH

1.6 Vcc+0.2 V

Input Voltage

V

IL

-0.3 0.4 V

CAPACITANCE

(f = 1 MHz, Ta = 25°C,)

PARAMETER SYMBOL CONDITION MAX. UNIT

Input Capacitance

C

IN

V

IN

= 0V

6 pF

Input/ Output Capacitance

C

I/O

V

IN

=

V

OUT

= 0V

8 pF

Note: This parameter is guaranteed by device characterization and is not production tested.

AC TEST CONDITIONS

PARAMETER CONDITIONS

Input Pulse Levels 0.2V to 2.1V

Input Rise and Fall Times 3.0 ns

Input and Output Timing Reference Level 1.4V

C

L

=30pF+1TTL Load(55ns/70ns)

Output Load

C

L

=100pF+1TTL Load(Load for 100ns)

AC TEST LOADS AND WAVEFORM

DQ

Z

0

= 50 ohm

50 ohm 30 pF

Vt =1.4V

Fig.A * Including Scope and Jig Capacitance

TTL

CL*

Fig.B Output Load Equivalent

R

L

C

L

Page 6

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 6 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

AC CHARACTERISTICS

(

V

cc

=2.4 to 3.6V, Gnd = 0V, Ta =

0 ~ +70 °C

/-40°C to 85°C)

(1) READ CYCLE

-55 -70 -100

PARAMETER SYM.

Min Max Min Max Min Max

UNIT

Read Cycle Time

t

RC

55 - 70 - 100 - ns

Address Access Time

t

AA

- 55 - 70 - 100 ns

Chip Enable Access Time

t

ACE

- 55 - 70 - 100 ns

Output Enable Access Time

t

OE

- 30 - 35 - 50 ns

Output Hold from Address Change

t

OH

10 - 10 - 10 - ns

Chip Enable to Output in Low-Z

t

LZ

10 - 10 - 10 - ns

Chip Disable to Output in High-Z

t

HZ

- 20 - 25 - 30 ns

Output Enable to Output in Low-Z

t

OLZ

5 - 5 - 5 - ns

Output Disable to Output in High-Z

t

OHZ

- 20 - 25 - 30 ns

(2)WRITE CYCLE

-55 -70 -100

PARAMETER SYM.

Min Max Min Max Min Max

UNIT

Write Cycle Time

t

WC

55 - 70 - 100 - ns

Chip Enable to Write End

t

CW

50 - 60 - 80 - ns

Address Valid to Write End

t

AW

50 - 60 - 80 - ns

Address Setup Time

t

AS

0 - 0 - 0 - ns

Write Pulse Width

t

WP

45 - 50 - 70 - ns

Write Recovery Time

t

WR

0 - 0 - 0 - ns

Data Valid to Write End

t

DW

25 - 30 - 40 - ns

Data Hold Time

t

DH

0 - 0 - 0 - ns

Write Enable to Output in High-Z

t

WHZ

- 25 - 25 - 30 ns

Output Active from Write End

t

OW

5 - 5 - 5 - ns

Page 7

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 7 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

TIMING WAVEFORMS

READ CYCLE 1

(Address Controlled)

Address

D

out

Previous Data Vaild Data Vaild

t

OH

t

AA

t

RC

DON'T CARE

UNDEFINED

READ CYCLE 2

(Chip Enable Controlled)

CE1

D

out

CE2

t

LZ

t

ACE

t

HZ

DON'T CARE

UNDEFINED

Notes (READ CYCLE) :

1.

WE

are high for read cycle.

2. All read cycle timing is referenced from the last valid address to the first transition address.

3. t

HZ

and t

OHZ

are defined as the time at which the outputs achieve the open circuit condition referenced to

V

OH

or VOL levels.

4. At any given temperature and voltage condition. t

HZ

(max.) is less than t

LZ

(min.) both for a given device

and from device to device interconnection.

5. Transition is measured ±200mV from steady state voltage with load. This parameter is sampled and not

100% tested.

6. Device is continuously selected with

1CE

=VIL .

Page 8

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 8 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

WRITE CYCLE 1 (

WE

Controlled)

D

out

CE1

Address

CE2

WE

D

IN

t

WC

t

AW

t

WR

t

CW

t

AS

t

WP

t

WHZ

t

OW

t

DH

t

DW

High-Z

High-Z

DON'T CARE

UNDEFINED

WRITE CYCLE 2 (

CE Controlled)

D

out

CE1

Addres

s

CE2

WE

D

IN

t

WC

t

AW

t

WR

t

CW

t

AS

t

WP

t

DH

t

DW

High-Z

High-Z

DON'T CARE

UNDEFINED

NOTES ( WRITE CYCLE ) :

1. A write occurs during the overlap of a low

1CE

, a high CE2 and a low WE . A write begins at

the lateat transition among

1CE

goes low, CE2 going high and WEgoing low. A write end at

the earliest transition among

1CE

going high, CE2 going low and WE going high. tWP is

measured from the beginning of write to the end of write.

2. tCW is measured from the later of

1CE

going low or CE2 going high to the end of write.

3. tAS is measured from the address valid to the beginning of write.

4. tWR is measured from the end of write to the address change.

Page 9

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 9 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

DATA RETENTION CHARACTERISTICS

(Ta = 0 ~ +70 °C /-40°C to 85°C)

PARAMETER SYM. TEST CONDITION MIN. MAX. UNIT

VCC for Data Retention VDR

1CE

≥ V

DD

-0.2V

1.5 - V

Data Retention Current I

CCDR

CE2 ≤ 0.2V - 5* uA

Chip Deselect to Data Retention Time t

CDR

VIN ≥ Vcc -0.2V or 0 - ns

Operation Recovery Time tR VIN ≤ 0.2V tRC - ns

* VCC=1.8V

DATA RETENTION WAVEFORM

(Ta = 0 ~ +70 °C /-40°C to 85°C)

Da ta Reten tio n Mode

V

DR

> 1.5V

Vcc_typ

t

CDR

VCC

CE1

V

IH

CE1>VCC-0.2V

V

IH

t

R

Vcc_TYP

V

IH

CE2 < 0.2V

V

IH

CE2

Page 10

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 10 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

PACKAGE DIMENSIONS

32-LEAD SOP

1

16

17

32

EHE

b

D

S

A

A2

A1

Seating Plane

e

y

See De tail F

LE

C

e1

L

e1

Detail F

Dimension in inches Dimension in mm

Symbol

min. typ. max min. typ. max.

A

- - 0.118 - - 3.00

A1

0.004 - - 0.10 - -

A2

0.101 0.106 0.111 2.57 2.69 2.82

b

0.014 0.016 0.020 0.36 0.41 0.51

C

0.006 0.008 0.012 0.15 0.20 0.31

D

- 0.805 0.817 - 20.45 20.75

E

0.440 0.445 0.450 11.18 11.30 11.43

e

0.044 0.050 0.056 1.12 1.27 1.42

HE

0.546 0.556 0.556 13.87 14.12 14.38

L

0.023 0.031 0.039 0.58 0.79 0.99

LE

0.047 0.055 0.063 1.19 1.40 1.60

S

- - 0.036 - - 0.91

y

- - 0.004 - - 0.10

θθθθ

0°

-

10° 0°

-

10°

Notes :

1. Dimensions D max. & S

include mold flash or tie bar

burrs.

2. Dimension b does not include

dambar protrusion / intrusion.

3. Dimensions D & E include

mold mismatch and determined

at the mold parting line.

4. controlling dimension : inches

5. general appearance spec should

be based on final visual

inspection spec.

Page 11

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 11 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

PACKAGE DIMENSIONS

32-LEAD TSOP (8x20mm)

DIMENSIONS IN INCHES DIMENSIONS IN MM

SYMBOL

MIN NOM MAX MIN NOM MAX

A -- - 0.047 - - 1.20

A1 0.002 - 0.006 0.05 - 0.15

A2 0.035 0.040 0.041 0.90 1.00 1.05

b 0.007 0.008 0.011 0.17 0.20 0.27

C 0.004 0.006 0.008 0.10 0.15 0.21

D 0.787 TYP 20.00 TYP

Db 0.724 TYP 18.40 TYP

E 0.315 TYP 8.00 TYP

L 0.020 0.024 0.028 0.598 0.610 0.622

L1 0.032 TYP 0.813 TYP

θ

0°~12° 0°~12°

Page 12

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 12 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

PACKAGE DIMENSIONS

32-LEAD TSOP-I (8x13.4mm)

SYMBOL Dimension in inches Dimension in mm

A

0.044(MAX) 1.10(MAX)

A1

0.004±0.002 0.05±0.05

A2

0.041(MAX) 1.02(MAX)

b

0.008±0.004 0.20±0.10

C

0.006±0.001 0.15±0.02

D

0.465±0.008 11.8±0.2

E

0.315±0.004 8.0±0.1

HD

0.528±0.008 13.4±0.2

e

0.020(TYP.) 0.5(TYP.)

L

0.020±0.004 0.5±0.1

L1

0.031±0.008 0.8±0.2

y

0.002(MAX) 0.05(MAX)

θθθθ

0° ~ 5°

0° ~ 5°

HD

1

16 17

32

D

"A "

C

b

e

A2AA1

E

L

L1

D e ta il "A"

Seating plane

Seating plane y

Page 13

TE

CH

tm

T15N1024A

TM Technology Inc. reserves the right P. 13 Publication Date: FEB. 2003

to change products or specifications without notice. Revision:E

PACKAGE DIMENSIONS

Units : millimeters

48-pin CSP (8 row x 6 column)

48 BALL FINE PITCH BGA (0.75mm ball pitch)

Bottom View

Top View

B

B1

0.50

0.50

C

C1

B/2

C1/2

#A1

A1 INDEX MARK

D

0.30

E2

E1

E

A

Y

Symbol min typ max

A

- 0.75 -

B

5.95 6.00 6.05

B1

- 3.75 -

C

7.95 8.00 8.05

C1

- 5.25 -

D

0.25 0.30 0.35

E

- 1.10 1.20

E1

- 0.95 -

E2

0.20 0.25 0.30

Y

- - 0.08

Notes :

1. Bump counts : 48 (8 row x 6column)

2. Bump pitch : (x,y)=(0.75 x 0.75) typ.

3. All tolerance are ±0.050 unless otherwise specified.

4. ‘Y’ is coplanarity : 0.08(max)

5. Units : mm

Loading...

Loading...