Page 1

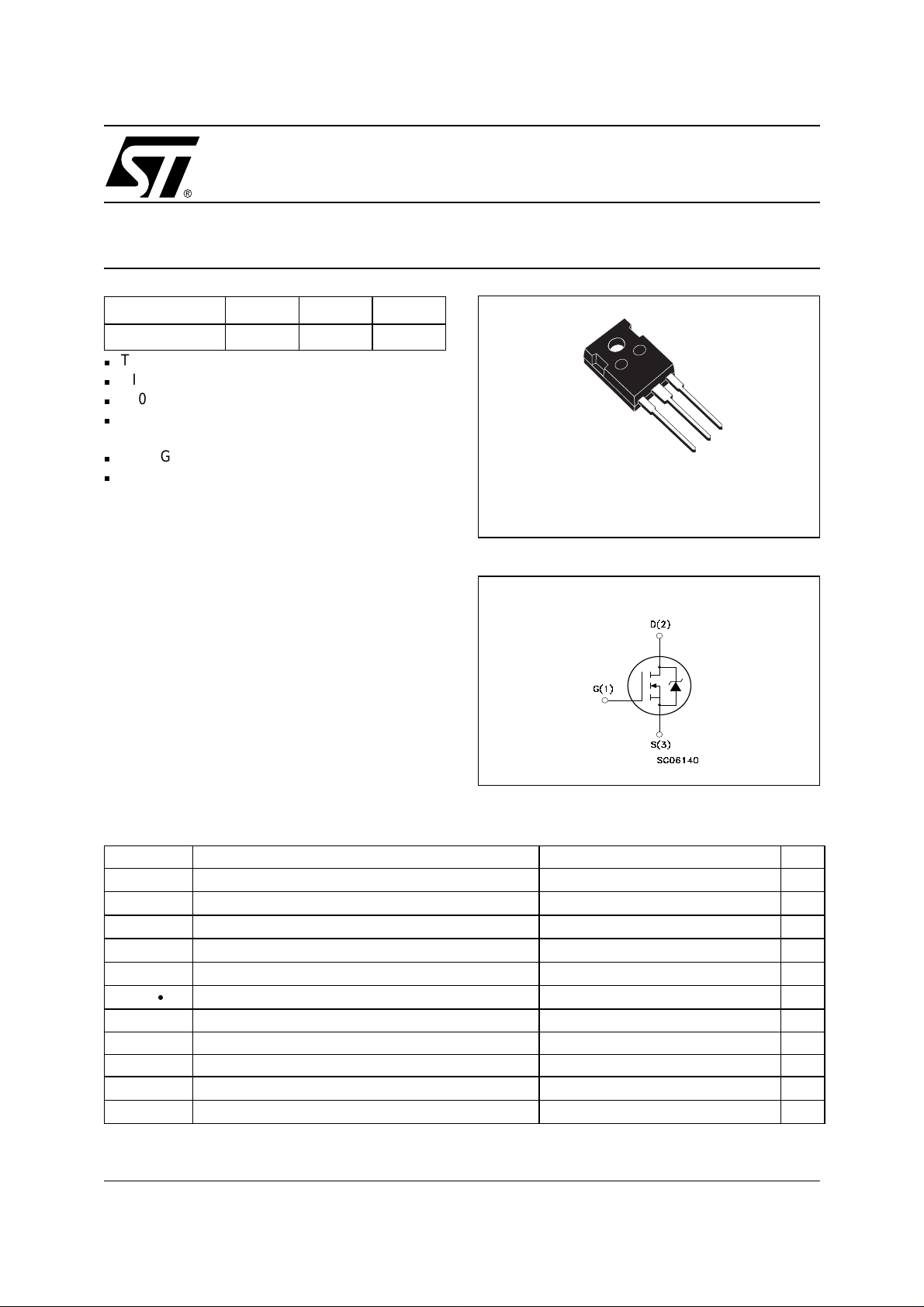

STW45NM60

N-CHANNEL 600V - 0.09Ω - 45A TO-247

MDmesh™Power MOSFET

TYPE V

DSS

R

DS(on)

I

D

STW45NM60 600V < 0.11Ω 45 A

n

TYPICAL RDS(on) = 0.09Ω

n

HIGH dv/dt AND AVALANCHE CAPABILITIES

n

100% AVALANCHE TESTED

n

LOW INPUT CAPACITANCE AND GATE

CHARGE

n

LOW GATE INPUT RESIST ANC E

n

TIGHT PROCESS CONTROL AND HIGH

MANUFACTURING YIELDS

DESCRIPTION

The MDmesh™

is a new revolutionary MOSFET

technology that associates the Multiple Drain process with the Company’s PowerMESH™ horizontal

layout. The resulting product has an outstanding low

on-resistance, impressively high dv/dt and excellent

avalanche characteristics. The adoption of the

Company’s proprietary strip technique yields overall

dynamic performance that is significantly better than

that of similar competition’s products.

APPLICATIONS

The MDmesh™ family is very suitable for increasing

power density of high voltage converters allowing

system miniaturization and higher efficiencies.

3

2

1

TO-247

INTERNAL SCHEMATIC DIAGRAM

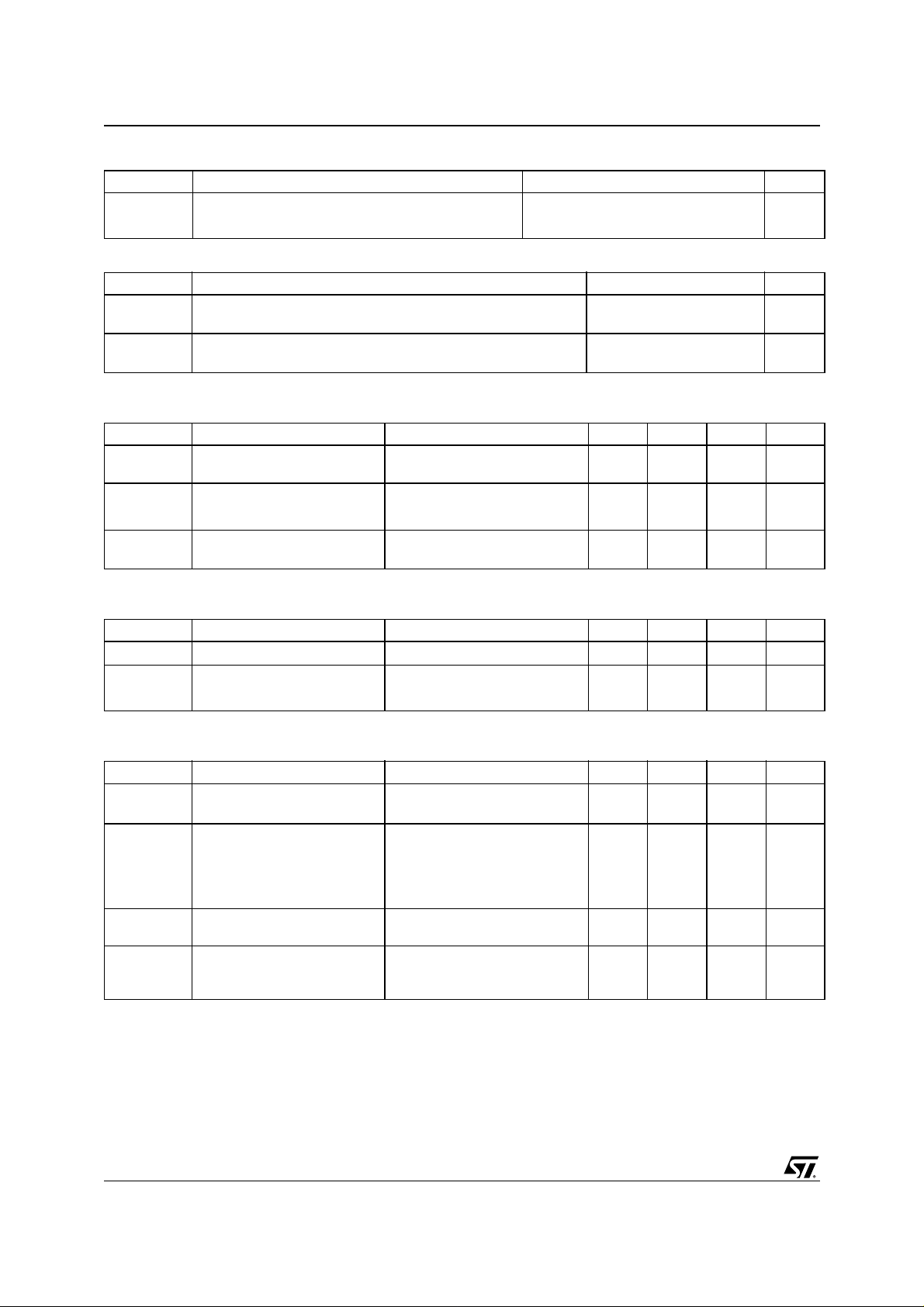

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

DS

V

DGR

V

GS

I

D

I

D

I

DM

P

TOT

dv/dt (1) Peak Diode Recovery voltage slope 15 V/ns

T

stg

T

j

(•)Pu l se width limite d by safe operating area

Drain-source Voltage (VGS = 0)

Drain-gate Voltage (RGS = 20 kΩ)

600 V

600 V

Gate- source Voltage ±30 V

Drain Current (continuous) at TC = 25°C

Drain Current (continuous) at TC = 100°C

(l)

Drain Current (pulsed) 180 A

Total Dissipation at TC = 25°C

45 A

28 A

417 W

Derating Factor 3.33 W/°C

Storage Temperature –65 to 150 °C

Max. Operating Junction Temperature 150 °C

(1) ISD ≤45A, di/dt ≤400A/µs, VDD ≤ V

(BR)DSS

, Tj ≤ T

JMAX.

1/8August 2002

Page 2

STW45NM60

THERMA L D ATA

Rthj-case Thermal Resistance Junction-case Max 0.3 °C/W

Rthj-amb Thermal Resistance Junction-ambient Max 30 °C/W

T

l

AVALANCHE CHARACTERISTICS

Symbol Parameter Max Value Unit

I

AR

E

AS

Maximum Lead Temperature For Soldering Purpose 300 °C

Avalanche Current, Repetitive or Not-Repetitive

(pulse width limited by T

max)

j

Single Pulse Avalanche Energy

(starting T

= 25 °C, ID = IAR, VDD = 35 V)

j

15 A

850 mJ

ELECTRICAL CHARACTERISTICS (T

= 25 °C UNLESS OTHERWISE SPECIFIED)

CASE

OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

Drain-source

ID = 250 µA, VGS = 0 600 V

Breakdown Voltage

ON

I

I

GSS

(1)

DSS

Zero Gate Voltage

Drain Current (V

GS

Gate-body Leakage

Current (V

DS

= 0)

= 0)

V

= Max Rating

DS

VDS = Max Rating, TC = 125 °C

V

= ±30V ±100 nA

GS

10 µA

100 µA

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

GS(th)

R

DS(on)

Gate Threshold Voltage

Static Drain-source On

V

= VGS, ID = 250µA

DS

VGS = 10V, ID = 22.5A

345V

0.09 0.11 Ω

Resistance

DYNAMIC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

(1) Forward Transconductance VDS > I

g

fs

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance 1250 pF

Reverse Transfer

Capacitance

C

(2) Equivalent Output

oss eq.

Capacitance

R

G

1. Pulsed: Pu l se duration = 300 µs, duty cyc l e 1.5 %.

2. C

Gate Input Resistance f=1 MHz Gate DC Bias = 0

is defined as a constant equivalent capacitance giving the same charging time as C

oss eq.

V

DSS

I

= 22.5A

D

V

DS

VGS = 0V, VDS = 0V to 480V 340 pF

Test Signal Level = 20mV

Open Drain

D(on)

x R

DS(on)max,

= 25V, f = 1 MHz, VGS = 0

15 S

3800 pF

46 pF

1.4 Ω

when VDS increase s fr om 0 to 80%

oss

2/8

Page 3

STW45NM60

ELECTRICAL CHARACTERISTICS (CONTINUED)

SWITCHING ON

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

t

d(on)

Q

Q

Q

t

r

g

gs

gd

Turn-on Delay Time

Rise Time 20 ns

Total Gate Charge

Gate-Source Charge 31 nC

Gate-Drain Charge 43 nC

SWITCHING OFF

Symbol Param eter Test Conditions Min. Typ. Max. U nit

t

r(Voff)

t

t

f

c

Off-voltage Rise Time

Fall Time 23 ns

Cross-over Time 40 ns

SOURCE DRAIN DIODE

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

VSD (1)

t

rr

Q

rr

I

RRM

t

rr

Q

rr

I

RRM

Note: 1. Pulsed: Pulse duration = 300 µ s, duty cycle 1.5 %.

2. Pulse width lim i t ed by safe operating area.

(2)

Source-drain Current 45 A

Source-drain Current (pulsed) 180 A

Forward On Voltage

Reverse Recovery Time

Reverse Recovery Charg e

Reverse Recovery Curren t

Reverse Recovery Time

Reverse Recovery Charg e

Reverse Recovery Curren t

= 250V, ID = 22.5A

DD

RG= 4.7Ω VGS = 10V

(see test circuit, Figure 3)

V

= 400V, ID = 45A,

DD

V

= 10V

GS

V

= 400V, ID = 45A,

DD

RG= 4.7Ω, V

GS

= 10V

(see test circuit, Figure 5)

ISD = 45A, VGS = 0

= 45A, di/dt = 100A/µs,

I

SD

V

= 100 V, Tj = 25°C

DD

(see test circuit, Figure 5)

= 45A, di/dt = 100A/µs,

I

SD

VDD = 100 V, Tj = 150°C

(see test circuit, Figure 5)

30 ns

96 134 nC

16 ns

1.5 V

508

10

40

650

14

43

ns

µC

A

ns

µC

A

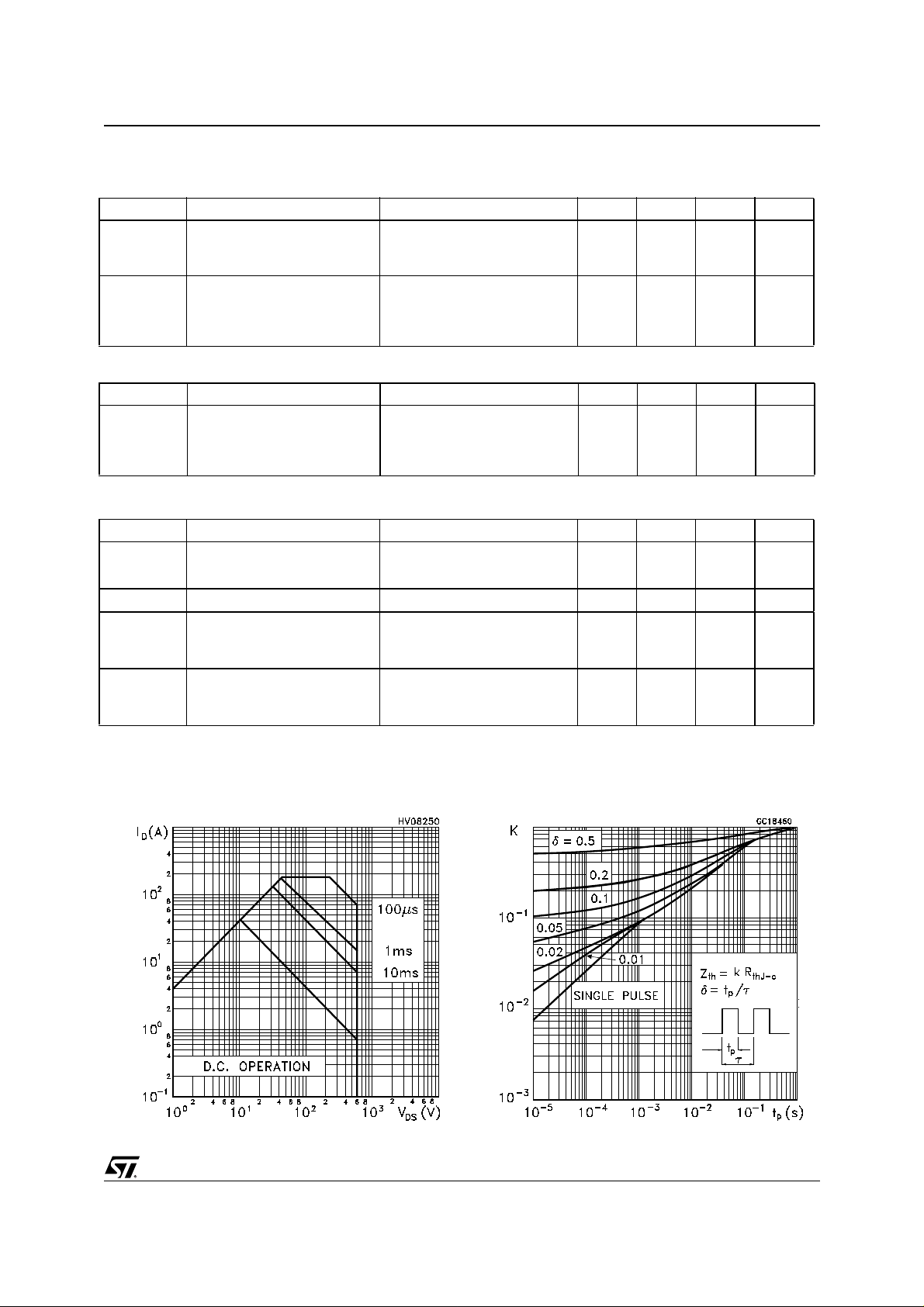

Thermal ImpedanceSafe Operating Area

3/8

Page 4

STW45NM60

Output Characteristics Transfer Characteristics

Transconductance Static Drain-source On Resistance

Gate Charge vs Gate-source Voltage Capacitance Variations

4/8

Page 5

Source-drain Diode Forward Characteristics

STW45NM60

Normalized On Resistance vs TemperatureNormalized Gate Thereshold Voltage vs Temp.

5/8

Page 6

STW45NM60

Fig. 2: Unclamped Inductive WaveformFig. 1: Unclamped Inductive Load Test Circuit

Fig. 3: Switching Times Test Circuit For

Resistive Load

Fig. 5: Test Circuit For Inductive Load Switching

And Diode Recovery Times

Fig. 4: Gate Charge test Circuit

6/8

Page 7

TO-247 MECHANICAL DATA

STW45NM60

DIM.

A 4.85 5.15 0.19 0.20

D 2.20 2.60 0.08 0.10

E 0.40 0.80 0.015 0.03

F 1 1.40 0.04 0.05

F1 3 0.11

F2 2 0.07

F3 2 2.40 0.07 0.09

F4 3 3.40 0.11 0.13

G 10.90 0.43

H 15.45 15.75 0.60 0.62

L 19.85 20.15 0.78 0.79

L1 3.70 4.30 0.14 0.17

L2 18.50 0.72

L3 14.20 14.80 0.56 0.58

L4 34.60 1.36

L5 5.50 0.21

M 2 3 0.07 0.11

V

V2

Dia 3.55 3.65 0.14 0.143

MIN. TYP MAX. MIN. TYP. MAX.

mm. inch

5º5º

60º 60º

7/8

Page 8

STW45NM60

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for t he

consequences of use of su ch in formation nor for any in fringement of patents or other rights of third parties w hich may result from

its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications

mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information

previously suppli ed. STMi croelect ronics pr oducts are not author ized for use as cr itical component s in li fe suppo rt devi ces or

systems without express written approval of STMicroelectronics.

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco

© The ST logo is a registered trademark of STMicroelectronics

© 2002 STMicroelectronics - Printed in Italy - All Rights Reserved

Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

STMicroelectronics GROUP OF COMPANIES

© http://www.st.com

8/8

Loading...

Loading...