Page 1

STQ1HNC60

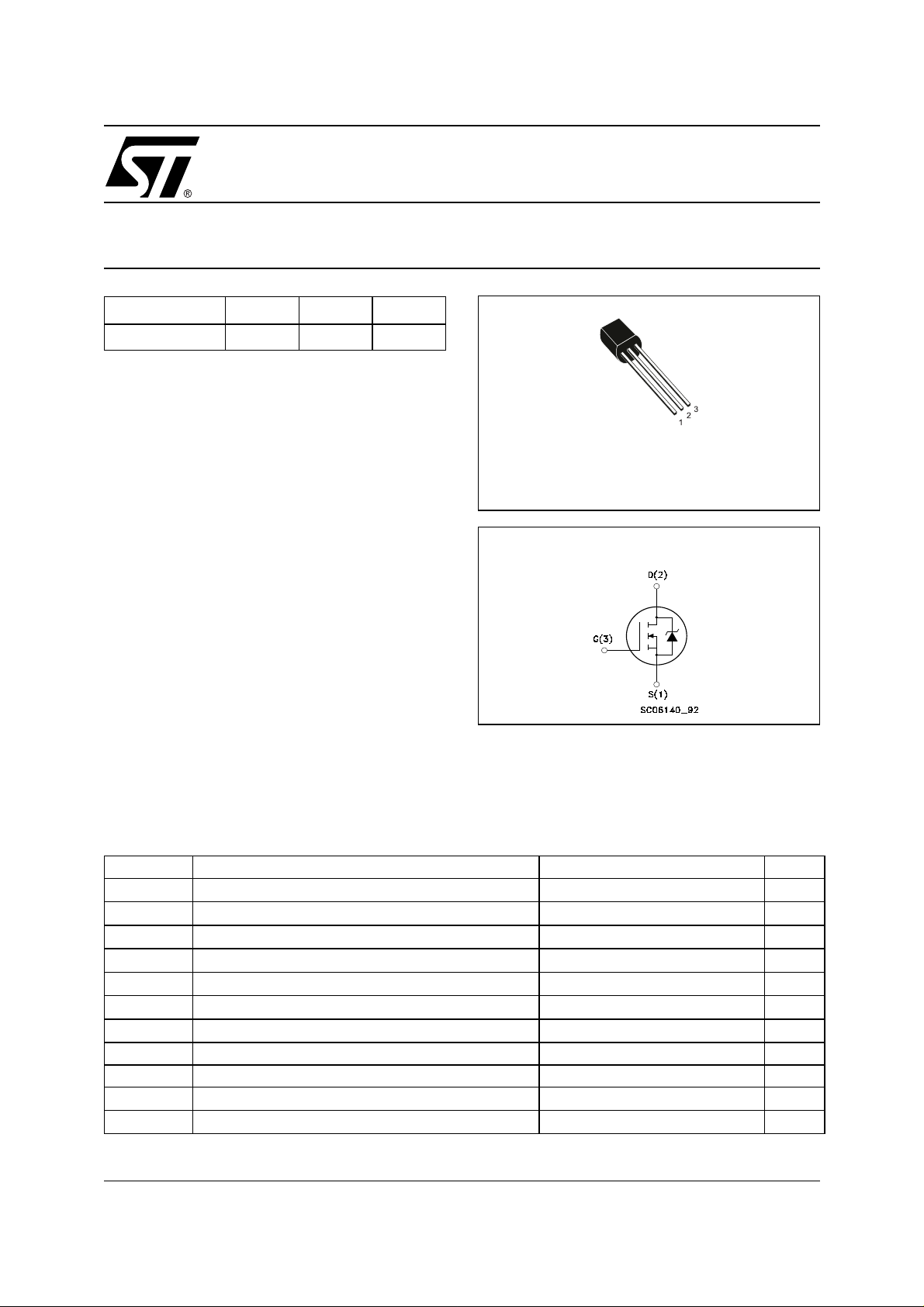

N-CHANNEL 600V - 7Ω - 0.4A TO-92

PowerMesh™II MOSFET

PRELIMINARY DATA

TYPE V

DSS

R

DS(on)

I

D

STQ1HNC60 600 V < 8 Ω 0.4 A

■ TYPICAL R

■ EXTREMELY HIGH dv /d t C APABILITY

■ 100% AVALANCHE TESTED

■ NEW HIGH VOLTAGE BENCHMARK

■ GATE CHARGE MINIMIZED

(on) = 7 Ω

DS

DESCRIPTION

Using the latest high voltage MESH OVERLAY™II

process, STMicroelectronics has designed an advanced family of power MOSFETs with outstanding

performances. The new patent pending strip layout

coupled with the Company’s proprietary edge termination structure, gives the lowest RDS(on) per area,

exceptional avalanche and dv/dt capabilities and

unrivalled gate charge and switching characteristics.

APPLICATIONS

■ SWITCH MODE LOW POWER SUPPIES

(SMPS)

■ CFL

TO-92

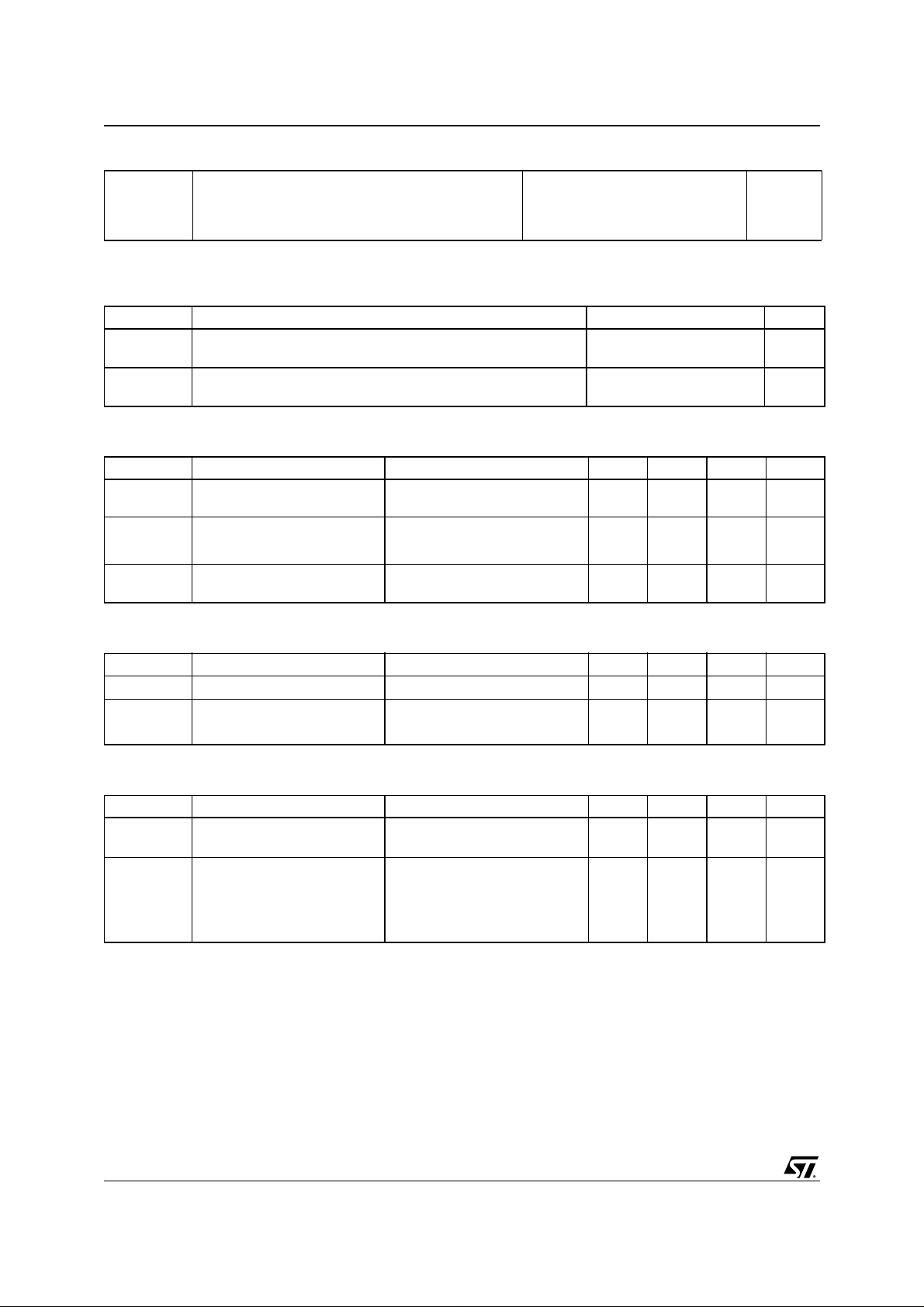

INTERNAL SCHEMATIC DIAGRAM

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

DS

V

DGR

V

GS

I

D

I

D

I

DM

P

TOT

dv/dt(1) Peak Diode Recovery voltage slope 3.5 V/ns

T

stg

T

(•)Pu l se width limited by safe operating area

August 2001

Drain-source Voltage (VGS = 0)

Drain-gate Voltage (RGS = 20 kΩ)

600 V

600 V

Gate- source Voltage ± 30 V

Drain Current (continuos) at TC = 25°C

Drain Current (continuos) at TC = 100°C

(●)

Drain Current (pulsed) 1.6 A

Total Dissipation at TC = 25°C

0.4 A

0.25 A

3.5 W

Derating Factor 0.028 W/°C

Storage Temperature –65 to 150 °C

Max. Operating Junction Temperature 150 °C

j

(1)ISD ≤ 0.4 A, di/dt ≤100A/µs, VDD ≤ V

(BR)DSS

, Tj ≤ T

JMAX.

1/6

Page 2

STQ1HNC60

THERMA L D ATA

Rthj-case

Rthj-amb

Thermal Resistance Junction-case

Thermal Resistance Junction-ambient Max

(Surface Mounted)

T

l

Maximum Lead Temperature For Soldering Purpose

AVALANCHE CHARACTERISTICS

Symbol Parameter Max Value Unit

I

AR

E

AS

Avalanche Current, Repetitive or Not-Repetitive

(pulse width limited by T

max)

j

Single Pulse Avalanche Energy

(starting T

= 25 °C, ID = IAR, VDD = 50 V)

j

ELECTRICAL CHARACTERISTICS (TCASE = 25 °C UNLESS OTHERWISE SPECIFIED)

OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

I

DSS

I

GSS

Drain-source

Breakdown Voltage

Zero Gate Voltage

Drain Current (V

GS

Gate-body Leakage

Current (V

DS

= 0)

= 0)

ID = 250 µA, VGS = 0 600 V

V

= Max Rating

DS

V

= Max Rating, TC = 125 °C

DS

V

= ± 30V ±100 nA

GS

35.7

60

300

0.4 A

100 mJ

1µA

50 µA

°C/W

°C/W

°C

ON

(1)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

V

GS(th)

R

DS(on)

Gate Threshold Voltage

Static Drain-source On

= VGS, ID = 250 µA

DS

= 10V, ID = 0.4 A

V

GS

234V

78Ω

Resistance

DYNAMIC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

g

fs

Forward Transconductance VDS > I

ID= 0.4 A

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance 26 pF

Reverse Transfer

V

DS

Capacitance

x R

D(on)

DS(on)max,

= 25V, f = 1 MHz, VGS = 0

1.25 S

160 pF

3.8 pF

2/6

Page 3

STQ1HNC60

ELECTRICAL CHARACTERISTICS (CONTINUED)

SWITCHING ON

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(on)

t

r

Q

g

Q

gs

Q

gd

Turn-on Delay Time

Rise Time

Total Gate Charge

Gate-Source Charge 2.8 nC

Gate-Drain Charge 2.8 nC

SWITCHING OFF

Symbol Param eter Test Conditions Min. Typ. Max. Unit

t

r(Voff)

t

f

t

c

Off-voltage Rise Time

Fall Time 9 ns

Cross-over Time 34 ns

SOURCE DRAIN DIODE

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

VSD (1)

t

rr

Q

rr

I

RRM

Note: 1. Pulsed: Pul se duration = 30 0 µs, duty cycl e 1.5 %.

2. Pulse width l i m i t ed by safe ope rat i ng area.

(2)

Source-drain Current 0.4 A

Source-drain Current (pulsed) 1.6 A

Forward On Voltage

Reverse Recovery Time

Reverse Recovery Charg e 950 µC

Reverse Recovery Curren t 3.8 A

VDD = 300V, ID = 0.7 A

RG= 4.7Ω, VGS = 10V

(see test circuit, Figure 3)

V

= 480V, ID = 1.4 A,

DD

VGS = 10V, RG=4.7Ω

V

= 480 V, ID = 1.4 A,

DD

RG= 4.7Ω, V

GS

= 10V

(see test circuit, Figure 5)

ISD = 0.4 A, VGS = 0

I

= 1.4 A, di/dt = 100A/µs,

SD

VDD = 100V, Tj = 150°C

(see test circuit, Figure 5)

8ns

8ns

8.5 11.5 nC

25 ns

1.6 V

500 ns

3/6

Page 4

STQ1HNC60

Fig. 2: Unclamped Inductive WaveformFig. 1: Unclamped Inductive Load Test Circuit

Fig. 3: Switching Times Test Circuit For

Resistive Load

Fig. 5: Test Circuit For Inductive Load Switching

And Diode Recovery Times

Fig. 4: Gate Charge test Circuit

4/6

Page 5

TO-92 MECHANICAL DATA

STQ1HNC60

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 4.58 5.33 0.180 0.210

B 4.45 5.2 0.175 0.204

C 3.2 4.2 0.126 0.165

D 12.7 0.500

E1.27 0.050

F 0.4 0.51 0.016 0.020

G0.35 0.14

mm inch

5/6

Page 6

STQ1HNC60

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such informa tion n or for an y infring ement of patent s or other rig hts of third part ies which may resu lt from its use . No l i cen se i s

granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are

subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products

are not authorized for use as critical compo nents in life support devices or systems without express written approval of STMicroelectronics.

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -

The ST logo is a trademark of STMicroelectronics

© 2000 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

6/6

Loading...

Loading...