Page 1

↓

Ordering number: EN 4680B

Thick Film Hybrid IC

STK401-060

AF Power Amplifier (Split Power Supply)

(35W + 35W min, THD = 0.4%)

Overview

The STK401-060 is a thick-film audio power amplifier IC

belonging to a series in which all devices are pin compatible. This allows a single PCB design to be used to construct amplifiers of various output capacity simply by

changing hybrid ICs. Also, this series is part of a new,

larger series that comprises mutually similar devices with

the same pin compatibility. This makes possible the development of a 2-channel amplifier from a 3-channel amplifier using the same PCB. In addition, this new series

features 6/3 Ω drive in order to support the low impedance

of modern speakers.

Features

• Pin compatible

STK400-000 series (3-channel/single package)

STK401-000 series (2-channel/single package)

• Output load impedance R

• New pin configuration

Pin configuration has been grouped into individual

blocks of inputs, outputs and supply lines, minimizing

the adverse effects of pattern layout on operating characteristics.

• Few external components

In comparison with existing series, external bootstrap

resistors and capacitors can be eliminated.

= 6/3 Ω supported

L

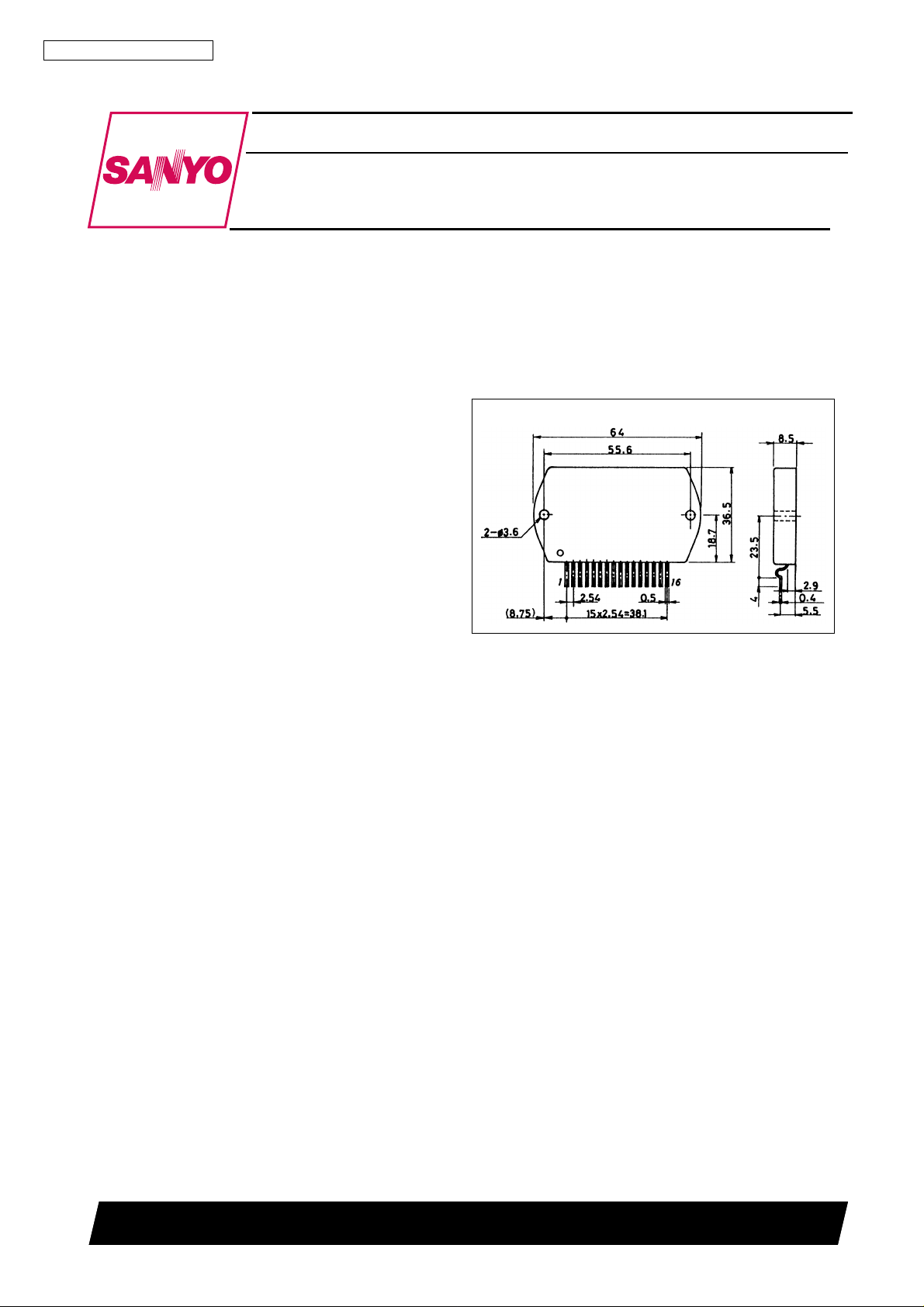

Package Dimensions

unit: mm

4134

[STK401-060]

SANYO Electric Co., Ltd. Semiconductor Business Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

10997HA(ID) / 71696HA(ID) / 41495TH(ID) No. 4680—1/8

Page 2

Specifications

±

θ

°

°

°

−

°

−

STK401-060

Maximum Ratings

at Ta = 25 ° C

Parameter Symbol Conditions Ratings Unit

Maximum supply voltage

Thermal resistance

V

max

CC

j-c Per power transistor 1.8

Junction temperature Tj 150

Operating substrate temperature Tc 125

Storage temperature Tstg

Available time for load short-circuit t

Operating Characteristics

at Ta = 25 ° C, R

V

= ± 28V, R

s

CC

f = 50Hz, P

= 6 Ω (noninductive load), Rg = 600 Ω , VG = 40dB

L

= 6 Ω ,

L

= 35W

O

30 to +125

Parameter Symbol Conditions min typ max Unit

Quiescent current I

P

Output power

P

THD(1)

Total harmonic distortion

THD(2)

Frequency response f

Input impedance r

Output noise voltage V

Neutral voltage V

CCO

(1)

O

(2)

O

, f

L

i

NO

N

H

V

= ± 34V 20 60 100 mA

CC

V

= ± 28V, f = 20Hz to

CC

20kHz, THD = 0.4%

V

= ± 23V, f = 1kHz,

CC

THD = 1.0%, R

V

= ± 28V, f = 20Hz to

CC

20kHz, P

V

= ± 28V, f = 1kHz,

CC

P

= 5.0W

O

V

= ± 28V, P

CC

V

= ± 28V, f = 1kHz,

CC

P

= 1.0W

O

V

= ± 34V, Rg = 10k Ω

CC

V

= ± 34V

CC

= 3 Ω

L

= 1.0W

O

= 1.0W, – 20 to 50k – Hz

O

+0

dB

−

3

35 40 – W

35 40 – W

– – 0.4 %

– 0.01 – %

–55–k

– – 1.2 mVrms

70 0 +70 mV

41 V

C/W

C

C

C

1s

Ω

Notes.

All tests are measured using a constant-voltage supply unless otherwise specified.

Available time for load short-circuit and output noise voltage are measured using the transformer supply specified below.

The output noise voltage is the peak value of an av er age-reading meter with an rms value scale (VTVM). A regulated AC supply (50Hz) should be used to eliminate the

effects of AC primary line flicker noise.

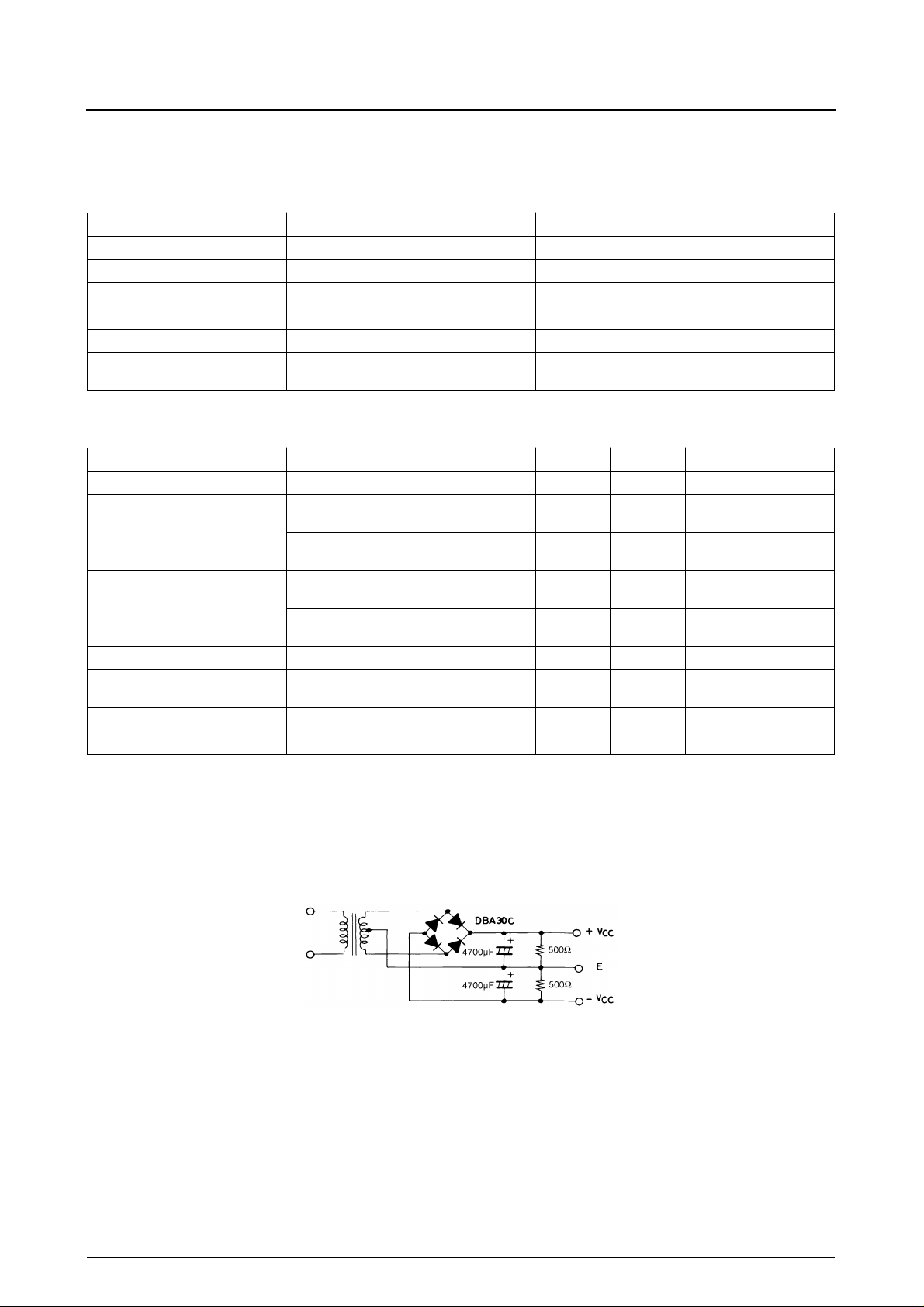

Specified Transformer Supply (RP-25 or Equivalent)

No. 4680—2/8

Page 3

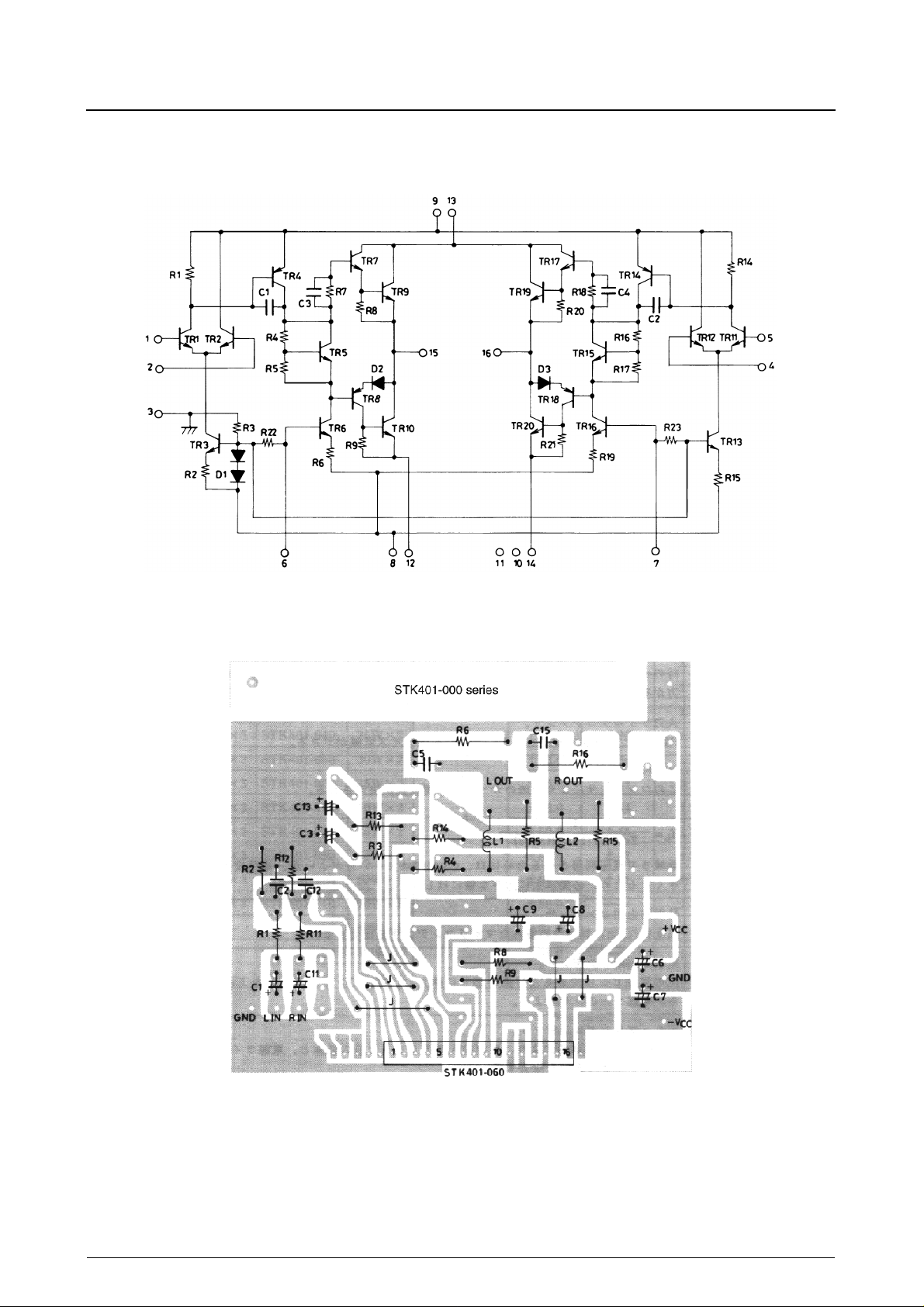

Equivalent Circuit

STK401-060

Sample PCB Layout for 2-Channel or 3-Channel Amplifiers

Pin 6 of STK400-000 series devices corresponds to pin 1 of STK401-000 series devices.

Copper (Cu) foil surface

No. 4680—3/8

Page 4

Sample Application Circuit

STK401-060

Ω

External Component Description

Input coupling capacitors.

For DC blocking. Since capacitor reactance becomes larger at lower frequencies, the output noise can be adversely aff ected b y signal source

C1, C11

C2, C12

C3, C13

C5, C15

C6, C7

C8, C9

R1, R11 Input filter resistors.

R2, R12

R3, R13

R4, R14

R5, R15 Oscillation prevention resistors.

R6, R16

R8, R9

L1, L2

resistance-dependent 1/f noise. In this case, a lower reactance value should be chosen. In order to remove pop noise at power-on, larger

values of capacitance should be chosen for C1 and C11, which determine the input time constant, and smaller values for C3 and C13 in the

NF circuit.

Input filter capacitors.

These, together with R1 and R11, form filters to reduce high-frequency noise.

NF capacitors.

These determine the low-side cut-off frequency.

f

-----------------------------------------------------------------=

L

2 π C3 C13

Large values should be chosen for C3 and C13 to maintain voltage gain at lo w frequencies. Howev er , because this w ould tend to increase the

shock noise at power-on, values larger than absolutely necessary should be avoided.

Oscillation prevention capacitors.

Mylar capacitors are recommended for their excellent thermal and frequency characteristics.

Oscillation prevention capacitors.

These should be inserted as close as possible to the IC supply pins to reduce supply impedance and hence provide stable IC operation.

Electrolytic capacitors are recommended.

Decoupling capacitors.

These, together with R8 and R9, form time constant circuits that remove shock noise and ripple voltage from the supply, preventing any noise

being coupled to the inputs.

Input bias resistors.

These are used to bias the input pins at zero potential. The input impedance is largely determined by this resistance.

Voltage-gain VG setting resistors.

VG = 40dB is recommended using R3, R13 = 560

adjustments are made using R4 and R14, then set R2, R12 = R4, R14 to maintain V

Oscillation prevention resistors.

The power dissipated in these resistors is dependent on the frequency, as given below.

R6(R16)

P

where f is the output signal frequency upper limit.

Ripple filter resistors.

P

max, ripple rejection and supply power-on shock noise are all affected by this resistance. These resistors should be chosen taking into

O

consideration both the function they perform as predriver transistor limiting resistors during load short circuits and the peak current that flows

through them when charging C8 and C9.

Oscillation prevention coils.

These correct the phase difference caused by capacitive loads and increase stability against oscillation.

1

() R

---------------------------------------------------------------------------

=

12 π f ⁄ C5 C15

R

()××

3

V

CC

13

max 2

()×

, and R4, R14 = 56k Ω . Gain adjustments are best made using R3 and R13. If gain

⁄

+

R

2

6

16

R

×

R

()

6

16

R

()

balance stability.

N

No. 4680—4/8

Page 5

Series Configuration

STK401-060

3-channel

amplifier type

Nos.

Rated

output

STK400-010 10W × 3 STK401-010 10W × 2

2-channel

amplifier type

Nos.

Rated

output

THD [%]

f = 20Hz to 20kHz

V

max1 V

CC

–

STK400-020 15W × 3 STK401-020 15W × 2–

1. V

STK400-030 20W

STK400-040 25W

STK400-050 30W

STK400-060 35W

STK400-070 40W

STK400-080 45W

STK400-090 50W

STK400-100 60W

STK400-110 70W

– – STK401-120 80W × 2

– – STK401-130 100W × 2

– – STK401-140 120W × 2

max1 (R

CC

= 6 Ω ), V

L

× 3 STK401-030 20W × 2–

× 3 STK401-040 25W × 2–

× 3 STK401-050 30W × 2–

× 3 STK401-060 35W × 2–

× 3 STK401-070 40W × 2–

× 3 STK401-080 45W × 2–

0.4

× 3 STK401-090 50W × 2–

×

3 STK401-100 60W × 2–

×

3 STK401-110 70W × 2

max2 (R

CC

= 3 to 6 Ω ), V

L

CC

1 (R

= 6 Ω ), V

L

CC

2 (R

= 3 Ω )

L

±

56.0 –

±

61.0 –

±

65.0 –

±

74.0 –

Supply voltage [V]

max2 V

CC

±

±

±

±

±

±

±

±

±

51

1

1V

CC

17.5

± 20

± 23

± 25

± 26

± 28

± 30

± 31

± 32

±

35

±

38 –

±

42 –

±

45 –

±

51 –

Sample Designs using a Common PCB

CC

14

± 16

± 19

± 21

± 22

± 23

± 24

± 25

26

±

±

27

2

± 26 ±

±

29

34

36

39

41

44

45

47

No. 4680—5/8

Page 6

External Circuit Diagram

STK401-060

Heatsink Design Considerations

The heatsink thermal resistance, θc-a, required to dissipate

the STK401-060 device total power dissipation, Pd, is

determined as follows:

Condition 1: IC substrate temperature not to exceed

125°C.

Pd × θc-a + Ta < 125°C........................................ (1)

where Ta is the guaranteed maximum ambient temperature.

Condition 2: Power transistor junction temperature, Tj, not

to exceed 150°C.

Pd × θc-a + Pd/N × θj-c + Ta < 150°C.................(2)

where N is the number of power transistors and θj-c is the

power transistor thermal resistance per transistor. Note

that the power dissipated per transistor is the total, Pd,

divided evenly among the N power transistors.

Expressions (1) and (2) can be rewritten making θc-a the

subject.

θc-a < (125 − T a)/Pd............................................. (1)′

θc-a < (150 − T a)/Pd − θj-c/N .............................. (2)′

The heatsink required must have a thermal resistance that

simultaneously satisfies both expressions.

The heatsink thermal resistance can be determined from

(1)′ and (2)′ once the following parameters have been

defined.

• Supply voltage, V

• Load resistance, R

CC

L

• Guaranteed maximum ambient temperature, Ta

The total device power dissipation when STK401-060

VCC = ±28V and RL = 6Ω, for a continuous sine wave signal, is a maximum of 54W, as shown in Figure 1.

When estimating the power dissipation for an actual audio

signal input, the rule of thumb is to select Pd corresponding to 1/10 PO max (within safe limits) for a continuous

sine wave input. For example, from Figure 1,

Pd = 32.4W (for 1/10 PO max = 3.5W)

The STK401-060 has 4 power transistors, and the thermal

resistance per transistor, θj-c, is 1.8°C/W. If the guaranteed maximum ambient temperature, Ta, is 50°C, then the

required heatsink thermal resistance, θc-a, is:

From expression (1)′: θc-a < (125 − 50)/32.4

< 2.31

From expression (2)′: θc-a < (150 − 50)/32.4 − 1.8/4

< 2.63

Therefore, to satisfy both expressions, the required heatsink must have a thermal resistance less than 2.31°C/W.

No. 4680—6/8

Page 7

STK401-060

Similarly, when STK401-060 VCC = ±23V and RL = 3Ω,

from Figure 2:

Pd = 38W (for 1/10 PO max = 3.5W)

From expression (1)′: θc-a < (125 − 50)/38

< 1.97

From expression (2)′: θc-a < (150 − 50)/38 − 1.8/4

< 2.18

Figure 1. Pd — P

O

Therefore, to satisfy both expressions, the required heatsink must have a thermal resistance less than 1.97°C/W.

This heatsink design example is based on a constant-voltage supply, and should be verified within your specific set

environment.

Figure 2. Pd — P

O

THD — P

PO — V

O

IN

THD — P

PO — f

O

No. 4680—7/8

Page 8

STK401-060

PO — V

CC

VG — f I

VG — f

CCO

, VN — Tc

I

, VN — V

CCO

■

No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear

CC

power control systems, vehicles, disaster/crime-pre v ention equipment and the lik e, the failure of which may directly or indirectly cause injury,

death or property loss.

■

Anyone purchasing any products described or contained herein for an above-mentioned use shall:

➀

Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their

officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated

with such use:

➁

Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO.,

LTD., its affiliates, subsidiaries and distributors or any of their officers and employees, jointly or severally.

■

Information (including circuit diagrams and circuit parameters) herein is for e xample only; it is not guaranteed for volume production. SANYO

believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of

intellectual property rights or other rights of third parties.

This catalog provides information as of January, 1997. Specifications and information herein are subject to change without notice.

No. 4680—8/8

Loading...

Loading...