Page 1

Overview

Now, thick-film audio power amplifier ICs are available

with pin-compatibility to permit a single PCB to be

designed and amplifier output capacity changed simply by

installing a hybrid IC. This new series was developed

with this kind of pin-compatibility to ensure integration

between systems everywhere. With this new series of IC,

even changes from 3-channel amplifier to 2-channel

amplifiers is possible using the same PCB. In addition,

this new series of ICs has a 6/3Ω drive in order to support

the low impedance of modern speakers.

Features

• Pin-compatible

STK400-000 series (3-channel/single package)

STK401-000 series (2-channel/single package)

• Output load impedance RL=6Ω/3Ω supported

• New pin arrangement

To simplify input/output pattern layout and minimize

the effects of pattern layout on operational

characteristics, pin assignments are grouped into blocks

consisting of input, output and power systems.

• Few external circuits

Compared to those series used until now, boot-strap

capacitors and boot-strap resistors for external circuits

can be greatly reduced.

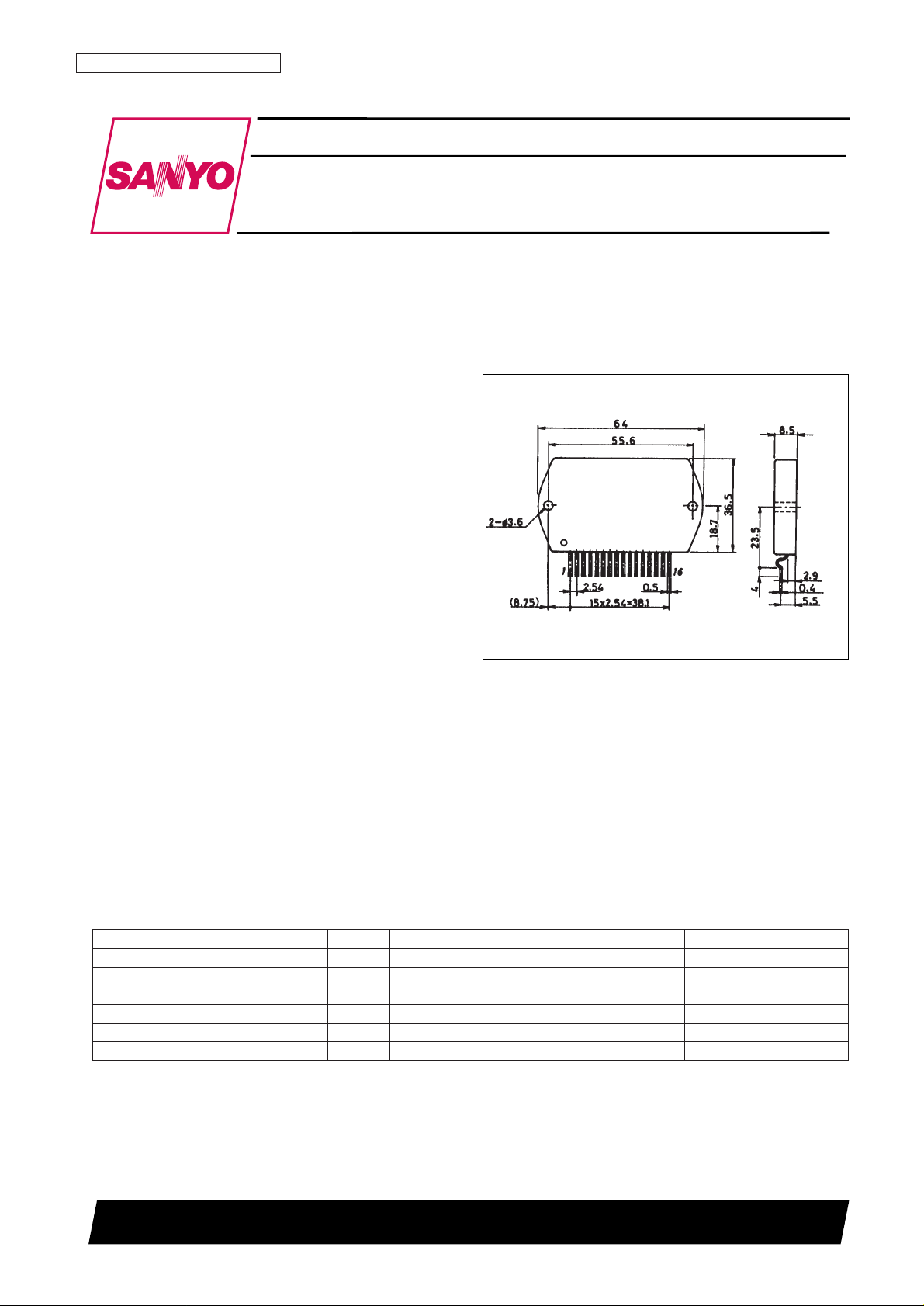

Package Dimensions

unit: mm

4134

Thick Film Hybrid IC

D3096HA(OT)/31293YO (OT) No. 4343-1/9

[STK401-050]

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

AF Power Amplifier (Split Power Supply)

(30 W + 30 W min, THD = 0.4%)

STK401-050

Ordering number : EN4343A

➙

Specifications

Maximum Ratings at Ta = 25°C

Parameter Symbol Conditions Ratings Unit

Maximum supply voltage V

CC

max ±39 V

Thermal resistance

θj-c Per power transistor 1.8 °C/W

Junction temperature Tj 150 °C

Operating substrate temperature Tc 125 °C

Storage temperature range Tstg –30 to +125 °C

Available time for load short-circuit t

s

V

CC

= ±26 V, RL = 6 Ω, f = 50 Hz, PO = 30 W 1 s

Page 2

No. 4343-2/9

STK401-050

Parameter Symbol Conditions

Ratings

Unit

min typ max

Quiescent current I

CCO

VCC=± 31 V 20 60 100 mA

Output power

P

O

(1) VCC= ±26 V, f = 20 Hz to 20 kHz, THD = 0.4% 30 35 W

P

O

(2) VCC= ±22 V, f = 1 kHz, THD = 1.0%, RL= 3 Ω 30 35 W

Total harmonic distortion

THD (1) V

CC

= ±26 V, f = 20 Hz to 20 kHz, PO= 1.0 W 0.4 %

THD (2) V

CC

= ±26 V, f = 1 kHz, PO= 5.0 W 0.01 %

Frequency response f

L

, fHVCC= ±26 V, PO= 1.0 W, dB

20 to 50 k

Hz

Input impedance r

i

VCC= ±26 V, f = 1 kHz, PO= 1.0 W 55 kΩ

Output noise voltage V

NOVCC

= ±31 V, Rg = 10 kΩ 1.2 mVrms

Neutral voltage V

N

VCC= ±31 V –70 0 +70 mV

+0

–3

Operating Characteristics at Ta = 25°C, RL= 6Ω, Rg = 600Ω, VG = 40dB, RL(non-inductive)

Notes

• Use rated power supply for test unless otherwise specified.

• When measuring available time for load short-circuit and output noise voltage use transformer power supply indicated

below.

• Output noise voltage is represented by the peak value rms (VTVM) for mean reading. Use an AC stabilized power

supply (50 Hz) on the primary side to eliminate the effect of AC flicker noise.

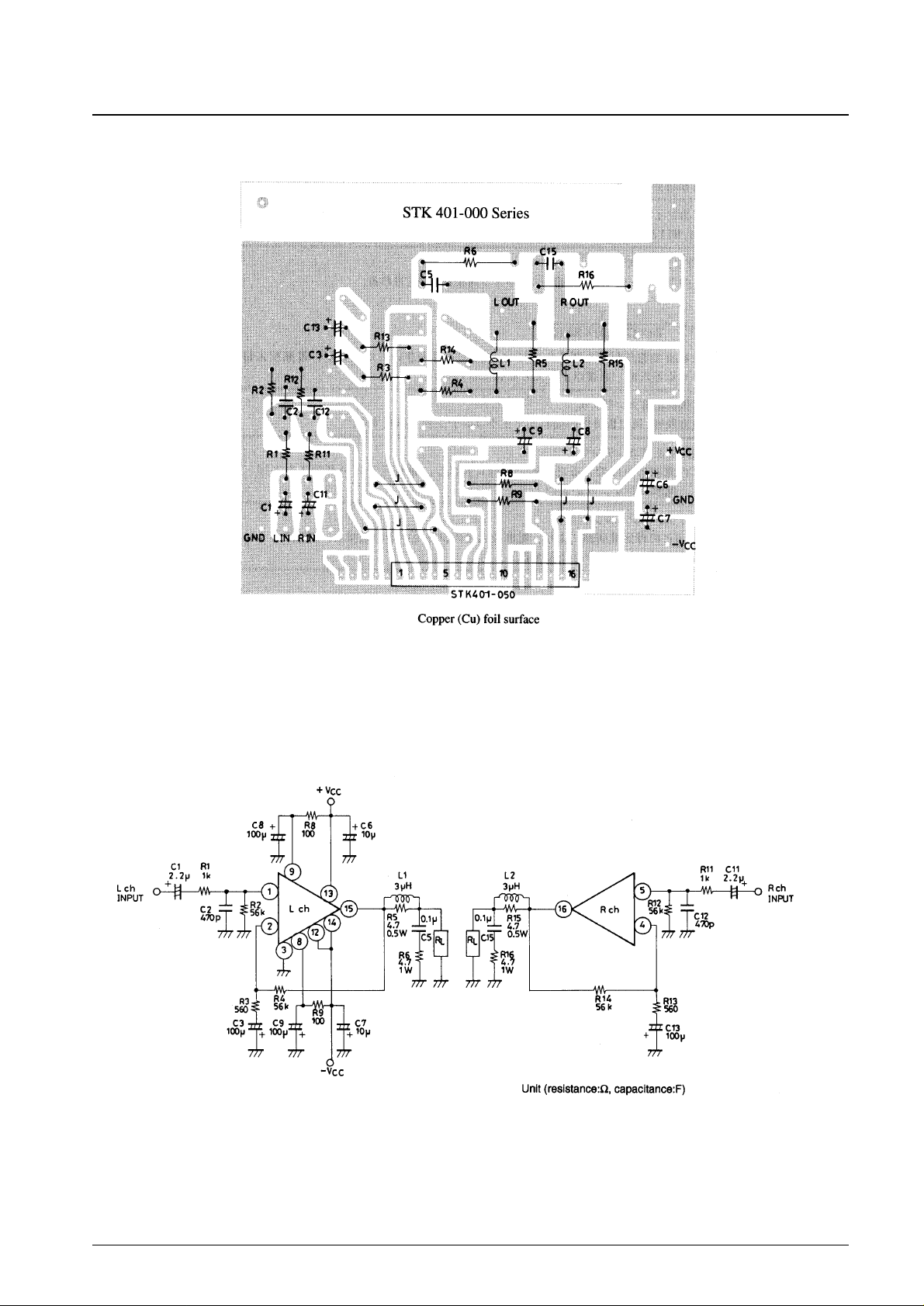

Unit (resistance:Ω, capacitance:F)

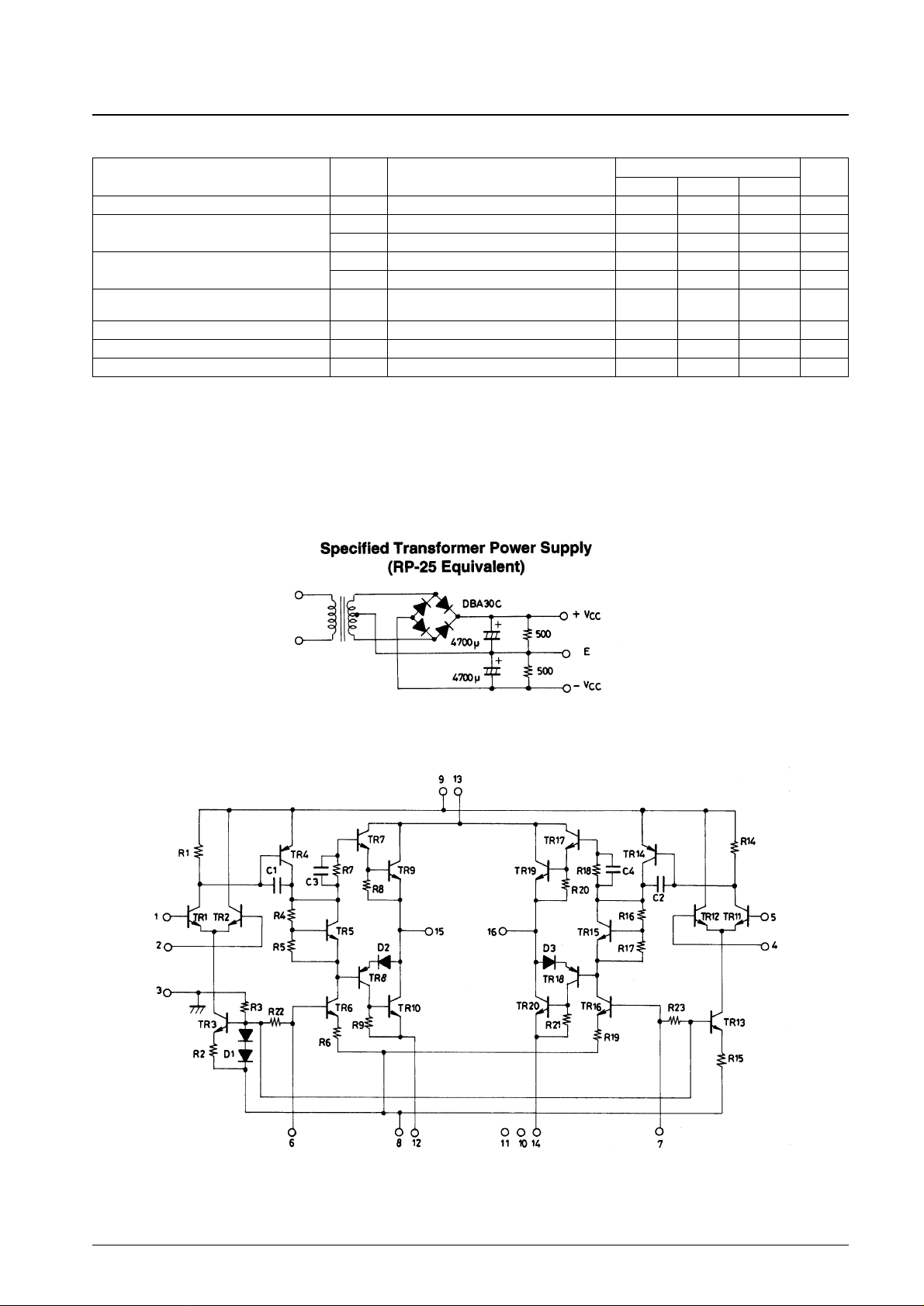

Internal Equivalent Circuit

Page 3

Pattern Example for PCB used with either 2- or 3-channel Amplifiers.

With the STK401-000 series, the 6 pin corresponds to the 1 pin with respect to the

STK400-000 series.

Sample Application Circuit

No. 4343-3/9

STK401-050

Page 4

No. 4343-4/9

STK401-050

Description of External Circuits

C1, 11 For input coupling capacitor. Used for DC current blocking. When capacitor reactance with low

frequency is increased, the reactance value should be reduced in order to reduce the output

noise from the signal resistance dependent 1/f noise. In response to the popping noise which

occurs when the system power is turned on, C1 and C11 which determine the decay time

constant on the input side are increased while C3 and C13 on the NF side are decreased.

C2, 12 For input filter capacitor. Permits high-region noise reduction by utilizing filter constructed with

R1 and R11.

C3, 13 For NF capacitor. This capacitor determines the decline of the cut-off frequency and is

calculated according to the following equation.

f

L

=

1

2π X C3 (13) X R3 (13)

For the purpose of achieving voltage gains prior to reduction, it is best that C3 and C13 are large.

However, because the shock noise which occurs when the system power is turned on tends to

increase, values larger than those absolutely necessary should be avoided.

C5, 15 For oscillation prevention capacitor. A Mylar capacitor with temperature and frequency features

is recommended.

C6, 7 For oscillation prevention capacitor. To ensure safe IC functioning, the capacitor should be

installed as close as possible to the IC power pin to reduce power impedance. An electrolytic

capacitor is good.

C8, 9 For decoupling capacitor. Reduces shock noise during power up using decay time constant

circuits with R8 and R9 and eliminates components such as ripples crossing over into the input

side from the power line.

R1, 11 For input filter applied resistor.

R2, 12 For input bias resistor. The input pin is biased to zero potential. Input impedance is mostly

decided with this resistance value.

R3, 13, 4, 14

For resistors to determine voltage gain (VG). We recommend a VG = 40 dB using R3 and R13 =

560Ω and R4 and R14 = 56Ω. VG adjustments are best performed using R3 and R13. When

using R4 and R14 for such purposes, R4 and R14 should be set to equal R2 and R12 in order to

establish a stable V

N

balance.

R5, 15 For oscillation prevention resistor.

R6, 16 For oscillation prevention resistor. This resistor’s electrical output resides in the signal frequency

and is calculated according to the following formula.

P R6 (16) =

(

VCCmax/√2

)

2

X R6 (16)

1/2π fC5 (15) + R6 (16)

f = output signal frequency upper limit

R8, 9 For ripple filter applied resistor. P

O

max, ripple rejection and power-up shock noise are modified

according to this value. Set the electrical output of these resistors while keeping in mind the flow

of peak current during recharging to C8 and C9 which function as pre-drive TR control resistors

during load shorts.

L1, 2 For oscillation prevention coil. Compensates

phase dislocation caused by load capacitors

and ensures stable oscillation.

Page 5

No. 4343-5/9

STK401-050

Series Configuration

VCCmax1 VCCmax2 VCC1 VCC2

STK400-010 10W X 3 STK401-010 10W X 2 — ±27 ±18 ±14

STK400-020 15W X 3 STK401-020 15W X 2 — ±29 ±20 ±16

STK400-030 20W X 3 STK401-030 20W X 2 — ±34 ±23 ±19

STK400-040 25W X 3 STK401-040 25W X 2 — ±36 ±25 ±21

STK400-050 30W X 3 STK401-050 30W X 2 — ±39 ±26 ±22

STK400-060 35W X 3 STK401-060 35W X 2 — ±41 ±28 ±23

STK400-070 40W X 3 STK401-070 40W X 2

0.4

— ±44 ±30 ±24

STK400-080 45W X 3 STK401-080 45W X 2 — ±45 ±31 ±25

STK400-090 50W X 3 STK401-090 50W X 2 — ±47 ±32 ±26

STK400-100 60W X 3 STK401-100 60W X 2 — ±51 ±35 ±27

STK400-110 70W X 3 STK401-110 70W X 2 ±56.0 — ±38 —

— — STK401-120 80W X 2 ±61.0 — ±42 —

— — STK401-130 100W X 2 ±65.0 — ±45 —

— — STK401-140 120W X 2 ±74.0 — ±51 —

V

CC

max1 RL= 6Ω

VCCmax2 RL= 6Ω to 3Ω

V

CC

1 RL= 6Ω

VCC2 RL= 3Ω

Example of Set Design for Common PCB

Supply voltage [V]

3ch Amp

IC Name

Fixed

Standard

Output

2ch Amp

IC Name

Fixed

Standard

Output

THD [%]

f = 20 to 20kHz

Page 6

External Circuit Diagram

Heat Radiation Design Considerations

The radiator thermal resistance θc-a required for total substrate power dissipation Pd in the STK401-050 is determined as:

Condition 1: IC substrate temperature Tc not to exceed 125°C.

Pd x θc-a+Ta <125°C ······························· (1)

where Ta is set assured ambient temperature.

Condition 2: Power transistor junction temperature Tj not to exceed 150°C.

Pd x θc-a+Pd/N x θj-c+Ta<150°C·············(2)

where N is the number of power transistors and θj-c is the thermal resistance per power transistor chip

.

However, power transistor power consumption is Pd equally divided by N units.

Expressions (1) and (2) can be rewritten based on θc-a to yield:

θc-a<(125–Ta)/Pd······································(1)'

θc-a<(150–Ta)/Pd–θj-c/N··························(2)'

The required radiator thermal resistance will satisfy both of these expressions.

From expressions (1)' and (2)', the required radiator thermal resistance can be determined once the following

specifications are known:

• Supply voltage V

CC

• Load resistance R

L

• Assured ambient temperature Ta

The total substrate power consumption when STK401-050 VCCis ±26 V and RLis 6 Ω, for a continuous sine wave

signal, is a maximum of 45.7W (Fig. 1). In general, when this sort of continuous signal is used for estimation of power

consumption, the Pd used is 1/10th of POmax (slight variation depending on safety standard).

Pd=27.7W (1/10 POmax=during 3W)

No. 4343-6/9

STK401-050

Page 7

The STK401-050 has four power transistors, so the thermal resistance per transistor θj-c is 1.8°C / W. With an assured

ambient temperature Ta of 50°C, the required radiator thermal resistance θc-a would be:

From expression (1)' θc-a <(125–50)/27.7

<2.70

From expression (2)' θc-a <(150–50)/27.7–1.8/4

<3.16

To satisfy both, 2.70°C/W is the required radiator thermal resistance.

Figure 2 illustrates Pd - POwhen the VCCof STK401-050 is ±22V and RLis functioning at 3Ω.

Pd = 33.5W (1/10 POmax = during 3W)

From expression (1)' θc-a <(125–50)/33.5

<2.23

From expression (2)' θc-a <(150-50)/33.5–1.8/4

<2.53

To satisfy both, 2.23°C / W is the required radiator thermal resistance. This design example is based on a fixed voltage

supply, and will require verification within your specific set environment.

No. 4343-7/9

STK401-050

Page 8

No. 4343-8/9

STK401-050

Page 9

No. 4343-9/9

STK401-050

This catalog provides information as of July, 1997. Specifications and information herein are subject to change

without notice.

■ No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace

equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of

which may directly or indirectly cause injury, death or property loss.

■ Anyone purchasing any products described or contained herein for an above-mentioned use shall:

➀ Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and

distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all

damages, cost and expenses associated with such use:

➁ Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on

SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees

jointly or severally.

■ Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for

volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied

regarding its use or any infringements of intellectual property rights or other rights of third parties.

Loading...

Loading...