Page 1

STD35NF3LL

STD35NF3LL-1

N-CHANNEL 30V - 0.014 Ω - 35A IPAK/DPAK

STripFET™ II POWER MOSFET

TYPE

STD35NF3LL

STD35NF3LL-1

■ TYPICAL R

■ OPTIMAL R

■ CONDUCTION LOSSES REDUCED

■ SWITCHING LOSSES REDUCED

■ LOW THRESHOLD DRIVE

■ THROUGH-HOLE IPAK (TO-251) POWER

DS

DS

V

DSS

30 V

30 V

(on) = 0.016 Ω @ 4.5V

(on) x Qg TRADE-OFF @ 4.5V

R

DS(on)

< 0.0195

< 0.0195

I

D

35 A

Ω

35 A

Ω

PACKAGE IN TUBE (SUFFIX “- 1 ")

■ SURFACE-MOUNTING DPAK (TO-252)

POWER PACKAGE IN TAPE & REEL

(SUFFIX “T4")

DESCRIPTION

This application specific Power MOSFET is the third

genaration of STMicro electronis unique "Single Feature

Size™" strip-based process. The resulting transistor

shows the best trade-off between on-resistance and gate

charge. When used as high and low side in buck

regulators, it gives the be st perfor manc e in terms of both

conduction and switching losses. This is extremely

important for motherboards where fast switching and

high efficiency are of paramount importance.

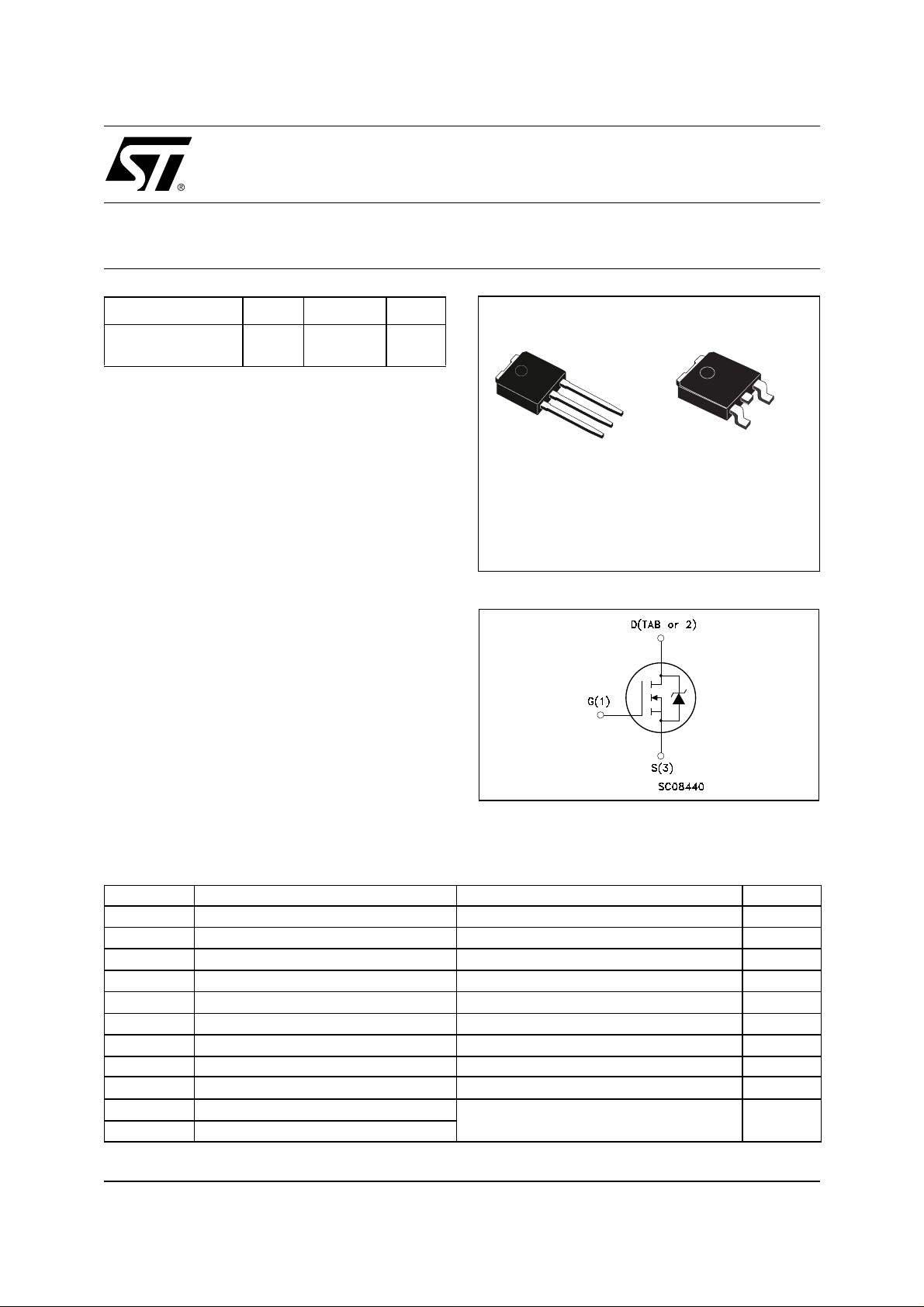

3

2

1

IP AK

TO-251

(Suffix “-1”)

DPAK

TO-252

(Suffix “T4”)

INTERNAL SCHEMATIC DIAGRAM

3

1

APPLICATIONS

■ SPECIFICALL Y D ESIGNED AND OP TIMISED

FOR HIGH EFFICIENCY DC/DC

CONVERTERS

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

DS

V

DGR

V

GS

I

D

I

D

(

I

DM

P

tot

E

AS

T

stg

T

j

(

Pulse width limited by safe operating area. (1) Starting Tj = 25 oC, ID = 17.5 A, VDD= 24 V

•)

.

Drain-source Voltage (VGS = 0)

Drain-gate Voltage (RGS = 20 kΩ)

30 V

30 V

Gate- source Voltage ± 16 V

Drain Current (continuos) at TC = 25°C

Drain Current (continuos) at TC = 100°C

•)

Drain Current (pulsed) 140 A

Total Dissipation at TC = 25°C

35 A

25 A

50 W

Derating Factor 0.33 W/°C

(1)

Single Pulse Avalanche Energy 300 mJ

Storage Temperature

Max. Operating Junction Temperature

-55 to 175 °C

1/10February 2002

Page 2

STD35NF3LL/STD35NF3LL-1

THERMA L D ATA

Rthj-case

Rthj-amb

T

Thermal Resistance Junction-case

Thermal Resistance Junction-ambient

Maximum Lead Temperature For Soldering Purpose

l

Max

Max

Typ

3

100

300

°C/W

°C/W

°C

ELECTRICAL CHARACTERISTICS (T

= 25 °C unless otherwise specified)

case

OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

V

(BR)DSS

Drain-source

= 250 µA, VGS = 0

D

30 V

Breakdown Voltage

V

= Max Rating

DS

V

= Max Rating TC = 100°C

DS

V

= ± 16 V

GS

1

10

±100 nA

ON

(*)

I

DSS

I

GSS

Zero Gate Voltage

Drain Current (V

GS

Gate-body Leakage

Current (V

DS

= 0)

= 0)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

V

GS(th)

R

DS(on)

Gate Threshold Voltage

Static Drain-source On

Resistance

= VGS I

DS

= 10 V ID = 17.5 A

V

GS

V

= 4.5 V ID = 17.5 A

GS

= 250 µA

D

1V

0.014

0.016

0.0195

0.0215

DYNAMIC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

(*)

g

fs

C

iss

C

oss

C

rss

Forward Transconductance

Input Capacitance

Output Capacitance

Reverse Transfer

Capacitance

V

=15 V ID= 17.5 A

DS

= 25V, f = 1 MHz, VGS = 0

V

DS

19 S

800

250

60

µA

µA

Ω

Ω

pF

pF

pF

2/10

Page 3

STD35NF3LL/STD35NF3LL-1

ELECTRICAL CHARACTERISTICS (continued)

SWITCHING ON

Symbol Parameter Test Conditions Min. Typ. Max. Unit

= 15 V ID = 17.5 A

t

d(on)

Turn-on Delay Time

t

r

Rise Time

V

DD

R

= 4.7 Ω VGS = 4.5 V

G

(Resistive Load, Figure 3)

Q

g

Q

gs

Q

gd

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

= 24 V ID = 35 A VGS= 5V

V

DD

SWITCHING OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

= 15 V ID = 17.5 A

t

d(off)

Turn-off Delay Time

t

f

Fall Time

V

DD

R

= 4.7 Ω V

G

GS

= 4.5 V

(Resistive Load, Figure 3)

SOURCE DRAIN DIODE

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

V

SD

t

rr

Q

rr

I

RRM

(*)

Pulsed: P ul se duration = 300 µs, duty cycle 1.5 %.

(

•)Pulse width limited by s afe operating area.

Source-drain Current

(•)

Source-drain Current (pulsed)

(*)

Forward On Voltage

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

I

= 35 A VGS = 0

SD

= 35 A di/dt = 100A/µs

I

SD

V

= 15 V Tj = 150°C

DD

(see test circuit, Figure 5)

17

100

12.5

4.2

5.2

20

21

35

44

2.5

17 nC

35

140

1.3 V

ns

ns

nC

nC

ns

ns

A

A

ns

nC

A

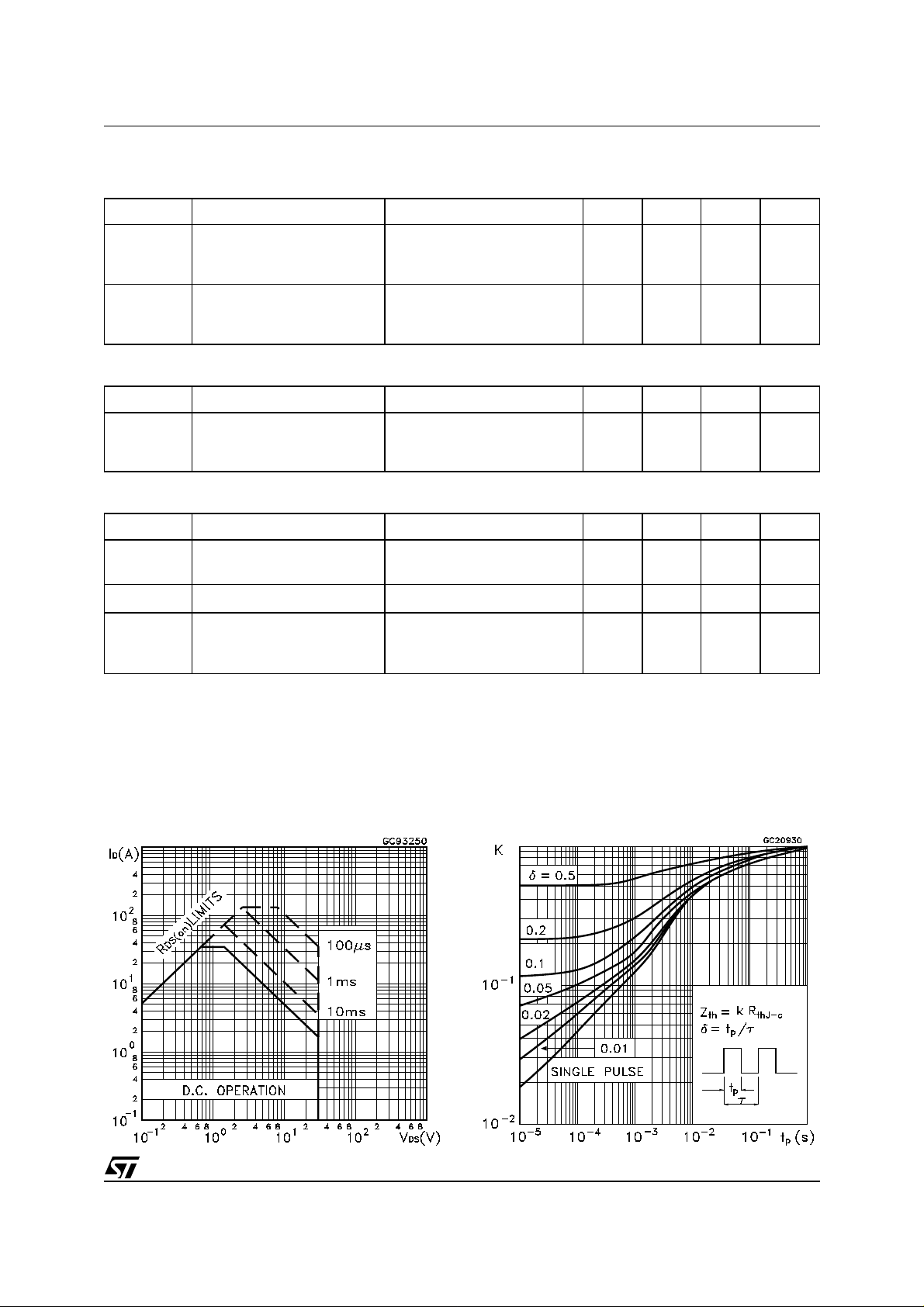

Safe Operating Area

Thermal Impedance

3/10

Page 4

STD35NF3LL/STD35NF3LL-1

Output Characteristics Transfer Characteristics

Transconductance Static Drain-source On Resistance

Gate Charge vs Gate-source Voltage Capacitance Variations

4/10

Page 5

STD35NF3LL/STD35NF3LL-1

Normalized Gate Threshold Voltage vs Temperature Normalized on Resistance vs Temperature

Source-drain Diode Forward Characteristics Normalized Breakdown Voltage vs Temperature.

. .

. .

5/10

Page 6

STD35NF3LL/STD35NF3LL-1

Fig. 1: Unclamped Inductive Load Test CircuitFig. 1: Unclamped Inductive Load Test Circuit Fig. 2: Unclamped Inductive Waveform

Fig. 3: Switching Times Test Circuits For Resistive

Load

Fig. 5: Test Circuit For Inductive Load Switching

And Diode Recovery Times

Fig. 4: Gate Charge test Circuit

6/10

Page 7

STD35NF3LL/STD35NF3LL-1

TO-251 (IPAK) MECHANI CAL DAT A

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.2 2.4 0.086 0.094

A1 0.9 1.1 0.035 0.043

A3 0.7 1.3 0.027 0.051

B 0.64 0.9 0.025 0.031

B2 5.2 5.4 0.204 0.212

B3 0.85 0.033

B5 0.3 0.012

B6 0.95 0.037

C 0.45 0.6 0.017 0.023

C2 0.48 0.6 0.019 0.023

D 6 6.2 0.236 0.244

E 6.4 6.6 0.252 0.260

G 4.4 4.6 0.173 0.181

H 15.9 16.3 0.626 0.641

L 9 9.4 0.354 0.370

L1 0.8 1.2 0.031 0.047

L2 0.8 1 0.031 0.039

A

C2

L2

E

B2

= =

= =

H

C

A3

A1

B6

L

B

B5

G

= =

D

B3

2

1 3

L1

0068771-E

7/10

Page 8

STD35NF3LL/STD35NF3LL-1

TO-252 (DPAK) MECHANICAL DATA

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.2 2.4 0.086 0.094

A1 0.9 1.1 0.035 0.043

A2 0.03 0.23 0.001 0.009

B 0.64 0.9 0.025 0.035

B2 5.2 5.4 0.204 0.212

C 0.45 0.6 0.017 0.023

C2 0.48 0.6 0.019 0.023

D 6 6.2 0.236 0.244

E 6.4 6.6 0.252 0.260

G 4.4 4.6 0.173 0.181

H 9.35 10.1 0.368 0.397

L2 0.8 0.031

L4 0.6 1 0.023 0.039

A

C2

L2

E

B2

==

H

DETAIL "A"

D

==

C

B

2

1 3

L4

A1

G

==

A2

DETAIL "A"

0068772-B

8/10

Page 9

STD35NF3LL/STD35NF3LL-1

DPAK FOOTPRINT

All dimensions are in millimeters

TAPE AND REEL SHIPMENT (suffix ”T4”)*

TUBE SHIPMENT (no suffix)*

All dimensions

are in millimeters

REEL MECHANICAL DATA

DIM.

A 330 12.992

B 1.5 0.059

C 12. 8 13.2 0.504 0.520

D 20. 2 0.795

G 16.4 18.4 0.645 0.724

N 50 1.968

T 22.4 0.881

mm inch

MIN. MAX. MIN. MAX.

TAPE MECHANICAL DATA

DIM.

A0 6.8 7 0.267 0.275

B0 10.4 10.6 0.409 0.417

B1 12.1 0.476

D 1.5 1.6 0.059 0.063

D1 1.5 0.059

E 1.65 1.85 0.065 0.073

F 7.4 7.6 0.291 0.299

K0 2.55 2.75 0.100 0.108

P0 3.9 4.1 0.153 0.161

P1 7.9 8.1 0.311 0.319

P2 1.9 2.1 0.075 0.082

R 40 1.574

W 15.7 16.3 0.618 0.641

*on sales ty pe

mm inch

MIN. MAX. MIN. MAX.

BASE QTY BULK QTY

1000 1000

9/10

Page 10

STD35NF3LL/STD35NF3LL-1

Information furnished is believed to be ac curate and reli able. Howev er, STMicroel ectronics assumes no resp onsibility for the cons equences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implic ation or otherwise under any patent or patent rights of STMi croelectr onics. Sp ecifications mentioned in thi s publicati on are subject

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not

authorized for use as cri tical comp onents in life support dev i ces or systems wi thout express written approval of STMicroel ectronics.

The ST log o i s registered trademark of STMicroelectronics

2002 STMi croelectr onics - All Rights Rese rved

All other names are the property of their resp ective owner s.

Australi a - Brazil - Canada - Chin a - F i nl and - Franc e - Germany - Hong Kong - India - Israel - Italy - Japan - M al aysia - Malta - Morocco -

Singapor e - S pai n - Sweden - S witzerland - United Kingdom - United States.

STMicroelect ro n ics GRO UP OF COMPANI ES

http://www.st.com

10/10

Loading...

Loading...