Datasheet SST58LD008-70-C-P1H, SST58SD192-70-C-P1H, SST58SD128-70-C-P1H, SST58SD096-70-C-P1H, SST58SD064-70-C-P1H Datasheet (Silicon Storage Technology)

...Page 1

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

8MB / 16MB / 24MB / 32MB / 48MB / 64MB / 96MB / 128MB / 192MB

SST58SD/LDxxxATA-Disk Chip

FEATURES:

• ATA/IDE standard interface

– 512 Bytes per sector

– ATA command set compatible

– Support Data Transfer Speed up to PIO Mode-4

• 8, 16, 24, 32, 48, 64, 96, 128, and 192 MByte

capacities

• 600 mil 32-pin DIP package

• Single Voltage Read and Write Operation

– 5.0V-only for SST58SDxxx

– 3.3V-only for SST58LDxxx

• Supports 5.0-Volt or 3.3-Volt Read and Write

– 4.5-5.5V or 3.135-3.465V for Commercial

• Low Power Consumption

– Active mode: 35 mA/55 mA (3.3V/5.0V)(typical)

– Sleep mode: 100 µA/150 µA (3.3V/5.0V)(typical)

• Extended Data Protection and Security

– WP# pin for Dat a Protection

– Factory-Programmed, 20-Byte Unique ID number

• Sustained Write Performance

– Up to 1.4 MB/sec (host to flash)

Data Sheet

• Controller Overhead Command to DRQ

– Less than 0.5 ms

• Zero Power Data Retention

– Batteries not required for data storage

•Start Up Time

– Sleep to read: 200 ns (typical)

– Sleep to write: 200 ns (typical)

– Power-on to Ready:200 ms (typical)

• Support for Commercial Temperature Range

– 0°C to +70°C for Operating Commercial

– -50°C to +100°C for non-Operating (storage)

• Extremely Rugged and Reliable

– Built-in ECC support corrects 3 Bytes of error

per 512 Byte sector

• Intelligent ATA/IDE Controller

– Built-in microcontroller with intelligent firmware

– Built-in Embedded Flash File System

• Power Management Unit

– Immediate disabling of unused circuitry

PRODUCT DESCRIPTION

SST’s ATA-Disk Chip (ADC) is a low cost, high performance, embedded flash memory data storage system.

This product is well suited for solid state mass storage

applications of fering new a nd expanded f un ctional ity whil e

enabling cost effective designs.

ATA-based solid state mass storage technology is widely

used in such products as portable and desktop computers,

digital cameras, music players, handheld data collection

scanners, cell ular phones , PCS pho nes, PD As , handy terminals, personal communicators, advanced two-way pagers,

audio recorders, monitoring devices, and set-top boxes.

ADC provides comple te IDE Hard Disk Drive functionali ty

and compatibility. ADC is a perfect solution to consum er

electronic products requiring smaller, but more reliable and

cost effe ct i ve data storage. The ADC is re ad an d writ ten to

using a single power supply of 5.0V or 3.3V and is available

in 8 to 192 MByte capacities.

The ADC is a solid state disk drive that is designed to

replace conventional IDE hard disk dr ive and uses standard ATA/IDE protocol . It h as b uilt i n microc ontrol ler and file

management fir mware that communicates with ATA stan-

dard interfaces; therefore, the ADC does not require additional or propr ietary software such as Flash File System

(FFS) and Memory Technology Driv er (MTD) softw are .

The ADC is designed to work at either 5V or 3.3V. The pin

assignment is designed to match existing IDE signal traces

on the motherboard. It uses standard AT A driver that is part

of all major OS such as Windows 95/98/2000/NT/CE,

MAC, UNIX, etc.

All signals, except WP #, are in compliance wi th the ATA

specifications. WP# is used to write protect the information

stored on the ADC. The WP# ca n be either conn ected to

motherboard write protect control logic or a jumper. When

WP# is low, the ADC is write protected to prohibit any inadvertent writes.

Every ADC comes with factory-programmed, 20-Byte long,

unique identific ation number for extended data protection .

This feature prevents unauthorized duplic ation by allow ing

encryption of customer data.

The ADC is packaged in the 600 mil 32-pin DIP package

for easy and cost effective mounting to the system motherboard.

©2001 Silicon Storage Technology, Inc.

S71167-05-000 9/01 391

1

The SST logo and SuperFlash are registered trademarks of Silicon Storage Technology, Inc.

ATA-Disk Chip is a trademark of Silicon Storage Tech nology, Inc.

These specifications are subject to change without notice.

Page 2

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

TABLE OF CONTENTS

PRODUCT DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.0 GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1 Performance-optimized ATA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1.1 Microcontroller Unit (MCU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1.2 Internal Direct Memory Access (DMA). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1.3 Power Management Unit (PMU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1.4 SRAM Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1.5 Embedded Flash File System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1.6 Error Correction Code (ECC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.2 SST’s ATA-Disk Chip Product Offering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.0 ELECTRICAL INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.0.1 Pin Assignment and Pin Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.1 Electrical Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.2 Absolute Maximum Stress Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.3 Electrical Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3.1 Absolute Maximum Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3.2 Input Leakage Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3.3 Input Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.3.4 Output Drive Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.3.5 Output Drive Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.3.6 I/O Input (Read) Timing Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.3.7 I/O Output (Write) Timing Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.4 I/O Transfer Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.4.1 I/O Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.0 SOFTWARE INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.1 ATA-Disk Chip Drive Register Set Definitions and Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.1.1 ATA-Disk Chip Addressing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.1.2 ATA-Disk Chip Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.1.2.1 Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.1.2.2 Error Register (Read Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.1.2.3 Feature Register (Write Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1.2.4 Sector Count Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1.2.5 Sector Number (LBA 7-0) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1.2.6 Cylinder Low (LBA 15-8) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1.2.7 Cylinder High (LBA 23-16) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1.2.8 Drive/Head (LBA 27-24) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1.2.9 Status & Alternate Status Registers (Read Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.1.2.10 Device Control Register (Write Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.1.2.11 Drive Address Register (Read Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.1.2.12 Command Register (Write Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

2

Page 3

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.2 ATA-Disk Chip Command Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.2.1 ATA-Disk Chip Command Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.2.1.1 Check Power Mode - 98H or E5H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.2.1.2 Execute Drive Diagnostic - 90H . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.2.1.3 Format Track - 50H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.2.1.4 Identify Drive - ECH. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.2.1.4.1 General Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.2 Default Number of Cylinders. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.3 Default Number of Heads. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.4 Default Number of Sectors per Track . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.5 Number of Sectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.6 Memory Serial Number. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.7 Buffer Type. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.8 Buffer Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.9 ECC Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.10 Firmware Revision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.11 Model Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.12 Read/Write Multiple Sector Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.13 Capabilities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1.4.14 PIO Data Transfer Cycle Timing Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.2.1.4.15 Translation Parameters Valid . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.2.1.4.16 Current Number of Cylinders, Heads, Sectors/Track . . . . . . . . . . . . . . . . . . . 24

3.2.1.4.17 Current Capacity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.2.1.4.18 Multiple Sector Setting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.2.1.4.19 Total Sectors Addressable in LBA Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.2.1.4.20 Advanced PIO Data Transfer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.2.1.4.21 Minimum PIO Transfer Cycle Time Without Flow Control . . . . . . . . . . . . . . . 24

3.2.1.4.22 Minimum PIO Transfer Cycle Time With IORDY . . . . . . . . . . . . . . . . . . . . . . 24

3.2.1.5 Idle - 97H or E3H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.2.1.6 Idle Immediate - 95H or E1H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.2.1.7 Initialize Drive Parameters - 91H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.2.1.8 Read Buffer - E4H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.2.1.9 Read Multiple - C4H . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.2.1.10 Read Long Sector - 22H or 23H . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.2.1.11 Read Sectors - 20H or 21H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.2.1.12 Read Verify Sector(s) - 40H or 41H . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.2.1.13 Recalibrate - 1XH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.2.1.14 Seek - 7XH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.2.1.15 Set Features - EFH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.2.1.16 Set Multiple Mode - C6H . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.2.1.17 Set Sleep Mode - 99H or E6H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.2.1.18 Standby - 96H or E2H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.2.1.19 Standby Immediate - 94H or E0H . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.2.1.20 Write Buffer - E8H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.2.1.21 Write Long Sector - 32H or 33H . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.2.1.22 Write Multiple Command - C5H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.2.1.23 Write Sector(s) - 30H or 31H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.2.1.24 Write Verify - 3CH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.2.2 Error Posting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

3

Page 4

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

4.0 APPENDIX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.1 Differences between ATA-Disk Chip and ATA/ATAPI-5 Specifications. . . . . . . . . . . . . . . . . . . . . . . . . 35

4.1.1 Electrical Differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.1.1.1 TTL Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.1.1.2 Pull Up Resistor Input Leakage Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.1.2 Functional Differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.1.2.1 Idle Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.1.2.2 Recovery from Sleep Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

5.0 PHYSICAL DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.0 PRODUCT ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

6.1 Valid Combinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

7.0 LIMITED WARRANTY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

7.1 Life Support Policy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

7.2 Patent Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

4

Page 5

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

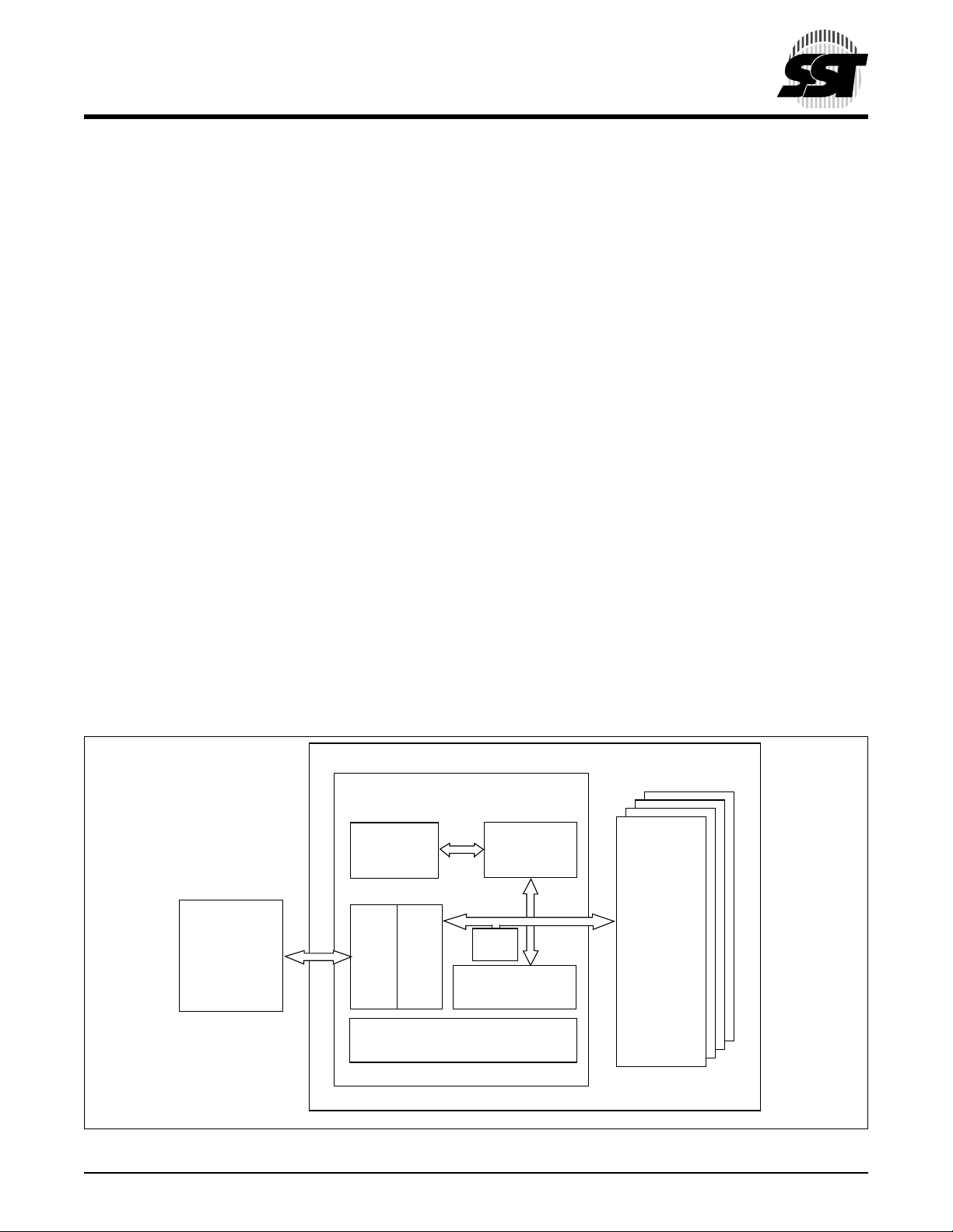

1.0 GENERAL DESCRIPTION

The SST’s ATA-Disk Chip (ADC) contains a controller,

embedded firmware and Flash Media in a 32-pin DIP package. Refer to Figure 1-1 for SST’s ADC block diagram. The

controller interfaces with the host system allowing data to

be written to and read from the Flash Media.

1.1 Performance-optimized ATA Controller

The heart of the ADC is the AT A controller which translates

standard ATA signals into Flas h Media data an d controls.

SST’s ADC contains a propr ietar y ATA controller that was

specifically designed to attain high data throughput from

host to Flash. The following co mponents cont ribute to the

ATA controller’ s ope rati on.

1.1.1 Microcontroller Unit (MCU)

The MCU translates ATA command s into data an d control

signals required for flash memory operation.

1.1.2 Internal Direct Memory Access (DMA)

The ATA controller inside ADC uses DMA allowing instant

data transfer from buffer to memory. This implementation

eliminates microc ontroller overhead associated with traditional, firmware based, memory control, increasing data

transfer rate.

1.1.3 Power Management Unit (PMU)

Power Management Unit control s the power c onsumptio n

of the ADC. The PMU dramatically extends product battery

life by putting the part of the circuitry that is not in operation

into sleep mode.

1.1.4 SRAM Buffer

A key contributor to the ATA controller performance is an

SRAM buffer. The buffer optimizes host’s data writes to

Flash Media.

1.1.5 Embedded Flash File System

Embedded Flash File System is an integral part of the

SST’s ATA controller. It contains MCU Firmware that performs the f ollow ing tasks:

1. Translates host side signals into Flash Media

Writes and Reads.

2. Provides Flash Media wear leveling to spread the

Flash writes across all the memory address space

to increase the longevity of Flash Media.

3. Keeps track of data file structures.

1.1.6 Error Correction Code (ECC)

The ATA Controller contain s E CC algori th m th at c o rr ec t s

3 Bytes of error pe r 512 Byte se cto r.

ATA Controller

Embedded

Flash

File System

SRAM Buffer

HOST

ATA/IDE

BUS

PMU

FIGURE 1-1: SST ATA-D

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

ISK CHIP BLOCK DIAGRAM

ECC

5

MCU

Flash

Media

Internal

DMA

391 ILL1-1.5

Page 6

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

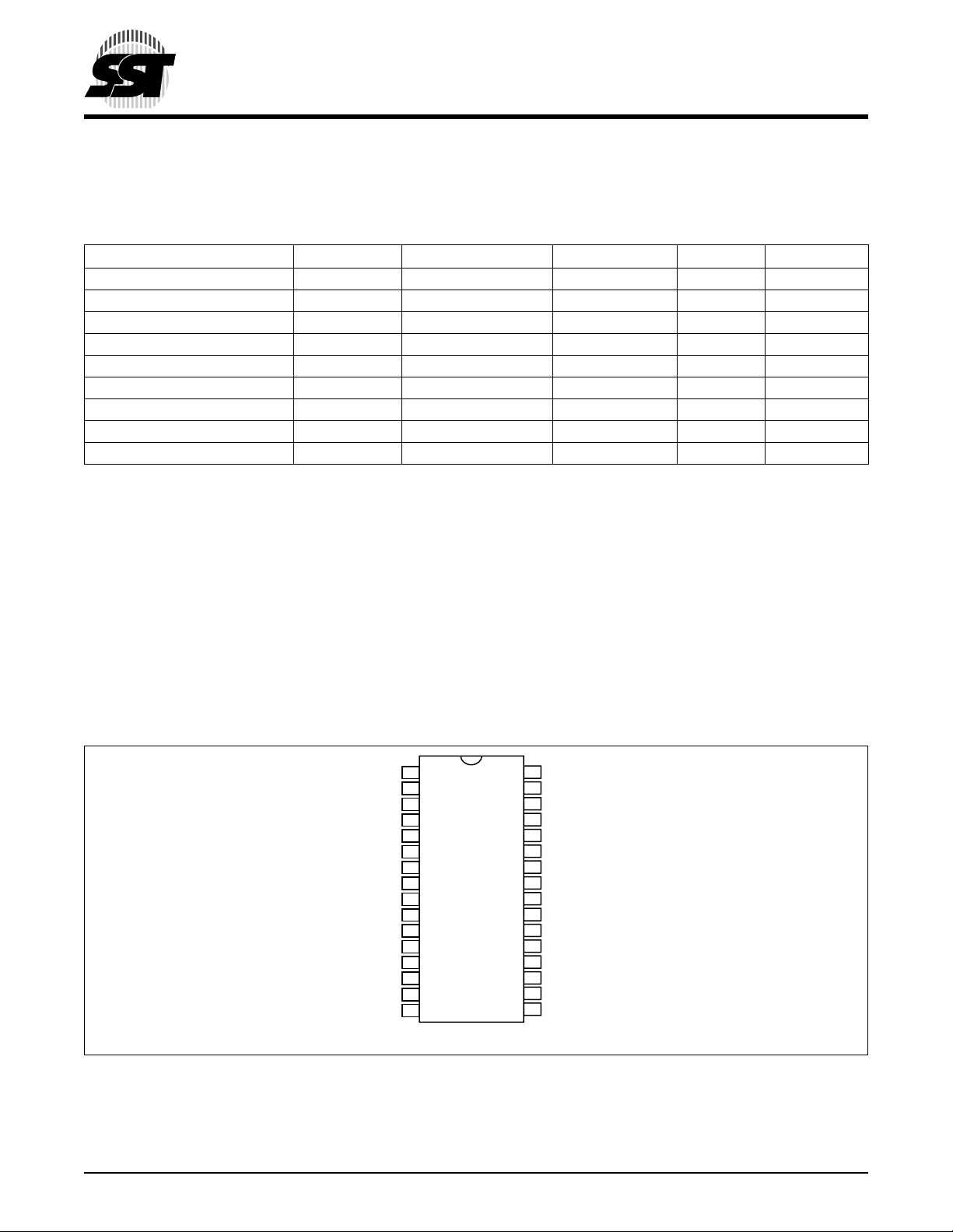

1.2 SST’s ATA-Disk Chip Product Offering

The SST58SD/LDxxx ATA-Disk Chip product family is available in 8 to 192 MByte capacities. The following table

shows the specific capacity, default number of cylinder heads, sectors and cylinders for each product line.

Model Number Density T ota l Bytes Cylinders Heads Sectors

SST58SD/LD008 8 MB 8,028,160 245 2 32

SST58SD/LD016 16 MB 16,023,552 489 2 32

SST58SD/LD024 24 MB 24,051,712 367 4 32

SST58SD/LD032 32 MB 32,047,104 489 4 32

SST58SD/LD048 48 MB 48,037,888 733 4 32

SST58SD/LD064 64 MB 64,028,672 977 4 32

SST58SD/LD096 96 MB 96,075,776 733 8 32

SST58SD/LD128 128 MB 128,057 ,344 977 8 32

SST58SD/LD192 192 MB 192,151 ,552 733 16 3 2

2.0 ELECTRICAL INTERFACE

2.0.1 Pin Assignment and Pin Type

The signal/pin assignments are listed in Table 2-1. Low active signals have a “#” suffix. Pin types are Input, Output or Input/

Output. Section 2.3 defines the DC characteristics for all input and output type structures.

2.1 Electrical Description

The ADC functions in A TA Mode, which is compatible with IDE hard disk drives.

Table 2-2 descr ibes the I/O sign als. Signa ls who se sour ce is t he hos t are des igna ted as input s whil e signa ls tha t the AD C

sources are ou tputs. All outputs from the ADC are totem pole except the data bus signals which are in the bi-dir ectional tristate. Refer to Section 2.3.2 for definitions of Input and Output types.

RESET#

D7

D6

D5

D4

D3

D2

D1

D0

WP#

IORD#

INTRQ

A1

A0

CS1FX#

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32-pin

PSDIP

T op Vie w

32

V

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

CC

D8

D9

D10

D11

D12

D13

D14

D15

IOWR#

CSEL

IOCS16#

PDIAG#

A2

CS3FX#

DASP#

391 ILL F01.5

FIGURE 2-1: P

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

IN ASSIGNMENTS FOR 32-PIN PSDIP

6

Page 7

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

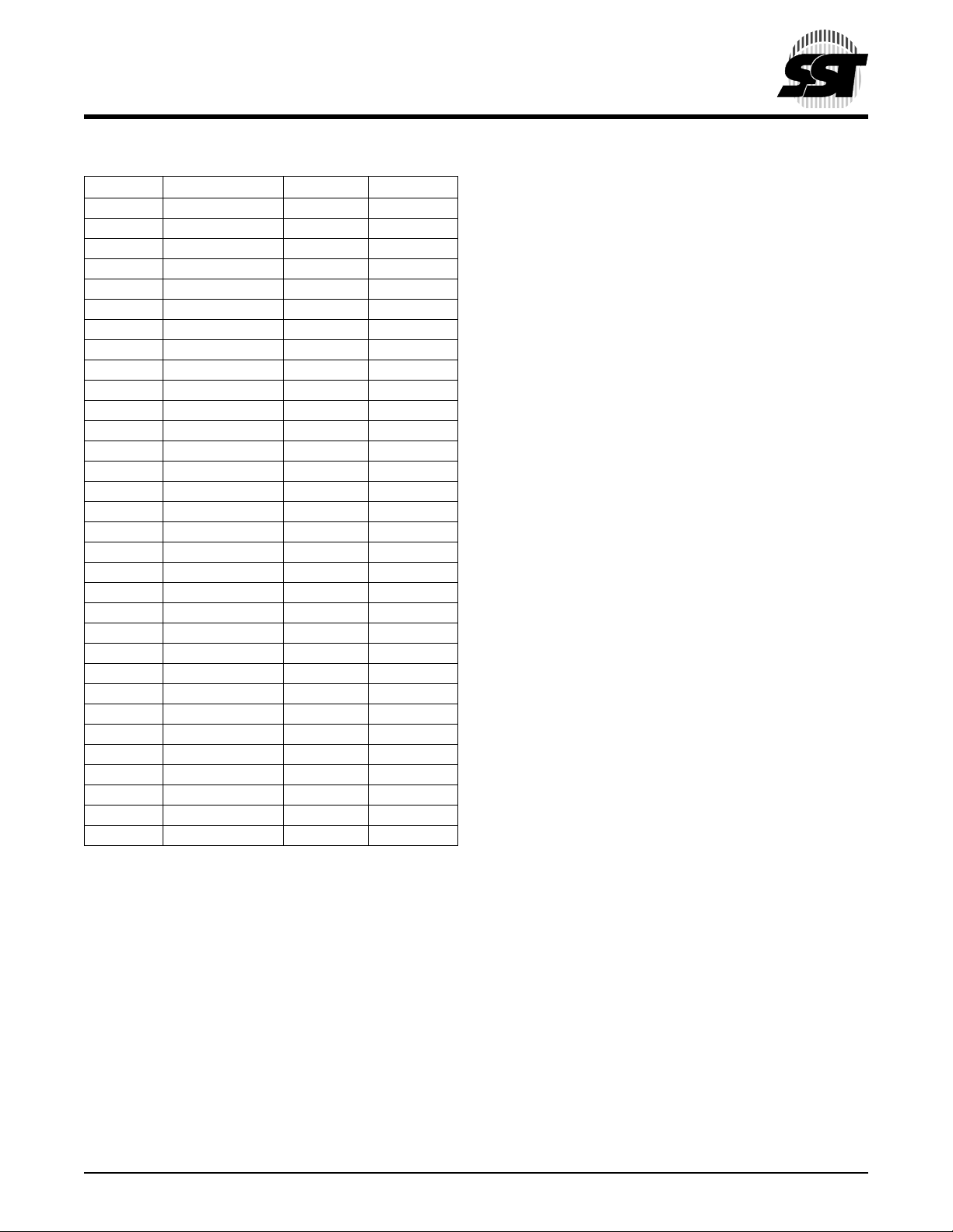

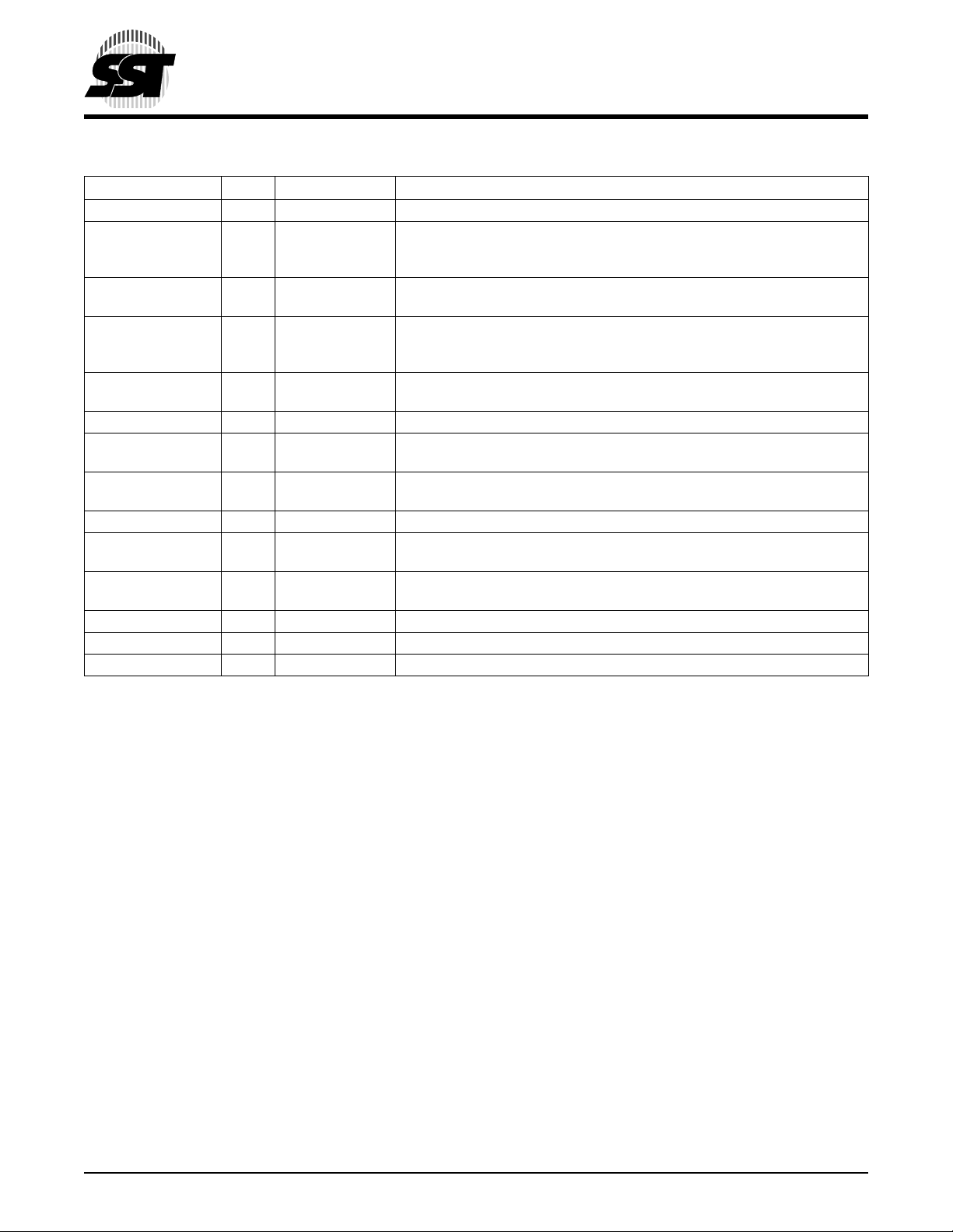

TABLE 2-1: PIN ASSIGNMENTS

Pin No. Signal Name Pin Type I/O Type

1 RESET# I I4U

2 D7 I/O I2D, O2

3 D6 I/O I2D, O2

4 D5 I/O I2D, O2

5 D4 I/O I2D, O2

6 D3 I/O I2D, O2

7 D2 I/O I2D, O2

8 D1 I/O I2D, O2

9 D0 I/O I2D, O2

10 WP# I I2U

11 IORD# I I3U

12 INTRQ O O1

13 A1 I I2D

14 A0 I I2D

15 CS1FX# I I3U

16 GND - Ground

17 DASP# I/O I2U, O1

18 CS3FX# I I3U

19 A2 I I2D

20 PDIAG# I/O I2U, O1

21 IOCS16# O O2

22 CSEL I I2U

23 IOWR# I I3U

24 D15 I/O I2D, O2

25 D14 I/O I2D, O2

26 D13 I/O I2D, O2

27 D12 I/O I2D, O2

28 D11 I/O I2D, O2

29 D10 I/O I2D, O2

30 D9 I/O I2D, O2

31 D8 I/O I2D, O2

32 V

1. Please refer to Sections 2.3.1 to 2.3.4 for detail

DD

-Power

1

T2-1.5 391

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

7

Page 8

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

TABLE 2-2: SIGNAL DESCRIPTION

Symbol Type

A2 - A0 I 13,14,19 A[2:0] are used to select the one of eight registers in the Task File.

D15 - D0 I/O 9,8,7,6,5,4,3,2,

CS1FX#, CS3FX# I 15,18 CS1FX# is the chip select f or the task file registers while CS3 FX# is used to

CSEL I 22 This internally pulled-up signal is used to configure this device as a Master

IORD# I 11 This is an I/O Read st robe gen erated b y the ho st. This si gnal gates I/O data

IOWR# I 23 The I/O Write strobe pulse is used to clock I/O data into the chip.

IOCS16# O 21 This output signal is asse rted low when this dev ice is e xpec ting a w ord data

WP# I 10 Write protect pin is used to disable Write operation. When this pin is low,

INTRQ O 12 Signal is the active high Interrupt Request to the host.

PDIAG# I/O 20 This input/output is the Pass Diagnostic signal in the Master/Slave

DASP# I/O 17 This inp ut/output is the Disk Activ e/Sla ve pre sent signal i n the Master/Sla v e

RESET# I 1 This input pin is the active low hardware reset from the host.

GND - 16 Ground

V

DD

1. Please refer to Sections 2.3.1 to 2.3.4 for detail

1

-32Power

Pin Name and Functions

Data bus

31,30,29,28,27,

26,25,24

select the Alternate Status Register and the Device Control Register.

or a Slave. When this pin is grounded, this device is configured as a Master.

When the pin is open, this device is configured as a Slave.

onto the bus from the chip.

transf er cy cl e .

data on chip will be write protected.

handshake prot oco l.

handshake prot oco l.

T2-2.3 391

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

8

Page 9

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

2.2 Absolute Maximum Stress Ratings

Absolute Maximum Stress Ratings (Applied conditions greater than those listed under “Absolute Maximum

Stress Ratings” may cause pe r manent dama ge to the device. This is a stres s rating only and funct ional operatio n

of the device at these conditions or conditions greater tha n those defined in the ope rational sections of this data

sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.)

Temperature Under Bias . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55°C to +125°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -50°C to +100°C

D.C. Voltage on any Pin to Ground Potential . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to

Transient Voltage (<20 ns) on Any Pin to Ground Potential . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1.0V to

Package Power Dissipation Capability (Ta = 25°C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.0W

Through Hole Lead Soldering Temperature (10 Seconds). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300° C

Surface Mount Lead Soldering Temperature (3 Seconds) 240°C

1

Output Short Circ uit Curr ent

1. Outputs shorted for no more than one second. No more than one output shorted at a time.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 mA

V

V

DD

DD

+0.5V

+1.0V

OPERATING RANGE: SST58SDXXX

Range Ambient Temp V

Commercial 0°C to +70°C 4.5-5.5V

DD

OPERATING RANGE: SST58LDXXX

Range Ambient Temp V

Commercia l 0°C to +70°C 3.135-3.465V

AC CONDITIONS OF TEST

Input Rise/Fall Time . . . . . . . . . . . . . . 10 ns

Output Load . . . . . . . . . . . . . . . . . . . . C

= 100 pF

L

See Figures 2-3 and 2-4

Note: All AC specifications are guaranteed by design.

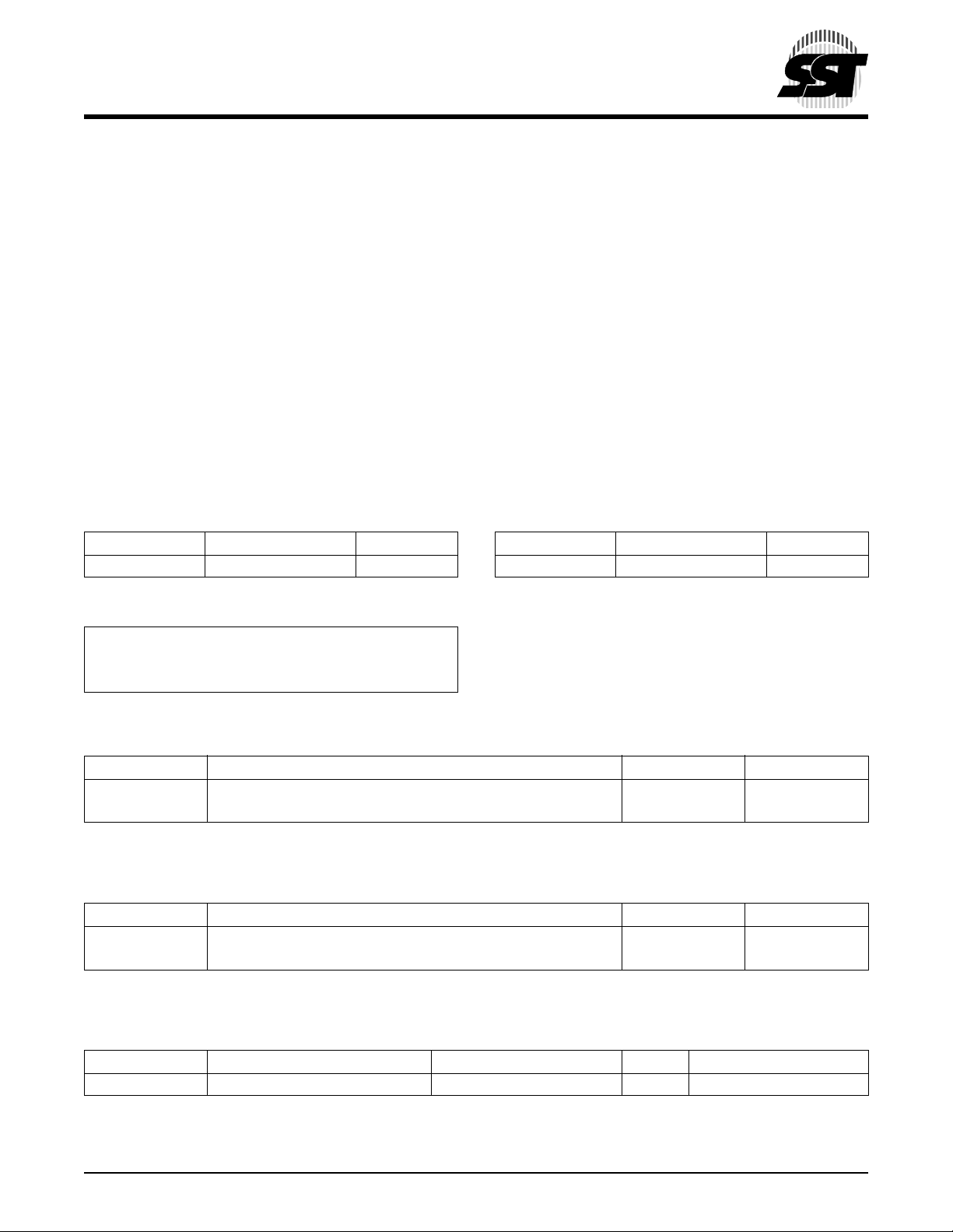

TABLE 2-3: RECOMMENDED SYSTEM POWER-UP TIMINGS

Symbol Parameter Maximum Units

T

PU-READY

T

PU-WRITE

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

1

1

Power-up to Ready Operation 500 ms

Power-up to Write Operation 500 ms

TABLE 2-4: CAPACITANCE (Ta = 25°C, f=1 Mhz, other pins open)

Parameter Description Test Condition Maximum

1

C

I/O

1

C

IN

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

I/O Pin Capacitance V

= 0V 15 pF

I/O

Input Capacitance VIN = 0V 9 pF

DD

T2-3.0 391

T2-4.0 391

TABLE 2-5: RELIABILITY CHARACTERISTICS

Symbol Parameter Minimum Specification Units Test Method

1

I

LTH

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

Latch Up 100 + I

9

DD

mA JEDEC Standard 78

T2-5.1 391

Page 10

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

2.3 Electrical Specification

The following tables define all D.C. Characteristics for the SST ATA-Disk Chip product family.

2.3.1 Absolute Maximum Conditions

Unless otherwise stated, conditions are for Commercial Temperature:

Non-operating (storage) temperature range: -50°C to +100°C

V

= 4.5-5.5V

DD

V

= 3.135-3.465V

DD

Ta = 0°C to +70°C

BSOLUTE MAXIMUM CONDITIONS

A

Parameter Symbol Conditions

Input Powe r V

Voltage on any pin except V

with respect to GND V -0.5V min. to VDD + 0.5V max.

DD

DD

INPUT POWER

Maximum Average RMS

Voltage

3.135-3.465V 75 mA 200 µA 3.3V at 25

4.5-5.5V 100 mA 300 µA 5.0V at 25°C

Active Current

Maximum Average RMS

Sleep Current Measurement Method

-0.3V min. to 6.5V max.

Data Sheet

1

°C

1

1. Current measurement is accomplished by connecting an amp meter (set to the 2 amp scale range) in series with the VDD supply to

the ADC. Current measurements are to be taken while looping on a data transfer command with a sector count of 128.

Current consumption values for both Read and Write commands are not to exceed the Maximum Average RMS Current specified in

this table.

ADC products sha ll operate correctly in b oth voltage ranges as shown in the tables above. To comply with this

specification, current requirements must not exceed the maximum limit.

2.3.2 Input Leakage Current

In the table below, x refers to the characteristics descri bed in section 2.3.2. For example, I1U indicates a pull up

resistor with a type 1 input characteristic.

Type Parameter Symbol Conditions Min Typ Max Units

IxZ Input Leakage Current IL V

IxU Pull Up Resistor RPU1 VDD = 5.0V 50k 500k Ohm

IxD Pull Down Resistor RPD1 VDD = 5.0V 50k 500k Ohm

= VDD / VIL = Gnd -1 1 µA

IH

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

10

Page 11

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

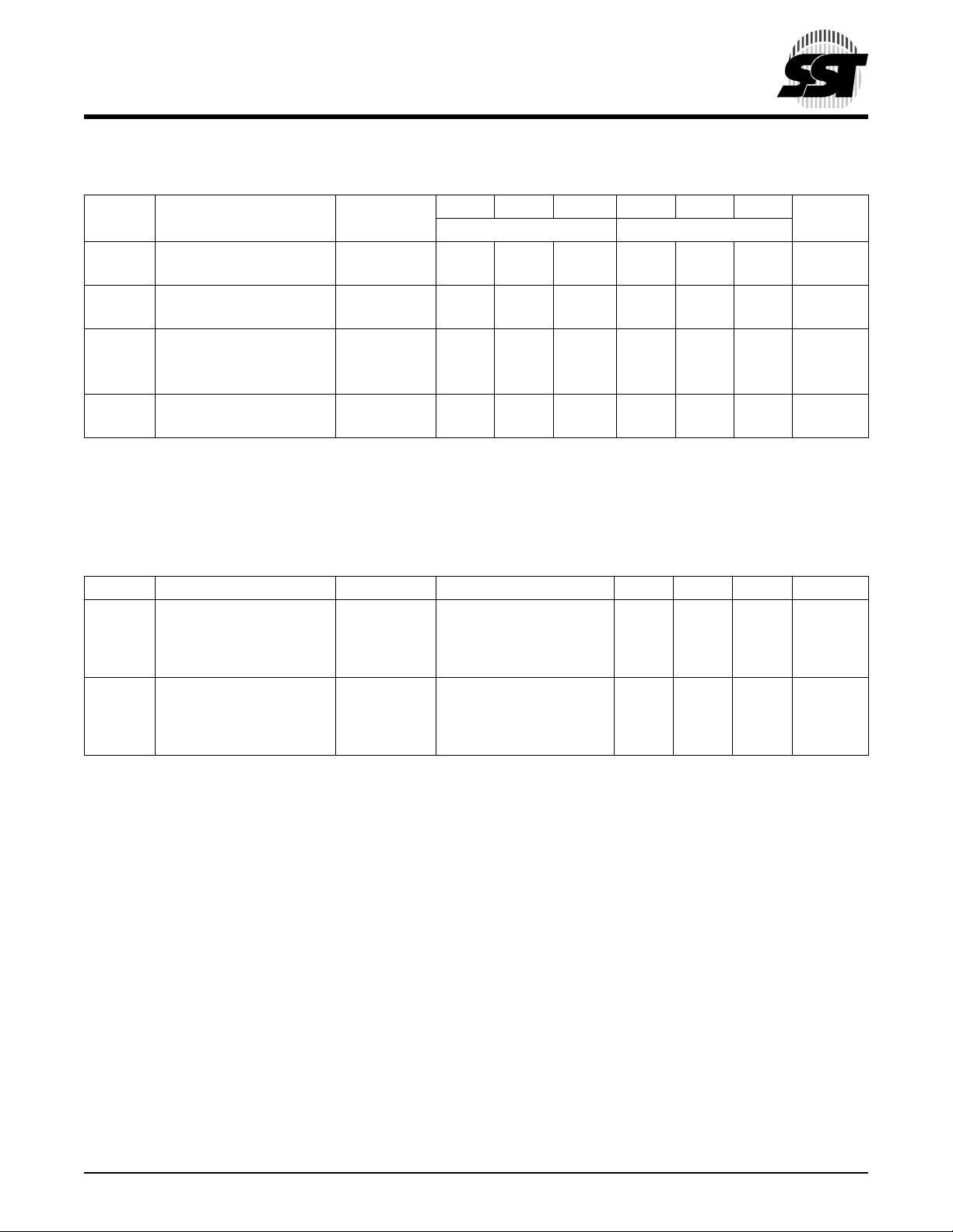

2.3.3 Input Characteristics

Min Typ Max Min Typ Max

Type Parameter Symbol

1 Input Voltage V

CMOS V

2 Input Voltage V

CMOS V

3 Input Voltage V

CMOS V

Schmitt Trigger

4 Input Voltage V

CMOS Schmitt Trigger V

2.3.4 Output Drive Type

All output drive type are CMOS level.

IH

IL

IH

IL

TH

TL

TH

TL

2.4 2.4 Volts

0.6 0.8

2.0 2.7 Volts

0.8 0.8

2.0 2.4 Volts

0.5 0.8

1.8 2.4 Volts

0.9 0.8

UnitsVDD = 3.3V VDD = 5.0V

2.3.5 Output Drive Characteristics

Type Parameter Symbol Conditions Min Typ Max Units

O1 Output Voltage V

O2 Output Voltage V

OH

V

OL

OH

V

OL

IOH = -4 mA V

DD

-0.8V

IOL = 4 mA Gnd

+0.4V

IOH = -8 mA V

DD

-0.8V

IOL = 8 mA Gnd

+0.4V

Volts

Volts

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

11

Page 12

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

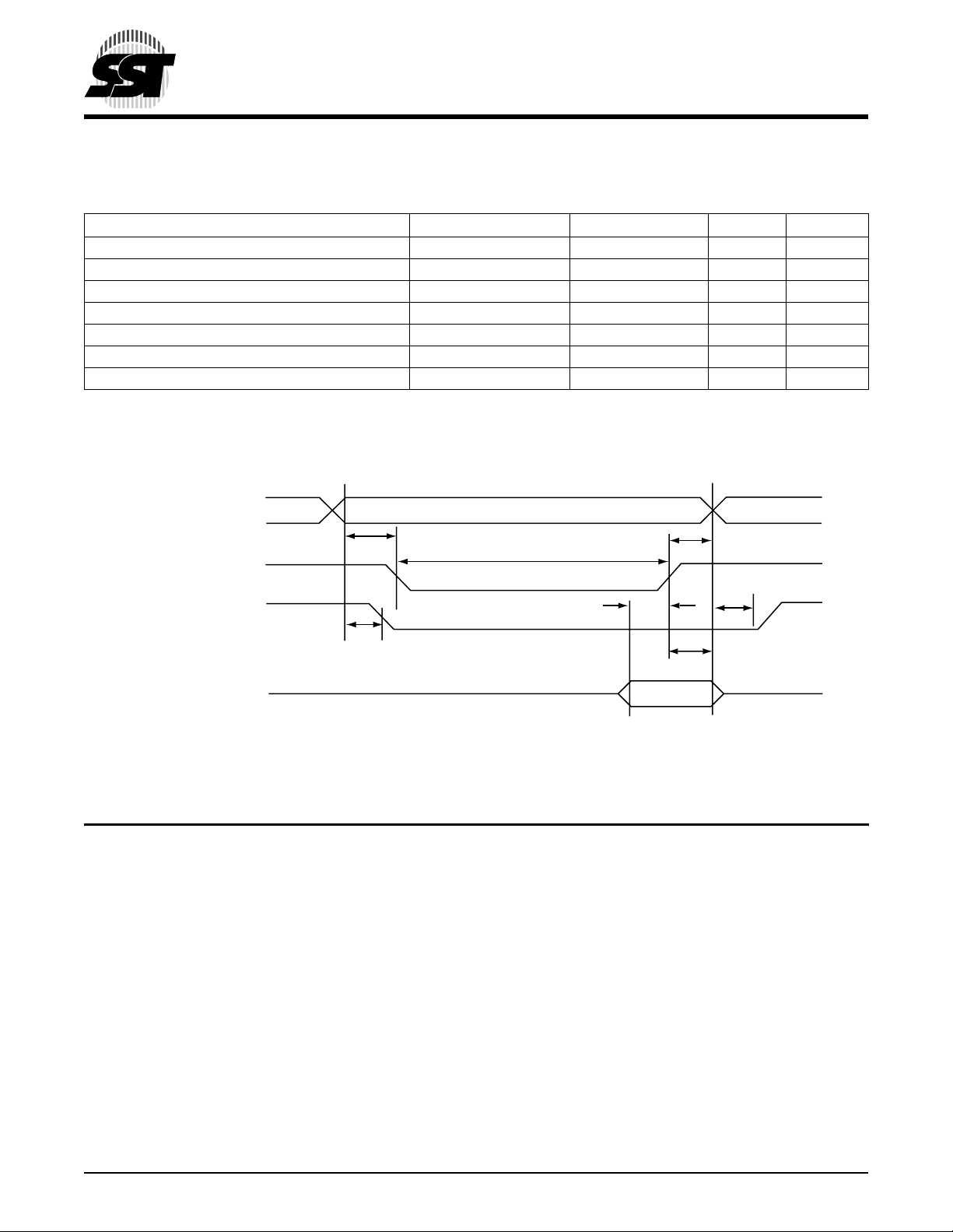

2.3.6 I/O Input (Read) Timing Specification

TABLE 2-6: I/O READ TIMING

Item Symbol IEEE Symbol Min Max

Data Setup before IORD# tsu(IORD) tDVIRH 20 Data Hold following IORD# th(IORD) tlGHQX 5 IORD# Width Time tw(IORD) tlGLIGH 70 Address Setup before IORD# tsuA(IORD) tAVIGL 25 Address Hold following IORD# thA(IORD) tlGHAX 10 IOCS16# Delay Falling from Address tdfIOCS16(ADR) tAVISL - 20

IOCS16# Delay Rising from Address tdrIOCS16(ADR) tAVISH - 20

Note: All times are in nanoseconds. The maximum load on IOCS16# is 1 LSTTL with 50pF total load.

All AC specifications are guaranteed by design.

T2-6.4 391

Valid Address

1

IORD#

IOCS16#

tdfIOCS16(ADR)

D15-D0

1. Valid Address consists of signals CS1FX#, CS3FX# and A2-A0.

FIGURE 2-2: I/O READ TIMING DIAGRAM

tsuA(IORD)

tw(IORD)

tsu (IORD)

thA(IORD)

tdrIOCS16(ADR)

th(IORD)

Dout

391 ILL2-7.1

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

12

Page 13

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

2.3.7 I/O Output (Write) Timing Specification

TABLE 2-7: I/O WRITE TIMING

Item Symbol IEEE Symbol Min Max

Data Setup before IOWR# tsu(IOWR) tDVIWH 20 Data Hold following IOWR# th(IOWR) tlWHDX 10 IOWR# Width Time tw(IOWR) tlWLIWH 70 Address Setup before IOWR# tsuA(IOWR) tAVIWL 25 Address Hold following IOWR# thA(IOWR) tlWHAX 10 IOCS16 Delay Falling from Address tdfIOCS16(ADR) tAVISL - 20

IOCS16 Delay Rising from Addres s tdrIOCS16(ADR) tAVISH - 20

Note: All times are in nanoseconds. The maximum load on IOCS16 is 1 LSTTL with 50pF total load.

All AC specifications are guaranteed by design.

T2-7.4 391

Valid Address

1

IOWR#

IOCS16#

tdfIOCS16(ADR)

D15-D0

1. Valid Address consists of signals CS1FX#, CS3FX# and A2-A0.

FIGURE 2-3: I/O WRITE TIMING DIAGRAM

V

IHT

V

ILT

V

HT

V

LT

tsuA(IOWR)

REFERENCE POINTS OUTPUTINPUT

tw(IOWR)

thA(IOWR)

tdrIOCS16(ADR)

th(IOWR)tsu(IOWR)

Din Valid

391 ILL2-8.2

V

HT

V

LT

391 ILL F11.0

AC test inputs are driven at V

inputs and outputs are V

HT

(2.4V) for a logic “1” and V

IHT

(0.4V) for a logic “0”. Mea surement reference points for

IL T

(2.0V) and VLT (0.8V). Input rise and fall times (10% ↔ 90%) are <10 ns.

Note: V

V

V

V

HT

LT

IHT

ILT

- V

- V

- V

- V

HIGH

LOW

INPUT

INPUT

Test

Test

HIGH Test

LOW Test

FIGURE 2-4: AC INPUT/OUTPUT REFERENCE WAVEFORMS

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

13

Page 14

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

2.4 I/O Transfer Function

2.4.1 I/O Function

ADC permits 8-bit data access if the user issues a Set Feature Command to enable 8-bit Mode.

The following table defines the function of various operations.

ATA-Disk Chip

Data Sheet

TABLE 2-8: I/O F

UNCTION

Function Code CS3FX# CS1FX# A0-A2 IORD# IOWR# D15-D8 D7-D0

Invalid Mode V

Standby Mode V

Task File Write V

Task File Read V

Data Register Write V

Data Register Read V

Control Register Write V

Alt Status Read V

Drive Address V

1. X can be VIL or VIH, but no other value.

2. If 8-bit data transfer mode is enabled.

In 8-bit data transfer mode, High Byte is undefined for Data Out; can be V

IL

IH

IH

IH

IH

IH

IL

IL

IL

V

IL

V

IH

V

IL

V

IL

V

IL

V

IL

V

IH

V

IH

V

IH

1

X

X X Undefined Undefined

X X X High Z High Z

1-7H V

1-7H V

IH

IL

0VIHV

0VILV

6H V

6H V

7H V

IH

IL

IL

or VIH, but no other value, for Data In.

IL

V

IL

V

IH

IL

IH

V

IL

V

IH

V

IH

XData In

High Z Data Out

2

In

2

Out

X Control In

High Z Status Out

High Z Data Out

In

Out

T2-8.1 391

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

14

Page 15

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.0 SOFTWARE INTERFACE

3.1 ATA-Disk Chip Drive Re gister Set Definitions and Protocol

3.1.1 ATA-Disk Chip Addressing

The I/O decoding for an ADC is as follows:

TABLE 3-1: T

CS3FX# CS1FX# A2 A1 A0 IORD# = 0 IOWR# = 0

1 0 0 0 0 RD Data WR Data

1 0 0 0 1 Error Register Features

1 0 0 1 0 Sector Count Sector Count

1 0 0 1 1 Sector No. Sector No.

1 0 1 0 0 Cylinder Low Cylinder Low

1 0 1 0 1 Cylinder High Cylinder High

1 0 1 1 0 Select Card/Head Select Card/Head

1 0 1 1 1 Status Command

0 1 1 1 0 Alt Status Device Control

0 1 1 1 1 Drive Address Reserved

ASK REGISTERS

T3-1.0 391

3.1.2 ATA-Disk Chip Registers

The following section descr ib es the hardware registe rs used by the host so ftware to iss ue com mands to the A DC.

These registers are often collectively referred to as the “Task File Registers.”

3.1.2.1 Data Register

This 16-bit register is used to transfer data blocks between the device data buffer and the host. It is also the register

through which sector information is transferred on a Format Track command . Data transfer can be performed in

PIO mode.

3.1.2.2 Error Register (Read Only)

This register co ntains a dditional informatio n abou t the sou rce of an error wh en an er ror is indicat ed in bi t 0 of th e

Status register. The bits are defined as follows:

D7 D6 D5 D4 D3 D2 D1 D0

BBK UNC 0 IDNF 0 ABRT 0 AMNF

Bit 7 (BBK) This bit is set when a Bad Block is detected.

Bit 6 (UNC) This bit is set when an Uncorrectable Error is encountered.

Bit 5 This bit is 0.

Bit 4 (IDNF) The requested sector ID is in error or cannot be found.

Bit 3 This bit is 0.

Bit 2 (Abort) This bit is set if the com mand has been aborte d because of an ADC status condi tion:

(Not Ready , Write Fault, etc.) or when an invalid command has been issued.

Bit 1 This bit is 0.

Bit 0 (AMNF) This bit is set in case of a general error.

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

15

Page 16

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.1.2.3 Fea tur e Regi ster (Writ e Only)

This register provides information regarding features of the ADC that the host can utilize.

3.1.2.4 Sector Count Register

This register cont ains the numbers of sectors of data requested to be transferred on a Read or Write operation

between the host and the ADC. If the value in thi s register i s zero, a count of 256 sec tors is s pecified. If the command was successful, this register is zero at command completion. If not successfully completed, the register contains the number of sectors that need to be transferred in order to complete the request.

3.1.2.5 Sector Number (LBA 7-0) Register

This register contains the star ti ng secto r number or bits 7-0 of the Logical Block Address ( LBA) for any ADC data

access for the subsequent command.

3.1.2.6 Cy lin der Low (LBA 15-8) Register

This register contains the low order 8 bits of the starting cylinder address or bits 15-8 of then Logical Block

Address.

3.1.2.7 Cylinder High (LBA 23-16) Register

This register contains the high order bits of the starting cylinder address or bits 23-16 of the Logical Block Address.

3.1.2.8 Drive/Head (LBA 27-24) Register

The Drive/Head register is used to se lect the drive and h ead. It is also used to select LB A addressing in stead of

cylinder/head/sector addressing. The bits are defined as follows:

D7 D6 D5 D4 D3 D2 D1 D0

1LBA1

Bit 7 This bit is set to 1.

Bit 6 LBA is a flag to select either Cylinder/Head/Sector (CHS) or Logical Block Address Mode (LBA).

When LBA=0, Cylinder/Head/Sector mode is selected. When LBA=1, Logical Block Address is

selected. In Logical Block Mode, the Logical Block Address is interpreted as follows:

LBA7-LBA0: Sector Number Register D7-D0.

LBA15-LBA8: Cylinder Low Register D7-D0.

LBA23-LBA16: Cylinder High Register D7-D0.

LBA27-LBA24: Drive/Head Register bits HS3-HS0.

Bit 5 This bit is set to 1.

Bit 4 (DRV) DRV is the drive number. When DRV=0 (Master), Master is selected.

When DRV=1(Slave), Slave is selected.

Bit 3 (HS3) When operating in the Cylinder, Head, Sector mode, this is bit 3 of the head number.

It is Bit 27 in the Logical Block Address mode.

Bit 2 (HS2) When operating in the Cylinder, Head, Sector mode, this is bit 2 of the head number.

It is Bit 26 in the Logical Block Address mode.

Bit 1 (HS1 When operating in the Cylinder, Head, Sector mode, this is bit 1 of the head number.

It is Bit 25 in the Logical Block Address mode.

Bit 0 (HS0) When operating in the Cylinder, Head, Sector mode, this is bit 0 of the head number.

It is Bit 24 in the Logical Block Address mode.

DRV HS3 HS2 HS1 HS0

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

16

Page 17

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.1.2.9 Status & Alternate Status Registers (Read Only)

These register s ret urn the ADC sta tus when r ead by the host. Reading the Status re gis te r do es cl ea r a pe nd in g

interrupt while rea di ng the Auxiliary Status register does not. Th e me an ing of th e st a tus bit s a r e describ ed as follows:

D7 D6 D5 D4 D3 D2 D1 D0

BUSY RDY DWF

Bit 7 (BUSY) The busy bit is set when the ADC has access to the command buffer and registers and

the host is locked out from accessing the command re gister and buffer. No other bits in

this register are valid when this bit is set to a 1.

Bit 6 (RDY ) RDY indicates whe ther the device is capable of performing ADC operations. Th is bit is

cleared at power up and remains cleared until the ADC is ready to accept a command.

Bit 5 (DWF) This bit, if set, indicates a write fault has occurred.

Bit 4 (DSC) This bit is set when the ADC is ready.

Bit 3 (DRQ) The Data Request is set when the ADC requires that information be transferred either to

or from the host through the Data register.

Bit 2 (CORR) This bit is set when a Cor rectable data error has been encounter ed and the data has

been corrected. This condition does not terminate a multi-sector Read operation.

Bit 1 (IDX) This bit is always set to 0.

Bit 0 (ERR) This bit is set wh en the previous comman d has ended in some type of error. The bits in

the Error register contai n additional information des cribing the error. It is recommended

that media access commands (such as Read Sect ors and Write Sectors) tha t end with

an error condition should have the address of the first sec tor in error in the command

block registers.

DSC DRQ CORR 0 ERR

3.1.2.10 Device Control Register (Write Only)

This register is used to control the ADC interrupt request and to issue a software Reset. This register can be written

to even if the device is BUSY. The bits are defined as follows:

D7 D6 D5 D4 D3 D2 D1 D0

XXX

Bit 7 This bit is an X (don’t care).

Bit 6 This bit is an X (don’t care).

Bit 5 This bit is an X (don’t care).

Bit 4 This bit is an X (don’t care).

Bit 3 This bit is ignored by the ADC.

Bit 2 (SW Rst)This bit is set to 1 in ord er to force the ADC to per form a s oft ware Rese t opera tion. Th e

chip remains in Reset until this bit is reset to ‘0.’

Bit 1 (-IEn) The Interrupt Enable bit enables interrupts when the bit is 0. When the bit is 1, interrupts

from the ADC are disabled. This bit is Reset to 0 at power on and Reset.

Bit 0 This bit is ignored by the ADC.

X1SW Rst-IEn0

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

17

Page 18

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.1.2.11 Drive Address Register (Read Only)

This register con tains the i nverte d dr ive selec t and h ead s elect addr esses of th e curr ently sel ected dr ive. The bits

in this register are as follows:

D7 D6 D5 D4 D3 D2 D1 D0

HiZ -WTG -HS3 -HS2 -HS1 -HS0 -DS1 -DS0

Bit 7 This bit is HiZ.

Bit 6 (-WTG) This bit is 0 when a Write operation is in progress, otherwise, it is 1.

Bit 5 (-HS3) This bit is the negation of bit 3 in the Drive/Head register.

Bit 4 (-HS2) This bit is the negation of bit 2 in the Drive/Head register.

Bit 3 (-HS1) This bit is the negation of bit 1 in the Drive/Head register.

Bit 2 (-HS0 This bit is the negation of bit 0 in the Drive/Head register.

Bit 1 (-DS1) This bit is 0 when drive 1 is active and selected.

Bit 0 (-DS0) This bit is 0 when drive 0 is active and selected.

3.1.2.12 Command Register (Write Only)

This register cont ains the command cod e being sent to the dr ive. Command execution begins immediately a fter

this register is wr itten. The executable commands, the command codes, an d the necessar y parameters for each

command are listed in Table 3-2.

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

18

Page 19

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.2 ATA-Disk Chip Command Description

This section defines the sof tware requirements an d the f ormat of the command s the host sends to the ADC . Commands

are issued to the ADC by loading the required registers in the command block with the supplied parameters, and then

writing the command code to the Command Register. The manner in which a command is accepted varies. There are

three classes (see Table 3-2) of command acceptance, all dependent on the host not issuing commands unless the

ADC is not busy (BSY=0).

3.2.1 ATA-Disk Chip Command Set

Table 3-2 summari zes the ADC comman d set with the paragraphs tha t follow describing the in dividua l commands

and the task file for each.

TABLE 3-2: ATA-D

Class Command Code FR

1 Check Power Mode E5H or 98H - - - - D

ISK CHIP COMMAND SET

1

SC

2

SN

3

CY

4

DH

5

8

1 Execute Drive Diagnostic 90H - - - - D 2 Format Track 50H - Y

7

-YY

8

1 Identify Drive ECH - - - - D 1 Idle E3H or 97H - Y - - D 1 Idle Immediate E1H or 95H - - - - D 1 Initialize Drive Parameters 91H - Y - - Y 1 Read Buffer E4H - - - - D 1 Read Long Sector 22H or 23H - - Y Y Y Y

1Read Multiple C4H -YYYY Y

1Read Sector(s) 20H or 21H -YYYY Y

1Read Verify Sector(s) 40H or 41H -YYYY Y

1 Recalibrate 1XH - - - - D 1Seek 7XH --YYY Y

1 Set Features EFH Y - - - D 1 Set Multiple Mode C6H - Y - - D 1 Set Sleep Mode E6H or 99H - - - - D 1 Stand By E2H or 96H - - - - D 1 Stand By Immediate E0H or 94H - - - - D 2 Write Buffer E8H - - - - D 2 Write Long Sector 32H or 33H - - Y Y Y Y

3Write Multiple C5H -YYYY Y

2Write Sector(s) 30H or 31H -YYYY Y

3Write Verify 3CH -YYYY Y

1. FR - Features Register

2. SC - Sector Count Register

3. SN - Sector Number Register

4. CY - Cylinder Registers

5. DH - Drive/Head Register

6. LBA - Logical Block Address Mode Supported (see command descriptions for use)

7. Y - The register contains a valid parameter for this command.

8. For the Drive/Head Register: Y means both the ADC and Head parameters are used;

D means only the ADC parameter is valid and not the Head parameter.

6

LBA

-

Y

T3-2.1 391

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

19

Page 20

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

3.2.1.1 Ch eck Power Mode - 98H or E5H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

This command checks the power mode.

Because SST ADC can recover from sleep in 200 ns, Idle Mode is never enabled.

ADC sets BSY, sets the Sector Count Register to 00H, clears BSY and generates an interrupt.

3.2.1.2 Execute Drive Diagnostic - 90H

XDrive X

ATA-Disk Chip

Data Sheet

98H or E5H

X

X

X

X

X

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

XDrive X

90H

X

X

X

X

X

This command performs the internal diagnostic tests implemented by the ADC.

If the Drive bit is ignored and the diagnosti c command is executed by both the Master and the Slave

with the Master responding with status for both devices.

The Diagnostic codes shown in Table 3-3 are returned in the Error Register at the end of the command.

TABLE 3-3: DIAGNOSTIC CODES

Code Error Type

01H No Error Detected

02H Formatter Device Error

03H Sector Buffer Error

04H ECC Circuitry Error

05H Controlling Microprocessor Error

8XH Slave Error

T3-3.1 391

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

20

Page 21

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.2.1.3 Fo rmat Track - 50H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

1 LBA 1 Drive Head (LBA 27-24)

Cylinder High (LBA 23-16)

Cylinder Low (LBA 15-8)

Count (LBA mode only)

This command writ es the desired head and cylinder of the selected dr ive with a vendor unique data

pattern (typically FFH or 00H). To remain host backward compatible, the ADC expects a sector buffer of

data from the host to fol low the command with the same protocol as the Write Sector(s) com mand

although the informat ion in the buffer is not used by the ADC. If LBA =1 then the num ber of secto rs to

format is taken from the Sec Cnt register (0=256). The use of this command is not recommended.

50H

X (LBA 7-0)

X

3.2.1.4 Identify Drive - ECH

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

The Identify Drive command enables the host to receive parameter information from the ADC. This

command has the same pro tocol as the Read Se ctor(s) comman d. The parameter words in the buffer

have the arrangement and meanings defined in Table 3-4. All reserved bits or words are zero. Table 3-4

gives the definition for each field in the Identify Drive Information.

ECH

XXXDrive X

X

X

X

X

X

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

21

Page 22

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

TABLE 3-4: IDENTIFY DRIVE INFORMATION

Word

Address

0 044AH 2 General configuration bi t-significant information

1 XXXXH 2 Default number of cylinders

2 0000H 2 Reserved

3 00XXH 2 Default number of heads

4 0000H 2 Reserved

5 0000H 2 Reserved

6 XXXXH 2 Default number of sectors per track

7-8 XXXXH 4 Number of sectors per card (Word 7 = MSW, Word 8 = LSW)

9 XXXXH 2 Vendor Unique

10-19 aaaa

20 0002H 2 Buffer type

21 XXXXH 2 Buffer size in 512 Byte increments

22 0004H 2 # of ECC bytes passed on Read/Write Long Commands

23-26 aaaa

27-46 aaaa

47 000XH 2 Maximum number of sectors on Read/Write Multiple command

48 0000H 2 Reserved

49 0200H 2 Capabilities

50 0000H 2 Reserved

51 0X00H 2 PIO data transfer cycle timing mode

52 0000H 2 Reserved

53 000XH 2 Translation parameters are valid

54 XXXXH 2 Current numbers of cylinders

55 XXXXH 2 Current numbers of heads

56 XXXXH 2 Current sectors per track

57-58 XXXXH 4 Current capacity in sectors (LBAs)(Word 57 = LSW, Word 58 = MSW)

59 010XH 2 Multiple sector setti ng

60-61 XXXXH 4 Total number of sectors addressable in LBA Mode

62-63 0000H 4 Reserved (DMA data transfer is not supported in ADC)

64 00XXH 2 Advanced PIO Transfer Mode Supported

65-66 0000H 4 Reserved

67 XXXXH 2 Minimum PIO transfer cycle time without flow control

68 XXXXH 2 Minimum PIO transfer cycle time with IORDY flow control

69-127 0000H 138 Reserved

128-159 0000H 64 Vendor unique bytes

160-255 0000H 192 Reserved

1. aaaa - any SST specific number

Default

Value

Total

Bytes Data Field Type Information

1

1

1

20 Serial number in ASCII. Big E ndian Byte Order in Word

8 Firmware revision in ASCII. Big Endian Byte Order in Word

40 Model number in ASCII. Big Endian Byte Order in Word

Data Sheet

T3-4.3 391

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

22

Page 23

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.2.1.4.1 General Configuration

This field informs th e host tha t this is a non-mag netic, hard se ctored, removable storage device with a

transfer rate greater than 10 MByte/sec and is not MFM encoded.

3.2.1.4.2 Default Number of Cylinders

This field contains th e number of tran slate d cylind ers in the default translat ion m ode. This value will be

the same as the number of cylinders.

3.2.1.4.3 Default Number of Heads

This field contains the number of translated heads in the default translation mode.

3.2.1.4.4 Default Number of Sectors per Track

This field contains the number of sectors per track in the default translation mode.

3.2.1.4.5 Number of Sectors

This field contains the number of sectors per ADC. This double word value is also the first invalid

address in LBA translation mode.

3.2.1.4.6 Memory Serial Number

The contents of this field are right justified and padded with spaces (20H).

3.2.1.4.7 Buffer Type

This field defines the buffer capability:

0002H: a dual ported multi-sector buffer capable of simultaneous data transfers to or from the host and the ADC.

3.2.1.4.8 Buffer Size

This field defines the buffer capacity in 512 Byte increm ents. SST’s ADC has up to 2 sector data buffer

for host interface.

3.2.1.4.9 ECC Count

This field defines the number of ECC b y tes used on each sector in th e Re ad and Write Long commands .

3.2.1.4.10 Firmware Revision

This field contains the revision of the firmware for this product.

3.2.1.4.11 Model Number

This field contains the model number for this product and is left justified and padded with spaces (20H).

3.2.1.4.12 Read/Write Multiple Sector Count

This field contains the max imum number of sectors that can be read or written per interr upt using the

Read Multiple or Write Multiple commands.

3.2.1.4.13 Capabilities

Bit 13: Standby Timer Set to 0, forces sleep mode when host is inactive.

Bit 11: IORDY Support Set to 0, indicates that this device may support IORDY operation.

Bit 9: LBA support Set to 1, SST’s ADCs support LBA mode addressing.

Bit 8: DMA Support This bit is set to 0. DMA mode is not supported.

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

23

Page 24

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

3.2.1.4.14 PIO Data Transfer Cycle Timing Mode

This field defines the mode for PIO data transfer. ADC supports up to PIO Mode-4.

3.2.1.4.15 Translation Parameters Valid

If bit 0 is 1, it indicat es that words 54 to 58 are valid and r eflec t the c urrent num ber of cy linde rs, heads

and sectors. If bit 1 is 1, it indicates that words 64 to 70 are valid to support PIO Mode-3 and 4.

3.2.1.4.16 Current Number of Cylinders, Heads, Sectors/Track

These fields contain s the current numb er of user addres sable Cylinders, Heads, and Sec tors/Track in

the current translation mode.

3.2.1.4.17 Current Capacity

This field contains the product of the current cylinders times heads times sectors.

3.2.1.4.18 Multiple Sector Setting

This field contains a validity flag in the Odd Byte and the current number of sectors that can be

transferred per interrupt for R/W Multiple in the Even Byte. The Odd Byte is always 01H which indicates

that the Even Byte is always valid.

The Even Byte value depends on the value set by the Set Multiple comma nd. The Even Byte of this

word by default contains a 00H which indicates that R/W Multiple commands are not valid.

ATA-Disk Chip

Data Sheet

3.2.1.4.19 Total Sectors Addressable in LBA Mode

This field contains the number of sectors addressable for the ADC in LBA mode only.

3.2.1.4.20 Advanced PIO Data Transfer Mode

ADC supports up to PIO Mode-4.

3.2.1.4.21 Minimum PIO Transfer Cycle Time Without Flow Control

The ADC’s minimum cycle time is 120 ns.

3.2.1.4.22 Minimum PIO Transfer Cycle Time With IORDY

The ADC’s minimum cycle time is 120 ns, e.g., PIO Mode-4.

3.2.1.5 Idle - 97H or E3H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

XDrive X

Timer Count (5 msec increments)

97H or E3H

X

X

X

X

This command causes the ADC to set BSY, enter the Idle Mode, clear BSY and generate an interrupt. If

the sector count is non-zero, it is inter p reted a s a timer co unt wi th each c oun t bei ng 5 mi ll isec ond s an d

the automatic power down mode is enabled. If the sector count is zero, the automatic power down

mode is also enabled, the t imer co unt is set to 3, with each cou nt b eing 5 ms. Note that this tim e bas e

(5 msec) is different from the ATA specification.

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

24

Page 25

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.2.1.6 Idle Immediate - 95H o r E1H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

This command causes the ADC to set BSY, enter the Idle Mode, clear BSY and generate an interrupt.

3.2.1.7 Initialize Drive Parameters - 91H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

X 0 X Drive Max Head (no. of heads-1)

XDrive X

95H or E1H

X

X

X

X

X

91H

X

X

X

Number of Sectors

X

This command enables the host to set the number of sectors per track and the number of head s per

cylinder. Only the Sector Count and the Drive/Head registers are used by this command.

3.2.1.8 Read Buffer - E4H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

The Read Buffer command enables the host to read the c urrent contents of the ADC’s sector buffer.

This command has the same protocol as the Read Sector(s) command

E4H

XDrive X

X

X

X

X

X

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

25

Page 26

3.2.1.9 Read Multiple - C4H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

The Read Multiple command is similar to the Read Sector(s) command. Interrupts are not generated on

every sector, but on the transfer of a block which contains the number of sectors defined by a Set

Multiple command.

Command execution is identical to the Read Sectors operation except that the number of sectors

defined by a Set Multip le comma nd are transferred with out int ervening interr upts. DRQ qual ification o f

the transfer is required only at the start of the data block, not on each sector.

The block count of sectors to be transferred witho ut intervening interr upts is programmed by the Set

Multiple Mode command, which must be executed prior to the Read Multiple command. When the Read

Multiple command is issued, the Sector Count Register contains the number of sectors (not the number

of blocks or the block count) requested. If the number of requested sectors is not evenly divisible by the

block count, as many full blocks as pos sible are transferred, followed by a final, par tial block transfer.

The partial block transfer is for n sectors, where

If the Read Multiple command is attempted before the Set Multiple Mode command has been executed

or when Read Multiple commands are disabled, the Read Multiple operation is rejected with an Aborted

Command error. Disk errors encounter ed during Read Multipl e c om man ds are pos ted at the beg in ning

of the block or partial block transfer, but DRQ is still set and the data transfer will take place as it

normally would, including transfer of corrupted data, if any.

Interrupts are ge nerated when DRQ is set at the beginning of each block or par tial block. The error

reporting is the same as that on a Read Sector(s) Command. This command reads from 1 to 256

sectors as specified in the Sector Count register. A sector count of 0 requests 256 sectors. The transfer

begins at the sector specified in the Sector Number Register.

At command compl etion, the C ommand Blo ck Register s con tain t he c ylinder, head and sector number

of the last sector read.

If an error occurs, the r ead terminates at the s ector where the error occurre d. The Command Block

Registers contain the cylind er, head and sect or number of the sector where the error occurred. The

flawed data is pending in the sector buffer.

Subsequent blocks or par tial blocks are transferred only if the error was a correctable data error. All

other errors cause the command to stop after transfer of the block which contained the error.

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

C4H

1 LBA 1 Drive Head (LBA 27-24)

Cylinder High (LBA 23-16)

Cylinder Low (LBA 15-8)

Sector Number (LBA 7-0)

Sector Count

X

n = remainder (sector count/block count).

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

26

Page 27

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.2.1.10 Read Long Sector - 22H or 23H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

1 LBA 1 Drive Head (LBA 27-24)

The Read Long command performs similarly to the Read Sector(s) command except that it returns 516

Bytes of data instead of 512 Bytes. Du ring a Read Lon g command, th e ADC does not check the EC C

bytes to determine if there has been a data error. Only single sector read long operations are

suppor ted. The transfer consis ts of 512 Bytes of da ta trans ferred in Word-Mode followed by 4 Bytes o f

ECC data transferred in Byte-Mode. This command has the same protocol as the Read Sector(s)

command. Use of this command is not recommended.

22H or 23H

Cylinder High (LBA 23-16)

Cylinder Low (LBA 15-8)

Sector Number (LBA 7-0)

X

X

3.2.1.11 Read Sectors - 20H or 21H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

1 LBA 1 Drive Head (LBA 27-24)

This command reads fro m 1 to 256 s ectors as speci fied in th e Sect or Count regis ter. A sector count of

0 requests 256 sectors. The transfer begins at the sector specified in th e Sector Number Register.

When this command is issu ed and after each secto r of da ta (except the la st one) has been read by the

host, the ADC sets BSY, puts th e sector of data i n the buffer, sets DRQ, clears BSY, and gen erates an

interrupt. The host then reads the 512 Bytes of data from the buffer.

At command compl etion, the C ommand Blo ck Register s con tain t he c ylinder, head and sector number

of the last sector read. If an err or occurs, the read termina tes at the sector where the error oc curred.

The Command Block Re gisters con tain the cylind er, head, and sector number of the secto r where th e

error occurred. The flawed data is pending in the sector buffer.

20H or 21H

Cylinder High (LBA 23-16)

Cylinder Low (LBA 15-8)

Sector Number (LBA 7-0)

Sector Count

X

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

27

Page 28

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

3.2.1.12 Read Verify Sector(s) - 40H or 41H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

This command is i den tic al to th e R ead S ec tor s co mm and, except t hat DRQ i s never set and no d ata is

transferred to the host. When the command is accepted, the ADC sets BSY.

When the requested sectors have been verified, the ADC clears BSY and generates an interrupt. Upon

command complet ion , t he Com man d Bl ock Regis ter s c on tai n the c ylin der, head, and sec tor num ber o f

the last sector verified.

If an error occurs, the verify terminates at the sector where the error occurs. The Command Block

Registers contain the cylind er, head and sect or number of the sector where the error occurred. The

Sector Count Register contains the number of sectors not yet verified.

1 LBA 1 Drive Head (LBA 27-24)

ATA-Disk Chip

Data Sheet

40H or 41H

Cylinder High (LBA 23-16)

Cylinder Low (LBA 15-8)

Sector Number (LBA 7-0)

Sector Count

X

3.2.1.13 R ecalibrate - 1XH

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

This command is effectively a NOP command to the ADC and is provided for compatibility purposes.

3.2.1.14 Seek - 7XH

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

1XH

1LBA1Drive X

X

X

X

X

X

7XH

1 LBA 1 Drive Head (LBA 27-24)

Cylinder High (LBA 23-16)

Cylinder Low (LBA 15-8)

X (LBA 7-0)

X

X

This command is effectively a NOP command to the ADC although it does perform a range ch eck of

cylinder and head or LBA address and returns an error if the address is out of range.

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

28

Page 29

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.2.1.15 Set Features - EFH

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

XDrive X

This command is use d by the host to establish or selec t certain features. Table 3-5 defines all features

that are supported.

TABLE 3-5: FEATURES SUPPORTED

Feature Operation

01H Enable 8-bit data transfers.

55H Disable Read Look Ahead.

66H Disable Power on Reset (POR) establishment of defaults at software Reset.

69H NOP - Accepted for backward compatibility.

81H Disable 8-bit data transfer.

96H NOP - Accepted for backward compatibility.

97H Accepted for backward compatibility. Use of this Feature is not recommended.

9AH NOP - accepted for compatibility.

BBH 4 Bytes of data apply on Read/Write Long commands.

CCH Enable Power on Reset (POR) establishment of defaults at software Reset.

EFH

X

X

X

Config

Feature

T3-5.0 391

Features 01H and 81H are used to enable and clear 8-bit data transfer mode. If the 01H feature

command is issued all data transfers will occur on the low order D7-D0 data bus and the IOIS16# signal

will not be asserted for data register accesses.

Features 55H and BBH are the default features for the ADC; thus, th e ho st do es not have to issue th is

command with these features unless it is necessary for compatibility reasons.

Features 66H and CCH can be used to enable and disable whether the Power On Reset (POR)

Defaults will be set when a software Reset occurs.

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

29

Page 30

3.2.1.16 Set Multiple Mo de - C6H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

This command enables the ADC to perform Read and Write Multiple operations and establish es the

block count for these commands. The Sector Count Registe r is loaded wit h the number of sectors per

block. Upon receipt of the command, the ADC sets BSY to 1 and checks the Sector Count Register.

If the Sector Count Register contains a valid value and the block count is supported, the value is loaded

for all subsequent Read Mu ltiple and Wri te Multiple command s and execution of those command s is

enabled. If a block count is not supported, an Aborted Command error is posted, and Read Multiple and

Write Multiple c ommands are d isabled. If the Sector Cou nt Register con tains 0 when th e command is

issued, Read and W rite Multiple com mands are di sabled. At power on, o r after a h ardware or (u nless

disabled by a Set Feature command) software reset, the default mode is Read and Write Multiple

disabled.

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

C6H

XDrive X

X

X

X

Sector Count

X

3.2.1.17 Set Sleep Mode - 99H or E6H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

This command causes the ADC to set BSY , enter the Sleep mode, clear BSY and generate an interrupt.

Recovery from sleep mode is accomplished by simply is suing another comm and (a reset is per mitted

but not required). Sleep mode is also entered when int er nal timers expire so the host does not nee d to

issue this command except whe n it wishes to en ter Sleep mode immed iately. The default value fo r the

timer is 15 milliseconds.

99H or E6H

XDrive X

X

X

X

X

X

©2001 Silicon Storage Technology, Inc. S71167-05-000 9/01 391

30

Page 31

ATA-Disk Chip

SST58SD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LD008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Data Sheet

3.2.1.18 Standby - 96H or E2H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

XDrive X

This command causes the ADC to set BSY, enter the Sleep mode (which corresponds to the ATA

“Standby” Mode), clear BSY and return the interrupt immediately. Recovery from sleep mode is

accomplished by simply issuing another command (a reset is not required).

3.2.1.19 Standby Immediate - 94H or E0H

96H or E2H

X

X

X

X

X

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

This command causes the ADC to set BSY, enter the Sleep mode (which corresponds to the ATA

“Standby” Mode), clear BSY and return the interrupt immediately. Recovery from sleep mode is

accomplished by simply issuing another command (a reset is not required).

3.2.1.20 Write Buffer - E8H

Bit ->76543210

Command (7)

C/D/H (6)

Cyl High (5)

Cyl Low (4)

Sec Num (3)

Sec Cnt (2)

Feature (1)

94H or E0H

XDrive X

X

X

X

X

X

E8H

XDrive X

X

X

X

X

X

The Write Buffer command enables the host to overwrite content s of the ADC’s sector buffer with any

data pattern desired. This command has the same protocol as the Write Sector(s) command and