Page 1

查询SSM2301 供应商查询SSM2301 供应商

Filterless High Efficiency Mono 1.4 W

Preliminary Technical Data

FEATURES

Filterless Class-D amplifier with built-in output stage

1.4 W into 8 Ω at 5.0 V supply with less than 1% THD

85% efficiency at 5.0 V, 1.4 W into 8 Ω speaker

Better than 98 dB SNR (signal-to-noise ratio)

Single-supply operation from 2.5 V to 5.0 V

20 nA ultralow shutdown current

Short-circuit and thermal protection

Available in 8-lead, 3 mm × 3 mm LFCSP

Pop-and-click suppression

Built-in resistors reduce board component count

Fixed and user-adjustable gain configurations

APPLICATIONS

Mobile phones

MP3 players

Portable gaming

Portable electronics

Educational toys

GENERAL DESCRIPTION

The SSM2301 is a fully integrated, high efficiency, Class-D audio

amplifier. It is designed to maximize performance for mobile

phone applications. The application circuit requires a minimum

of external components and operates from a single 2.5 V to 5.0 V

supply. It is capable of delivering 1.4 W of continuous output

power with less than 1% THD + N driving an 8 Ω load from a

5.0 V supply.

The SSM2301 features a high efficiency, low noise modulation

scheme that does not require any external LC output filters. The

modulation continues to provide high efficiency even at low

Class-D Audio Amplifier

SSM2301

output power. It operates with 85% efficiency at 1.4 W into 8 Ω

from a 5.0 V supply and has a signal-to-noise ratio (SNR) that is

better than 93 dB. Spread-spectrum modulation is used to

provide lower EMI-radiated emissions compared with other

Class-D architectures.

The SSM2301 has a micropower shutdown mode with a

maximum shutdown current of 30 nA. Shutdown is enabled by

applying a logic low to the

The device also includes pop-and-click suppression circuitry.

This minimizes voltage glitches at the output during turn-on

and turn-off, thus reducing audible noise on activation and

deactivation.

The fully differential input of the SSM2301 provides excellent

rejection of common-mode noise on the input. Input coupling

capacitors can be omitted if the dc input common-mode voltage

is approximately V

DD

/2.

The SSM2301 also has excellent rejection of power supply noise,

including noise caused by GSM transmission bursts and RF

rectification. PSRR is typically 63 dB at 217 Hz.

The gain can be set to 6 dB or 12 dB utilizing the gain control

select pin connected respectively to ground or V

also be adjusted externally by using an external resistor.

The SSM2301 is specified over the comercial temperature range

(−40°C to +85°C). It has built-in thermal shutdown and output

short-circuit protection. It is available in an 8-lead, 3 mm × 3 mm

lead-frame chip scale package (LFCSP).

SD

pin.

. Gain can

DD

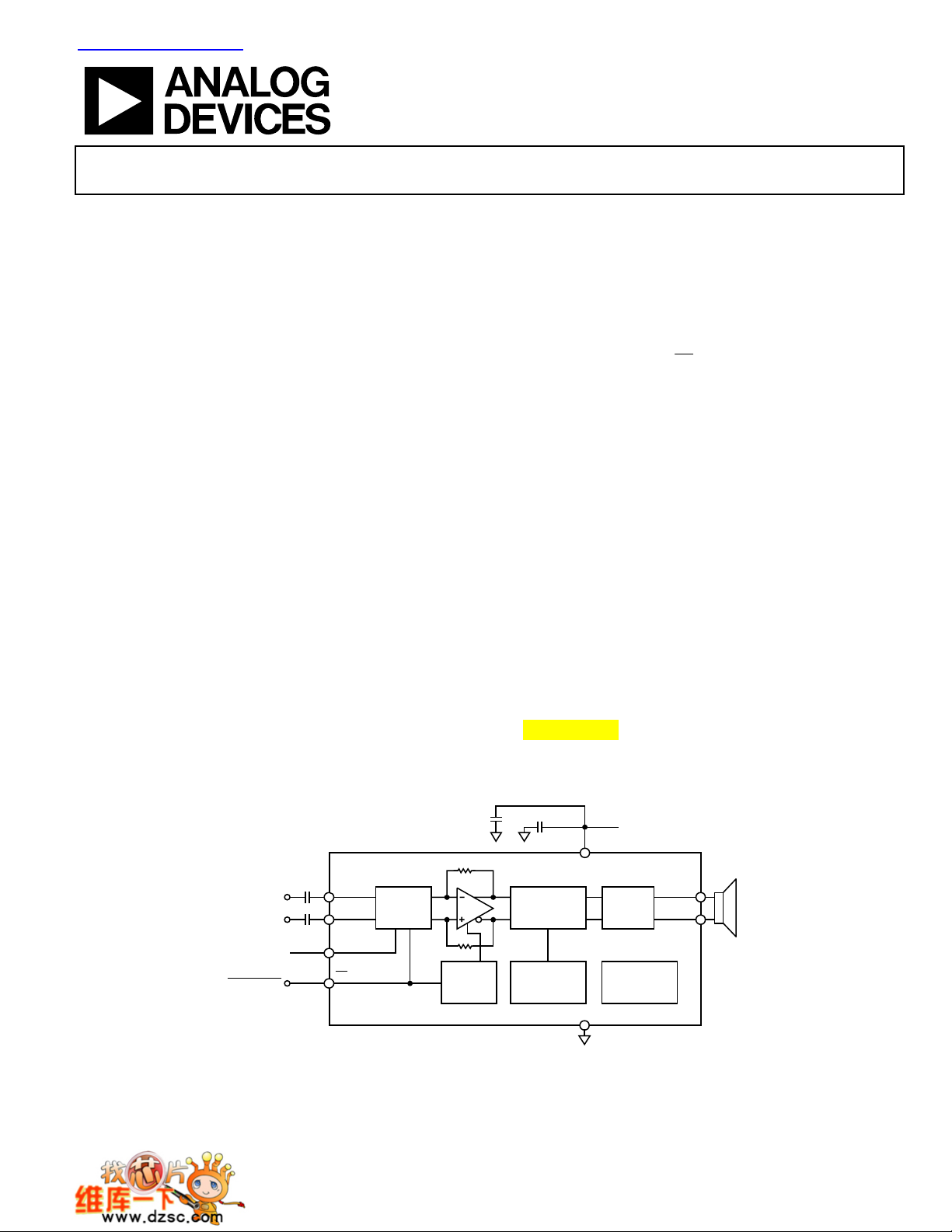

FUNCTIONAL BLOCK DIAGRAM

SSM2301

1

0.01µF

AUDIO IN+

AUDIO IN–

SHUTDOWN

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

IN+

IN–

1

0.01µF

GAIN

SD

1

INPUT CAPS ARE OPTIONAL IF INPUT DC COMMON-MODE

VOLTAGE IS APPROXIMATELY V

GAIN

CONTROL

DD

10µF

BIAS

/2.

Figure 1.

0.1µF

VDD

MODULATOR

OSCILLAT OR

GND

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

VBATT

2.5V TO 5. 0V

FET

DRIVER

POP/CLICK

SUPRESSION

OUT+

OUT–

06163-001

Page 2

SSM2301 Preliminary Technical Data

TABLE OF CONTENTS

Features.............................................................................................. 1

Pop-and-Click Suppression ...................................................... 11

Applications....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 4

Thermal Resistance ...................................................................... 4

ESD Caution.................................................................................. 4

Pin Configuration and Function Descriptions............................. 5

Typical Performance Characteristics ............................................. 6

Typical Application Circuits............................................................ 9

Application Notes........................................................................... 11

Overview...................................................................................... 11

Gain Selection ............................................................................. 11

Layout .......................................................................................... 12

Input Capacitor Selection.......................................................... 12

Proper Power Supply Decoupling............................................ 12

Evaluation Board Information...................................................... 13

Introduction................................................................................ 13

Operation .................................................................................... 13

SSM2301 Application Board Schematic.................................. 14

SSM2301 Stereo Class-D Amplifier Evaluation Module

Component List.......................................................................... 15

SSM2301 Application Board Layout........................................ 16

Outline Dimensions....................................................................... 17

Ordering Guide .......................................................................... 17

REVISION HISTORY

7/06—Revision 0: Initial Version

Page 3

Preliminary Technical Data SSM2301

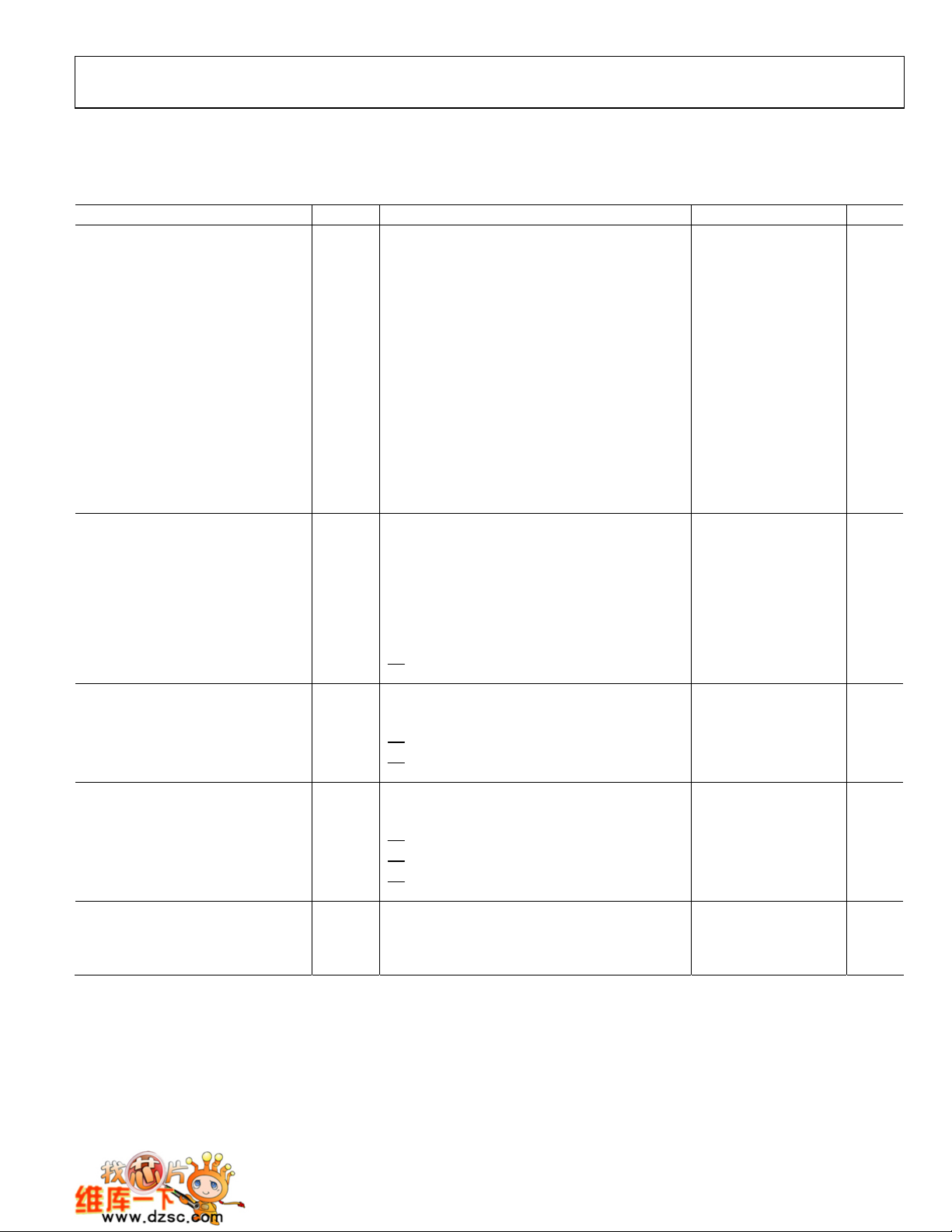

SPECIFICATIONS

VDD = 5.0 V, TA = 25oC, RL = 8 Ω, unless otherwise noted

Table 1.

Parameter Symbol Conditions Min Typ Max Unit

DEVICE CHARACTERISTICS

Output Power P

O

R

R

R

R

R

Efficiency η P

Total Harmonic Distortion + Noise THD + N PO = 1 W into 8 Ω, f = 1 kHz, VDD = 5.0 V 0.1 %

P

Input Common-Mode Voltage Range VCM 1.0 VDD − 1 V

Common-Mode Rejection Ratio CMRR

Average Switching Frequency fSW 1.8 MHz

Differential Output Offset Voltage V

OOS

POWER SUPPLY

Supply Voltage Range V

DD

Power Supply Rejection Ratio PSRR VDD = 2.5 V to 5.0 V, 50 Hz, input floating/ground 70 85 dB

PSRR

Supply Current I

SY

V

V

Shutdown Current ISD

GAIN CONTROL

Closed-Loop Gain Av0 GAIN pin = 0 V 6 dB

Av1 GAIN pin = VDD 12 dB

Differential Input Impedance Z

IN

SHUTDOWN CONTROL

Input Voltage High V

Input Voltage Low V

Turn-On Time t

Turn-Off Time t

Output Impedance Z

IH

IL

WU

SD

OUT

NOISE PERFORMANCE

Output Voltage Noise en

Signal-to-Noise Ratio SNR P

RL = 8 Ω, THD = 1%, f = 1 kHz, 20 kHz BW, VDD = 5.0 V 1.4 W

= 8 Ω, THD = 1%, f = 1 kHz, 20 kHz BW, VDD = 3.6 V 0.615 W

L

= 8 Ω, THD = 1%, f = 1 kHz, 20 kHz BW, VDD = 2.5 V 0.275 W

L

= 8 Ω, THD = 10%, f = 1 kHz, 20 kHz BW, VDD = 5.0 V 1.53 W

L

= 8 Ω, THD = 10%, f = 1 kHz, 20 kHz BW, VDD = 3.6 V 0.77 W

L

= 8 Ω, THD = 10%, f = 1 kHz, 20 kHz BW, VDD = 2.5 V 0.35 W

L

=1.4 W, 8 Ω, VDD = 5.0 V 85 %

OUT

= 0.5 W into 8 Ω, f = 1 kHz, VDD = 3.6 V 0.04 %

O

GSM VCM

= 2.5 V ± 100 mV at 217 Hz 55 dB

G = 6 dB; G = 12 dB 2.0 mV

Guaranteed from PSRR test 2.5 5.0 V

GSM

V

= 100 mV at 217 Hz, inputs ac GND,

RIPPLE

= 0.01 μF, input referred

C

IN

63 dB

VIN = 0 V, no load, VDD = 5.0 V 5.5 mA

= 0 V, no load, VDD = 3.6 V 4.5 mA

IN

= 0 V, no load, VDD = 2.5 V 4.0 mA

IN

SD

= GND

SD

= VDD,

SD

= GND

20 nA

150 KΩ

210 KΩ

ISY ≥ 1 mA 1.2 V

ISY ≤ 300 nA 0.5 V

SD

rising edge from GND to VDD

SD

falling edge from VDD to GND

SD

= GND

= 2.5 V to 5.0 V, f = 20 Hz to 20 kHz, inputs are

V

DD

ac grounded, sine wave, A

= 1.4 W, RL = 8 Ω 98 dB

OUT

= 6 dB, A weighting

V

30 ms

5 μs

>100 KΩ

35 μV

Page 4

SSM2301 Preliminary Technical Data

ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings apply at 25°C, unless otherwise noted.

Table 2.

Parameter Rating

Supply Voltage 6 V

Input Voltage V

Common-Mode Input Voltage V

Storage Temperature Range −65°C to +150°C

Operating Temperature Range −40°C to +85°C

Junction Temperature Range −65°C to +165°C

Lead Temperature Range

(Soldering, 60 sec)

DD

DD

300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 3. Thermal Resistance

Package Type θJA θ

8-lead, 3 mm × 3 mm LFCSP 62 TBD °C/W

Unit

JC

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Page 5

Preliminary Technical Data SSM2301

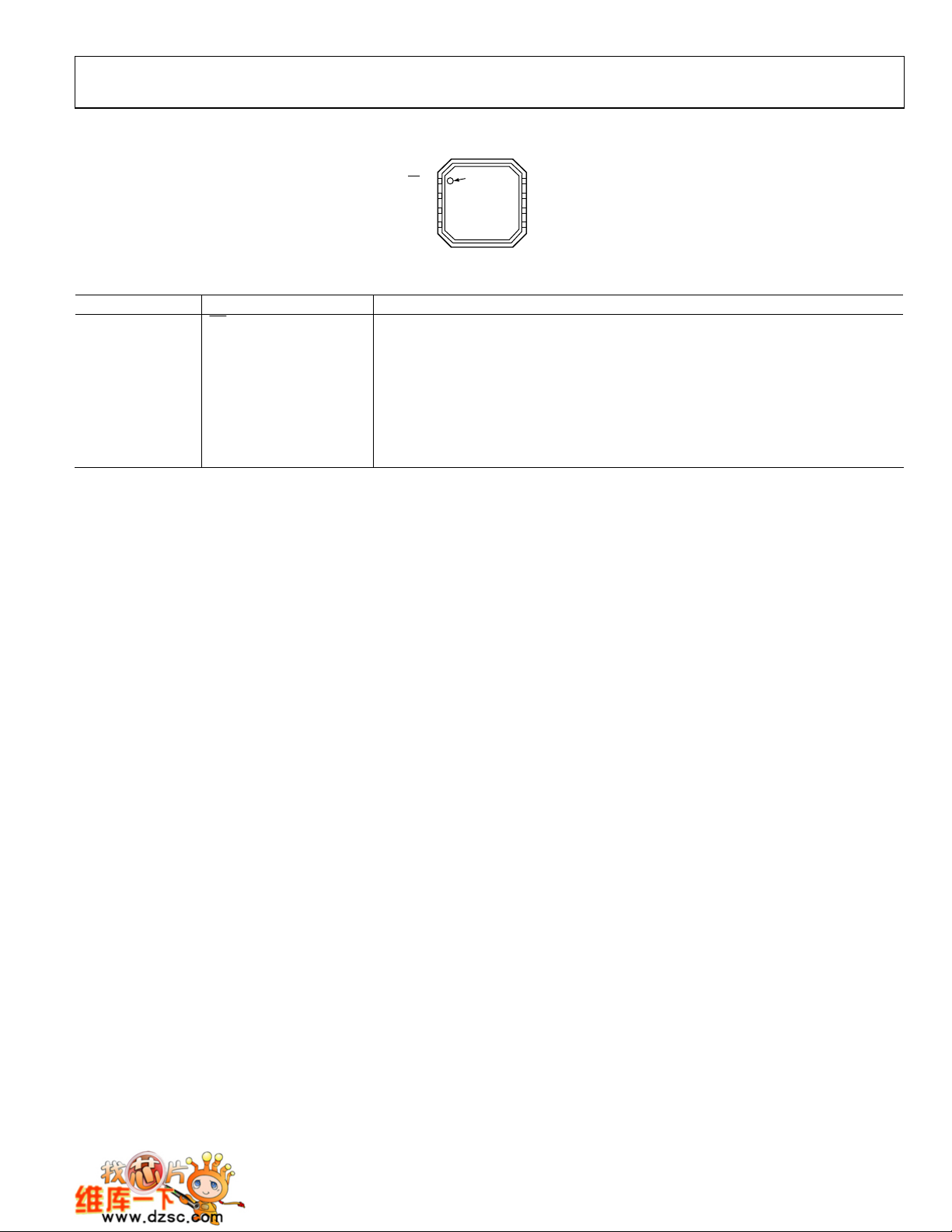

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

2GAIN

3IN+

(Not to Scale)

4IN–

PIN 1

INDICATO R

SSM2301

TOP VIEW

8OUT–

7GND

6VDD

5OUT+

06163-002

SD

Figure 2. SSM2301 LFCSP Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1

SD

Shutdown Input. Active low digital input.

2 GAIN Gain Selection. Digital input.

3 IN+ Noninverting Input.

4 INL− Inverting Input.

5 OUT+ Noninverting Output.

6 VDD Power Supply.

7 GND Ground.

8 OUT− Inverting Output.

Page 6

SSM2301 Preliminary Technical Data

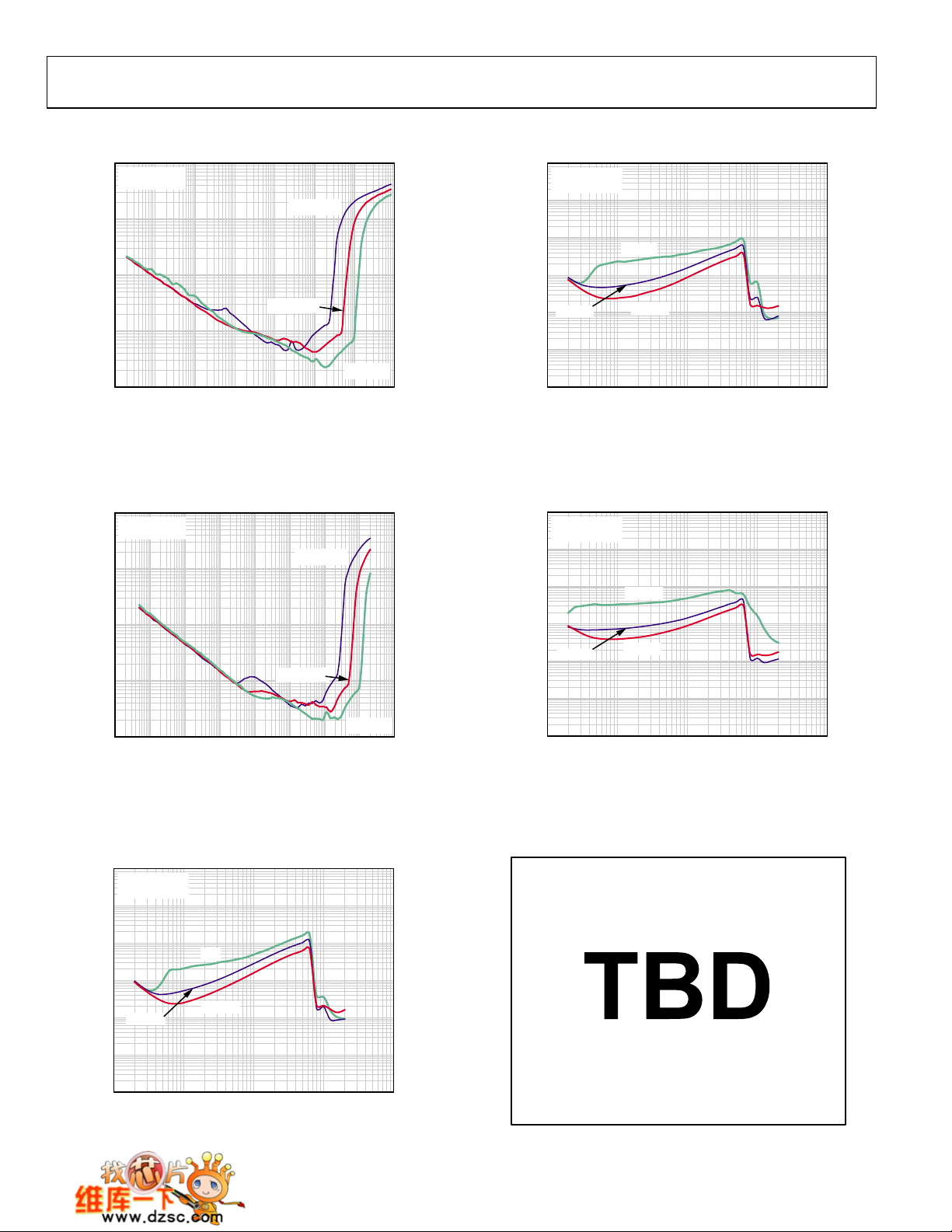

TYPICAL PERFORMANCE CHARACTERISTICS

100

RL = 8Ω, 33µH

GAIN = 12dB

10

1

THD + N (%)

0.1

0.01

0.000001 0.00010.00001 10

0.001 0.01 0.1 1

OUTPUT POWER (W)

Figure 3. THD + N vs. Output Power into 8 Ω, A

VDD = 2.5V

VDD = 3.6V

VDD = 5V

= 12 dB

V

06163-003

100

VDD = 3.6V

= 8Ω, 33µH

R

L

10

1

0.1

THD + N (%)

250mW

0.01

0.001

0.0001

10 100k

Figure 6. THD + N vs. Frequency, V

500mW

125mW

100 1k 10k

FREQUENCY (Hz)

= 3.6 V

DD

06163-006

100

RL = 8Ω, 33µH

GAIN = 6dB

10

1

THD + N (%)

0.1

0.01

0.000001 0.0001

0.0000001

0.00001 10

0.001

OUTPUT POWER (W)

Figure 4. THD + N vs. Output Power into 8 Ω, A

100

VDD = 5V

= 8Ω, 33µH

R

L

10

1

0.1

THD + N (%)

0.01

500mW

1W

250mW

VDD = 2.5V

VDD = 3.6V

0.01

0.1

VDD = 5V

1

= 6 dB

V

100

VDD = 2.5V

R

= 8Ω, 33µH

L

10

1

0.1

THD + N (%)

125mW

0.01

0.001

0.0001

10 100k

06163-004

Figure 7. THD + N vs. Frequency, V

250mW

750mW

100 1k 10k

FREQUENCY (Hz)

= 2.5 V

DD

06163-007

0.001

0.0001

10 100k

100 1k 10k

FREQUENCY (Hz)

Figure 5. THD + N vs. Frequency, V

= 5.0 V

DD

06163-005

Figure 8. Supply Current vs. Supply Voltage, No Load

Page 7

Preliminary Technical Data SSM2301

12

10

8

VDD = 5V

6

4

SHUTDOWN CURRENT ( µA)

2

0

0.1 0. 2 0.3 0.4 0.5 0.6 0.7

00.8

SHUTDOWN VOLTAGE (V)

VDD = 2.5V

VDD = 3.6V

06163-009

Figure 9. Supply Current vs. Shutdown Voltage

0.9

VDD = 3.6V

R

= 8Ω, 33µH

L

0.8

0.7

0.6

0.5

0.4

0.3

POWER DISSIPATIO N (W)

0.2

0.1

0

0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 1.1 1.2 1.3

01.4

OUTPUT POWER (W)

Figure 12. Power Dissipation vs. Output Power at V

1.6

VDD = 5V

= 8Ω, 33µH

R

L

1.4

= 3.6 V

DD

06163-012

1.2

1.0

0.8

0.6

POWER DISSIPATIO N (W)

0.4

0.2

0

0.10.20.30.40.50.60.70.80.91.01.11.21.31.41.51.6

01.7

Figure 10. Maximum Output Power vs. Supply Voltage

100

90

VDD = 2.5V

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

01.4

VDD = 3.6V

0.2 0.4 0.6 0.8 1.0 1.2

OUTPUT POWER (W)

RL = 8Ω, 33µH

VDD = 5V

06163-011

Figure 13. Power Dissipation vs. Output Power at V

350

RL = 8Ω, 33µH

300

250

200

VDD = 2.5V

150

100

SUPPLY CURRENT (mA)

50

0

01.6

Figure 11. Efficiency vs. Output Power into 8 Ω

Figure 14. Output Power vs. Supply Current, One Channel

OUTPUT POWER (W)

DD

VDD = 5V

VDD = 3.6V

0.2 0. 4 0.6 0.8 1.0 1.2 1.4

OUTPUT POWER (W)

= 5.0 V

06163-013

06163-014

Page 8

SSM2301 Preliminary Technical Data

0

–10

–20

–30

–40

–50

PSRR (dB)

–60

–70

–80

–90

–100

10 100k

100 1k 10k

FREQUENCY (Hz)

Figure 15. Power Supply Rejection Ratio vs. Frequency

0

RL = 8Ω, 33µH

GAIN = 6dB

–10

–20

–30

–40

CMRR (dB)

–50

–60

–70

–80

10 100k

100 1k 10k

FREQUENCY (Hz)

Figure 16. Common-Mode Rejection Ratio vs. Frequency

06163-015

06163-016

7

6

5

4

SD INPUT

3

2

VOLTAGE

1

0

–1

–2

–10 90

–5 0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 75 80 85

OUTPUT

TIME (ms)

Figure 17. Turn-On Response

7

6

5

SD INPUT

4

3

2

VOLTAGE

1

0

–1

–2

–20 180

0 20 40 60 80 100 120 140 160

OUTPUT

TIME (ms)

Figure 18. Turn-Off Response

06163-017

06163-018

Page 9

Preliminary Technical Data SSM2301

TYPICAL APPLICATION CIRCUITS

0.1µF

MODULATOR

OSCILLAT OR

VDD

GND

VBATT

2.5V TO 5. 0V

FET

DRIVER

POP/CLICK

SUPRESSION

OUT+

OUT–

06163-019

AUDIO IN+

AUDIO IN–

V

DD

SHUTDOWN

10µF

SSM2301

1

0.01µF

IN+

IN–

1

0.01µF

GAIN

SD

1

INPUT CAPS ARE OPTIONAL IF INPUT DC COMMON-MODE

VOLTAGE IS APPROXIMATELY V

GAIN

CONTROL

BIAS

/2.

DD

Figure 19. Differential Input Configuration, Gain = 12 dB

0.1µF

MODULATOR

VDD

VBATT

2.4V TO 5. 0V

FET

DRIVER

OUT+

OUT–

AUDIO IN

0.01µF

0.01µF

SSM2301

IN+

IN–

GAIN

GAIN

CONTROL

10µF

SHUTDOWN

SD

BIAS

OSCILLAT OR

GND

POP/CLICK

SUPRESSION

6163-020

Figure 20. Single-Ended Input Configuration, Gain = 6 dB

EXTERNAL GAIN SETTINGS = 20 log[4/(1 + R/150kΩ)]

SSM2301

1

0.01µF

R

AUDIO IN+

AUDIO IN–

SHUTDOWN

0.01µF

IN+

R

IN–

1

V

DD

GAIN

SD

1

INPUT CAPS ARE OPTIONAL IF INPUT DC COMMON-MODE

VOLTAGE IS APPROXIMATELY V

GAIN

CONTROL

Figure 21. Differential Input Configuration, User-Adjustable Gain

10µF

BIAS

/2.

DD

0.1µF

MODULATOR

OSCILLAT OR

VDD

GND

VBATT

2.4V TO 5. 0V

FET

DRIVER

POP/CLICK

SUPRESSION

OUT+

OUT–

06163-021

Page 10

SSM2301 Preliminary Technical Data

EXTERNAL GAIN SETTINGS = 20 log[4/(1 + R/150kΩ)]

10µF

0.1µF

VBATT

2.4V TO 5. 0V

SSM2301

0.01µF

R

AUDIO IN

0.01µF

SHUTDOWN

IN+

R

IN–

V

DD

GAIN

SD

GAIN

CONTROL

Figure 22. Single-Ended Input Configuration, User-Adjustable Gain

EXTERNAL GAIN SETTINGS = 20 log[2/(1 + R/150kΩ)]

SSM2301

1

0.01µF

R

AUDIO IN+

AUDIO IN–

SHUTDOWN

0.01µF

IN+

R

IN–

1

GAIN

SD

GAIN

CONTROL

BIAS

10µF

BIAS

MODULATOR

OSCILLAT OR

0.1µF

MODULATOR

OSCILLAT OR

VDD

GND

VDD

GND

FET

DRIVER

POP/CLICK

SUPRESSION

VBATT

2.4V TO 5. 0V

FET

DRIVER

POP/CLICK

SUPRESSION

OUT+

OUT–

OUT+

OUT–

6163-022

1

INPUT CAPS ARE OPTIONAL IF INPUT DC COMMON-MODE

VOLTAGE IS APPROXIMATELY V

/2.

DD

06163-023

Figure 23. Differential Input Configuration, User-Adjustable Gain

EXTERNAL GAIN SETTINGS = 20 log[2/(1 + R/150kΩ)]

SSM2301

0.01µF

R

AUDIO IN

0.01µF

SHUTDOWN

IN+

IN–

R

GAIN

SD

GAIN

CONTROL

Figure 24. Single-Ended Input Configuration, User-Adjustable Gain

10µF

BIAS

0.1µF

MODULATOR

OSCILLAT OR

VDD

GND

VBATT

2.4V TO 5. 0V

FET

DRIVER

POP/CLICK

SUPRESSION

OUT+

OUT–

6163-024

Page 11

Preliminary Technical Data SSM2301

APPLICATION NOTES

OVERVIEW

The SSM2301 mono Class-D audio amplifier features a filterless

modulation scheme that greatly reduces the external components

count, conserving board space and thus reducing systems cost.

The SSM2301 does not require an output filter, but instead relies

on the inherent inductance of the speaker coil and the natural

filtering of the speaker and human ear to fully recover the audio

component of the square-wave output. While most Class-D amplifiers use some variation of pulse-width modulation (PWM), the

SSM2301 uses a Σ-Δ modulation to determine the switching

pattern of the output devices. This provides a number of important

benefits. Σ-Δ modulators do not produces a sharp peak with

many harmonics in the AM frequency band, as pulse-width

modulators often do. Σ-Δ modulation provides the benefits of

reducing the amplitude of spectral components at high frequencies;

that is, reducing EMI emission that might otherwise be radiated

by speakers and long cable traces. The SSM2301 also offers

protection circuits for overcurrent and temperature protection.

GAIN SELECTION

Pulling the GAIN pin high of the SSM2301 sets the gain of the

speaker amplifier to 12 dB; pulling it low sets the gain of the

speaker amplifier to 6 dB.

POP-AND-CLICK SUPPRESSION

Voltage transients at the output of audio amplifiers can occur when

shutdown is activated or deactivated. Voltage transients as low

as 10 mV can be heard as an audio pop in the speaker. Clicks

and pops can also be classified as undesirable audible transients

generated by the amplifier system, therefore as not coming from

the system input signal. Such transients can be generated when

the amplifier system changes its operating mode. For example, the

following can be sources of audible transients: system power-up/

power-down, mute/unmute, input source change, and sample rate

change. The SSM2301 has a pop-and-click suppression architecture

that reduces these output transients, resulting in noiseless activation

and deactivation.

It is possible to adjust the SSM2301 gain by using external resistors

at the input. To set a gain lower than 12 dB refer to Figure 21 for

differential input configuration and Figure 22 for single-ended

configuration. For external gain configuration from a fixed 12 dB

gain, use the following formula:

External Gain Settings = 20 log[4/(1 + R/150 kΩ)]

To set a gain lower than 6 dB refer to Figure 23 for differential

input configuration and Figure 24 for single-ended configuration.

For external gain configuration from a fixed 6 dB gain, use the

following formula:

External Gain Settings = 20 log[2/(1 + R/150 kΩ)]

Page 12

SSM2301 Preliminary Technical Data

LAYOUT

As output power continues to increase, care needs to be taken to

lay out PCB traces and wires properly between the amplifier,

load, and power supply. A good practice is to use short, wide

PCB tracks to decrease voltage drops and minimize inductance.

Make track widths at least 200 mil for every inch of track length

for lowest DCR, and use 1 oz or 2 oz of copper PCB traces to

further reduce IR drops and inductance. A poor layout

increases voltage drops, consequently affecting efficiency. Use

large traces for the power supply inputs and amplifier outputs to

minimize losses due to parasitic trace resistance. Proper

grounding guidelines help to improve audio performance,

minimize crosstalk between channels, and prevent switching

noise from coupling into the audio signal. To maintain high

output swing and high peak output power, the PCB traces that

connect the output pins to the load and supply pins should be as

wide as possible to maintain the minimum trace resistances. It

is also recommended to use a large-area ground plane for

minimum impedances. Good PCB layouts also isolate critical

analog paths from sources of high interference. High frequency

circuits (analog and digital) should be separated from low

frequency ones. Properly designed multilayer printed circuit

boards can reduce EMI emission and increase immunity to RF

field by a factor of 10 or more compared with double-sided

boards. A multilayer board allows a complete layer to be used

for ground plane, whereas the ground plane side of a doubleside board is often disrupted with signal crossover. If the system

has separate analog and digital ground and power planes, the

analog ground plane should be underneath the analog power

plane, and, similarly, the digital ground plane should be

underneath the digital power plane. There should be no overlap

between analog and digital ground planes nor analog and

digital power planes.

INPUT CAPACITOR SELECTION

The SSM2301 will not require input coupling capacitors if the

input signal is biased from 1.0 V to V

capacitors are required if the input signal is not biased within

this recommended input dc common-mode voltage range, if

high-pass filtering is needed (Figure 19), or if using a singleended source (Figure 20). If high-pass filtering is needed at the

input, the input capacitor along with the input resistor of the

SSM2301 will form a high-pass filter whose corner frequency is

determined by the following equation:

= 1/(2π × RIN × CIN)

f

C

Input capacitor can have very important effects on the circuit

performance. Not using input capacitors degrades the output

offset of the amplifier as well as the PSRR performance.

− 1.0 V. Input

DD

PROPER POWER SUPPLY DECOUPLING

To ensure high efficiency, low total harmonic distortion (THD),

and high PSRR, proper power supply decoupling is necessary.

Noise transients on the power supply lines are short-duration

voltage spikes. Although the actual switching frequency can

range from 10 kHz to 100 kHz, these spikes can contain

frequency components that extend into the hundreds of

megahertz. The power supply input needs to be decoupled with

a good quality low ESL and low ESR capacitor—usually around

4.7 μF. This capacitor bypasses low frequency noises to the

ground plane. For high frequency transients noises, use a 0.1 μF

capacitor as close as possible to the VDD pin of the device.

Placing the decoupling capacitor as close as possible to the

SSM2301 helps maintain efficiency performance.

Page 13

Preliminary Technical Data SSM2301

EVALUATION BOARD INFORMATION

INTRODUCTION

The SSM2301 audio power amplifier is a complete low power,

Class-D, stereo audio amplifier capable of delivering 1.4 W/channel

into 8 Ω load. In addition to the minimal parts required for the

application circuit, measurement filters are provided on the

evaluation board so that conventional audio measurements can

be made without additional components.

This section provides an overview of Analog Devices SSM2301

evaluation board. It includes a brief description of the board as

well as a list of the board specifications.

Table 5. SSM2301 Evaluation Board Specifications

Parameter Specification

Supply Voltage Range, VDD 2.5 V to 5.0 V

Power Supply Current Rating 1.5 A

Continuous Output Power, PO

= 8 Ω, f = 1 kHz, 22 kHz BW)

(R

L

Minimum Load Impedance 8 Ω

1.4 W

OPERATION

Use the following steps when operating the SSM2301

evaluation board.

Power and Ground

1. Set the power supply voltage between 2.5 V and 5.0 V. When

connecting the power supply to the SSM2301 evaluation

board, make sure to attach the ground connection to the

GND header pin first and then connect the positive supply

to the VDD header pin.

Inputs and Outputs

1. Ensure that the audio source is set to the minimum level.

Gain Control

The gain select header controls the gain setting of the SSM2301.

1. Select jumper to LG for 6 dB gain.

2. Select jumper to HG for 12 dB gain.

External Gain Settings

It is possible to adjust the SSM2301 gain using external resistors

at the input. To set a gain lower than 12 dB refer to Figure 21

and Figure 22 on the product data sheet for proper circuit configuration. For external gain configuration from a fixed 12 dB

gain, use the following formula:

External Gain Settings = 20 log[4/(1 + R/150 kΩ)]

To set a gain lower than 6 dB refer to Figure 23 and Figure 24

on the product data sheet for proper circuit configuration. For

external gain configuration from a fixed 6 dB gain, use the

following formula:

External Gain Settings = 20 log[2/(1 + R/150 kΩ)]

Shutdown Control

The shutdown select header controls the shutdown function of

the SSM2301. The shutdown pin on the SSM2301 is active low,

meaning that a low voltage (GND) on this pin places the SSM2301

into shutdown mode.

1. Select jumper to 1-2 position. Shutdown pulled to V

2. Select jumper to 2-3 position. Shutdown pulled to GND.

DD

.

Input Configurations

1. For differential input configuration with input capacitors

do not place a jumper on J2 and J3.

2. Connect the audio source to Inputs IN± and IN±.

3. Connect the speakers to Outputs OUT± and OUT±.

2. For differential input configuration without input capacitors

place a jumper on J2 and J3.

Page 14

SSM2301 Preliminary Technical Data

SSM2301 APPLICATION BOARD SCHEMATIC

J3

POWER

12

V

DD

J2

12

J1

4

3

2

1

C1

0.1µF

C2

0.1µF

2

SD

GAIN

1

C7

0.1µFC60.1µFC510µF

1

SD

2

GAIN

3

IN+

4

IN–

8

OUT–

7

GND

6

VDD V

5

OUT+

J4

1

OUTPUT

2

DD

JP3

V

DD

R3

100kΩ

GAIN SD

JP6

1

3

5

HEADER 3X2

V

DD

2

4

6

R4

100kΩ

Figure 25. SSM2301 Application Board Schematic

06163-025

Page 15

Preliminary Technical Data SSM2301

SSM2301 STEREO CLASS-D AMPLIFIER EVALUATION MODULE COMPONENT LIST

Table 6.

Reference Description Footprint Quantity Manufacturer/Part Number

C6, C7 Capacitor, 0.1 μF 0603 2 Murata Manufacturing Co., Ltd./GRM18

C5 Capacitor, 10 μF 0805 1 Murata Manufacturing Co., Ltd./GRM21

C1, C2, C3, C4 Capacitor, 1 nF 0402 4 Murata Manufacturing Co., Ltd./GRM15

R3, R4 Resistor, 100 kΩ 0603 2 Vishay/CRCW06031003F

L1, L2, Ferrite bead 0402 2 Murata Manufacturing Co., Ltd./BLM15EG121

U1 IC, SSM2301 3.0 mm × 3.0 mm 1 SSM2301CSPZ

EVAL BOARD PCB evaluation board 1

Page 16

SSM2301 Preliminary Technical Data

SSM2301 APPLICATION BOARD LAYOUT

06163-035

Figure 26. SSM2301 Application Board Layout

Page 17

Preliminary Technical Data SSM2301

R

OUTLINE DIMENSIONS

0.50

0.40

0.30

1

4

1.50

REF

PIN 1

INDICATO

1.89

1.74

1.59

PIN 1

INDICATOR

3.00

BSC SQ

TOP

VIEW

2.75

BSC SQ

0.50

BSC

0.60 MAX

8

5

1.60

1.45

1.30

0.90 MAX

0.85 NOM

SEATING

PLANE

12° MAX

0.30

0.23

0.18

0.70 MAX

0.65 TYP

0.05 MAX

0.01 NOM

0.20 REF

Figure 27. 16-Lead Lead Frame Chip Scale Package [LFCSP_VD]

3 mm × 3 mm Body, Very Thin, Dual Lead

(CP-8-2)

Dimensions shown in millimeters

ORDERING GUIDE

Model Temperature Range Package Description Package Option Branding

SSM2301CPZ-R21 −40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_VD] CP-8-2 A1C

SSM2301CPZ-REEL1 −40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_VD] CP-8-2 A1C

SSM2301CPZ-REEL71 −40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_VD] CP-8-2 A1C

1

Z = Pb-free part.

Page 18

SSM2301 Preliminary Technical Data

NOTES

Page 19

Preliminary Technical Data SSM2301

NOTES

©2006 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

Loading...

Loading...